# Libero® SoC v2021.1

# SmartTime Static Timing Analyzer (STA) User Guide

### Introduction

SmartTime is a Libero<sup>®</sup> SoC interactive gate-level static timing analysis tool that allows you to visualize and identify timing issues in your designs. Using this tool, you can evaluate how close you are to meeting your timing requirements, create custom sets to track, set timing exceptions to obtain timing closure, and define cross-probe paths with other tools.

SmartTime is supported in SmartFusion<sup>®</sup>2, IGLOO<sup>®</sup>2, RTG4<sup>™</sup>, PolarFire<sup>®</sup>, and PolarFire SoC families.

Key SmartTime features allow you to:

- Perform complete timing analysis of your design to ensure that your designs meet all timing constraints and operate at the desired speed, with the appropriate amount of margin across all operating conditions.

- Browse through your design's various clock domains to examine the timing paths and identify those that violate

your timing requirements.

- · Create customizable timing reports.

- Navigate directly to the paths responsible for violating your timing requirements.

**Note:** Creating and editing timing constraints are handled in a separate Timing Constraints Editor. For more information, see the Timing Constraints Editor User Guide.

# **Table of Contents**

| Intr | oducti                    | on                                          | 1  |

|------|---------------------------|---------------------------------------------|----|

| 1.   | Abou                      | t SmartTime                                 | 5  |

|      | 1.1.                      | Static Timing Analysis (STA)                | 5  |

|      | 1.2.                      | Timing Constraints                          |    |

|      | 1.3.                      | Timing Analysis                             |    |

|      | 1.4.                      | SmartTime and Place and Route               |    |

|      | 1.5.                      | Timing Reports                              | 5  |

|      | 1.6.                      | Cross-probing into Chip Planner             | 6  |

|      | 1.7.                      | Cross-probing into Constraints Editor       | 6  |

| 2.   | Desi                      | gn Flows with SmartTime                     | 7  |

| 3.   | Starti                    | ng and Closing SmartTime                    | 8  |

| 4.   | Confi                     | guring SmartTime Settings                   | g  |

|      | 4.1.                      | Configuring SmartTime General Settings      | 9  |

|      | 4.2.                      | Configuring SmartTime Analysis Settings     | 10 |

|      | 4.3.                      | Configuring SmartTime Advanced Settings     | 11 |

| 5.   | Smar                      | tTime Toolbar                               | 13 |

| 6.   | Smar                      | tTime Timing Analyzer                       | 14 |

|      | 6.1.                      | SmartTime Analyzer Components               | 14 |

|      | 6.2.                      | Analyzing Your Design                       |    |

|      | 6.3.                      | Maximum Delay Analysis View                 |    |

|      | 6.4.                      | Managing Clock Domains                      | 15 |

|      | 6.5.                      | Managing Path Sets                          | 16 |

|      | 6.6.                      | Displaying Path List Timing Information     | 18 |

|      | 6.7.                      | Displaying Expanded Path Timing Information | 19 |

|      | 6.8.                      | Using Filters                               | 21 |

| 7.   | Adva                      | nced Timing Analysis                        | 23 |

|      | 7.1.                      | Understanding Inter-Clock Domain Analysis   | 23 |

|      | 7.2.                      | Activating Inter-Clock Domain Analysis      | 23 |

|      | 7.3.                      | Displaying Inter-Clock Domain Paths         | 24 |

|      | 7.4.                      | Deactivating a Specific Inter-Clock Domain  |    |

|      | 7.5.                      | Changing Output Port Capacitance            | 26 |

| 8.   | Generating Timing Reports |                                             | 28 |

|      | 8.1.                      | Types of Reports                            | 28 |

|      | 8.2.                      | Generating a Timing Report                  |    |

|      | 8.3.                      | Understanding Timing Reports                |    |

|      | 8.4.                      | Generating a Timing Violation Report        |    |

|      | 8.5.                      | Understanding Timing Violation Reports      |    |

|      | 8.6.                      | Generating a Constraints Coverage Report    |    |

|      | 8.7.                      | Understanding Constraints Coverage Reports  |    |

|      | 8.8.                      | Generating a Bottleneck Report              | 34 |

|     | 8.9. Understanding Bottleneck Reports - SmartFusion2, IGL  | .002, RTG4, and PolarFire | 34  |

|-----|------------------------------------------------------------|---------------------------|-----|

|     | 8.10. Generating a Datasheet Report                        |                           | 35  |

|     | 8.11. Understanding Datasheet Reports                      |                           | 35  |

|     | 8.12. Generating a Combinational Loop Report               |                           | 37  |

|     | 8.13. Understanding Combinational Loop Reports             |                           | 37  |

|     | 8.14. Generating a Clock Domain Crossing (CDC) Report      |                           | 38  |

| 9.  | ). Timing Concepts                                         |                           | 48  |

|     | 9.1. Static Timing Analysis Versus Dynamic Simulation      |                           | 48  |

|     | 9.2. Delay Models                                          |                           |     |

|     | 9.3. Timing Path Types                                     |                           | 48  |

|     | 9.4. Maximum Clock Frequency                               |                           | 48  |

|     | 9.5. Setup Check                                           |                           | 49  |

|     | 9.6. Arrival Time, Required Time, and Slack                |                           | 49  |

|     | 9.7. Timing Exceptions Overview                            |                           | 49  |

|     | 9.8. Clock Skew                                            |                           | 50  |

|     | 9.9. Cross Probing                                         |                           | 50  |

| 10. | SmartTime Tutorials                                        |                           | 56  |

|     | 10.1. Tutorial 1 - 32-Bit Shift Register with Clock Enable |                           | 56  |

|     | 10.2. Tutorial 2 - False Path Constraints                  |                           | 68  |

| 11. | SmartTime Dialog Boxes                                     |                           | 78  |

|     | 11.1. Add Path Analysis Set Dialog Box                     |                           | 78  |

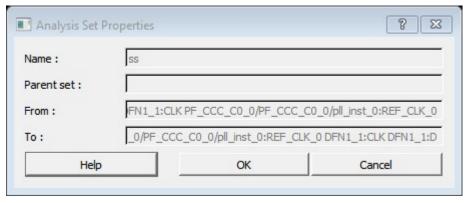

|     | 11.2. Analysis Set Properties Dialog Box                   |                           | 79  |

|     | 11.3. Edit Filter Set Dialog Box                           |                           | 80  |

|     | 11.4. Customize Analysis View Dialog Box                   |                           | 80  |

|     | 11.5. Manage Clock Domains Dialog Box                      |                           | 82  |

|     | 11.6. Set False Path Constraint Dialog Box                 |                           | 82  |

|     | 11.7. SmartTime Options Dialog Box                         |                           | 83  |

|     | 11.8. Create Filter Set Dialog Box                         |                           | 86  |

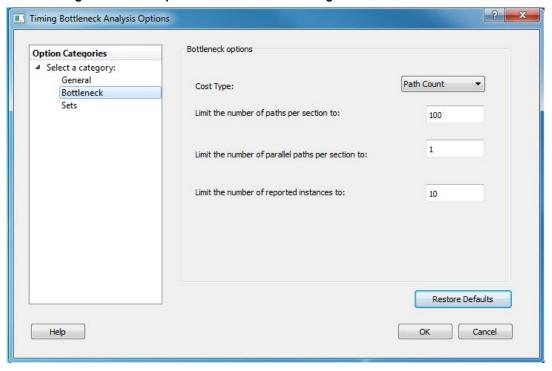

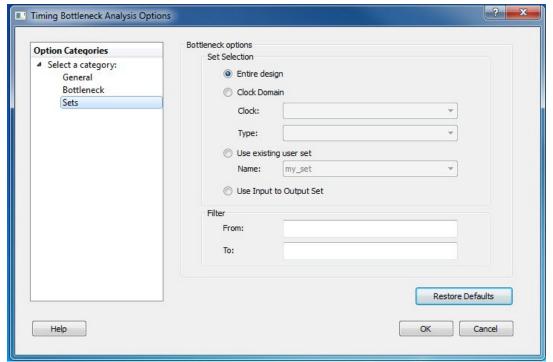

|     | 11.9. Timing Bottleneck Analysis Options Dialog Box        |                           | 87  |

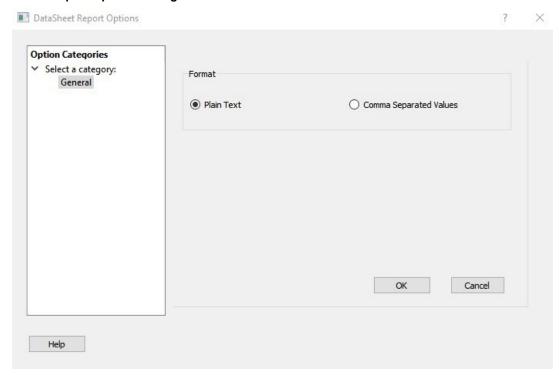

|     | 11.10. Timing Datasheet Report Options Dialog Box          |                           |     |

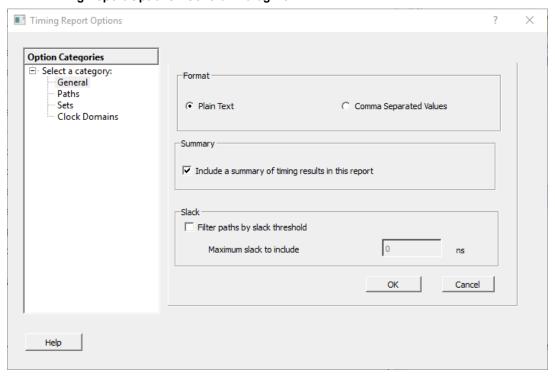

|     | 11.11. Timing Report Options Dialog Box                    |                           |     |

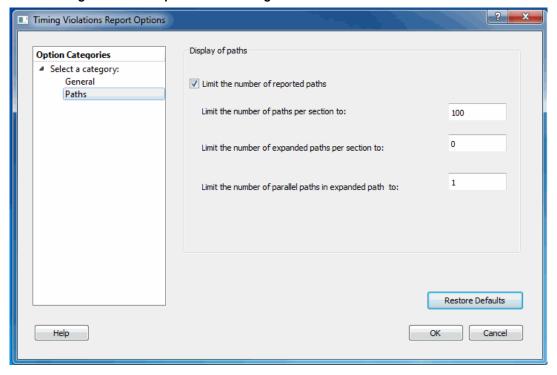

|     | 11.12. Timing Violations Report Options Dialog Box         |                           |     |

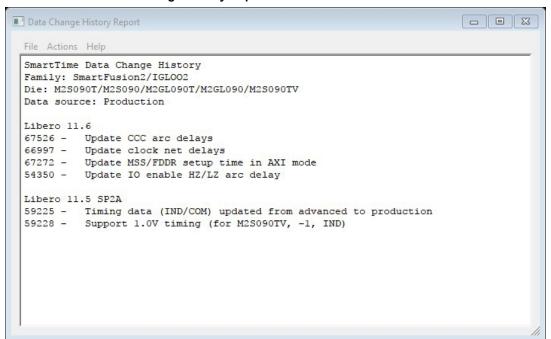

|     | 11.13. Data Change History - SmartTime                     |                           | 96  |

| 12. | 2. Tcl Commands                                            |                           | 98  |

| 13. | 3. Glossary                                                |                           | 99  |

| 14. | 4. Revision History                                        |                           | 102 |

| 15. | Microchip FPGA Technical Support                           |                           | 103 |

|     | 15.1. Customer Service                                     |                           |     |

|     | 15.2. Customer Technical Support                           |                           |     |

|     | 15.3. Website                                              |                           |     |

|     | 15.4. Outside the U.S                                      |                           |     |

| The | he Microchip Website                                       |                           | 104 |

# Libero® SoC v2021.1

| Product Change Notification Service       | 104 |

|-------------------------------------------|-----|

| Customer Support                          | 104 |

| Microchip Devices Code Protection Feature | 104 |

| Legal Notice                              | 105 |

| Trademarks                                | 105 |

| Quality Management System                 | 106 |

| Worldwide Sales and Service               | 107 |

### 1. About SmartTime

The following sections describe SmartTime functions.

### 1.1 Static Timing Analysis (STA)

Static timing analysis (STA) offers an efficient technique for identifying timing violations in your design and ensuring that it meets all your timing requirements. You can communicate timing requirements and timing exceptions to the system by setting timing constraints. A static timing analysis tool will then check and report setup and hold violations as well as violations on specific path requirements.

STA is particularly well suited for traditional synchronous designs. The main advantage of STA is that unlike dynamic simulation, it does not require input vectors. It covers all possible paths in the design and does all the above with relatively low run-time requirements.

The major disadvantage of STA is that the STA tools do not automatically detect false paths in their algorithms as it reports all possible paths, including false paths, in the design. False paths are timing paths in the design that do not propagate a signal. To get a true and useful timing analysis, you need to identify those false paths, if any, as false path constraints to the STA tool and exclude them from timing considerations.

The SmartTime user interface provides efficient, user-friendly ways to define these critical false paths.

### 1.2 Timing Constraints

SmartTime supports a range of timing constraints to provide useful analysis and efficient timing-driven layout.

#### 1.3 Timing Analysis

SmartTime provides a selection of analysis types that allow you to:

- Find the minimum clock period/highest frequency that does not result in a timing violations

- · Identify paths with timing violations

- · Analyze delays of paths that have no timing constraints

- · Perform inter-clock domain timing verification

- · Perform maximum and minimum delay analysis for setup and hold checks

To improve the accuracy of the results, SmartTime evaluates clock skew during timing analysis by computing individual clock insertion delays for each register.

SmartTime checks the timing requirements for violations while evaluating timing exceptions such as multicycle or false paths.

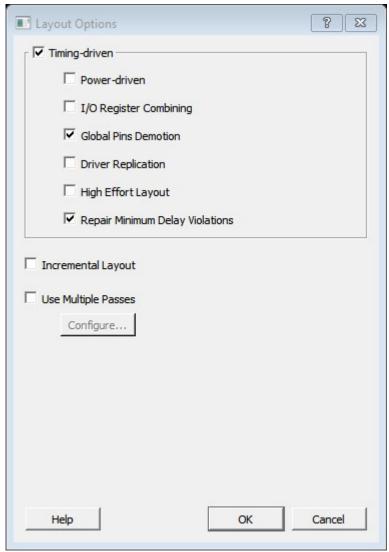

### 1.4 SmartTime and Place and Route

Libero SoC Place and Route uses SmartTime STA during timing-driven place-and-route operations run in the background. As a result, your analysis and place and route constraints are always consistent.

#### 1.5 Timing Reports

SmartTime provides robust reporting capabilities that allow you to generate the following report files:

- · Timing Report for Max and Min Delay Analysis

- · Timing Violations Report for Max and Min Delay Analysis

- · Bottleneck Report

- Constraints Coverage Report

· Combinational Loop Report

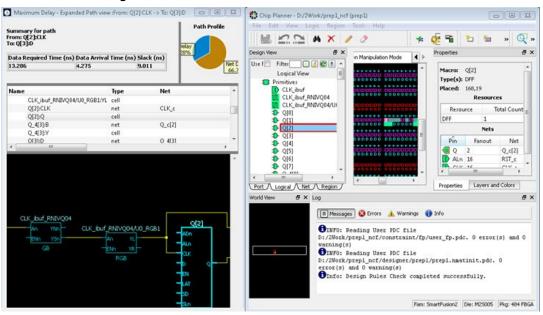

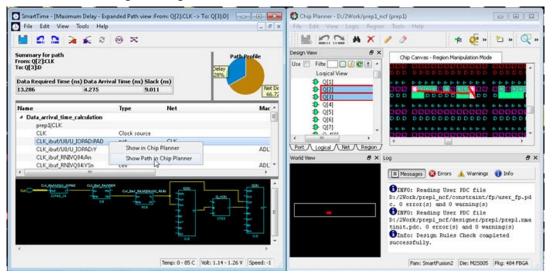

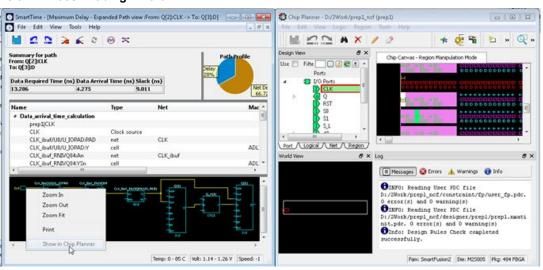

# 1.6 Cross-probing into Chip Planner

From SmartTime, you can select a design object and cross-probe the same design object in Chip Planner.

Design objects that can be cross-probed from SmartTime to Chip Planner include:

- Ports

- Macros

- Timing paths

# 1.7 Cross-probing into Constraints Editor

From SmartTime, you can cross-probe into the Constraints Editor. The Constraints Editor must be running for cross-probing to work.

For more information, see 9.9.3 Cross-probing from SmartTime to Chip Planner.

# 2. Design Flows with SmartTime

You can access SmartTime in Libero SoC during the following design implementation phases:

- During Place and Route when you select timing-driven place-and-route, SmartTime runs in the background to provide accurate timing information.

- After Place and Route run SmartTime to perform post-layout timing analysis and adjust timing constraints. In the Libero SoC Design Flow window, expand Implement Design > Verify Post-Layout Implementation and then either:

- Double-click **Verify Timing** to generate Timing Reports.

- Right-click Open SmartTime > Open Interactively to run SmartTime.

- During Back-Annotation SmartTime runs in the background to generate the SDF file for timing simulation.

You can also run SmartTime to generate Timing Reports, regardless of which design implementation phase you are in

For more information about Place and Route and Back-Annotation, see the Libero SoC User Guide.

# **Starting and Closing SmartTime**

# 3. Starting and Closing SmartTime

You must complete Place and Route for your design before using SmartTime interactively. Otherwise, Libero SoC completes that phase before starting SmartTime.

To open SmartTime interactively:

- 1. Select Implement Design > Verify Post Layout Implementation.

- Right-click Open SmartTime and select Open Interactively.

SmartTime reads your design and displays post- or pre-layout timing information.

To close SmartTime, choose Exit from the File menu.

# 4. Configuring SmartTime Settings

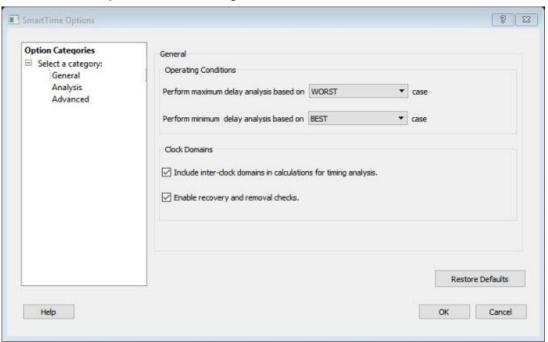

The SmartTime Options dialog box allows you to change general, analysis, and advanced settings.

# 4.1 Configuring SmartTime General Settings

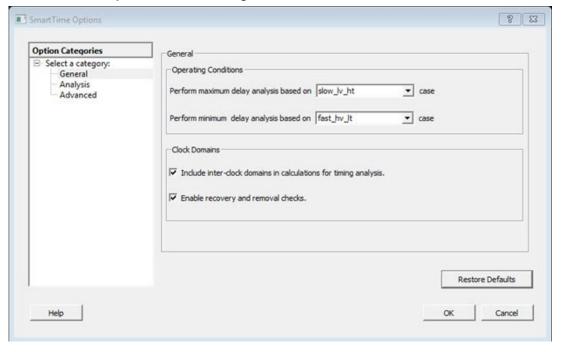

To configure **General** settings in the SmartTime Options dialog box:

1. From the SmartTime Maximum/Minimum Delay Analysis View window, choose **Tools > Options**. The SmartTime Options dialog box appears.

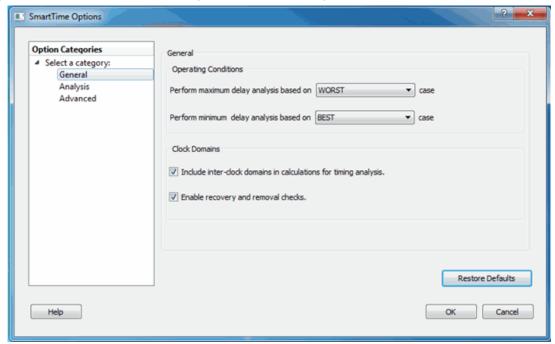

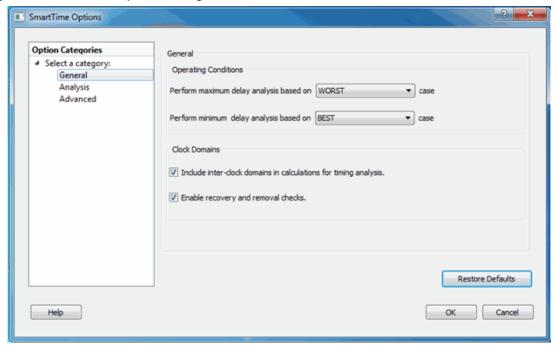

Figure 4-1. SmartTime Options Dialog Box - General Settings for SmartFusion<sup>®</sup>2, IGLOO<sup>®</sup>2, and RTG4<sup>™</sup>

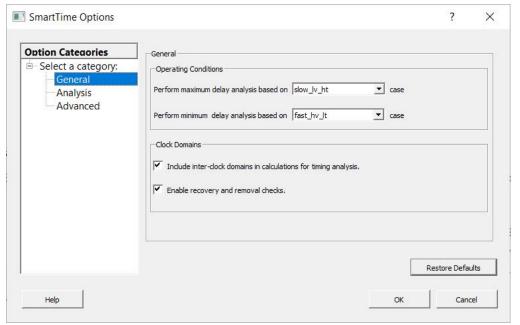

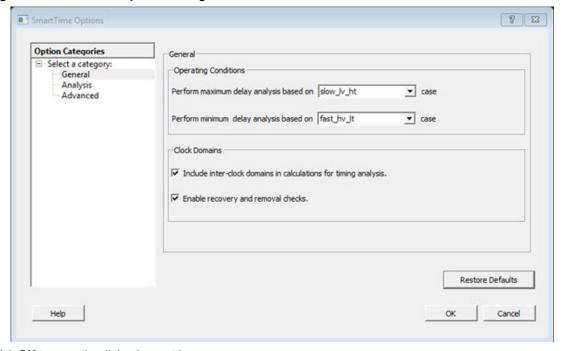

Figure 4-2. SmartTime Options Dialog Box - General Settings for PolarFire

- 2. In the **General** category, select the settings for the operating conditions. SmartTime performs maximum or minimum delay analysis based on the best, typical, or worst case.

- 3. Specify whether you want SmartTime to use inter-clock domains in calculations for timing analysis.

- 4. To revert the **General** settings to their default value, click **Restore Defaults**.

- 5. Change Analysis and Advanced settings as necessary.

- 6. When finished, click **OK**.

# 4.2 Configuring SmartTime Analysis Settings

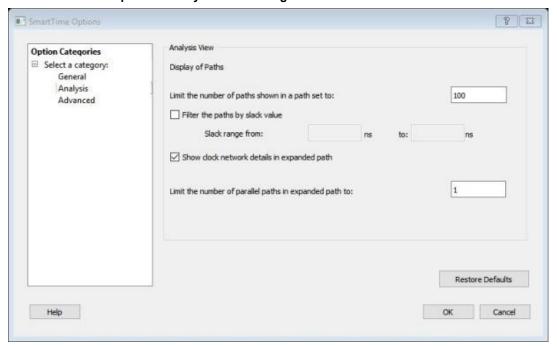

To configure **Analysis** settings in the SmartTime Options dialog box:

- 1. From the SmartTime Maximum/Minimum Delay Analysis View window, choose **Tools > Options**. The SmartTime Options dialog box appears.

- 2. In the left pane, click Analysis.

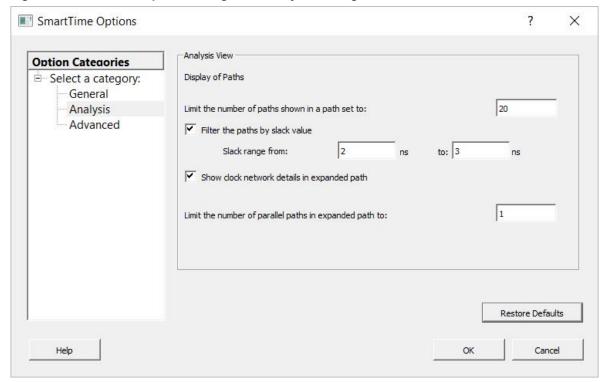

Figure 4-3. SmartTime Options Dialog Box - Analysis Settings

- 3. Enter a number greater than 1 to specify the maximum number of paths to include in a path set during timing analysis.

- 4. Check or uncheck whether to filter the paths by slack value. If you check this box, specify the slack range between the minimum slack and maximum slack.

- 5. Check or uncheck whether to include clock network details.

- 6. To specify the number of parallel paths in the expanded path, enter a number greater than 1.

- 7. To revert the **Analysis** settings to their default value, click **Restore Defaults**.

- 8. Change **General** and **Advanced** settings as necessary.

- 9. When finished, click **OK**.

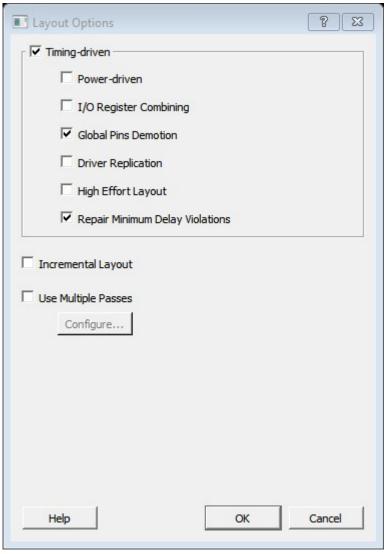

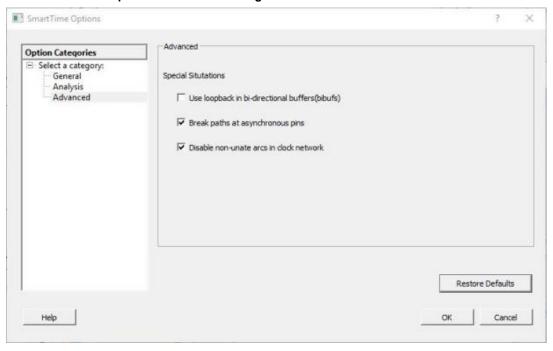

#### 4.3 Configuring SmartTime Advanced Settings

To configure **Advanced** settings in the SmartTime Options dialog box:

- 1. From the SmartTime Maximum/Minimum Delay Analysis View window, choose **Tools > Options**. The SmartTime Options dialog box appears.

- 2. In the left pane, click Advanced.

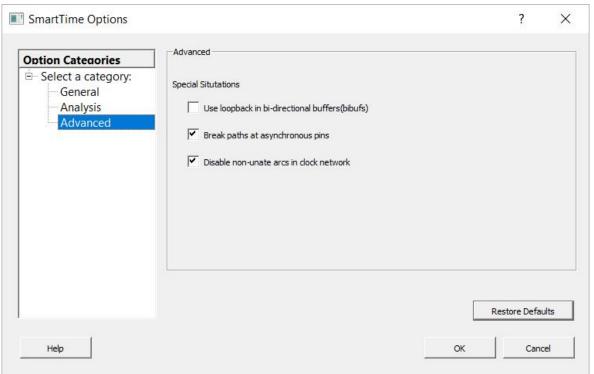

Figure 4-4. SmartTime Options Dialog Box - Advanced Settings

- 3. Specify whether to use loopback in bidirectional buffers (bibufs) and/or break paths at asynchronous pins. The specify whether to disable non-unate arcs in the clockpath.

- 4. To revert the **Advanced** settings to their default value, click **Restore Defaults**.

- 5. Change General and Analysis settings as necessary.

- 6. When finished, click OK.

# **SmartTime Toolbar**

# 5. SmartTime Toolbar

The SmartTime toolbar contains icons for constraining or analyzing designs. Tool tips are available for each icon.

Table 5-1. SmartTime Toolbar Icons

| Icon        | Description                             |

|-------------|-----------------------------------------|

|             | Saves the changes.                      |

| <u> </u>    | Undoes previous changes.                |

| <u>C</u>    | Redoes previous changes.                |

| <u>&gt;</u> | Opens the maximum delay analysis view.  |

| <u></u>     | Opens the minimum delay analysis view.  |

| <u></u>     | Opens the manage clock domains manager. |

| ×           | Opens the path set manager.             |

| 0           | Recalculates all analyses.              |

# 6. SmartTime Timing Analyzer

The following sections describe the SmartTime Timing Analyzer functions.

### 6.1 SmartTime Analyzer Components

SmartTime Timing Analyzer consists of the following components:

- Domain Browser: allows you to perform your timing analysis on a per domain basis.

- · Path List: shows paths in a specific set within a given domain sorted by slack.

- Path Details: shows detailed timing analysis of a selected path in the paths list.

- Analysis View Filter: allows you to filter the content of the paths list.

- Path Slack Histogram: when a set is selected in the Domain Browser, Path Slack Histogram shows a distribution

of the path slacks for that set. Selecting one or multiple bars in the Path Slack Histogram filters the paths shown

in the Path List.

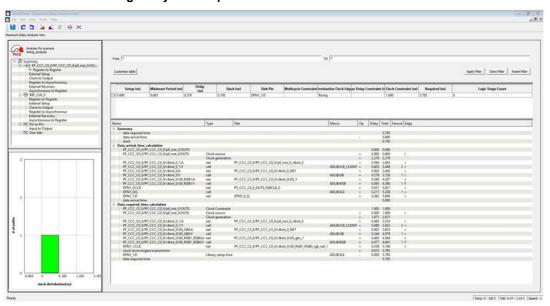

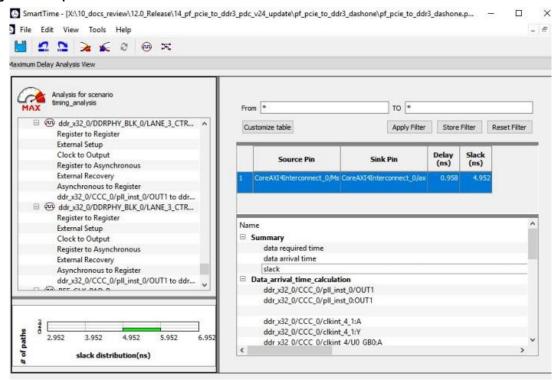

The following figure shows the SmartTime Timing Analyzer Components. You can copy and change the resolution and number of bars of the chart from the right-click menu.

Figure 6-1. SmartTime Timing Analyzer Components

### 6.2 Analyzing Your Design

The timing engine uses the following priorities when analyzing paths and calculating slack:

- 1. False path

- 2. Max/Min delay

- 3. Multi-cycle path

- 4. Clock

If multiple constraints of the same priority apply to a path, the timing engine uses the tightest constraint.

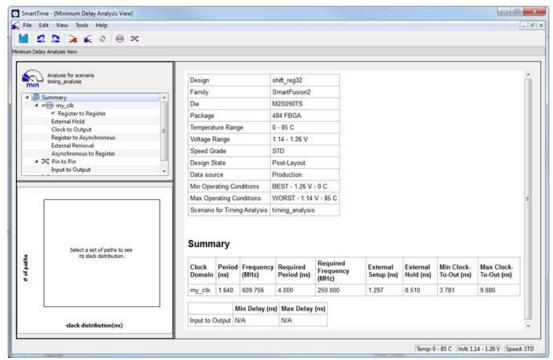

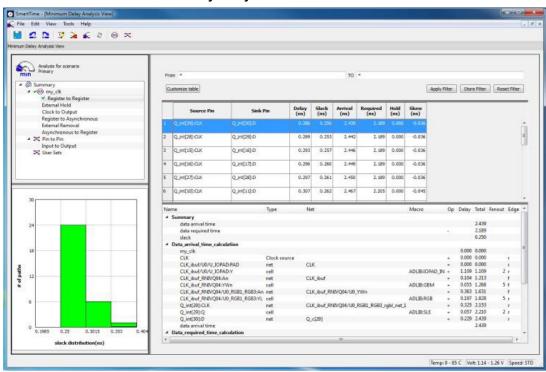

You can perform two types of timing analysis:

- Maximum Delay Analysis

- Minimum Delay Analysis

To perform the basic timing analysis, use one of the following methods to open the Timing Analysis View:

- From the SmartTime Tools menu, choose Timing Maximum Delay Analysis or Minimum Delay Analysis.

- From the SmartTime window, click the icon for Maximum Delay Analysis or the icon for Minimum Delay Analysis.

Note: When you open the Timing Analyzer from Designer, the Maximum Delay Analysis window appears by default.

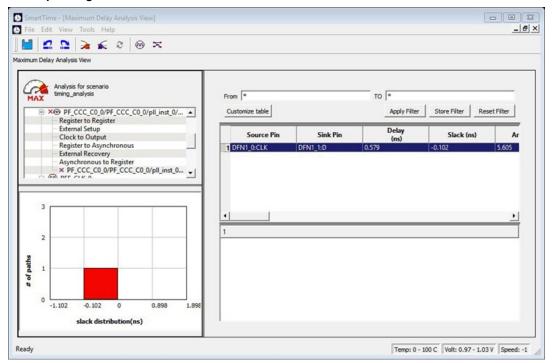

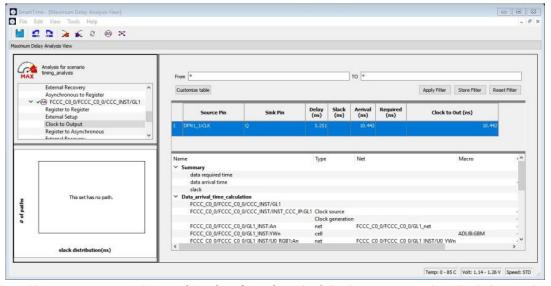

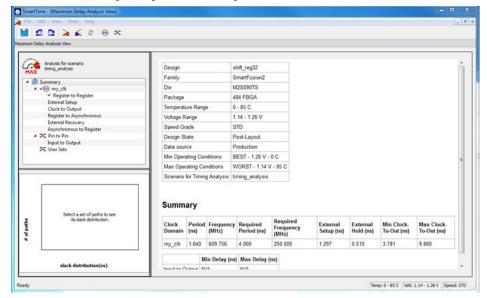

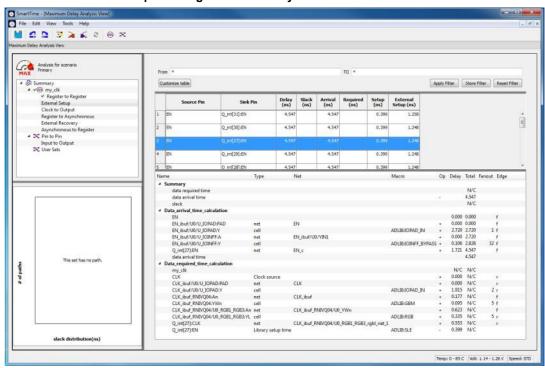

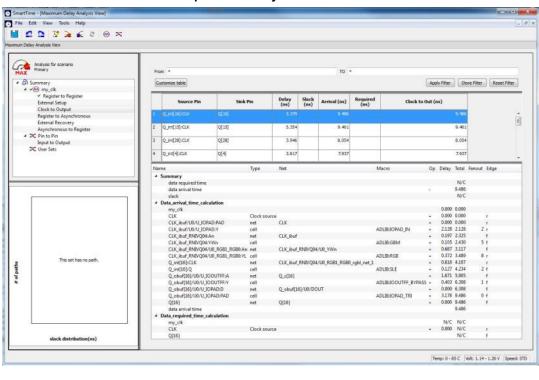

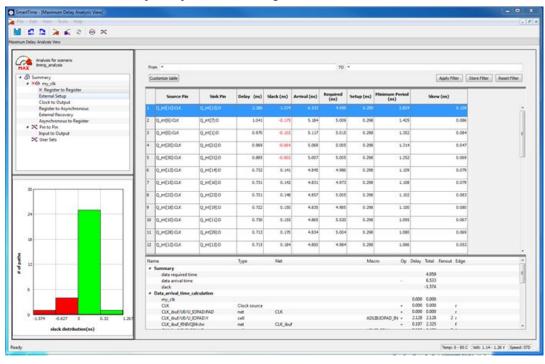

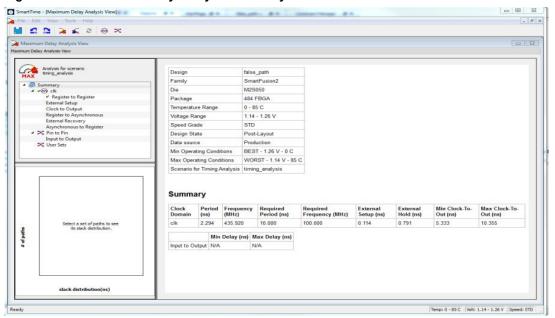

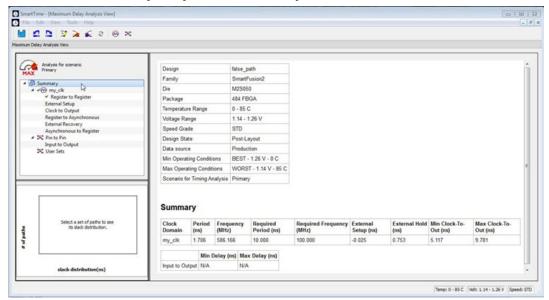

### 6.3 Maximum Delay Analysis View

To enter Maximum Delay Analysis View:

- 1. In the Domain Browser, select the clock domain. Clock domains with a ★ indicate that the timing requirements in these domains were met. Clock domains with an x indicate that there are violations within these domains. **Paths List** shows the timing paths sorted by slack. The path with the lowest slack (biggest violation) is at the top of the list.

- 2. Select the path you want to view.

- **Path Details** below the **Paths List** shows detailed information about how the slack was computed by detailing the arrival time and required time calculation. If a path is violated, the slack is negative and shown in red.

- 3. To display a separate view that includes the path details and schematic, double-click the path.

- 4. Repeat this procedure as necessary.

**Note:** If the minimum pulse width of one element on the critical path limits the maximum frequency for the clock, an icon for the clock name appears in the **Summary List**. Clicking the icon displays the name of the pin that limits the clock frequency.

#### 6.4 Managing Clock Domains

In SmartTime, timing paths are organized by clock domains.

By default, SmartTime displays domains with explicit clocks. Each clock domain includes at least three path sets:

- Register to Register

- External Setup (in the Maximum Analysis View) or External Hold (in the Minimum Analysis View)

- Clock to Out

You must select a path set to display a list of paths in that specific set.

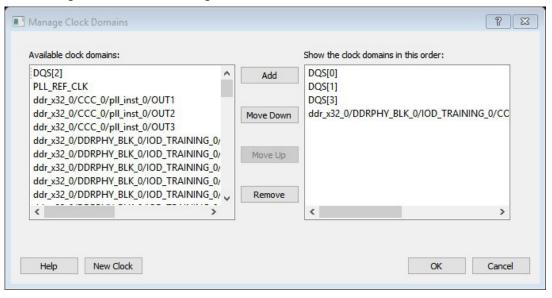

To manage the clock domains:

Right-click anywhere in the Domain Browser and choose Manage Clock Domains.

The Manage Clock Domains dialog box appears.

**Tip:** You can click the icon in the SmartTime window bar to display the Manage Clock Domains dialog box.

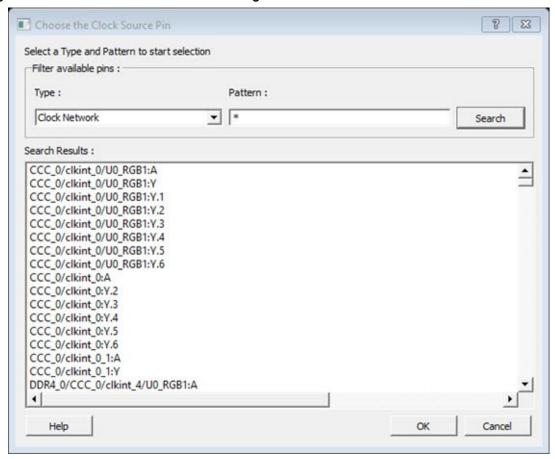

To add a new domain, select a clock domain from the Available clock domains list and click Add. To add a non-explicit clock domain, click New Clock.

The Choose the Clock Source Pin dialog box appears, and you can select the clock source pin. You can choose to filter the available pins and search.

Figure 6-2. Choose the Clock Source Pin Dialog Box

- To remove a displayed domain, select a clock domain from the Show the clock domains in this order list and click Remove.

- 4. To change the display order in the Domain Browser, select a clock domain from the **Show the clock domains** in this order list, and then use **Move Up** or **Move Down** to change the order in the list.

- Click **OK**.

SmartTime updates the Domain Browser based on your specifications. If you added a new clock domain, it includes at least three path sets, as mentioned above.

# 6.5 Managing Path Sets

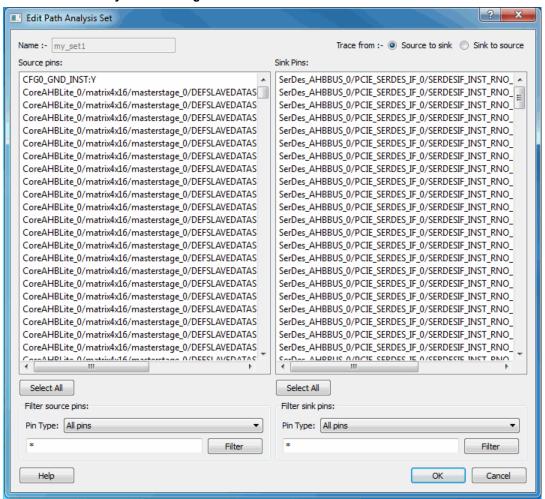

You can create and manage custom path sets for timing analysis and tracking purposes.

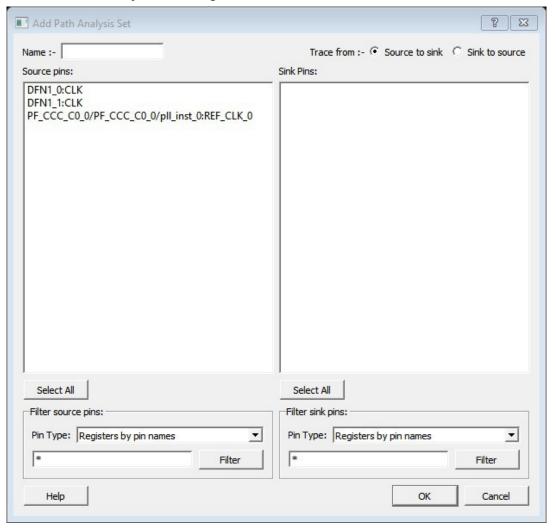

Path sets appear below **Custom Path Sets** at the bottom of the Domain Browser. To manage path sets:

Right-click anywhere in the Domain Browser and choose Add Set.

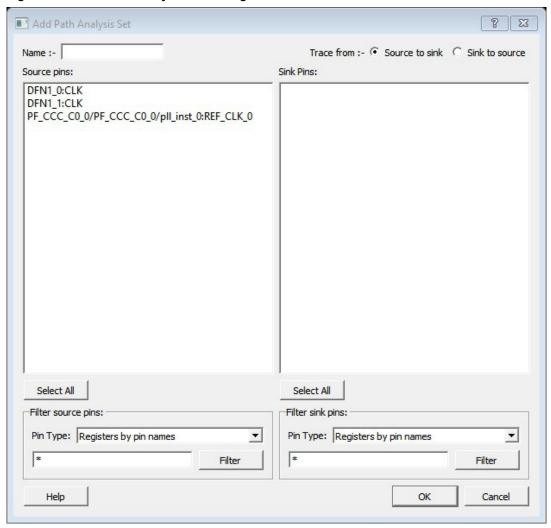

The Add Path Analysis Set Dialog Box appears.

**Tip:** You can click the icon in the SmartTime window bar to display the Add Path Analysis Set dialog box.

Figure 6-3. Add Path Analysis Set Dialog Box

- 2. Enter a name for the path set.

- 3. Select the source and sink pins. You can use the filters to control the type of pins displayed.

- 4. Click **OK**

The new path set appears below User Sets in the Domain Browser.

Figure 6-4. Updated Domain Browser with User Sets

- 5. To rename a path:

- a) Select the path set from User Sets in the Domain Browser.

- b) Right-click the set you want to rename, and then choose **Rename Set** from the right-click menu.

- c) Edit the name directly in the Domain Browser.

- 6. To remove a path:

- a) Select the path set from **User Sets** in the Domain Browser.

- b) Right-click the set you want to delete, and then choose **Delete Set** from the right-click menu.

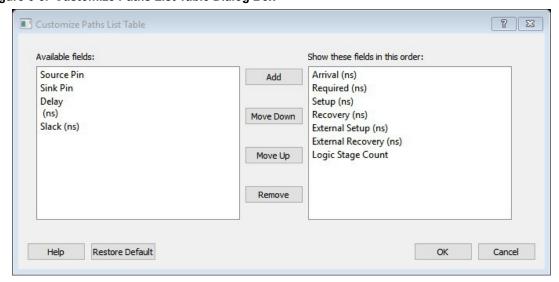

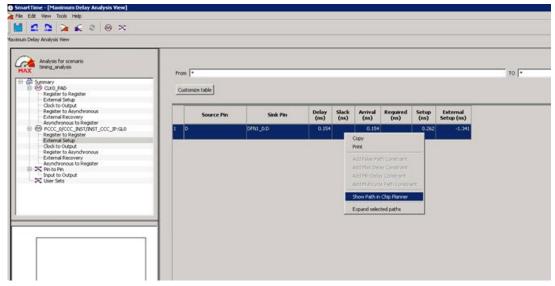

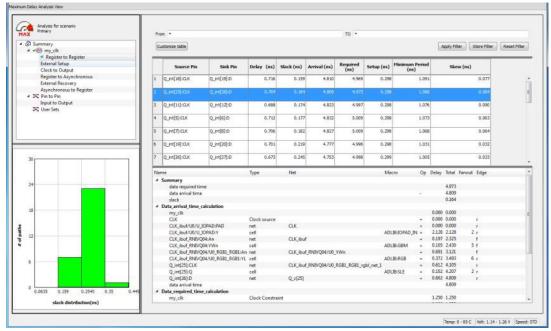

# 6.6 Displaying Path List Timing Information

Path List in the Timing Analysis View shows the timing information required to verify the timing requirements and identify violating paths. The Path List is organized in a grid where each row represents a timing path with the corresponding timing information displayed in columns. Timing information is customizable, allowing you to add or remove columns for each type of set.

By default, each type of set displays the following subset of columns:

- Register to Register: Source Pin, Sink Pin, Delay, Slack, Arrival, Required, Setup, Minimum Period, and Skew.

- · External Setup: Source Pin, Sink Pin, Delay, Slack, Arrival, Required, Setup, and External Setup.

- · Clock to Out: Source Pin, Sink Pin, Delay, Slack, Arrival, Required, and Clock to Out.

- Input to Output: Source Pin, Sink Pin, Delay, and Slack.

- Custom Path Sets: Source Pin, Sink Pin, Delay, and Slack. You can add the following columns for each type of set:

- Register to Register: Clock, Source Clock Edge, Destination Clock Edge, Logic Stage Count, Max Fanout,

Clock Constraint, Maximum Delay Constraint, and Multicycle Constraint.

- External Setup: Clock, Destination Clock Edge, Logic Stage Count, Max Fanout, Clock Constraint, Input Delay Constraint, Required External Setup, Maximum Delay Constraint, and Multicycle Constraint.

- Clock to Out: Clock, Source Clock Edge, Logic Stage Count, Max Fanout, Clock Constraint, Output Delay Constraint, Required Maximum Clock to Out, Maximum Delay Constraint, and Multicycle Constraint.

- Input to Output: Arrival, Required, Setup, Hold, Logic Stage Count, and Max Fanout.

- Custom Path Sets

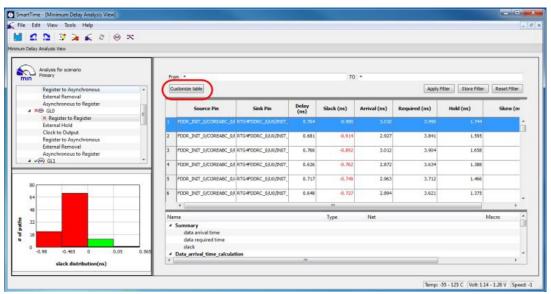

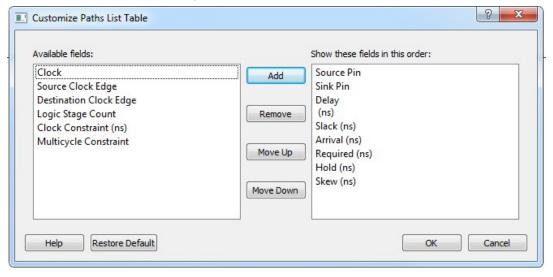

To customize the set of timing information in the Path List:

Choose Customize table on the top-left corner of path list to open the Customize Paths List Table dialog box.

Figure 6-5. Customize Paths List Table Dialog Box

- 2. To add one or more columns, select the fields to add from the Available fields list and click Add.

- To remove one or more columns, select the fields to remove from the Show these fields in this order list, and click Remove.

- To change the order in which the fields appear, select fields in the Show these fields in this order list and click Move Up or Move Down.

- Click **OK** to add or remove the selected columns. SmartTime updates the Timing Analysis View.

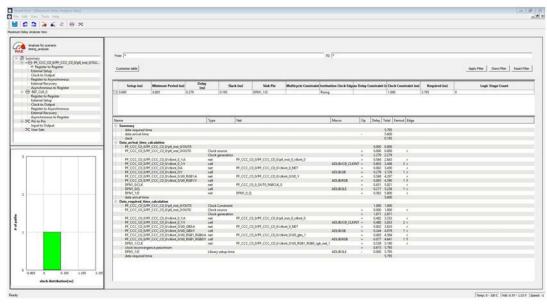

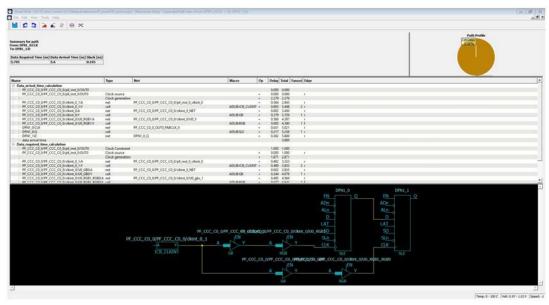

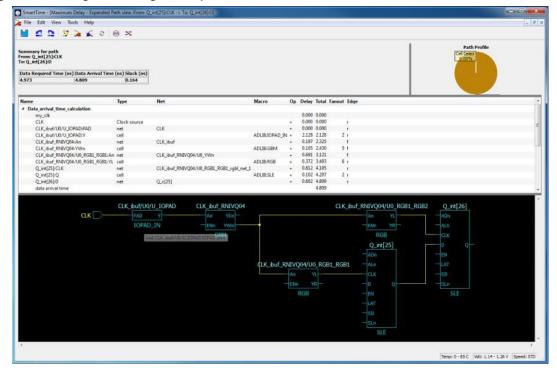

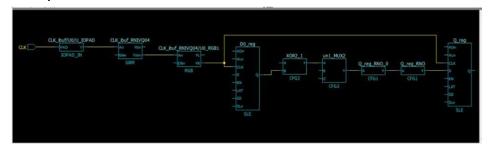

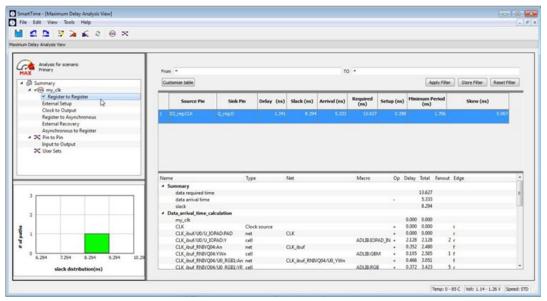

### 6.7 Displaying Expanded Path Timing Information

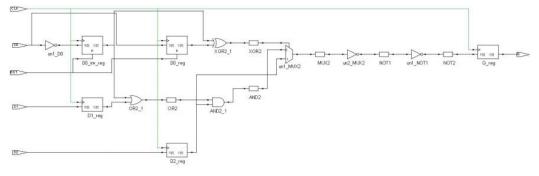

SmartTime displays the list of paths and path details for all parallel paths.

The Path Details grid displays the path details for all parallel paths. The Path List displays all parallel paths in your design.

Figure 6-6. Path List View

To display the Expanded Path View:

- From the Path List, double-click the path, or right-click a path and select expand selected paths.

- 2. From the Expanded Path View, double-click the path, or right-click the path and select **expand path**.

Figure 6-7. Expanded Path View

The Expanded Path Summary provides a summary of all parallel paths for the selected path. The Path Profile chart shows the percentage of time taken by cells and nets for the selected path. If no parallel path is selected in this view, the Path Profile shows the percentage for all paths. By default, SmartTime shows only one path for each Expanded Path. To change this default, use the SmartTime Options dialog box.

The Expanded Path View includes a schematic of the path and a path profile chart for the paths selected in the Expanded Path Summary.

### 6.8 Using Filters

You can use filters in SmartTime to limit the Path List content (that is, create a filtered list on the source and sink pin names).

Filtering options appear at the top of the Timing Analysis View. You can save these filters one level below the set under which they have been created.

To use the filter:

- 1. Select a set in the Domain Browser to display a given number of paths, depending on your SmartTime Options settings (100 paths by default).

- 2. Enter the filter criteria in both the From and To fields, and then click **Apply Filter**. The display limits the paths to those that match your filter criteria.

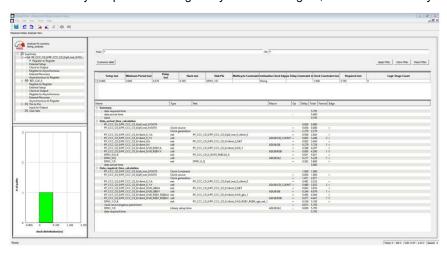

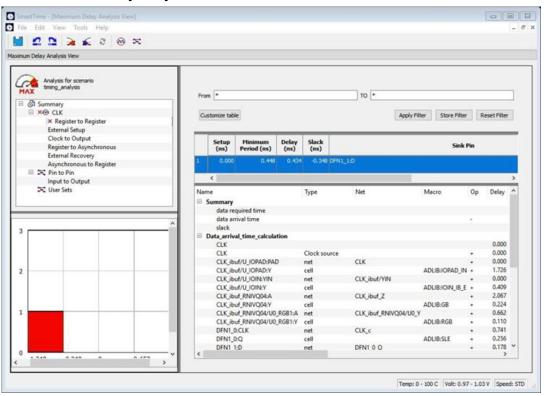

Figure 6-8. Maximum Delay Analysis View

Click Store Filter to save your filter criteria with a special name.

The Create Filter Set dialog box appears.

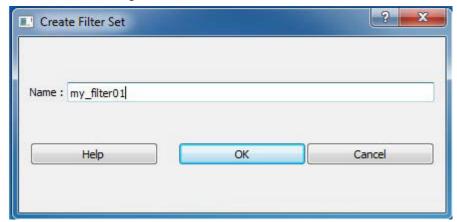

Figure 6-9. Create Filter Set Dialog Box

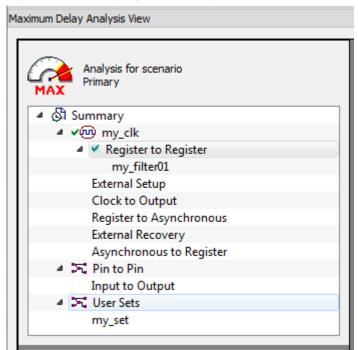

4. Enter a name for the filter, such as myfilter01, and click **OK**. Your new filter name appears below the set under which it was created.

Figure 6-10. Specifying the Filter my\_filter01

- 5. Repeat this procedure to cascade as many sets as you need using the filtering mechanism.

- 6. To edit a filter in the set:

- a) Select the filter you want to edit.

- Right-click the filter and choose **Edit Set** from the shortcut menu.

- 7. To rename a set created with filters:

- Select the set that uses filters.

- b) Right-click the set, and choose **Rename Set** from the shortcut menu.

- c) Edit the name directly in the Domain Browser.

# 7. Advanced Timing Analysis

The following sections describe advanced timing analysis.

### 7.1 Understanding Inter-Clock Domain Analysis

When functional paths exist across two clock domains (the register launching the data and the one capturing it are clocked by two different clock sources), you must provide accurate specification of both clocks to allow a valid inter-clock domain timing check. This is important especially when the clocks are specified with different waveforms and frequencies.

When you specify multiple clocks in your design, consider whether the inter-clock domain paths are false or functional. If the paths are functional, perform setup and hold checks between the clock domains in SmartTime. Unless specified otherwise, SmartTime considers the inter-clock domain as false, and therefore does not perform setup or hold checks between the clock domains.

If you have several clock domains that are subset of a single clock (such as if you want to measure clock tree delay from an input clock to a generated clock), you must configure Generated Clock Constraints for each of the clock domains in order for SmartTime to execute the calculation and show timing for each of the inter-clock domain paths.

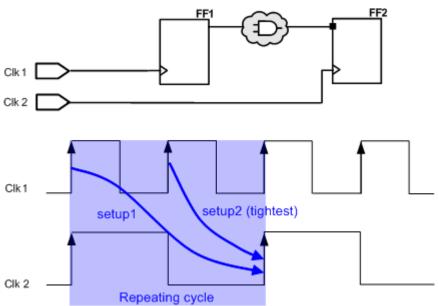

Once you include the inter-clock domains for timing analysis, SmartTime analyzes for each inter-clock domain the relationship between all the active clock edges over a common period equal to the least common multiple of the two clock periods. The new common period represents a full repeating cycle (or pattern) of the two clock waveforms (as shown below).

Figure 7-1. New Common Period

For setup check, SmartTime considers the tightest relation launch-capture to ensure that the data arrives before the capture edge. The hold check verifies that a setup relationship is not overwritten by a following data launch.

# 7.2 Activating Inter-Clock Domain Analysis

To activate the inter-clock domain checking:

- From the SmartTime Tools menu, choose Options.

The SmartTime Options dialog box dialog box appears (as shown below).

- 2. In the General category, check Include inter-clock domains in calculations for timing analysis.

Figure 7-2. SmartTime Options Dialog Box for SmartFusion2, RTG4, and IGLOO2

Figure 7-3. SmartTime Options Dialog Box for PolarFire

Click **OK** to save the dialog box settings.

### 7.3 Displaying Inter-Clock Domain Paths

After you activate the inter-clock domain checking for a given clock domain CK1, SmartTime detects automatically all other domains CKn with paths ending at CK1.

SmartTime creates inter-clock domain sets CKn to CK1 under the domain CK1. Each set allows you to display the inter-clock domain paths between a given clock domain and CK1.

To display an inter-clock domain set:

1. Expand the receiving clock domain of the inter-clock domain in the Domain Browser to display its related sets. For the inter-clock domain CK1 to CK2, expand clock domain CK2.

Figure 7-4. Expanding the Inter-Clock Domain

Select the inter-clock domain you want to expand from these sets.

All paths between the related two domains are displayed in Paths List in the same way as any register to register set.

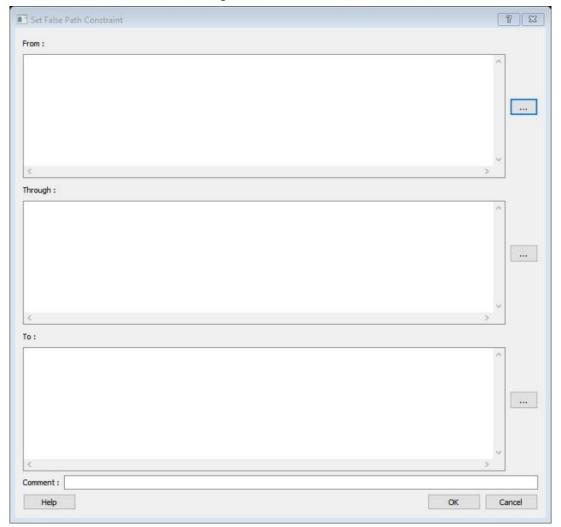

# 7.4 Deactivating a Specific Inter-Clock Domain

To deactivate the inter-clock domain checking for the specific clock domains clk2->clk1, without disabling this option for the other clock domains:

- 1. From the Tools menu, choose Constraints Editor > Primary Scenario to open the Constraints Editor View.

- In the Constraints Browser, double-click False Path under Exceptions.

The Set False Path Constraint dialog box appears.

- 3. Click the **Browse** button to the right of the **From** text box.

The Select Source Pins for False Path Constraint dialog box appears.

- 4. For Specify pins, select by keyword and wildcard.

- 5. For Pin Type, select Registers by clock names from the Pin Type drop-down list.

- In the filter box, type the inter-clock domain name (for example, Clk2), and then click Filter.

- 7. Click **OK** to begin filtering the pins by your criteria. In this example, [get\_clocks {Clk2}] appears in the **From** text box in the Set False Path Constraint dialog box.

- 8. Repeat steps 3 to 7 for the **TO** option in the Set False Path Constraint dialog box and type Clk2 in the filter box.

- 9. Click **OK** to validate the new false path and display it in the Paths List of the Constraints Editor.

- 10. Click the Recalculate All icon in the toolbar.

- 11. Select the inter-clock domain set clk2 -> clk1 in the Domain Browser (as shown below).

Figure 7-5. Selecting the Inter-clock Domain Set clk2 -> clk1

12. Verify that the set does not contain any paths.

## 7.5 Changing Output Port Capacitance

Output propagation delay is affected by both the capacitive loading on the board and the I/O standard.

The I/O Attribute Editor in Chip Planner provides a way to set the expected capacitance to improve the propagation delay model. SmartTime uses the modified delay model automatically for delay calculations.

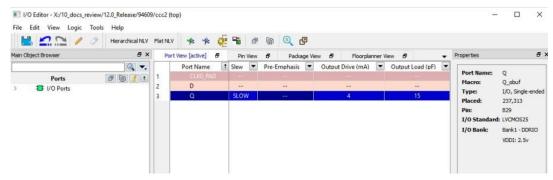

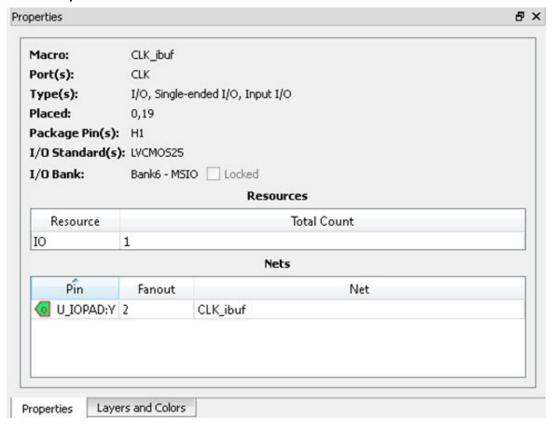

To change the output port capacitance and view the effect of this change in SmartTime Timing Analyzer, see the following example. The following figure shows a delay of 6.603 ns from DFN1 to output port Q based on the default loading of 5 pF.

Figure 7-6. Maximum Delay Analysis View

If your board has an output capacitance of 15 pf on Q, perform the following steps to update the timing number.

Open the I/O Attribute Editor and change the output load to 15 pf.

Figure 7-7. I/O Attribute Editor

- 2. Select File > Save.

- 3. Select File > Close.

- 4. Open the SmartTime Timing Analyzer and confirm that the Clock to Output delay changed to 5.952 ns.

# 8. Generating Timing Reports

The following sections describe how to generate timing reports.

### 8.1 Types of Reports

The following table describes the types of timing reports you can generate using SmartTime.

Table 8-1. Types of Timing Reports

| Report                       | Description                                                                                                                |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Timer Report                 | Displays the timing information organized by clock domain.                                                                 |

| Timing Violations Report     | Provides information about constraint violations.                                                                          |

| Bottleneck Report            | Displays points in the design that contribute to the most timing violations.                                               |

| Datasheet Report             | Describes the characteristics of the pins, I/O technologies, and timing properties in the design.                          |

| Constraints Coverage Report  | Displays the overall coverage of the timing constraints set on the current design.                                         |

| Combinational Loop Report    | Displays loops found during initialization.                                                                                |

| Clock Domain Crossing Report | Analyzes timing paths that cross from one clock domain (the source clock) to another clock domain (the destination clock). |

# 8.2 Generating a Timing Report

The Timing Report allows you to determine whether timing problems exist in your design.

The Maximum Delay Analysis Timing Report lists the following information about your design:

- Maximum delay from input I/O to output I/O

- Maximum delay from input I/O to internal registers

- Maximum delay from internal registers to output I/O

- · Maximum delays for each clock network

- · Maximum delays for interactions between clock networks

To generate a Timing Report:

- From the SmartTime Max/Min Delay Analysis View, choose Tools > Reports > Timer.

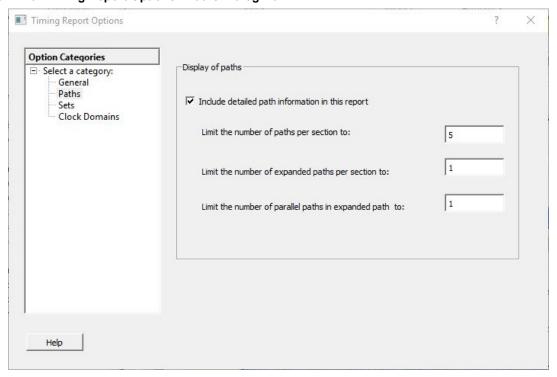

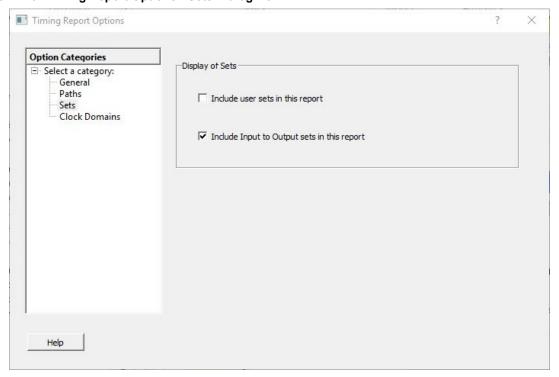

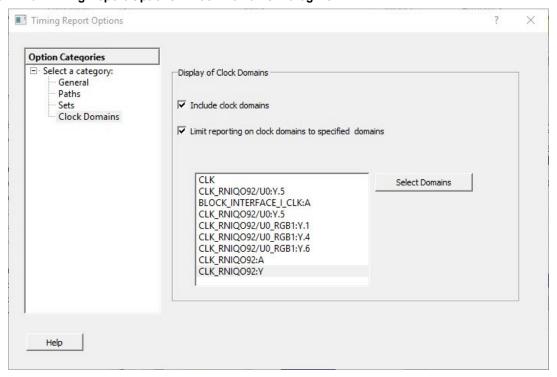

The Timing Report Options dialog box appears.

- Select the options you want to include in the report, and then click **OK**.

The Timing Report appears in a separate window.

# 8.3 Understanding Timing Reports

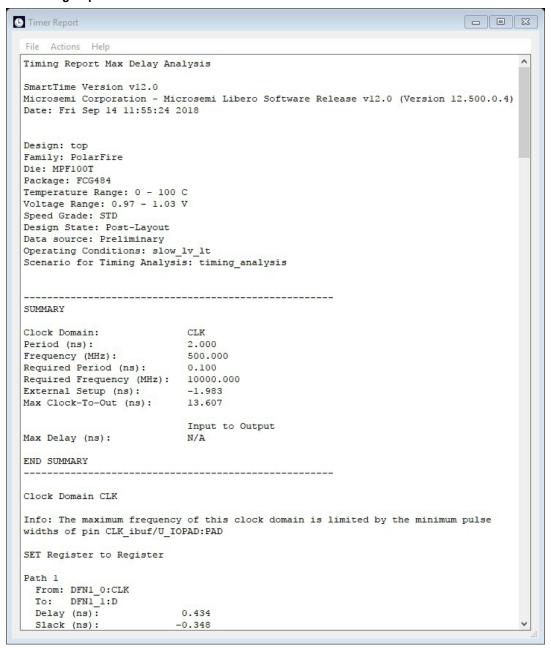

The Timing Report contains the following sections:

#### **Table 8-2. Timing Report Sections**

| Section | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Header  | Lists the:  Report type  Version of Designer used to generate the report  Date and time the report was generated  General design information (name, family, and so on)                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Summary | Reports the timing information for each clock domain. By default, the clock domains reported are the explicit clock domains that are shown in SmartTime. To filter the domains and show only specific sections in the report, use the Timing Report Options dialog box.                                                                                                                                                                                                                                                                                                                                                |

| Path    | Lists the timing information for different types of paths in the design. This section is reported by default. You can deselect this option in the Timing Report Options dialog box.  By default, the number of paths displayed per set is 5. You can filter the domains using the Timing Report Options dialog box. You can also view the stored filter sets in the generated report using the Timing Report options. The filter sets are listed by name in their appropriate section. The number of paths reported for the filter set is the same as for the main sets. By default, the filter sets are not reported. |

#### 8.3.1 Clock Domains

Paths are organized by clock domain.

#### 8.3.2 Register to Register Set

This set reports the paths from the registers clock pins to the registers data pins in the current clock domain.

#### 8.3.3 External Setup Set

This set reports the paths from the top-level design input ports to the registers in the current clock domain.

#### 8.3.4 Clock to Output Set

This set reports the paths from the registers clock pins to the top-level design output ports in the current clock domain.

#### 8.3.5 Register to Asynchronous Set

This set reports the paths from registers to asynchronous control signals, such as asynchronous set/reset.

#### 8.3.6 External Recovery Set

This set reports the external recovery check timing for asynchronous control signals, such as asynchronous set/reset.

#### 8.3.7 Asynchronous to Register Set

This set reports the paths from asynchronous control signals, such as asynchronous set/reset, to registers.

#### 8.3.8 Inter-clock Domain

This set reports the paths from the registers clock pins of the specified clock domain to the registers data pins in the current clock domain. Inter-domain paths are not reported by default.

# **Generating Timing Reports**

#### 8.3.9 Pin to Pin

This set lists input to output paths and user sets. Input-to-output paths are reported by default. To see the user-defined sets, use the Timing Report Options dialog box.

#### 8.3.10 Input to Output Set

This set reports the paths from the top-level design input ports to the top-level design output ports.

#### 8.3.11 Expanded Paths

Expanded paths can be reported for each set. By default, the number of expanded paths to report is set to 1. You can select and change the number when you specify Timing Report options.

Figure 8-1. Timing Report

#### 8.4 Generating a Timing Violation Report

The Timing Violations Report provides a Flat Slack Report centered around constraint violations.

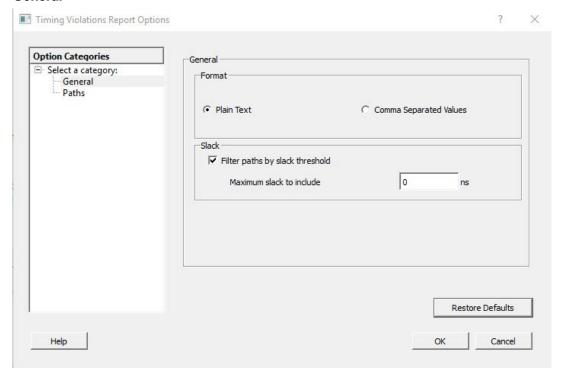

To Timing Violations Report:

- From the SmartTime Max/Min Delay Analysis View window, choose Tools > Reports > Timing Violations.

The Timing Violations Report Options dialog box appears.

- 2. Select the options you want to include in the report, and then click **OK**. The Timing Violations Report appears in a separate window.

#### 8.5 Understanding Timing Violation Reports

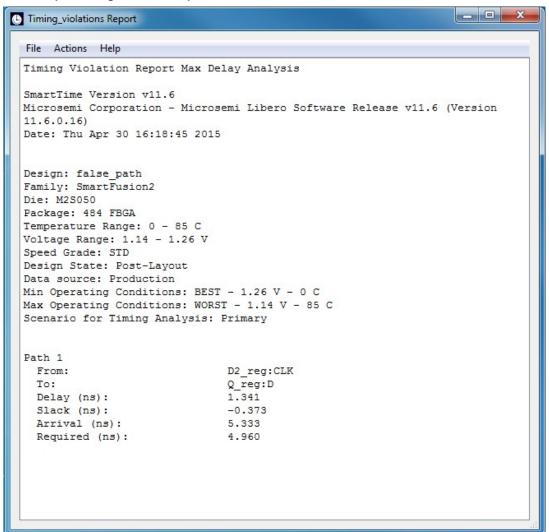

The following figure shows an example of a Timing Violations Report.

Figure 8-2. Sample Timing Violation Report

The Timing Violation Report contains the following sections:

**Table 8-3. Timing Violation Report Sections**

| Section | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Header  | This section lists the:  Report type  Version of Designer used to generate the report  Date and time the report was generated  General design information (name, family, and so on)                                                                                                                                                                                                                            |

| Paths   | This section lists the timing information for different types of paths in the design. The number of paths displayed is controlled by the following parameters:  • A maximum slack threshold to report  • A maximum number or path to report  By default, the slack threshold is 0 and the number of paths is limited. The default maximum number of paths reported is 100.All clocks domains are mixed in this |

|         | report. The paths are listed by decreasing slack. You can also choose to expand one or more paths. By default, no paths are expanded. For details, see the Timing Violation Report options.                                                                                                                                                                                                                    |

### 8.6 Generating a Constraints Coverage Report

The Constraints Coverage Report contains information about the constraints in the design.

To generate a Constraints Coverage Report:

- 1. From the SmartTime Max/Min Delay Analysis View, choose **Tools > Reports > Constraints Coverage**.

- Select the text format and number of unconstrained instances and click **OK**.

The report appears in a separate window.

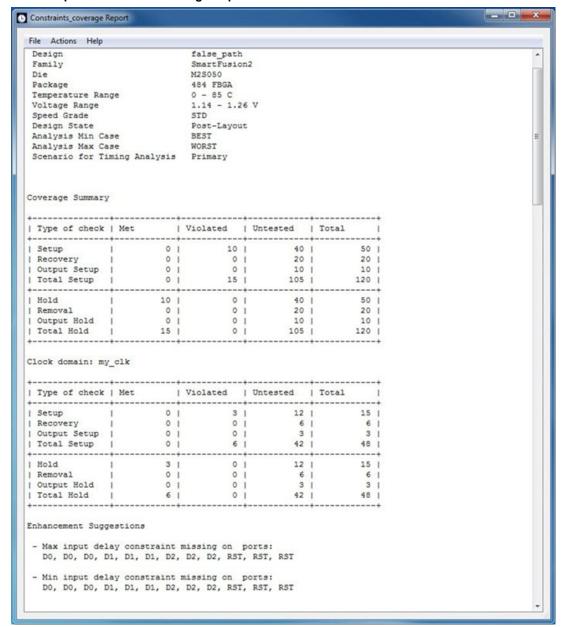

## 8.7 Understanding Constraints Coverage Reports

The Constraints Coverage Report shows the overall coverage of the timing constraints set on the current design. You can generate this report either from within Designer or within SmartTime Analyzer.

Figure 8-3. Sample Constraints Coverage Report

The Constraints Coverage Report contains the following sections:

**Table 8-4. Constraints Coverage Report Sections**

| Section                 | Description                                                                                                                                                                                                                                                                                                                       |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Coverage Summary        | Shows statistical information about the timing constraint in the design. For each type of timing checks (Setup, Recovery, Output, Hold, and Removal), it specifies how many are Met (there is a constraint and it is satisfied), Violated (there is a constraint and it is not satisfied), or Untested (no constraint was found). |

| Results by Clock Domain | This section provides a coverage summary for each clock domain.                                                                                                                                                                                                                                                                   |

# **Generating Timing Reports**

| continued               |                                                                                                                                                                                           |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Section                 | Description                                                                                                                                                                               |  |

| Enhancement Suggestions | Reports, per clock domain, a list of constraints that can<br>be added to the design to improve the coverage. It also<br>reports if some options impacting the coverage can be<br>changed. |  |

| Detailed Stats          | Provides detailed suggestions about specific clocks or I/O ports that may require to be constrained for every pin/port that requires checks.                                              |  |

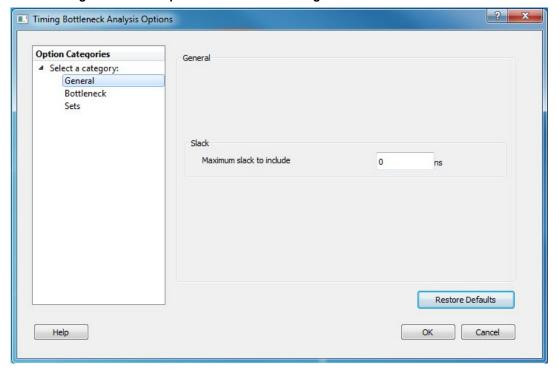

### 8.8 Generating a Bottleneck Report

To generate a Bottleneck Report:

From the SmartTime Max/Min Delay Analysis View, choose Tools > Reports > Bottleneck.

The report appears in a separate window.

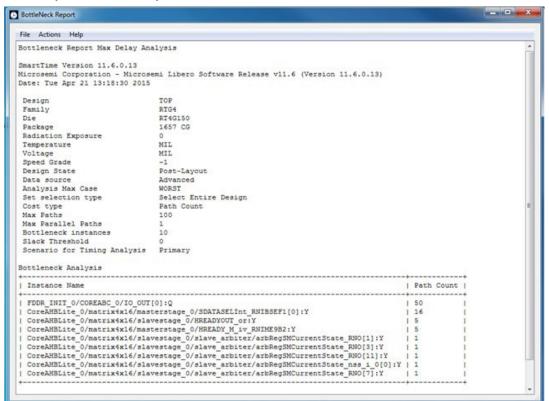

### 8.9 Understanding Bottleneck Reports - SmartFusion2, IGLOO2, RTG4, and PolarFire

A bottleneck is a point in the design that contributes to multiple timing violations. The Bottleneck Report lists the bottlenecks in the design. You can generate this report from SmartTime Analyzer.

Notes: The bottleneck can be computed only when a cost type is defined. There are two cost type options available:

- Path count: associates the severity of the bottleneck to the count of violating/critical paths that traverse the instance.

- Path cost: associates the severity of the bottleneck to the sum of the timing violations for the violating/critical paths that traverse the instance.

Figure 8-4. Sample Bottleneck Report

The Bottleneck Report contains the following parts:

#### Table 8-5. Bottleneck Report Sections

| Part                | Description                                                                                                                                                                                                                        |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Description  | Contains general information about the design, including:     Design name     Family     Die     Package     Software version                                                                                                      |

| Bottleneck Analysis | Lists the core of the bottleneck information. It is organized into two columns:  • Instance Name: refers to the output pin name of the instance.  • Path Count: shows the number of violating paths that include the instance pin. |

# 8.10 Generating a Datasheet Report

The Datasheet Report shows information about a design's external characteristics.

To generate a Datasheet Report:

From the SmartTime Max/Min Delay Analysis View, choose Tools > Reports > Datasheet.

The report appears in a separate window.

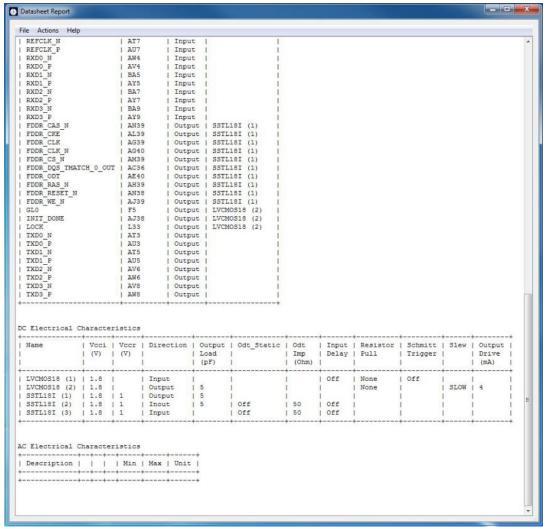

# 8.11 Understanding Datasheet Reports

The Datasheet Report displays the external characteristics of the design. You can generate this report from SmartTime Max/Min Delay Analysis View.

Figure 8-5. Sample Datasheet Report

The Datasheet Report contains three tables:

Table 8-6. Datasheet Report Tables

| Table                         | Description                                                                                                                                                                                                                |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Description               | Provides the port name in the netlist, location on the package, type of port, and I/O technology assigned to it. Types can be input, output, or clock. Clock ports are ports shown as "clock" in the Clock domain browser. |

| DC Electrical Characteristics | Provides the parameters of the different I/O technologies used in the design. The number of parameters displayed depends on the family for which you have created the design.                                              |

# **Generating Timing Reports**

| continued                     |                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Table                         | Description                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| AC Electrical Characteristics | Provides the timing properties of the ports of the design. For each clock, this section includes the maximum frequency. For each input, it includes the external setup, external hold, external recovery, and external removal for every clock where it applies. For each output, it includes the clock-to-out propagation time. This section also displays the input-to-output propagation time for combinational paths. |  |  |  |  |

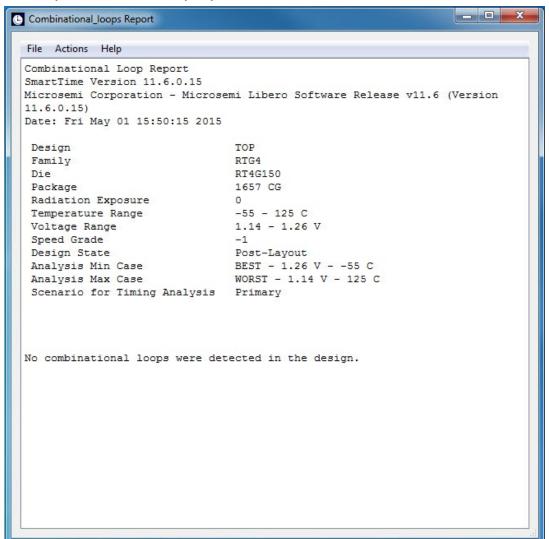

# 8.12 Generating a Combinational Loop Report

The Combinational Loop Report shows all loops found during initialization and reports pins associated with the loop(s) and the location where a loop is broken.

To generate a Combinational Loop Report:

- From the Tools menu, choose Reports > Combinational Loops.

The Combinational\_Loops Report Options dialog box appears.

- 2. Select either Plain Text or Comma Separated Values.

- 3. Click OK.

# 8.13 Understanding Combinational Loop Reports

The Combinational Loop Report shows all loops found during initialization, reports the pins associated with the loops, and identifies the locations where loops are broken.

Figure 8-6. Sample Combinational Loop Report

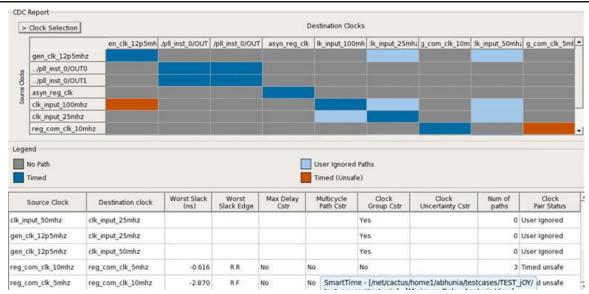

## 8.14 Generating a Clock Domain Crossing (CDC) Report

The Clock Domain Crossing (CDC) Report analyzes timing paths that cross from one clock domain (the source clock) to another clock domain (the destination clock). The CDC report helps identify instances where there may be data loss or metastability issues.

To generate the CDC Report:

- From the Tools menu, choose Reports > Clock Domain Crossing (CDC)...

The Clock Domain Crossing Report Options dialog box appears.

- 2. Select either CDC Table or Comma Separated Values.

- Click OK.

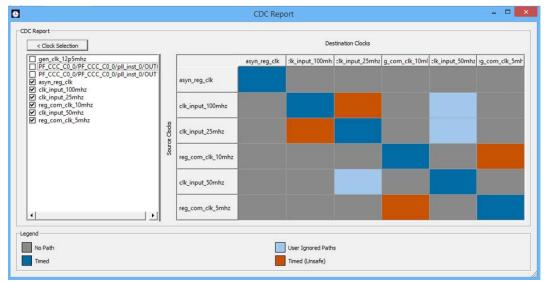

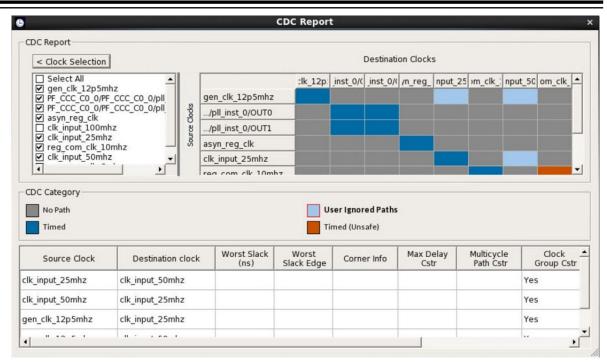

Selecting **CDC Table** displays a graphical table with color-coded cells. Each cell represents a CDC type between the source clock and the destination clock domains that have constraints. Clocks without constraints do not appear in the CDC table.

# **Generating Timing Reports**

The attributes present in the path table are as follows:

- · Source Clock: Source of the clock

- · Destination Clock: Destination of the clock

- · Worst Slack (ns): Worst slack of the CDC path in nanoseconds

- Worst Slack Edge: This is the source/sink edge for the worst path of CDC

- · Max Delay Cstr:

| Value   | Description                                  |  |  |  |  |

|---------|----------------------------------------------|--|--|--|--|

| Yes     | All paths in CDC have set_max_delay applied  |  |  |  |  |

| No      | No paths in CDC have the constraints applied |  |  |  |  |

| Partial | Any path in CDC has the constraint applied   |  |  |  |  |

### Multicycle Path Cstr:

| Value   | Description                                       |  |  |  |

|---------|---------------------------------------------------|--|--|--|

| Yes     | All paths in CDC have set_multicycle_path applied |  |  |  |

| No      | No paths in CDC have the constraints applied      |  |  |  |

| Partial | Any path in CDC has the constraint applied        |  |  |  |

#### · Clock Group Cstr:

| Value | Description                               |  |  |  |

|-------|-------------------------------------------|--|--|--|

| Yes   | CDC has set_clock_group applied           |  |  |  |

| No    | CDC does not have set_clock_group applied |  |  |  |

- Clock Uncertainty Cstr: It is the uncertainty value for the worst path in CDC; else, the clock uncertainty field is left empty.

- Num of Paths: Number of paths in CDC. For User Ignored paths, the value is 0.

- Clock Pair Status: The status can be Timed Safe, Timed Unsafe or User Ignored.

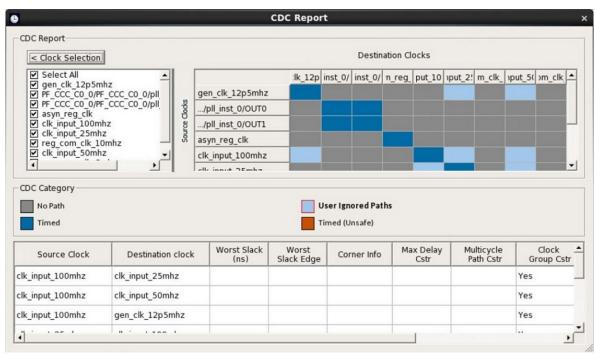

In the CDC Report dialog box, you can select the clocks to view or hide. Clicking the **Clock Selection** button at the top left of the dialog box lists all clocks that can be viewed or hidden. By default, all clocks are checked and visible. To hide a clock, clear its check box.

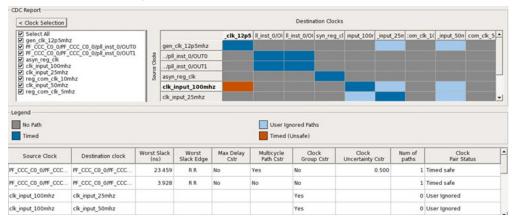

Figure 8-7. Showing or Hiding Clocks

The following table describes the colors in the CDC Report shown in the preceding figure.

| Pattern                                                                                                                                                                                                                                                           | Status             | Color      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|

| Paths from the source clock domain to the destination clock domain have all been disabled by false path or clock group constraints.                                                                                                                               | User-Ignored Paths | Light blue |

| No Paths found from the source clock domain to the destination clock domain.                                                                                                                                                                                      | No Paths           | Gray       |

| The source and destination clocks are synchronous: Both the clocks have a common primary clock and paths are found from the source clock domain to the destination clock domain.                                                                                  | Timed              | Dark Blue  |

| The source and destination clocks are asynchronous: Both the clocks have NO common primary clock, while paths are found from the source clock domain to the destination clock domain. Currently, synchronizers, if present, are not accounted for in this report. | Timed (unsafe)     | Brown      |

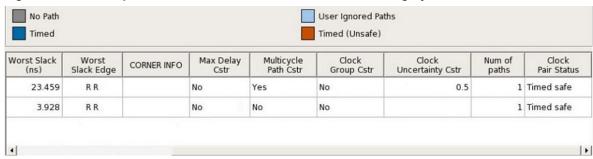

There are certain scenarios related to the path table as explained in the following:

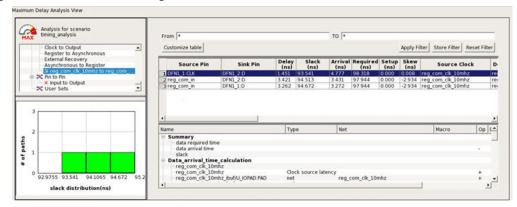

1. When CDC report is generated, path table is shown by default for all CDC having paths. Each row shows the worst slack for a clock crossing. Similarly, when clicking on a particular CDC crossing in CDC report, you can have a single row showing the worst slack for CDC crossing.

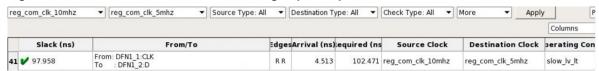

Example: The path table shown in the following figure, the worst path for reg\_com\_clk\_10mhz to reg\_com\_clk\_5mhz has the worst slack of 93.541. The same path is displayed by default, when the CDC crossing is selected.

Figure 8-8. Worst Path with Slack 93.541 ns

| Source Clock      | Destination clock | Worst Slack<br>(ns) | Worst<br>Slack Edge | Max Delay<br>Cstr | Multicycle<br>Path Cstr | Clock<br>Group Cstr | Clock<br>Uncertainty Cstr | Num of<br>paths | Clock<br>Pair Status |

|-------------------|-------------------|---------------------|---------------------|-------------------|-------------------------|---------------------|---------------------------|-----------------|----------------------|

| gen_clk_12p5mhz   | clk_input_25mhz   |                     |                     |                   |                         | Yes                 |                           | 0               | User Ignored         |

| gen_clk_12p5mhz   | clk_input_50mhz   |                     |                     |                   |                         | Yes                 |                           | 0               | User Ignored         |

| reg_com_clk_10mhz | reg_com_clk_5mhz  | 93.541              | RR                  | No                | No                      | No                  | 5.000                     | 3               | Timed unsafe         |

| reg_com_clk_5mhz  | reg_com_clk_10mhz | 89.703              | RF                  | No                | No                      | No                  | 2.000                     | 2               | Timed unsafe         |

Figure 8-9. Smarttime Showing the Worst Path with Slack 93.541 ns

Clicking on the CDC box shows the worst slack for a clock crossing as in path table in the following figure.

Figure 8-10. Highlighted CDC Box Showing the Worst Slack in Path Table

Clicking on the same CDC box again will show the details for all the clocks selected in CDC report.

Figure 8-11. CDC Path Table Showing All Clocks on Deselecting the Selected CDC Box

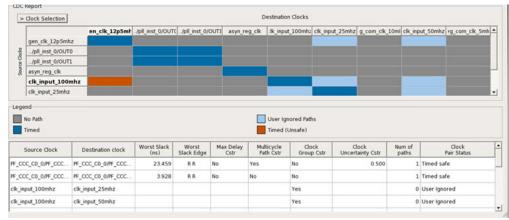

For all clocks having large names, tool-tips for columns have been added.

Figure 8-12. CDC Path Table Showing Tool-Tip for a Source Clock Name

| Source Clock        | Destination clock          | Worst Slack<br>(ns) |  |

|---------------------|----------------------------|---------------------|--|

| PF_CCC_C0_0/PF_CCC  | . PF_CCC_C0_0/PF_CCC       | 23.459              |  |

| PF_CCC_PF_CCC_C0_0/ | PF_CCC_C0_0/pll_inst_0/OUT | 3.928               |  |

| clk_input_100mhz    | clk_input_25mhz            |                     |  |

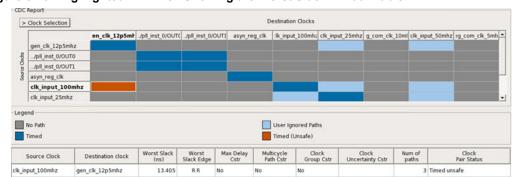

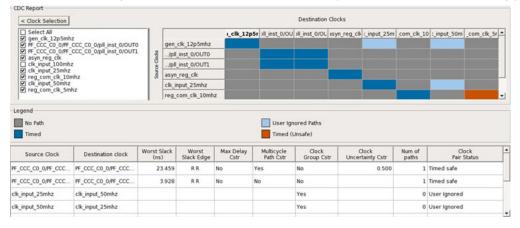

3. Selecting/deselecting clocks in clock selection will dynamically change the path table along with the CDC table. Both the tables are in sync. Example: Here, clk\_input\_100mhz is selected, therefore, the clock is displayed in CDC table and path table.

Figure 8-13. CDC Table in Sync with Clock Selection Section

When the clock clk\_input\_100mhz is unselected, then the same clock is removed from the CDC table. The crossings related to the clock are also removed from the path table as shown in the following figure.

Figure 8-14. Deselecting a Clock in Clock Selection Section Syncs the Path Table Accordingly

On clicking any one of the four options in the CDC category, the clock table is filtered according to the CDC category selected.

The following is a scenario where Timed button has been selected, and Timed safe CDC is only displayed in the clock table.

Figure 8-15. CDC Report When Timed Button is Selected in CDC Category

Clicking on the same CDC category shows the details for all the clocks selected in CDC report. Selecting/ unselecting clocks in clock selection does dynamically change the clock table along with the CDC table.

In the following figure, the User Ignored CDC category button is chosen and clk\_input\_100mhz is selected. Therefore, the clock is displayed in CDC table and clock table.

Now, when clock clk\_input\_100mhz is unselected, the same clock is moved from CDC table and the crossings related to that clock are also removed from clock table. Therefore, when the User Ignored CDC category is selected, entries related to clk\_input\_100mhz are not visible.

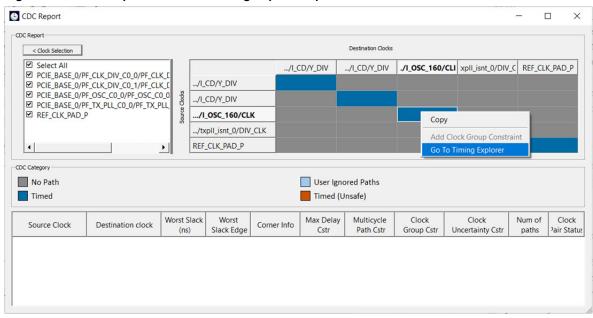

On right-clicking a CDC box, you can choose to **Copy**, **Add a Clock Group Constraint** or **Go to Timing Explorer**.

Figure 8-16. CDC Report with Go to Timing Explorer Option

Selecting the **Go to Timing Explorer** option opens the Timing Explorer dialog box.

# Generating Timing Reports

clk 10mhz ibuf/

Figure 8-17. Timing Report Explorer

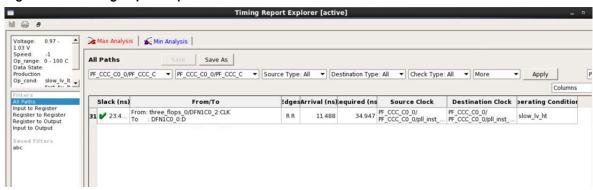

There are corner scenarios when cross probing between CDC and Timing Explorer:

#### Scenario 1:

This is a scenario where difference is seen between SmartTime and Verify timing, when two clocks are defined on same port and when cross probing for CDC reg\_com\_clk\_10mhz and reg\_com\_clk\_5mhz is unable to find the same in Timing Report Explorer.

The constraints are as follows:

```

create_clock -name {reg_com_clk_10mhz} -period 100 -waveform {0 50 } [ get_ports

{ reg_com_clk_10mhz } ]

create_clock -name {reg_com_clk_5mhz} -period 200 -waveform {0 100 } -add [ get_ports

{ reg_com_clk_10mhz } ]

```

The Timing Report Explorer does not pick reg\_com\_clk\_5mhz as destination clock, and Smart time does pick the reg\_com\_clk\_10mhz and reg\_com\_clk\_5mhz pair as CDC, as shown in the following.

Figure 8-18. Timing Report Explorer Snapshot - 1

From: D reg\_com\_clk\_10mhz

Figure 8-20. SmartTime Snapshot

Timing Explorer is picking the worst slack path for a pair of start and end point. Therefore, you can miss CDC and other reg to reg paths with lower slack values.

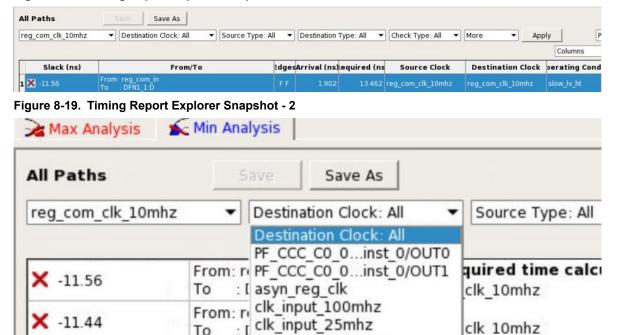

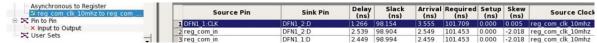

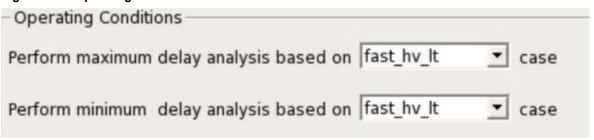

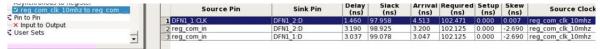

#### Scenario 2:

This is a scenario where due to different operating conditions set in Smart Time, you can have different results, when cross probing between CDC and Timing Report Explorer. SmartTime and CDC are in sync.

Figure 8-21. Worst Slack of 97.958 ns in Timing Report Explorer

Figure 8-22. Worst Slack of 98.154 ns in SmartTime

Figure 8-23. Operating Conditions

The Timing Report Explorer reports the path from slow\_lv\_lt, and SmartTime reports using the operating condition fast\_hv\_lt. When the operating condition in SmartTime is changed to slow\_lv\_lt, the worst slack becomes the same as in the Timing Report Explorer.

Figure 8-24. Slack After Changing the Operating Condition to slow\_lv\_lt

CDC reports worst path for a particular corner selected in SmartTime, and Timing Report Explorer reports the worst path across all the corners.

In such cases, you can see changes in values when navigating from CDC to Timing Report Explorer. To make you aware of such situations, Corner Info column is added to display the operating conditions.

#### Note:

- The path details for the same clock crossing (C1 to C1) are not shown in the path tale as they are not valid clock crossings and are currently shown as timed safe by default in CDC report.

- The clock table has CDC details only related to clocks checked in clock selection from CDC report.

- Path table will not show any CDC having no paths.

- For User Ignored CDC columns, "Worst Slack (ns)", "Worst Slack Edge", "Max Delay Cstr", "Multicycle Path Cstr", and "Clock Uncertainty Cstr" are empty.

- Cross probing is allowed to Timing Report Explorer for the same clock crossing (C1 to C1).

- · For User Ignored CDC category, Corner Info column is empty.

Selecting **Comma Separated Value** exports the CDC Report to a CSV file. If you select this option, a window appears in which you assign a name to the CSV file and specify the location where it will be exported. The

# **Generating Timing Reports**

CSV file shows details about the CDC between each clock domain in numeric format. Each CDC type is represented as a number similar to colors in the table. The CSV file includes an explanation of each number type and CDC type.

### Figure 8-25. Sample CSV Report

# 9. Timing Concepts

The following sections describe timing concepts associated with the RTG4 FPGA Clock Conditioning Circuit with PLL configuration.

# 9.1 Static Timing Analysis Versus Dynamic Simulation

STA offers an efficient technique for identifying timing violations in your design and ensuring that it meets all your timing requirements. You can communicate timing requirements and timing exceptions to the system by setting timing constraints. A static timing analysis tool will then check and report setup and hold violations as well as violations on specific path requirements.

STA is well suited for traditional synchronous designs. The main advantage of STA is that, unlike dynamic simulation, it does not require input vectors. It covers all possible paths in the design and does all the above with relatively low run-time requirements. The major disadvantage of STA is that the STA tools do not automatically detect false paths in their algorithms.

# 9.2 Delay Models

The first step in timing analysis is the computation of single component delays. These components can be either a combinational gate or block or a single interconnect connecting two components.

Gates that are part of the library are pre-characterized with delays under different parameters, such as input-slew rates or capacitive loads. Traditional models provide delays between each pair of I/Os of the gate and between rising and falling edges.

The accuracy with which interconnect delays are computed depends on the design phase. These can be estimated using a simple Wire Load Model (WLM) at the pre-layout phase or a more complex Resistor and Capacitor (RC) tree solver at the post-layout phase.

## 9.3 Timing Path Types

Path delays are computed by adding delay values across a chain of gates and interconnects. SmartTime uses this information to check for timing violations. Traditionally, timing paths are presented by static timing analysis tools in four categories or "sets."

- Paths between sequential components internal to the design. SmartTime displays this category under the Register to Register set of each displayed clock domain.

- Paths that start at input ports and end at sequential components internal to the design. SmartTime displays this category under the External Setup and External Hold sets of each displayed clock domain.

- Paths that start at sequential components internal to the design and end at output ports. SmartTime displays this category under the Clock to Out set of each displayed clock domain.

- Paths that start at input ports and end at output ports. SmartTime displays this category under the Input to Output set.

## 9.4 Maximum Clock Frequency

Generally, you set clock constraints on clocks for which you have a specified requirement. The absence of violations indicates that this clock can run at least at the specified frequency. However, in the absence of such requirements, you may still be interested in computing the maximum frequency of a specific clock domain.

To obtain the maximum clock frequency, a static timing analysis tool computes the minimum period for each path between two sequential elements. To compute the maximum period, the tool evaluates the maximum data path delay and the minimum skew between the two elements, as well as the setup on the receiving sequential element. It also considers the polarity of each sequential element. The maximum frequency is the inverse of the largest value among the maximum period of all the paths in the clock domain. The path responsible for limiting the frequency of a given clock is called the "critical path."

# 9.5 Setup Check

The setup and hold check ensures that the design works as specified at the required clock frequency.

Setup check specifies when data is required to be present at the input of a sequential component so that the clock can capture the data effectively into the component. Timing analyzers evaluate the setup check as a maximum timing budget allowed between adjacent sequential elements.

For more information about how setup check is processed, see Arrival Time, Required Time, and Slack.

# 9.6 Arrival Time, Required Time, and Slack

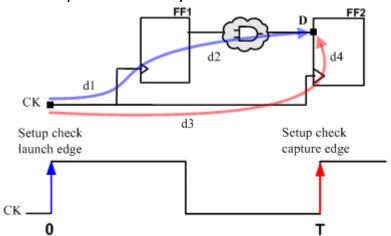

You can use arrival time and required time to verify timing requirements in the presence of constraints. The following simple example is applied to verify the clock requirement for setup between sequential elements in the design.

The arrival time represents the time at which the data arrives at the input of the receiving sequential element. In this example, the arrival time is considered from the setup launch edge at CK, taken as a time reference (instant zero). It follows the clock network along the blue line until the clock pin on FF1 (delay d1). Then it continues along the data path always following the blue line until the data pin D on FF2. Therefore,

The required time represents when the data is required to be present at the same pin FF2:D. Assume in this example that in the presence of an FF with the same polarity, the capturing edge is simply one cycle following the launch edge. Using the period T provided to the tool through the clock constraint, the event gets propagated through the clock network along the red line until the clock pin of FF2 (delay d3). Taking FF2 setup (delay d4) into account. This means the clock constraint requires the data to be present d4 time before the capturing clock edge on FF2. Therefore, the required time is:

Required TimeFF2:D = T + d3 - d4

If the slack is negative, the path is violating the setup relationship between the two sequential elements.

The slack is simply the difference between the required time and arrival time: SlackFF2:D = Required\_TimeFF2:D - Arrival\_TimeFF2:D

Figure 9-1. Arrival Time and Required Time for Setup Check

## 9.7 Timing Exceptions Overview

Use timing exceptions to overwrite the default behavior of the design path.

Timing exceptions include:

Setting multicycle constraint to specify paths that (by design) will take more than one cycle.

- Setting a false path constraint to identify paths that must not be included in the timing analysis or the

optimization flow.

- Setting a maximum/minimum delay constraint on specific paths to relax or to tighten the original clock constraint requirement.

#### 9.8 Clock Skew

The clock skew between two sequential components is the difference between the insertion delays from the clock source to the clock pins of these components. SmartTime calculates the arrival time at the clock pin of each sequential component. Then it subtracts the arrival time at the receiving component from the arrival time at the launching component to obtain an accurate clock skew.

Both setup and hold checks must account for clock skew. However, for setup check, SmartTime looks for the smallest skew. This skew is computed by using the maximum insertion delay to the launching sequential component and the shortest insertion delay to the receiving component.

For hold check, SmartTime looks for the largest skew. This skew is computed by using the shortest insertion delay to the launching sequential component and the largest insertion delay to the receiving component.

SmartTime makes the distinction between setup and hold checks and hold checks automatically.

## 9.9 Cross Probing

Design objects displayed in SmartTime can be cross-probed into other Libero SoC tools. Libero SoC allows cross-probing from SmartTime to the Constraints Editor (but not vice versa) and from SmartTime to Chip Planner (but not vice versa). When cross-probing from SmartTime to one of the other tools, both SmartTime and the other tool must first be opened.

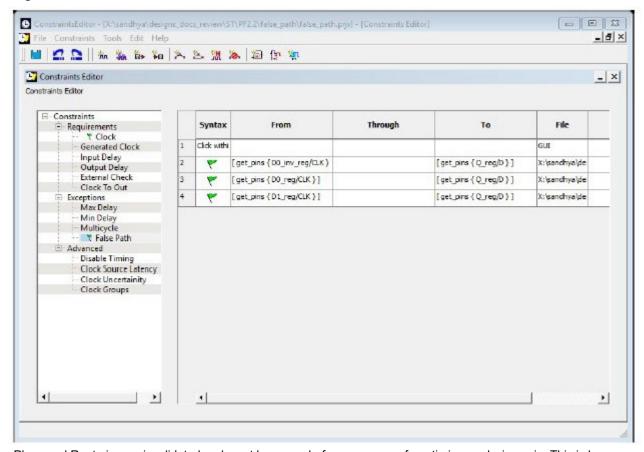

#### 9.9.1 Cross-probing from SmartTime into the Constraints Editor

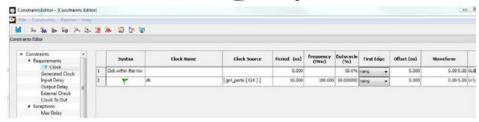

To add a timing exception constraint from SmartTime and have the Constraints Editor display the constraint:

- From the SmartTime Maximum or Minimum Delay Analysis view, click a timing path to add a timing exception constraint.

- 2. When the Constraints Editor's Add Constraint dialog box appears, the fields for source (from) pin and destination (to) pin are populated with the correct names from the timing path you selected.

#### 9.9.2 Adding a Timing Exception Constraint from a Timing Path

To add a timing exception constraint from a timing path in SmartTime Max/Min Delay Analysis View:

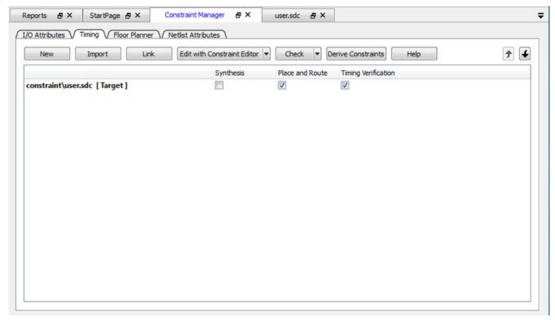

- Open SmartTime (Design Flow Window > Verify Timing > Open interactively).

- 2. Open the Constraints Editor (Constraint Manager > Timing Tab > Edit with Constraints Editor).

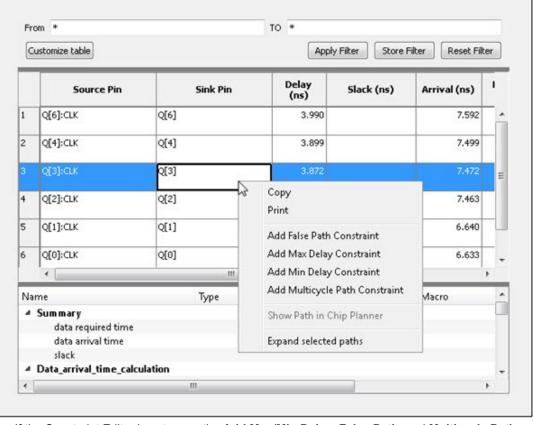

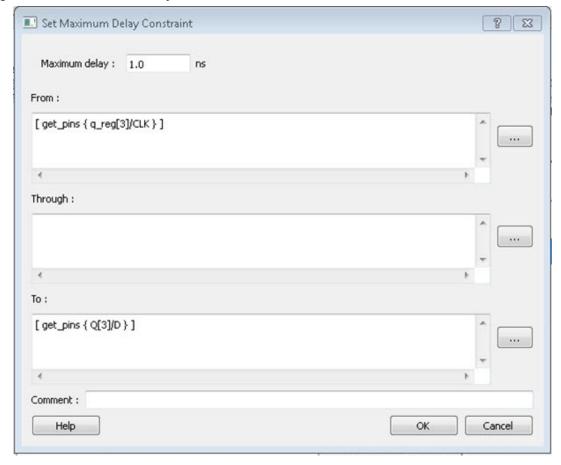

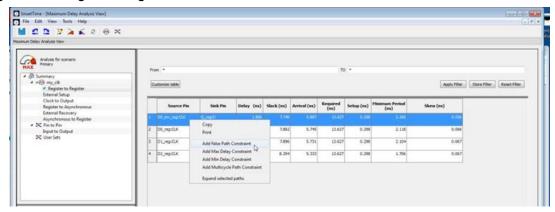

- 3. Select Max/Min Delay Analysis View, and then right-click a timing path in the table.

- 4. Select a timing exception constraint to add:

- False Path Constraint

- · Maximum Delay Constraint

- · Minimum Delay Constraint

- Multicycle Path Constraint

Figure 9-2. Add Timing Constraint from SmartTime's Reported Timing Path

**Note:** If the Constraint Editor is not open, the **Add Max/Min Delay**, **False Path**, and **Multicycle Path Constraint** menu items are grayed out.

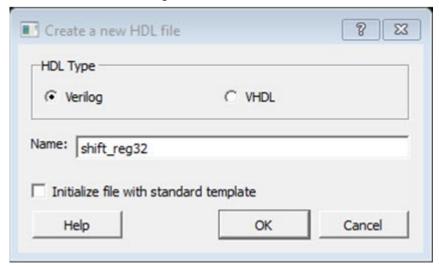

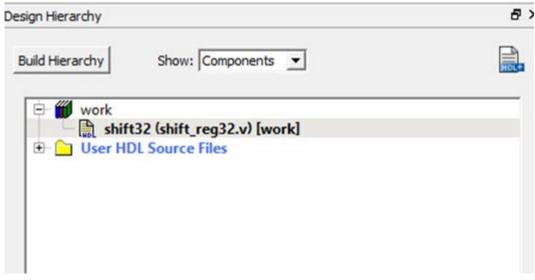

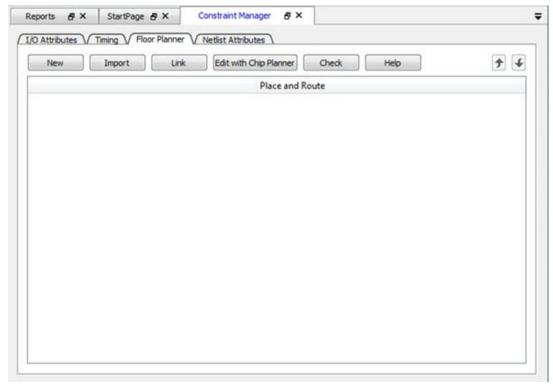

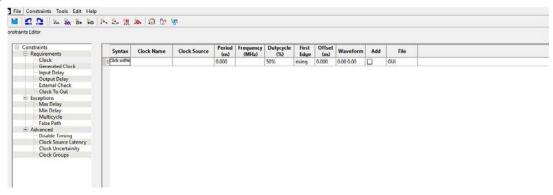

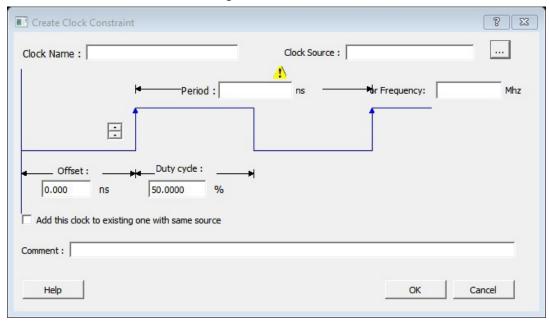

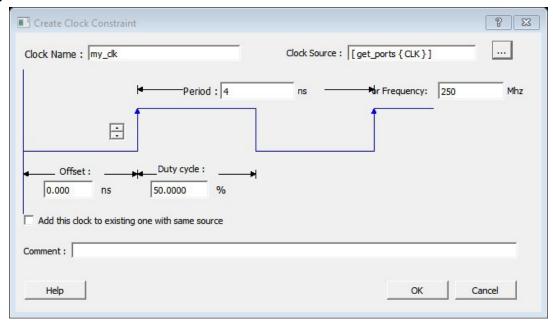

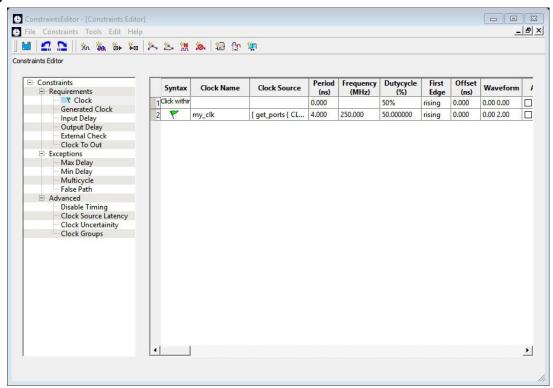

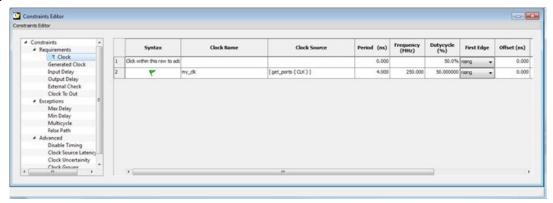

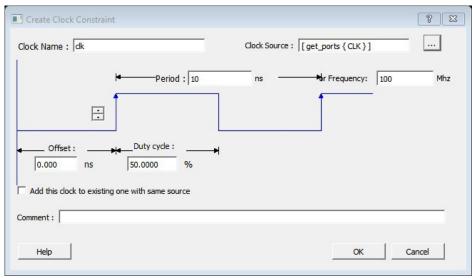

- 5. Add the Constraint in the Add Constraint dialog box. The **source/from pin** and **destination/to pin** fields are populated with the appropriate pin names captured from the SmartTime reported path (Source Pin and Sink Pin) you clicked.