## RT PolarFire<sup>®</sup>: TMR and Spatial Separation for Higher Reliability

### Introduction

The purpose of this application note is to help FPGA designers to implement the Triple Module Redundancy (TMR) design technique on a VHDL design, which is targeted on a Microchip Radiation-Tolerant PolarFire (RT PolarFire) FPGA.

This application note describes how to implement each logical register with a TMR register on different hierarchies of a VHDL/Verilog design. It shows how to use the syn\_radhardlevel synthesis attribute on the architecture and signal on different hierarchies.

These design example projects are targeted towards use in a RTPF500T-CG1509M device (Rad-Tolerant PolarFire FPGA, 500K Logic-Elements with High-Speed Serial Transceivers in a Ceramic Column Grid Array Package with 1509 solder columns).

### Features

Following are the TMR features supported in Libero<sup>®</sup> SoC v12.4 or later.

- TMR attribute.

- Perform spatial placement of registers in a TMR triplet.

## **Table of Contents**

| Intro | oductio | n1                              |

|-------|---------|---------------------------------|

|       | 1.      | Features1                       |

| 1.    | Descr   | ption3                          |

| 2.    | TMR     |                                 |

| 3.    | Attribu | te Declaration5                 |

| 4.    | Spatia  | l Placement6                    |

| 5.    | Desig   | n Description                   |

|       | 5.1.    | PATH1 Description               |

|       | 5.2.    | PATH2 Description               |

|       | 5.3.    | PATH3 Description               |

|       | 5.4.    | PATH4 Description11             |

|       | 5.5.    | PATH5 Description               |

|       | 5.6.    | PATH6 Description               |

| 6.    | Desig   | n Examples                      |

|       | 6.1.    | Limitations                     |

|       | 6.2.    | Summary                         |

| 7.    | Revisi  | on History                      |

| The   | Micro   | hip Website                     |

| Pro   | duct Cl | nange Notification Service      |

| Cus   | tomer   | Support                         |

| Mic   | rochip  | Devices Code Protection Feature |

| Leg   | al Noti | ce                              |

| Trac  | demark  | s                               |

| Qua   | lity Ma | nagement System                 |

| Wor   | ldwide  | Sales and Service               |

### 1. Description

To meet a radiation requirement, the Radiation-Survivability engineer should evaluate the Single Event Upset (SEU) rate of RT PolarFire D flip-flops (DFF):

A single native DFF (D flip-flop)/register inside a single Logic Element (LE): If the SEU rate required by a specific design is greater than or equal to the native SEU rate of a single DFF of a LE on the RT PolarFire FPGA, each register function can be implemented with a single DFF/register inside a single LE.

Or

• A TMR implementation of a register:

If the SEU rate required by a specific design or mission is less than the native SEU rate of a single DFF of a LE on the RT PolarFire FPGA, each register function can be implemented by decreasing the SEU rate of a register function with the TMR technique.

The SEU rate of a single native register in the fabric of a PolarFire or RT PolarFire device is listed in the radiation test report which are available at Microchip website.

For example, the FPGA design consists of three functional blocks:

- Block#1 is the top-level

- Block#2 is the video processor

- Block#3 is a navigation controller

If the SEU requirements of the entire FPGA logic design are less than the native SEU rate of each single DFF of a LE in RT PolarFire, implement all register function of the entire FPGA design as TMR-registers.

If the SEU requirements of the navigation block are less than the native SEU rate of a single DFF of a LE in RT PolarFire, implement:

- The register function of the Navigation block as TMR registers.

- The register function of the top-level and video processor with single native register cells.

Based on the requirements of a particular program, and of a specific function inside the FPGA, the radiation survivability engineer can tell the FPGA designer, which blocks can be implemented using:

- Single native DFF/register cells.

- TMR registers.

The Synplify Synthesis tools attribute called syn\_radhardlevel is used for implementation of register functions as single native DFF/register cells or TMR registers.

### 2. TMR

The TMR technique is a well-known design-technique that implements each register function as a set of three registers, votes these three outputs of these three registers together, and this produces the final output signal of this register function. Each register function that is implemented with the TMR consumes three registers and one Look-Up Table (LUT).

When three registers are implementing each register function, this group of three registers are sometimes referred to as a triplet.

The basic concept of TMR is that all three registers always sample the same data input, and have the same values. If radiation disturbs the stored charge/state of one of these three registers of the TMR triplet, two of the registers still have the correct logical value, and the LUT voter can still provide the correct/intended state that was stored into this TMR triplet.

## 3. Attribute Declaration

The TMR attribute syn\_radhardlevel triplicates the registers in the design and adds voter logic that looks at all three outputs to determine the final output based on the majority value. The value of the TMR attribute can be tmr or none. The syn\_radhardlevel attribute is supported at Global, Module Instance, and Register View levels in the Register Transfer Level (RTL) or FPGA Design Constraint (FDC), as listed in the following table.

#### Table 3-1. TMR Attribute

| Attribute Name   | Value | Global Attribute | Object                        |

|------------------|-------|------------------|-------------------------------|

| syn_radhardlevel | tmr   | Yes              | FDC: Global                   |

|                  |       |                  | Verilog: Top module           |

|                  |       |                  | VHDL: Top module architecture |

|                  | none  | No               | FDC: Register instance        |

|                  |       |                  | Verilog: Register             |

|                  |       |                  | VHDL: Signal                  |

#### Table 3-2. Attribute Level

| File                                         | Level at which<br>Attribute is Applied                                                                   | Example                                                                                                                                   |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| FDC through Synthesis<br>Scope or Libero >   | Libero > {tmr}                                                                                           | <pre>define_global_attribute {syn_radhardlevel} {tmr}</pre>                                                                               |

| Constraint Manage ><br>Netlist Attribute Tab | Instance level                                                                                           | <pre>define_attribute {v:work.t6} {syn_radhardlevel} {tmr}</pre>                                                                          |

|                                              | Register level                                                                                           | <pre>define_attribute {i:I_RDATA[7:0]} {syn_radhardlevel} {tmr}</pre>                                                                     |

| Verilog                                      | Global module top (datain1, datain2, datain3, da<br>clk, out1) /*synthesis syn_radhardlevel<br>= "tmr"*/ | —                                                                                                                                         |

|                                              | Register level                                                                                           | <pre>reg [1:0] datain2 /* synthesis syn_radhardlevel = "tmr"*/</pre>                                                                      |

| VHDL                                         | Global                                                                                                   | Architecture behavior of test is:<br>attribute syn_radhardlevel: string; attribute<br>syn_radhardlevel of behavior: architecture is "tmr" |

|                                              | Register level                                                                                           | Signal dout1: std_logic_vector(7 down to 0); attribute<br>syn_radhardlevel of dout1: signal is "tmr"                                      |

## 4. Spatial Placement

The **Place and Route** tool in the Libero SoC **Design Flow** tab includes a placement tool, which decides the best location on the die, to place each register. If a register function is implemented with the TMR technique, the placement tool picks the location on the die for each of these three registers in the TMR triplet.

Test data shows that when the three registers that comprise a TMR triplet are physically spaced apart from each other on the die, this improves (lowers) the SEU rate of the TMR register function. This is because the radiation event can upset two or more of the registers in the TMR triplet when these three registers are placed in the same logic cluster sharing the same cluster clock buffer.

The spatial separation in placement of TMR triplets in Libero SoC v12.4 and later actually places the triplets on three different cluster clocks. The spatial placement is constrained to achieve a balance of performance and SEU mitigation.

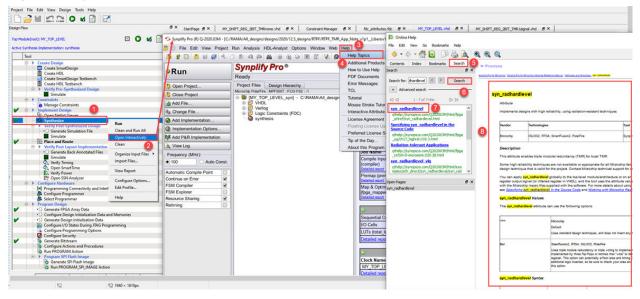

The following figure shows the syn\_radhardlevel TMR attribute.

Figure 4-1. syn\_radhardlevel TMR Attribute

### 5. Design Description

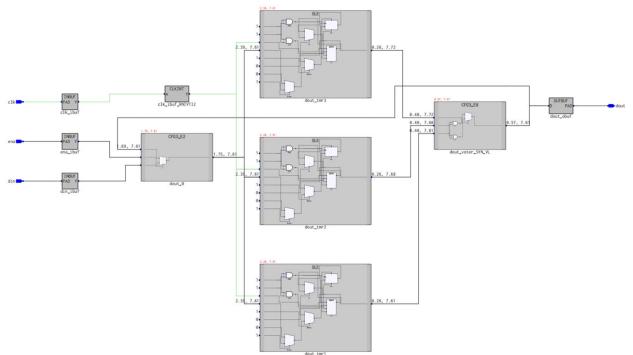

The FPGA design example describes how to implement TMR which consists of six different logical paths. Each path uses a different technique or is on a different level of the hierarchy, and these are used to show how to apply the syn\_radhardlevel synthesis attribute.

The description of the six different paths are as follows:

- PATH1: does not define any of the TMR attributes.

- PATH2: defines that one specific register in the top-level is not TMR'd by synthesis.

- PATH3: defines that one specific register in the top-level is TMR'd by synthesis.

- PATH4: defines that all registers in a component that is instantiated in the top-level are not TMR'd by synthesis.

- PATH5: defines that one specific register out of all the registers in the top-level is TMR'd by synthesis.

- PATH6: defines that all registers in a component that is instantiated in the top-level are TMR'd by synthesis.

The following table lists the path number and quantity of registers that are synthesized by each path.

| Path<br>Number | Registers<br>in this<br>circuit<br>path | syn_radhardlevel<br>is defined on the<br>quantity of<br>registers | syn_radhardlevel<br>is defined where | syn_radhardlevel<br>defined on this<br>object of the<br>design | syn_radhardlevel<br>is assigned this<br>value | Quantity<br>of<br>registers<br>used |

|----------------|-----------------------------------------|-------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------|-----------------------------------------------|-------------------------------------|

| PATH1          | 1                                       | Nothing                                                           | MY_TOP_LEVEL                         | Nothing assigned                                               | Nothing assigned                              | 1                                   |

| PATH2          | 1                                       | 0                                                                 | MY_TOP_LEVEL                         | Signal                                                         | no                                            | 1                                   |

| PATH3          | 1                                       | 1                                                                 | MY_TOP_LEVEL                         | Signal                                                         | tmr                                           | 3                                   |

| PATH4          | 2                                       | 0                                                                 | Component                            | Architecture                                                   | Nothing assigned                              | 2                                   |

| PATH5          | 2                                       | 1                                                                 | Component                            | 1 signal                                                       | 1 x tmr, 1 none                               | 4                                   |

| PATH6          | 2                                       | 2                                                                 | Component                            | Architecture                                                   | tmr                                           | 6                                   |

#### Table 5-1. PATH Information

Note: For 6. Design Examples, analyze the Synplify .srr log file output listed in the FFs that are TMR'd.

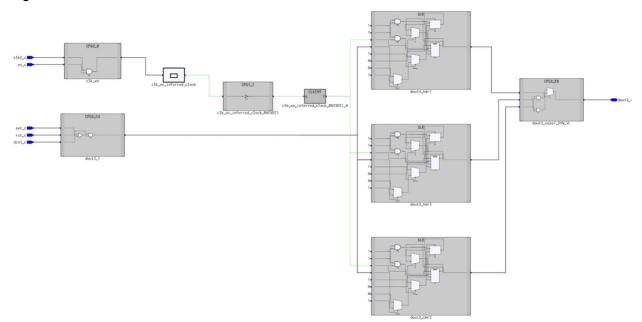

The example design is a pure VHDL code and consists of four VHDL source files as shown in the following figure.

#### Figure 5-1. Libero SoC Design Hierarchy

| Project File Edit View Design To | ools Help                |                                       |                           |

|----------------------------------|--------------------------|---------------------------------------|---------------------------|

|                                  |                          |                                       |                           |

| Design Hierarchy                 |                          |                                       | e >                       |

| Top Module(root): MY_TOP_LEVEL   |                          |                                       |                           |

| Build Herarchy                   |                          | Show: Components                      | · • • ? 🗞                 |

| B work                           | MY_ARCHITECTURE) (MY     | _TOP_LEVEL.vhd) [work]                |                           |

| MY_SHIFT_RE                      | G_2BIT_TMR1signal(MY_AR  | CHITECTURE) (MY_SHIFT_REG_2BIT_TMR1si | gnal.vhd) [work]          |

| MY_SHIFT_RE                      | G_2BIT_TMRarchitecture(M | Y_ARCHITECTURE) (MY_SHIFT_REG_2BIT_TM | Rarchitecture.vhd) [work] |

| MY_SHIFT_RE                      | G_2BIT_TMRnone(MY_ARCH   | HITECTURE) (MY_SHIFT_REG_2BIT_TMRnone | .vhd) [work]              |

| User HDL Source Fil              | es                       |                                       |                           |

### 5.1 PATH1 Description

PATH1 defines that one specific register in the top-level has no TMR attribute assigned to it. PATH1 is a VHDL RTL source code, describing a single DFF register, and the TMR attribute syn\_radhardlevel is not defined on this path. The Synthesis tool has no explicit guidance.

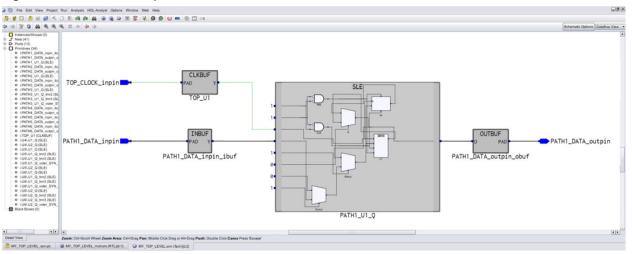

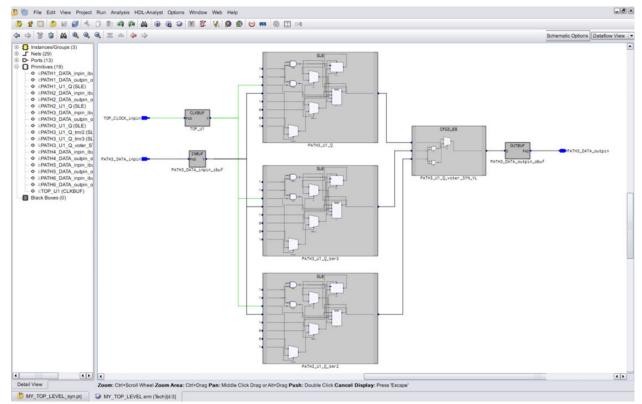

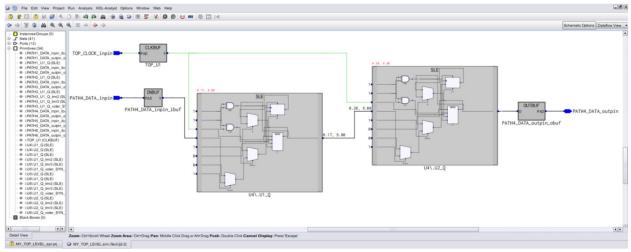

After synthesis, open **HDL-Analyst** > **Technology** > **Flattened View**, and then select the input port, output port, and clock port to see the gate implementation as shown in the following figure. This shows that PATH1 consumes one SLE macro, which is implemented by one DFF in one LE.

#### Figure 5-2. PATH1 Gate Implementation

### 5.2 PATH2 Description

PATH2 defines that one specific register in the top-level is not TMR'd by synthesis. PATH2 is a VHDL RTL source code, describing a single DFF register, and the TMR attribute syn\_radhardlevel is assigned a value none on the signal that is being driven by the register, to explicitly instruct the Synthesis tool not to implement TMR on the register.

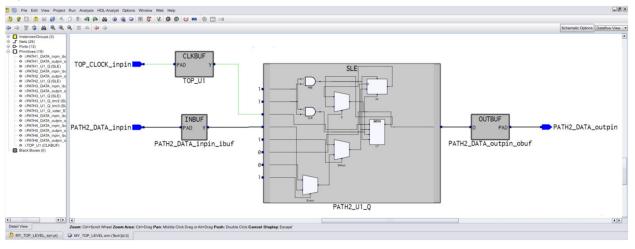

After synthesis, open **HDL-Analyst** > **Technology** > **Flattened View**, and then select the input port, output port, and clock port to see the gate implementation as shown in the following figure. This shows that PATH2 consumes one SLE macro, which is implemented by one DFF in one LE.

### 5.3 PATH3 Description

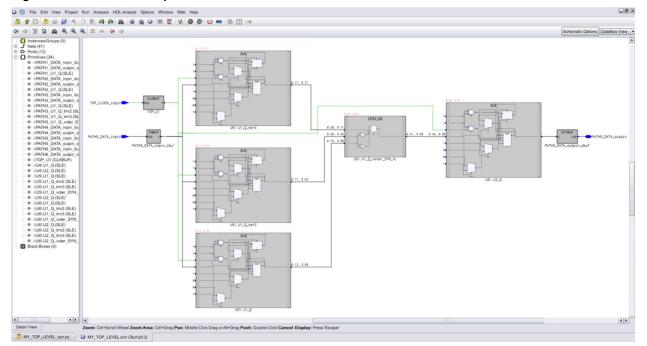

PATH3 defines that one specific register in the top-level is TMR'd by synthesis. PATH3 is a VHDL RTL source code, describing a single DFF register, and the TMR attribute syn\_radhardlevel is assigned a value tmr on the signal that is being driven by the register, to explicitly instruct the Synthesis tool to implement TMR on the register.

After synthesis, open **HDL-Analyst** > **Technology** > **Flattened View**, and then select the input port, output port, and clock port to see the gate implementation as shown in the following figure. This register is named as PATH3\_U1\_Q by VHDL code. Since this register has TMR attribute, the Synthesis tool is created for two additional registers, named

PATH3\_U1\_Q\_tmr2 and PATH3\_U1\_tmr3. This shows that PATH3 consumes three SLE macros and one CFG3 macro, which is implemented by three DFF in three LE's and one CFG3.

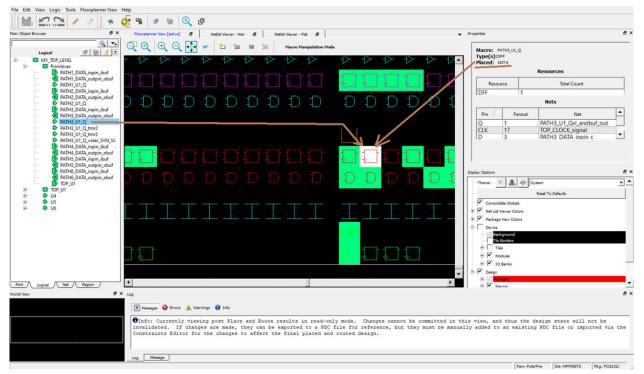

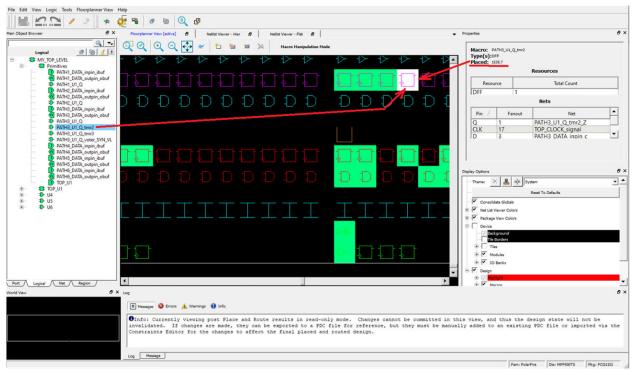

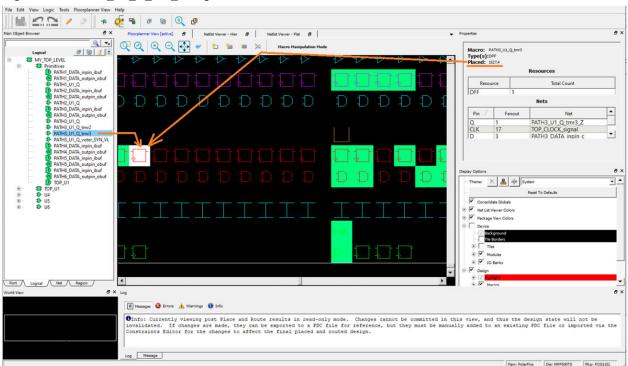

#### 5.3.1 Spatial Placement of the R-cells in a TMR Implemented Register Function

Libero SoC v12.4 or later has an enhanced feature that improves (lowers) the SEU rate of a TMR register. The enhanced Libero SoC placement tool physically places the three registers of the TMR triplet into distinct logic clusters on the die, preventing the sharing of cluster clock buffers. This improves (lowers) the SEU rate of the TMR register because it dramatically reduces the probability of a clock upset in the cluster clock affecting more than one of the three registers in the TMR triplet.

When the TMR attribute is assigned, the three registers are physically spaced apart with the Chip Planner tool placement of TMR. They are not directly next to each other on the die. It improves (reduces) the SEU rate relative to the SEU rate which is observed if these three registers were placed on the same cluster clock branch.

The location of the three registers in the Chip Planner is mapped as follows:

- PATH3\_U1\_Q is located at coordinates 1537,4 on the die.

- PATH3\_U1\_Q\_tmr\_2 is located at coordinates 1539,7 on the die.

- PATH3\_U1\_Q\_tmr\_3 is located at coordinates 1527,4 on the die.

#### Figure 5-5. PATH3\_U1\_Q Register

#### Figure 5-6. PATH3\_U1\_Q\_tmr\_2 Register

#### Figure 5-7. PATH3\_U1\_Q\_tmr\_3 Register

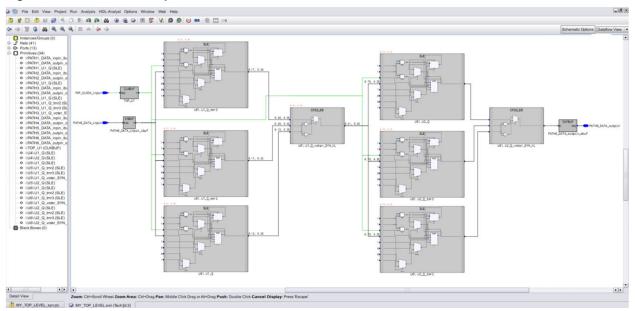

### 5.4 PATH4 Description

PATH4 defines that all registers in a component that is instantiated in the top-level are not TMR'd by synthesis. Its logic is defined in an instantiated component, named 'MY\_SHIFT\_REG\_2BIT\_TMRnone', and the TMR attribute syn radhardlevel is not defined on this component in the top-level.

The 'MY\_SHIFT\_REG\_2BIT\_TMRnone' component is the VHDL RTL source code, describing two DFF registers connected in series (a 2-bit shift register). The TMR attribute syn radhardlevel is not defined in this VHDL code.

After synthesis, open the **HDL-Analyst** > **Technology** > **Flattened View**, and then select the input port, output port, and clock port to see the gate implementation as shown in the following figure. This shows that PATH4 consumes two SLE macros, which is implemented by two DFF in two LE's.

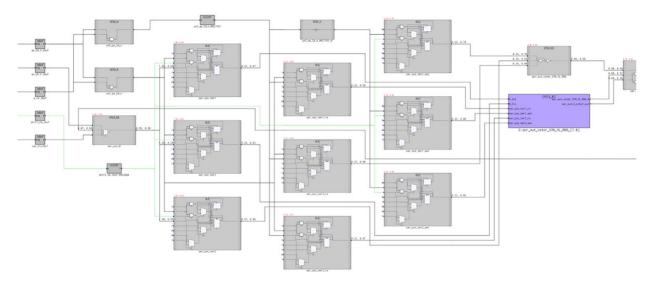

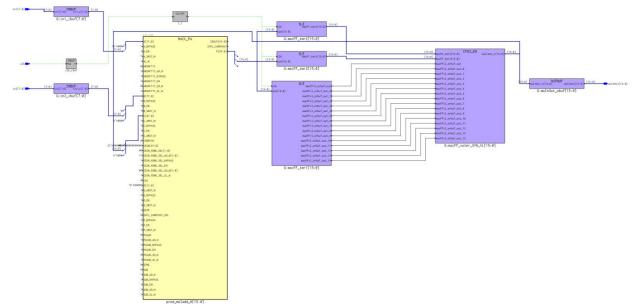

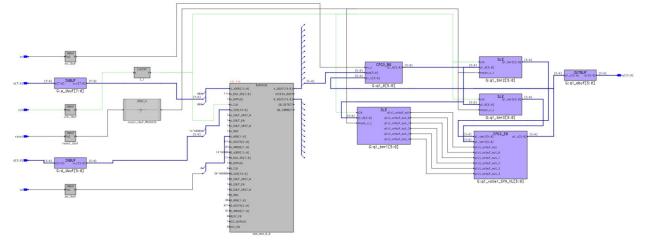

### 5.5 PATH5 Description

PATH5 defines that one of the two registers in the instantiated component is to be TMR'd, and one of the two registers in the same instantiated component is not to be TMR'd by Synthesis. Its logic is defined in an instantiated component, named 'MY\_SHIFT\_REG\_2BIT\_TMR1signal', and the TMR attribute syn\_radhardlevel is not defined on this component in the top-level.

The 'MY\_SHIFT\_REG\_2BIT\_TMR1signal' component is the VHDL RTL source code, describing two DFF registers connected in series (a 2-bit shift register), and the TMR attribute syn\_radhardlevel is defined as tmr on one signal driven by one register and is defined as none on one signal driven by a second register.

After synthesis, open the **HDL-Analyst** > **Technology** > **Flattened View**, and then select the input port, output port, and clock port to see the gate implementation as shown in the following figure. This shows that PATH5 logic consumptions are:

- The first register (that is TMR'd) consumes three SLE macros and one CFG3, which is implemented by three DFF in three LE's, and one CFG3.

- The second register (that is not TMR'd) consumes one SLE macro in one LE.

#### Figure 5-9. PATH5 Gate Implementation

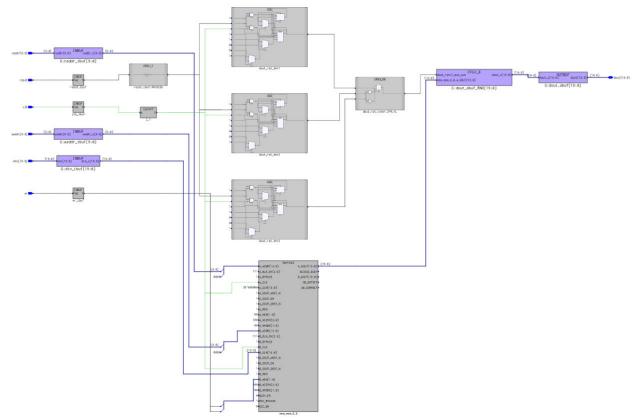

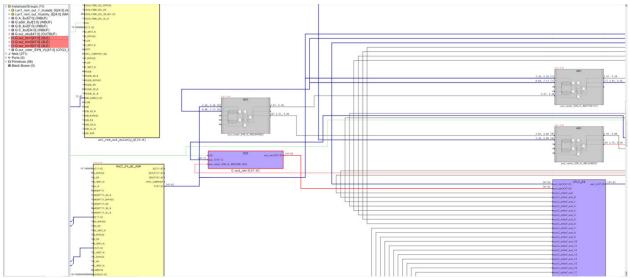

### 5.6 PATH6 Description

PATH6 defines that one of the two registers in the instantiated component are TMR'd by Synthesis. Its logic is defined in an instantiated component, named 'MY\_SHIFT\_REG\_2BIT\_TMRarchitecture' and the TMR attribute <code>syn\_radhardlevel</code> is not defined on this component in the top-level.

The 'MY\_SHIFT\_REG\_2BIT\_TMRarchitecture' component is VHDL RTL source code, describing two DFF registers connected in series (a 2-bit shift register), and the TMR attribute <code>syn\_radhardlevel</code> is defined as <code>tmr</code> on the architecture, so all registers in this file are to be TMR'd by Synthesis.

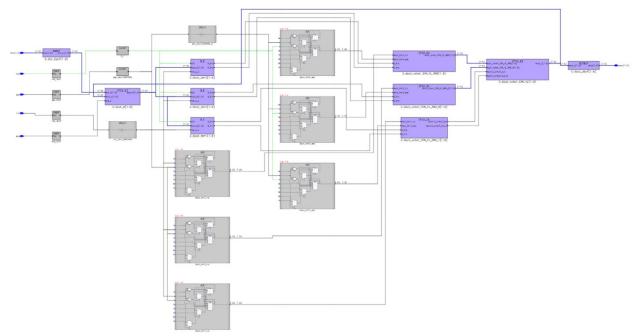

After synthesis, open the **HDL-Analyst** > **Technology** > **Flattened View**, and then select the input port, output port, and clock port to see the gate implementation as shown in the following figure. This shows that PATH6 logic consumptions are:

The first register (that is TMR'd) consumes three SLE macros and one CFG3 macro, which is implemented by three DFF in three LE's and one CFG3.  The second register (that is TMR'd) consumes three SLE macros and one CFG3 macro, which is implemented by three DFF in three LE's and one CFG3.

#### Figure 5-10. PATH6 Gate Implementation

**Note:** When applying the syn\_radhardlevel on a signal, you must first define the signal in the VHDL code, and then the signal is declared. You can define the syn\_radhardlevel applied to that signal.

Example: If the user declares a signal on line#100 of the VHDL/Verilog design, you must apply the syn radhardlevel on line# 101 or later. Otherwise, Synplify Synthesis fails with a synthesis error.

**Note:** When a component is instantiated in a VHDL/Verilog block, the user cannot guide synthesis to implement that instantiated block with the TMR, by applying the syn\_radhardlevel attribute onto the signal that the instantiated block is driving in the upper-level block.

**Note:** Do not apply syn\_radhardlevel to the signal that are instantiated as modules. If you apply the syn\_radhardlevel to the output signal of an instantiated block, Synthesis passes without an error or Synthesis does not implement it as TMR, and does not report any note, warning, or error.

### 6. Design Examples

Design examples related to TMR are explained in this chapter. All these examples are validated on the Libero SoC v12.4 Synplify Pro tool.

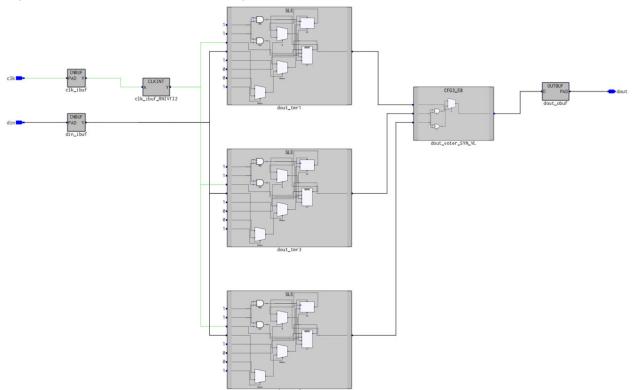

**Example 1**: Basic Flop without Control Signal (TMR attribute globally applied through FDC file). Synplify Pro triplicates each register and inserts majority voting logic at register outputs.

HDL:

FDC:

define global attribute {syn radhardlevel} {tmr}

#### Figure 6-1. Basic Flop without Control Signal

**Example 2**: Basic Flop with Asynchronous Reset Control Signal (TMR attribute is globally applied on the module in Verilog)

Synplify Pro triplicates each register and inserts majority voting logic at register outputs.

else dout <= din; endmodule

#### Figure 6-2. Basic Flop with Asynchronous Reset Control Signal

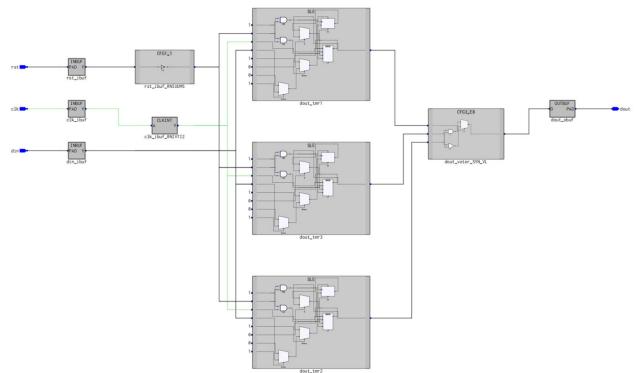

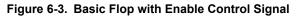

**Example 3**: Basic Flop with Enable Control Signal (TMR attribute globally applied in Verilog)

Synplify Pro triplicates each register and inserts majority voting logic at register outputs. Enable logic implemented using voter logic output.

HDL:

```

module test3 (clk, ena, din, dout);

input clk, ena, din;

output reg dout;

always @(posedge clk)

if (ena)

dout <= din;

endmodule

```

#### FDC:

define\_global\_attribute {syn\_radhardlevel} {tmr}

**Example 4**: Flop with Asynchronous Reset and Set Control Signals (TMR attribute is globally applied in FDC)

Synplify Pro triplicates each register and inserts majority voting logic at register outputs. Asynchronous set logic is implemented using latch and flop, and triplicated.

HDL:

#### FDC:

define\_global\_attribute {syn\_radhardlevel} {tmr}

Figure 6-4. Flop with Asynchronous Reset and Set Control Signals

**Example 5**: Flop with Asynchronous Reset, Asynchronous Set, and Enable Control Signal (TMR attribute globally applied in Verilog)

Synplify Pro triplicates each register and inserts majority voting logic at register outputs. Asynchronous set logic is implemented using latch and flop, and triplicated. Enable logic implemented using voter logic output.

Figure 6-5. Flop with Asynchronous Reset, Asynchronous Set, and Enable Control Signal applied in Verilog

**Example 6**: Flop with Asynchronous Reset, Asynchronous Set, and Enable Control Signal (TMR attribute globally applied in VHDL)

Synplify Pro triplicates each register and inserts majority voting logic at register outputs. Asynchronous set logic is implemented using latch and flop, and triplicated. Enable logic is implemented using voter logic output.

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENTITY test39_sle_reseten_globtmr IS

PORT (

shift ck:in

STD LOGIC;

STD LOGIC;

ser in:in

STD LOGIC;

p_in:in

as_ld_n:in

STD_LOGIC;

en_ck_n:in

STD LOGIC;

ser out:out

STD LOGIC

);

END test39_sle_reseten_globtmr;

architecture behaviour of test39 sle reseten globtmr is

attribute syn radhardlevel: string;

attribute syn_radhardlevel of behaviour: architecture is "tmr";

begin

process (as_ld_n,p_in,shift_ck)

begin

IF (as ld n = '0' and p in = '0') THEN

ser out <= '0';</pre>

ELSIF (as_ld_n = '0' \text{ and } p_in = '1') THEN

ser_out <= '1';</pre>

ELSIF rising edge(shift ck) THEN

IF (en ck n = '0') THEN

ser out <= ser in;

END IF;

END IF;

END process;

END behaviour;

```

Figure 6-6. Flop with Asynchronous Reset, Asynchronous Set, and Enable Control Signal applied in VHDL

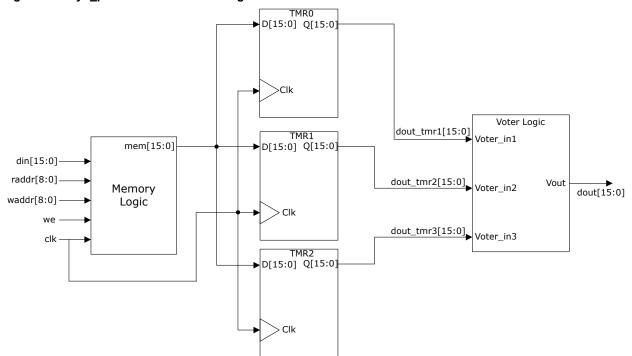

When the syn\_preserve attribute is applied on the read address register and output register of the memory, Synplify Pro stops packing the registers inside the RAM block and triplicates each register and inserts majority voting logic at register outputs.

Figure 6-7. syn\_preserve Attribute on Register Associated with RAM Block

**Example 8**: No syn\_preserve attribute on register with asynchronous reset associated with RAM block (TMR attribute globally applied in FDC)

When the syn\_preserve attribute is not applied to the output register of memory, Synplify Pro packs the registers inside the RAM block and triplicates the control logic and inserts majority voting logic at register outputs.

HDL:

```

module ram 2port outreg areset(clk,din,wr,reset,waddr,raddr,dout);

input clk;

input [19:0] din;

input wr,reset;

input [9:0] waddr, raddr;

output [19:0] dout;

reg [19:0] dout;

reg [19:0] mem [0:1023];

always@(posedge clk)

begin

if(wr)

mem[waddr] <= din;</pre>

end

always@(posedge clk or posedge reset )

begin

if(reset)

dout <= 0;

else

dout <= mem[raddr];</pre>

end

endmodule

```

#### FDC:

define\_global\_attribute {syn\_radhardlevel} {tmr}

Figure 6-8. No syn\_preserve Attribute on Register with Asynchronous Reset Associated with RAM Block

**Example 9**: The syn\_preserve attribute on register associated with DSP logic (TMR attribute globally applied in FDC, syn\_preserve in FDC)

When the syn\_preserve attribute is applied to the input and output register of multiplier/MAC, Synplify Pro stops packing the register inside block DSP and triplicates each register and inserts majority voting logic at register outputs.

HDL:

FDC:

```

define_global_attribute {syn_radhardlevel} {tmr}

define_attribute {i:macFF[15:0]} {syn_preserve} {1}

```

Figure 6-9. syn\_preserve Attribute on Register Associated with DSP Logic

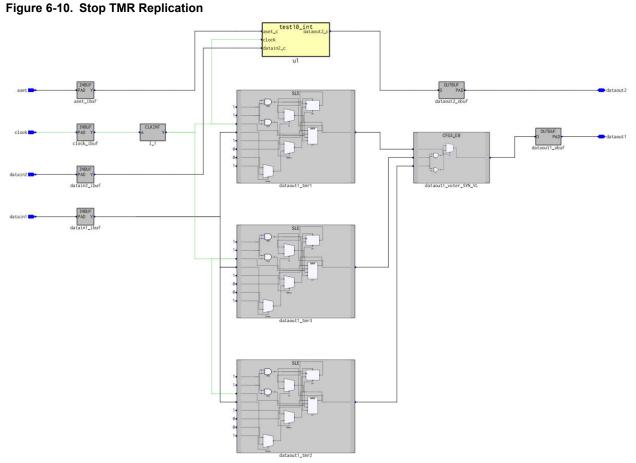

Example 10: Stop TMR replication (TMR attribute set to none in the FDC file for instance)

Synplify Pro stops the triplication of registers inside the module when the syn\_radhardlevel = none attribute is specified for the view.

HDL:

```

module test10(clock,aset,datain1,datain2, dataout1, dataout2);

input clock, aset, datain1, datain2;

output reg dataout1;

output dataout2;

always @(posedge clock)

dataout1 <= datain1;</pre>

test10 int u1 (clock (clock), .aset (aset), datain (datain2), dataout (dataout2));

endmodule

module test10 int(clock,aset,datain,dataout);

input clock, aset;

input datain;

output reg dataout;

always @(posedge clock or posedge aset)

begin

if (aset == 1'b1)

dataout <= 1;</pre>

else

dataout <= datain;</pre>

end

endmodule

```

FDC:

```

define_global_attribute {syn_radhardlevel} {tmr}

define_attribute {i:ul.dataout} {syn_radhardlevel} {none}

```

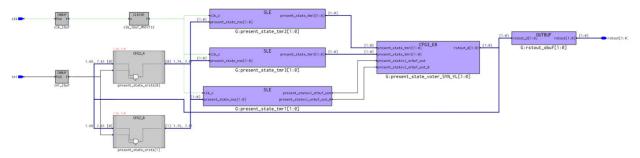

Example 11: Safe CASE FSM (TMR attribute set globally in RTL)

Synplify Pro triplicates all state register and inserts voter logic at the output of the register. Illegal state transition logic implemented using voter logic output.

```

module state_test(clk, in1,rstout)/* synthesis syn_radhardlevel=tmr */;

input in1;

input clk;

parameter s0 = 2'b00;

parameter s1 = 2'b01;

parameter s2 = 2'b10;

reg [1:0] present state, next state;

wire [1:0] present_state_keep/* synthesis syn_preserve=1 */;

output [1:0] rstout;

assign present_state_keep = present_state;

assign rstout = present_state_keep;

always @ (posedge clk)

begin

present_state <= next state;</pre>

end

always @ (in1, present state)

case (present state)

s0: begin

if (in1) next state <= s1;

else next_state <= s0;</pre>

end

sl: begin

if (in1) next_state <= s2;

else next_state <= s0;</pre>

end

s2: begin

if (in1) next state <= s1;

```

```

else next_state <= s0;

end

default: next_state <= s0;

endcase

endmodule

```

#### Figure 6-11. Safe CASE FSM

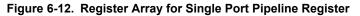

**Example 12**: Register array for single port pipeline register, use of syn\_ramstyle = register attribute, TMR attribute applied on pipeline register.

Synplify Pro triplicates the pipeline register and none of the registers in the design.

HDL:

```

module test26_spregarray_pipe_globtmr(clk,we,addr,din,dout);

output reg [3:0] dout /* synthesis syn_radhardlevel=tmr */;

input [3:0] din;

input [3:0] addr;

input we, clk;

reg [3:0] mem [15:0]/* synthesis syn ramstyle= "registers" */;

reg [3:0] dout1;

always @(posedge clk)

begin

dout1 <= mem[addr];</pre>

if(we)

mem[addr] <= din;</pre>

end

always @(posedge clk)

begin

dout <= dout1;</pre>

end

endmodule

```

Example 13: Shift register implemented using URAM (TMR attribute is applied through FDC on the output register).

Synplify Pro triplicates the output register and inserts majority voting logic at register outputs.

```

module test33_shiftregINIT_fdctmr(clk,we,din,dout,s_rst,addr);

input clk, we, s_rst;

input [6:0] din;

input [5:0] addr;

output [6:0] dout;

```

```

reg [6:0] dout /* synthesis syn_preserve = 1 */;;

reg [6:0] regBank[36:0];

integer i;

always @(posedge clk) begin

if (we) begin

for (i=37; i>0; i=i-1) begin

regBank[i] <= regBank[i-1];

end

regBank[0] <= din;

end

dout = regBank[addr];

end

endmodule

```

#### FDC:

```

define_attribute {i:dout} {syn_radhardlevel} {tmr}

```

Figure 6-13. Shift Register Implemented using URAM

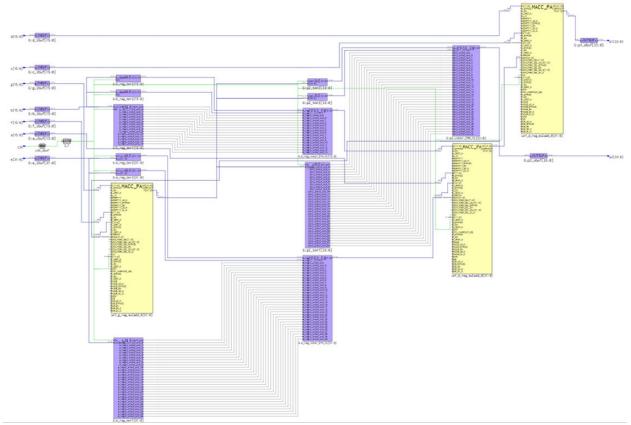

Synplify Pro triplicates the register on which the syn\_preserve attribute is applied and inserts majority voting logic at register outputs.

```

module test49_maccvariations_tmr( clk,a,b,c,d,e,f,g,p1,p2 );

/* synthesis syn radhardlevel=tmr */

parameter M = 16;

parameter N = 16;

input clk;

input signed[M-1:0] a, b;

input signed[N-1:0] c, d,f,g;

input signed[N*2-1:0] e;

output signed[M+N+1:0] p1,p2;

reg [M-1:0] a_reg;

reg [M-1:0] b_reg /* synthesis syn_preserve=1 */;

reg [N-1:0] c_reg, d_reg;

reg [N-1:0] f_reg, g_reg;

reg [N*2-1:0] e_reg /* synthesis syn_preserve=1 */;

reg [M+N+1:0] p1;

reg [M+N+1:0] p2 /* synthesis syn preserve=1 */;

always@(posedge clk)

begin

a_reg <= a;

b_reg <= b;</pre>

c_reg <= c;</pre>

d reg <= d;

e_reg <= e;

f_reg <= f;

g_reg <= g;

p\overline{1} \le e reg + (a reg * b reg) + (c reg * d reg);

p2 \le p\overline{2} + (f_reg * g_reg);

```

end endmodule

Figure 6-14. Register triplication with syn\_preserve attribute on Few Registers Associated with MACC Logic

Example 15: Global TMR attribute in FDC on three modules, but disable TMR attribute on one module in RTL.

Synplify Pro triplicates the registers in t1 and t3 module, but it does not triplicate registers in the t2 module.

```

module test9_3modules_fdcglobtmr(clk0,clk1,clk2,rst,set,en,din1, dout1,din2,dout2,din3,dout3);

input clk0, clk1, clk2, rst, set, en, din1, din2, din3;

output dout1, dout2, dout3;

t1 t1_0 (clk0, rst, set, din1, dout1);

t2 t2<sup>0</sup> (clk1, rst, set, din2, dout2);

t3 t3<sup>0</sup> (clk2, rst, set,en,din3, dout3);

endmodule

module t1 (clk0, rst, set, din1, dout1);

input clk0, rst, set;

input din1;

output reg dout1;

always @(posedge clk0 or posedge rst or posedge set)

if (rst)

dout1 <= 0;

else if (set)

dout1 <= 1;

else

dout1 <= din1;</pre>

endmodule

module t2 (clk1, rst, set, din2, dout2)/* synthesis syn_radhardlevel = "none" */;

input clk1, rst, set;

input din2;

output reg dout2;

always @(posedge clk1)

if (rst)

dout2 <= 0;

else if (set)

```

```

dout2 <= 1;

else

dout2 <= din2;

endmodule

module t3 (clk2, rst, set, en, din3, dout3);

input clk2, rst, set,en;

input din3;

output reg dout3;

assign clk_en = clk2 && en;

always @(negedge clk_en)

if (!rst)

dout3 <= 0;

else if (!set)

dout3 <= 1;

else

dout3 <= din3;</pre>

endmodule

```

#### FDC:

define\_global\_attribute {syn\_radhardlevel} {tmr}

#### Figure 6-15. Global TMR Attribute in FDC on Three Modules

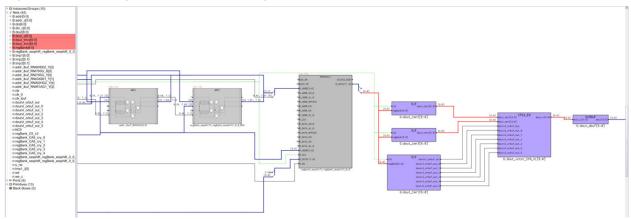

**Example 16**: Register triplication with syn\_preserve attribute on registers associated with MACC\_PC\_BA\_ROM logic.

Synplify Pro triplicates the output register on which the syn\_preserve attribute is applied. MACC\_PA\_BC\_ROM is inferred.

```

module test31_maccrom_synpreserve_globtmr(clk,A,B,C,out,addr)/* synthesis

syn_radhardlevel=tmr */;

input clk;

input [7:0] A;

input [7:0] B;

input [34:0] C;

input [3:0] addr;

output [47:0] out;

reg [16:0] rom_out;

reg [47:0] out/* synthesis syn_preserve=1 */;

always@(posedge clk)

begin

case (addr)

```

| <pre>4'd0: rom_out &lt;= 17'b011000010011001;<br/>4'd1: rom_out &lt;= 17'b00001101100111001;<br/>4'd2: rom_out &lt;= 17'b010110111010000000001;<br/>4'd4: rom_out &lt;= 17'b010010000100010101;<br/>4'd5: rom_out &lt;= 17'b01001000100010101;<br/>4'd6: rom_out &lt;= 17'b01001010101010111;<br/>4'd7: rom_out &lt;= 17'b01001010101010111;<br/>4'd9: rom_out &lt;= 17'b0100101011111010;<br/>4'd10: rom_out &lt;= 17'b01000100010001;<br/>4'd11: rom_out &lt;= 17'b10100011000010001;<br/>4'd12: rom_out &lt;= 17'b10100001000010001;<br/>4'd13: rom_out &lt;= 17'b1011010101111101;<br/>4'd13: rom_out &lt;= 17'b01110100000100001;<br/>4'd14: rom_out &lt;= 17'b01110100000100001;<br/>4'd14: rom_out &lt;= 17'b011010101011110;<br/>4'd16: rom_out &lt;= 17'b0010010100001;<br/>4'd16: rom_out &lt;= 17'b0010010101010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end<br/>endmodule</pre> |                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| <pre>4'd2: rom_out &lt;= 17'b01011011110110011;<br/>4'd3: rom_out &lt;= 17'b010010000000000000000000000000000000</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4'd0: rom out <= 17'b01100000100011001;   |

| <pre>4'd3: rom_out &lt;= 17'b10100110000000001;<br/>4'd4: rom_out &lt;= 17'b01101001111111001;<br/>4'd5: rom_out &lt;= 17'b010100010001001101;<br/>4'd6: rom_out &lt;= 17'b10101001001001101;<br/>4'd7: rom_out &lt;= 17'b1001010101011111;<br/>4'd9: rom_out &lt;= 17'b1001010111110110;<br/>4'd10: rom_out &lt;= 17'b10100011000010001;<br/>4'd11: rom_out &lt;= 17'b101000110010111111;<br/>4'd12: rom_out &lt;= 17'b10110101011111011;<br/>4'd13: rom_out &lt;= 17'b0111010011000001;<br/>4'd14: rom_out &lt;= 17'b01110100011000001;<br/>4'd15: rom_out &lt;= 17'b011010101100001;<br/>4'd16: rom_out &lt;= 17'b00101010100001;<br/>4'd16: rom_out &lt;= 17'b001001010100001;<br/>4'd16: rom_out &lt;= 17'b0010010101010101;<br/>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                            | 4'd1: rom out <= 17'b00001101100111001;   |

| <pre>4'd4: rom_out &lt;= 17'b01101001111111001;<br/>4'd5: rom_out &lt;= 17'b010100010001001101;<br/>4'd6: rom_out &lt;= 17'b101011010001101;<br/>4'd7: rom_out &lt;= 17'b100101010101011;<br/>4'd8: rom_out &lt;= 17'b1001010111110110;<br/>4'd10: rom_out &lt;= 17'b1000011000010001;<br/>4'd11: rom_out &lt;= 17'b101000110010111101;<br/>4'd12: rom_out &lt;= 17'b1011010110111101;<br/>4'd13: rom_out &lt;= 17'b0111010010100001;<br/>4'd14: rom_out &lt;= 17'b011101001000001;<br/>4'd14: rom_out &lt;= 17'b01101010100001;<br/>4'd15: rom_out &lt;= 17'b011010010100001;<br/>4'd16: rom_out &lt;= 17'b00100101010001;<br/>default: rom_out &lt;= 17'b0010010101010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                  | 4'd2: rom out <= 17'b01011011110110011;   |

| <pre>4'd4: rom_out &lt;= 17'b01101001111111001;<br/>4'd5: rom_out &lt;= 17'b010100010001001101;<br/>4'd6: rom_out &lt;= 17'b101011010001101;<br/>4'd7: rom_out &lt;= 17'b100101010101011;<br/>4'd8: rom_out &lt;= 17'b1001010111110110;<br/>4'd10: rom_out &lt;= 17'b1000011000010001;<br/>4'd11: rom_out &lt;= 17'b101000110010111101;<br/>4'd12: rom_out &lt;= 17'b1011010110111101;<br/>4'd13: rom_out &lt;= 17'b0111010010100001;<br/>4'd14: rom_out &lt;= 17'b011101001000001;<br/>4'd14: rom_out &lt;= 17'b01101010100001;<br/>4'd15: rom_out &lt;= 17'b011010010100001;<br/>4'd16: rom_out &lt;= 17'b00100101010001;<br/>default: rom_out &lt;= 17'b0010010101010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                  | 4'd3: rom out <= 17'b1010011000000001;    |

| <pre>4'd5: rom_out &lt;= 17'b010100010010101;<br/>4'd6: rom_out &lt;= 17'b01010010001001101;<br/>4'd7: rom_out &lt;= 17'b0100100100101011;<br/>4'd8: rom_out &lt;= 17'b011011100011111;<br/>4'd9: rom_out &lt;= 17'b01000110000010001;<br/>4'd10: rom_out &lt;= 17'b01000110000010011;<br/>4'd12: rom_out &lt;= 17'b01101010101111011;<br/>4'd13: rom_out &lt;= 17'b01101010101111011;<br/>4'd14: rom_out &lt;= 17'b0111010001000001;<br/>4'd14: rom_out &lt;= 17'b011010100010001;<br/>4'd16: rom_out &lt;= 17'b00100101010001001;<br/>4'd16: rom_out &lt;= 17'b0010010101010101;<br/>default: rom_out &lt;= 17'b00010010101010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                          | —                                         |

| <pre>4'd6: rom_out &lt;= 17'b101011010001101;<br/>4'd7: rom_out &lt;= 17'b01001001010010101;<br/>4'd8: rom_out &lt;= 17'b0110111000111111;<br/>4'd9: rom_out &lt;= 17'b1001010111110110;<br/>4'd10: rom_out &lt;= 17'b1100000100001;<br/>4'd11: rom_out &lt;= 17'b111000001001101111;<br/>4'd12: rom_out &lt;= 17'b111010101101111011;<br/>4'd13: rom_out &lt;= 17'b01101010101111011;<br/>4'd14: rom_out &lt;= 17'b0011011010011110;<br/>4'd15: rom_out &lt;= 17'b11110101000010001;<br/>4'd16: rom_out &lt;= 17'b0001001011010011;<br/>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                         |                                           |

| <pre>4'd7: rom_out &lt;= 17'b0100100101010101;<br/>4'd8: rom_out &lt;= 17'b01110111000111111;<br/>4'd9: rom_out &lt;= 17'b01001010111110110;<br/>4'd10: rom_out &lt;= 17'b0100011000010001;<br/>4'd11: rom_out &lt;= 17'b11100000110111011;<br/>4'd12: rom_out &lt;= 17'b01101010110111011;<br/>4'd13: rom_out &lt;= 17'b011010101000001;<br/>4'd14: rom_out &lt;= 17'b011010101000010001;<br/>4'd15: rom_out &lt;= 17'b00100101010001001;<br/>default: rom_out &lt;= 17'b00010010101010101;<br/>default: rom_out &lt;= 17'b00010010101010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                                                                |                                           |

| <pre>4'd8: rom_out &lt;= 17'b01110111000111111;<br/>4'd9: rom_out &lt;= 17'b01001010111110110;<br/>4'd10: rom_out &lt;= 17'b0100011000010001;<br/>4'd11: rom_out &lt;= 17'b11100000110111011;<br/>4'd12: rom_out &lt;= 17'b1011010110111011;<br/>4'd13: rom_out &lt;= 17'b0111010011000001;<br/>4'd14: rom_out &lt;= 17'b011010100010001;<br/>4'd15: rom_out &lt;= 17'b11110101000010001;<br/>4'd16: rom_out &lt;= 17'b0001001011010101;<br/>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                                                                                                                     | —                                         |

| <pre>4'd9: rom_out &lt;= 17'b10010101111110110;<br/>4'd10: rom_out &lt;= 17'b010001000010001;<br/>4'd11: rom_out &lt;= 17'b11100000110110011;<br/>4'd12: rom_out &lt;= 17'b011010110110111101;<br/>4'd13: rom_out &lt;= 17'b0111010010000001;<br/>4'd14: rom_out &lt;= 17'b0110101000010001;<br/>4'd15: rom_out &lt;= 17'b11110101000010001;<br/>4'd16: rom_out &lt;= 17'b0001001011010101;<br/>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |

| <pre>4'd10: rom_out &lt;= 17'b0100011000010001;<br/>4'd11: rom_out &lt;= 17'b11100000110110011;<br/>4'd12: rom_out &lt;= 17'b10110101101111011;<br/>4'd13: rom_out &lt;= 17'b0111101001100001;<br/>4'd14: rom_out &lt;= 17'b0110110100011001;<br/>4'd15: rom_out &lt;= 17'b111101000010001;<br/>4'd16: rom_out &lt;= 17'b0001001011010101;<br/>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4'd8: rom out <= 17'b01110111000111111;   |

| <pre>4'd11: rom_out &lt;= 17'b11100000110110011;<br/>4'd12: rom_out &lt;= 17'b10110101101111011;<br/>4'd13: rom_out &lt;= 17'b011110100100001;<br/>4'd14: rom_out &lt;= 17'b0110110100011010;<br/>4'd15: rom_out &lt;= 17'b1111010000010001;<br/>4'd16: rom_out &lt;= 17'b0001001011010101;<br/>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4'd9: rom out <= 17'b10010101111110110;   |

| <pre>4'd12: rom_out &lt;= 17'b10110101101111011;<br/>4'd13: rom_out &lt;= 17'b01111010011000001;<br/>4'd14: rom_out &lt;= 17'b00110110100111110;<br/>4'd15: rom_out &lt;= 17'b111101000010001;<br/>4'd16: rom_out &lt;= 17'b0001001011010101;<br/>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4'd10: rom out <= 17'b01000110000010001;  |

| <pre>4'd13: rom_out &lt;= 17'b01111010011000001;<br/>4'd14: rom_out &lt;= 17'b00110110100111110;<br/>4'd15: rom_out &lt;= 17'b11110101000010001;<br/>4'd16: rom_out &lt;= 17'b0001001011010101;<br/>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4'd11: rom out <= 17'b11100000110110011;  |

| <pre>4'd14: rom_out &lt;= 17'b00110110100111110;<br/>4'd15: rom_out &lt;= 17'b11110101000010001;<br/>4'd16: rom_out &lt;= 17'b0001001011010101;<br/>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4'd12: rom out <= 17'b10110101101111011;  |

| <pre>4'd14: rom_out &lt;= 17'b00110110100111110;<br/>4'd15: rom_out &lt;= 17'b11110101000010001;<br/>4'd16: rom_out &lt;= 17'b0001001011010101;<br/>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4'd13: rom_out <= 17'b01111010011000001;  |

| <pre>4'd15: rom_out &lt;= 17'b1111010100010001;<br/>4'd16: rom_out &lt;= 17'b00010010110101001;<br/>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                           |

| <pre>4'd16: rom_out &lt;= 17'b00010010110101001;<br/>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                         |

| <pre>default: rom_out &lt;= 17'b0001001011010101;<br/>endcase<br/>out &lt;= (rom_out * A) + B;<br/>end</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                           |

| endcase _<br>out <= (rom_out * A) + B;<br>end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                           |

| <pre>out &lt;= (rom_out * A) + B; end</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | default: rom_out <= 17'b0001001011010101; |

| end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | endcase                                   |

| end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $out \leq (rom out * A) + B;$             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |

| endmodule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | endmodule                                 |

Figure 6-16. syn\_preserve Attribute on Registers Associated with MACC\_PC\_BA\_ROM Logic

Synplify Pro infers RAM1Kx20 and triplicates the pipeline register.

```

module ram_singleport_addreg_pipe_areset_en(clk,we,a,d,q1,reset,en);

input [5:0] d;

input [7:0] a;

input clk, we,reset,en;

output [5:0] q;

wire [5:0] q;

reg [7:0] addr;

reg [5:0] q1;

reg [5:0] mem [255:0];

always @(posedge clk) begin

addr <= a;

if(we)

mem[a] <= d;</pre>

end

assign q = mem[addr];

always @ (posedge clk or posedge reset)

begin

if(reset)

q1 <= 0;

else if(en)

```

```

q1 <= q;

end

endmodule

```

#### FDC:

```

define_global_attribute {syn_radhardlevel} {tmr}

```

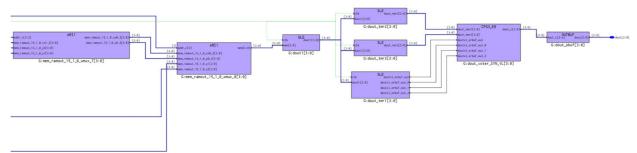

#### Figure 6-17. Register Triplication of Pipeline Register with Control Logic Associated with Single Port RAM

**Example 18**: Register triplication of output register with control logic associated with Dual Port RAM, use of syn keep and syn preserve attributes.

Synplify Pro infers RAM in registers and LUTs. All inferred registers are triplicate, since the attribute is applied globally.

```

module ram dport addreg 8kx2(data0,data1,waddr0,waddr1,we0,we1,clk, q0, q1);

/*synthesis syn_radhardlevel="tmr" */

parameter d width = 2;

parameter addr width = 10;

parameter mem_depth = 1024;

input [d width-1:0] data0, data1;

input [addr_width-1:0] waddr0, waddr1;

input we0, we1, clk;

reg [d width-1:0] mem [mem depth-1:0];

reg [addr_width-1:0] reg waddr0, reg waddr1;

output [d_width-1:0] q0 /*synthesis syn_preserve=1 */;

output [d_width-1:0] q1 /*synthesis syn_preserve=1 */;

wire [addr_width-1:0] reg_waddr0_net/* synthesis syn_keep = 1 */;

wire [addr width-1:0] reg waddr1 net/* synthesis syn keep = 1 */;

assign reg_waddr0_net = reg_waddr0;

assign reg_waddr1_net = reg_waddr1;

assign q0 = mem[reg_waddr0_net];

assign q1 = mem[reg_waddr1_net];

always (posedge clk)

begin

if (we0)

mem[waddr0] <= data0;</pre>

reg waddr0 <= waddr0;</pre>

end

always @(posedge clk)

begin

if (wel)

mem[waddr1] <= data1;</pre>

reg waddr1 <= waddr1;</pre>

end

endmodule

```

### 6.1 Limitations

- The syn\_radhardlevel TMR attribute triplicates the inferred Sequential Logic Element (SLE) register instance only. SLE Latch instances are not triplicated by this attribute. The SLEs should be inferred by Synplify Pro.

- The syn\_radhardlevel TMR attribute applied to the SLE, D-type Flip-Flop Output Non-Inverted (DFN), D-type Latch Output Non-Inverted (DLN), and macros manually instantiated in the RTL is not triplicated.

- For syn\_radhardlevel TMR specified globally, registers associated with memory and multipliers are packed inside RAM and DSP blocks, and are not triplicated.

- Users must add syn\_radhardlevel=none, if CDC synchronizer FFs are used inside logic.

### 6.2 Summary

This application note has described the various ways to specify logic synthesized as a TMR implementation. It also shows the TMR implemented register functions in the Libero SoC v12.4 and later are spatially placed apart to improve the SEU rate further.

The examples include the correct syntax and placement in the VHDL code, along with helpful comments.

## 7. Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

| Revision | Date    | Description      |

|----------|---------|------------------|

| A        | 12/2020 | Initial Revision |

## The Microchip Website

Microchip provides online support via our website at www.microchip.com/. This website is used to make files and information easily available to customers. Some of the content available includes:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- **General Technical Support** Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- **Business of Microchip** Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

## Customer Support

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- · Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

### **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- · Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code

protection does not mean that we are guaranteeing the product is "unbreakable." Code protection is constantly

evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act.

If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue

for relief under that Act.

### Legal Notice

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUENTIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

<sup>©</sup> 2020, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-7391-6

# Quality Management System

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

| MERICAS                  | ASIA/PACIFIC          | ASIA/PACIFIC            | EUROPE                 |

|--------------------------|-----------------------|-------------------------|------------------------|

| orporate Office          | Australia - Sydney    | India - Bangalore       | Austria - Wels         |

| 355 West Chandler Blvd.  | Tel: 61-2-9868-6733   | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39   |

| handler, AZ 85224-6199   | China - Beijing       | India - New Delhi       | Fax: 43-7242-2244-393  |

| el: 480-792-7200         | Tel: 86-10-8569-7000  | Tel: 91-11-4160-8631    | Denmark - Copenhagen   |

| ax: 480-792-7277         | China - Chengdu       | India - Pune            | Tel: 45-4485-5910      |

| echnical Support:        | Tel: 86-28-8665-5511  | Tel: 91-20-4121-0141    | Fax: 45-4485-2829      |

| ww.microchip.com/support | China - Chongqing     | Japan - Osaka           | Finland - Espoo        |

| Veb Address:             | Tel: 86-23-8980-9588  | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820    |

| www.microchip.com        | China - Dongguan      | Japan - Tokyo           | France - Paris         |

| tlanta                   | Tel: 86-769-8702-9880 | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20  |

| uluth, GA                | China - Guangzhou     | Korea - Daegu           | Fax: 33-1-69-30-90-79  |

| el: 678-957-9614         | Tel: 86-20-8755-8029  | Tel: 82-53-744-4301     | Germany - Garching     |

| ax: 678-957-1455         | China - Hangzhou      | Korea - Seoul           | Tel: 49-8931-9700      |

| ustin, TX                | Tel: 86-571-8792-8115 | Tel: 82-2-554-7200      | Germany - Haan         |

| el: 512-257-3370         | China - Hong Kong SAR | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400   |

| Boston                   | Tel: 852-2943-5100    | Tel: 60-3-7651-7906     | Germany - Heilbronn    |

| Vestborough, MA          | China - Nanjing       | Malaysia - Penang       | Tel: 49-7131-72400     |

| el: 774-760-0087         | Tel: 86-25-8473-2460  | Tel: 60-4-227-8870      | Germany - Karlsruhe    |

| ax: 774-760-0088         | China - Qingdao       | Philippines - Manila    | Tel: 49-721-625370     |

| hicago                   | Tel: 86-532-8502-7355 | Tel: 63-2-634-9065      | Germany - Munich       |

| asca, IL                 | China - Shanghai      | Singapore               | Tel: 49-89-627-144-0   |

| el: 630-285-0071         | Tel: 86-21-3326-8000  | Tel: 65-6334-8870       | Fax: 49-89-627-144-44  |

| ax: 630-285-0075         | China - Shenyang      | Taiwan - Hsin Chu       | Germany - Rosenheim    |

| allas                    | Tel: 86-24-2334-2829  | Tel: 886-3-577-8366     | Tel: 49-8031-354-560   |

| ddison, TX               | China - Shenzhen      | Taiwan - Kaohsiung      | Israel - Ra'anana      |

| el: 972-818-7423         | Tel: 86-755-8864-2200 | Tel: 886-7-213-7830     | Tel: 972-9-744-7705    |

| ax: 972-818-2924         | China - Suzhou        | Taiwan - Taipei         | Italy - Milan          |

| etroit                   | Tel: 86-186-6233-1526 | Tel: 886-2-2508-8600    | Tel: 39-0331-742611    |

| lovi, MI                 | China - Wuhan         | Thailand - Bangkok      | Fax: 39-0331-466781    |

| el: 248-848-4000         | Tel: 86-27-5980-5300  | Tel: 66-2-694-1351      | Italy - Padova         |

| louston, TX              | China - Xian          | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286    |

| el: 281-894-5983         | Tel: 86-29-8833-7252  | Tel: 84-28-5448-2100    | Netherlands - Drunen   |

| idianapolis              | China - Xiamen        | 101. 04-20-0440-2100    | Tel: 31-416-690399     |

| loblesville, IN          | Tel: 86-592-2388138   |                         | Fax: 31-416-690340     |

| el: 317-773-8323         | China - Zhuhai        |                         | Norway - Trondheim     |

| ax: 317-773-5453         | Tel: 86-756-3210040   |                         | Tel: 47-72884388       |

| el: 317-536-2380         | 101.00-700-02100+0    |                         | Poland - Warsaw        |

| os Angeles               |                       |                         | Tel: 48-22-3325737     |

| lission Viejo, CA        |                       |                         | Romania - Bucharest    |

| el: 949-462-9523         |                       |                         | Tel: 40-21-407-87-50   |

| ax: 949-462-9608         |                       |                         | Spain - Madrid         |

| el: 951-273-7800         |                       |                         | Tel: 34-91-708-08-90   |

| aleigh, NC               |                       |                         | Fax: 34-91-708-08-91   |

| el: 919-844-7510         |                       |                         | Sweden - Gothenberg    |

| ew York, NY              |                       |                         | Tel: 46-31-704-60-40   |

| el: 631-435-6000         |                       |                         | Sweden - Stockholm     |

| an Jose, CA              |                       |                         | Tel: 46-8-5090-4654    |

| el: 408-735-9110         |                       |                         | UK - Wokingham         |