# HB0911 Handbook MIV\_RV32IMC v2.1

March 2020

а <u> Міскосні</u>р company

# Contents

| Revision History                                                                      | 1  |

|---------------------------------------------------------------------------------------|----|

| ,<br>1.1 Revision 1.0                                                                 |    |

|                                                                                       | 2  |

| 2 Introduction                                                                        |    |

| 2.1 Overview                                                                          |    |

| 2.2 Features.                                                                         |    |

| 2.3 Core Version                                                                      |    |

| 2.4 Supported Families                                                                |    |

| 2.5 Device Resource Utilization and Performance<br>2.5.1 Typical Resource Utilization |    |

| 2.5.1 Typical Resource Offization                                                     |    |

|                                                                                       | /  |

| 3 Functional Description                                                              | 9  |

| 3.1 MIV_RV32IMC Architecture                                                          | 9  |

| 3.2 Hart                                                                              | 10 |

| 3.3 Memory System                                                                     | 10 |

| 3.4 Interrupts                                                                        | 10 |

| 3.5 Debug Support via JTAG                                                            | 11 |

| 3.6 External Interfaces                                                               | 11 |

| 3.7 Tightly Coupled Memory                                                            |    |

| 3.8 Direct Access Port                                                                |    |

| 3.9 Clocks                                                                            |    |

| 3.10 Resets                                                                           | 11 |

| 4 Interface                                                                           | 13 |

| 4.1 Configuration Parameters                                                          |    |

| 4.2 I/O Signals                                                                       |    |

|                                                                                       |    |

| 5 Programmer's Model                                                                  |    |

| 5.1 Processor Operating States                                                        |    |

| 5.2 Reset Operation                                                                   |    |

| 5.3 Data Types                                                                        |    |

| 5.4 General Purpose Registers                                                         |    |

| 5.5 Machine Control and Status Registers                                              |    |

| 5.6 Debug Module                                                                      |    |

| 5.6.1 Debug Transport Module                                                          |    |

| 5.6.2 Debug Unit                                                                      |    |

| 5.6.3 Hart Debug Logic                                                                |    |

| 5.7 Memory Map                                                                        |    |

| 5.8 Subsystem Restrictions                                                            |    |

| 5.9 Exceptions                                                                        |    |

| 5.9.1 Vectored and Non-Vectored Interrupts                                            |    |

| 5.9.2 Nested Interrupts                                                               |    |

| 5.9.3 Available Interrupts                                                            |    |

| 5.9.4 Interrupt Handling<br>5.9.5 Vectored Interrupt Offsets and Exception Priorities |    |

| 5.9.6 OPSRV Register Interrupts                                                       |    |

| 5.9.6 OPSRV Register Interrupts                                                       |    |

| 5.10 OPSKV Register                                                                   |    |

| 5.12 ECC                                                                              |    |

| 5.12 LCC                                                                              | 40 |

| 6 Tool Flow                                                          | 42 |

|----------------------------------------------------------------------|----|

| 6.1 License                                                          |    |

| 6.1.1 RTL                                                            |    |

| 6.2 SmartDesign                                                      |    |

| 6.3 Configuring MIV_RV32IMC                                          |    |

| 6.3.1 Extension Options                                              |    |

| 6.3.2 Interface Options                                              |    |

| 6.3.3 Reset Vector Address                                           |    |

| 6.3.4 Interrupt Options                                              |    |

| 6.3.5 Tightly Coupled Memory (TCM) Options                           | 44 |

| 6.3.6 Other Options                                                  |    |

| 6.3.7 Memory Map Tab                                                 |    |

| 6.4 Debugging                                                        |    |

| 6.5 Simulation Flows                                                 |    |

| 6.6 Synthesis in Libero                                              | 47 |

| 6.7 Place-and-Route in Libero                                        |    |

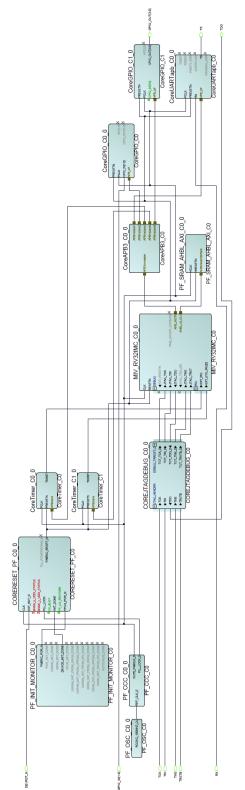

| 7 System Integration                                                 | 48 |

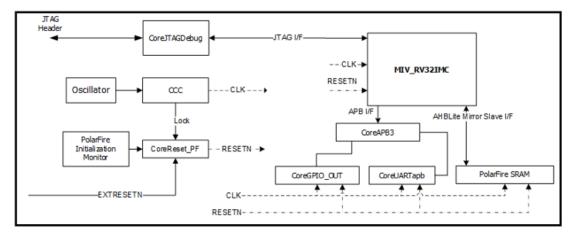

| 7.1 PolarFire Example System                                         |    |

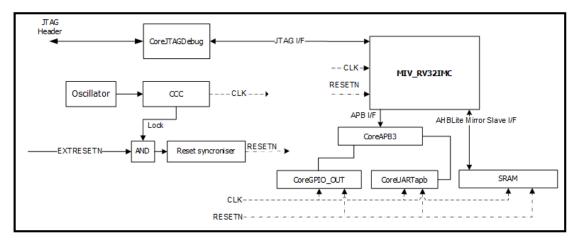

| 7.2 RTG4/SF2/IG2 Example System                                      |    |

| 7.3 Reset Synchronization                                            |    |

| 7.3.1 RESETN                                                         |    |

| 7.3.2 TRST                                                           | 50 |

| 8 Design Constraints                                                 | 51 |

| 9 SoftConsole                                                        | 52 |

| 9.1 Setting the System Clock Frequency and Peripheral Base Addresses |    |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

# 1.1 Revision 1.0

Revision 1.0 was published in March 2020. This is the first publication of the MIV\_RV32IMC IP.

# 2 Introduction

# 2.1 Overview

The MIV\_RV32IMC is a processor core designed to implement the RISC-V instruction set for use in Microchip FPGAs.

The core includes an industry standard JTAG interface to facilitate debug access. Three optional bus interfaces are available for peripheral and memory accesses. They are AHB, APB3, and AXI which can be configured as AXI3 or AXI4.

There are three dedicated interrupts as well as six optional external interrupts.

A quick start guide is available on how to create an MIV\_RV32IMC Libero design from the help menu in the core configurator.

## 2.2 Features

- Designed for low power FPGA soft-core implementations

- Supports the RISC-V standard RV32I ISA with optional Multiply and Divide (M) and Compressed (C) extensions

- Tightly coupled memory is available and size is defined by address range

- Direct Access Port (DAP) to TCM

- External, Timer and Soft Interrupts

- Up to six optional external interrupts

- Vectored and non-vectored interrupt support

- Optional on-chip debug unit with a JTAG interface

- AHBL, APB3, and AXI3/AXI4 optional external bus interfaces

## 2.3 Core Version

This Handbook applies to MIV\_RV32IMC version 2.1.

Note: The five accompanying manuals for this core are as follows:

- The RISC-V Instruction Set Manual Volume I: Unprivileged ISA

- The RISC-V Instruction Set Manual Volume II: Privileged Architecture

- RISC-V External Debug Support Version 0.13.2

- MiV\_RV32IMC Quick Start Guide

- Supplementary Resource Utilization and Performance (RUP) tables

## 2.4 Supported Families

- PolarFire<sup>®</sup>

- RTG4<sup>™</sup>

- IGLOO<sup>®</sup>2

- SmartFusion<sup>®</sup>2

# 2.5 Device Resource Utilization and Performance

The device Resource Utilization and Performance (RUP) data is listed in tables 1 to 9 for the supported device families. This data is indicative only. The overall resource utilization and performance of the core is system dependent.

The entire RUP data was generated using Libero SoC v 12.3 and Synplify v2019.03M-SP1. The **P&R LEs** signify the number of logic elements used in the synthesized component for benchmarking. This value is for reference only and varies between place-and-route runs. The following tables list the device resource utilization and performance for selected configurations of the processor.

| Family                      | Part                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | Synthesis |       | P&R LEs | Performance/MHz |  |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|-------|---------|-----------------|--|--|

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DFF | 4LUT      | Total |         |                 |  |  |

| PolarFire                   | MPF500T-1<br>FCG1152E                                                                                                                                                                                                                                                                                                                                                                                                                                | 984 | 3899      | 4883  | 4105    | 109.206         |  |  |

| RTG4                        | RTG4150L<br>FCG1657                                                                                                                                                                                                                                                                                                                                                                                                                                  | 984 | 3829      | 4813  | 4017    | 89.815          |  |  |

| SmartFusion2                | M2S150T<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                    | 982 | 3852      | 4834  | 4059    | 89.654          |  |  |

| IGLOO2                      | M2GL150<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                    | 982 | 3852      | 4834  | 4059    | 89.654          |  |  |

| Configuration<br>Parameters | RISC-V Extensions: I, Multiplier: n, AHB Master: n, AHB Mirrored I/F: n, APB Master: APB3, APB Mirrored I/F: n, AXI Master: n, AXI Mirrored I/F: n, Reset Vector Address Upper 16 bits: 0x4000, Reset Vector Address Lower 16 bits: 0x0, External IRQs: 0, MTVEC Offset: 0x34, Vectored Interrupts: n, TCM: y (4 k), TCM Direct Access Port: n, Internal MTIME: n, Internal MTIME IRQ: n, Debug: n, Register Forwarding: n, ECC: n, GPR Registers: n |     |           |       |         |                 |  |  |

#### Table 1 • RV32I APB TCM

### Table 2 • RV32I APB All Features

| Family                      | Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P&R LEs | Performance/MHz |       |      |        |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------|-------|------|--------|--|--|--|

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DFF     | 4LUT            | Total |      |        |  |  |  |

| PolarFire                   | MPF500T-1<br>FCG1152E                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2663    | 7901            | 10564 | 8471 | 67.249 |  |  |  |

| RTG4                        | RTG4150L<br>FCG1657                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2660    | 7746            | 10406 | 8433 | 56.577 |  |  |  |

| SmartFusion2                | M2S150T<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2660    | 7787            | 10447 | 8411 | 72.129 |  |  |  |

| IGLOO2                      | M2GL150<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2660    | 7787            | 10447 | 8411 | 72.129 |  |  |  |

| Configuration<br>Parameters | RISC-V Extensions: I, Multiplier: n, AHB Master: AHBLite, AHB Mirrored I/F: y, APB Master: APB3, APB Mir-<br>rored I/F: n, AXI Master: y, AXI Mirrored I/F: y, Reset Vector Address Upper 16 bits: 0x8000, Reset Vector<br>Address Lower 16 bits: 0x0, External IRQs: 6, MTVEC Offset: 0x34, Vectored Interrupts: y, TCM: y (4 k), TC-<br>M Direct Access Port: y, Internal MTIME: y, Internal MTIME IRQ: y, Debug: y, Register Forwarding: y, ECC:<br>y, GPR Registers: y |         |                 |       |      |        |  |  |  |

### Table 3 • RV32IC APB TCM

| Family                      | Part                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P&R LEs | Performance/MHz |       |      |        |  |  |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------|-------|------|--------|--|--|--|

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DFF     | 4LUT            | Total |      |        |  |  |  |

| PolarFire                   | MPF500T-1<br>FCG1152E                                                                                                                                                                                                                                                                                                                                                                                                                                            | 982     | 4165            | 5147  | 4355 | 98.678 |  |  |  |

| RTG4                        | RTG4150L<br>FCG1657                                                                                                                                                                                                                                                                                                                                                                                                                                              | 986     | 4230            | 5216  | 4428 | 83.417 |  |  |  |

| SmartFusion2                | M2S150T<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                                | 987     | 4240            | 5227  | 4446 | 95.822 |  |  |  |

| IGLOO2                      | M2GL150<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                                | 987     | 4240            | 5227  | 4446 | 95.822 |  |  |  |

| Configuration<br>Parameters | RISC-V Extensions: IC, Multiplier: n, AHB Master: n, AHB Mirrored I/F: n, APB Master: APB3, APB Mirrored I/F: n, AXI Master: n, AXI Mirrored I/F: n, Reset Vector Address Upper 16 bits: 0x4000, Reset Vector A-<br>ddress Lower 16 bits: 0x0, External IRQs: 0, MTVEC Offset: 0x34, Vectored Interrupts: n, TCM: y (4 k),<br>TCM Direct Access Port: n, Internal MTIME: n, Internal MTIME IRQ: n, Debug: n, Register Forwarding:<br>n, ECC: n, GPR Registers: n |         |                 |       |      |        |  |  |  |

### Table 4 • RV32IC APB All Features

| Family                      | Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | is   | P&R LEs | Performance/MHz |      |        |  |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-----------------|------|--------|--|--|

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DFF  | 4LUT    | Total           |      |        |  |  |

| PolarFire                   | MPF500T-1<br>FCG1152E                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2666 | 8236    | 10902           | 8800 | 68.923 |  |  |

| RTG4                        | RTG4150L<br>FCG1657                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2670 | 8104    | 10774           | 8756 | 55.941 |  |  |

| SmartFusion2                | M2S150T<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2661 | 8200    | 10861           | 8849 | 70.957 |  |  |

| IGLOO2                      | M2GL150<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2661 | 8200    | 10861           | 8849 | 70.957 |  |  |

| Configuration<br>Parameters | RISC-V Extensions: IC, Multiplier: n, AHB Master: AHBLite, AHB Mirrored I/F: y, APB Master: APB3, APB<br>Mirrored I/F: n, AXI Master: y, AXI Mirrored I/F: y, Reset Vector Address Upper 16 bits: 0x8000, Reset<br>Vector Address Lower 16 bits: 0x0, External IRQs: 6, MTVEC Offset: 0x34, Vectored Interrupts: y, TCM:<br>y (4k), TCM Direct Access Port: y, Internal MTIME: y, Internal MTIME IRQ: y, Debug: y, Register Forwarding:<br>y, ECC: y, GPR Registers: y |      |         |                 |      |        |  |  |

### Table 5 • RV32IM (MACC-Pipelined) APB TCM

| Family    | Part                  | Synthesis      |      |      | P&R LEs | Performance/MHz |

|-----------|-----------------------|----------------|------|------|---------|-----------------|

|           |                       | DFF 4LUT Total |      |      |         |                 |

| PolarFire | MPF500T-1<br>FCG1152E | 1120           | 4442 | 5562 | 4802    | 87.093          |

| RTG4      | RTG4150L              | 1127           | 4529 | 5656 | 4879    | 83.696          |

| Family                      | Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | Synthesis | 5     | P&R LEs | Performance/MHz |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|-------|---------|-----------------|--|--|--|

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DFF  | 4LUT      | Total |         |                 |  |  |  |

|                             | FCG1657                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |           |       |         |                 |  |  |  |

| SmartFusion2                | M2S150T<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1122 | 4568      | 5690  | 4918    | 88.708          |  |  |  |

| IGLOO2                      | M2GL150<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1122 | 4568      | 5690  | 4918    | 88.708          |  |  |  |

| Configuration<br>Parameters | RISC-V Extensions: IM, Multiplier: MACC-Pipelined, AHB Master: n, AHB Mirrored I/F: n, APB Master: A-<br>PB3, APB Mirrored I/F: n, AXI Master: n, AXI Mirrored I/F: n, Reset Vector Address Upper 16 bits: 0x40<br>00, Reset Vector Address Lower 16 bits: 0x0, External IRQs: 0, MTVEC Offset: 0x34, Vectored Interrupts:<br>n, TCM: y (4k), TCM Direct Access Port: n, Internal MTIME: n, Internal MTIME IRQ: n, Debug: n, Register<br>Forwarding: n, ECC: n, GPR Registers: n |      |           |       |         |                 |  |  |  |

### Table 6 • RV32IM (MACC-Pipelined) All Features

| Family                      | Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Part Synthesis |      |       |      |        |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|-------|------|--------|--|

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DFF            | 4LUT | Total |      |        |  |

| PolarFire                   | MPF500T-1<br>FCG1152E                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2808           | 8372 | 11180 | 9061 | 67.522 |  |

| RTG4                        | RTG4150L<br>FCG1657                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2798           | 8374 | 11172 | 9162 | 58.224 |  |

| SmartFusion2                | M2S150T<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2798           | 8450 | 11248 | 9228 | 71.235 |  |

| IGLOO2                      | M2GL150<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2798           | 8450 | 11248 | 9228 | 71.235 |  |

| Configuration<br>Parameters | RISC-V Extensions: IM, Multiplier: MACC-Pipelined, AHB Master: y, AHB Mirrored I/F: y, APB Master: AP-<br>B3, APB Mirrored I/F: n, AXI Master: y, AXI Mirrored I/F: y, Reset Vector Address Upper 16 bits: 0x8000,<br>Reset Vector Address Lower 16 bits: 0x0, External IRQs: 6, MTVEC Offset: 0x34, Vectored Interrupts: y,<br>TCM: y (4k), TCM Direct Access Port: y, Internal MTIME: y, Internal MTIME IRQ: y, Debug: y, Register For-<br>warding: y, ECC: y, GPR Registers: y |                |      |       |      |        |  |

### Table 7 • RV32IMC (Fabric) APB TCM

| Family       | Part                  | P&R LEs | Performance/MHz |       |      |        |

|--------------|-----------------------|---------|-----------------|-------|------|--------|

|              |                       | DFF     | 4LUT            | Total |      |        |

| PolarFire    | MPF500T-1<br>FCG1152E | 1157    | 5170            | 6327  | 5374 | 95.841 |

| RTG4         | RTG4150L<br>FCG1657   | 1159    | 5197            | 6356  | 5421 | 81.907 |

| SmartFusion2 | M2S150T<br>FC1152     | 1155    | 5191            | 6346  | 5403 | 86.498 |

| Family                      | Part                                                                                                                                                                       |                                                                    | Synthesis                     | 5                                 | P&R LEs                          | Performance/MHz                              |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------|-----------------------------------|----------------------------------|----------------------------------------------|

|                             |                                                                                                                                                                            | DFF                                                                | 4LUT                          | Total                             |                                  |                                              |

| IGLOO2                      | M2GL150<br>FC1152                                                                                                                                                          | 1155                                                               | 5191                          | 6346                              | 5403                             | 86.498                                       |

| Configuration<br>Parameters | RISC-V Extensions: IMC, Multip<br>B Mirrored I/F: n, AXI Master: n<br>Vector Address Lower 16 bits:<br>y (4k), TCM Direct Access Port:<br>ing: n, ECC: n, GPR Registers: n | n, <b>AXI Mirro</b><br>0x0, <b>Externa</b><br>n, <b>Internal N</b> | red I/F: n, R<br>I IRQs: 0, N | eset Vector Ad<br>ITVEC Offset: ( | dress Upper 10<br>0x34, Vectored | 6 bits: 0x4000, Reset<br>Interrupts: n, TCM: |

### Table 8 • RV32IMC (Fabric) All Features

| Family                      | Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | Synthes | is    | P&R LEs | Performance/MHz |  |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-------|---------|-----------------|--|--|--|

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DFF  | 4LUT    | Total |         |                 |  |  |  |

| PolarFire                   | MPF500T-1<br>FCG1152E                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2835 | 9265    | 12100 | 9803    | 64.943          |  |  |  |

| RTG4                        | RTG4150L<br>FCG1657                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2883 | 9203    | 12036 | 9845    | 57.840          |  |  |  |

| SmartFusion2                | M2S150T<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2883 | 9251    | 12084 | 9908    | 69.238          |  |  |  |

| IGLOO2                      | M2GL150<br>FC1152                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2883 | 9251    | 12084 | 9908    | 69.238          |  |  |  |

| Configuration<br>Parameters | RISC-V Extensions: IMC, Multiplier: Fabric, AHB Master: y, AHB Mirrored I/F: y, APB Master: APB3, APB<br>Mirrored I/F: n, AXI Master: y, AXI Mirrored I/F: y, Reset Vector Address Upper 16 bits: 0x8000, Reset V-<br>ector Address Lower 16 bits: 0x0, External IRQs: 6, MTVEC Offset: 0x34, Vectored Interrupts: y, TCM: y<br>(4k), TCM Direct Access Port: y, Internal MTIME: y, Internal MTIME IRQ: y, Debug: y, Register Forwarding:<br>y, ECC: y, GPR Registers: y |      |         |       |         |                 |  |  |  |

For more information, see the Supplementary RUP Tables manual, which is included with the core.

## 2.5.1 Typical Resource Utilization

The following table lists a breakdown of average resource usage for core options across the supported families.

### Table 9 • Option Resources

| Feature                | Parts                                                                     | Synthesis |           |            |  |

|------------------------|---------------------------------------------------------------------------|-----------|-----------|------------|--|

|                        |                                                                           | Avg. DFF  | Avg. 4LUT | Avg. Total |  |

| AHBL                   | MPF500T-1FCG1152E<br>RTG4150L FCG1657<br>M2S150T FC1152<br>M2GL150 FC1152 | 108       | 102       | 210        |  |

| АРВ                    |                                                                           | 115       | 144       | 259        |  |

| ΑΧΙ                    |                                                                           | 514       | 492       | 1006       |  |

| Ext_sys_interrupts (6) |                                                                           | 6         | 61        | 67         |  |

| Feature             | Parts | Synthesis |           |            |  |

|---------------------|-------|-----------|-----------|------------|--|

|                     |       | Avg. DFF  | Avg. 4LUT | Avg. Total |  |

| Vectored interrupts |       | 35        | 154       | 189        |  |

| ТСМ (4 k)           |       | 62        | 372       | 434        |  |

| DAP                 |       | 0         | 84        | 84         |  |

| Mtime and Mtime irq |       | 160       | 425       | 585        |  |

| Debug               |       | 564       | 1756      | 2320       |  |

| ECC                 |       | 12        | 407       | 429        |  |

| GPR registers       |       | 989       | 1544      | 2533       |  |

| Register forwarding |       | 5         | 289       | 294        |  |

## 2.5.2 Benchmarks

### Table 10 • Coremark Results

| Benchmarks                | Memory<br>Location | RV32 | Multiplier | Reg<br>Fwd | Reg<br>GPRs | ECC | Coremark/MHz |

|---------------------------|--------------------|------|------------|------------|-------------|-----|--------------|

|                           | тсм                | IMC  | MACC       | 1          | 1           | 0   | 2.767        |

| <u>ل</u>                  | тсм                | ІМС  | MACC       | 0          | 1           | 0   | 2.533        |

| ision benc<br>marks       | тсм                | IM   | MACC       | 0          | 0           | 0   | 1.567        |

| Extension bench-<br>marks | тсм                | IM   | MACC pipe  | 0          | 0           | 0   | 1.567        |

| Ш<br>Ш                    | тсм                | ІМС  | MACC       | 0          | 0           | 0   | 1.567        |

|                           | тсм                | IMC  | MACC       | 1          | 0           | 0   | 1.567        |

|                           | тсм                | IMC  | MACC pipe  | 0          | 0           | 0   | 1.5          |

|                           | тсм                | IM   | Fabric     | 0          | 0           | 0   | 1.067        |

|                           | тсм                | I    | n/a        | 1          | 1           | 0   | 1.067        |

|                           | тсм                | ІМС  | Fabric     | 0          | 0           | 0   | 1.033        |

|                           | тсм                | I    | n/a        | 0          | 1           | 0   | 0.967        |

|                           | тсм                | I    | n/a        | 0          | 0           | 0   | 0.533        |

|                           | тсм                | IC   | n/a        | 0          | 0           | 0   | 0.533        |

|                           | тсм                | 1    | n/a        | 0          | 0           | 1   | 0.533        |

|                           | тсм                | I    | n/a        | 1          | 0           | 0   | 0.533        |

| Benchmarks                | Memory<br>Location | RV32 | Multiplier | Reg<br>Fwd | Reg<br>GPRs | ECC | Coremark/MHz |

|---------------------------|--------------------|------|------------|------------|-------------|-----|--------------|

|                           | АНВ                | ІМС  | MACC       | 0          | 0           | 0   | 0.467        |

| ÷                         | АНВ                | IM   | MACC       | 0          | 0           | 0   | 0.433        |

| Interface bench-<br>marks | АНВ                | IC   | n/a        | 0          | 0           | 0   | 0.2          |

| nterfac                   | АНВ                | 1    | n/a        | 0          | 1           | 0   | 0.2          |

| -                         | AHB                | 1    | n/a        | 1          | 1           | 0   | 0.2          |

|                           | AHB                | I    | n/a        | 0          | 0           | 0   | 0.167        |

|                           | AHB                | I    | n/a        | 1          | 0           | 0   | 0.167        |

|                           | ΑΧΙ                | IM   | MACC       | 0          | 0           | 0   | 0.4          |

|                           | AXI                | IMC  | MACC       | 0          | 0           | 0   | 0.4          |

|                           | AXI                | IC   | n/a        | 0          | 0           | 0   | 0.167        |

|                           | ΑΧΙ                | 1    | n/a        | 0          | 1           | 0   | 0.167        |

|                           | AXI                | I    | n/a        | 0          | 0           | 0   | 0.133        |

|                           | AXI                | I    | n/a        | 1          | 0           | 0   | 0.133        |

# **3** Functional Description

# 3.1 MIV\_RV32IMC Architecture

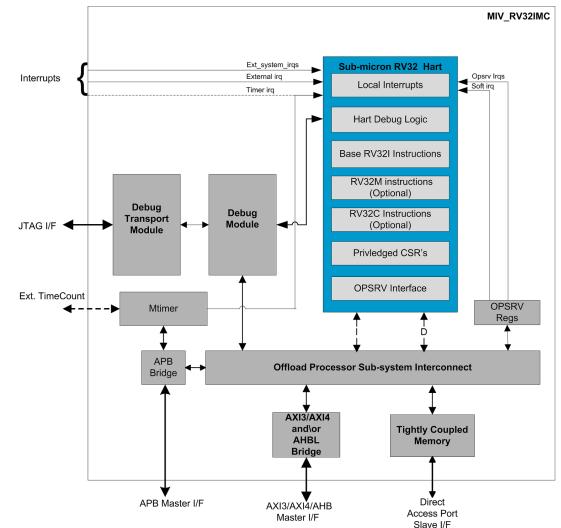

The core architecture comprises of a RV32IMC four stage pipelined processor unit integrated with an Offload Processor Subsystem for RISC-V (OPSRV). The OPSRV consists of a system interconnect with a JTAG Debug Module, System MTimer, Tightly Coupled Memory (TCM) with a Direct Access Port (DAP- Slave APB), AHB\AXI\APB master interfaces, and OPSRV registers. The following figure shows the block level architecture of MIV\_RV32IMC device.

### Figure 1 • MIV\_RV32IMC Block Diagram

The following table lists the key features of the core.

| Table 11 • MIV | <b>RV32IMC Architecture features</b> |

|----------------|--------------------------------------|

|----------------|--------------------------------------|

| Feature                            | Value             | Units | Notes                                                                                                                                 |

|------------------------------------|-------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------|

| ISA support                        | RV32IMC           |       | Base RV32I, optional multiply and divide and optional compressed extensions                                                           |

| Harts                              | 1                 |       | Submicron RV32IMC                                                                                                                     |

| Reset vector                       | Configurable      |       | Word aligned address 0x1000_0000 and above available                                                                                  |

| Interrupts                         | 13                |       | External, Software and Timer interrupts, six optional ex-<br>ternal interrupts, and ECC interrupts. Vectored interrupts<br>supported. |

| Timers/Counters                    | 1                 |       | An MTIME block is available to generate a time value and periodic interrupts                                                          |

| Bus interfaces                     | AHB/AXI3/AXI4/APB |       | Optional AHB, AXI3/AXI4, and APB                                                                                                      |

| JTAG debug transport address width | 7                 | Bits  |                                                                                                                                       |

| Local memories                     | 1                 |       | Width of TCM start and end address determines the size of the local memory                                                            |

| Local memory access                | 1                 |       | Optional Direct Access Port (DAP) provides slave APB access to TCM                                                                    |

## 3.2 Hart

The MIV\_RV32IMC hart is based on the RISC-V Instruction Set Architecture (ISA). The hart supports the RISC-V standard RV32 Integer (I), Multiply (M), and Compressed (C) ISA. It also supports the machine-mode privileged architecture and debug mode.

The hart is a four stage pipelined submicron processor, which has been designed to be highly configurable for use in Microchip FPGAs. It is designed to be used as a standalone or auxiliary processor within FPGA designs. The hart contains the base RISC-V Integer ISA extension. Optionally, the RISC-V M ISA extension adds hardware multiply and divide instructions. Optionally, the RISC-V C ISA extension adds the compressed instruction set.

## 3.3 Memory System

The core is non-cached. The Tightly Coupled Memory (TCM) is available as for instruction and data storage. A range of system peripherals are accessed across AXI (AXI4/AXI3), AHB, and APB bus interfaces.

## 3.4 Interrupts

The RISC-V external interrupt is available for use as a top-level input to the core. Six optional external interrupts can also be enabled at the top level for use as external interrupts. The RISC-V software interrupt is available and can be accessed through the OPSRV register. The timer interrupt can be exposed to the top level or connected internally to a compare register that can be accessed through software, and generates interrupts at a fixed interval. There is an OPSRV register interrupt available that signals TCM, ECC, or AXI write errors. Interrupts can be configured in vectored or non-vectored mode when the core is being configured to allow for a defined vector for each interrupt, if required. Interrupts are positive edge triggered.

# 3.5 Debug Support via JTAG

The core includes support for an external debugger using a JTAG port. This v0.13.2 debug implementation is abstract command based and uses system bus access to write to memory. The core does not support the use of a program buffer. The following debug features are provided:

- Hart can be halted and resumed

- All hart registers (including CSRs) can be read/written

- Memory can be accessed

- Binary files can be downloaded to memory

- Hart can be debugged from the very first instruction executed

- Debug can perform single-step operations and can execute one instruction at a time

- A RISC-V hart can be halted when a software breakpoint instruction is executed

# 3.6 External Interfaces

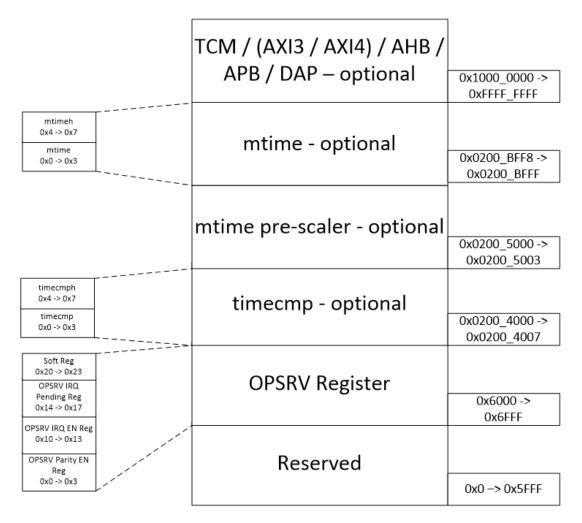

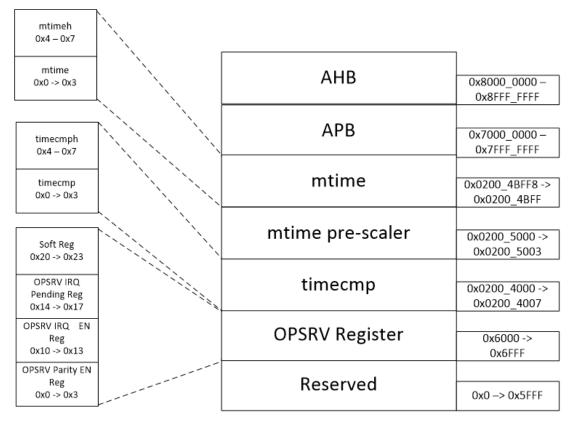

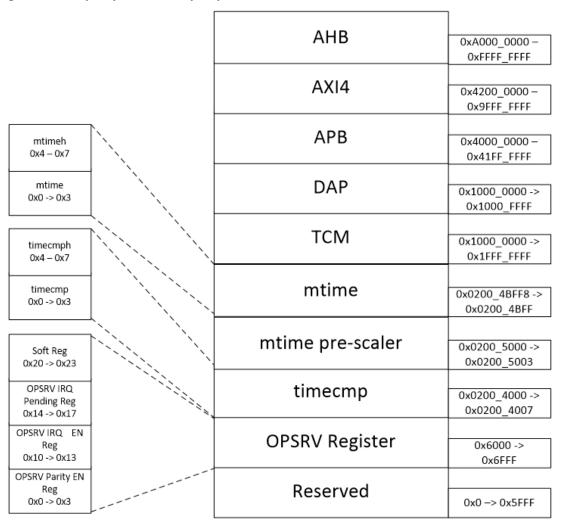

The core supports three optional external interfaces: AHB, APB, and AXI (AXI3/AXI4). Each interface has its own address space mapped at compile time. The address spaces may not overlap.

The core can boot from a word aligned address range, within the configurator specified address space, by setting the RESET\_VECTOR and modifying the linker scripts for the firmware project. This address can be half word aligned, if C extension is used.

# 3.7 Tightly Coupled Memory

The core supports Tightly Coupled Memory (TCM). The size of the memory is defined by the start and end address of the TCM. This memory can be booted by setting the RESET\_VECTOR to the address of the TCM. The TCM can also be initialized at power on or programmed through the DAP interface.

# 3.8 Direct Access Port

A Direct Access Port is available over an APB slave interface. This allows reading and writing to the TCM from an external source before the core is brought out of reset. It is recommended that the address widths for the TCM and the DAP are of the same size to avoid memory read/write violations.

# 3.9 Clocks

The system clock frequency should be chosen to meet design timing requirements with clock constraints applied. The tables in *Device Resource Utilization and Performance* section list the upper clock frequency obtained for a specified device from each supported FPGA family, whilst meeting timing requirements for the configurations defined. Sequential logic within the core is driven on the positive clock edge.

When the debug option is enabled, the JTAG debug signals are made available at the top level. The JTAG has a clock signal TCK whose characteristics are determined by the connected JTAG debugger. It is advised that the applied TCK frequency should not be greater than one-seventh of the system clock frequency and remain within the maximum frequency permitted for the JTAG probe in use. The TCK should have clock constraints applied. For more information, see the *Design Constraints* section.

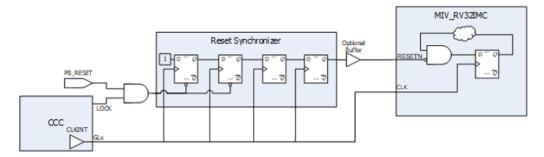

# 3.10 Resets

The RESETN is an active low hard reset, which resets everything within the core. An external reset synchronizer is required (for more information, see the *Reset Synchronization* section). In many cases, the synchronizer is integrated within a family specific reset core, for example, Core\_Reset\_PF.

The EXT\_RESETN is an active low reset output. This is fed through from the RESETN and also driven from the debug module during a debug session to allow a system reset through the debugger.

There is an internal CPU Soft Reset feature accessible through software. For more information, see the *Table 46* • *opsrv\_soft\_reg (0x6020)* table in the OPSRV Register section.

The TRST is an active high reset signal for the JTAG Test Access Port (TAP).

# 4 Interface

# 4.1 Configuration Parameters

The following table lists the parameters (Verilog) or generics (VHDL) for configuring the RTL code of the core.

| Name                | Range         | Default Value | Description                                                                                                                                                  |

|---------------------|---------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET_VECTOR_ADDR_1 | 0x1000-0xFFFF | 0x8000        | This is the address the processor will start executing from after a reset. This address is byte aligned.                                                     |

| RESET_VECTOR_ADDR_0 | 0x0000-0xFFFC | 0x0           |                                                                                                                                                              |

| DEBUGGER            | 0 or 1        | 1             | JTAG Debugger<br>0: Disable<br>1: Enabled                                                                                                                    |

| AXI_MASTER_TYPE     | 0 to 2        | 0             | AXI Master Type<br>0: None<br>1: AXI3<br>2: AXI4                                                                                                             |

| AXI_SLAVE_MIRROR    | 0 or 1        | 0             | AXI Slave Mirror<br>0: None<br>1: AXI Slave Mirror<br>Note: This parameter is only used when an AXI Master is selected                                       |

| AXI_START_ADDR_1    | 0x1000-0xFFFF | 0x6000        | This is the AXI start address. AXI_START_ADDR_1 and A-XI_START_ADDR_0 represent the upper and lower 16 bits                                                  |

| AXI_START_ADDR_0    | 0x0000-0xFFFF | 0x0           | of the address respectfully.                                                                                                                                 |

| AXI_END_ADDR_1      | 0x1000-0xFFFF | 0x6FFF        | This is the AXI end address. AXI_END_ADDR_1 and AX<br>END_ADDR_0 represent the upper and lower 16 bits of th                                                 |

| AXI_END_ADDR_0      | 0xFFFF-0xFFFC | OxFFFF        | address respectfully.                                                                                                                                        |

| AHB_MASTER_TYPE     | 0 or 1        | 1             | AHB Master Type<br>0: None<br>1: AHB-Lite                                                                                                                    |

| AHB_SLAVE_MIRROR    | 0 or 1        | 0             | <ul> <li>AHB Slave Mirror</li> <li>0: None</li> <li>1: AXI Slave Mirror</li> <li>Note: This parameter is only used when an AHB Master is selected</li> </ul> |

| AHB_START_ADDR_1    | 0x1000-0xFFFF | 0x8000        | This is the AHB start address. AHB_START_ADDR_1 and AHB_START_ADDR_0 represent the upper and lower 16                                                        |

| AHB_START_ADDR_0    | 0x0000-0xFFFF | 0x0           | bits of the address respectfully.                                                                                                                            |

| AHB_END_ADDR_1      | 0x1000-0xFFFF | 0x8FFF        | This is the AHB end address. AHB_END_ADDR_1 and AHB_<br>END_ADDR_0 represent the upper and lower 16 bits of the                                              |

| AHB_END_ADDR_0      | 0xFFFF-0xFFFC | OxFFFF        | address respectively.                                                                                                                                        |

| Name                | Range         | Default Value | Description                                                                                                                   |  |

|---------------------|---------------|---------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| APB_MASTER_TYPE     | 0 or 1        | 1             | APB Master Type<br>0: None<br>1: APB3                                                                                         |  |

| APB_SLAVE_MIRROR    | 0 or 1        | 0             | AHB Slave Mirror<br>0: None<br>1: AXI Slave Mirror<br><b>Note:</b> This parameter is only used when an AHB Master is selected |  |

| APB_START_ADDR_1    | 0x1000-0xFFFF | 0x7000        | This is the APB start address. APB_START_ADDR_1 and APB_START_ADDR_0 represent the upper and lower 16                         |  |

| APB_START_ADDR_0    | 0x0000-0xFFFF | 0x0           | bits of the address respectfully.                                                                                             |  |

| APB_END_ADDR_1      | 0x1000-0xFFFF | 0x7FFF        | This is the APB end address. APB_END_ADDR_1 and APB_<br>END_ADDR_0 represent the upper and lower 16 bits of the               |  |

| APB_END_ADDR_0      | 0xFFFF-0xFFFC | OxFFFF        | address respectfully.                                                                                                         |  |

| TCM_PRESENT         | 0 or 1        | 0             | TCM Present<br>0: Disabled<br>1: Enabled                                                                                      |  |

| TCM_START_ADDR_1    | 0x1000-0xFFFF | 0x4000        | This is the TCM start address. TCM_START_ADDR_1 and TCM START ADDR 0 represent the upper and lower 16                         |  |

| TCM_START_ADDR_0    | 0x0000-0xFFFF | 0x0           | bits of the address respectfully.                                                                                             |  |

| TCM_END_ADDR_1      | 0x1000-0xFFFF | 0x4000        | This is the TCM end address. TCM_END_ADDR_1 and TC<br>END ADDR 0 represent the upper and lower 16 bits of th                  |  |

| TCM_END_ADDR_0      | 0xFFFF-0xFFFC | 0x4000        | address respectfully.                                                                                                         |  |

| TCM_DAP_PRESENT     | 0 or 1        | 0             | TCM DAP Present<br>0: Disabled<br>1: Enabled                                                                                  |  |

| DAP_START_ADDR_1    | 0x1000-0xFFFF | 0x4000        | This is the TCM DAP start address. DAP_START_ADDR_1<br>and DAP START ADDR 0 represent the upper and lower                     |  |

| DAP_START_ADDR_0    | 0x0000-0xFFFF | 0x0           | 16 bits of the address respectfully.                                                                                          |  |

| DAP_END_ADDR_1      | 0x1000-0xFFFF | 0x4000        | This is the TCM DAP end address. DAP_END_ADDR_1 and DAP_END_ADDR_0 represent the upper and lower 16 bits                      |  |

| DAP_END_ADDR_0      | 0xFFFF-0xFFFC | 0x4000        | of the address respectfully.                                                                                                  |  |

| GEN_DECODE_RV32     | 0 to 3        | 3             | RISCV ISA Extension Select<br>0: I<br>1: IM<br>2: IC<br>3: IMC                                                                |  |

| GEN_MUL_TYPE        | 0 to 2        | 0             | Multiplier Type<br>0: Fabric<br>1: MACC (Non-Pipelined)<br>2: MACC (Pipelined)                                                |  |

| VECTORED_INTERRUPTS | 0 or 1        | 1             | Vectored Interrupts<br>0: Disabled                                                                                            |  |

| Name               | Range         | Default Value | Description                                                                                                                                                                     |

|--------------------|---------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |               |               | 1: Enabled                                                                                                                                                                      |

| MTVEC_OFFSET       | 0x0 to 0xFFFF | 0x34          | MTVEC Offset as defined in the RISC-V HAL (currently 0x100).                                                                                                                    |

| NUM_EXT_IRQS       | 0 to 6        | 6             | Number of external interrupts                                                                                                                                                   |

| FWD_REGS           | 0 or 1        | 0             | Forwarding Registers<br>0: Disabled<br>1: Enabled                                                                                                                               |

| ECC_ENABLE         | 0 or 1        | 0             | ECC<br>0: Disabled<br>1: Enabled                                                                                                                                                |

| INTERNAL_MTIME     | 0 or 1        | 1             | Internal MTIME<br>0: Disabled<br>1: Enabled                                                                                                                                     |

| MTIME_PRESCALER    | 0 to 65535    | 100           | The MTIME_PRESCALER integer value divided by the CLK frequency derives an MTIME time base given by the equation:<br>$MTIME \text{ timebase} = \frac{MTIME_PRESCALER}{CLK (Hz)}$ |

| INTERNAL_MTIME_IRQ | 0 or 1        | 1             | Internal MTIME<br>0: Disabled<br>1: Enabled                                                                                                                                     |

| GPR_REGS           | 0 or 1        | 0             | GPR Registers<br>0: Disabled<br>1: Enabled                                                                                                                                      |

# 4.2 I/O Signals

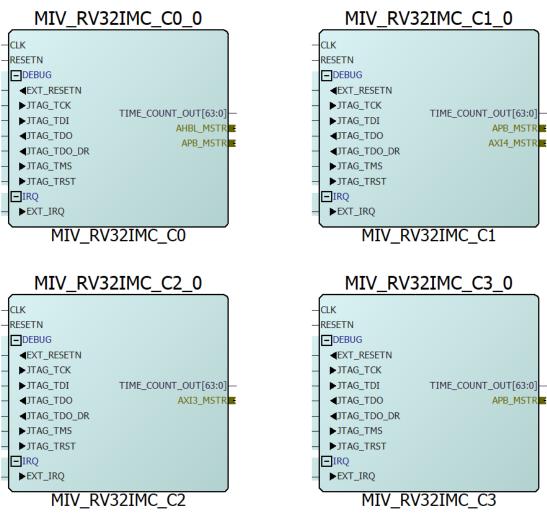

The following figure shows all the I/O signals for the core.

### Figure 2 • MIV\_RV32IMC Full I/O View

| CLK                    |            |

|------------------------|------------|

| -RESETN                |            |

| DAP_APB_SLV            |            |

| -DEBUG                 |            |

| — ▶JTAG_TCK            |            |

| → JTAG_TDI             |            |

| – ◀JTAG_TDO            | EXT_RESETN |

|                        | AXI3_MSTR  |

| — ▶JTAG_TMS            | AXI4_MSTR  |

| — ▶JTAG_TRST           | AHBL_MSTR  |

| ACCESS                 | APB_MSTR   |

| TCM_CPU_ACCESS_DISABLE | AXI3_M_SLV |

| TCM_DAP_ACCESS_DISABLE | AXI4_M_SLV |

| - IRQ                  | AHBL_M_SLV |

| – ►EXT_IRQ             | APB_M_SLV  |

| EXT_SYS_IRQ[5:0]       |            |

| — ► TMR_IRQ            |            |

| -SYS_TIMER             |            |

| TIME_COUNT_IN[63:0]    |            |

| TIME_COUNT_OUT[63:0]   |            |

|                        |            |

The following table lists the MIV\_RV32IMC I/O signal description.

### Table 13 • MIV\_RV32IMC I/O Signal Description

| Port Name              | Width | Direction | Description                                                                                                                                                                        |

|------------------------|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Global Signals         |       |           |                                                                                                                                                                                    |

| CLK                    | 1     | In        | System clock. All other I/Os are synchronous to this clock.                                                                                                                        |

| RESETN                 | 1     | In        | Synchronized reset signal. This signal is active low.                                                                                                                              |

| EXT_RESETN             | 1     | Out       | External system reset, active low. Driven by RESETN and Debugger system reset (debug mode).                                                                                        |

| JTAG Interface Signals |       |           |                                                                                                                                                                                    |

| JTAG_TDI               | 1     | In        | Test Data In (TDI). This signal is used by the JTAG device for downloading and debugging programs. Sampled on the rising edge of TCK.                                              |

| JTAG_TCK               | 1     | In        | Test Clock (TCK). This signal is used by the JTAG device for downloading and debugging programs.                                                                                   |

| JTAG_TMS               | 1     | In        | Test Mode Select (TMS). This signal is used by the JTAG device when<br>downloading and debugging programs. It is sampled on the rising edge<br>of TCK to determine the next state. |

| Port Name              | Width | Direction | Description                                                                                                                                                                              |  |  |  |  |  |

|------------------------|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| JTAG_TRST              | 1     | In        | Test Reset (TRST). This is an optional signal used to reset the TAP con-<br>trollers state machine. This signal is active high.                                                          |  |  |  |  |  |

| JTAG_TDO               | 1     | Out       | Test Data Out (TDO). This signal is the data, which is shifted out of the device during debugging. It is valid on FALLING/RISING edge of TCK.                                            |  |  |  |  |  |

| JTAG_TDO_DR            | 1     | Out       | Drive Test Data Out (DRV_TDO). This signal is used to drive a tri-state buffer.                                                                                                          |  |  |  |  |  |

| Interrupt Signals      |       |           |                                                                                                                                                                                          |  |  |  |  |  |

| EXT_IRQ                | 1     | In        | External interrupt from peripheral source. An active high level based in-<br>terrupt signal. Tie this input low if unused.                                                               |  |  |  |  |  |

| EXT_SYS_IRQ            | 6     | In        | Optional External System Interrupts. This signal is active high. Tie any unused inputs low.                                                                                              |  |  |  |  |  |

| TMR_IRQ                | 1     | In        | A Timer interrupt input is exposed when the internal MTIME IRQ param-<br>eter is not selected in the GUI. This in an active high level based interrupt.<br>Tie this input low if unused. |  |  |  |  |  |

| System Time Signals    |       |           |                                                                                                                                                                                          |  |  |  |  |  |

| TIME_COUNT_IN          | 64    | In        | External system timer count                                                                                                                                                              |  |  |  |  |  |

| TIME_COUNT_OUT         | 64    | Out       | Internal system timer count                                                                                                                                                              |  |  |  |  |  |

| TCM Access Signals     |       |           | ·                                                                                                                                                                                        |  |  |  |  |  |

| TCM_CPU_ACCESS_DISABLE | 1     | In        | When asserted, CPU access to the TCM is disabled.                                                                                                                                        |  |  |  |  |  |

| TCM_DAP_ACCESS_DISABLE | 1     | In        | When asserted, DAP access to the TCM is disabled.                                                                                                                                        |  |  |  |  |  |

| APB Master Interface   |       |           |                                                                                                                                                                                          |  |  |  |  |  |

| APB_MSTR_PADDR         | 32    | Out       | APB Master Interface. The address range is 0x1000_0000 to 0xFFFF_FFF-<br>F. This interface can also be configured as a mirrored slave through the                                        |  |  |  |  |  |

| APB_MSTR_PSEL          | 1     | Out       | GUI.                                                                                                                                                                                     |  |  |  |  |  |

| APB_MSTR_PENABLE       | 1     | Out       |                                                                                                                                                                                          |  |  |  |  |  |

| APB_MSTR_PWRITE        | 1     | Out       |                                                                                                                                                                                          |  |  |  |  |  |

| APB_MSTR_PRDATA        | 32    | In        |                                                                                                                                                                                          |  |  |  |  |  |

| APB_MSTR_PWDATA        | 32    | Out       |                                                                                                                                                                                          |  |  |  |  |  |

| APB_MSTR_PREADY        | 1     | In        |                                                                                                                                                                                          |  |  |  |  |  |

| APB_MSTR_PSLVERR       | 1     | In        |                                                                                                                                                                                          |  |  |  |  |  |

| AHB Master Interface   |       |           |                                                                                                                                                                                          |  |  |  |  |  |

| AHB_MSTR_HMASTLOCK     | 1     | Out       | AHB Master Interface. The address range is 0x1000_0000 to 0xFFFF_FFF-<br>F. This interface can also be configured as a mirrored slave through the                                        |  |  |  |  |  |

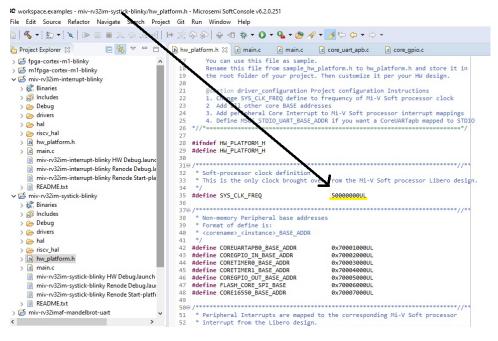

| AHB_MSTR_ HTRANS       | 2     | Out       | GUI.                                                                                                                                                                                     |  |  |  |  |  |