## Libero SoC v12.6 Release Notes

### Introduction

The Libero® system on chip (SoC) v12.6 unified design suite is Microchip's flagship FPGA software for designing with Microchip's latest power efficient flash FPGAs, SoC FPGAs, and rad-tolerant FPGAs. The suite integrates industry-standard Synopsys Synplify Pro® synthesis and Mentor Graphics ModelSim® simulation with best-in-class constraints management, debug capabilities, and secure production programming support.

Use Libero SoC v12.6 for designing with Microchip's RTG4<sup>™</sup> Rad-Tolerant FPGAs, SmartFusion®2 and IGLOO® 2 SoC FPGAs, PolarFire® FPGAs, and PolarFire SoC FPGAs.

To design with Microchip's older Flash FPGA families, use Libero SoC v11.9 and subsequent service packs.

To access datasheets, silicon user guides, tutorials, and application notes, visit <a href="www.microsemi.com">www.microsemi.com</a>, navigate to the relevant product family page, and click the **Documentation** tab. Development Kits & Boards are listed in the **Design Resources** tab.

**Note:** Libero SoC v12.6 does not support Classic Constraint Flow. IGLOO2, SmartFusion2, and RTG4 projects using the "Classic" flow cannot be opened in this release. For details about how to migrate Classic Constraint Flow projects to the Enhanced Constraint Flow, refer to Migrating an Existing Project Created with Classic Constraint Flow to Enhanced Constraint Flow.

#### **Related Release Notes**

In addition to these release notes, you may find the information in the following release notes helpful.

PolarFire SoC MSS Configurator v2.0 Release Notes

# **Table of Contents**

| ntr                                     | oductio | n            |             |                                                                            | 1  |

|-----------------------------------------|---------|--------------|-------------|----------------------------------------------------------------------------|----|

| 2~                                      | latad D | ologeo N     | lotos       |                                                                            | 1  |

|                                         |         |              |             |                                                                            |    |

| Libero SoC v12.6 Software Release Notes |         |              |             |                                                                            |    |

|                                         | 1.1.    |              |             | ion (CN) Support                                                           |    |

|                                         |         | 1.1.1.       |             | PCN20027 Maximum Read Frequency on Certain LSRAM Read Modes                |    |

|                                         |         |              |             | en Reduced                                                                 |    |

|                                         | 1.2.    |              |             | ort                                                                        |    |

|                                         |         | 1.2.1.       |             | SoC                                                                        |    |

|                                         |         | 1.2.2.       |             |                                                                            |    |

|                                         |         | 1.2.3.       |             | Fire                                                                       |    |

|                                         | 1.3.    |              |             | and Enhancements                                                           |    |

|                                         |         | 1.3.1.       |             | eport Explorer                                                             |    |

|                                         |         | 1.3.2.       |             | ne CDC Report Enhancements                                                 |    |

|                                         |         | 1.3.3.       | -           | Map Generator                                                              |    |

|                                         |         | 1.3.4.       |             | ed IP Configuration Report in HDL                                          |    |

|                                         |         | 1.3.5.       |             | Option to Sanitize All sNVM/eNVM Pages in Erase Action                     |    |

|                                         |         | 1.3.6.       |             | bug LSRAM ECC Support                                                      |    |

|                                         |         | 1.3.7.       |             | ro and Identify                                                            |    |

|                                         |         | 1.3.8.       |             | n ME and Modelsim ME Pro                                                   |    |

|                                         | 1.4.    |              |             | res and Enhancements                                                       |    |

|                                         |         | 1.4.1.       |             | SoC                                                                        |    |

|                                         |         |              | 1.4.1.1.    | MPFS250 FCVG484 – Bank1 and Bank9 Common Voltage DRC                       |    |

|                                         |         |              | 1.4.1.2.    | Fast MSS DDR Memory Simulation                                             |    |

|                                         |         |              | 1.4.1.3.    | Simulation of User Cryptoprocessor for "S" Devices                         |    |

|                                         |         |              | 1.4.1.4.    | MSS I/Os and Bank Configuration                                            |    |

|                                         |         |              | 1.4.1.5.    | PolarFire SoC Security Policy Manager Option to Disable eNVM Field Updates |    |

|                                         |         |              | 1.4.1.6.    | PolarFire SoC Zeroization Support                                          | 10 |

|                                         |         |              | 1.4.1.7.    | SmartDebug - I/O Margining Analysis for DDR Memory Controllers             | 10 |

|                                         |         | 1.4.2.       | PolarFire   | , RT PolarFire, and PolarFire SoC                                          | 11 |

|                                         |         |              | 1.4.2.1.    | Synthesis Clock Gating                                                     | 11 |

|                                         |         |              | 1.4.2.2.    | Bank-Based I/O Recalibration                                               | 11 |

|                                         |         |              | 1.4.2.3.    | FlashPro 6 Expanded SPI Flash Memory Device Support                        | 11 |

|                                         |         |              | 1.4.2.4.    | FlashPro Express Developer Mode                                            | 12 |

|                                         |         |              | 1.4.2.5.    | SmartDebug XCVR Read/Write Access                                          | 12 |

|                                         |         |              | 1.4.2.6.    | PolarFire XCVR Sourced Fabric Clocks and Jitter Compensation               | 12 |

| 2.                                      | Migra   | ting Desi    | gns to Libe | ro SoC v12.6                                                               | 14 |

|                                         | 2.1.    | Design       | and Core Ir | nvalidation                                                                | 14 |

|                                         |         | 2.1.1.       | MPFS250     | FCVG484 Designs Layout Invalidation Designs Layout Invalidation            | 14 |

|                                         | 2.2.    | Core E       |             | its and Upgrades                                                           |    |

|                                         | 2.3.    |              |             | ersion                                                                     |    |

| 3.                                      | Reso    | olved Issues |             |                                                                            |    |

| 4.  | Known Issues and Limitations                                      | 20 |

|-----|-------------------------------------------------------------------|----|

| 5.  | System Requirements                                               | 23 |

|     | 5.1. Supported 64-bit Operating Systems                           | 23 |

|     | 5.2. Random-Access Memory (RAM) Requirements                      |    |

| 6.  | Download Libero SoC v12.6 Software                                | 24 |

| 7.  | Documents Updated in this Release                                 | 25 |

| 8.  | Appendix A. RTG4 SPLL and FPLL Calibration and Workaround         | 26 |

| 9.  | Appendix B: New Device Support Matrices                           | 27 |

|     | 9.1. PolarFire SoC New Device Support Matrices                    | 27 |

|     | 9.2. PolarFire New Production Timing Support Matrix               | 37 |

|     | 9.3. RT PolarFire Licensing and Device/Package Combination Matrix | 38 |

| 10. | . Revision History                                                | 39 |

| 11. | Microchip FPGA Technical Support                                  | 40 |

|     | 11.1. Customer Service                                            | 40 |

|     | 11.2. Customer Technical Support                                  | 40 |

|     | 11.3. Website                                                     | 40 |

|     | 11.4. Outside the U.S                                             | 40 |

| The | e Microchip Website                                               | 41 |

| Pro | oduct Change Notification Service                                 | 41 |

| Cus | stomer Support                                                    | 41 |

| Mic | crochip Devices Code Protection Feature                           | 41 |

| Leg | gal Notice                                                        | 42 |

| Tra | ademarks                                                          | 42 |

| Qua | ality Management System                                           | 43 |

| Wo  | orldwide Sales and Service                                        | 44 |

### 1. Libero SoC v12.6 Software Release Notes

These release notes contain important information about the Libero® system on chip (SoC) v12.6 unified design suite.

### 1.1 Customer Notification (CN) Support

Libero SoC v12.6 includes changes that address certain important issues.

# 1.1.1 PolarFire PCN20027 Maximum Read Frequency on Certain LSRAM Read Modes Have Been Reduced

The following PolarFire LSRAM configurations have derated Fmax specifications.

Users who use one of the following LSRAM configurations with a design that runs faster than the new limits listed in the following table should upgrade to Libero v12.6 and re-run static timing using SmartTime. For more information, see PCN200027 at www.microsemi.com/company/quality/product-notifications/pcn/asic-soc-fpga.

Table 1-1. LSRAM Configurations that have Derated Fmax Specifications

| Condition                                                              | Datasheet Revision 1.7 |     | Datasheet Revision 1.8 |     | ion 1.8 |

|------------------------------------------------------------------------|------------------------|-----|------------------------|-----|---------|

|                                                                        | STD                    | -1  | -STD                   | -1  | Unit    |

| Dual-port, all supported widths, non-pipelined, and read-before-write  | 274                    | 285 | 240                    | 285 | MHz     |

| Dual-port, all supported widths, pipelined, and read-before-write      | 274                    | 285 | 240                    | 285 | MHz     |

| Two-port, all supported widths, pipelined, and read-before-write       | 274                    | 285 | 240                    | 285 | MHz     |

| Two-port, all supported widths, non- pipelined, and read-before-write  | 274                    | 285 | 240                    | 285 | MHz     |

| Two-port pipelined ECC mode, pipelined, and read-before-write          | 274                    | 285 | 240                    | 285 | MHz     |

| Two-port non-pipelined ECC mode, pipelined, and read-before- write     | 274                    | 285 | 198                    | 240 | MHz     |

| Two-port pipelined ECC mode, non- pipelined, and read-before-write     | 274                    | 285 | 240                    | 285 | MHz     |

| Two-port non- pipelined ECC mode, non-pipelined, and read-before-write | 193                    | 285 | 193                    | 240 | MHz     |

### 1.2 New Device Support

#### 1.2.1 PolarFire SoC

Libero SoC v12.6 introduces programming support, and Advance/Preliminary timing and power support for PolarFire SoC devices. The following tables summarize the preliminary and advanced timing and power information. For detailed information, see 9.1 PolarFire SoC New Device Support Matrices.

Table 1-2. PolarFire SoC Preliminary Timing and Power

| Part Number  | Speed Grade/Temperature | Device Range                                      |

|--------------|-------------------------|---------------------------------------------------|

| MPFS250TS_ES | STD/-1 1.0/1.5V         | EXT devices along with programming and SmartDebug |

| continued   |                         |              |  |  |

|-------------|-------------------------|--------------|--|--|

| Part Number | Speed Grade/Temperature | Device Range |  |  |

| MPFS250TS   | STD/-1 1.0/1.5V         | IND devices  |  |  |

| MPFS250TLS  | STD 1.0/1.5             | IND devices  |  |  |

Table 1-3. PolarFire SoC Advanced Timing and Power

| Part Number            | Speed Grade/Temperature | Device Range    |

|------------------------|-------------------------|-----------------|

| MPFS025/095/160T       | STD/-1 1.0/1.5V         | EXT/IND devices |

| MPFS025/095/160TL      | STD 1.0/1.5V            | EXT/IND devices |

| MPFS025/095/160/460TS  | STD/-1 1.0/1.5V         | IND devices     |

| MPFS025/095/160/460TLS | STD 1.0/1.5V            | IND devices     |

#### 1.2.2 PolarFire

Production timing support has been added for PolarFire devices for 1.0 V and 1.05 V. The following table summarizes the automotive Tgrade2 production timing and power information. For detailed information, see 9.2 PolarFire New Production Timing Support Matrix.

Table 1-5. PolarFire Automotive Tgrade2 Production Timing and Power

| Part Number     | Speed Grade/Temperature | Device Range    |

|-----------------|-------------------------|-----------------|

| MPF100/200/300T | STD/-1 1.0/1.05V        | Tgrade2 devices |

#### 1.2.3 RT PolarFire

Libero SoC v12.6 introduces programming support, and Advance timing and power support for RT PolarFire devices within the PolarFire device family selection. The following table summarizes the advance timing and power information. For detailed information, see 9.3 RT PolarFire Licensing and Device/Package Combination Matrix.

Table 1-6. RT PolarFire Advance Timing and Power

| Part Number      | Speed Grade/Temperature | Device Range |

|------------------|-------------------------|--------------|

| RTPF500T/TS      | -1 1.0/1.05V            | MIL devices  |

| RTPF500TS/TL/TLS | STD 1.0/1.05V           | MIL devices  |

#### 1.3 Software Features and Enhancements

#### 1.3.1 Timing Report Explorer

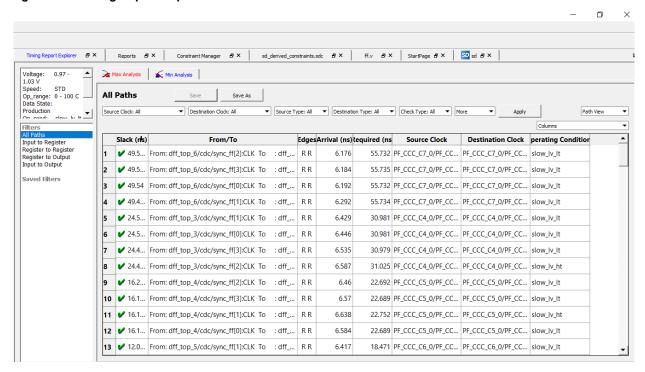

Libero SoC v12.6 introduces Timing Report Explorer to provide a consolidated view of the timing paths present in the Timing Report. The Timing Report Explorer contains filters to select:

- Launch clock and Capture clock

- · Start point and End point

- Setup and hold violations

The Timing Report Explorer is invoked from the Libero menu by selecting **Tools > Timing Browser**.

For more information, see the SmartTime User Guide.

Figure 1-1. Timing Report Explorer

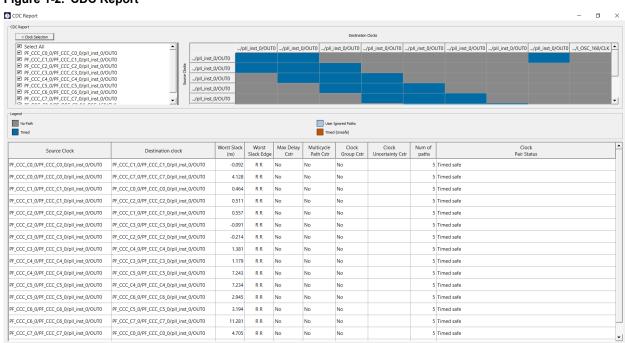

#### 1.3.2 SmartTime CDC Report Enhancements

The CDC Report from SmartTime has been enhanced in Libero SoC v.12.6 to display the following additional information for each source and destination clock group:

- Source Clock

- Destination clock

- · Worst Slack

- Max Delay Cstr

- Multicycle Path Cstr

- · Worst Slack Edge

- · Number of Paths

- Clock Pair Status

#### Figure 1-2. CDC Report

#### 1.3.3 Memory Map Generator

Libero SoC v12.6 enables memory map generation for all AXI, AHB, and APB peripherals connected to a bus host within all SmartDesign components in the active design hierarchy.

The memory map generates Start Address, Range, and DRC, which can be viewed in the SmartDesign Memory Map View widget and can be exported to a JSON file using a menu or a Tcl command.

For more information, see the SmartDesign User Guide.

Figure 1-3. View Memory Map SD View Memory Map X Show Slaves Start Address DRC Master/Bus/Bridge/Peripheral Range top/PFSOC\_MSS\_C0\_0/Coreplex Ė AXI\_SWITCH □ S1\_FIC0\_MSS\_TO\_FABRIC\_AXI4\_512MB 0x6000 0000 0x2000\_0000 □ COREAXI4INTERCONNECT\_C1\_0/AXI4mmaster0 PF\_PCIE\_C0\_0:AXI\_1\_SLAVE 0x7000\_0000 0x1000\_0000 PF\_SRAM\_AHBL\_AXI\_C1\_0:AXI4\_Slave 0x6100\_0000 0x0F00 0000 COREAXI4DMACONTROLLER\_C0\_0:AXI4SlaveCtrl\_IF 0x6002\_0000 0x0001\_0000 PFSOC\_MSS\_C0\_0:FIC\_1\_AXI4\_SLAVE 0xC000\_0000 0x1000\_0000 ₱── S1\_FIC0\_MSS\_TO\_FABRIC\_AXI4\_64GB 0x20\_0000\_0000 0x10\_0000\_0000 S2\_FIC1\_MSS\_TO\_FABRIC\_AXI4\_512MB 0xE000\_0000 0x2000\_0000 0x30\_0000\_0000 0x10\_0000\_0000 S2\_FIC1\_MSS\_TO\_FABRIC\_AXI4\_64GB 0x4000\_0000 0x2000\_0000 S3\_FIC3\_MSS\_TO\_FABRIC\_APB\_512MB ☐ CoreAPB3\_C0\_0/APB3mmaster PF\_PCIE\_CO\_0:PCIE\_APB\_SLAVE 0x4300\_0000 0x0100 0000 CoreGPIO\_C0\_0:APB\_bif 0x4200\_0000 0x0100 0000 S7\_DDRC\_NON\_CACHED\_WCB\_256MB 0xD000\_0000 0x1000\_0000 S7\_DDRC\_NON\_CACHED\_WCB\_16GB 0x18\_0000\_0000 0x04\_0000\_0000 S7\_DDRC\_NON\_CACHED\_256MB 0xC000\_0000 0x1000 0000 S7\_DDRC\_NON\_CACHED\_16GB 0x14\_0000\_0000 0x04\_0000\_0000 S8\_DDRC\_CACHED\_1GB 0x8000 0000 0x4000 0000 0x10 0000 0000 0x04 0000 0000 S8\_DDRC\_CACHED\_16GB 0x0004\_0000 S9\_TRACE 0x2300 0000 ⊕ S5\_AXI\_TO\_AHB0\_BRIDGE 0x2000\_0000 0x2800\_0000 0x0800\_0000 top/PF\_PCIE\_C0\_0 COREAXI4INTERCONNECT\_C0\_0/AXI4mmaster0 PFSOC\_MSS\_C0\_0:FIC\_0\_AXI4\_SLAVE 0x0\_8000\_0000 0x1000\_0000 PF\_SRAM\_AHBL\_AXI\_C0\_0:AXI4\_Slave 0x0\_0000\_0000 0x0000\_1000 top/COREAXI4DMACONTROLLER\_C0\_0 □ COREAXI4INTERCONNECT\_C1\_0/AXI4mmaster1 PF PCIE CO 0:AXI 1 SLAVE 0x0 7000 0000 0x1000 0000 PF\_SRAM\_AHBL\_AXI\_C1\_0:AXI4\_Slave 0x0 6100 0000 0x0F00 0000 COREAXI4DMACONTROLLER\_C0\_0:AXI4SlaveCtrl\_IF 0x0 6002 0000 0x0001 0000 PFSOC\_MSS\_C0\_0:FIC\_1\_AXI4\_SLAVE 0x0 c000 0000 0x1000 0000 Close

## 1.3.4 Embedded IP Configuration Report in HDL

Starting with Libero SoC v12.6, the Tcl commands for IP core generation are embedded in the generated RTL created by SmartDesign. This simplifies regenerating the IP with the same configuration when the design is transferred to another user or when the Libero Project is archived.

For more information, see the Libero SoC Design Flow User Guide or the PolarFire Design Flow User Guide.

#### 1.3.5 Bitstream Option to Sanitize All sNVM/eNVM Pages in Erase Action

Libero v12.6 supports **sanitize sNVM** and **sanitize eNVM** options for the ERASE action. This option programs all 0's into all eNVM/sNVM pages.

- The sNVM sanitize option is supported for PolarFire, RT PolarFire, and PolarFire SoC.

- The eNVM sanitize option is supported for SmartFusion2, IGLOO2, and PolarFire SoC.

The tools that have these options are:

- Generate bitstream.

- · Export bitstream.

- · Export job.

The tools have the new Tcl parameters **sanitize\_snvm** (PolarFire, RT PolarFire, and PolarFire SoC) and **sanitize envm** (SmartFusion2, IGLOO2, and PolarFire SoC).

The sNVM sanitization option is enabled in the Generate Bitstream and Export Job tools if Fabric/sNVM component is selected. In the Export Bitstream, the option is enabled if Fabric/sNVM component is selected for at least one programming file type (master or update).

The eNVM sanitization option is enabled in the Generate Bitstream and Export Job tools if eNVM is configured and eNVM component is selected. In the Export Bitstream tool, the option is available if eNVM is configured and selected for at least one file type (master or update).

Default for both options when they are enabled is "off".

**Note:** The sanitization options do not depend on the OTP security setting. ERASE actions fail if there is OTP security.

#### 1.3.6 SmartDebug LSRAM ECC Support

SmartDebug LSRAM ECC provides the ability to inject single-bit or multi-bit errors and validate design response. This feature applies to RTG4, PolarFire, RT PolarFire, and PolarFire SoC.

Libero SoC v12.6 enhances the SmartDebug GUI for Two-Port LSRAM configured in ECC mode. In this mode, SmartDebug:

- Allows error injection.

- · Displays the Data and ECC bits separately.

- · Reports Single-bit and Double-bit errors.

For more information, see the SmartDebug User Guide.

#### 1.3.7 SynplifyPro and Identify

The SynplifyPro and Identify tools bundled in Libero SoC v12.6 have been upgraded to version Q-2020.03M-SP1.

SynplifyPro Q-2020.03M-SP1 flags warning messages for unconnected Input ports of instantiated macros. For non-hierarchical modules having unconnected input ports for the instantiated macros, the tool issues an error message. For hierarchical or black-box modules having unconnected input ports for instantiated macros, the tool issues a warning message, such as <siqnal> is Unconnected. Assign a valid signal to this pin.

#### 1.3.8 Modelsim ME and Modelsim ME Pro

The Modelsim ME and Modelsim ME Pro bundled in Libero SoC v12.6 have been upgraded to version 2020.3 OEM.

For installations that use a floating license, the floating license daemons must be updated to the latest version listed in the following table.

**Important:** To work with Libero SoC v12.6, users must update their Daemons version. Otherwise, Mentor tool displays an error message and will not open.

#### Table 1-7. Updating Floating License Daemons

| Download        | Imgrd/Imutil/<br>Imhostid | actImgrd   | snpslmd    | mgcld      |

|-----------------|---------------------------|------------|------------|------------|

| Windows Daemons | v11.16.6.0                | v11.16.1.0 | v11.16.6.0 | v11.16.4.0 |

| continued     |                           |            |            |            |  |

|---------------|---------------------------|------------|------------|------------|--|

| Download      | Imgrd/Imutil/<br>Imhostid | actImgrd   | snpslmd    | mgcld      |  |

| Linux Daemons | v11.16.6.0                | v11.16.1.0 | v11.16.6.0 | v11.16.4.0 |  |

#### 1.4 New Silicon Features and Enhancements

#### 1.4.1 PolarFire SoC

#### 1.4.1.1 MPFS250 FCVG484 - Bank1 and Bank9 Common Voltage DRC

In the MPFS250-FCVG484 package, there is no VDDI for Bank9. Instead, this package supports VDDI on Bank1 as in the case of the FCVG484 package for the PolarFire SoC Icicle kit.

A Design Rule Check (DRC) has been implemented in Libero SoC v12.6 to check for this restriction.

For more information check the PPAT file for each package.

#### 1.4.1.2 Fast MSS DDR Memory Simulation

Libero SoC v12.6 introduces a Fast Mode simulation model for the MSS DDR. The fast mode model bypasses the DDR initialization sequence to speed up simulation.

The model also includes a QoS feature to tune the bandwidth for the fabric hosts when accessing DDR.

For more information, see the PolarFire SoC MSS simulation User Guide.

#### 1.4.1.3 Simulation of User Cryptoprocessor for "S" Devices

Libero SoC v12.6 introduces simulation support for User Cryptoprocessor for PolarFire SoC "S" devices.

For more information, see the PolarFire SoC MSS simulation User Guide.

#### 1.4.1.4 MSS I/Os and Bank Configuration

Libero SoC v12.6 introduces MSS I/Os so that bank voltage, placement, and IOSTD are displayed in new columns in the I/O Editor and are read-only.

The I/O and bank information are also reported in the pin report. The board layout pin report has been updated to show how to connect all the bank VDDIs, depending on what is used in the design.

For more information, see the PolarFire IO Editor User Guide.

#### 1.4.1.5 PolarFire SoC Security Policy Manager Option to Disable eNVM Field Updates

Using this option, eNVM can be pass key protected for field updates. By default, field updates are allowed for eNVM without requiring FlashLock Passcode (UPK1). To protect eNVM, select the option to disable erase/write operations, which requires FlashLock Passcode (UPK1) to be able to update eNVM.

#### 1.4.1.6 PolarFire SoC Zeroization Support

Libero SoC v12.6 enables Zeroization support in "Export Bitstream". The generated file will have ZEROIZE LIKE NEW and ZEROIZE UNRECOVERABLE programming actions.

For more information, see the PolarFire Design Flow User Guide.

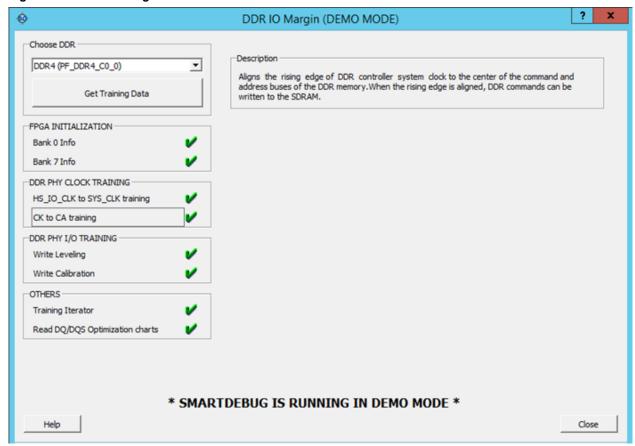

#### 1.4.1.7 SmartDebug - I/O Margining Analysis for DDR Memory Controllers

With Libero SoC 12.6, SmartDebug extends the Debug DDR Memory tool for DDR3/DDR4/LPDDR3 for PolarFire SoC devices. This tool helps users visualize the margin on the DDR I/Os after the DDR Memory I/O interface is trained.

For more information, see the PolarFire SmartDebug User Guide.

Figure 1-4. DDR IO Margin

#### 1.4.2 PolarFire, RT PolarFire, and PolarFire SoC

#### 1.4.2.1 Synthesis Clock Gating

Synplify Pro bundled with Libero SoC v12.6 has been enhanced to support clock gating inference for PolarFire and PolarFire SoC in synthesis. Synplify Pro will infer clock enable logic coded in HDL as GCLKINT or RCLKINT PolarFire macros. This feature can be enabled in Tcl or from the GUI under the **Synthesis > Configure Options**.

For more information, see the Synplify Pro User Guide.

#### 1.4.2.2 Bank-Based I/O Recalibration

Libero SoC v12.6 introduces the capability for users to recalibrate I/Os manually/on-demand for each bank. I/O recalibration is sometimes required to account for delays or to compensate Vt performance impact.

For more information, see the PolarFire IO User Guide.

#### 1.4.2.3 FlashPro 6 Expanded SPI Flash Memory Device Support

Libero SoC v12.6 introduces support for additional SPI Flash devices for programming from FlashPro 6. The support includes devices from Microchip, Macronix, Spansion, ISSI, Winbond, and Micron. For more information, see the Programming User Guide for the specific device family.

Table 1-8. Expanded SPI Flash Memory Device Support

| Manufacturer | Device          |

|--------------|-----------------|

| Micron       | MT25QL01GBBB8ES |

| continued        |                   |  |

|------------------|-------------------|--|

| Manufacturer     | Device            |  |

| Micron           | MT25QPL128AB      |  |

| Macronix         | MX25V4035         |  |

| Macronix         | MX66L51235SF      |  |

| Macronix         | MX66U1G45GMI00    |  |

| Macronix         | MX25L8006EM2I-12G |  |

| Spansion/Cypress | S25FL128S         |  |

| Spansion/Cypress | S25FL256S         |  |

| Spansion/Cypress | S25FL512S         |  |

| Winbond          | W25Q256FV         |  |

| Winbond          | W25Q80DVSSIG      |  |

| Microchip        | SST25PF040CT      |  |

| Microchip        | SST26VF064b       |  |

| Cypress          | CYRS16B256        |  |

#### 1.4.2.4 FlashPro Express Developer Mode

In developer mode, users can create a new job project by automatically constructing chain by scanning the physical devices connected to the selected programmer. This feature is available only in JTAG mode. In FPExpress - developer mode, the programmer connectivity and interface feature is available, which can be used to add, edit, delete devices in a chain, load/unload programming files, and load/unload SPI flash files. This feature is similar to the programming connectivity and interface feature in Libero SoC.

#### 1.4.2.5 SmartDebug XCVR Read/Write Access

Libero SoC v12.6 enables read/write access to the XCVR registers from the SmartDebug GUI. Register access was available from Tcl commands in previous Libero versions.

For more information, see the SmartDebug User Guide.

#### 1.4.2.6 PolarFire XCVR Sourced Fabric Clocks and Jitter Compensation

The PolarFire XCVR can source three different clocks into the fabric:

- TX\_CLK

- RX CLK

- REFCLK (FAB\_REF\_CLK)

These clocks contain high frequency jitter that is not automatically taken into account by Libero in the timing report and SmartTime. It is recommended that users add clock-uncertainty constraints to these clocks in their design.

The following table shows recommended values for clock uncertainty per clock, resource, and speed-grade.

Table 1-9. Recommended Values for Clock Uncertainty

| Clock Type              | STD    | -1     |

|-------------------------|--------|--------|

| FAB_REF_CLK on Global   | 275 ps | 200 ps |

| FAB_REF_CLK on Regional | N/A    | N/A    |

| TX_CLK_G on Global      | 300 ps | 225 ps |

| TX_CLK_R on Regional    | 225 ps | 150 ps |

| continued            |        |        |

|----------------------|--------|--------|

| Clock Type           | STD    | -1     |

| RX_CLK_G on Global   | 325 ps | 250 ps |

| RX_CLK_R on Regional | 250 ps | 175 ps |

The following example shows a clock-uncertainty constraint that can be added to the user's timing SDC file.

```

set_clock_uncertainty -setup 0.150 [ get_pins { PF_XCVR_ERM_LANE2/I_XCVR/LANE0/

TX_CLK_R } ]

set_clock_uncertainty -setup 0.175 [ get_pins { PF_XCVR_ERM_LANE2/I_XCVR/LANE0/

RX_CLK_R } ]

# TX_CLK and RX_CLK on Globals

set_clock_uncertainty -setup 0.300 [ get_pins { PF_XCVR_ERM_LANE2/I_XCVR/LANE0/

TX_CLK_G } ]

set_clock_uncertainty -setup 0.325 [ get_pins { PF_XCVR_ERM_LANE2/I_XCVR/LANE0/

RX_CLK_G } ]

# FAB_REF_CLK on Global

set_clock_uncertainty -setup 0.275 [get_clocks PF_DDR4_C0_0/CCC_0/pll_inst_0/OUT1]

```

The automatic management of these constraints will be added in a future release of Libero SoC.

**Note:** It is also important to add the other required jitter sources as clock uncertainty into your design constraints. See the datasheet for the jitter to be added for components such as PLL, DLL and RC Oscillator. For input pins that are direct or are inputs to the DLL (but not for a PLL), the input jitter on the clock input pin must also be added to your timing constraints.

## 2. Migrating Designs to Libero SoC v12.6

#### 2.1 Design and Core Invalidation

#### 2.1.1 MPFS250 FCVG484 Designs Layout Invalidation Designs Layout Invalidation

Place and route performed with earlier Libero SoC version will be invalidated when Libero SoC v12.6 is invoked for designs using any of the MPFS250-FCVG484 devices if Bank1 and Bank9 have a different VCCI setting. The two banks are physically connected in the package and have a common VCCI pin. For more information, see the Public Pin Assignment Table (PPAT).

### 2.2 Core Enhancements and Upgrades

Table 2-1. Core Enhancements and Upgrades

| Core               | 12.6 Version | Status         | Comments                                                                               |

|--------------------|--------------|----------------|----------------------------------------------------------------------------------------|

| PF_DRI             | 1.1.100      | Production     | Enhancements: Added APB Slave interface option to allow for connectivity via CoreAPB3. |

| PF_INIT_MONITOR    | 2.0.203      | Production     | Enhancements: Added options to enable I/O banks recalibration.                         |

| PF_IOD_OCTAL_DDR   | 2.0.101      | Production     | No functional change: Moved core from pre-production to production status.             |

| PF_TX_PLL          | 2.0.300      | Production     | New advanced Jitter Attenuation options.                                               |

| PFSOC_INIT_MONITOR | 1.0.204      | Pre-production | Enhancements: Added options to enable I/O banks recalibration.                         |

| RTG4_SRAM_AHBL_AXI | 1.0.115      | Production     | Enhancement: Added Tcl support to specify memory files for simulation.                 |

For more information about updating a core version, see 2.3 Updating a Core Version.

### 2.3 Updating a Core Version

Perform the following procedure to update a core version:

- 1. Download the latest version of the core into your vault.

- 2. Upgrade each configured core in your design to the latest version by right-clicking on the core component in the design hierarchy and selecting **Replace Component Version**.

- 3. Regenerate the core.

- Derive the Timing Constraints again from the Constraint Manager tool to use the latest generated core timing constraints.

- Rerun the design flow.

## 3. Resolved Issues

The following table lists the customer-reported defects and enhancement requests resolved in Libero SoC v12.6 that have case numbers. Resolution of previously reported "Known Issues and Limitations" are also noted in this table.

Table 3-1. Customer-reported Defects and Enhancement Requests with Case Numbers

| Case Number        | Description                                                                                 | Resolution                                                                                                                                |

|--------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 493642-2736476316  | "Instruction not yet implemented" error in PolarFire PCIe BFM simulation.                   | Increased Max instruction size to 32768 in serdes_bfm.v file to support more instructions.                                                |

| 493642-2760929388  | Net search/navigation problem not fixed.                                                    | Fixed the Libero code to allow for proper search and navigation between the design tree and the schematic view in the Netlist Viewer.     |

| 493642-2761848512, | Libero 12.4 Unlinking HDL files.                                                            | Fixed the issue to allow for proper                                                                                                       |

| 493642-2789984624  |                                                                                             | search and navigation between the design tree and the schematic view in the Netlist Viewer.                                               |

| 493642-2739601296  | First stage init client occupies 18 pages and user guide mentions only one page.            | Updated the <i>PolarFire FPGA Design Flow User Guide</i> with the correct information.                                                    |

| 493642-2717100262  | TEMPR with custom-specific temperatures.                                                    | Updated the PolarFire FPGA Tcl Command Reference Guide and the Libero SoC Tcl Command Reference Guide to include the missing information. |

| 493642-2174852554  | Enable eNVM/sNVM Sanitization Action/command - ERASE action.                                | Added eNVM/sNVM sanitization to this release. See 1.3.5 Bitstream Option to Sanitize All sNVM/eNVM Pages in Erase Action.                 |

| 493642-2787088315  | Place and Route failure with MPF100T-FCG484I.                                               | Fixed the assertion failure in this release. P&R passes when XCVR is placed using the IO Editor or PDC.                                   |

| 493642-2773005455  | RTPF- Report that tells the user which registers Layout has placed with cluster separation. | Libero now prints a TMR summary after Place and Route is complete.                                                                        |

| 493642-2778179128  | PF_SOC: xport MPE : SmartPower crashes for MSS-based designs.                               | Fixed the crash in this release.                                                                                                          |

| 493642-2736787772, | The I/O standard for the LPDDR4 is                                                          | Corrected the I/O standard for DDR                                                                                                        |

| 493642-2760732693  | not present.                                                                                | banks based on the selected DDR standard.                                                                                                 |

| 493642-2752765844  | FP6 - Support for Spansion /<br>Cypress S25FL512S SPI Flash<br>memory.                      | Expanded support for SPI flash devices. See 1.4.2.3 FlashPro 6 Expanded SPI Flash Memory Device Support.                                  |

| 493642-2748414757  | FP6 - Support for Macronix<br>MX25V4035F SPI Flash memory.                                  | Expanded support for SPI flash devices. See 1.4.2.3 FlashPro 6 Expanded SPI Flash Memory Device Support.                                  |

| continued          |                                                                              |                                                                                                                   |

|--------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Case Number        | Description                                                                  | Resolution                                                                                                        |

| 493642-2684754568, | FP6: PolarFire: SPI-Flash                                                    | Expanded support for SPI flash                                                                                    |

| 493642-2490103952, | Programming devices supported.                                               | devices. See 1.4.2.3 FlashPro 6                                                                                   |

| 493642-2568791212, |                                                                              | Expanded SPI Flash Memory Device Support.                                                                         |

| 493642-2606807822. |                                                                              | Саррана                                                                                                           |

| 493642-2635375032. |                                                                              |                                                                                                                   |

| 493642-2661732256  |                                                                              |                                                                                                                   |

| 493642-2707013487  | FP6 - Support for Cypress<br>S70FS01GSAGMFI010 SPI Flash<br>memory.          | Expanded support for SPI flash devices. See 1.4.2.3 FlashPro 6 Expanded SPI Flash Memory Device Support.          |

| 493642-2706626995  | FP6 - Support for Macronix<br>MX66U1G45G SPI Flash memory.                   | Expanded support for SPI flash devices. See 1.4.2.3 FlashPro 6 Expanded SPI Flash Memory Device Support.          |

| 493642-2761396209  | Provide SPI Flash memory custom size less than 1 MB.                         | Expanded support for SPI flash devices. See 1.4.2.3 FlashPro 6 Expanded SPI Flash Memory Device Support.          |

| 493642-2782147144  | Import HDL Source Folders does not detect files with capital .VHD extension. | Extended Libero support to recognize files with .VHD extension as VHDL files.                                     |

| 493642-2754199742  | Firmware catalog fails to run in Linux.                                      | Fixed the crash in this release.                                                                                  |

| 493642-2672550556  | MEMORYMAP: PF: RISC-V system memory map.                                     | Libero now generates a memory map report. For details, see 1.3.3 Memory Map Generator.                            |

| 493642-2782712105  | I/O editor crashes when io_std is assigned to JTAG banks in PDC.             | Fixed the crash in this release.<br>Libero reports an error when IO<br>standard is assigned to dedicated<br>I/Os. |

| 493642-2782399975  | Enhancement Request on ChipPlanner.                                          | Mousing-over the I/O now displays package pin and I/O bank type.                                                  |

| 493642-2758998134  | HDL_LANGUAGE: Creating testbench instantiates package, but not top module.   | Instantiated the top module as unit under test.                                                                   |

| 493642-2041544240, | Batch mode command for Libero to                                             | Added the new option                                                                                              |

| 493642-2289485500, | display the STD out on screen.                                               | console_mode:show to the Libero command line to display STDOUT on                                                 |

| 493642-2633077946, |                                                                              | the console.                                                                                                      |

| 493642-2725172462  |                                                                              |                                                                                                                   |

| 493642-2783805520  | System Builder and MDDR Configurator seem to block 4 Burst.                  | Added checks for the Burst Length option based on the DDR memory type.                                            |

| 493642-2772574227  | Issue programming PolarFire device through SmartDebug via Tcl script.        | Corrected the exported Tcl file in this release and programming through the Tcl script passes.                    |

| continued                               |                                                                                                      |                                                                                                                           |

|-----------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Case Number                             | Description                                                                                          | Resolution                                                                                                                |

| 493642-2507765827,<br>493642-2638828358 | RTG4: Use SmartDebug to Inject Errors on ECC RAM blocks.                                             | Enhanced Libero SmartDebug to inject errors in RAM blocks. See 1.3.6 SmartDebug LSRAM ECC Support.                        |

| 493642-2205214756                       | MEMORY_MAP: Libero crashes (assertion failure) when Modify Memory Map is invoked.                    | Fixed the reported crash in this release.                                                                                 |

| 493642-2798761326                       | Libero 12.5: B_WEN is wrongly configured for SF2 LSRAM.                                              | Enabled SmartFusion2 LSRAM WEN bit for widths of 10-12.                                                                   |

| 493642-2766233920,<br>493642-2763576582 | Libero crashes when trying to open Top level Smartdesign.                                            | Fixed the crash in this release.                                                                                          |

| 493642-2751906843                       | PF_XCVR: TXPLL: Switching between CDR ref clock and TxPLL.                                           | Removed support for the clocks switching feature and removed the corresponding options from the Transceiver configurator. |

| 493642-2747946263                       | RTG4FCCC: Frequency entry < 400 MHz                                                                  | Fixed the issue in Libero CCC configurator by preventing users from entering a frequency greater than 400 MHz.            |

| 493642-2639320907                       | PF_SRAM_AHBL_AXI: Support of '.ihx' for PF_SRAM_AHBL_AXI.                                            | Added '.ihx' file support to Libero.                                                                                      |

| 493642-2790717260                       | Synplfiy Pro crashes: Error Code [nvhdlgen.cpp:6245 : Error occurred while inferring asymmetric ram. | Fixed this issue in the Synplify Proversion Q-2020.03M-SP1 bundled with Libero SoC.                                       |

| 493642-2774341913                       | m_generic.exe Synplify error.                                                                        | Fixed this issue in the Synplify Proversion Q-2020.03M-SP1 bundled with Libero SoC.                                       |

| 493642-2757444781                       | Remove TMR fault injection feature in GUI.                                                           | Removed the fault injection feature from Synplify Pro options.                                                            |

| 493642-2766323753                       | Synplify crash (on P2019, Q2020 releases).                                                           | Fixed this issue in the Synplify Proversion Q-2020.03M-SP1 bundled with Libero SoC.                                       |

| 493642-2746622253                       | Synthesis timing report question - Large delay associated with OUTBUF.                               | Corrected the output pad delay values.                                                                                    |

| 493642-2759945306                       | Synplify inferring uSRAM instead of LSRAM.                                                           | Fixed this issue in SynplifyPro to infer LSRAM instead of uSRAM.                                                          |

| 493642-2726041637                       | Synthesize error: VHDL slice array assignation not working correctly.                                | Fixed in the SynplifyPro version Q-2020.03M-SP1 bundled with Libero SoC.                                                  |

| 493642-2725654320                       | Synthesize error: VHDL when else in the 'loop' not interpreted correctly.                            | Fixed in the SynplifyPro version Q-2020.03M-SP1 bundled with Libero SoC.                                                  |

| 493642-2725616347                       | Synthesize error: VHDL concatenation (&) with array typed range does not work.                       | Fixed in the SynplifyPro version Q-2020.03M-SP1 bundled with Libero SoC.                                                  |

| continued         |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                 |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Case Number       | Description                                                                                                                                                                                                                    | Resolution                                                                                                                                                                                                                                                                      |

| 493642-2775228780 | Project state is not preserved while opening project via tcl command.                                                                                                                                                          | Fixed this issue in this release. Project state is preserved when the Libero project is reopened.                                                                                                                                                                               |

| 493642-2707807672 | Absolute/Relative path: Enhancement Request: Synthesis script setting in the "configure_tool - name {SYNTHESIZE}" is stored with hard path.                                                                                    | Added this enhancement to this release. Relative paths can now be set in <b>Synthesis -&gt; Configure Options</b> .                                                                                                                                                             |

| 493642-2771635140 | SpaceWire Data Timing path used in V12.3 no longer exists.                                                                                                                                                                     | Fixed this issue in this release. SmartTime now allows path ending at a register clock pin to be reported in user sets.                                                                                                                                                         |

| 493642-2820892077 | When DRI mode is enabled, ECALIB configurator will not open in Libero SoC 12.5 SP1. When DRI mode is disabled and GL0 is not used in the design, ECALIB configurator will not open in Libero SoC 12.5 and Libero SoC 12.5 SP1. | Use Libero SoC v12.6 or Libero SoC v 12.4. While computing internal delays, Libero takes GL0 as the slowest clock that is not used. As a result, configurator does not open in Windows and causes an assertion failure in Linux. To avoid this, use Libero 12.6 or Libero 12.4. |

| 493642-2829401262 | In Libero v12.5 and v12.5 SP1, Chip Planner crashed after the regions were renamed in the <b>Regions</b> tab.                                                                                                                  | This issue has been resolved in Libero v12.6.                                                                                                                                                                                                                                   |

The following table lists the customer-reported defects and enhancement requests resolved in Libero SoC v12.6 that do not have case numbers. Resolution of previously reported "Known Issues and Limitations" are also noted in this table.

Table 3-2. Customer-reported Defects and Enhancement Requests (No Case Numbers)

| Description                                                                    | Resolution                                                                                                                         |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| I/O: Remove I/O placement table from compile and move it to the layout report. | For SmartFusion2/IGLOO2/RTG4, moved the I/O placement section from the compile report to the layout log after the resource report. |

| RTG4 exported full placement pdc constraint fails constraint manager check.    | Excluded duplicated RGRESET created by layout from the PDC export that was causing the error.                                      |

| Reading X.509 certificate from JTAG using FlashPro.                            | Displayed the X.509 certificate in FlashPro Express log window under "READ_DEVICE_CERTIFICATE" action.                             |

| Incorrect FPGA state printed relative to the selected run Action.              | Fixed the issue with Flash Pro and the correct state of device is now displayed.                                                   |

| PF_IOD_CDR: hs io clk bridging in io cdr causes issues.                        | Prevents low skew bridging with PF_IOD_CDR.                                                                                        |

| IOFF Combining for DIFF IO PADN Flow and Reporting Issues.                     | Addressed reporting issues so that compile report now displays the correct differential IO usage.                                  |

| Add Usage Details for PolarFire/IGLOO2/RTG4 routing conflicts report.          | Added the routing conflicts report to the Libero online help to which users can.                                                   |

| continued                                                                                                                                                |                                                                                                                                                             |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Description                                                                                                                                              | Resolution                                                                                                                                                  |  |

| Tcl command download_core does not work in command line execution.                                                                                       | Fixed a Libero issue with loading web repositories in command line mode. Users can now download cores from the command line.                                |  |

| Utilization report doesn't match compile report.                                                                                                         | Fixed a Power Estimator issue with exporting Math Blocks with zero activity. The utilization between Power Estimator and Libero compile report now matches. |  |

| Support for ISSI SPI Flash memory.                                                                                                                       | Expanded support for SPI flash devices. See 1.4.2.3 FlashPro 6 Expanded SPI Flash Memory Device Support.                                                    |  |

| MEMORY_MAP: REPORT: Incomplete Design Summary produced.                                                                                                  | Enhanced Libero to generate a Memory map. For details, see 1.3.3 Memory Map Generator.                                                                      |  |

| Don't limit NUM_MULTI_PASSES to 25.                                                                                                                      | Removed the limit on the number of multipass seeds. Users can set a number higher than 25 in Tcl mode only.                                                 |  |

| HDL_LANGUAGE: HDL check displays incorrect errors.                                                                                                       | Fixed the error in "Check HDL" function. Check HDL no longer displays incorrect errors in this scenario.                                                    |  |

| PF_PCIE: AXI-Slave (from the fabric side) limit increase.                                                                                                | Fixed the Libero limitation of 2 GB addressing. PolarFire PCle can now address the full 4 GB address range.                                                 |  |

| PF_DRI: APBS port on PF_DRI should be configured as a slave interface.                                                                                   | Enhanced PF_DRI IP to support a new APB slave interface.                                                                                                    |  |

| Crash with msg::Internal Error in m_generic.exe.                                                                                                         | Fixed the crash in this release.                                                                                                                            |  |

| SynplifyPro O-2018.09M-SP1-1: Enable signal disables input/output pipeline register packing for wide multipliers.                                        | Fixed this issue in the SynplifyPro bundled with this release. Synplify now packs registers in the Math Block for wide multipliers.                         |  |

| Libero 12.2, Customer VHDL Issue with unconstrained array type error.                                                                                    | Fixed this issue in the SynplifyPro bundled with his release.                                                                                               |  |

| Synthesis VHDL Compiler gives error message "choice 0 is out of range" for the slice array assignment statement.                                         | Corrected Synthesis VHDL Compiler to interpret the slice array assignment statement properly without any error.                                             |  |

| Synthesis VHDL Compiler gives error message "index out of range" for when-else statement used in the for loop in the RTL.                                | Corrected Synthesis VHDL Compiler to interpret the whenelse statement used in the for loop correctly without any error.                                     |  |

| Synthesis VHDL Compiler fails in the concatenation of array if the Array range is defined as subtype natural_downto range <> instead of natural_range<>. | Corrected Synthesis VHDL Compiler to interpret the concatenation of array correctly if the Array range is defined as natural_downto range <>.               |  |

## 4. Known Issues and Limitations

The following table lists known issues and limitations associated with Libero SoC v12.6.

Table 4-1. Known Issues and Limitations Associated with Libero SoC v12.6

| Family                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                             | Libero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| All families                | For designs using CoreAHBLite combined region slot, the SmartDesign Memory Map does not show the correct Range of the combined region slot. The expected range of the combined region slot is n times the size of each slot, where n is the number of slots assigned to the combined region slot. However, in the View Memory Map dialog, the range for the combined region slot is shown as 0x0000_0000 resulting in a DRC.                                                                                                                                                                                                               |  |  |

| IGLOO2                      | For a System Builder design that uses only FDDR out of the DDR/SERDES peripherals, the exported Tcl description file shows the FABRIC_DDR_SETTLING_TIME is not set (the EXTMEM page is not configured).  Note: There is no issues if only MDDR is used or if FDDR is used in combination with MDDR in a design.                                                                                                                                                                                                                                                                                                                            |  |  |

|                             | Workaround: If there's a requirement of a FABRIC_DDR_SETTLING_TIME other than its default value 200, manually update the exported Tcl description file to add the below lines after the Device Features page configuration.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                             | # Configuring the Memories page of System Builder component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                             | <pre>sb_configure_page -component_name \${sysbld_name} -page_name {EXTMEM} \ -params {FABRIC_DDR_SETTLING_TIME:<non_default_value>}</non_default_value></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PolarFire                   | Opening two or more views (for example, Hierarchical RTL View and Flattened Post-Compile View) in Netlist Viewer may cause a crash due to memory usage. Avoid opening multiple views for large designs.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                             | The DRC check in the I/O Editor does not validate all the constraints set in the tool. You must run Place and Route to validate these constraints.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| PolarFire                   | Using the protocol setting APMemory PSRAM of PF_IOD_OCTAL_DDR causes Place and Route to fail.  Workaround: Change to configuration to HyperBus with I0R0_RSTO_N enabled and I0R0_INT_N disabled. The generated core will work properly with APMemory PSRAM.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| PolarFire, PolarFire<br>SoC | In Libero, selecting <b>Disable SNVM</b> through <b>Debug Policy</b> on the <b>Configure Security Wizard</b> dialog box does not disable sNVM SmartDebug access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                             | This affects PolarFire family in Libero v12.0 and later, and PolarFire SoC family in Libero v12.5 and later.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| N/A                         | If a module is present in an include file that is coming from a global include path but is not imported into the project, the file is shown as linked file in the Design Hierarchy. If the Global Include Path is broken (path is missing when opening a project), the include file also is shown with a broken link. If the user tries to fix the broken global include path with a new path, the broken file link with the old path still appears. This does not affect functionality, but an extra broken link is shown in the project. Users must remove this link manually when changing the Global Include Path in Project Settings. |  |  |

|                             | Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| continued                   |                                                                                                                                                                                                                                                                                                                                                               |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Family                      | Description                                                                                                                                                                                                                                                                                                                                                   |  |

| PolarFire                   | With Automatic Compile Point ON in Synthesis, some designs with the CoreAXI4Interconnect IP might fail in derived constraints check in Place & Route.                                                                                                                                                                                                         |  |

|                             | Workaround 1: In the <b>Synthesis -&gt; Configure Options</b> , turn OFF the Automatic Compile Point and then run Synthesis.                                                                                                                                                                                                                                  |  |

|                             | Workaround 2: Use get_pins instead of get_nets for the following constraint in <top_level>_derived_constraints.sdc file.</top_level>                                                                                                                                                                                                                          |  |

|                             | <pre>set_false_path -through [ get_pins { AXI4_Interconnect_0/ ARESETN* } ]</pre>                                                                                                                                                                                                                                                                             |  |

| RTG4 and PolarFire          | The ECC inference has been deprecated from SynplifyPro for RTG4 and PolarFire families. All references to RAM Inference in ECC mode are removed from SynplifyPro documentation from Libero 12.5 onwards. Replace any inferred ECC memory in your design for all IP cores with modules generated by the respective LSRAM Configurators.                        |  |

|                             | Timing/Power                                                                                                                                                                                                                                                                                                                                                  |  |

| PolarFire                   | The datasheet has slight variations of Max Frequency that software does not represent. In particular, the following two modes have a slightly lower Max Frequency:  • 18 × 19 multiplier pre-adder ROM mode  • Complex 18 × 19 multiplication                                                                                                                 |  |

|                             | The variations are small and on the high-end of the chip frequencies (between 455 and 470MHz at dash-one).                                                                                                                                                                                                                                                    |  |

| PolarFire                   | Starting with Libero SoC v12.4, SmartTime stopped propagating clocks when a generated clock is reached. For example, in a design, the clocks are clk1> gen1> gen2. If gen2 is specified using gen1 as master, there is no issue. If gen2 is specified using clk1 as master, however, the generation fails as clk1 never reaches gen2 (it is stopped by gen1). |  |

|                             | Workaround: Specify the second generated clock using the first generated clock as master.                                                                                                                                                                                                                                                                     |  |

| PolarFire                   | In the SmartTime tool, the search option using <b>Apply filter</b> is not working.                                                                                                                                                                                                                                                                            |  |

|                             | SmartDebug                                                                                                                                                                                                                                                                                                                                                    |  |

| PolarFire, PolarFire<br>SoC | In the SmartDebug when Dual mode PCle design is considered, the following issues are observed in the PCle debug feature:                                                                                                                                                                                                                                      |  |

|                             | <ul> <li>Not showing the PCle0, only PCle1 is shown in the UI in the case of dual PCle<br/>designs that have PCl0 and PCle1 controllers.</li> </ul>                                                                                                                                                                                                           |  |