# AC492 Application Note Running BareMetal User Applications on PolarFire SoC FPGA

а 🔨 Міскоснір company

Microsemi Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# Contents

|   | Revision History         1.1       Revision 2.0         1.2       Revision 1.0                                                       | . 1 |

|---|--------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | Running BareMetal User Applications on PolarFire SoC FPGA      2.1    Prerequisites                                                  |     |

| 3 | Running the BareMetal User Applications         3.1       System Services         3.1.1       Running the System Service Application | . 3 |

# **Figures**

| Figure 1  | Debug Configurations               | 3 |

|-----------|------------------------------------|---|

| Figure 2  | Launching the Debugger             | 4 |

| Figure 3  | Confirm Perspective Switch Message | 4 |

| Figure 4  | Resume Debugging                   | 5 |

| Figure 5  | System Services Options            | 5 |

| Figure 6  | Read Device Serial Number          | 5 |

| Figure 7  | Read Device User-code              | 5 |

| Figure 8  | Read Device Design-info            | 5 |

| Figure 9  | Read Device Certificate            |   |

| Figure 10 | Read Digest                        | 7 |

| Figure 11 | Security Locks                     |   |

| Figure 12 | Read Debug Information             | 7 |

| Figure 13 | Digital Signature                  | 8 |

| Figure 14 | PUF Emulation Service              | 8 |

| Figure 15 | Nonce Value                        | 8 |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

# 1.1 Revision 2.0

Updated for Libero SoC v12.6.

# 1.2 Revision 1.0

The first publication of this document.

# 2 Running BareMetal User Applications on PolarFire SoC FPGA

Microchip's PolarFire<sup>®</sup> SoC FPGAs include industry's first RISC-V based Microprocessor Subsystem (MSS) and a fabric that inherits all the features of the PolarFire family. The PolarFire SoC MSS includes 5x 64-bit RISC-V processor cores, AXI Switch, DDR Controller, fabric Interface Controllers (FIC), and a rich set of peripherals. For more information about the PolarFire SoC MSS and its components, see *UG0880: PolarFire SoC FPGA MSS User Guide*. PolarFire SoC FPGAs are ideal for running BareMetal applications.

PolarFire SoC standalone MSS Configurator (no separate license required) facilitates independent configuration of MSS for use in Libero<sup>®</sup> SoC and SoftConsole. The standalone MSS configurator provides a seamless interface and can be used by Embedded Software developers and FPGA designers. For more information, see *PolarFire SoC Standalone MSS Configurator User Guide*. FPGA designers can add fabric components by using Libero SoC SmartDesign and IP Library.

Microchip's MPFS-ICICLE-KIT features the MPFS250T\_ES SoC FPGA, a rich set of peripherals, ROM, and RAM options. For ROM requirement, the kit includes an 8 GB eMMC Flash memory. For external RAM requirement, the kit includes a 2 GB LPDDR4 device. The kit also features an SD Card slot. For more information, see *UG0882: PolarFire SoC FPGA ICICLE Kit User Guide*.

This application note describes how to run BareMetal user applications on MPFS-ICICLE-KIT.

# 2.1 **Prerequisites**

Before running the BareMetal user applications, the ICICLE kit must be programmed with the ICICLE reference design. Ensure to follow the documentation provided on *GitHub* and program the ICICLE kit reference design with one of the FlashPro Express programming files.

# 3 Running the BareMetal User Applications

Before you start, ensure to program the ICICLE KIT as described in Prerequisites. After successful programming, the following user applications can be run:

- System Services

- Single-Bit Error Detection and Correction for L2 LIM

- MicroPython

This document describes the steps to run the System Services application.

**Note:** For information about running other BareMetal user applications, see the *baremetal\_applications GitHub* web page.

# 3.1 System Services

System Services SoftConsole project includes the following source files for running System Services:

- BareMetal MSS System Services driver which is available at the following location: https://github.com/polarfire-soc/polarfire-soc-bare-metal-library/tree/master/src/platform/driv-ers/mss\_sys\_services

- PolarFire SoC hardware abstraction layer source code (mpfs\_hal). Using the mpfs\_hal code, the user can access all of the PolarFire SoC MSS registers like E51 and U54 local interrupt registers, L2 cache, MPU, segmentation blocks, and others registers. This folder also includes the MSS peripherals base address file.

- **Note:** Hardware parameters like MSS clocks, memory, and peripheral source files are generated in SoftConsole using the MSS XML configuration file. The MSS XML configuration file is available at <a href="https://github.com/polarfire-soc/icicle-kit-reference-design/tree/master/XML">https://github.com/polarfire-soc/icicle-kit-reference-design/tree/master/XML</a>.

# 3.1.1 Running the System Service Application

This section describes how to launch the System Services application in debug mode using SoftConsole and run the PolarFire SoC System Services via serial interface.

**Note:** This SoftConsole project can also be built in release mode and run from eNVM. Select Run > External Tools > PolarFire SoC program non secure boot mode 1 option to program the eNVM with the application and execute it.

To run the System Services:

- 1. Launch SoftConsole with the provided System Services project.

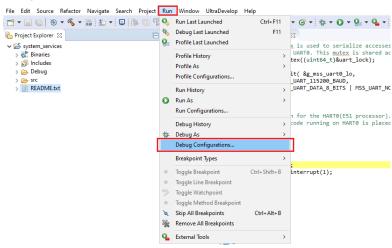

- 2. Click Run->Debug Configurations.

### Figure 1 • Debug Configurations

- 3. In the Debug Configurations window, select the debug project highlighted in Figure 2.

- 4. Select the **Debug** option in the dialog box for launching the application in debug mode.

# Figure 2 • Launching the Debugger

| eate, manage, and run config |                                           |                            |                   | 20     |

|------------------------------|-------------------------------------------|----------------------------|-------------------|--------|

| i 🖻 🕫 🗎 🔲 🏹 🗸                |                                           |                            |                   | 2      |

|                              | Name: system_services Debug               |                            |                   |        |

| ype filter text              | 🗎 Main 🔅 Debugger 🍉 Startup 🦆 S           | Source 🔲 Common 🔀 SVD Path | ]                 |        |

| C GDB OpenOCD Debugging      | Project:                                  |                            |                   |        |

| 🚜 Launch Group               | system_services                           |                            |                   | Browse |

| Robot                        | C/C++ Application:                        |                            |                   |        |

| Robot Remote                 | Debug\system_services.elf                 |                            |                   |        |

| S UltraDevelop OCD           | · · · · · · · · · · · · · · · · · · ·     | Variables                  | Search Project    | Browse |

| 🄏 UltraDevelop Remote Target | Build (if required) before launching      |                            |                   |        |

|                              | Build Configuration: Select Automatically | /                          |                   | ~      |

|                              | O Enable auto build                       | O Disable auto build       |                   |        |

|                              | Use workspace settings                    | Configure Workspac         |                   |        |

|                              |                                           |                            | <u>e settings</u> |        |

|                              |                                           |                            | <u>e seungs</u>   |        |

5. In the Confirm Perspective Switch window, click Switch to go to the debug view.

## Figure 3 • Confirm Perspective Switch Message

| sc Con | firm Perspective Switch X                                                                                                                                          |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ?      | This kind of launch is configured to open the Debug perspective when it suspends.                                                                                  |  |  |

|        | This Debug perspective is designed to support application debugging. It incorporates<br>views for displaying the debug stack, variables and breakpoint management. |  |  |

|        | Do you want to switch to this perspective now?                                                                                                                     |  |  |

| 🗌 Ren  | nember my decision Switch No                                                                                                                                       |  |  |

|        |                                                                                                                                                                    |  |  |

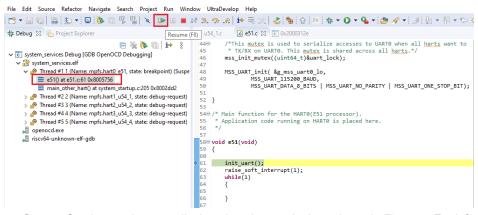

The debugger stops at the <code>void e51 (void)</code> startup function in the <code>e51.c</code> file. This function initializes the UART interface and sends a software interrupt to the U54\_1 processor core and releases it from the wait for interrupt mode (WFI). The <code>u54\_1</code> hart starts executing the System Services functions.

6. Click Resume to start running System Services application as shown in Figure 4.

## Figure 4 • Resume Debugging

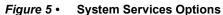

7. System Services options are displayed on the terminal, as shown in Figure 5. For information about each System Service and output bit fields, see UG0905: PolarFire SoC FPGA System Services User Guide.

| **** PolarFireSoC system services Example ****<br>Notes: Return data from System controller is displayed byte-vise with LSB first<br>Input data is provided LSB first. Each ASCII character is one Nibble of d<br>ata                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Select Service:                                                                                                                                                                                                                                            |

| Device and Design Information Services:                                                                                                                                                                                                                    |

| 1. Read Device Serial Number<br>2. Read Device User-code<br>3. Read Device Design-info<br>4. Read Device Design-info<br>5. Read Digest Certificate<br>5. Read Digest Security<br>6. Query Security<br>7. Read Debug Information<br>Data Security Services: |

| 8. Digital Signature<br>9. PUF Emulation<br>a. Nonce                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                            |

- 8. Enter 1 to select Read Device Serial Number.

- The 128-bit Read Device Serial Number (DSN) is displayed, as shown in Figure 6.

## Figure 6 • Read Device Serial Number

Device serial number: E24BABFEB7CA08B639F6FDB7D0E9EB45

Each PolarFire SoC FPGA device has a unique, publicly readable, 128-bit DSN. The DSN can be used in cryptographic protocols to uniquely identify the device. For more information, see *UG0918: PolarFire SoC FPGA Security User Guide*.

Enter 2 to select Read Device User-code. This can be configured in the Libero SoC project from Design flow->Program Design->Configure Programming Options.

The 32-bit device USERCODE/Silicon signature is displayed, as shown in Figure 7.

### Figure 7 • Read Device User-code

### 32bit USERCODE/Silicon signature (MSB first): ABCDEF01

- **Note:** In the Libero project, this USERCODE/silicon signature can be configured from Design flow->Program Design->Configure Programming Options. If the values are not entered, you can see zero.

- 10. Enter 3 to select Read Device Design-info.

- Figure 8 Read Device Design-info

| Design | ID:      |           |           |  |  |

|--------|----------|-----------|-----------|--|--|

|        |          | 000000000 | 000000000 |  |  |

|        |          |           | 000000000 |  |  |

| Design | Version: | 0100      |           |  |  |

| Design | Back-Lev | el: 0000  | )         |  |  |

The device design information consists of:

- 256-bit user-defined Design ID.

- 16-bit design version: This can be configured from Design flow->Program Design->Configure Programming Options. In auto update programming, the current design version is compared with the available images in external SPI flash to initiate the auto update on power up.

- 16-bit design back-level: This can be configured from Design flow->Program Design->Configure Security. When back level protection is enabled, the device can only be programmed if the target design version is more than the back-level value.

- 11. Enter 4 to select Read Device certificate.

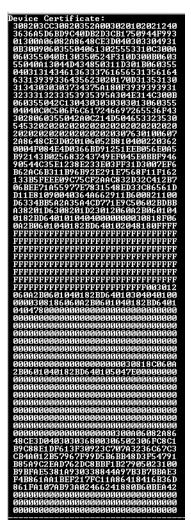

The device supply chain assurance certificate is displayed, as shown in Figure 9.

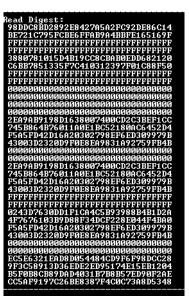

#### Figure 9 • Read Device Certificate

The Device Certificate is a 1024 bytes Microsemi-signed X-509 certificate programmed during manufacturing. The certificate is used to guarantee the authenticity of a device and its characteristics.

12. Enter 5 to select Read Digest.

The 576 bytes Digest contains the fabric digest, sNVM digest, and user key digests. The digest protects data integrity. Figure 10 shows the 576 bytes digest.

Figure 10 • Read Digest

13. Enter 6 to select Query Security.

The non-volatile states of user security lock is displayed, as shown in Figure 11.

The design does not include any user security settings for device security. Security locks can be configured from Design flow->Program and Debug Design->Configure Security.

## Figure 11 • Security Locks

#### 14. Enter 7 to select Read Debug Information.

The debug information is displayed, as shown in Figure 12. In Figure 12, the highlighted 4 bytes E1000000 (LSB first) indicates the number of times the device was programmed (programming cycles).

Figure 12 • Read Debug Information

| Debug info:                        |

|------------------------------------|

| 000000CE280021002300CF09C409CB09   |

| 0A07B902CC1900000000000000000000   |

| C101C44C0171198AFF00FFFF00000000   |

| 0003FFFFCA00000044040000E1000000   |

| 0080781015D4B19C000000000000010010 |

| FF3E00007E000300030000000000       |

15. Enter 8 to select Digital Signature.

The digital signature in both Raw and DER formats is displayed, as shown in Figure 13.

### Figure 13 • Digital Signature

Digital Signature service: 48 byte hash value: 1850c211898959574808084B47DD499D 1CD655Dc4C188187F4CE5866265F689D 1850c2118989595748080084B47DD499D Raw format: Digital Signature service successful. Output Digital Signature - Raw format: FCFACE438477C71DC45E37A95C996FD4 223B044547B1C914B5800647PFFC1D13 865DB76095864B4C51975E8936725A45 3287F42FEDDAC4F6452P14151BD0C754 BF18Ea57D679579B1F6EF40733F9E40BA 7EEF45F2D33F562A99D5243B2ECA61A8 DER format: Digital Signature service successful. Output Digital Signature - DER format: 3066023100A83885070B274618CAF277 33B889C06A8B87E9D48D6515E61D22CE1 540251979A623190B9D457652591E 640251979A623190B9D245769CE911E 900C2125DFC2E777A052BB5AE5E77959 6418BB7005F2E289963A2E852643ACEA

The digital signature service takes a user supplied SHA384 hash and signs it with the devices private key. The application randomly generates the SHA384 hash value. The Digital Signature service sends the hash value to the System Controller. The System Controller Cryptoprocessor runs the Elliptic Curve Digital Signature Algorithm (ECDSA) using the hash and the device private key to generate the signature.

16. Enter 9 to select PUF Emulation service.

The PUF emulation service provides a mechanism for authenticating a device, or for generating a pseudo-random bit strings that can be used for different purposes. When this service is selected, the service by default accepts a 128-bit challenge and an 8-bit optype, and returns a 256-bit response unique to the challenge and the optype as shown in Figure 14.

### Figure 14 • PUF Emulation Service

| The challenge OPTYPE range(0x0 to 0xFF): C8          |

|------------------------------------------------------|

| 16 byte challenge:                                   |

| C8B02F4FB7F702B1A08AD1FECBACCC63                     |

| PUF emulation service successful.Generated Response: |

| 23C8C11D424C6837C1DFCCBFAFE60D05                     |

| 59C96927D179026E187E1B1FDE996DB6                     |

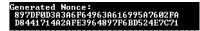

17. Enter "a" to select Nonce service.

The 32 bytes nonce value is generated by the device as shown in Figure 15.

### Figure 15 • Nonce Value

This concludes the running System Services application and the SoftConsole debug session can be terminated.