# **CoreTSE User Guide**

## Introduction

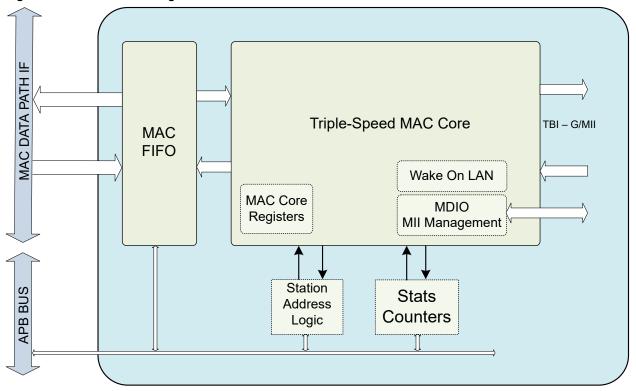

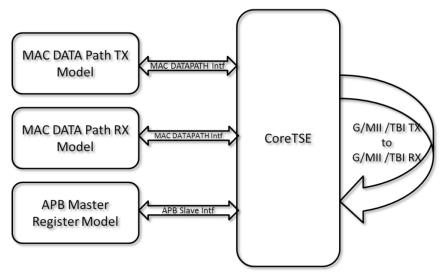

The CoreTSE provides 10/100/1000 Mbps Ethernet Media Access Controller (MAC) with a Gigabit Media Independent Interface (G/MII) or Serial Gigabit Media Independent Interface (SGMII) Ten Bit Interface (TBI) to support 1000BASE-T and 1000BASE-X.

The CoreTSE has the following major interfaces:

- · G/MII or SGMII TBI physical layer (PHY) interface connects to Ethernet PHY

- Management data input/output (MDIO) interface to communicate with the MDIO manageable device (MMD) in the PHY

- MAC data path interface

- · Advanced peripheral bus (APB) Target interface for MAC configuration registers and status counters access

A triple speed MAC core is responsible for the main functionalities of CoreTSE. They are:

Statistics gathering - Statistics information is gathered from the data transmitted and received over the Ethernet link. Station address functions - Station address (SAL) feature provides address filtering capability.

Figure 1. CoreTSE Block Diagram

### **Features**

CoreTSE has the following features:

- 10/100/1000 Mbps Operation

- Full-duplex Support at 10/100/1000 Mbps

- Half-duplex Support at 10/100 Mbps

- · Standard G/MII Interface

- · MDIO Interface for PHY Register access

- SGMII Ten Bit Interface (TBI)

- · Wake on LAN (WoL) with Magic Packet Detection

- · Frame Statistics Counters

- · Destination Address-Based Filtering

#### **Core Version**

This document applies to CoreTSE version 3.2.

# Supported Families

- PolarFire<sup>®</sup> SoC

- PolarFire

- IGLOO®2

- RTG4<sup>™</sup>

- SmartFusion®2

### **Device Utilization and Performance**

Device utilization and performance data is provided in Table 1 to Table 4 for the supported device families. The TXCLK, RXCLK, TBI\_TX\_CLK, and TBI\_RX\_CLK performance is above 125 MHz. The data in the following table is achieved using typical synthesis and layout settings. The data described in the table is only indicative. The overall device utilization and performance of the core is system dependent.

#### **CoreTSE Device Utilization**

The following table describes the CoreTSE device utilization applicable for these (G/MII, PACKET\_SIZE = 256 Bytes, SAL-OFF, WoL-OFF, and STATS-OFF) parameters.

**Table 1. CoreTSE Device Utilization**

| Family (Device)             | Utilization      |                     |       | Performance (MHz |      |        | lz)    |

|-----------------------------|------------------|---------------------|-------|------------------|------|--------|--------|

|                             | Sequential (DFF) | Combinational (LUT) | Total | %                | PCLK | MTXCLK | MRXCLK |

| SmartFusion2® (M2S050)      | 2347             | 3211                | 5558  | 9.87             | 190  | 220    | 197    |

| IGLOO2® (M2GL050)           | 2347             | 3211                | 5558  | 9.87             | 190  | 220    | 197    |

| RTG4 <sup>®</sup> (RT4G150) | 2323             | 3313                | 5635  | 3.71             | 156  | 186    | 152    |

| PolarFire® (MPF300T)        | 2287             | 3143                | 5430  | 1.81             | 297  | 304    | 266    |

| PolarFire SoC (MPFS250T)    | 2287             | 3143                | 5430  | 2.14             | 292  | 340    | 292    |

#### **CoreTSE Device Utilization**

The following table describes the CoreTSE device utilization applicable for these (G/MII, PACKET\_SIZE = 32 KB, SAL-ON, WoL-ON, and STATS-ON) parameters.

**Table 2. CoreTSE Device Utilization**

| Family (Device)             | Utilization      |                     |       |       | Performance (MHz) |        |        |  |

|-----------------------------|------------------|---------------------|-------|-------|-------------------|--------|--------|--|

|                             | Sequential (DFF) | Combinational (LUT) | Total | %     | PCLK              | MTXCLK | MRXCLK |  |

| SmartFusion®2 (M2S050)      | 5564             | 8267                | 13831 | 24.55 | 140               | 186    | 124    |  |

| IGLOO®2 (M2GL050)           | 5564             | 8267                | 13831 | 24.55 | 140               | 186    | 124    |  |

| RTG4 <sup>™</sup> (RT4G150) | 5579             | 8662                | 14241 | 9.38  | 115               | 146    | 91     |  |

| PolarFire® (MPF300T)        | 5299             | 8568                | 13867 | 4.63  | 220               | 248    | 187    |  |

| PolarFire SoC<br>(MPFS250T) | 5299             | 8568                | 13867 | 5.46  | 203               | 256    | 174    |  |

#### **CoreTSE Device Utilization**

The following table describes the CoreTSE device utilization applicable for these (TBI, PACKET\_SIZE = 256 Bytes, SAL-OFF, WoL-OFF, and STATS-OFF) parameters.

**Table 3. CoreTSE Device Utilization**

| Family (Device)             | Utilization      |                     |       |       | Perfor | mance (Mŀ | (MHz)  |  |

|-----------------------------|------------------|---------------------|-------|-------|--------|-----------|--------|--|

|                             | Sequential (DFF) | Combinational (LUT) | Total | %     | PCLK   | MTXCLK    | MRXCLK |  |

| SmartFusion®2 (M2S050)      | 3408             | 5271                | 8679  | 15.40 | 177    | 221       | 184    |  |

| IGLOO®2 (M2GL050)           | 3408             | 5271                | 8679  | 15.40 | 177    | 221       | 184    |  |

| RTG4 <sup>™</sup> (RT4G150) | 3374             | 5324                | 8698  | 5.73  | 162    | 163       | 154    |  |

| PolarFire® (MPF300T)        | 3329             | 5113                | 8442  | 2.82  | 288    | 358       | 301    |  |

| PolarFire SoC (MPFS250T)    | 3329             | 5113                | 8442  | 3.32  | 292    | 340       | 292    |  |

#### **CoreTSE Device Utilization**

The following table describes the CoreTSE device utilization applicable for these (TBI, PACKET\_SIZE = 32 KB, SAL-ON, WoL-ON, and STATS-ON) parameters.

Table 4. CoreTSE Device Utilization

| Family (Device)             | Utilization      |                     |       |       | Perfor | mance (MF | nance (MHz) |  |

|-----------------------------|------------------|---------------------|-------|-------|--------|-----------|-------------|--|

|                             | Sequential (DFF) | Combinational (LUT) | Total | %     | PCLK   | MTXCLK    | MRXCLK      |  |

| SmartFusion®2 (M2S050)      | 6623             | 10206               | 16829 | 29.87 | 136    | 166       | 126         |  |

| IGLOO®2 (M2GL050)           | 6623             | 10206               | 16829 | 29.87 | 136    | 166       | 126         |  |

| RTG4 <sup>™</sup> (RT4G150) | 6633             | 10718               | 17315 | 11.43 | 120    | 127       | 90          |  |

| PolarFire® (MPF300T)        | 6341             | 10529               | 16870 | 5.63  | 207    | 290       | 191         |  |

| PolarFire SoC<br>(MPFS250T) | 6341             | 10529               | 16870 | 6.64  | 203    | 256       | 174         |  |

# **Table of Contents**

| Intr | oductio | on                                                                  | 1  |

|------|---------|---------------------------------------------------------------------|----|

|      | Featu   | ires                                                                | 2  |

|      | Core    | Version                                                             | 2  |

|      | Supp    | orted Families                                                      | 2  |

|      | Devic   | e Utilization and Performance                                       | 2  |

| 1.   | Funct   | ional Description                                                   | 6  |

|      | 1.1.    | Triple Speed MAC                                                    | 6  |

|      | 1.2.    | PAUSE Flow Control                                                  | 6  |

|      | 1.3.    | Jumbo Frame Support                                                 | 7  |

|      | 1.4.    | Inter-Frame-Gap                                                     | 7  |

|      | 1.5.    | Address Detect                                                      | 7  |

|      | 1.6.    | Hash Table Support                                                  | 7  |

|      | 1.7.    | Length Checking and Maximum Length Enforcement                      | 7  |

|      | 1.8.    | Internal Loopback at G/MII                                          |    |

|      | 1.9.    | WoL                                                                 | 8  |

|      | 1.10.   | MDIO Management                                                     | 8  |

|      |         | MAC FIFO                                                            |    |

|      | 1.12.   | Station Address Logic for Frame Filtering                           | 9  |

|      |         | Statistics Counters Logic                                           |    |

|      |         | SGMII/Ten-Bit Interface                                             |    |

|      | 1.15.   | COMMA Alignment Logic                                               | 11 |

| 2.   | Progr   | ammer Guide                                                         | 12 |

|      | 2.1.    | Functional Overview                                                 | 12 |

| 3.   | Regis   | ter Map                                                             | 13 |

|      | 3.1.    | MAC Core Registers                                                  | 13 |

|      | 3.2.    | MAC-FIFO Core Registers                                             | 20 |

|      | 3.3.    | Statistics Counters Core Register                                   | 28 |

|      | 3.4.    | System Registers                                                    |    |

|      | 3.5.    | SGMII/TBI/1000Base-X – Registers (Indirect Addressing through MDIO) | 37 |

| 4.   | Interfa | ace                                                                 | 45 |

|      | 4.1.    | Ports                                                               | 45 |

|      | 4.2.    | Configuration Parameters                                            | 48 |

| 5.   | Tool F  | Flow                                                                | 50 |

|      | 5.1.    | License                                                             | 50 |

|      | 5.2.    | RTL                                                                 | 50 |

|      | 5.3.    | SmartDesign                                                         | 50 |

|      | 5.4.    | Configuring CoreTSE in SmartDesign                                  | 50 |

|      | 5.5.    | Simulation Flows                                                    | 51 |

|      | 5.6.    | Synthesis in Libero SoC                                             | 51 |

|      | 5.7.    | Place-and-Route in Libero SoC                                       | 51 |

| 6.   | Clock   | s and Reset                                                         | 52 |

**User Guide**

|     | 6.1.     | Clocks                          | 52 |

|-----|----------|---------------------------------|----|

|     | 6.2.     | Reset                           | 52 |

| 7.  | Desig    | n Constraints                   | 53 |

|     | 7.1.     | Timing Constraints              | 53 |

| 8.  | Testbe   | ench                            | 55 |

|     | 8.1.     | User Testbench                  | 55 |

| 9.  | Syste    | m Integration                   | 56 |

| 10. | Refere   | ences                           | 57 |

| 11. | Revisi   | ion History                     | 58 |

| Mic | rochip   | FPGA Support                    | 59 |

| The | Micro    | chip Website                    | 59 |

| Pro | duct Cl  | hange Notification Service      | 59 |

| Cus | tomer    | Support                         | 59 |

| Mic | rochip   | Devices Code Protection Feature | 59 |

| Leg | al Noti  | ce                              | 60 |

| Tra | demark   | (8                              | 60 |

| Qua | ality Ma | anagement System                | 61 |

| Woı | rldwide  | Sales and Service               | 62 |

# 1. Functional Description

This section describes the functionality of the CoreTSE.

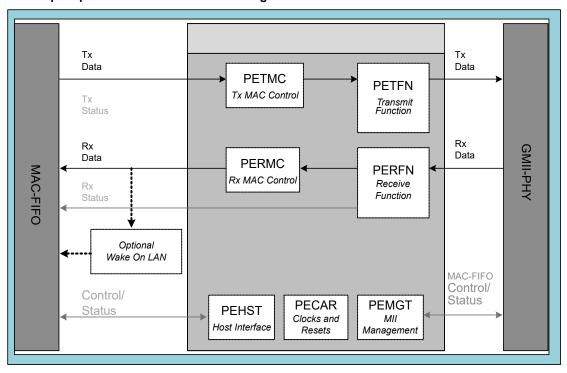

## 1.1 Triple Speed MAC

This core is a full-featured 10/100/1000 Mbps MAC with standard G/MII. The MAC has built in G/MII to TBI converter, which supports 1000 Mbps with TBI. The core is capable of full-duplex operation at 10, 100, or 1000 Mbps and of half duplex operation at 10 and 100 Mbps.

In half-duplex mode, the MAC adheres to the Carrier Sense Multiple Access/Collision Detect Access method as defined in IEEE 802.3 and its several supplements including IEEE 802.3u. In full-duplex mode, the MAC follows IEEE 802.3x, which ignores both carrier and collisions. Following each packet transmission or abortion, a transmit statistics vector is used for statistics collection.

The external PHY device presents packets to the MAC. The MAC scans the preamble searching for the start frame delimiter (SFD). When the SFD is found, the preamble and SFD are stripped and the frame is passed to the system. Following each frame reception, a Receive Statistics Vector is used for frame filtering and statistics collection.

CoreTSE supports PAUSE control frames. This core also includes optional support for Wake-on-LAN (WoL) module. The WoL module detects both IEEE 802.3-compliant unicast frames with a destination address that matches the station address and packets that use AMD's Magic Packet<sup>™</sup> Detection technology. The detection functionality can be enabled or disabled.

Figure 1-1. Triple Speed MAC Functional Block Diagram

### 1.2 PAUSE Flow Control

MAC transmit logic (MACTL) provides native support for PAUSE flow control frames. PAUSE frames are control frames (frames with 0x8808 as the Ether Type) with a particular DA (01-80-c2-00-00-01) and the opcode 0x0001. The FIFO-logic automatically Request-to-Send a PAUSE frame by pulsing transmit-control-request (TCRQ) and provides the pause time value available on control-frame-register (CFPT [15:0]). Pause frame payload contains CFPT and CFEP (Control Frame extended parameter). Once a frame is received and detected as a control frame,

## **Functional Description**

MAC checks for the DA and the Opcode fields. If the DA is either the reserved multicast address used by PAUSE (01-80-c2-00-00-01) or the station's unique address, and the Opcode is 0x0001, then the Control frame is considered to be a PAUSE Control frame.

When a PAUSE Control frame is received:

- The MAC receive logic (MACRL) module indicates the MACTL to pause the stream of data frames and allows

control frames transmission to the link partner. When either a PAUSE frame with a zero-value pause time is

received or the MACRL pause timer expires, MACTL is considered to be unpaused and normal data frames gets

resumed.

- The pause time value is loaded into the PERMC pause timer. This pause timer is a 16-bit down counter that decrements every pause quanta (a speed-independent constant of 64 byte-times). Whenever the pause time counter is nonzero, the MAC is considered to be paused and no data frames are sent.

## 1.3 Jumbo Frame Support

The CoreTSE supports jumbo frames that exceed the 1500 byte maximum of the standard Ethernet frame. When using jumbo frames the amount of idles that are present in the systems reduced and therefore the frequency of clock compensation events are lower. When supporting jumbo frames the clocking tolerance between the transmit clock and the receive clock is required to be 0 ppm to account for the reduction in idles.

The Jumbo frame length transmitted/received by the CoreTSE is according to Maximum Frame Length (0x010) register configuration and supports up to 4000 bytes only.

## 1.4 Inter-Frame-Gap

MACRL provides the capability to filter frames that have less than a certain inter-frame-gap. The standard states that the inter-frame-gap should be 160 bit-times. This includes 96 bits of inter packet gap (IPG), 56 bits of preamble and 8 bits of start frame delimiter (SFD). To protect downstream logic from over-running, MACRL can be programmed with a minimum inter frame gap (IFG) parameter. The second of two back-to-back frames to violate the minimum IFG is dropped.

#### 1.5 Address Detect

MACRL scans the frame and determine its address type. The 48-bit programmed station address is compared to each receive frame's DA. When they match, the unicast address detect (UCAD) is asserted. If the broadcast address is detected, MACRL asserts broadcast address detect (BCAD). If a multicast address is detected, the MAC asserts multicast address detect (MCAD).

### 1.6 Hash Table Support

MACRL supports hash table with up to 128 entries. Seven bits of the Cyclic Redundancy Check (CRC) of the DA are used as the Hash Value (HASHV [6:0]).

#### 1.7 Length Checking and Maximum Length Enforcement

MACRL can optionally compare the length field with the actual length of the data field portion of the frame. This is enabled through the MAC Configuration #2 register. MACRL first determines if the length/type field is a valid length. If so, it is compared with the data field length and any mismatches are updated to the receive statistics.

MACRL can limit the length of receive frames passed to the system. The maximum length is programmed through the Maximum Frame Length register. Frames which exceed this maximum are truncated.

## 1.8 Internal Loopback at G/MII

Asserting the internal loopback enable bit in MAC Configuration #1 register, enables MAC transmit output's looped back to the MAC receive inputs at G/MII interface.

#### 1.9 WoL

The MAC-WoL is based on AMD's Magic Packet Detection technology.

The first step of the detection procedure is to scan the first twelve bytes of the frame, which contain Destination and Station addresses. Magic Packet detection is only carried out when the incoming frame's destination address matches the MAC's station address, or if the frame's destination address is a multicast or broadcast address.

After the first twelve bytes of the frame have matched, core searches for the Magic Packet technology's defined preamble of six continuous aligned bytes with all bits asserted (0xFFh). Following a valid Magic Packet preamble, core immediately expects 16 back-to-back repetitions of the six-byte MAC station address. Failure to achieve this exact pattern by a single byte at any time during the frame resets the circuitry back to the preamble search state.

After successful recognition of the Magic Packet payload or a successful compare of the MAC's station address with the incoming frame's destination address, the Interface STATUS Register (bit field Wake on Lane Detected) is asserted and status bit can only be cleared through assertion of the Wake on Lane Detected Clear bit field of Interface Control register.

# 1.10 MDIO Management

Control and status is provided to and from the PHY through the two-wire MDIO management interface described in IEEE802.3u Clause22.

The MDIO write/read cycles are requested through the APB target. MAC performs a write cycle using the MDIO\_PHYID, register address and 16-bit write data. MAC performs a read cycle using the MDIO\_PHYID register address and updates the sixteen-bit read data into the MDIO Management STATUS Register, which can be read through APB target.

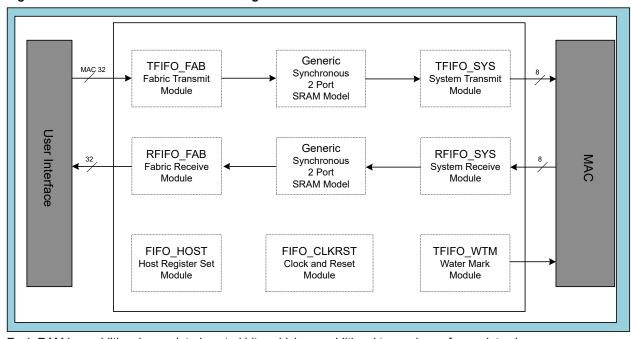

#### 1.11 MAC FIFO

This core provides data queuing for increased throughput and sits between back-end, user-interface logic, and MAC core. The core provides clock-domain crossing, automatic pause frame handshaking, and graceful frame dropping.

The data is buffered between the system-interface and the MAC core by transmit and receive FIFOs. The FIFO size can be configured with PACKET\_SIZE parameter.

Figure 1-2. MAC-FIFO Functional Block Diagram

Each RAM has additional associated control bits, which are additional to maximum frame data size.

Table 1-1. MAC-FIFO RAM Configurations

| PACKET_SIZE       | Transmit RAM     |                                 | Receive RAM      |                                 |

|-------------------|------------------|---------------------------------|------------------|---------------------------------|

| Parameter (Bytes) | RAM Size in Bits | Number of Address bits (TABITS) | RAM Size in Bits | Number of Address bits (RABITS) |

| 256               | 64 x 39          | 6                               | 128 x 36         | 7                               |

| 512               | 128 x 39         | 7                               | 256 x 36         | 8                               |

| 1K                | 256 x 39         | 8                               | 512 x 36         | 9                               |

| 2K                | 512 x 39         | 9                               | 1K x 36          | 10                              |

| 4K                | 1K x 39          | 10                              | 2K x 36          | 11                              |

| 8K                | 2K x 39          | 11                              | 4K x 36          | 12                              |

| 16K               | 4K x 39          | 12                              | 8K x 36          | 13                              |

| 32K               | 8K x 39          | 13                              | 16K x 36         | 14                              |

## 1.12 Station Address Logic for Frame Filtering

This module provides a mechanism to statistically filter frames not intended for this node.

The MAC core performs DA comparison on all the received frames and provides three information signals: UCAD (Perfect DA match), MCAD, and BCAD along with seven most significant bits of the resulting CRC of DA. This information is used to perform a hashing algorithm, compare the result to a programmable hash table and then communicate to the FIFO logic to either delete or store the frame.

The programmability allows the user to assert any bits in a 128 bit hash table that corresponds to the desired Ethernet MAC DA. If the corresponding bit in the table is set, the frame is accepted. In addition, hashing can selectively be performed on unicast addresses or multicast addresses.

## 1.13 Statistics Counters Logic

This module has separate counters, which simply counts or accumulate conditions that occur upon packets transmitted and received. These counters support remote network monitoring (RMON) management information base (MIB) group 1, RMON MIB group 2, RMON MIB group 3, RMON MIB group 9, RMON MIB 2, and the dot 3 Ethernet MIB.

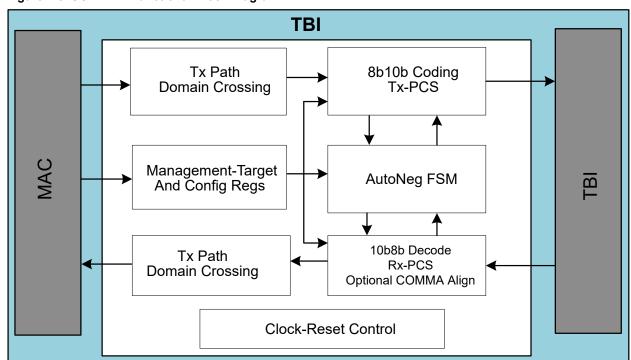

#### 1.14 SGMII/Ten-Bit Interface

This module takes the transmit G/MII data stream, encodes it into 10-bit symbols and presents 10-bit interface data to Transceiver. Packet data replication is used to match data rates for the different modes of the MII to the transmit clock. In the receive direction de-serialized 10-bit symbols are decoded and converted into the receive G/MII signal set. Packet data under sampling is used to match data rates for the different modes of the MII to the TBI receive clock

The design uses transmit, receive, and synchronization state machines as specified in Clause 36 of IEEE 802.3z. Also included auto-negotiation (AN) for 1000BASE-X, which is used to exchange information between the link partners. This module is managed and monitored through the MDIO management interface. The extended set of management registers is provided.

Both the transmit and receive paths leverage the physical coding sub layer and the Auto-negotiation sub-layers of the IEEE 802.3z specification, as contained in Clauses 36 and 37. For complete clock domain isolation of the TBI from the MAC, both transmit and receive elasticity FIFOs are used.

The control information exchanged differs from the IEEE specification. Instead of using the ability advertisement, the PHY sends the control information through its Tx\_config\_Reg [15:0], as listed in Table 1-2. Upon receiving control information, the MAC acknowledges the update of the control information by asserting bit 14 of its Tx\_config\_Reg [15:0].

Figure 1-3. SGMII/TBI Functional Block Diagram

To maintain a constant clock frequency at the PHY interface for all MAC speeds, the MII bus data must be replicated internally to the TBI. Nibble packet data transmitted by a 100 Mbps MAC must be aligned, concatenated, and replicated 10 times. Nibble packet data transmitted by a 10 Mbps MAC must be aligned, concatenated, and replicated 100 times.

Table 1-2. SGMII/TBI Auto-Negotiation Control Information Sent/Received

| Bit     | Tx_config from PHY to MAC        | Tx_config from MAC to PHY |

|---------|----------------------------------|---------------------------|

| 15      | Link:  1: Link up  0: link down  | 0: Reserved               |

| 14      | Reserved for AN ACK.             | 1                         |

| 13      | 0: Reserved                      | 0: Reserved               |

| 12      | Duplex mode: • 1: Full • 0: Half | 0: Reserved               |

| [11:10] | Speed:                           | 0: Reserved               |

| [9:1]   | 0: Reserved                      | 0: Reserved               |

| 0       | 1                                | 1                         |

Packet data received by the TBI through the PHY must be under sampled by a factor of 10 before being sent to a 100 Mbps MAC. Packet data received by the TBI through the PHY must be under sampled by a factor of 100 before being sent to a 10 Mbps MAC. For half-duplex functionality, carrier sense is inferred from RXDV, and collision is derived from the simultaneous assertion of TXEN and RXDV.

## 1.15 COMMA Alignment Logic

The PHY layer includes COMMA alignment logic in the receive path. This logic detects COMMA data and aligns the 10-bit data to the proper word boundary before passing the data to the receive path.

# 2. Programmer Guide

This section has all the information regarding utilization of the core.

#### 2.1 Functional Overview

The MAC Data interface module is interfaced with MAC transmit FIFO for transmit data and MAC receive FIFO for receive data operations. The transmit and receive operations are described in Figure 2-1 and Figure 2-2 respectively.

#### 2.1.1 Transmit Operation

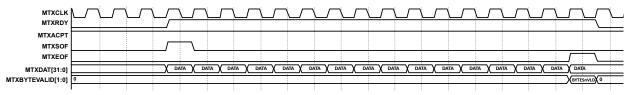

Figure 2-1. Transmit Operation

The MTXDAT(transmit data) word is recorded into MAC transmit FIFO on rising edge of MTXCLK upon the assertion of MTXRDY and MTXACPT and the MTXSOF should be asserted for the first word transfer of the frame. Transmit data stored into MAC transmit FIFO until MTXEOF (end of frame date). MTXBYTEVALID indicates the byte enables of the MTXDAT last word. MTXACPT is asserted when CoreTSE is capable of receiving at least one word from the MAC data path transmit interface. MTXACPT should be monitored for every transmission.

### 2.1.2 Receive Operation

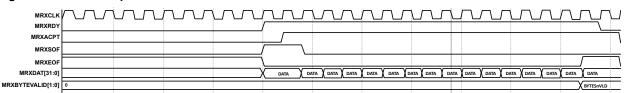

Figure 2-2. Receive Operation

The core asserts the MRXRDY along with MRXSOF and MRXDAT (receive data) and waits for the MRXACPT. MRXDAT word is available on rising edge of MRXCLK from the MAC receive FIFO until MRXEOF (end of frame date). MRXBYTEVALID indicates the byte enables of the MRXDAT last word.

# 3. Register Map

The external APB initiator uses a 32-bit APB target interface for accessing control and status registers.

Table 3-1. Core Register MAP

| Address Offset | Function                                                                                     |

|----------------|----------------------------------------------------------------------------------------------|

| 0x000-0x044    | Access to MAC core registers                                                                 |

| 0x048-0x07C    | Access to FIFO core registers                                                                |

| 0x080-0x1BF    | Access to Statistics Counters core registers 0x080–0x13C are valid addresses                 |

| 0x1C0-0x1FF    | Access to System Registers (SAL and miscellaneous controls) 0x1C0–0x1D4 are valid addresses. |

# 3.1 MAC Core Registers

This section describes the MAC core registers used for the CoreTSE.

Table 3-2. Control/Status Registers

| Address[9:0] | Function                                                                                                                                                                                                                                                       |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x000        | MAC Configuration #1                                                                                                                                                                                                                                           |

|              | [31] (R/W) SOFT RESET: Default 1 Setting this bit puts all modules within the MAC in reset except the APB target interface.                                                                                                                                    |

|              | [30:9] Reserved [8] (R/W) LOOP BACK: Default 0                                                                                                                                                                                                                 |

|              | Setting this bit causes the PETFN MAC Transmit outputs to be looped back to the MAC Receive inputs. Clearing this bit results in normal operation.                                                                                                             |

|              | [7:6] Reserved [5] (R/W) RECEIVE FLOW CONTROL ENABLE: Default 0                                                                                                                                                                                                |

|              | Setting this bit causes the PERFN Receive MAC Control to detect and act on PAUSE Flow Control frames. Clearing this bit causes the Receive MAC Control to ignore PAUSE Flow Control frames.                                                                    |

|              | [4] (R/W) TRANSMIT FLOW CONTROL ENABLE: Default 0 Setting this bit allows the PETMC Transmit MAC Control to send PAUSE Flow Control frames when requested by the system. Clearing this bit prevents the Transmit MAC Control from sending Flow Control frames. |

|              | [3] (RO) SYNCHRONIZED RECEIVE ENABLE: Receive Enable synchronized to the receive stream.                                                                                                                                                                       |

|              | [2] (R/W) RECEIVE ENABLE: Default 0 Setting this bit allows the MAC to receive frames from the PHY. Clearing this bit prevents the reception of frames.                                                                                                        |

|              | [1] (RO) SYNCHRONIZED TRANSMIT ENABLE: Transmit Enable synchronized to the transmit stream.                                                                                                                                                                    |

|              | [0] (R/W) TRANSMIT ENABLE: Default 0 Setting this bit allows the MAC to transmit frames from the system. Clearing this bit prevents the transmission of frames.                                                                                                |

| continued    |                                                                                                                                                                                                                                                                                             |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address[9:0] | Function                                                                                                                                                                                                                                                                                    |

| 0x004        | MAC Configuration #2                                                                                                                                                                                                                                                                        |

|              | [31:16] Reserved<br>[15:12] (R/W) PREAMBLE LENGTH: Default 0x7                                                                                                                                                                                                                              |

|              | This field determines the length of the preamble field of the packet, in bytes. Minimum value supported for this field is 0x3.                                                                                                                                                              |

|              | [11:10] Reserved<br>[9:8] (R/W) INTERFACE MODE: Default 0x10                                                                                                                                                                                                                                |

|              | This field determines the type of MAC interface mode.                                                                                                                                                                                                                                       |

|              | <ul> <li>2'b00: MAC Tx/Rx represents MII 10Mbps interface (Nibble Mode).</li> <li>2'b01: MAC Tx/Rx represents MII 100Mbps interface (Nibble Mode).</li> <li>2'b10: MAC Tx/Rx represents GMII 1000Mbps interface (Byte Mode).</li> <li>2'b11: Reserved.</li> </ul>                           |

|              | [7:6] Reserved [5] (R/W) HUGE FRAME ENABLE: Default 0                                                                                                                                                                                                                                       |

|              | Setting this bit allows frames longer than the MAXIMUM FRAME LENGTH to be transmitted and received. Clear this bit to have the MAC limit the length of frames at the MAXIMUM FRAME LENGTH value. (Maximum Frame Length is set in separate Maximum Frame Length register.)                   |

|              | [4] (R/W) LENGTH FIELD CHECKING: Default 0 Setting this bit causes the MAC to check the frame's length field to ensure it matches the actual data field length. Clear this bit if no length field checking is desired.                                                                      |

|              | [3] Reserved [2] (R/W) PAD/CRC ENABLE: Default 0                                                                                                                                                                                                                                            |

|              | Set this bit to have the MAC pad all short frames and append a CRC to every frame whether or not padding was required. Clear this bit if frames presented to the MAC have a valid length and contain a CRC.                                                                                 |

|              | [1] (R/W) CRC ENABLE: Default 0 Set this bit to have the MAC append a CRC to all frames. Clear this bit if frames presented to the MAC have a valid length and contain a valid CRC. If the PAD/CRC ENABLE Configuration bit or the per-packet PAD/CRC ENABLE is set, CRC ENABLE is ignored. |

|              | [0] (R/W) FULL-DUPLEX: Default 0 Setting this bit configures the MAC to operate in full-duplex mode. Clearing this bit configures the MAC to operate in half-duplex mode only.                                                                                                              |

| continued    | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address[9:0] | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x008        | IPG/IFG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              | [31] Reserved<br>[30:24] (R/W) NON-BACK-TO-BACK INTER-PACKET-GAP PART1 (IPGR1):                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              | This programmable field represents the optional carrier sense window referenced in IEEE 802.3/4.2.3.2.1 Carrier Deference. If a carrier is detected during the timing of IPGR1, the MAC defers to the carrier. If, however, the carrier becomes active after IPGR1, the MAC continues timing IPGR2 and transmits, knowingly causing a collision. This ensures fair access to the medium. The permitted range of values is 0x0 to IPGR2. Default is 0x40 (64d) which follows the two-thirds/one-thirds guideline. |

|              | [23] Reserved [22:16] (R/W) NON-BACK-TO-BACK INTER-PACKET-GAP PART2 (IPGR2):                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              | This programmable field represents the Non-Back-to-Back Inter-Packet-Gap in bit times. Default is 0x60 (96d), which represents the minimum IPG of 96 bits.                                                                                                                                                                                                                                                                                                                                                       |

|              | [15:8] (R/W) MINIMUM IFG ENFORCEMENT: Default 0x50  This programmable field represents the minimum size of IFG to enforce between frames (expressed in bit times). A frame whose IFG is less than that programmed is dropped. The default setting of 0x50 (80d) represents half of the nominal minimum IFG which is 160 bits.                                                                                                                                                                                    |

|              | [7] Reserved<br>[6:0] (R/W) BACK-TO-BACK INTER-PACKET-GAP: Default 0x60                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              | This programmable field represents the IPG between Back-to-Back packets (expressed in bit times). This is the IPG parameter used exclusively in full-duplex mode when two transmit packets are sent back-to-back. Set this field to the desired number of bits. The default setting of 0x60 (96d) represents the minimum IPG of 96 bits. Minimum value supported for this field is 0x28 (40d).                                                                                                                   |

| continued    |                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address[9:0] | Function                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0x00C        | Half-Duplex [31:24] Reserved                                                                                                                                                                                                                                                                                                                                                                                              |

|              | [23:20] (R/W) ALTERNATE BINARY EXPONENTIAL BACKOFF TRUNCATION: Default 0xA                                                                                                                                                                                                                                                                                                                                                |

|              | This field is used when ALTERNATE BINARY EXPONENTIAL BACKOFF ENABLE is set. The value programmed is substituted for the Ethernet standard value of ten.                                                                                                                                                                                                                                                                   |

|              | [19] (R/W) ALTERNATE BINARY EXPONENTIAL BACKOFF ENABLE: Default 0 Setting this bit configures the Tx MAC to use the ALTERNATE BINARY EXPONENTIAL BACKOFF TRUNCATION setting instead of the 802.3 standard tenth collisions. The Standard specifies that any collision after the tenth uses 210-1 as the maximum backoff time. Clearing this bit causes the Tx MAC to follow the standard binary exponential backoff rule. |

|              | [18] (R/W) BACKPRESSURE NO BACKOFF: Default 0 Setting this bit configures the Tx MAC to immediately re-transmit following a collision during back pressure operation. Clearing this bit causes the Tx MAC to follow the binary exponential back off rule.                                                                                                                                                                 |

|              | [17] (R/W) NO BACKOFF: Default 0 Setting this bit configures the Tx MAC to immediately re-transmit following a collision. Clearing this bit causes the Tx MAC to follow the binary exponential back off rule.                                                                                                                                                                                                             |

|              | [16] (R/W) EXCESSIVE DEFER: Default 1 Setting this bit configures the Tx MAC to allow the transmission of a packet that has been excessively deferred. Clearing this bit causes the Tx MAC to abort the transmission of a packet that has been excessively deferred.                                                                                                                                                      |

|              | [15:12] (R/W) RETRANSMISSION MAXIMUM: Default 0xF This is a programmable field specifying the number of retransmission attempts following a collision before aborting the packet due to excessive collisions. The Standard specifies the maximum number of attempts to be 0xF (15d).                                                                                                                                      |

|              | [11:10] Reserved<br>[9:0] (R/W) COLLISION WINDOW: Default 0x37                                                                                                                                                                                                                                                                                                                                                            |

|              | This programmable field represents the slot time or collision window during which collisions might occur in a properly configured network. Since the collision window starts at the beginning of transmission, the preamble and SFD are included. The default of 0x37 (55d) corresponds to the count of frame bytes at the end of the window.                                                                             |

| 0x010        | Maximum Frame Length [31:16] Reserved                                                                                                                                                                                                                                                                                                                                                                                     |

|              | [15:0] (R/W) MAXIMUM FRAME LENGTH: Default 0x07D0 (2000 d)                                                                                                                                                                                                                                                                                                                                                                |

|              | This programmable field sets the maximum frame size in both the transmit and receive directions.                                                                                                                                                                                                                                                                                                                          |

| 0x014        | Control Frame extended parameter (Used for pause frame) [31:16] Reserved                                                                                                                                                                                                                                                                                                                                                  |

|              | [15:0] (R/W) CFEP: Default 0x0000                                                                                                                                                                                                                                                                                                                                                                                         |

|              | This register bits are append as Pause frame payload.                                                                                                                                                                                                                                                                                                                                                                     |

| 0x018        | Control Frame parameter (Used for pause Value)                                                                                                                                                                                                                                                                                                                                                                            |

|              | [31:16] Reserved<br>[15:0] (R/W) CFPT: Default 0xFFFF                                                                                                                                                                                                                                                                                                                                                                     |

|              | This register bits are append as Pause frame payload.                                                                                                                                                                                                                                                                                                                                                                     |

| continued | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01C     | Test Register [31:4] Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | [3] (R/W) MAXIMUM BACKOFF: Default 0                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | Setting this bit causes the MAC to back off for the maximum possible length of time. This test bit is used to predict back off times in Half-Duplex mode.                                                                                                                                                                                                                                                                                                     |

|           | [2] (R/W) REGISTERED TRANSMIT FLOW ENABLE: Default 0                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | Registered Transmit half-duplex Flow Enable.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           | [1] (R/W) TEST PAUSE: Default 0 Setting this bit allows the MAC to be paused through the APB target interface for testing purposes.                                                                                                                                                                                                                                                                                                                           |

|           | [0] (R/W) SHORTCUT SLOT TIME: Default 0 Setting this bit allows the slot time counter to expire regardless of the current count. This bit is for testing purposes only. Upon PAUSE condition frame transmission gets paused until slot time counter reached 'h7e for 1G and 'h3e non 1G modes and it can be overcome by writing 1 to this bit.                                                                                                                |

| 0x020     | MDIO Mgmt: Configuration [31] (R/W) RESET MDIO MGMT: Default 0                                                                                                                                                                                                                                                                                                                                                                                                |

|           | Setting this bit resets MDIO Mgmt. Clearing this bit allows MDIO Mgmt to perform Mgmt read/write cycles as requested via the APB target interface.                                                                                                                                                                                                                                                                                                            |

|           | [30:6] Reserved<br>[5] (R/W) SCAN AUTO INCREMENT: Default 0                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | Setting this bit causes MDIO Mgmt to continually read from a set of PHYs of contiguous address space. The starting address of the PHY is specified by the content of the PHY address field recorded in the MDIO Mgmt Address register. The next PHY to be read is PHY address + 1. The last PHY to be queried in this read sequence is the one residing at address 0x31, after which the read sequence returns to the PHY specified by the PHY address field. |

|           | [4] (R/W) PREAMBLE SUPPRESSION: Default 0 Setting this bit causes MDIO Mgmt to suppress preamble generation and reduce the Mgmt cycle from 64 clocks to 32 clocks. This is in accordance with IEEE 802.3/22.2.4.4.2. Clearing this bit causes MDIO Mgmt to perform Mgmt read/write cycles with the 64 clocks of preamble.                                                                                                                                     |

|           | [2:0] (R/W) MGMT CLOCK SELECT: Default 0x0 This field determines the clock frequency of the Mgmt Clock (MDC). The following list of MDC select encoding determines how to program this field. PCLK is the source clock.                                                                                                                                                                                                                                       |

|           | <ul> <li>3'b000/3'b001: Source clock divided by 4</li> <li>3'b010: Source clock divided by 6</li> <li>3'b011: Source clock divided by 8</li> <li>3'b100: Source clock divided by 10</li> </ul>                                                                                                                                                                                                                                                                |

|           | <ul> <li>3'b101: Source clock divided by 14</li> <li>3'b110: Source clock divided by 20</li> <li>3'b111: Source clock divided by 28</li> </ul>                                                                                                                                                                                                                                                                                                                |

| continued    |                                                                                                                                                                 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address[9:0] | Function                                                                                                                                                        |

| 0x024        | MDIO Mgmt: Command[31:2] Reserved [1] (R/W) SCAN CYCLE: Default 0                                                                                               |

|              | This bit causes MDIO Mgmt to perform Read cycles continuously. This is useful for monitoring Link Fail.                                                         |

|              | [0] (R/W) READ CYCLE: Default 0                                                                                                                                 |

|              | This bit causes MDIO Mgmt to perform a single Read cycle. The Read data is returned in MDIO Mgmt STATUS Register.                                               |

| 0x028        | MDIO Mgmt: Address                                                                                                                                              |

|              | [31:13] Reserved<br>[12:8] (R/W) PHY ADDRESS: Default 0x0                                                                                                       |

|              | This field represents the 5-bit PHY Address field used in Mgmt cycles. Up to 31 PHYs can be addressed.                                                          |

|              | [7:5] Reserved<br>[4:0] (R/W) REGISTER ADDRESS: Default 0x0                                                                                                     |

|              | This field represents the 5-bit Register Address field of Mgmt cycles.                                                                                          |

| 0x02C        | MDIO Mgmt: Control                                                                                                                                              |

|              | [31:16] Reserved<br>[15:0] (WO) MDIO MGMT CONTROL (PHY Control):Default 0x0                                                                                     |

|              | When written, an MDIO Mgmt write cycle is performed using the 16-bit data and the preconfigured PHY and Register addresses from the MDIO Mgmt Address Register. |

| 0x030        | MDIO Mgmt: Status                                                                                                                                               |

|              | [31:16] Reserved<br>[15:0] (RO) MDIO MGMT STATUS (PHY STATUS):                                                                                                  |

|              | Following an MDIO Mgmt Read Cycle, the 16-bit data can be read from this location.                                                                              |

| 0x034        | MDIO Mgmt: Indicators                                                                                                                                           |

|              | [31:3] Reserved [2] (RO) NOT VALID: Default 0                                                                                                                   |

|              | When 1 is returned-indicates MDIO Mgmt Read cycle has not completed and the Read Data is not yet valid.                                                         |

|              | [1] (RO) SCANNING: Default 0 When 1 is returned-indicates a scan operation (continuous MDIO Mgmt Read cycles) is in progress.                                   |

|              | [0] (RO) BUSY: Default 0 When 1 is returned-indicates MDIO Mgmt block is currently performing an MDIO Mgmt Read or Write cycle.                                 |

| continued    | continued                                                                                                                                                                                                                                                                                           |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Address[9:0] | Function                                                                                                                                                                                                                                                                                            |  |

| 0x038        | Interface Control                                                                                                                                                                                                                                                                                   |  |

|              | [31:8] Reserved<br>[7] (W/R) WoL: Unicast match enable: Default 0                                                                                                                                                                                                                                   |  |

|              | Setting this bit configures WoL module to enable Wake On Lane Detected assertion based on Unicast match.                                                                                                                                                                                            |  |

|              | [6] (W/R) WoL: Magic Packet detection enable: Default 0 Setting this bit configures WoL module to enable Wake On Lane Detected assertion based on magic packet detection.                                                                                                                           |  |

|              | [5] (W/R) WoL: Wake On Lane Detected Clear status clear: Default 0 When this bit is asserted, Wake On Lane Detected status is held low. When this bit is cleared, Wake On Lane Detected may become asserted appropriately.                                                                          |  |

|              | [4] (W/R) Stats Counters – Auto clear counters on read: Default 0 Setting this bit enables auto-clear-on-read feature for all the counters.                                                                                                                                                         |  |

|              | [3] (W/R) Stats Counters – Clear All counters: Default 0 Setting this bit clears all the statistics counters.                                                                                                                                                                                       |  |

|              | [2] (W/R) Stats Counters – Module enable: Default 0 Setting this bit enables statistics counter module.                                                                                                                                                                                             |  |

|              | [1:0] Reserved                                                                                                                                                                                                                                                                                      |  |

| 0x03C        | Interface Status                                                                                                                                                                                                                                                                                    |  |

|              | [31:11] Reserved<br>[10] (RO/LH) Wake On Lane Detected:                                                                                                                                                                                                                                             |  |

|              | This bit is only used when the optional WoL module is integrated It is set when the MAC detects a Magic Packet and stays high until it is cleared by the assertion of Wake On Lane Detected Clear. Its reset value is low.                                                                          |  |

|              | [9] (RO/LH) EXCESS DEFER: This bit sets when the MAC excessively defers a transmission. It clears when read. This bit latches high.                                                                                                                                                                 |  |

|              | Excessive Deferred is a condition when the MAC has deferred sending a packet for a time longer than the length of two maximum length frames.                                                                                                                                                        |  |

|              | [8:4] Reserved [3] (RO) LINK FAIL:                                                                                                                                                                                                                                                                  |  |

|              | When read as a 1, the MDIO management module has read the PHY link fail register to be 1. When read as a 0, the MDIO management module has read the PHY link fail register to be 0. Note that for asynchronous host accesses, this bit must be read at least once every scan read cycle of the PHY. |  |

|              | [2:0] Reserved                                                                                                                                                                                                                                                                                      |  |

| 0x040        | Station Address Lower Register-Default 0x0000_0000                                                                                                                                                                                                                                                  |  |

|              | [31:24] (W/R) First octet of the DA in the frame<br>[23:16] (W/R) Second octet of the DA in the frame                                                                                                                                                                                               |  |

|              | [15: 8] (W/R) Third octet of the DA in the frame                                                                                                                                                                                                                                                    |  |

|              | [7: 0] (W/R) Fourth octet of the DA in the frame                                                                                                                                                                                                                                                    |  |

| continued    |                                                                                                                         |

|--------------|-------------------------------------------------------------------------------------------------------------------------|

| Address[9:0] | Function                                                                                                                |

| 0x044        | Station Address Higher Register Default 0x0000_0000                                                                     |

|              | [31:24] (W/R) Fifth octet of the DA in the frame<br>[23:16] (W/R) Sixth octet of the DA in the frame<br>[15:0] Reserved |

# 3.2 MAC-FIFO Core Registers

This section describes the MAC-FIFO Core Registers of the CoreTSE.

## Table 3-3. MAC-FIFO Core Registers

| Address[9:0] | Function                                                                                                                                                                                                                                                 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x048        | MAC-FIFO Configuration Register 0 [31:21] Reserved                                                                                                                                                                                                       |

|              | [20] (RO) Fabric transmit module enable status (ftfenrply): Default 0 When asserted, the Fabric transmit module is enabled. When negated, the Fabric transmit module is disabled. The bit should be polled until it reaches the expected value.          |

|              | [19] (RO) System transmit module enable status (stfenrply): Default 0 When asserted, the System transmit module is enabled. When negated, the System transmit module is disabled. The bit should be polled until it reaches the expected value.          |

|              | [18] (RO) Fabric receive module enable status (frfenrply): Default 0 When asserted, the Fabric receive module is enabled. When negated, the Fabric receive module is disabled. The bit should be polled until it reaches the expected value.             |

|              | [17] (RO) System receive module enable status (srfenrply): Default 0 When asserted, the System receive module is enabled and start of packet has been received. When negated, the System receive module is disabled and end-of-frame signal is received. |

|              | [16] (RO) Water mark module enable status(wtmenrply): Default When asserted, the Water mark module is enabled. When negated, the Water mark module is disabled. The bit should be polled until it reaches the expected value.                            |

|              | [15:13] Reserved [12] (R/W) Fabric transmit module enable request(ftfenreq): Default 0                                                                                                                                                                   |

|              | When asserted, requests enabling of the Fabric transmit module.                                                                                                                                                                                          |

|              | When negated, requests disabling of the Fabric transmit module.                                                                                                                                                                                          |

|              | [11] (R/W) System transmit module enable request (stfenreq): Default 0                                                                                                                                                                                   |

|              | When asserted, requests enabling of the System transmit module.                                                                                                                                                                                          |

|              | When negated, requests disabling of the System transmit module.                                                                                                                                                                                          |

|              | [10] (R/W) Fabric receive module enable request(frfenreq): Default 0                                                                                                                                                                                     |

|              | When asserted, requests enabling of the Fabric receive module.                                                                                                                                                                                           |

|              | [9] (R/W) System receive module enable request(srfenreq): Default 0                                                                                                                                                                                      |

|              | When asserted, requests enabling of the System receive module.                                                                                                                                                                                           |

|              | When negated, requests disabling of the System receive module.                                                                                                                                                                                           |

|              | [8] (R/W) Water mark module enable request(wtmenreq): Default 0                                                                                                                                                                                          |

|              | When asserted, requests enabling of the Water mark module.                                                                                                                                                                                               |