# CorePWM v4.3

Handbook

#### Microsemi Corporation, Mountain View, CA 94043

© 2015 Microsemi Corporation. All rights reserved.

Printed in the United States of America

Part Number: 50200113-7

Release: January 2015 Revision 7

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Microsemi.

Microsemi makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Microsemi assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Microsemi Corporation.

#### Trademarks

Microsemi, IGLOO, Microsemi Fusion, ProASIC, SmartFusion, SmartFusion2, IGLOO2, RTG4, Libero, Pigeon Point and the associated logos are trademarks or registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

# Table of Contents

|   | Introduction       4         Core Overview       4         Core Version       5         Supported Interfaces       5         Utilization and Performance       5             |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Design Description11Functional Blocks11I/O Signals12Register Map16Configuration Example21APB Interface Timing24                                                              |

| 2 | Tool Flows25SmartDesign25Importing into Libero IDE27Simulation Flows27Synthesis in the Libero IDE28Place-and-Route in Libero IDE28                                           |

| 3 | Example Applications       29         General Purpose PWM Application – Temperature Monitor       29         DAC       29                                                    |

| 4 | Software Driver                                                                                                                                                              |

| A | List of Document Changes                                                                                                                                                     |

| В | Product Support34Customer Service34Customer Technical Support Center34Technical Support34Website34Contacting the Customer Technical Support Center34ITAR Technical Support35 |

| С | Index                                                                                                                                                                        |

## Introduction

## Core Overview

### **Intended Use**

CorePWM is a general purpose, multi-channel pulse width modulator (PWM) module for motor control, tone generation, battery charging, heating elements, and more.

In General Purpose PWM mode, duty cycle updates can be performed asynchronously or synchronously, based on parameter selection. In synchronous mode, all channels are updated at the beginning of the PWM period, which is useful for motor control and can be used to keep a constant dead band space between channel waveforms. Asynchronous mode is relevant to applications such as LED control, where synchronous updates are not required. Asynchronous mode lowers the area size, reducing shadow register requirements.

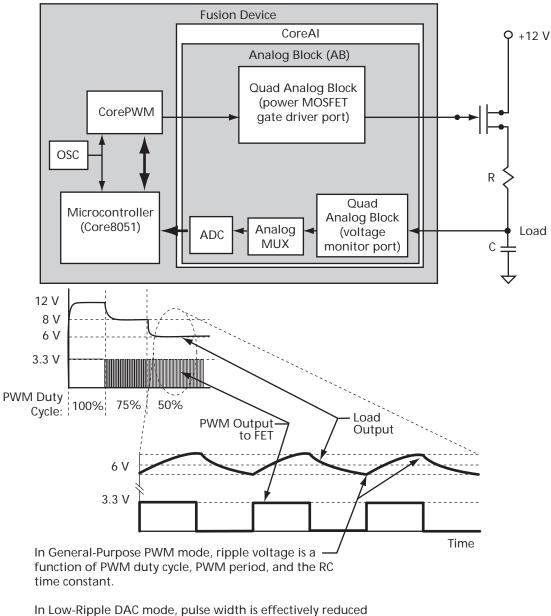

In addition to the general purpose PWM modes, there is a "Low Ripple DAC" mode that creates a minimum period pulse train whose High/Low average is that of the chosen duty cycle. When used with a low-pass filter (such as a simple RC circuit), a DAC can be created with far better bandwidth and ripple performance than a standard PWM algorithm can achieve. This type of DAC is ideally suited for fine tuning of power supply output levels.

CorePWM also provides support for tachometer monitoring of 3- and 4-wire fans. Incoming tachometer data is read by the firmware through the APB interface to calculate fan speed.

#### **Key Features**

- Configuration updates for all channels can be synchronized to the beginning of the PWM period, allowing precise updates and maintaining phase alignments between channels

- · Configurable resolution based on the APB bus width

- · Low-cost PWM solution with up to 16 separate PWM digital outputs, configurable via a register interface

- For DAC applications: Optional, per-channel Low Ripple DAC mode, allowing for greater resolution output of a given filter

- Low-cost TACHOMETER solution with up to 16 separate TACH digital inputs, configurable via a register interface

- All PWM outputs are double-edge-controlled

- · Per-channel fixed register option for lower tile count

- · Edge control based on a configurable PWM period with prescaler value and 0% to 100% duty cycle capability

- · Set High, set Low, and Toggle Edge-Control modes

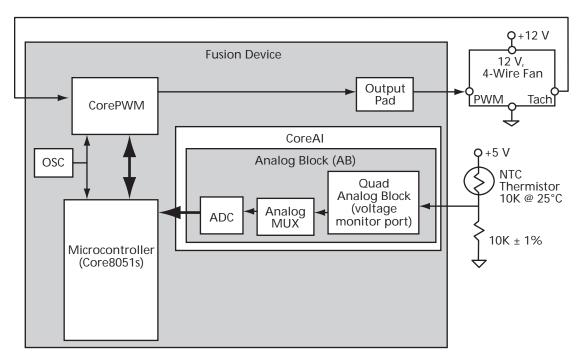

- Can be programmed on-the-fly from a microcontroller, such as Core8051s, CoreABC, or the Fusion backbone

- · Can be used to perform open or closed-loop margining of power supplies

CorePWM v4.3

## Supported Families

- IGLOO®/e

- ProASIC®3/E/L

- Fusion

- ProASIC<sup>PLUS®</sup>

- Axcelerator®

- RTAX-S

- RTAX-DSP

- SmartFusion<sup>®</sup>

- SmartFusion®2

- IGLOO®2

- RTG4™

## Core Version

This handbook supports CorePWM version 4.3.

## Supported Interfaces

CorePWM is available with an APB interface, which is described in the "APB Interface Timing" section on page 24.

## Utilization and Performance

CorePWM has been implemented in several of Microsemi's device families. A summary of various implementation data is listed in the following tables (using standard speed grades).

As shown in Table 1 through Table 8 on page 10, it is recommended to fix all registers that are not used, via parameters, to ensure optimal synthesis tile reduction.

| Family                  | Tiles      |               |       | Utilization |       | Performance |

|-------------------------|------------|---------------|-------|-------------|-------|-------------|

| ranniy                  | Sequential | Combinatorial | Total | Device      | Total | (MHz)       |

| IGLOO/e                 | 20         | 96            | 116   | AGLE600     | 1.0%  | 72          |

| ProASIC3/E              | 20         | 76            | 96    | A3P250      | 2.0%  | 96          |

| Fusion                  | 20         | 76            | 96    | AFS600      | 1.0%  | 101         |

| ProASIC <sup>PLUS</sup> | 20         | 102           | 122   | APA300      | 1.0%  | 101         |

| Axcelerator             | 20         | 31            | 51    | AX250       | 1.0%  | 252         |

| RTAX-S                  | 20         | 31            | 51    | RTAX250S    | 1.0%  | 223         |

| SmartFusion             | 20         | 78            | 98    | A2F500M3G   | 0.85% | 180         |

Table 1 · CorePWM Device Utilization and Performance (one 8-bit DAC channel configuration)

Note: Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics were set as follows: PWM\_NUM = 1, APB\_DWIDTH = 8; DAC\_MODE1 = 1 (DAC mode), FIXED\_PRESCALE\_EN = 1, FIXED\_PRESCALE = 0, FIXED\_PERIOD\_EN = 1, FIXED\_PERIOD = 1, SHADOW\_REG\_EN1 = 0.

Introduction

| Table 1 · CorePWM Device Utilization and Performance    | (and Q hit DAC | abannal configuration) (continued) |

|---------------------------------------------------------|----------------|------------------------------------|

| Table 1 · ColeP with Device Utilization and Performance | tone o-bit DAC | channel configuration) (continued) |

|                                                         |                |                                    |

| SmartFusion2 | 20 | 30 | 50 | M2S150T  | 0.03% | 450 |

|--------------|----|----|----|----------|-------|-----|

| IGLOO2       | 20 | 30 | 50 | M2GL150T | 0.03% | 450 |

| RTG4         | 20 | 40 | 60 | RT4G150  | 0.04% | 300 |

Note: Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics were set as follows: PWM\_NUM = 1, APB\_DWIDTH = 8; DAC\_MODE1 = 1 (DAC mode), FIXED\_PRESCALE\_EN = 1, FIXED\_PRESCALE = 0, FIXED\_PERIOD\_EN = 1, FIXED\_PERIOD = 1, SHADOW\_REG\_EN1 = 0.

| Family                  | Tiles      |               |       | Utilization |       | Performance |

|-------------------------|------------|---------------|-------|-------------|-------|-------------|

| Family                  | Sequential | Combinatorial | Total | Device      | Total | (MHz)       |

| IGLOO/e                 | 54         | 147           | 201   | AGLE600V2   | 2.0%  | 59          |

| ProASIC3/E              | 54         | 111           | 165   | A3P250      | 3.0%  | 85          |

| Fusion                  | 54         | 111           | 165   | AFS600      | 1.0%  | 94          |

| ProASIC <sup>PLUS</sup> | 55         | 209           | 264   | APA200      | 3.0%  | 74          |

| Axcelerator             | 57         | 53            | 110   | AX250       | 2.0%  | 210         |

| RTAX-S                  | 57         | 53            | 110   | RTAX250S    | 1.0%  | 176         |

| SmartFusion             | 86         | 140           | 226   | A2F500M3G   | 2.0%  | 132         |

| SmartFusion2            | 53         | 68            | 121   | M2S150T     | 0.09% | 245         |

| IGLOO2                  | 53         | 68            | 121   | M2GL150T    | 0.09% | 245         |

| RTG4                    | 69         | 75            | 144   | RT4G150     | 0.1%  | 227         |

Table 2 · CorePWM Device Utilization and Performance

(one 16-bit DAC channel configuration)

Note: Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics were set as follows: PWM\_NUM = 1, APB\_DWIDTH = 16; DAC\_MODE1 = 1 (DAC mode), FIXED\_PRESCALE\_EN = 1, FIXED\_PRESCALE = 0, FIXED\_PERIOD\_EN = 1, FIXED\_PERIOD = 1, SHADOW\_REG\_EN1 = 1.

Table 3 · CorePWM Device Utilization and Performance (one 8-bit general purpose PWM channel configuration)

| Family     | Tiles      |               |       | Utilizatio | Performance |       |

|------------|------------|---------------|-------|------------|-------------|-------|

| 1 anni y   | Sequential | Combinatorial | Total | Device     | Total       | (MHz) |

| IGLOO/e    | 15         | 55            | 70    | AGLE600V2  | 1.0%        | 82    |

| ProASIC3/E | 15         | 55            | 70    | A3P250     | 1.0%        | 130   |

Note: Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics were set as follows: PWM\_NUM = 1, APB\_DWIDTH = 8; DAC\_MODE1 = 0 (general purpose PWM mode), FIXED\_PRESCALE\_EN = 1, FIXED\_PRESCALE = 0, FIXED\_PERIOD\_EN = 1, FIXED\_PERIOD = 8, FIXED\_PWM\_POS\_EN1 = 1, FIXED\_PWM\_POSEDGE1 = 0, FIXED\_PWM\_NEG\_EN1 = 0, FIXED\_PWM\_NEGEDGE1 = 0, SHADOW\_REG\_EN1 = 0

| Fusion                  | 15 | 55 | 70 | AFS600    | 1.0%  | 144 |

|-------------------------|----|----|----|-----------|-------|-----|

| ProASIC <sup>PLUS</sup> | 15 | 58 | 73 | APA300    | 1.0%  | 141 |

| Axcelerator             | 16 | 40 | 56 | AX250     | 1.0%  | 181 |

| RTAX-S                  | 16 | 40 | 56 | RTAX250S  | 1.0%  | 187 |

| SmartFusion             | 15 | 60 | 75 | A2F500M3G | 0.65% | 211 |

| SmartFusion2            | 23 | 45 | 68 | M2S150T   | 0.05% | 319 |

| IGLOO2                  | 23 | 45 | 68 | M2GL150T  | 0.05% | 319 |

| RTG4                    | 21 | 58 | 79 | RT4G150   | 0.05% | 238 |

## Table 3 · CorePWM Device Utilization and Performance (one 8-bit general purpose PWM channel configuration) (continued)

Note: Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics were set as follows: PWM\_NUM = 1, APB\_DWIDTH = 8; DAC\_MODE1 = 0 (general purpose PWM mode), FIXED\_PRESCALE\_EN = 1, FIXED\_PRESCALE = 0, FIXED\_PERIOD\_EN = 1, FIXED\_PERIOD = 8, FIXED\_PWM\_POS\_EN1 = 1, FIXED\_PWM\_POSEDGE1 = 0, FIXED\_PWM\_NEG\_EN1 = 0, FIXED\_PWM\_NEGEDGE1 = 0, SHADOW\_REG\_EN1 = 0

Table 4 · CorePWM Device Utilization and Performance (one 16-bit general purpose PWM channel configuration)

| Family                  | Tiles      |               |       | Utilization |       | Performance |

|-------------------------|------------|---------------|-------|-------------|-------|-------------|

| T anny                  | Sequential | Combinatorial | Total | Device      | Total | (MHz)       |

| IGLOO/e                 | 91         | 272           | 363   | AGLE600V2   | 3.0%  | 46          |

| ProASIC3/E              | 91         | 275           | 366   | A3P250      | 6.0%  | 72          |

| Fusion                  | 91         | 275           | 366   | AFS600      | 3.0%  | 79          |

| ProASIC <sup>PLUS</sup> | 127        | 482           | 609   | APA300      | 6.0%  | 59          |

| Axcelerator             | 93         | 145           | 238   | AX250       | 6.0%  | 110         |

| RTAX-S                  | 93         | 145           | 238   | RTAX250S    | 6.0%  | 88          |

| SmartFusion             | 90         | 324           | 414   | A2F500M3G   | 3.6%  | 110         |

| SmartFusion2            | 100        | 150           | 350   | M2S150T     | 0.17% | 170         |

| IGLOO2                  | 100        | 150           | 350   | M2GL150T    | 0.17% | 170         |

| RTG4                    | 134        | 166           | 300   | RT4G150     | 0.2%  | 182         |

Note: Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics were set as follows: PWM\_NUM = 1, APB\_DWIDTH = 16; DAC\_MODE1 = 0 (General Purpose PWM mode); SHADOW\_REG\_EN1 = 1, FIXED\_PRESCALE\_EN = 1, FIXED\_PRESCALE = 64.

| Family                  |            | Tiles         |       | Utilizati |       |                      |

|-------------------------|------------|---------------|-------|-----------|-------|----------------------|

|                         | Sequential | Combinatorial | Total | Device    | Total | Performance<br>(MHz) |

| IGLOO/e                 | 58         | 208           | 266   | AGLE600V2 | 2.0%  | 76                   |

| ProASIC3/E              | 58         | 150           | 208   | A3P250    | 3.0%  | 101                  |

| Fusion                  | 58         | 150           | 208   | AFS600    | 2.0%  | 109                  |

| ProASIC <sup>PLUS</sup> | 58         | 280           | 338   | APA300    | 4.0%  | 101                  |

| Axcelerator             | 58         | 66            | 124   | AX250     | 2.0%  | 250                  |

| RTAX-S                  | 58         | 66            | 124   | RTAX250S  | 2.0%  | 217                  |

| SmartFusion             | 66         | 159           | 225   | A2F500M3G | 2.0%  | 157                  |

| SmartFusion2            | 66         | 72            | 138   | M2S150T   | 0.1%  | 467                  |

| IGLOO2                  | 66         | 72            | 138   | M2GL150T  | 0.1%  | 467                  |

| RTG4                    | 66         | 77            | 143   | RT4G150   | 0.09% | 300                  |

Table 5 · CorePWM Device Utilization and Performance (8-bit multiple-output configuration example: 3 DAC mode outputs without shadow update register)

Note: Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics were set as follows: PWM\_NUM = 3, APB\_DWIDTH = 8; DAC\_MODE1, DAC\_MODE2, and DAC\_MODE3 = 1 (DAC Mode) FIXED\_PERIOD\_EN = 1, FIXED\_PERIOD = 1, FIXED\_PRESCALE\_EN = 1, FIXED\_PRESCALE = 0, SHADOW\_REG\_EN1 = 0, SHADOW\_REG\_EN2 = 0, SHADOW\_REG\_EN3 = 0.

| Table 6 · CorePWM Device Utilization and Performance (12-bit multiple-output configuration example: 3 DAC mode |

|----------------------------------------------------------------------------------------------------------------|

| outputs, 3 general purpose PWM mode outputs)                                                                   |

| Family                  | Tiles      |               |       | Utilization |       | Performance |

|-------------------------|------------|---------------|-------|-------------|-------|-------------|

| Failiny                 | Sequential | Combinatorial | Total | Device      | Total | (MHz)       |

| IGLOO/e                 | 212        | 723           | 935   | AGLE600V2   | 7.0%  | 45          |

| ProASIC3/E              | 212        | 694           | 906   | A3P250      | 15.0% | 74          |

| Fusion                  | 212        | 694           | 906   | AFS600      | 7.0%  | 82          |

| ProASIC <sup>PLUS</sup> | 229        | 1054          | 1,283 | APA300      | 16.0% | 67          |

| Axcelerator             | 216        | 307           | 523   | AX250       | 12.0% | 103         |

| RTAX-S                  | 216        | 307           | 523   | RTAX250S    | 12.0% | 87          |

| SmartFusion             | 148        | 396           | 552   | A2F500M3G   | 4.8%  | 132         |

Note: Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics were set as follows: PWM\_NUM = 6, APB\_DWIDTH = 16; DAC\_MODE1, DAC\_MODE2, and DAC\_MODE3 = 1 (DAC mode), DAC\_MODE4, DAC\_MODE5, and DAC\_MODE6 = 0 (general purpose PWM mode), FIXED\_PRESCALE\_EN = 1, FIXED\_PRESCALE = 8, SHADOW\_REG\_EN1 = 0, SHADOW\_REG\_EN2 = 0, SHADOW\_REG\_EN3 = 0, SHADOW\_REG\_EN3 = 0, SHADOW\_REG\_EN4 = 0, SHADOW\_REG\_EN5 = 0, SHADOW\_REG\_EN6 = 0,.

| Family       | Tiles      |               |       | Utilizati | Performance |       |

|--------------|------------|---------------|-------|-----------|-------------|-------|

| T annry      | Sequential | Combinatorial | Total | Device    | Total       | (MHz) |

| SmartFusion2 | 176        | 274           | 450   | M2S150T   | 0.31%       | 215   |

| IGLOO2       | 176        | 274           | 450   | M2GL150T  | 0.31%       | 215   |

| RTG4         | 254        | 339           | 593   | RT4G150   | 0.39%       | 114   |

Table 6 · CorePWM Device Utilization and Performance (12-bit multiple-output configuration example: 3 DAC mode outputs, 3 general purpose PWM mode outputs) (continued)

Note: Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics were set as follows: PWM\_NUM = 6, APB\_DWIDTH = 16; DAC\_MODE1, DAC\_MODE2, and DAC\_MODE3 = 1 (DAC mode), DAC\_MODE4, DAC\_MODE5, and DAC\_MODE6 = 0 (general purpose PWM mode), FIXED\_PRESCALE\_EN = 1, FIXED\_PRESCALE = 8, SHADOW\_REG\_EN1 = 0, SHADOW\_REG\_EN2 = 0, SHADOW\_REG\_EN3 = 0, SHADOW\_REG\_EN3 = 0, SHADOW\_REG\_EN4 = 0, SHADOW\_REG\_EN5 = 0, SHADOW\_REG\_EN6 = 0,.

| Table 7 · CorePWM Device Utilization and Performance (one 16-bit general purpose PWM channel and one TACH input |

|-----------------------------------------------------------------------------------------------------------------|

| configuration)                                                                                                  |

| Family                  |            | Tiles         |       | Utilizati | on    | Performance |

|-------------------------|------------|---------------|-------|-----------|-------|-------------|

| Fainity                 | Sequential | Combinatorial | Total | Device    | Total | (MHz)       |

| IGLOO/e                 | 314        | 768           | 082   | AGLE600V2 | 8.0%  | 47          |

| ProASIC3/E              | 314        | 768           | 082   | A3P250    | 18.0% | 75          |

| Fusion                  | 314        | 768           | 1,082 | AF600     | 8.0%  | 83          |

| ProASIC <sup>PLUS</sup> | 328        | 1,043         | 1,371 | APA300    | 17.0% | 70          |

| Axcelerator             | 319        | 483           | 802   | AX250     | 19.0% | 103         |

| RTAX-S                  | 319        | 483           | 802   | RTAX250S  | 19.0% | 87          |

| SmartFusion             | 197        | 613           | 810   | A2F500M3G | 7.1%  | 115         |

| SmartFusion2            | 252        | 416           | 668   | M2S150T   | 0.45% | 137         |

| IGLOO2                  | 252        | 416           | 668   | M2GL150T  | 0.45% | 137         |

| RTG4                    | 329        | 436           | 765   | RT4G150   | 0.51% | 164         |

Note: Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics were set as follows: CONFIG\_MODE = 1, PWM\_NUM=3, TACH\_NUM=3,APB\_DWIDTH=16; DAC\_MODE1=0 (General Purpose PWM mode), FIXED\_PRESCALE\_EN=1, FIXED\_PRESCALE=8, FIXED\_PERIOD\_EN=0, FIXED\_PWM\_POS\_EN1=1, FIXED\_PWM\_POSEDGE1=0, FIXED\_PWM\_NEG\_EN1=0, FIXED\_PWM\_NEGEDGE1=0, SHADOW\_REG\_EN1=0, FIXED\_PWM\_POS\_EN2=1, FIXED\_PWM\_POSEDGE2=0, FIXED\_PWM\_NEG\_EN2=0, FIXED\_PWM\_NEGEDGE2=0, SHADOW\_REG\_EN2=0, FIXED\_PWM\_NEG\_EN3=1, FIXED\_PWM\_POSEDGE3=0, FIXED\_PWM\_NEG\_EN3=0, FIXED\_PWM\_NEGEDGE3=0, SHADOW\_REG\_EN3=0

#### Introduction

| Family                  |            | Tiles         |       | Utilizati | on    | Performance |

|-------------------------|------------|---------------|-------|-----------|-------|-------------|

| Family                  | Sequential | Combinatorial | Total | Device    | Total | (MHz)       |

| IGLOO/e                 | 207        | 389           | 596   | AGLE600V2 | 4.0%  | 52          |

| ProASIC3/E              | 207        | 383           | 590   | A3P250    | 10.0% | 89          |

| Fusion                  | 207        | 383           | 590   | AF600     | 4.0%  | 98          |

| ProASIC <sup>PLUS</sup> | 207        | 506           | 713   | APA300    | 9.0%  | 92          |

| Axcelerator             | 209        | 269           | 478   | AX250     | 5%    | 114         |

| RTAX-S                  | 209        | 269           | 478   | RTAX250S  | 11%   | 101         |

| SmartFusion             | 204        | 469           | 673   | A2F500M3G | 5.8%  | 132         |

| SmartFusion2            | 156        | 248           | 404   | M2S150T   | 0.28  | 210         |

| IGLOO2                  | 156        | 248           | 404   | M2GL150T  | 0.28  | 210         |

| RTG4                    | 204        | 243           | 447   | RT4G150   | 0.29% | 172         |

Table 8 · CorePWM Device Utilization and Performance (one TACH input configuration with 16-bit APB data width)

*Note:* Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics were set as follows: CONFIG\_MODE = 2, TACH\_NUM=3, APB\_DWIDTH=16.

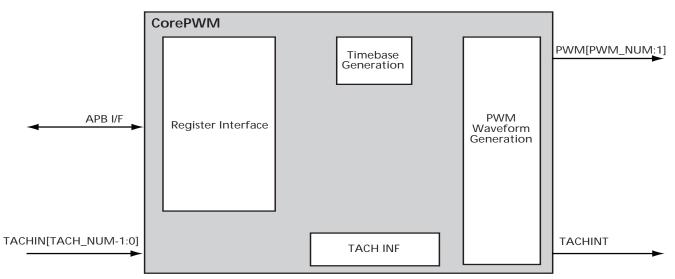

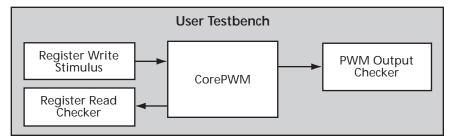

## Functional Blocks

The CorePWM (pulse width modulation) macro generates up to 16 general purpose PWM signals, as shown in Figure 1-1. CorePWM includes a Register Interface block, Timebase Generation block, TACK INF block, and PWM Generation block.

Figure 1-1 · CorePWM Block Diagram

The **Register Interface** block connects to an APB bus for PWM register configuration and updating. Descriptions for all registers are given in Table 1-3 on page 16. A Shadow Register may be used so that PWM waveform updates occur only at the beginning of a PWM period. A shadow register holds all values and writes them when the SYNC\_UPDATE register is set to 1. In other words, for all channel synchronous updates, write a "1" to the SYNC\_UPDATE register after writing to all the channel registers.

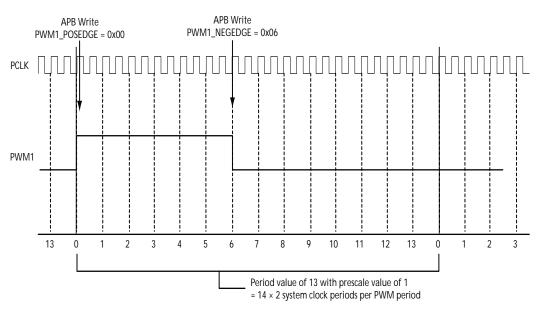

The **Timebase Generation** block accepts PRESCALE and PERIOD register values and produces a PERIOD count. The number of system clocks between PERIOD counts is equal to the PRESCALE value.

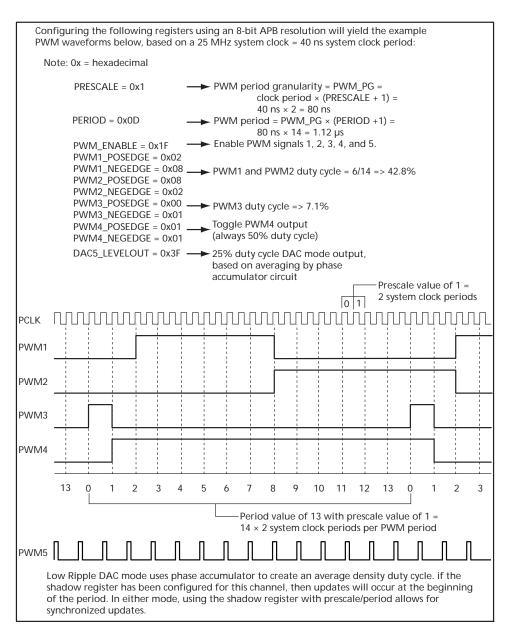

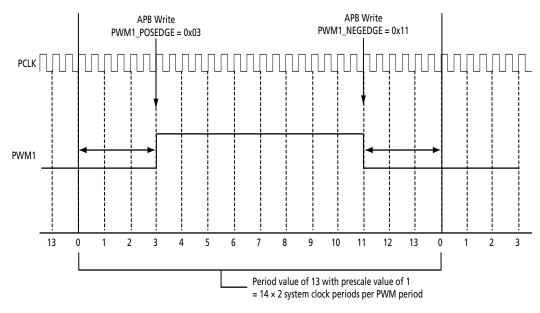

The PWM Waveform Generation block has two modes:

General Purpose PWM mode takes input Period\_cnt counter values and compares them with the register values for all the PWM positive and negative edge locations. When a comparison is met, each respective output waveform is set to the correct high/low/toggle value. An example General Purpose PWM waveform configuration is demonstrated in Figure 1-3 on page 21. The example explains the relationship between the Prescale and Period register values, and how to configure the PWM waveforms with a given Prescale/Period timebase.

Low Ripple DAC mode is intended to drive a low-pass filter, typically a single-pole RC filter. Narrow pulses of constant width are spread evenly over time such that the average voltage is equal to the duty cycle. The output of the filter is then a DC voltage directly proportional to the duty cycle. This type of pulse train allows for much lower ripple at the output of the filter, and benefits from either higher bandwidth and/or smaller R and C values.

In the Tach interface module, the width of the decrementing counter is configured to 16 bits. The Tach interface module is used to measure the period of the TACHIN[x] signal by measuring between two successive positive or negative edges of TACHIN[x]. The measured value will be stored in the corresponding input's TACHPULSEDUR register. The measured value will be read by the firmware through the APB interface. The access to the control and status registers of the Tach interface module is through the APB interface. The stored value in TACHPULSEDUR will correspond to the count for half of a revolution of a four pole fan. When determining the speed for other than four pole fans, the algorithm

that converts the counter value to RPMs must be adjusted by the firmware. TACH INF supports 16- and 32-bit APB interface, but it does not support 8-bit interfaces.

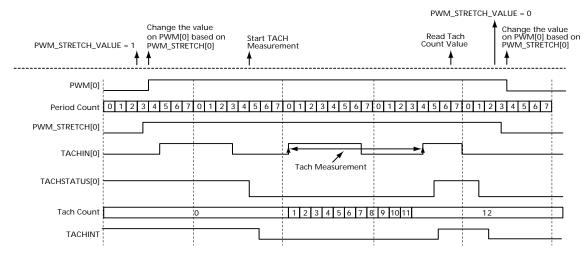

To accurately measure the speed of 3-wire fans, you must turn on the fan periodically and long enough to get a complete tach measurement, often referred to as PWM pulse stretching. The PWM\_STRETCH register allows you to set the desired PWMx signals to the level specified by PWM\_STRETCH\_VALUE. The following algorithm can be used to measure the speed of 3-wire fans. This algorithm assumes that the TACHMODEy bit is set to '1' (one-shot mode):

- Software enables pulse stretching by writing a '1' to PWM\_STRETCHx, which forces PWMx to PWM\_STRETCH\_VALUEx. This requirement is not enforced by the hardware.

- Software can add a delay to ensure the fan tachometer circuitry is operational before enabling fan speed measurement.

- Software clears the TACHSTATUSy bit, enabling a one-time Tach measurement on the input signal TACHINy corresponding to one of the fans controlled by PWMx

- Software receives an interrupt and verifies that the Tach measurement for TACHINy has been completed (via TACHSTATUSy bit)

- Software disables pulse stretching by writing a '0' to PWM\_STRETCHx.

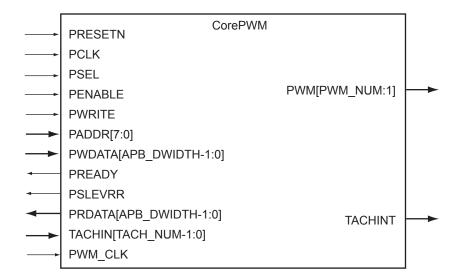

## I/O Signals

The port signals for the CorePWM macro are defined in Table 1-1 on page 13 and illustrated in Figure 1-2. All signals are either Input (input only) or Output (output only).

Figure 1-2 · CorePWM I/O Signal Diagram

| Name                    | Туре   | Description                                                                                                                                                                                          |  |  |  |

|-------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| System Signals          |        |                                                                                                                                                                                                      |  |  |  |

| PRESETN                 | Input  | Active low asynchronous reset                                                                                                                                                                        |  |  |  |

| PCLK                    | Input  | System clock – all operations and status shall be synchronous to the rising edge of this clock signal                                                                                                |  |  |  |

| Microcontroller Signals |        |                                                                                                                                                                                                      |  |  |  |

| PSEL                    | Input  | Select line for CorePWM                                                                                                                                                                              |  |  |  |

| PENABLE                 | Input  | Read output enable                                                                                                                                                                                   |  |  |  |

| PWRITE                  | Input  | Write enable                                                                                                                                                                                         |  |  |  |

| PADDR[7:0]              | Input  | Register address                                                                                                                                                                                     |  |  |  |

| PWDATA[APB_DWIDTH-1:0]  | Input  | Write address/data input                                                                                                                                                                             |  |  |  |

| PREADY                  | Output | Ready signal, tied High                                                                                                                                                                              |  |  |  |

| PSLVERR                 | Output | Transfer error signal, tied Low                                                                                                                                                                      |  |  |  |

| PRDATA[APB_DWIDTH-1:0]  | Output | Read data output                                                                                                                                                                                     |  |  |  |

| PWM Signals             |        |                                                                                                                                                                                                      |  |  |  |

| PWM[PWM_NUM:1]          | Output | Pulse width modulation output                                                                                                                                                                        |  |  |  |

| TACH Signals            |        |                                                                                                                                                                                                      |  |  |  |

| TACHIN[TACH_NUM -1:0]   | Input  | TACH input                                                                                                                                                                                           |  |  |  |

| TACHINT                 | Output | Interrupt output for the tachometer. This signal indicates a TACHSTATUS register bit has been set to one.<br>The polarity of this signal is controlled by the TACHINT_ACT_LEVEL configurable option. |  |  |  |

| PWM_CLK                 | Input  | PWM clock - This clock used if the required frequency for PWM generation is greater/less than PCLK. This signal is only enabled when SEPERATE_PWM_CLK = 1                                            |  |  |  |

Table 1-1 · CorePWM I/O Signal Descriptions

Note: All signals active-High (logic 1) unless otherwise noted.

## Verilog/VHDL Parameters

CorePWM has parameters (Verilog) and generics (VHDL) for configuring the RTL code, described in Table 1-2. All parameters and generics are integer types.

| Name              | Description                                                                                                                                                                                           |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | Selects the Target family. Must be set to match the supported FPGA family:                                                                                                                            |

|                   | 11 - Axcelerator                                                                                                                                                                                      |

|                   | 12 - RTAX-S                                                                                                                                                                                           |

|                   | 14 - ProASICPLUS                                                                                                                                                                                      |

|                   | 15 - ProASIC3                                                                                                                                                                                         |

|                   | 16 - ProASIC3E                                                                                                                                                                                        |

| TA MILL X7        | 17 - Fusion                                                                                                                                                                                           |

| FAMILY            | 18 - SmartFusion                                                                                                                                                                                      |

|                   | 19 - SmartFusion2                                                                                                                                                                                     |

|                   | 20 - IGLOO                                                                                                                                                                                            |

|                   | 21 - IGLOOe                                                                                                                                                                                           |

|                   | 22 - ProASIC3L                                                                                                                                                                                        |

|                   | 24 - IGLOO2                                                                                                                                                                                           |

|                   | 25 - RTG4                                                                                                                                                                                             |

|                   | When 0, supports PWM only (legacy with dead banding support)                                                                                                                                          |

| CONFIG_MODE       | When 1, supports both PWM and TACH                                                                                                                                                                    |

|                   | When 2, supports TACH only                                                                                                                                                                            |

| PWM_NUM           | Number of PWM outputs from 1 to 16. This parameter is used only when CONFIG_MODE is set to 0 or 1.                                                                                                    |

| APB_DWIDTH        | PWM resolution and APB bus width from 8 to 32. This parameter must be set to either 16 or 32 when CONFIG_MODE is either 1 or 2.                                                                       |

| FIXED_PRESCALE_EN | Fixed Prescale Enable. FIXED_PRESCALE_EN hardwires the register, disallowing APB write-access, and reducing tile count. This parameter is used only when CONFIG_MODE set to 0 or 1.                   |

| FIXED_PRESCALE    | Hardwired PRESCALE[APB_DWIDTH -1:0] register value. This parameter is used only when CONFIG_MODE set to 0 or 1.                                                                                       |

| FIXED_PERIOD_EN   | Fixed Period Enable. FIXED_PERIOD_EN hardwires the register, disallowing APB write-access, and reducing tile count. This parameter is used only when CONFIG_MODE set to 0 or 1.                       |

| FIXED_PERIOD      | Hardwired PERIOD[APB_DWIDTH -1:0] register value. This parameter is used only when CONFIG_MODE set to 0 or 1.                                                                                         |

| SHADOW_REG_ENx    | Shadow Register Enable. Synchronizes all register modification changes to the beginning of the PWM cycle; that is, when PERIOD Count = 0. This parameter is used only when CONFIG_MODE set to 0 or 1. |

|                   | DAC mode. 1 = Low ripple DAC mode; 0 = General purpose PWM mode.                                                                                                                                      |

| DAC_MODE <i>x</i> | Note: x refers to each channel, from 1 to 16.                                                                                                                                                         |

|                   | This parameter is used only when CONFIG_MODE set to 0 or 1.                                                                                                                                           |

Table 1-2 · CorePWM Parameters/Generics Descriptions

CorePWM v4.3

| Table 1-2         CorePWM Parameters/Generics Descriptions (continued) |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

|                                                   | Fixed per channel Positive Edge Enable.                                                                                                                                                                                                                                                                         |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                   | <i>Note:</i> x refers to each channel, from 1 to 16. FIXED_PWM_POS_ENx hardwires the register, disallowing APB write-access, and reducing tile count.                                                                                                                                                           |

| FIXED_PWM_POS_ENx                                 | In a typical PWM application, either the FIXED_PWM_POS_ENx or the FIXED_PWM_NEG_ENx could be set if one of those edges do not need to be software controlled with APB write-accesses. Fixing both edges would result in static output.                                                                          |

|                                                   | This parameter is used only when CONFIG_MODE set to 0 or 1.                                                                                                                                                                                                                                                     |

|                                                   | Hardwired POSEDGE[APB_DWIDTH -1:0] register value.                                                                                                                                                                                                                                                              |

| FIXED_PWM_POSEDGEx                                | Note: x refers to each channel, from 1 to 16.                                                                                                                                                                                                                                                                   |

|                                                   | This parameter is used only when CONFIG_MODE set to 0 or 1.                                                                                                                                                                                                                                                     |

|                                                   | Fixed per channel Negative Edge Enable.                                                                                                                                                                                                                                                                         |

|                                                   | <i>Note: x</i> refers to each channel, from 1 to 16. FIXED_PWM_NEG_ENx hardwires the register, disallowing APB write-access, and reducing tile count.                                                                                                                                                           |

| FIXED_PWM_NEG_EN <i>x</i><br>FIXED_DAC_OUT_ENx    | In a typical PWM application, either the FIXED_PWM_NEG_ENx or the<br>FIXED_PWM_POS_ENx could be set if one of those edges do not need to be software-controlled<br>with APB write-accesses. Fixing both edges would result in static output.                                                                    |

|                                                   | For DAC applications, the FIXED_PWM_POS_ENx value is unconnected while the FIXED_DAC_OUT_ENx value would typically be disabled, as using it would result in static output.                                                                                                                                      |

|                                                   | This parameter is used only when CONFIG_MODE set to 0 or 1.                                                                                                                                                                                                                                                     |

| FIXED_PWM_NEGEDGE <i>x</i><br>FIXED_DAC_LEVELOUTx | Hardwired NEGEDGE[APB_DWIDTH -1:0] register value. When in DAC Mode, this parameter also fixes DACx_LEVELOUT, which is typically not fixed in DAC applications, as it would only create a static duty cycle output. Note: x refers to each channel, from 1 to 16.                                               |

| TIALD_DIAC_LLVLLOUIX                              | This parameter is used only when CONFIG_MODE set to 0 or 1.                                                                                                                                                                                                                                                     |

|                                                   | Defines PWMx level when PWM_STRETCHx is set to 1.                                                                                                                                                                                                                                                               |

| PWM_STRETCH_VALUEx                                | When 0, PWMx is set to 0 if PWM_STRETCHx is set to 1.                                                                                                                                                                                                                                                           |

| r wwwi_51KE1CI1_vALUEx                            | When 1, PWMx is set to 1 if PWM_STRETCHx is set to 1 (default).                                                                                                                                                                                                                                                 |

|                                                   | This parameter is used only when CONFIG_MODE set to 1.                                                                                                                                                                                                                                                          |

| TACH_NUM                                          | Number of Tachometer inputs from 1 to 16. This parameter is used only when CONFIG_MODE set to 1 or 2.                                                                                                                                                                                                           |

| TACH_EDGEy                                        | Fixed per Tachometer input edge select. Selects the edge used to capture the counter value for the $TACH[x]$ input signals. 0, capture counter value on falling edge of $TACH[x]$ (default); 1, capture counter value on rising edge of $TACH[x]$ . This parameter is used only when CONFIG_MODE set to 1 or 2. |

| TACHINT_ACT_LEVEL                                 | Selects active Low or active High TACHINT interrupt: 0, active Low interrupt (default); 1, active High interrupt. This parameter is used only when CONFIG_MODE set to 1 or 2.                                                                                                                                   |

| SEPERATE_PWM_CLK                                  | Separate PWM Clock - If the clock frequency required for PWM generation is greater/less than PCLK this signal should be enabled. When enabled (1) input PWM_CLK can be used for PWM_CLK generation. If PCLK is at the desired clock frequency this parameter/generic should be disabled (0).                    |

| Note: APB_DWIDTH must alw                         | ays be greater than or equal to PWM_NUM for all APB read and write operations to be successful.                                                                                                                                                                                                                 |

|                                                   |                                                                                                                                                                                                                                                                                                                 |

## Register Map

All registers are based on APB width parameter selection; default is 8 bits.

| Table 1-3 · CorePWM Register Definitions | Definitions | Register | · CorePWM | Table 1-3 |

|------------------------------------------|-------------|----------|-----------|-----------|

|------------------------------------------|-------------|----------|-----------|-----------|

| Register Name                 | Paddr[7:0] | Description                                                                                                                                                                                                                                                                                                                                                            | Type | Default |

|-------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| PRESCALE                      | 0x00       | PWM MODE: The system clock cycle is multiplied with the PRESCALE value resulting in the minimum PERIOD count timebase.<br>DAC MODE: The Prescale and Period Registers could be used in conjunction with the shadow register to synchronize DAC LEVELOUT.                                                                                                               | R/W  | 0x08    |

| PERIOD                        | 0x04       | PWM MODE: The PRESCALE value is multiplied with the PERIOD value yielding the PWM waveform cycle.                                                                                                                                                                                                                                                                      | R/W  | 0x08    |

| PWM_ENABLE_0_7                | 0x08       | Bitwise channel enables for PWM/DAC channels 1 through 8.                                                                                                                                                                                                                                                                                                              | R/W  | 0x00    |

| PWM_ENABLE_8_15               | 0x0C       | Bitwise channel enables for PWM/DAC channels 9 through 16.                                                                                                                                                                                                                                                                                                             | R/W  | 0x00    |

| SYNC_UPDATE                   | 0xE4       | SYNC_UPDATE: When this bit is set to "1" and SHADOW_REG_EN<br>is selected, all POSEDGE and NEGEDGE registers are updated<br>synchronously. Synchronous updates to the PWM waveform occur only<br>when SHADOW_REG_EN is asserted and SYNC_UPDATE is set to<br>"1".<br>When this bit is set to "0", all the POSEDGE and NEGEDGE registers<br>are updated asynchronously. | R/W  | 0x00    |

| PWM1_POSEDGE                  | 0x10       | PWM MODE: Sets the positive edge of the output with respect to the<br>PERIOD resolution. When APB writes to this register, all the channels are<br>updated.                                                                                                                                                                                                            | R/W  | 0x00    |

| PWM1_NEGEDGE<br>DAC1_LEVELOUT | 0x14       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%.                                                                                                                                                                                                                         | R/W  | 0x00    |

| PWM2_POSEDGE                  | 0x18       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                                                                                                                                                                                                                                                  | R/W  | 0x00    |

| PWM2_NEGEDGE<br>DAC2_LEVELOUT | 0x1C       | PWM MODE: Sets the negative edge of the output with respect to thePERIOD resolution.DAC MODE: Sets the desired output level, from 0-100%.                                                                                                                                                                                                                              | R/W  | 0x00    |

| PWM3_POSEDGE                  | 0x20       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                                                                                                                                                                                                                                                  | R/W  | 0x00    |

| PWM3_NEGEDGE<br>DAC3_LEVELOUT | 0x24       | PWM MODE: Sets the negative edge of the output with respect to thePERIOD resolution.DAC MODE: Sets the desired output level, from 0-100%.                                                                                                                                                                                                                              | R/W  | 0x00    |

| PWM4_POSEDGE                  | 0x28       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                                                                                                                                                                                                                                                  | R/W  | 0x00    |

| PWM4_NEGEDGE<br>DAC4_LEVELOUT | 0x2C       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%.                                                                                                                                                                                                                         | R/W  | 0x00    |

| PWM5_POSEDGE                  | 0x30       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                                                                                                                                                                                                                                                  | R/W  | 0x00    |

| PWM5_NEGEDGE<br>DAC5_LEVELOUT | 0x34       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%.                                                                                                                                                                                                                         | R/W  | 0x00    |

| Register Name                   | Paddr[7:0] | Description                                                                                                                                    | Туре | Default |

|---------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| PWM6_POSEDGE                    | 0x38       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                          | R/W  | 0x00    |

| PWM6_NEGEDGE<br>DAC6_LEVELOUT   | 0x3C       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%. | R/W  | 0x00    |

| PWM7_POSEDGE                    | 0x40       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                          | R/W  | 0x00    |

| PWM7_NEGEDGE<br>DAC7_LEVELOUT   | 0x44       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%. | R/W  | 0x00    |

| PWM8_POSEDGE                    | 0x48       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                          | R/W  | 0x00    |

| PWM8_NEGEDGE<br>DAC8_LEVELOUT   | 0x4C       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%. | R/W  | 0x00    |

| PWM9_POSEDGE                    | 0x50       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                          | R/W  | 0x00    |

| PWM9_NEGEDGE<br>DAC9_LEVELOUT   | 0x54       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%. | R/W  | 0x00    |

| PWM10_POSEDGE                   | 0x58       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                          | R/W  | 0x00    |

| PWM10_NEGEDGE<br>DAC10_LEVELOUT | 0x5C       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%. | R/W  | 0x00    |

| PWM11_POSEDGE                   | 0x60       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                          | R/W  | 0x00    |

| PWM11_NEGEDGE<br>DAC11_LEVELOUT | 0x64       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%. | R/W  | 0x00    |

| PWM12_POSEDGE                   | 0x68       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                          | R/W  | 0x00    |

| PWM12_NEGEDGE<br>DAC12_LEVELOUT | 0x6C       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%. | R/W  | 0x00    |

| PWM13_POSEDGE                   | 0x70       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                          | R/W  | 0x00    |

| PWM13_NEGEDGE<br>DAC13_LEVELOUT | 0x74       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%. | R/W  | 0x00    |

| PWM14_POSEDGE                   | 0x78       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                          | R/W  | 0x00    |

| Register Name                   | Paddr[7:0] | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   | Туре      | Default |

|---------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|

| PWM14_NEGEDGE<br>DAC14_LEVELOUT | 0x7C       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.                                                                                                                                                                                                                                                                                                                                                         | R/W       | 0x00    |

| 2.1.di /_112/112001             |            | DAC MODE: Sets the desired output level, from 0-100%.                                                                                                                                                                                                                                                                                                                                                                                         |           |         |

| PWM15_POSEDGE                   | 0x80       | PWM MODE: Sets the positive edge of the output with respect to the PERIOD resolution.                                                                                                                                                                                                                                                                                                                                                         | R/W       | 0x00    |

| PWM15_NEGEDGE<br>DAC15_LEVELOUT | 0x84       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%.                                                                                                                                                                                                                                                                                                | R/W       | 0x00    |

| PWM16_POSEDGE                   | 0x88       | PWM MODE: Sets the positive edge of the output with respect to the<br>PERIOD resolution.                                                                                                                                                                                                                                                                                                                                                      | R/W       | 0x00    |

| PWM16_NEGEDGE<br>DAC16_LEVELOUT | 0x8C       | PWM MODE: Sets the negative edge of the output with respect to the PERIOD resolution.<br>DAC MODE: Sets the desired output level, from 0-100%.                                                                                                                                                                                                                                                                                                | R/W       | 0x00    |

| PWM_STRETCH                     | 0x90       | When 0, the state of PWMx is determined by PWMx_POSEDGE/<br>NEGEDGE register settings.<br>When 1, PWMx is set to PWM_STRETCH_VALUEx.                                                                                                                                                                                                                                                                                                          | R/W       | 0x0000  |

| TACHPRESCALE                    | 0x94       | Clock prescale setting. Determines effective clock rate for the counter<br>based on PCLK:<br>0000 = divide by 1 (default)<br>0001 = divide by 2<br>0010 = divide by 4<br>0011 = divide by 8<br>0100 = divide by 16<br>0101 = divide by 32<br>0110 = divide by 4<br>0111 = divide by 4<br>0111 = divide by 128<br>1000 = divide by 256<br>1001 = divide by 512<br>1010 = divide by 1,024<br>1011 = divide by 2,048<br>Others = divide by 2,048 | R/W       | 0x0     |

| TACHSTATUS                      | 0x98       | TACH status register which contains one bit per TACH input, indicating<br>whether the respective TACHPULSEDUR register has been updated at<br>least once since the bit was cleared. The bits in this register gets cleared by<br>writing "1", "0" does not have any effect.                                                                                                                                                                   | R/<br>W1C | 0x0000  |

| TACHIRQMASK                     | 0x9C       | TACH interrupt mask register with one bit per tachometer signal,<br>indicating whether CorePWM needs to assert an interrupt if the respective<br>bit in TACHSTATUS register is asserted.                                                                                                                                                                                                                                                      | R/W       | 0x0000  |

| TACHMODE                        | 0xA0       | TACH Mode. Sets the measurement mode used for each TACH input.<br>When 0: TACH input is continuously measured and stored in the<br>respective TACHPULSEDUR register.<br>When 1: A one-time measurement is performed only if the respective bit<br>in TACHSTATUS register is cleared.                                                                                                                                                          | R/W       | 0x0000  |

| Table 1-3 · CorePWM Register Definitions (cont | inued) |

|------------------------------------------------|--------|

|------------------------------------------------|--------|

#### CorePWM v4.3

| Register Name                                                                                                                                                                                                                                                                     | Paddr[7:0]                                                                                                                                                                                                                                                                | Paddr[7:0] Description                                                                                                                                                                                                                                       |        | Default |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|

| TACHPULSEDUR_0                                                                                                                                                                                                                                                                    | 0xA4                                                                                                                                                                                                                                                                      | Stores the number of timer ticks between two successive positive (or negative) edges from the TACHIN[0]. The edge to be used is configurable. If the number of timer ticks exceeds the maximum register value, the value of 0 shall be stored instead.       | R      | 0x0000  |

| TACHPULSEDUR_1                                                                                                                                                                                                                                                                    | 0xA8                                                                                                                                                                                                                                                                      | Stores the number of timer ticks between two successive positive (or negative) edges from the TACHIN[1]. The edge to be used is configurable. If the number of timer ticks exceeds the maximum register value, the value of 0 shall be stored instead.       | R      | 0x0000  |

| TACHPULSEDUR_2                                                                                                                                                                                                                                                                    | 0xAC                                                                                                                                                                                                                                                                      | Stores the number of timer ticks between two successive positive (or negative) edges from the TACHIN[2]. The edge to be used is configurable. If the number of timer ticks exceeds the maximum register value, the value of 0 shall be stored instead.       | R      | 0x0000  |

| TACHPULSEDUR_3                                                                                                                                                                                                                                                                    | 0xB0                                                                                                                                                                                                                                                                      | Stores the number of timer ticks between two successive positive (or negative) edges from the TACHIN[3]. The edge to be used is configurable. If the number of timer ticks exceeds the maximum register value, the value of 0 shall be stored instead.       | R      | 0x0000  |

| TACHPULSEDUR_4                                                                                                                                                                                                                                                                    | 0xB4                                                                                                                                                                                                                                                                      | Stores the number of timer ticks between two successive positive (or negative) edges from the TACHIN[4]. The edge to be used is configurable. If the number of timer ticks exceeds the maximum register value, the value of 0 shall be stored instead.       | R      | 0x0000  |

| TACHPULSEDUR_5                                                                                                                                                                                                                                                                    | 0xB8       Stores the number of timer ticks between two successive positive (or negative) edges from the TACHIN[5]. The edge to be used is configurable. If the number of timer ticks exceeds the maximum register value, the value of 0 shall be stored instead.         |                                                                                                                                                                                                                                                              | R      | 0x0000  |

| TACHPULSEDUR_6                                                                                                                                                                                                                                                                    | UR_6 0xBC Stores the number of timer ticks between two successive positive (or negative) edges from the TACHIN[6]. The edge to be used is configurable. If the number of timer ticks exceeds the maximum register value, the value of 0 shall be stored instead.          |                                                                                                                                                                                                                                                              | R      | 0x0000  |

| TACHPULSEDUR_7                                                                                                                                                                                                                                                                    | ACHPULSEDUR_7 0xC0 Stores the number of timer ticks between two successive positive (or negative) edges from the TACHIN[7]. The edge to be used is configurable. If the number of timer ticks exceeds the maximum register value, the value of 0 shall be stored instead. |                                                                                                                                                                                                                                                              | R      | 0x0000  |

| TACHPULSEDUR_80xC4Stores the number of timer ticks between two successive positive (or<br>negative) edges from the TACHIN[8]. The edge to be used is configurable.<br>If the number of timer ticks exceeds the maximum register value, the value<br>of 0 shall be stored instead. |                                                                                                                                                                                                                                                                           | R                                                                                                                                                                                                                                                            | 0x0000 |         |

| TACHPULSEDUR_9                                                                                                                                                                                                                                                                    | 0xC8                                                                                                                                                                                                                                                                      | xC8 Stores the number of timer ticks between two successive positive (or negative) edges from the TACHIN[9]. The edge to be used is configurable. If the number of timer ticks exceeds the maximum register value, the value of 0 shall be stored instead.   |        | 0x0000  |

| TACHPULSEDUR_10                                                                                                                                                                                                                                                                   | 0xCC                                                                                                                                                                                                                                                                      | Stores the number of timer ticks between two successive positive (or negative) edges from the TACHIN[10]. The edge to be used is configurable. If the number of timer ticks exceeds the maximum register value, the value of 0 shall be stored instead.      |        | 0x0000  |

| TACHPULSEDUR_11                                                                                                                                                                                                                                                                   | 0xD0                                                                                                                                                                                                                                                                      | 0xD0 Stores the number of timer ticks between two successive positive (or negative) edges from the TACHIN[11]. The edge to be used is configurable. If the number of timer ticks exceeds the maximum register value, the value of 0 shall be stored instead. |        | 0x0000  |

| Table 1-3 · CorePWM Register Definitions (continued) |

|------------------------------------------------------|

|------------------------------------------------------|