Handbook

#### Actel Corporation, Mountain View, CA 94043

© 2009 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 50200102-2

Release: February 2009

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### Trademarks

Actel and the Actel logo are registered trademarks of Actel Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

## **Table of Contents**

|   | Introduction       Key Features         Key Features       Core Overview         Supported Device Families       Core Version         Supported Interfaces       Utilization and Performance                  | 5<br>5<br>7<br>7<br>7 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 1 | Functional Block Description                                                                                                                                                                                  | 9                     |

| 2 | Tool Flows       1         Licenses       1         SmartDesign       1                                                                                                                                       | 1                     |

| 3 | Interface Description       1         Parameters/Generics       1         Parameter Dependencies and Precedence       2         Ports       2         Analog Interfaces       2                               | 7<br>3<br>4           |

| 4 | Register Maps       2         APB Register Map       2         ACM Interface       3                                                                                                                          | 9                     |

| 5 | ADC Operation                                                                                                                                                                                                 | 1                     |

| 6 | Testbench Operation and Modification       4         Simple Application Testbench       4                                                                                                                     | 3<br>3                |

| 7 | System Operation       4         Using CoreAI with Cortex-M1       4         Using CoreAI with Core8051s       4         Using CoreAI with CoreABC       4         Using CoreAI with ADC Results FIFO       4 | 5<br>5<br>6           |

| 8 | Ordering Information                                                                                                                                                                                          |                       |

| A | Product Support       5         Customer Service       5         Actel Customer Technical Support Center       5         Actel Technical Support       5         Website       5                              | 1<br>1<br>1           |

Table of Contents

| Contact | ing | ; th | le ( | Cu | isto | om | ler | T | ech | nni | cal | S | up | po | rt | Ce | ent | ter | • | • |   |     |   | • | • |   | • | • |   |   | <br>• | • | <br>• | 51 |

|---------|-----|------|------|----|------|----|-----|---|-----|-----|-----|---|----|----|----|----|-----|-----|---|---|---|-----|---|---|---|---|---|---|---|---|-------|---|-------|----|

| Index   |     |      | •    | •  | •    | •  | •   |   | •   |     |     |   |    | •  |    |    | •   | •   | • |   | • | • • | • |   | • | • | • | • | • | • | <br>• |   | •     | 53 |

## Introduction

CoreAI (Analog Interface) allows for simple control of the analog peripherals within the Fusion device family. Control may be implemented with an internal or external microprocessor or microcontroller such as CoreABC, Core8051s, or Cortex-M1, etc., or with user-created custom logic within the FPGA fabric.

### **Key Features**

CoreAI has the following features:

- Thin processor interface around Fusion AB (Analog Block) hard macro

- · ADC conversions controlled by processor writes

- Internal logic interface for controlling the ACM (Analog Configuration MUX)

- Internal logic to divide clock for generating ACM clock

- Optional hardware-controlled inputs to directly control some AB functions

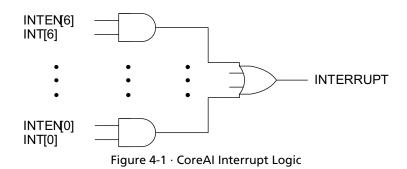

- Interrupt logic for various events (such as end of ADC conversions)

### **Core Overview**

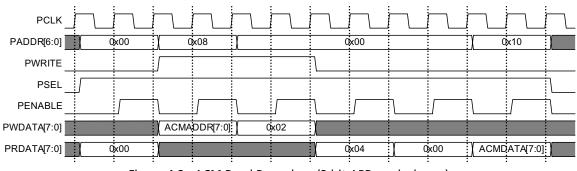

The industry-standard AMBA (Advanced Microcontroller Bus Architecture) APB (Advanced Peripheral Bus) slave interface is used as the primary control mechanism within CoreAI.

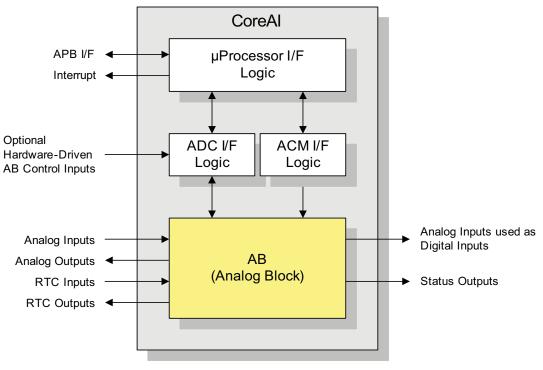

CoreAI instantiates the AB (Analog Block) macro (see Figure 1). The AB macro includes the ACM (Analog Configuration MUX) interface, Analog Quads, and RTC (Real-Time Counter). The ACM interface, within the AB macro, is used to control configuration of the Analog Quads and RTC in the Fusion device.

CoreAI generates the control signals used by the ACM, including its clock signal, which is generated by an internal clock divider. The ACM clock divider is used to ensure that the ACM interface is clocked at a frequency less than or equal to 10 MHz (see "ACM Interface" on page 36 for details). For more details on the silicon features of the AB macro, such as the Analog Quads, RTC, or ACM, refer to the Fusion datasheet (http://www.actel.com/products/fusion/ docs.aspx).

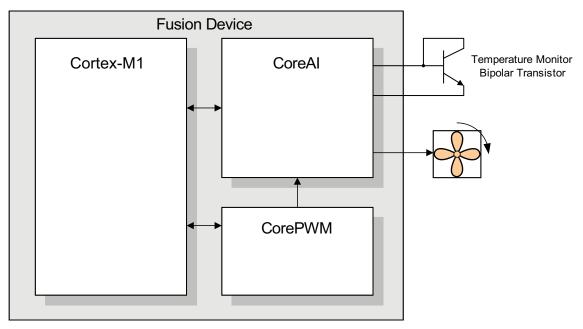

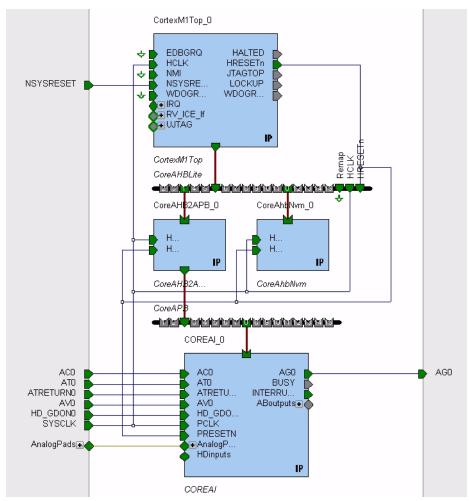

Several aspects of CoreAI can be configured using top-level parameters (Verilog) or generics (VHDL). For a detailed description of the parameters/generics, refer to Table 3-1 on page 17. The CoreAI block diagram is shown in Figure 1. A typical application using CoreAI is shown in Figure 2.

Figure 1 · Core Al Block Diagram

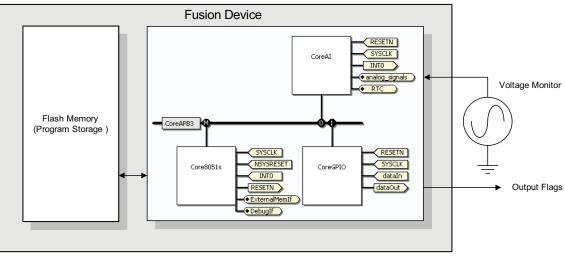

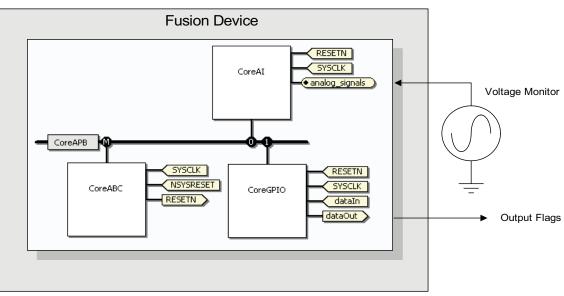

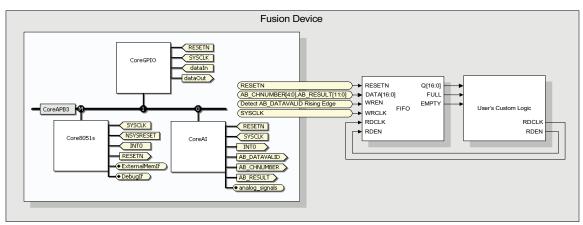

Figure 2 · Typical CoreAI Application

## **Supported Device Families**

Fusion

## **Core Version**

This handbook applies to CoreAI v3.0.

## **Supported Interfaces**

CoreAI is available with the APB (Advanced Peripheral Bus) slave interface and must be connected to an APB master interface or to dedicated FPGA logic that implements an APB master interface.

Actel recommends that you use SmartDesign in the Libero<sup>®</sup> IDE Project Manager to connect and configure CoreAI in a processor-based system, using Cortex-M1, Core8051s or CoreABC.

## **Utilization and Performance**

CoreAI has been implemented in the Actel Fusion device family. A summary of the data for CoreAI is listed in page 8 and Table 2. CoreAI can be used with any device in the Fusion family.

| Family  |            | Tiles         |       | Utiliz | Performance |               |

|---------|------------|---------------|-------|--------|-------------|---------------|

| I anniy | Sequential | Combinatorial | Total | Device |             | Terrormance   |

| Fusion  | 38         | 123           | 161   | AFS090 | 7%          | up to 100 MHz |

| Table 1 · CoreAI Device Utilization and Performance (minimum configuration |

|----------------------------------------------------------------------------|

|----------------------------------------------------------------------------|

Note: Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics that differ from the default values were set as follows: PCLK\_FREQUENCY = 40, CFG\_VAREFSEL = 2, CFG\_MODE = 32, CFG\_TVC = 512, CFG\_STC = 512, CFG\_ACx = 512, CFG\_ATx = 512, CFG\_TMSTBINT = 2, CFG\_GDx = 768, CFG\_INTERRUPT = 3, APB\_DWIDTH = 16.

| Table 2. Cana Al Davias 114 | linetian and Daufaunaanaa | (               |          |

|-----------------------------|---------------------------|-----------------|----------|

| Table 2 · CoreAI Device Uti | lization and Performance  | (maximum coning | uration) |

| Family  |            | Tiles         |       | Utiliz | Performance |               |

|---------|------------|---------------|-------|--------|-------------|---------------|

| I uniny | Sequential | Combinatorial | Total | Device |             | I eriormanee  |

| Fusion  | 103        | 208           | 317   | AFS600 | 2%          | up to 100 MHz |

Note: Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics that differ from the default values were set as follows: PCLK\_FREQUENCY = 40, CFG\_RTC = 1.

## **Functional Block Description**

CoreAI, shown in Figure 1 on page 6, consists of the microprocessor interface logic, ACM interface logic, and ADC interface logic blocks. The microprocessor interface logic implements APB slave logic and generates a maskable interrupt. The ACM interface block writes configuration data into the AB macro to control Analog Quad and RTC settings. The ADC interface block sends control data to and receives status information from the ADC.

### Licenses

CoreAI is licensed in two ways. Depending on your license type, tool flow functionality may be limited.

#### **Obfuscated**

Complete RTL code is provided for the core, allowing the core to be instantiated within SmartDesign. Simulation, Synthesis and Layout can be performed within the Libero IDE. The RTL code for the core is obfuscated and some of the testbench source files are not provided; they are pre-compiled into the compiled simulation library instead.

#### RTL

Complete RTL source code is provided for the core and testbenches.

## **SmartDesign**

CoreAI is available for download to the SmartDesign IP Catalog via the Libero IDE web repository. The parameters/ generics of the core can be configured using the IP configuration GUI within SmartDesign as shown in Figure 2-1, Figure 2-2, and Figure 2-3. The parameters/generics of the core are fully described in "Parameters/Generics" on page 17 and cross references to them are shown next to the IP configuration screenshots in Figure 2-1, Figure 2-2, and Figure 2-3.

Note: If you are using an AFS090 (or AFS090 variant) or AFS250 (or AFS250 variant), you must make the correct choice in the CoreAI IP configurator within SmartDesign via the Fusion Device selection box. For example, as shown in Figure 2-1, the device selected is AFS090. If you are not using either an AFS090 or AFS250 (or variants thereof), you must make the default choice of larger than AFS250 in the Fusion Device selection box.

#### **Tool Flows**

| Conf  | iguration-                                   |                                                       |           |

|-------|----------------------------------------------|-------------------------------------------------------|-----------|

|       | - Fusion Specific                            |                                                       |           |

|       | Fusion Device:                               | AF5090 (or AF5090 variants)                           | AQ_DS     |

| _BITS | Shift RESULT[11:0] right in ADC_STAT reg by: | 0 bits (no shift)                                     |           |

|       | AB macro enable/disable logic:               | Add AB enable/disable logic, ADCRESET starts inactive | CFG       |

|       | Processor Interface                          |                                                       |           |

|       | APB data bus width (in bits):                | 8                                                     | APB_D     |

| VCY – | PCLK frequency (up to nearest MHz):          | 40                                                    |           |

|       | Interrupt output:                            | Enabled (active high)                                 | CFG_INT   |

| LOG   | C Interrupt status register logic:           | All interrupt status register bits used               |           |

|       | Analog Quad 0                                |                                                       |           |

| 0     | AVO input: Voltage Monitor: 0V to 8V         | ACO input: Current Monitor                            | ✓ CFG_    |

|       | AT0 input: Disabled                          | AG0 output: Software-Driven 25 mA sink                |           |

|       | Analog Quad 1                                |                                                       | CFG_      |

|       | AV1 input: Voltage Monitor: 0V to 12V        | AC1 input: Disabled                                   | ✓         |

|       | AT1 input: Disabled                          |                                                       |           |

|       |                                              |                                                       |           |

|       | Analog Quad 2<br>AV2 input: Disabled         | AC2 input: Voltage Monitor: 0V to 12V                 |           |

|       |                                              | · · · · · · · · · · · · · · · · · · ·                 | ▲         |

|       | AT2 input: Disabled                          | AG2 output: Disabled                                  |           |

|       | Analog Quad 3                                |                                                       |           |

|       | AV3 input: Disabled                          | · · · · · · · · · · · · · · · · · · ·                 |           |

|       | AT3 input: Disabled                          | AG3 output: Disabled                                  |           |

|       | Analog Quad 4                                |                                                       |           |

|       | AV4 input: Disabled                          | AC4 input: Disabled                                   |           |

|       | AT4 input: Disabled                          | AG4 output: Disabled                                  |           |

|       | Analog Quad 5                                |                                                       |           |

|       | AV5 input: Disabled                          | AC5 input: Disabled                                   |           |

|       | AT5 input: Disabled                          | AG5 output: Disabled                                  |           |

|       |                                              |                                                       | OK Cancel |

For information on using SmartDesign to instantiate, configure, connect, and generate cores, refer to the Libero IDE online help. For a detailed tutorial on DirectCore IP flow using SmartDesign, refer to Using DirectCore in Libero IDE.

Figure 2-1 · CoreAI Configuration within SmartDesign

|   | onfiguring COREAI_0 (COREAI - 3.0.118)                               |                                            |   |

|---|----------------------------------------------------------------------|--------------------------------------------|---|

|   |                                                                      | it: Disabled                               |   |

| G | AV6 input: Disabled AC6 input                                        | ut: Disabled 🗸 🗸                           |   |

|   | AT6 input: Disabled V AG6 out                                        | put: Disabled 🗸                            |   |

|   | Analog Quad 7                                                        |                                            |   |

|   | AV7 input: Disabled AC7 input                                        | ut: Disabled 🗸                             |   |

|   | AT7 input: Disabled AG7 out                                          | put: Disabled                              |   |

|   | Analog Quad 8                                                        |                                            |   |

|   | AV8 input: Disabled AC8 inpu                                         | ut: Disabled 🗸                             |   |

|   | AT8 input: Disabled V AG8 out                                        | put: Disabled                              |   |

|   |                                                                      |                                            |   |

|   | Analog Quad 9                                                        |                                            |   |

|   | AV9 input: Disabled AC9 input                                        | ut: Disabled 🗸 🗸                           |   |

|   | AT9 input: Disabled AG9 out                                          | put: Disabled 🔽                            |   |

|   | Software/Hardware-Driven Control of Various AB (Analog Block) Inputs |                                            |   |

|   | VAREFSEL: Statically fixed Internal VAREF 💌 ADCRESET: S              | öoftware-Driven via internal register      | ✓ |

|   | PWRDWN: Software-Driven via internal register V ADCSTART:            | 5oftware-Driven via internal register      | ✓ |

|   | CHNUMBER: Software-Driven via internal register V MODE: 5            | 50ftware-Driven via internal register      | ~ |

|   |                                                                      |                                            |   |

|   |                                                                      | 5oftware-Driven via internal register      | × |

|   | Software/Hardware-Driven Control of CMSTB* AB (Analog Block) Inputs  |                                            |   |

|   | CMSTB0: Software-Driven via internal register 💙 CMSTB1               | : Software-Driven via internal register 👻  |   |

|   | CMSTB2: Software-Driven via internal register 🕑 CMSTB3               | : Software-Driven via internal register 📝  |   |

|   | CMSTB4: Software-Driven via internal register V                      | : Software-Driven via internal register 💟  |   |

|   | CMSTB6: Software-Driven via internal register CMSTB7                 | : Software-Driven via internal register 💉  |   |

|   | CMSTB8: Software-Driven via internal register V                      | : Software-Driven via internal register 👻  |   |

|   | Software/Hardware-Driven Control of TMSTB* AB (Analog Block) Inputs  |                                            |   |

|   |                                                                      | l: Software-Driven via internal register 💉 |   |

|   |                                                                      | 3: Software-Driven via internal register 🗸 |   |

|   |                                                                      | 5: Software-Driven via internal register 🗸 |   |

|   |                                                                      |                                            |   |

|   |                                                                      | 7: Software-Driven via internal register 💟 |   |

|   | TMSTB8: Software-Driven via internal register 🗸 TMSTB9               | 9: Software-Driven via internal register 🕑 |   |

| ۱ |                                                                      |                                            |   |

Figure 2-2 · CoreAI Configuration within SmartDesign (continued)

| -Real Time Clo | ck                                          |         |   |          |

|----------------|---------------------------------------------|---------|---|----------|

|                | Use Real Time Clock:                        | No      | ✓ | CFG_RTC  |

|                | RTC_COUNTER4 (byte 4) initial value (0 to : | 255): 0 |   | CFG_RTC_ |

|                | RTC_COUNTER3 (byte 3) initial value (0 to 2 | 255): 0 |   |          |

|                | RTC_COUNTER2 (byte 2) initial value (0 to 2 | 255): 0 |   |          |

|                | RTC_COUNTER1 (byte 1) initial value (0 to 2 | 255): 0 |   |          |

|                | RTC_COUNTER0 (byte 0) initial value (0 to ( | 255): 0 |   |          |

|                | RTC_MATCHREG4 (byte 4) initial value (0 to  | 255): 0 |   |          |

|                | RTC_MATCHREG3 (byte 3) initial value (0 to  | 255): 0 |   |          |

|                | RTC_MATCHREG2 (byte 2) initial value (0 to  | 255): 0 |   |          |

|                | RTC_MATCHREG1 (byte 1) initial value (0 to  | 255): 0 |   |          |

|                | RTC_MATCHREG0 (byte 0) initial value (0 to  | 255): 0 |   |          |

|                | RTC_CTRL_STAT initial value (0 to 255):     | 0       |   | ▼ _      |

| Testbench:     |                                             | User    |   |          |

| License:       |                                             |         |   |          |

|                | <ul> <li>Obfuscated</li> </ul>              | O RTL   |   |          |

| <u></u>        |                                             |         |   | <u> </u> |

Figure 2-3 · CoreAI Configuration within SmartDesign (continued)

#### **Simulation Flows**

To run simulations, select the user testbench in SmartDesign through the CoreAI IP configuration GUI. Generate the design in SmartDesign. The appropriate test bench files are now installed.

To run the testbenches, set the design root to the CoreAI instantiation in the Libero IDE File Manager and click the Simulation icon in the Project Flow tab. This invokes ModelSim® and automatically runs the simulation.

#### **Synthesis in Libero IDE**

To run Synthesis on the core with parameters set in SmartDesign, set the design root appropriately and click the Synthesis icon in the Project Manager. The Synthesis window appears, displaying the Synplicity project. Set Synplicity to use the Verilog 2001 standard if Verilog is being used. To perform synthesis, click the Run icon.

#### **Place-and-Route in Libero IDE**

After setting the design root appropriately and running Synthesis, click the Layout icon in the Project Manager to invoke Designer. CoreAI requires no special place-and-route settings.

## **Interface Description**

CoreAI is available with an APB slave interface and is easily connected to an APB bus on the SmartDesign Canvas.

### **Parameters/Generics**

CoreAI has parameters (Verilog) and generics (VHDL), described in Table 3-1. All parameters and generics are integer types.

| Name              | Valid<br>Range | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FAMILY            | 17             | Only the Fusion family is supported for this core.                                                                                                                                                                                                                                                                                                                                                                                          |

|                   |                | Disable Analog Quads based on Fusion device<br>0 - Disable use of Analog Quads 5 to 9 (AFS090 or AFS090 variants)                                                                                                                                                                                                                                                                                                                           |

| AQ_DSBL_CFG       | 0 to 2         | 1 - Disable use of Analog Quads 6 to 9 (AFS250 or AFS250 variants)                                                                                                                                                                                                                                                                                                                                                                          |

|                   |                | 2 - Do not disable use of any of the Analog Quads from 0 to 9 (default, used with devices larger than the AFS250)                                                                                                                                                                                                                                                                                                                           |

| APB_DWIDTH        | 8, 16, or 32   | Set this to the width of the APB data bus. Default is 8-bit width.                                                                                                                                                                                                                                                                                                                                                                          |

| PCLK_FREQUENCY    | 1 to 100       | Set this to the operating frequency in MHz of the PCLK input to the nearest integer, rounded up. CoreAI needs to know this information to set the internal clock divider correctly to communicate with the ACM interface within the AB macro. For example, if the actual PCLK input frequency is 19.15 MHz, PCLK_FREQUENCY should be set to 20; if the actual PCLK input frequency is exactly 19.0 MHz, PCLK_FREQUENCY should be set to 19. |

|                   |                | This parameter/generic shifts the lower 12 bits in the ADC Status Register 11:0 bits<br>0 - ADC Status Register 11:0 connected to AB macro outputs RESULT[11:0] (default,<br>not shifted)                                                                                                                                                                                                                                                   |

| SHIFT_RESULT_BITS | 0, 2, or 4     | 2 - ADC Status Register bits 11:10 tied low and bits 9:0 connected to AB macro outputs RESULT[11:2]                                                                                                                                                                                                                                                                                                                                         |

|                   |                | 4 - ADC Status Register bits 11:8 tied low and bits 7:0 connected to AB macro outputs RESULT[11:4]                                                                                                                                                                                                                                                                                                                                          |

|                   |                | AB Macro Enable Configuration                                                                                                                                                                                                                                                                                                                                                                                                               |

| CFG_AB            | 0, 1, or 2     | 0 - Legacy mode - no clock enable or associated logic for AB macro                                                                                                                                                                                                                                                                                                                                                                          |

|                   | 0, 1, 01 2     | 1 - Add clock enable logic for AB macro, ADCRESET starts inactive (default)                                                                                                                                                                                                                                                                                                                                                                 |

|                   |                | 2 - Add clock enable logic for AB macro, ADCRESET starts active                                                                                                                                                                                                                                                                                                                                                                             |

|                   |                | Interrupt Output Configuration                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                | 0 - Interrupt Active-high (default)                                                                                                                                                                                                                                                                                                                                                                                                         |

| CFG_INTERRUPT     | 0 to 3         | 1 - Interrupt Active-low                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   |                | 2 - Interrupt disabled (statically tied low)                                                                                                                                                                                                                                                                                                                                                                                                |

|                   |                | 3 - Interrupt disabled (statically tied high)                                                                                                                                                                                                                                                                                                                                                                                               |

#### Interface Description

#### Table 3-1 · CoreAl Parameter/Generic Description (continued)

| Name              | Valid<br>Range | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |                | Remove interrupt register logic                                                                                                                                                                                                                                                                                                                                                                                      |

| REMOVE_IREG_LOGIC | 0 or 1         | 0 - All bits of the Interrupt Status Register are used (default)                                                                                                                                                                                                                                                                                                                                                     |

|                   |                | 1 - bits 6, 3:0 of the Interrupt Status Register are tied low                                                                                                                                                                                                                                                                                                                                                        |

|                   |                | ADC Reset Configuration                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                | 0 - Software-controlled by internal register (default)                                                                                                                                                                                                                                                                                                                                                               |

|                   |                | 1 - Hardware-controlled by HD_ADCRESET input                                                                                                                                                                                                                                                                                                                                                                         |

| CFG_ADCRESET      | 0 or 1         | Note that if the ADCRESET is configured as being hardware-controlled by the HD_ADCRESET input, it is the user's responsibility to activate and de-activate the ADC reset condition to the AB block, whereas the de-activation of the software-controlled reset condition is automatically handled within CoreAI (Refer to Table 10: ADC Control Register 1 for description of the software-controlled ADCRESET bit). |

|                   |                | ADC Power Down Configuration                                                                                                                                                                                                                                                                                                                                                                                         |

|                   | 0 or 1         | 0 - Software-controlled by internal register (default)                                                                                                                                                                                                                                                                                                                                                               |

| CFG_PWRDWN        |                | 1 - Hardware-controlled by HD_PWRDWN input                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                | When hardware-controlled, the ADC will be powered up normally if the HD_PWRDWN input is logic 0 and will be powered down if the HD_PWRDWN input is logic 1.                                                                                                                                                                                                                                                          |

|                   |                | ADC Reference Voltage Selection Configuration                                                                                                                                                                                                                                                                                                                                                                        |

|                   |                | 0 - Software-controlled by internal register (default)                                                                                                                                                                                                                                                                                                                                                               |

|                   |                | 1 - Hardware-controlled by HD_VAREFSEL input                                                                                                                                                                                                                                                                                                                                                                         |

| CFG_VAREFSEL      | 0 to 3         | 2 - Statically fixed at logic 0 to select internal VAREF as output                                                                                                                                                                                                                                                                                                                                                   |

|                   |                | 3 - Statically fixed at logic 1 to select external VAREF as input                                                                                                                                                                                                                                                                                                                                                    |

|                   |                | (Refer to Table 10: ADC Control Register 1 for description of the software-controlled VAREFSEL bit)                                                                                                                                                                                                                                                                                                                  |

18

| Name     | Valid<br>Range                                            | Description                                                                                                                                                                                         |  |

|----------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          |                                                           | ADC Mode Selection Configuration (hexadecimal values shown)                                                                                                                                         |  |

|          |                                                           | This parameter/generic controls the connection to the MODE[3:0] input pins of the AB macro (controls ADC resolution, etc.).                                                                         |  |

|          |                                                           | 0x00 - Software-controlled by internal register (default)                                                                                                                                           |  |

|          |                                                           | 0x10 - Hardware-controlled by HD_MODE[3:0] inputs                                                                                                                                                   |  |

|          |                                                           | 0x20 - Statically fixed to 0x0 (ADC 10-bit mode)                                                                                                                                                    |  |

|          |                                                           | 0x21 - Statically fixed to 0x1 (ADC 12-bit mode)                                                                                                                                                    |  |

|          |                                                           | 0x22 - Statically fixed to 0x2 (ADC 8-bit mode)                                                                                                                                                     |  |

| CFG_MODE | 0, 16, 32 to<br>34, 36 to<br>38, 40 to<br>42, 44 to<br>46 | 0x24 - Statically fixed to 0x4 (ADC 10-bit mode without internal power-down after conversion)                                                                                                       |  |

|          |                                                           | 0x25 - Statically fixed to 0x5 (ADC 12-bit mode without internal power-down after conversion)                                                                                                       |  |

|          |                                                           | 0x26 - Statically fixed to 0x6 (ADC 8-bit mode without internal power-down after conversion)                                                                                                        |  |

|          |                                                           | 0x28 - Statically fixed to 0x8 (ADC 10-bit mode without internal calibration)                                                                                                                       |  |

|          |                                                           | 0x29 - Statically fixed to 0x9 (ADC 12-bit mode without internal calibration)                                                                                                                       |  |

|          |                                                           | 0x2A - Statically fixed to 0xA (ADC 8-bit mode without internal calibration)                                                                                                                        |  |

|          |                                                           | 0x2C - Statically fixed to 0xC (ADC 10-bit mode without internal calibration and without internal power-down after conversion)                                                                      |  |

|          |                                                           | 0x2D - Statically fixed to 0xD (ADC 12-bit mode without internal calibration and without internal power-down after conversion)                                                                      |  |

|          |                                                           | 0x2E - Statically fixed to 0xE (ADC 8-bit mode without internal calibration and without internal power-down after conversion)                                                                       |  |

|          |                                                           | ADC Clock Divider Configuration (hexadecimal values shown)                                                                                                                                          |  |

|          | 0, 256, 512<br>to 767                                     | This parameter/generic controls the connection to the TVC[7:0] input pins of the AB macro (controls ADC internal clock-divider that divides the PCLK frequency to generate the internal ADC clock). |  |

|          |                                                           | 0x000 - Software-controlled by internal register (default)                                                                                                                                          |  |

| CFG_TVC  |                                                           | 0x100 - Hardware-controlled by HD_TVC[7:0] inputs                                                                                                                                                   |  |

|          |                                                           | 0x200 - Statically fixed to 0x00 (PCLK/4)                                                                                                                                                           |  |

|          |                                                           | 0x201 - Statically fixed to 0x01 (PCLK/8)                                                                                                                                                           |  |

|          |                                                           |                                                                                                                                                                                                     |  |

|          |                                                           | 0x2FE - Statically fixed to 0xFE (PCLK/1020)                                                                                                                                                        |  |

|          |                                                           | 0x2FF - Statically fixed to 0xFF (PCLK/1024)                                                                                                                                                        |  |

#### Table 3-1 · CoreAl Parameter/Generic Description (continued)

| Name                                                                                                                                              | Valid<br>Range        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CFG_STC                                                                                                                                           | 0, 256, 512<br>to 767 | ADC Sample Time Control Configuration (hexadecimal values shown)<br>This parameter/generic controls the connection to the STC[7:0] input pins of the AB<br>macro (controls ADC sample time control).<br>0x000 - Software-controlled by internal register (default)<br>0x100 - Hardware-controlled by HD_STC[7:0] inputs<br>0x200 - Statically fixed to 0x00 (2 ADC clock periods)<br>0x201 - Statically fixed to 0x01 (3 ADC clock periods)<br><br>0x2FE - Statically fixed to 0xFE (256 ADC clock periods)      |  |

| CFG_ADCSTART                                                                                                                                      | 0 or 1                | 0x2FF - Statically fixed to 0xFF (257 ADC clock periods)         ADC Start Conversion Configuration         0 - Software-controlled by internal register (default)         1 - Hardware-controlled by HD_ADCSTART input                                                                                                                                                                                                                                                                                          |  |

| CFG_CHNUMBER                                                                                                                                      | 0 or 1                | ADC Channel Number Control Configuration<br>0 - Software-controlled by internal registers (default)<br>1 - Hardware-controlled by HD_CHNUMBER[4:0] inputs                                                                                                                                                                                                                                                                                                                                                        |  |

| CFG_CMSTB9,<br>CFG_CMSTB8,<br>CFG_CMSTB7,<br>CFG_CMSTB6,<br>CFG_CMSTB5,<br>CFG_CMSTB4,<br>CFG_CMSTB3,<br>CFG_CMSTB2,<br>CFG_CMSTB1,<br>CFG_CMSTB0 | 0 or 1                | Current Monitor Strobes Configuration<br>These parameters/generics control the connection to the CMSTB9 down to CMSTB0<br>input pins, respectively, of the AB macro (control current monitor strobes).<br>0 - Software-controlled by internal register (default)<br>1 - Hardware-controlled by HD_CMSTBx input<br>For example, if CFG_CMSTB3 is set to 1, the HD_CMSTB3 input will control the<br>CMSTB3 input pin of the AB macro, instead of software-controlled writes to bit 3 of<br>ADC Control Register 3. |  |

| CFG_TMSTBINT                                                                                                                                      | 0 to 2                | Internal Temperature Monitor Strobe Configuration<br>This parameter/generic controls the connection to the TMSTBINT input pin of the AB<br>macro (controls internal temperature monitor strobe).<br>0 - Software-controlled by internal register (default)<br>1 - Hardware-controlled by HD_TMSTBINT input<br>2 - Disabled (tied to logic 0 internally)                                                                                                                                                          |  |

#### Table 3-1 · CoreAl Parameter/Generic Description (continued)

| Table 3-1 · CoreAl Parameter/Generic Description (continued) |  |

|--------------------------------------------------------------|--|

|--------------------------------------------------------------|--|

| Name                                                                                                                                              | Valid<br>Range | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CFG_TMSTB9,<br>CFG_TMSTB8,<br>CFG_TMSTB7,<br>CFG_TMSTB6,<br>CFG_TMSTB5,<br>CFG_TMSTB4,<br>CFG_TMSTB3,<br>CFG_TMSTB2,<br>CFG_TMSTB1,<br>CFG_TMSTB0 | 0 or 1         | Temperature Monitor Strobes Configuration<br>These parameters/generics control the connection to the TMSTB9 down to TMSTB0<br>input pins, respectively, of the AB macro (control temperature monitor strobes).<br>0 - Software-controlled by internal register (default)<br>1 - Hardware-controlled by HD_TMSTBx input<br>For example, if CFG_TMSTB6 is set to 1, the HD_TMSTB6 input will control the<br>TMSTB6 input pin of the AB macro, instead of software-controlled writes to bit 6 of<br>ADC Control Register 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| CFG_AV9,CFG_AV8,<br>CFG_AV7,CFG_AV6,<br>CFG_AV5,CFG_AV4,<br>CFG_AV3,CFG_AV2,<br>CFG_AV1,CFG_AV0                                                   | 0 to 1,023     | Configure AVx Inputs (hexadecimal values shown)<br>Each of these parameters/generics is used to configure the AV9 down to AV0 inputs,<br>respectively, connected to the AB macro. The lower 8 bits of each of these 10-bit integers<br>are reserved for generating firmware settings for the target processor used with CoreAI<br>and are ignored by the CoreAI hardware. The upper 2 bits are used to create the settings<br>for each AVx input.<br>0x000 to 0x0FF - Voltage Monitor (default)<br>0x100 to 0x1FF - Digital Input<br>0x200 to 0x2FF - Reserved (unused)<br>0x300 to 0x3FF - Disabled<br>For example, if CFG_AV5 is set to the value 0x000, the AV5 input will be used as an<br>analog voltage monitor input. If CFG_AV5 is set to the value 0x100, the AV5 input will<br>be used as a digital input, and the buffered DAVOUT5 output would be connected to the<br>user's own logic. If CFG_AV5 is set to the value 0x300, the AV5 input will be disabled; in<br>this case, the CoreAI AV5 input will not be used and the AV5 input of the AB macro will<br>be hardwired to logic 0 within CoreAI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| CFG_AC9,CFG_AC8,<br>CFG_AC7,CFG_AC6,<br>CFG_AC5,CFG_AC4,<br>CFG_AC3,CFG_AC2,<br>CFG_AC1,CFG_AC0                                                   | 0 to 1,023     | <ul> <li>Configure ACx Inputs (hexadecimal values shown)</li> <li>Each of these parameters/generics is used to configure the AC9 down to AC0 inputs, respectively, connected to the AB macro. The lower 8 bits of each of these 10-bit integers are reserved for generating firmware settings for the target processor used with CoreAI and are ignored by the CoreAI hardware. The upper 2 bits are used to create the settings for each ACx input.</li> <li>0x000 to 0x0FF - Current Monitor (default)</li> <li>0x100 to 0x1FF - Digital Input</li> <li>0x200 to 0x2FF - Voltage Monitor</li> <li>0x300 to 0x3FF - Disabled</li> <li>For example, if CFG_AC7 is set to the value 0x000, the AC7 input will be used as an analog current monitor input. If CFG_AC7 is set to the value 0x100, the AC7 input will be used as an analog voltage monitor input. If CFG_AC7 is set to the value 0x200, the AC7 input will be used as an analog voltage monitor input. If CFG_AC7 is set to the value 0x200, the AC7 input will be used as an analog voltage monitor input. If CFG_AC7 is set to the value 0x200, the AC7 input will be used as an analog voltage monitor input. If CFG_AC7 is set to the value 0x300, the AC7 input will be used as an analog voltage monitor input. If CFG_AC7 is set to the value 0x300, the AC7 input will be used as an analog voltage monitor input. If CFG_AC7 is set to the value 0x300, the AC7 input will be used as an analog voltage monitor input. If CFG_AC7 is set to the value 0x300, the AC7 input will be used as an analog voltage monitor input. If CFG_AC7 is set to the value 0x300, the AC7 input will be used as an analog voltage monitor input. If CFG_AC7 is set to the value 0x300, the AC7 input will be used as an analog voltage monitor input. If CFG_AC7 is set to the value 0x300, the AC7 input will be disabled; in this case, the CoreAI AC7 input will not be used and the AC7 input of the AB macro will be hardwired to logic 0 within CoreAI.</li> </ul> |  |

| Name                                 | Valid<br>Range | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                | Configure ATx Inputs (hexadecimal values shown)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                      |                | Each of these parameters/generics is used to configure the AT9 down to AT0 inputs, respectively, connected to the AB macro. The lower 8 bits of each of these 10-bit integers are reserved for generating firmware settings for the target processor used with CoreAI and are ignored by the CoreAI hardware. The upper 2 bits are used to create the settings for each ATx input.                                                                                                                                                                                                                                 |

| CFG_AT9,CFG_AT8,                     |                | 0x000 to 0x0FF - Temperature Monitor (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CFG_AT7,CFG_AT6,                     |                | 0x100 to 0x1FF - Digital Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CFG_AT5,CFG_AT4,                     | 0 to 1,023     | 0x200 to 0x2FF - Voltage Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CFG_AT3,CFG_AT2,<br>CFG_AT1,CFG_AT0  |                | 0x300 to 0x3FF - Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      |                | For example, if CFG_AT2 is set to the value 0x000, the AT2 input will be used as an analog temperature monitor input. If CFG_AT2 is set to the value 0x100, the AT2 input will be used as a digital input, and the buffered DATOUT2 output would be connected to the user's own logic. If CFG_AT2 is set to the value 0x200, the AT2 input will be used as an analog voltage monitor input. If CFG_AT2 is set to the value 0x300, the AT2 input will be disabled; in this case, the CoreAI AT2 input will not be used and the AT2 input of the AB macro will be hardwired to logic 0 within CoreAI.                |

|                                      | 0 to 1,023     | Configure GDONx Gate Driver Control Inputs and AGx Gate Driver Outputs (hexadecimal values shown)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                      |                | Each of these parameters/generics is used to configure the GDON9 down to GDON0 inputs, respectively, connected to the AB macro, and the AG9 down to AG0 outputs, respectively, that are connected to the AB macro. The lower 8 bits of each of these 10-bit integers are reserved for generating firmware settings for the target processor used with CoreAI and are ignored by the CoreAI hardware. The upper 2 bits are used to create the settings for each GDONx input and AGx output.                                                                                                                         |

| CFG_GD9,CFG_GD8,<br>CFG_GD7,CFG_GD6, |                | 0x000 to 0x0FF - GDONx/AGx Software-controlled by internal register (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CFG_GD5,CFG_GD4,CFG                  |                | 0x100 to 0x1FF - GDONx/AGx Hardware-controlled by HD_GDONx input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| _GD3,CFG_GD2,                        |                | 0x200 to 0x2FF - Reserved (unused)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CFG_GD1,CFG_GD0                      |                | 0x300 to 0x3FF - Disabled (GDONx and AGx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      |                | For example, if CFG_GD1 is set to the value 0x00, the GDON1 input and AG1 gate-<br>driver output will be controlled by a software-controlled register within CoreAI (ADC<br>Control Register 5). If CFG_GD1 is set to the value 0x100, the HD_GDON1 input<br>(connected to the user's own logic) will be used to directly control the GDON1 input and<br>AG1 gate-driver output. If CFG_GD1 is set to the value 0x300, the GDON1 input and<br>AG1 output will be disabled; in this case, the CoreAI AG1 output will not be used and<br>the GDON1 input of the AB macro will be hardwired to logic 0 within CoreAI. |

#### Table 3-1 · CoreAl Parameter/Generic Description (continued)

| Name                                     | Valid<br>Range | Description                                                                                                                                                                                                                                                     |

|------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          |                | Configure use of RTC                                                                                                                                                                                                                                            |

|                                          |                | This parameter/generic controls whether or not the RTC is used                                                                                                                                                                                                  |

|                                          | 0 to 2         | 0 - Not used (default)                                                                                                                                                                                                                                          |

| CFG_RTC                                  |                | 1 - Used, the RTCPSMMATCH output is exposed on the SmartDesign canvas. You<br>must connect a Crystal Oscillator component and a Voltage Regulator component to your<br>design from the Libero IDE Catalog in the Fusion Peripherals category.                   |

|                                          |                | 2 - Used, the RTCPSMMATCH output is not exposed on the SmartDesign canvas. You must connect a Crystal Oscillator component to your design from the Libero IDE Catalog in the Fusion Peripherals category.                                                       |

|                                          |                | Consult the Libero IDE online help for information on how to connect Fusion peripherals to your design on the SmartDesign canvas.                                                                                                                               |

| CFG_RTC_COUNTER4,                        |                | Configure ACM RTC Counter Registers                                                                                                                                                                                                                             |

| CFG_RTC_COUNTER3,                        |                | Each of these parameters/generics is used to configure the RTC COUNTER4 down to                                                                                                                                                                                 |

| CFG_RTC_COUNTER2,                        | 0 to 255       | COUNTERO ACM registers, respectively, within the AB macro (see Table 18). Each of                                                                                                                                                                               |

| CFG_RTC_COUNTER1,                        |                | these 8-bit integers are reserved for generating firmware settings for the target processor                                                                                                                                                                     |

| CFG_RTC_COUNTER0                         |                | used with CoreAI and are ignored by the CoreAI hardware.                                                                                                                                                                                                        |