HB0562

Handbook

# CoreCIC v2.1

01 2018

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 E-mail: sales.support@microsemi.com www.microsemi.com

#### About Microsemi

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at <u>www.microsemi.com</u>.

©2018 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

# **Revision History**

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

## 1.1 Release 2.0

Updated this document for CoreCIC v2.1

## 1.2 Release 1.0

Revision 1.0 was the first publication of this document. Created for CoreCIC v2.0

# Contents

| Re | vision | n History                            | 3  |  |  |  |  |  |  |  |  |

|----|--------|--------------------------------------|----|--|--|--|--|--|--|--|--|

|    | 1.1    | Release 2.0                          | 3  |  |  |  |  |  |  |  |  |

|    | 1.2    | Release 1.0                          | 3  |  |  |  |  |  |  |  |  |

| 2  | Intro  | oduction                             | 8  |  |  |  |  |  |  |  |  |

|    | 2.1    | General Description                  |    |  |  |  |  |  |  |  |  |

|    | 2.2    | Key Features                         | 10 |  |  |  |  |  |  |  |  |

|    | 2.3    | Supported Families                   | 10 |  |  |  |  |  |  |  |  |

|    | 2.4    | Core Version                         | 10 |  |  |  |  |  |  |  |  |

|    | 2.5    | Utilization and Performance          | 11 |  |  |  |  |  |  |  |  |

| 3  | Theo   | ory of Operations                    | 16 |  |  |  |  |  |  |  |  |

|    | 3.1    | Moving Average                       | 16 |  |  |  |  |  |  |  |  |

|    |        | 3.1.1 CIC Filter Structures          | 17 |  |  |  |  |  |  |  |  |

|    | 3.2    | Multiple Channel Support             | 19 |  |  |  |  |  |  |  |  |

|    |        | 3.2.1 Multiple Interfaces            | 19 |  |  |  |  |  |  |  |  |

|    |        | 3.2.2 Comb and Integrator Time Share | 20 |  |  |  |  |  |  |  |  |

|    | 3.3    | Bit Growth                           | 21 |  |  |  |  |  |  |  |  |

| 4  | Inter  | rface Description                    | 22 |  |  |  |  |  |  |  |  |

|    | 4.1    | Parameters and Generics              | 22 |  |  |  |  |  |  |  |  |

|    | 4.2    | Ports                                | 23 |  |  |  |  |  |  |  |  |

|    |        | 4.2.1 Decimator Interface            | 27 |  |  |  |  |  |  |  |  |

|    |        | 4.2.2 Interpolator Interface         | 28 |  |  |  |  |  |  |  |  |

| 5  | Impl   | lementation Details                  | 32 |  |  |  |  |  |  |  |  |

|    | 5.1    | Reset                                | 32 |  |  |  |  |  |  |  |  |

|    | 5.2    | Latency                              | 32 |  |  |  |  |  |  |  |  |

|    | 5.3    | Multiple Interface Connections       | 32 |  |  |  |  |  |  |  |  |

|    | 5.4    | Variable Rate                        | 33 |  |  |  |  |  |  |  |  |

|    |        | 5.4.1 RAM Block Use                  | 34 |  |  |  |  |  |  |  |  |

|    | 5.5    | Decimation Filter Timing             | 34 |  |  |  |  |  |  |  |  |

|    | 5.6    | Interpolation Filter Timing          | 37 |  |  |  |  |  |  |  |  |

| 6  | Tool   | Flow                                 | 40 |  |  |  |  |  |  |  |  |

|    | 6.1    | License                              | 40 |  |  |  |  |  |  |  |  |

|    |        | 6.1.1 RTL                            | 40 |  |  |  |  |  |  |  |  |

|    | 6.2    | SmartDesign                          | 40 |  |  |  |  |  |  |  |  |

|    | 6.3    | Simulation Flows                     | 41 |  |  |  |  |  |  |  |  |

|    | 6.4    | Synthesis in Libero                  | 41 |  |  |  |  |  |  |  |  |

|    | 6.5    | Place-and-Route in Libero            | 42 |  |  |  |  |  |  |  |  |

| 7 | Testbench            | .43  |

|---|----------------------|------|

|   | 7.1 User Testbench   | . 43 |

| 8 | References           | .44  |

| 9 | Ordering Information | .45  |

|   | 9.1 Ordering Codes   | . 45 |

# **List of Figures**

| Figure 1 CIC Filter Application Examples                                                   | 9  |

|--------------------------------------------------------------------------------------------|----|

| Figure 2 Moving Average Block Diagram                                                      | 16 |

| Figure 3 Recursive Moving Average                                                          | 16 |

| Figure 4 Non-optimized Boxcar Decimator Filter                                             | 17 |

| Figure 5 Boxcar Interpolation Filter (Non-optimized)                                       | 17 |

| Figure 6 One-Stage CIC Decimation Filter                                                   | 17 |

| Figure 7 N-Stage Decimation CIC filter                                                     | 18 |

| Figure 8 One-Stage CIC Interpolation Filter                                                | 18 |

| Figure 9 N-Stage Interpolation CIC Filter                                                  | 18 |

| Figure 10 Three Interfaces, One Channel per Interface CIC Decimator                        | 19 |

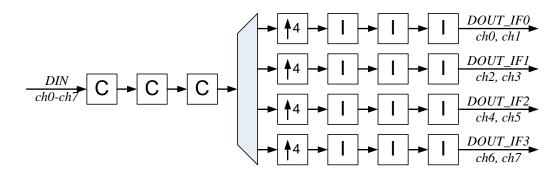

| Figure 11 Four Interfaces, One Channel per Interface CIC Interpolator                      | 20 |

| Figure 12 Three Interfaces, Two Channels per Interface CIC Decimator                       | 20 |

| Figure 13 Four Interfaces, Two Channels per Interface CIC Interpolator                     | 21 |

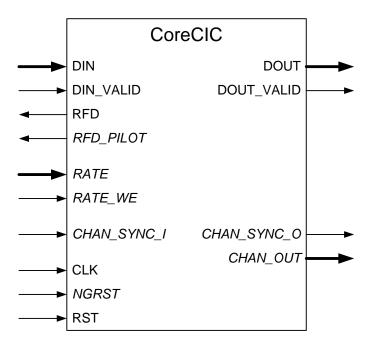

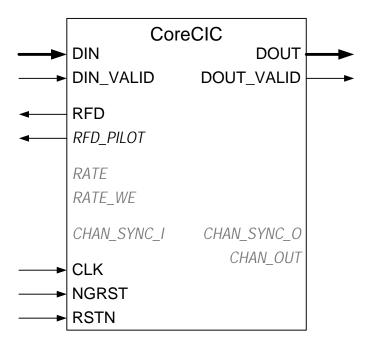

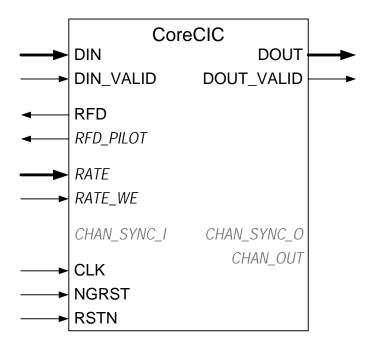

| Figure 14 I/O Ports                                                                        | 23 |

| Figure 15 Fixed Rate Single Channel CIC Filter                                             | 25 |

| Figure 16 Variable Rate Single Channel CIC Filter                                          | 26 |

| Figure 17 Fixed Rate Multiple Channel Mode                                                 | 26 |

| Figure 18 Using RFD_PILOT Signal                                                           | 29 |

| Figure 19 Example of Interpolator Input Signals at DIN_VALID Always Active                 | 30 |

| Figure 20 Example of Interpolator Input Signals at DIN_VALID Active Every Other Clock      | 30 |

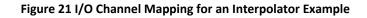

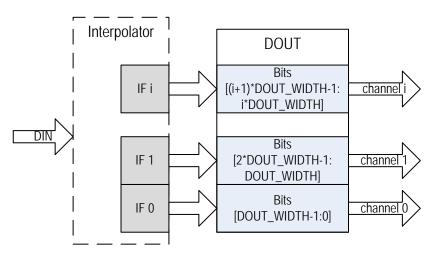

| Figure 21 I/O Channel Mapping for an Interpolator Example                                  | 31 |

| Figure 22 Data Concatenation for Multiple Interface Decimator                              | 33 |

| Figure 23 Output Concatenation of a Multiple Interface Interpolator                        | 33 |

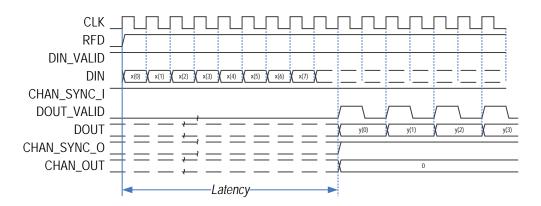

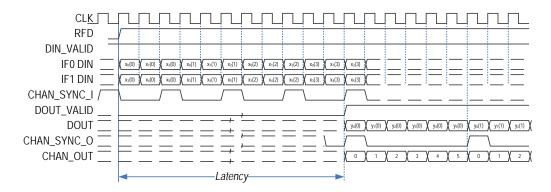

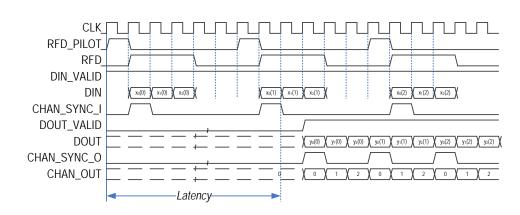

| Figure 24 Decimation CIC Timing - Single Channel, Data Permanently Valid                   | 34 |

| Figure 25 Decimation CIC Timing - Single Channel, Data Coming Every Other Clock            | 35 |

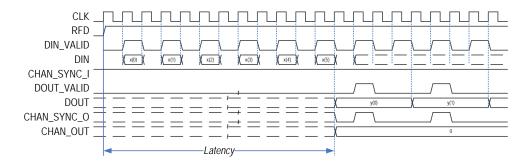

| Figure 26 Decimation CIC Timing - Three Time Share Channels, Data Permanently Valid        | 35 |

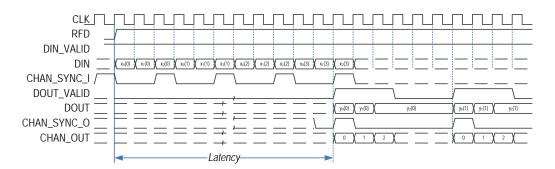

| Figure 27 Decimation CIC Timing - Two Interfaces, Data Permanently Valid                   | 36 |

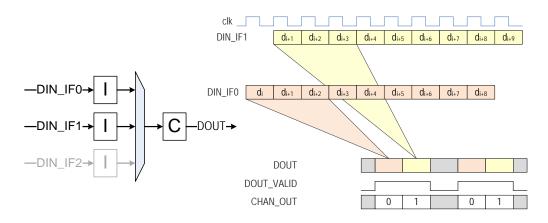

| Figure 28 6-Channel Decimator Timing - Two Interfaces Three Time Share Channels Each, Data |    |

| Always Valid                                                                               |    |

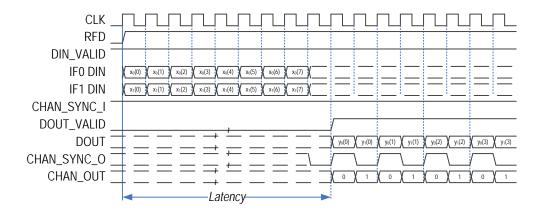

| Figure 29 Input Data Shift Between Interfaces IFO and IF1                                  |    |

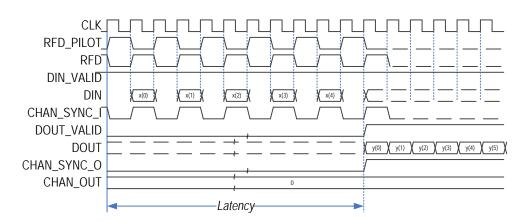

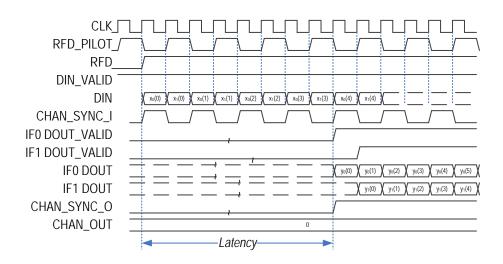

| Figure 30 Interpolation CIC Timing - Single Channel, Data Permanently Valid                |    |

| Figure 31 Interpolation CIC Timing - Single Channel, Data Coming Every Other Clock         |    |

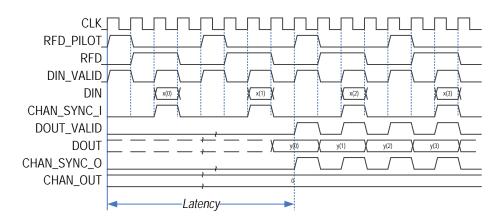

| Figure 32 Interpolation CIC Timing - Three Time Share Channels, Data Permanently Valid     |    |

| Figure 33 Interpolation CIC Timing - Two Interfaces, Data Permanently Valid                |    |

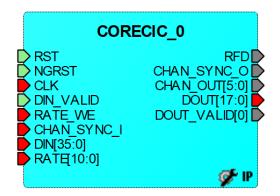

| Figure 34 CoreCIC Full I/O View                                                            |    |

| Figure 35 SmartDesign CoreCIC Configuration Window                                         |    |

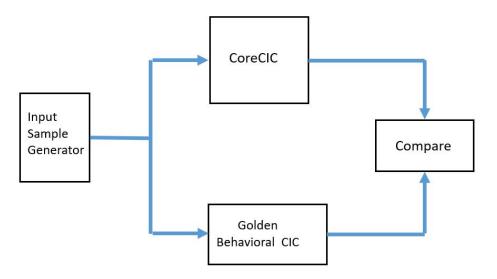

| Figure 36 CoreCIC User Testbench Simplified Block Diagram                                  | 43 |

# **List of Tables**

| Table 1 CIC Decimator Resource Utilization and Performance    | 11 |

|---------------------------------------------------------------|----|

| Table 2 CIC Interpolator Resource Utilization and Performance | 12 |

| Table 3 CIC Decimator Resource Utilization and Performance    | 13 |

| Table 4 CIC Interpolator Resource Utilization and Performance | 14 |

| Table 5 CoreCIC Parameter and Generic Descriptions            | 22 |

| Table 6 CIC Filter In or Out Signals                          | 24 |

| Table 7 Ordering Codes                                        | 45 |

## 2 Introduction

## 2.1 General Description

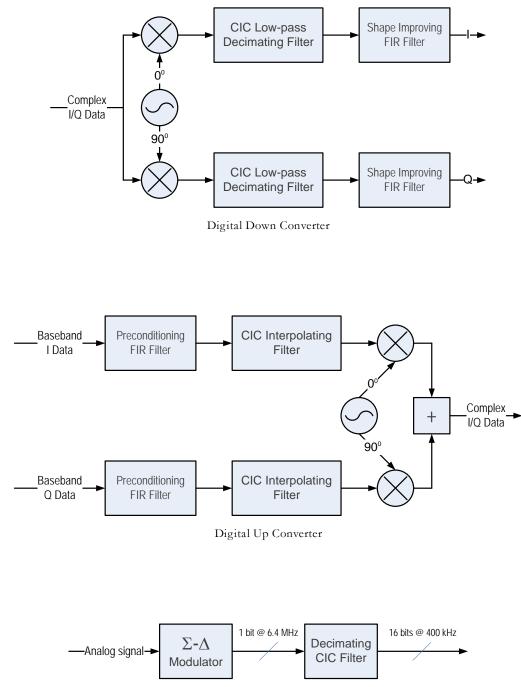

Microsemi<sup>®</sup> CoreCIC IP is a highly configurable RTL generator for the decimation or interpolation cascaded integrator-comb (CIC) filters. The CIC filters are widely used in multi-rate signal processing, particularly in up-converters and down-converters, modulators and demodulators, sigma-delta analog to digital converters, and so on. These filters are popular in decimation and interpolation filters where substantial rate change factor is required. The CIC filters provide a linear phase response.

The following figure shows a few application examples of the CIC filter.

#### Figure 1 CIC Filter Application Examples

$\Sigma - \Delta$  ADC

## 2.2 Key Features

CoreCIC supports decimation and interpolation filter types. Following are the key features of CoreCIC filter:

- Fixed or programmable rate change from 2 to 1024

- One to eight integrator-comb stages

- Comb differential delay of one or two

- Signed 2's complement input data

- Input data width from 1 to 32 bits

- Output data width up to 100 bits

- Choice of output data truncation and two rounding types

- Optional Hogenauer pruning

- Support for up to 64 channels

## 2.3 Supported Families

CoreCIC supports the following families:

- PolarFire<sup>®</sup>

- RTG4™

- IGLOO<sup>®</sup>2

- SmartFusion<sup>®</sup>2

## 2.4 Core Version

This handbook applies to CoreCIC v2.1.

## 2.5 Utilization and Performance

The resource utilization and core performance are shown on Table 1 and Table 2 for SmartFusion2 M2S050 device, speed grade -1.

| Configur         | ation                                           |                    |                  |              |                 | Resource Utilization |       |           |          | Maximum            |

|------------------|-------------------------------------------------|--------------------|------------------|--------------|-----------------|----------------------|-------|-----------|----------|--------------------|

| Input Data Width | Output Data Width                               | Rate Change Factor | Number of Stages | Number of IF | Channels per IF | 4LUT                 | DFF   | RAM 64x18 | RAM 1K18 | Clock Rate,<br>MHz |

| RAM blo          | RAM blocks are not used; Differential Delay = 1 |                    |                  |              |                 |                      |       |           |          |                    |

| 16               | 16                                              | 4                  | 3                | 1            | 1               | 751                  | 730   | 0         | 0        | 385                |

| 16               | 16                                              | 4                  | 3                | 4            | 1               | 1,905                | 1,902 | 0         | 0        | 345                |

| 16               | 16                                              | 4                  | 3                | 1            | 5               | 1,452                | 1,706 | 0         | 0        | 314                |

| 16               | 16                                              | 40                 | 3                | 1            | 1               | 1,063                | 1,022 | 0         | 0        | 341                |

| 16               | 16                                              | 40                 | 3                | 4            | 1               | 2,713                | 2,702 | 0         | 0        | 331                |

| 16               | 16                                              | 40                 | 3                | 1            | 5               | 2,030                | 2,388 | 0         | 0        | 313                |

| 16               | 16                                              | 4                  | 2                | 1            | 1               | 511                  | 495   | 0         | 0        | 386                |

| 16               | 16                                              | 4                  | 2                | 4            | 1               | 1,241                | 1,224 | 0         | 0        | 366                |

| 16               | 16                                              | 4                  | 2                | 1            | 5               | 956                  | 1,023 | 0         | 0        | 358                |

| RAM blo          | cks are not                                     | used; Diff         | erential De      | elay = 2     |                 |                      |       |           |          |                    |

| 16               | 16                                              | 4                  | 3                | 1            | 5               | 1,989                | 2,217 | 0         | 0        | 317                |

| 16               | 16                                              | 4                  | 5                | 1            | 1               | 1,849                | 1,959 | 0         | 0        | 336                |

| 16               | 16                                              | 4                  | 5                | 4            | 1               | 4,749                | 4,803 | 0         | 0        | 306                |

| 16               | 16                                              | 4                  | 5                | 1            | 5               | 3,880                | 4,506 | 0         | 0        | 304                |

| Use RAN          | 1 blocks is C                                   | Dn; Maxim          | um MicroR        | AM Depth     | =64; Differ     | rential Delay        | r = 1 |           |          |                    |

| 12               | 16                                              | 4                  | 3                | 4            | 14              | 2,232                | 2,090 | 15        | 0        | 250                |

| 30               | 18                                              | 4                  | 3                | 4            | 14              | 4,238                | 4,008 | 30        | 0        | 250                |

| Use RAN          | 1 blocks is C                                   | Dn; Maxim          | um MicroR        | AM Depth     | =0; Differe     | ential Delay :       | = 1   |           |          |                    |

| 12               | 16                                              | 4                  | 3                | 4            | 16              | 2,244                | 2,096 | 0         | 15       | 287                |

| 30               | 18                                              | 4                  | 3                | 4            | 16              | 3,712                | 3,476 | 0         | 15       | 286                |

| 12               | 16                                              | 4                  | 2                | 4            | 16              | 1,466                | 1,355 | 0         | 10       | 317                |

| 30               | 18                                              | 4                  | 2                | 4            | 16              | 2,479                | 2,299 | 0         | 10       | 317                |

| Use RAN          | 1 blocks is C                                   | Dn; Maxim          | um MicroF        | AM Depth     | =0; Differe     | ential Delay         | = 2   |           |          |                    |

| 12               | 16                                              | 4                  | 2                | 4            | 16              | 1,558                | 1,433 | 0         | 10       | 315                |

| 30               | 18                                              | 4                  | 2                | 4            | 16              | 2,575                | 2,376 | 0         | 10       | 308                |

#### Table 1 CIC Decimator Resource Utilization and Performance

| Configura       |                   |                    | erpolator        | Resource     | Resource Utilization |          |       |           | Maximum  |              |

|-----------------|-------------------|--------------------|------------------|--------------|----------------------|----------|-------|-----------|----------|--------------|

| comgura         |                   |                    |                  |              | nesource c           |          |       |           | Clock    |              |

| nput Data Width | Output Data Width | Rate Change Factor | Number of Stages | Number of IF | Channels per IF      | 4LUT     | DFF   | RAM 64x18 | RAM 1K18 | Rate,<br>MHz |

| RAM bloc        | ks are not        | _                  | _                | ay = 1       |                      |          |       |           | . –      | L            |

| 16              | 16                | 4                  | 3                | 1            | 1                    | 639      | 604   | 0         | 0        | 383          |

| 16              | 16                | 4                  | 3                | 4            | 1                    | 1,756    | 1,756 | 0         | 0        | 345          |

| 16              | 16                | 4                  | 3                | 1            | 5                    | 1,335    | 1,554 | 0         | 0        | 330          |

| 16              | 16                | 40                 | 3                | 1            | 1                    | 716      | 667   | 0         | 0        | 333          |

| 16              | 16                | 40                 | 3                | 4            | 1                    | 1,905    | 1,886 | 0         | 0        | 327          |

| 16              | 16                | 40                 | 3                | 1            | 5                    | 1,447    | 1,703 | 0         | 0        | 320          |

| 16              | 16                | 4                  | 2                | 1            | 1                    | 441      | 410   | 0         | 0        | 375          |

| 16              | 16                | 4                  | 2                | 4            | 1                    | 1,179    | 1,168 | 0         | 0        | 329          |

| 16              | 16                | 4                  | 2                | 1            | 5                    | 891      | 1,002 | 0         | 0        | 324          |

| RAM bloc        | ks are not        | used; Diffe        | rential Dela     | iy = 2       |                      |          |       |           |          |              |

| 16              | 16                | 4                  | 3                | 1            | 5                    | 1,622    | 1,870 | 0         | 0        | 316          |

| 16              | 16                | 4                  | 5                | 1            | 1                    | 1,335    | 1,377 | 0         | 0        | 334          |

| 16              | 16                | 4                  | 5                | 4            | 1                    | 3,703    | 3,731 | 0         | 0        | 325          |

| 16              | 16                | 4                  | 5                | 1            | 5                    | 2,927    | 3,478 | 0         | 0        | 301          |

| Use RAM         | blocks is O       | n; Max Mic         | roRAM De         | pth=64; Dif  | ferential D          | elay = 1 |       |           |          |              |

| 11              | 16                | 4                  | 3                | 4            | 14                   | 2,246    | 2,118 | 15        | 0        | 250          |

| 29              | 18                | 4                  | 3                | 4            | 14                   | 4,157    | 3,996 | 30        | 0        | 250          |

| Use RAM         | blocks is O       | n; Max Mic         | roRAM De         | pth=0; Diff  | erential De          | lay = 1  |       |           |          |              |

| 11              | 16                | 4                  | 3                | 4            | 16                   | 2,257    | 2,124 | 0         | 15       | 327          |

| 29              | 18                | 4                  | 3                | 4            | 16                   | 3,627    | 3,462 | 0         | 15       | 307          |

| 11              | 16                | 4                  | 2                | 4            | 16                   | 1,500    | 1,392 | 0         | 10       | 340          |

| 29              | 18                | 4                  | 2                | 4            | 16                   | 2,441    | 2,310 | 0         | 10       | 320          |

| Use RAM         | blocks is O       | n; Max Mic         | roRAM De         | pth=0; Diff  | erential De          | lay = 2  | 1     |           |          | 1            |

| 12              | 16                | 4                  | 2                | 4            | 16                   | 1,554    | 1,445 | 0         | 10       | 332          |

| 30              | 18                | 4                  | 2                | 4            | 16                   | 2,489    | 2,351 | 0         | 10       | 312          |

#### Table 2 CIC Interpolator Resource Utilization and Performance

The results shown on Table 1 and Table 2 were achieved at the Operating Conditions COM. The following tools were used:

- Libero v11.4.

- SynplifyPro H-2013.03M-SP1-1.

The other core parameters were set as follows:

• Enable Variable Rate = No

- Apply Hogenauer Pruning = No

- Rounding Mode = Truncation

The utilization and core performance data are shown in Table 3 and Table 4 for PolarFire (MPF300T) Device family. The overall device utilization and performance of the core is system dependent.

|                  | Table 3 CIC Decimator Resource Utilization and Performance |                    |                  |              |                 |               |             |           |          |                    |

|------------------|------------------------------------------------------------|--------------------|------------------|--------------|-----------------|---------------|-------------|-----------|----------|--------------------|

| Configura        | ation                                                      |                    |                  |              |                 | Resource l    | Jtilization |           |          | Maximum            |

| Input Data Width | Output Data Width                                          | Rate Change Factor | Number of Stages | Number of IF | Channels per IF | 41UT          | DFF         | RAM 64x12 | RAM 1K20 | Clock Rate,<br>MHz |

| RAM blo          | RAM blocks are not used; Differential Delay = 1            |                    |                  |              |                 |               |             |           |          |                    |

| 16               | 16                                                         | 4                  | 3                | 1            | 1               | 690           | 668         | 0         | 0        | 303.8              |

| 16               | 16                                                         | 4                  | 3                | 4            | 1               | 1,814         | 1804        | 0         | 0        | 322.7              |

| 16               | 16                                                         | 4                  | 3                | 1            | 5               | 1,431         | 1661        | 0         | 0        | 310.6              |

| 16               | 16                                                         | 40                 | 3                | 1            | 1               | 996           | 960         | 0         | 0        | 232.5              |

| 16               | 16                                                         | 40                 | 3                | 4            | 1               | 2,623         | 2612        | 0         | 0        | 240.9              |

| 16               | 16                                                         | 40                 | 3                | 1            | 5               | 2,009         | 2343        | 0         | 0        | 240.9              |

| 16               | 16                                                         | 4                  | 2                | 1            | 1               | 450           | 434         | 0         | 0        | 307.7              |

| 16               | 16                                                         | 4                  | 2                | 4            | 1               | 1,153         | 1132        | 0         | 0        | 328.8              |

| 16               | 16                                                         | 4                  | 2                | 1            | 5               | 910           | 1048        | 0         | 0        | 306.6              |

| RAM blo          | cks are not                                                | used; Diffe        | erential De      | lay = 2      |                 |               | -           |           |          |                    |

| 16               | 16                                                         | 4                  | 3                | 1            | 5               | 1,984         | 2225        | 0         | 0        | 215.6              |

| 16               | 16                                                         | 4                  | 5                | 1            | 1               | 1,805         | 1897        | 0         | 0        | 208.2              |

| 16               | 16                                                         | 4                  | 5                | 4            | 1               | 4,677         | 4706        | 0         | 0        | 205.1              |

| 16               | 16                                                         | 4                  | 5                | 1            | 5               | 3,918         | 4461        | 0         | 0        | 224.6              |

| Use RAM          | blocks is C                                                | Dn; Maxim          | um MicroR        | AM Depth     | =64; Differ     | ential Delay  | 2 = 1       |           |          |                    |

| 12               | 16                                                         | 4                  | 3                | 4            | 14              | 1955          | 1965        | 30        | 0        | 171.9              |

| 30               | 18                                                         | 4                  | 3                | 4            | 14              | 3507          | 3153        | 45        | 0        | 171.9              |

| Use RAM          | blocks is C                                                | Dn; Maxim          | um MicroR        | AM Depth     | =0; Differe     | ntial Delay = | = 1         |           |          |                    |

| 12               | 16                                                         | 4                  | 3                | 4            | 16              | 2,148         | 2019        | 0         | 15       | 178.6              |

| 30               | 18                                                         | 4                  | 3                | 4            | 16              | 3,519         | 3321        | 0         | 15       | 178.6              |

| 12               | 16                                                         | 4                  | 2                | 4            | 16              | 1,377         | 1278        | 0         | 10       | 179.3              |

| 30               | 18                                                         | 4                  | 2                | 4            | 16              | 2,316         | 2,148       | 0         | 10       | 178.6              |

| Use RAM          | blocks is C                                                | Dn; Maxim          | um MicroR        | AM Depth     | =0; Differe     | ntial Delay = | = 2         |           |          |                    |

| 12               | 16                                                         | 4                  | 2                | 4            | 16              | 1,463         | 1355        | 0         | 10       | 178.5              |

| 30               | 18                                                         | 4                  | 2                | 4            | 16              | 2,402         | 2225        | 0         | 10       | 178.0              |

Table 3 CIC Decimator Resource Utilization and Performance

| Configure        |                                                 |                    |                  | n Resource   | ion and Performance<br>Resource Utilization |             |       |           | Maximum  |             |

|------------------|-------------------------------------------------|--------------------|------------------|--------------|---------------------------------------------|-------------|-------|-----------|----------|-------------|

| Configuration    |                                                 |                    |                  |              |                                             | Resource    |       |           |          | Clock Rate, |

| Input Data Width | Output Data Width                               | Rate Change Factor | Number of Stages | Number of IF | Channels per IF                             | 41UT        | DFF   | RAM 64x12 | RAM 1K20 | MHz         |

| RAM bloc         | RAM blocks are not used; Differential Delay = 1 |                    |                  |              |                                             |             |       |           |          |             |

| 16               | 16                                              | 4                  | 3                | 1            | 1                                           | 623         | 588   | 0         | 0        | 324.5       |

| 16               | 16                                              | 4                  | 3                | 4            | 1                                           | 1685        | 1685  | 0         | 0        | 315.7       |

| 16               | 16                                              | 4                  | 3                | 1            | 5                                           | 1308        | 1510  | 0         | 0        | 233.1       |

| 16               | 16                                              | 40                 | 3                | 1            | 1                                           | 754         | 716   | 0         | 0        | 217.3       |

| 16               | 16                                              | 40                 | 3                | 4            | 1                                           | 1873        | 1869  | 0         | 0        | 207.9       |

| 16               | 16                                              | 40                 | 3                | 1            | 5                                           | 1495        | 1726  | 0         | 0        | 204.5       |

| 16               | 16                                              | 4                  | 2                | 1            | 1                                           | 421         | 388   | 0         | 0        | 333.9       |

| 16               | 16                                              | 4                  | 2                | 4            | 1                                           | 1,105       | 1094  | 0         | 0        | 316.5       |

| 16               | 16                                              | 4                  | 2                | 1            | 5                                           | 848         | 960   | 0         | 0        | 233.1       |

| RAM bloc         | ks are not                                      | used; Diffe        | erential De      | lay = 2      |                                             |             |       |           |          |             |

| 16               | 16                                              | 4                  | 3                | 1            | 5                                           | 1608        | 1828  | 0         | 0        | 233.1       |

| 16               | 16                                              | 4                  | 5                | 1            | 1                                           | 1,335       | 1375  | 0         | 0        | 302.9       |

| 16               | 16                                              | 4                  | 5                | 4            | 1                                           | 3,647       | 3674  | 0         | 0        | 213.6       |

| 16               | 16                                              | 4                  | 5                | 1            | 5                                           | 2,961       | 3435  | 0         | 0        | 233.1       |

| Use RAM          | blocks is C                                     | Dn; Max M          | icroRAM D        | epth=64; I   | Differentia                                 | l Delay = 1 |       |           |          |             |

| 11               | 16                                              | 4                  | 3                | 4            | 14                                          | 1939        | 1906  | 29        | 0        | 174.8       |

| 29               | 18                                              | 4                  | 3                | 4            | 14                                          | 3460        | 3536  | 45        | 0        | 174.8       |

| Use RAM          | blocks is C                                     | Dn; Max M          | icroRAM D        | epth=0; Di   | ifferential I                               | Delay = 1   |       |           |          |             |

| 11               | 16                                              | 4                  | 3                | 4            | 16                                          | 2,137       | 2032  | 0         | 15       | 184.3       |

| 29               | 18                                              | 4                  | 3                | 4            | 16                                          | 3,472       | 3344  | 0         | 15       | 181.7       |

| 11               | 16                                              | 4                  | 2                | 4            | 16                                          | 1394        | 1,306 | 0         | 10       | 181.7       |

| 29               | 18                                              | 4                  | 2                | 4            | 16                                          | 2300        | 2194  | 0         | 10       | 181.7       |

| Use RAM          | blocks is C                                     | Dn; Max M          | icroRAM D        | epth=0; Di   | ifferential I                               | Delay = 2   |       |           |          |             |

| 12               | 16                                              | 4                  | 2                | 4            | 16                                          | 1,492       | 1403  | 0         | 10       | 181.6       |

| 30               | 18                                              | 4                  | 2                | 4            | 16                                          | 2,389       | 2283  | 0         | 10       | 181.6       |

#### **Table 4 CIC Interpolator Resource Utilization and Performance**

Note: The data in this table is achieved using typical synthesis and layout settings. Frequency (in MHz ) was set to 100 and speed grade was -1.

The results shown in Table 3 and Table 4 were achieved at the operating Conditions COM. The following tools were used:

- Libero PolarFire v1.1

- Synplify Pro ME L-2016.09M-G5

The core parameter were set as follows:

- Enable Variable rate = No

- Apply Hogenauer Pruning = No

- Rounding Mode = Truncation.

## **3** Theory of Operations

## 3.1 Moving Average

The moving average is one of the most common filters in digital signal processing (DSP) and also called a boxcar filter. As the name implies, it averages a number of L input samples to generate each output sample:

$$y(k) = \frac{1}{L} \sum_{j=0}^{L-1} X(k+j)$$

EQ1

The filter calculates a time domain convolution between an input signal and a boxcar function. A frequency domain counterpart for the boxcar is sin(X)/X, which describes the frequency response of the filter. Hence, sinc filter is another name for moving average and CIC filters.

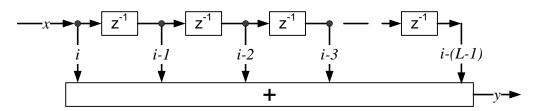

The following figure shows block diagram of the moving average filter except dividing the output by L.

#### Figure 2 Moving Average Block Diagram

The same result can be obtained by using a recursive form of the boxcar filter as shown in the following figure. An integrator accumulates input samples, while a comb adds a new accumulated sum and subtracts a delayed by L version of the sum.

#### Figure 3 Recursive Moving Average

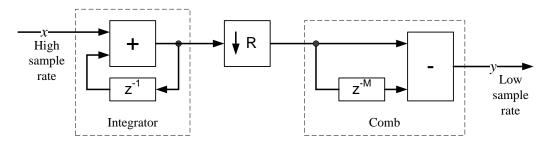

A recursive boxcar decimation filter adds a down-sampler by R where R is the decimation ratio. The following figure shows a non-optimized decimation filter assuming the delay L = M \* R, where, M is a constant coefficient called differential delay. M = 1 or 2. The down-sampler by R  $\downarrow$ R discards R-1 output samples from every R samples.

#### Figure 4 Non-optimized Boxcar Decimator Filter

The following figure shows a non-optimized interpolation filter structure.

#### Figure 5 Boxcar Interpolation Filter (Non-optimized)

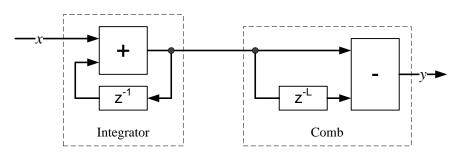

#### 3.1.1 CIC Filter Structures

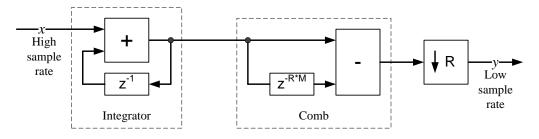

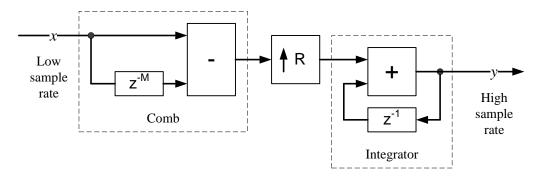

A CIC decimation filter is based on an optimized structure obtained from the non-optimized boxcar decimator block diagram as shown in Figure 4 (see References, 1 and 2). The following figure shows a one-stage CIC filter block diagram after placing the downsampler between the integrator and comb filter.

#### Figure 6 One-Stage CIC Decimation Filter

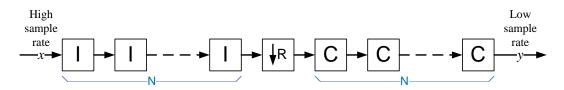

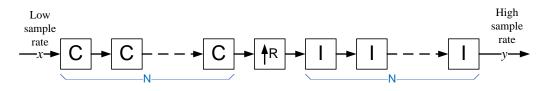

The following figure shows a cascaded N-stage decimation CIC filter where the integrators and combs are denoted as I and C, respectively. The filter contains N integrators and N combs. The frequency response is same as N cascaded boxcar filters.

Figure 7 N-Stage Decimation CIC filter

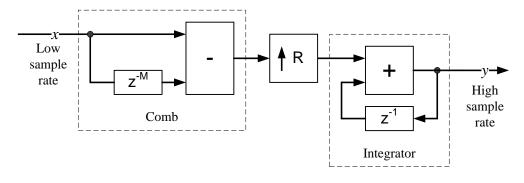

An interpolation CIC filter optimizes the structure, refer to Figure 5.

The following figure shows a one-stage interpolation CIC filter.

#### Figure 8 One-Stage CIC Interpolation Filter

The following figure shows an N-stage interpolation CIC filter.

#### Figure 9 N-Stage Interpolation CIC Filter

The CIC filter implementations are preferred over other rate changing filters because they only use adders and delays but not multipliers.

If the impulse response of a one- stage boxcar filter has a width of M  $^*$  R, the N cascades of identical boxcar filters have the overall Impulse Response Width of (M $^*$ R-1) $^*$ N+1.

EQ3 describes the system response of the CIC filter (see Reference 3):

$$H(z) = \left[\sum_{k=0}^{M*R-1} z^{-k}\right]^N$$

EQ2

## 3.2 Multiple Channel Support

#### 3.2.1 Multiple Interfaces

CIC filters of same configuration can share adders, subtractors, and other resources to process more channels, if the required data processing rate is relatively slow. This rate is always low for the CIC filter comb section where comb processing rate is R times lower than the processing rate of the integrator section, refer to Figure 7 and Figure 9. Thus a single comb can support up to R integrator sections. To fully utilize the comb section throughput, a CIC filter needs R integrator sections, each processing data at high sampling rate. In this handbook, such resource sharing is called comb sharing.

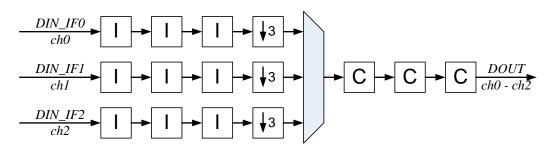

The following figure shows a 3-channel filter with a decimation factor, R\_RATE = 3. The CIC filter has three integrator sections, and is capable of filtering three input samples per clock. The data samples from the channels are fed at each clock interval.

The downsampled data from integrator are multiplexed so that each channel data occupies a separate time slot of one clock cycle. The comb section utilizes the three clock intervals (obtained due to reduction in the rate by a factor of 3) to process the integrated data samples.

The following figure shows a structure that has three interfaces namely, DIN\_IF0, DIN\_IF1, DIN\_IF2 and one output for the time-multiplexed output samples. For the core to generate the structure of three interfaces, one channel per interface CIC decimator, set the parameters as follows:

- IF\_NUM = 3

- CLK\_PER\_SAMPLE = 1

Figure 10 Three Interfaces, One Channel per Interface CIC Decimator

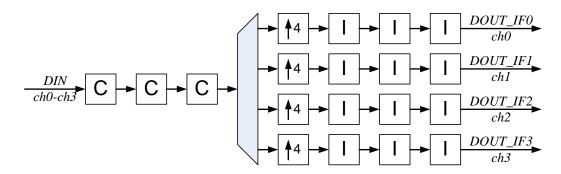

Similarly, the interpolation CIC filter can apply comb sharing to process more channels. The following figure shows an example of a 4-channel filter with interpolation rate factor of four. The low rate input channels are time-multiplexed, and the structure provides four output interfaces DOUT\_IF0 to DOUT\_IF3.

Set the parameter as:

- CLK\_PER\_SAMPLE = 1

- IF\_NUM = 4

#### Figure 11 Four Interfaces, One Channel per Interface CIC Interpolator

#### 3.2.2 Comb and Integrator Time Share

The input samples of each decimation channel can arrive at lower rate than the field programmable gate array (FPGA) clock rate, that is, there are idle clock intervals in between the samples of each input channel. Since they arrive at a lower rate, the integrator sections can be time shared as well. This handbook refers this as time sharing. The following figure shows a multi-channel CIC decimation example where input samples of every channel are separated by one idle clock cycle. If this instance is created when CLK\_PER\_SAMPLE = 2, each integrator can use two clock intervals, which is adequate to process two channels. The comb section has now six clock intervals, adequate to process all six channels. Every interface supports two channels totaling at CLK\_PER\_SAMPLE\*IF\_NUM = 6 channels.

# $\begin{array}{c} \underline{DIN\_IF0} \\ \hline ch0, ch1 \end{array} \qquad 1 \rightarrow 1 \rightarrow 1 \rightarrow 43 \rightarrow \\ \hline \underline{DIN\_IF1} \\ \hline ch2, ch3 \rightarrow 1 \rightarrow 1 \rightarrow 1 \rightarrow 43 \rightarrow \\ \hline \underline{DIN\_IF2} \\ \hline ch4, ch5 \rightarrow 1 \rightarrow 1 \rightarrow 1 \rightarrow 43 \rightarrow \\ \hline \end{array}$

#### Figure 12 Three Interfaces, Two Channels per Interface CIC Decimator

The time and comb sharing are independent of each other and can be combined as desired in decimation and interpolation CIC filter types. The following figure shows the CIC structure with four output interfaces and two channels per interface, totaling at CLK\_PER\_SAMPLE\*IF\_NUM = 8 channels.

The total number of channels processed by the CIC filter equals the product of the parameters IF\_NUM and CLK\_PER\_SAMPLE. If the product is more than the actual number of channels to be processed, use dummy channels.

CoreCIC automatically identifies multiple channel filters, if the product of IF\_NUM\*CLK\_PER\_SAMPLE > 1 and implements time and/or comb sharing based on the CLK\_PER\_SAMPLE and IF\_NUM parameter values.

#### Figure 13 Four Interfaces, Two Channels per Interface CIC Interpolator

## **3.3** Bit Growth

Data path width of the CIC filter needs to grow from input to output to support valid processing. The core automatically provides the required bit width for every component of the design. Internally, the processing results are calculated with full precision. You can limit the output bit width by entering a desired value in the Output Data Width field of the IP user interface and select truncation or rounding from **Rounding Mode** drop-down list. The core supports truncation, round away from 0 and convergent rounding (rounding to nearest even number). Either type of rounding or truncation applies to a full precision internal result.

CoreCIC in Decimation mode also supports optional Hogenauer pruning, which limits the intermediate stage bit widths as described in the article by E.Hogenauer. The core does not calculate full precision results even internally but limits their bit width in accordance with the approach by Hogenauer. When the reduced precision internal result still exceeds the desirable output bit width, the truncation or rounding applies similar to the full precision results. The Hogenauer pruning may reduce resource utilization.

# 4 Interface Description

## 4.1 Parameters and Generics

The following table describes the CoreCIC parameters (Verilog) or generics (VHDL). All the parameters and generics are positive integer type numbers.

| Parameter Name | Valid<br>Range | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N_STAGES       | 1-8            | 3       | Number of cascaded stages. There is always equal number of integrator<br>and comb stages. Any selected number N_STAGES means the CIC filter has<br>N_STAGES of integrators and N_STAGES of combs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| M_DLY          | 1, 2           | 1       | Differential comb delay M.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CIC_TYPE       | 0, 1           | 0       | 0: Decimation CIC filter.<br>1: Interpolation CIC filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DIN_WIDTH      | 1-32           | 18      | Input data bit width.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VAR_RATE       | 0, 1           | 0       | 0: Fixed rate change factor.<br>1: Variable programmable rate change factor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| R_RATE         | 2-1024         | 4       | Rate change factor R. If variable rate change is disabled VAR_RATE = 0, the R_RATE defines fixed rate change factor. Otherwise it defines an initial value of the variable factor set upon core configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VAR_R_MIN      | 2-1023         | 4       | Minimal variable rate change factor. Available only if VAR_RATE is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VAR_R_MAX      | 3-1024         | 5       | Maximal variable rate change factor. Available only if VAR_RATE is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PRUNE          | 0-1            | 0       | <ol> <li>Apply Hogenauer pruning across decimation filter stages. Available for<br/>decimation filter only, that is when CIC_TYPE = 0.</li> <li>Do not apply pruning.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DOUT_WIDTH     | 2-100          | 18      | Output data bit width. If the width set is less than full output bit width, the core truncates or rounds the filtered data to the DOUT_WIDTH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| QUANTIZATION   | 0-2            | 0       | Output data quantization mode. Applies when the output data bit width<br>selected is less than the automatic full precision processing bit width:<br>0: Truncation mode.<br>1: Round away from 0.<br>2: Convergent rounding.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IF_NUM         | 1-32           | 1       | Number of interfaces. For decimation filter, it is a number of input<br>interfaces; for interpolation filter it is a number of output interfaces. Each<br>interface is capable of accepting or generating one or more data channels.<br>In other words, IF_NUM indicates a number of physical integrator cascades<br>implemented.<br>IF_NUM cannot exceed the rate change factor R_RATE, that is IF_NUM ≤<br>R_RATE. In the case of variable rate (VAR_RATE=1), the IF_NUM cannot<br>exceed the value of VAR_R_MIN, that is IF_NUM ≤ VAR_R_MIN.<br>Since the channel number of a multichannel filter equals<br>IF_NUM * CLK_PER_SAMPLE, and the maximum channel count is 64, the<br>IF_NUM must not exceed the value of 64/CLK_PER_SAMPLE. |

Table 5 CoreCIC Parameter and Generic Descriptions

| Table 5 CoreCIC Parameter and Generic Description | ns |

|---------------------------------------------------|----|

|---------------------------------------------------|----|

| Parameter Name | Valid<br>Range                                    | Default | Description                                                                                                                                                                                                                                                                                                                                       |

|----------------|---------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_PER_SAMPLE | 1-64                                              | 1       | Number of FPGA clock cycles per sample of any channel.<br>Indicates a number of time-multiplexed channels per interface.<br>Since the channel number of a multichannel filter equals<br>IF_NUM * CLK_PER_SAMPLE, and the maximum channel count is 64, the<br>CLK_PER_SAMPLE must not exceed the value of 64/IF_NUM.                               |

| USE_RAM        | 0, 1                                              | 0       | Use RAM blocks to implement CIC registers.<br>0: Use only fabric-based register implementations.<br>1: Permission to use RAM blocks when appropriate.                                                                                                                                                                                             |

| URAM_MAX_DEPTH | 0, 4, 8, 16,<br>32, 64,<br>128, 256,<br>512, 1024 | 0       | Maximum depth of a RAM to be implemented using micro-RAM (uRAM)<br>blocks. If USE_RAM is set, the core uses hard RAM blocks available on a<br>selected FPGA device. When the uRAM blocks are available, the core uses<br>them if the required memory depth does not exceed the URAM_DEPTH.<br>Otherwise it builds the memory out of LSRAM blocks. |

## 4.2 Ports

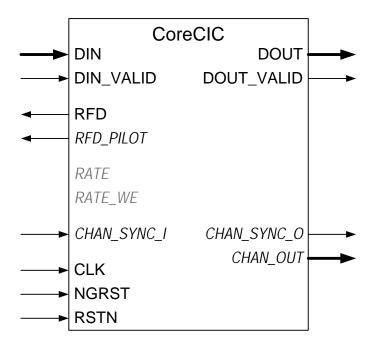

The following figure shows the CIC filter schematic representation where optional port names are in Italics.

#### Figure 14 I/O Ports

The pinout is a superset of all possible ports. The following table provides the port definitions for the core.

| Signal      | In/Out | Port Width Bits                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

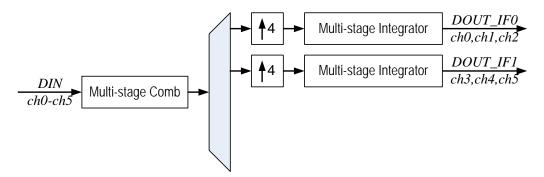

|-------------|--------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIN         | In     | DIN_WIDTH for<br>Interpolation CIC;<br>DIN_WIDTH*IF_NUM for<br>decimation filter   | Input data to be filtered. In case of interpolation filter or a<br>single channel for any CIC type, the data width equals<br>DIN_WIDTH. In case of decimation filter with multiple<br>Interfaces, the input data width for each interface is<br>DIN_WIDTH and the total input data width =<br>DIN_WIDTH*IF_NUM.                                                                                                                                                                                                                                                                                         |

| DIN_VALID   | In     | 1                                                                                  | Input data valid. Active High. When the signal is active, the input data sample is loaded into decimation CIC filter. If not used, the core assumes that every data sample is valid.<br>For the interpolation CIC filter, the signal not only marks the valid input sample but also defines a rate for the interpolated output samples. For example, if DIN_VALID has a duty cycle of three, the output sample rate is three times less than the CLK rate. The input sample of the interpolator is valid, if it is accompanied by DIN_VALID and CHAN_SYNC_I signals. The signal must be one-clock wide. |

| RFD         | Out    | 1                                                                                  | Ready for input data. In case of interpolation filter, the RFD notifies a data source that the CIC filter is ready for a new input sample. In case of decimation filter, the signal goes Low only when integrator reset process is underway. Input data samples are ignored when RFD is Low.                                                                                                                                                                                                                                                                                                            |

| RFD_PILOT   | Out    | 1                                                                                  | Optional pulse the CIC interpolator generates just before the RFD signal. The pulse width is one clock period. It can be used to let the data source more time to prepare another data sample.                                                                                                                                                                                                                                                                                                                                                                                                          |

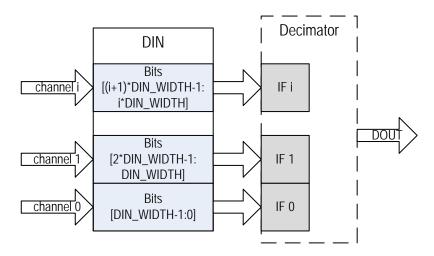

| DOUT        | Out    | DOUT_WIDTH for<br>Decimation CIC;<br>DOUT_WIDTH*IF_NUM<br>for Interpolation filter | Output filtered data. In case of decimation filter or a single<br>channel for any CIC type, the output data width equals<br>DOUT_WIDTH. In case of interpolation filter with multiple<br>Interfaces, the output data width for each interface is<br>DOUT_WIDTH and the total result data width =<br>DOUT_WIDTH*IF_NUM.                                                                                                                                                                                                                                                                                  |

| DOUT_VALID  | Out    | 1 for Decimation CIC;<br>IF_NUM for Interpolation<br>filter                        | Filtered data valid indicates that a new output data sample is<br>present at the DOUT port. For the decimation filter as well as a<br>single interface interpolation filter, the signal is one bit wide. In<br>case of interpolation filter with multiple interfaces, the output<br>data width for each interface is one and the total result signal<br>width = IF_NUM.                                                                                                                                                                                                                                 |

| RATE        | In     | 11                                                                                 | Variable rate value. The port is available when variable rate change mode is selected, VAR_RATE = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RATE_WE     | In     | 1                                                                                  | Register a new value of the variable RATE. The RATE_WE must<br>be a one-clock wide pulse. The port is available when variable<br>rate change mode is selected, VAR_RATE = 1. After the RATE<br>value is stored in the core, the effective rate factor does not<br>change yet. The new RATE value takes effect after the core<br>receives the synchronous reset RST pulse.                                                                                                                                                                                                                               |

| CHAN_SYNC_I | In     | 1                                                                                  | Channel synchronization signal. For a decimation filter, it<br>provides an advanced identification for the first data channel<br>when CLK_PER_SAMPLE > 1. For an interpolation filter, the<br>signal is expected to come even if the filter has only one                                                                                                                                                                                                                                                                                                                                                |

| Signal      | In/Out | Port Width Bits | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |        |                 | channel. Then the signal marks a time slot when the input<br>sample is valid. For a multichannel interpolator, when<br>CLK_PER_SAMPLE > 1 the signal is supposed to mark the valid<br>input sample of the first time-share channel. The<br>CHAN_SYNC_I must be a one-clock wide pulse.                                                                                                                                |

| CHAN_SYNC_O | Out    | 1               | Output channel synchronization signal. This clock-wide pulse identifies the first channel data output sample.                                                                                                                                                                                                                                                                                                         |

| CHAN_OUT    | Out    | 6               | Output channel numerical ID.                                                                                                                                                                                                                                                                                                                                                                                          |

| CLK         | In     | 1               | The core master clock.                                                                                                                                                                                                                                                                                                                                                                                                |

| NGRST       | In     | 1               | Optional asynchronous reset. Active Low. The signal is<br>expected to follow the FPGA power-on. The signal initiates<br>reset of all internal registers. If RAM blocks are used to<br>implement integrator or comb registers, the actual reset can<br>take several clock cycles. Then on the rear edge of the NGRST,<br>the core automatically generates an internal reset wide<br>enough to reset all the registers. |

| RST         | In     | 1               | Synchronous reset. Active High. The signal initiates reset of all<br>internal registers. If RAM blocks are used to implement<br>integrator or comb registers, the actual reset can take several<br>clock cycles. Then the RST signal initiates an internal reset wide<br>enough to reset all the registers.                                                                                                           |

Table 6 CIC Filter In or Out Signals

Figure 15 and Figure 16 show examples of using the core in fixed and variable rate modes.

Figure 16 Variable Rate Single Channel CIC Filter

The following figure shows the filter connections in multiple channel mode.

Figure 17 Fixed Rate Multiple Channel Mode

#### 4.2.1 Decimator Interface

This section describes basics of the CIC decimation functionality. For more information, refer to Implementation Details section.

A decimation filter receives R\_RATE input samples to generate an output sample. The input data samples sequentially arrive at DIN port of a single channel decimator. Every input sample is accompanied by the DIN\_VALID pulse of one clock period. The filter accepts arbitrary gaps between the input samples. The data source indicates the break by de-asserting the DIN\_VALID signal. For maximum throughput, there must not be any gaps in between the input samples. If a data source can supply a new sample for every FPGA clock cycle, attach the DIN\_VALID to VCC. Once the decimator gets R\_RATE input samples, it posts an output filtered sample on the DOUT port after it finishes the sample processing. It also accompanies the valid output sample by the clock-wide DOUT\_VALID signal. The CIC filter introduces processing latency that is described below.

A time share multichannel decimator, where CLK\_PER\_SAMPLE > 1 expects the data samples to come in the natural order. For example, at CLK\_PER\_SAMPLE = 3 the first channel sample comes first, followed by a sample of the second channel and then third channel. Input sample of each channel is accompanied by the DIN\_VALID pulse. Similarly, to the single channel, if there are no gaps in between the input samples the DIN\_VALID signal has to be permanently high. The data source identifies the first channel by the CHAN\_SYNC\_I pulse that accompanies the DIN\_Sample of the first channel. In other words, the CHAN\_SYNC\_I pulse is a copy of the DIN\_VALID pulse for the first data channel. The decimator assigns the channels numerical IDs, from 0 to 2. On receiving R\_RATE input samples from all channels, the decimator outputs filtered DOUT data, one sample at a time for the channels 0 to 2. The output channels are accompanied by the DOUT\_VALID pulses. The DOUT output for the channel 0 is accompanied by the CHAN\_SYNC\_O pulse. The CHAN\_SYNC\_O is a copy of the DOUT\_VALID signal. CHAN\_OUT provides the number of channels currently posted on the DOUT output. In this example, CHAN\_OUT sends the numbers 0, 1, 2 synchronized with valid output samples.

A multiple interface decimator, where IF\_NUM > 1 expects input data samples to come to each interface, simultaneously. A single DIN\_VALID pulse is used for all interfaces. It signifies another set of IF\_NUM input samples is ready to be received by all interfaces. Similarly, to the single channel, if there are no gaps in between the input samples, the DIN\_VALID signal must be permanently High. If multiple interface decimator does not utilize time share, that is the parameter CLK\_PER\_SAMPLE=1, the CHAN\_SYNC\_I signal must replicate the DIN\_VALID pulse. Once the decimator receives R\_RATE input samples on all its interfaces, it starts placing output samples on the DOUT port one channel at a time: an output sample for the channel coming to the interface 0 and the channel coming to the interface 1, and so on. Each output sample is accompanied by the DOUT\_VALID pulse. CHAN\_SYNC\_O marks the channel of the interface 0. CHAN\_OUT supplies the numerical channel IDs synchronized with the output samples.

A multichannel decimator can combine time share and comb share when IF\_NUM > 1 and CLK\_PER\_SAMPLE > 1. The total number of channels processed by such filter equals IF\_NUM\*CLK\_PER\_SAMPLE. Consider an example of a decimator processing six channels: IF\_NUM = 2 and CLK\_PER\_SAMPLE = 3.

The data samples are expected to come to the interface 0 in the following order:

- Sample 0 of the channel 0

- Sample 0 of the channel 1

- Sample 0 of the channel 2

- Sample 1 of the channel 0

- Sample 1 of the channel 1, and so on

Simultaneously the following data is coming to the interface 1:

- Sample 0 of the channel 3

- Sample 0 of the channel 4

- Sample 0 of the channel 5

- Sample 1 of the channel 3

- Sample 1 of the channel 4, and so on

Every sample of the channel 0 to channel 2 is accompanied by DIN\_VALID pulses unless the data is coming without gaps. Samples of the channel 0 are accompanied by the CHAN\_SYNC\_I pulses. Since the data to interfaces 0 and 1 is coming simultaneously, the CHAN\_SYNC\_I pulse marks the channel 3 as well. The filter outputs samples of the channel 0 to 5 sequentially with every sample accompanied by the DOUT\_VALID pulse. The core generates the CHAN\_SYNC\_O pulse when the channel 0 filtered sample shows up at the DOUT output. CHAN\_OUT supplies channel IDs from 0 to 5 synchronized with valid output samples.

Upon reset signals, NGRST or RTS, the decimator enters the reset state. During the reset state, the decimator keeps the RFD signal Low.

Note: The DIN\_VALID pulses are expected to be present at this time but the core ignores any input data while the RFD signal is Low. In the decimation mode, only during the reset state the RFD signal goes Low.

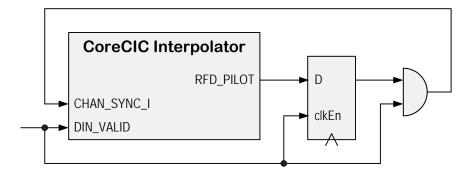

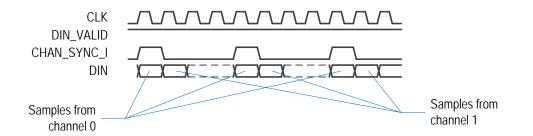

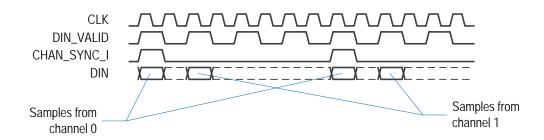

#### 4.2.2 Interpolator Interface