THINNING

### Getting Started with the RISC-V Based PolarFire® SoC FPGA Webinar Series Session 11: Handling Binaries Hugh Breslin, Design Engineer

Hugh Breslin, Design Engineer Thursday Mar. 12, 2020

### **Second Thursdays**

- Mar. 12 Webinar 11: Handling Binaries

- April 9 Webinar 12: Two Bare-Metal Applications on PolarFire<sup>®</sup> SoC

- May 14 Webinar 13: Linux<sup>®</sup> on Renode

- June 11 Webinar 14: Building Applications for Linux on PolarFire SoC

- July 9 Webinar 15: Real-Time (AMP Mode) on PolarFire SoC

## Supporting Content

### www.microsemi.com/Mi-V "Renode Webinar Series"

|              |                                                    |                                        |                                            |                                                                   |        | S                          | earch Microsemi.com |

|--------------|----------------------------------------------------|----------------------------------------|--------------------------------------------|-------------------------------------------------------------------|--------|----------------------------|---------------------|

| g            | Company                                            | Partners                               | Support                                    |                                                                   |        |                            |                     |

| LIL          |                                                    | Design Suit                            | 0 12.0                                     |                                                                   | <br>12 | Party and and and a series |                     |

| • 60<br>• 25 | % runtime impr<br>% runtime impr                   | ction for Timing a<br>ovment for Place | and 20% runtin<br>and Route                | Fusion2 and RTG4 fam<br>ne reduction for Powe                     |        |                            |                     |

| • 60<br>• 25 | % runtime inpr<br>% runtime impr<br>e / Products & | ction for Timing a<br>ovment for Place | and 20% runtin<br>and Route<br>'GA & SoC / | usion2 and RTG4 fam<br>ne reduction for Powe<br>MI-V RISC-V Ecosy |        |                            |                     |

Learn how to get started with the PolarFire SoC FPGA, the world's first RISC-V based SoC FPGA, to create fully deterministic, real-time systems alongside the Linux® operating system. We are holding a series of webinars to introduce you to the free Renode™ development platform from Mi-V partner Antmicro that is available with our SoftConsole v6.0 software development environment. You will see demo applications, learn how to create projects, and find out how to set up and configure your own systems targeting the new SoC FPGA architecture.

Click here to register

### Webinar 1 (May 2): Discover Renode for PolarFire<sup>™</sup> SoC Design and Debug

In this introductory session, we will provide you with an overview of SoftConsole 6.0 with Renode<sup>TM</sup> integration. We will introduce you to the Renode development framework and provide an overview of the platform and its features. You will also learn about the PolarFire™ SoC architecture and how to use Renode to develop your application.

Webinar 1: Discover Renode for PolarFire<sup>®</sup> SoC Design and Debug Webinar 2: How to Get Started with Renode for PolarFire SoC Webinar 3: Learn to Debug a Bare-Metal PolarFire SoC Application with Renode Webinar 4: Tips and Tricks for Even Easier PolarFire SoC Debug with Renode Webinar 5: Add and Debug PolarFire SoC Models with Renode Webinar 6: Add and Debug Pre-Existing Model in PolarFire SoC Webinar 7: How to Write Custom Models Webinar 8: What's New in SoftConsole v6.2

Webinar 9: Getting Started with PolarFire SoC

Webinar 10: Introduction to the PolarFire SoC Bare-Metal Library

- The PolarFire<sup>®</sup> SoC Start Up Sequence

- Setting Breakpoints on Specific Harts

- Demo PolarFire <sup>®</sup> SoC Start Up Sequence

- MPFS\_HAL\_FIRST\_HART

- MPFS\_HAL\_LAST\_HART

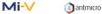

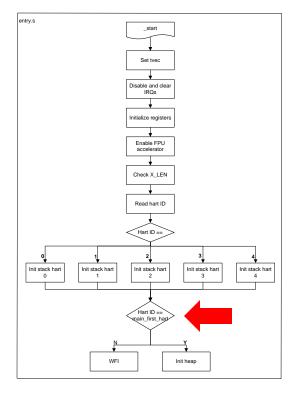

### The PolarFire<sup>®</sup> SoC Start Up Sequence

### The PolarFire<sup>®</sup> SoC Start Up Sequence

- 1. Harts start from the same "\_start" function

- 2. They diverge after initializing their stacks

- By default the U54 harts go to WFI

- E51 initializes the heap and wakes up harts in use

- 3. Harts jump to dedicated main functions

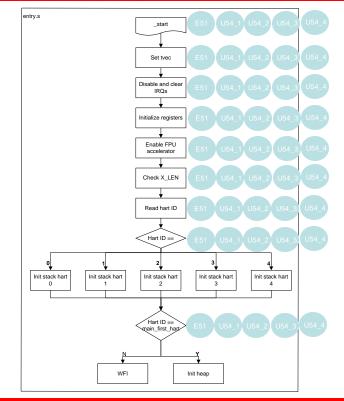

### The PolarFire<sup>®</sup> SoC Start Up Sequence

### The PolarFire<sup>®</sup> SoC Start Up Sequence

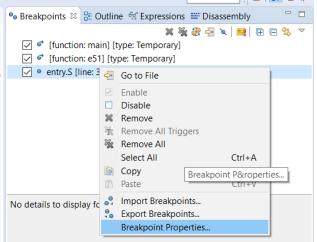

### Setting Breakpoints on Specific Harts

### Setting Breakpoints on Specific Harts

Breakpoints can be set for all threads by double clicking on the line the breakpoint is needed

| s entry.                        | s 🛛                                                                               |                                                                     |   | 🍨 Breakpoints 🛱 📴 Outline 🏘 Expressions 📟 Disassembly 👘 🗖                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32<br>33<br>34<br>5<br>36<br>37 | csrw mtvec, a4<br>/* Make sure that mtv<br>1:<br>csrr a5, mtvec<br>bne a4, a5, 1b | <pre># initalise machine trap vector address ec is updated */</pre> | ^ | <ul> <li>X X 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 -</li></ul> |

• They can also be filtered so that only specific harts halt at the breakpoint

- <u>While</u> debugging right click on the breakpoint

- Select "Breakpoint Properties..."

Note: breakpoint properties will reset between debug sessions

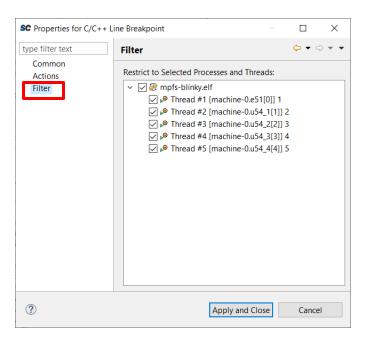

# Setting Breakpoints on Specific Harts

• Open the "Filter" heading

All threads are selected by default, deselect the threads (harts) you don't want to halt on the breakpoint

### Demo PolarFire<sup>®</sup> SoC Start Up Sequence

File Edit Source Refactor Navigate Search Project Git Run Window Help

K + K + 11 🔳 32 13 北州 iP 32 🗣 🛊 43 🗱 🗘 🗸 🖉 🗸 🖉 🖉 🗸 🖉 Quick Access 10 林 - 6 😤 Outline 😚 Expressions 🚟 Disassembly 🎱 PF SOC STARTUP.jpg 656×1504 pixels 😫 - -ြဲ Project Explorer 🕱 -S entry.S 🕱 [ system startup.c [ c e51.c 23 .option norvc  $\nabla$ file:///home/miv/Downloads/PF\_SOC\_STARTUP.ipg 24 .section .text.init,"ax", %progbits miv-rv32im-systick-blinky 25 .globl reset vector i miv-rv32imaf-mandelbrot-uart 26 .globl \_start lentry.s start i miv-rv32imaf-raytracer-uart-cr 28 reset vector: 😂 mpfs-blinky 29 start: 🕨 🖑 Binaries 30 /\* Setup trap handler \*/ 31 la a4, ‡rap vector Includes Set tyec 32 csrw mt≑ec, a4 # initalise machine trap vector address ▼ 🕮 src 33 /\* Make sure that mtvec is updated \*/ application 34 1: 35 csrr a5, mtvec modules Disable and clear 36 bne a4, a5, 1b IRQs 🕶 👝 platform 37 /\* Disable and clear all interrupts \*/ 🕨 🕞 config 38 39 li a2, MSTATUS MIE Arivers # clear interrupt enable bit 40 csrc mstatus, a2 Initialize registers > 🕞 hal 41 csrw mie, zero 42 csrw mip, zero ▼ (> mpfs hal 43 # mscratch must be init to zero- we are not using scratch memory h atomic.h Enable FPU 44 csrw mscratch, zero accelerator bits.h 45 csrw mcause, zero 46 csrw mepc, zero 🕨 🚡 encoding.h 47 li x1.0 s entry.S 48 li x2, 0 Check X LEN ▶ h mcall.h 49 li x3.0 li x4, 0 50 ▶ 🚯 mss clint.h 51 li x5, 0 ▶ 🚡 mss coreplex.h Read hart ID 躗 Problems 🐙 Tasks 📮 Console 🕱 🧬 Terminal 🛷 Search 🙀 Debugger Console 🎄 Debug III Registers 🔀 N 🖬 🕞 🖃 📑 🖸 🗸 📬 🕶 約 🧯 📄 📑 😁 🍷 🗶 🍇 🔐 🖘 🔪 📑 🖬 🖷 😫 <terminated> PolarFire-SoC-Renode-emulation-platform [Program] /usr/bin/mono Sreakpoints ⋈ Value 10:00:21.1262 [DEBUG] machine-0: Disposing sysbus.i2c0. Name 10:00:21.1274 [DEBUG] machine-0: Disposing sysbus.i2c1. 10:00:21.1276 [DEBUG] machine-0: Disposing sysbus.envmData. entry.S [line: 186] 10:00:21.1280 [DEBUG] machine-0: Disposing sysbus.usb. 🔽 🛯 system startup.c [line: 62] 10:00:21.1290 [DEBUG] machine-0: Disposing sysbus.l2Lim. 10:00:21.1295 [DEBUG] machine-0: Disposing sysbus.e51DTim. 🛜 🛯 system startup.c [line: 162] 10:00:21.1296 [DEBUG] machine-0: Disposing sysbus.e51HartOITim. 😴 🛚 system\_startup.c [line: 166] 10:00:21.1298 [DEBUG] machine-0: Disposing sysbus.u54Hart1ITim. 🔽 🛯 system startup.c [line: 170] 10:00:21.1300 [DEBUG] machine-0: Disposing sysbus.u54Hart2ITim. 10:00:21.1301 [DEBUG] machine-0: Disposing sysbus.u54Hart3ITim. 💟 🛛 system\_startup.c [line: 174] 10:00:21.1303 [DEBUG] machine-0: Disposing sysbus.u54Hart4ITim. 🔽 🔍 system startup.c [line: 178] 10:00:21.1305 [DEBUG] machine-0: Disposing sysbus.ddr. 10:00:21.1306 [DEBUG] machine-0: Disposing sysbus.pcie0. No details to display for the current selection. 10:00:21.1316 [DEBUG] machine-0: Disposing sysbus.pciel. 10:00:21.1325 [INFO] machine-0: Disposed.

S /mpfs-blinky/src/platform/mpfs\_hal/entry.S

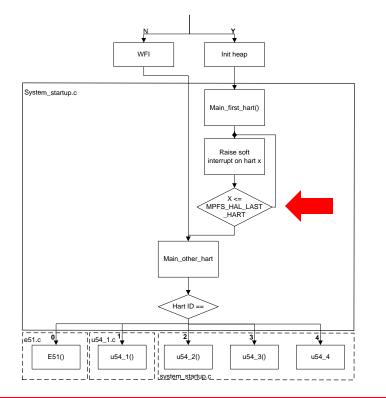

## **MPFS\_HAL\_FIRST\_HART**

### MPFS\_HAL\_FIRST\_HART

Here the harts will diverge and the main hart of the system will wake harts in use from WFI, the "MPFS\_HAL\_FIRST\_HART" value can be changed to determine which hart is the main hart.

### MPFS\_HAL\_FIRST\_HART

🖻 🔄 🗠 🗖 b mss sw config.h ⊠ Project Explorer 🕴 fpga-cortex-m1-blinky 26 @section m1fpga-cortex-m1-blinky 27 miv-rv32im-interrupt-blinky 28 \*//\*==== 29 miv-rv32im-systick-blinky miv-rv32imaf-mandelbrot-uart miv-rv32imaf-ravtracer-uart-cpp 32 ✓ ≌ mpfs-blinky 339/\* > 🖑 Binaries 34 Includes 36 🗸 🐸 src 37 > > application 38 > > pmodules 39 ✓ ▷ platform 🗸 🗁 config bardware 42 \*/ > 🗁 linker ✓ ⇒ software 45 #endif Arivers 46 mpfs hal > h mss\_sw\_config.h > readme.txt 49 #endif > > > drivers 50 > 🗁 hal 51⊖/\* 52 > >> profs hal 53 \*/ > > Debug mpfs-blinky hw-emulation all-harts Debug.launch

30 #ifndef USER CONFIG MSS USER CONFIG H 31 #define USER CONFIG MSS USER CONFIG H MPFS HAL FIRST HART and MPFS HAL LAST HART defines used to specify whi 35 \* harts to actually start. \* Set MPFS HAL FIRST HART to a value other than 0 if you do not want you \* to start and execute code on the E51 hart. \* Set MPFS HAL LAST HART to a value smaller than 4 if you do not wish to \* all U54 harts. \* Harts that are not started will remain in an infinite WFI loop unless through some other method 43 #ifndef MPFS HAL FIRST HART 44 #define MPFS HAL FIRST HART 0 47 #ifndef MPFS HAL LAST HART 48 #define MPFS HAL LAST HART 4 \* Markers used to indicate startup status of hart 54 #define HLS DATA IN WFI 0x12345678U

The "MPFS\_HAL\_FIRST\_HART" value is set to 0 by default to select the E51 as the main hart, this value can be changed to use a U54 hart as the main hart. File Edit Source Refactor Navigate Search Project Git Run Window Help

🔊 🔍 🛨 🐮 🛨 11 🖩 3, 13, 14 M is 32 🛸 👘 🕼 48 🗛 🗸 🗸 🖓 🗸 🖓 🗸 🦛 🖉 👘 🖉 🖓 🗸 👘 Ouick Access 111 林 - ic system\_startup.c in mss\_sw\_config.h ☎ ic e51.c 😫 Outline 🏘 Expressions 📟 Disassembly 🎄 Debug 😫 - -Project Explorer 🕄 S entry.S - 8 ▼ 30 #ifndef USER CONFIG MSS USER CONFIG H ‱ i+ ▽ 31 #define USER CONFIG MSS USER CONFIG H hart1 ▼ ■ mpfs-blinky Renode all-harts Start-platform-and-debug [Launch Group] 32 33@/\*----▶ 👝 inc /usr/bin/mono 34 \* MPFS HAL FIRST HART and MPFS HAL LAST HART defines used to specify which modules <terminated, exit value: 0>riscv64-unknown-elf-gdb 35 \* harts to actually start. ▼ 👝 platform 36 \* Set MPFS HAL FIRST HART to a value other than 0 if you do not want your code PolarFire-SoC-Renode-emulation-platform [Program] 37 \* to start and execute code on the E51 hart. 💌 👝 config /usr/bin/mono 38 \* Set MPFS HAL LAST HART to a value smaller than 4 if you do not wish to use hardware c <terminated>mpfs-blinky Renode all-harts Debug [GDB OpenOCD Debugging] 39 \* all U54 harts. 40 \* Harts that are not started will remain in an infinite WFI loop unless used Iinker <terminated, exit value: 0>riscv64-unknown-elf-gdb 41 \* through some other method ▼ > software 42 \*/ drivers 43 #ifndef MPFS HAL FIRST HART 🕶 👝 mpfs hal 44 #define MPFS HAL FIRST HART 0 45 #endif Is mss sw config.h 46 readme.txt 47 #ifndef MPFS HAL LAST HART Arivers 48 #define MPFS HAL LAST HART 4 49 #endif ) 👝 hal 50 🕶 👝 mpfs hal 518/\*-----52 \* Markers used to indicate startup status of hart ▶ h atomic.h 53 \*/ b bits.h 54 #define HLS DATA IN WFI 0x12345678U In encoding.h 55 #define HLS DATA PASSED WFI 0x87654321U 56 Is entry.S 57@/\*-----In mcall.h \* Define the size of the HLS used h mss clint.h \* In our HAL, we are using Hart Local storage for debug data storage only 59 ● Breakpoints 💥 🗶 🍇 🥵 🏹 🔪 🔜 🖽 🖃 😫 \* as well as flags for wfi instruction management. 60 entry.5 [iine: 128] 61 \* The TLS will take memory from top of the stack if allocated (x)= Variables 🔀 📲 Registers - o entry.S [line: 132] 62 \* 63 \*/ 8 ot 😑 😁 🗢 🗢 64 #define HLS DEBUG AREA SIZE 64 entry.5 [line: 156] Name Type o entry.S [line: 168] 📕 🗶 🍇 🔒 🚮 🕗 💭 🛃 🚽 🖬 🕶 🗖 🕶 🗖 🕶 🗖 🕐 Problems 🧔 Tasks 📮 Console 🕱 🧶 Terminal 🛷 Search 🚱 Debugger Console o system startup.c [line: 62] PolarFire-SoC-Renode-emulation-platform [Program] /usr/bin/mono system startup.c [line: 162] 16:23:54.5567 [INFO] Loaded monitor commands from: /home/miv/Microsemi\_SoftConsole\_v6.2/renode/./scripts/monitor.py System\_startup.c [line: 166] 16:23:55.4877 [INFO] Including script: /home/miv/Microsemi SoftConsole v6.2/renode-microchip-mods/scripts/polarfire-soc-generic-16:23:58.7669 [ERROR] Script: Renode has been started successfully and is ready for a odb connection. (This is not an error) System startup.c [line: 170] 💟 🛛 system\_startup.c [line: 174] 🗹 🛯 system startup.c [line: 178] No details to display for the current selection. Writable Smart Insert 44:31 📔 🐠 📄 😇 🚱 🖳 18:03 SC workspace....6.2.0.251 🛐 1 2 3 4 🖃 🙆 📰 🖿 miv aterminal - 2 windows Renode - 2 windows

## **MPFS\_HAL\_LAST\_HART**

### MPFS\_HAL\_LAST\_HART

The main hart will loop here turning on the harts being used in the system.

If harts aren't being used, the "MPFS\_HAL\_LAST\_HART" value can be changed to leave unused harts in "wfi" mode.

### **MPFS HAL LAST HART**

| Project Explorer 🖾                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ⊑ 🔩 ▽ 🗆 🗆  | ⓑ mss_sw_config.h ⊠                                                 |                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| <ul> <li>fpga-cortex-m1-blinky</li> <li>m1fpga-cortex-m1-blinky</li> <li>miv-rv32im-interrupt-blinky</li> <li>miv-rv32imaf-raytracer-uart-cpp</li> <li>miv-rv32imaf-raytracer-uart-cpp</li> <li>miv-rv32imaf-raytracer-uart-cpp</li> <li>mit-rv32imaf-raytracer-uart-cpp</li> <li>mit-rv32i</li></ul> |            | <pre>26 @section 27 28 *//*==================================</pre> | FIG_H_<br>HAL_LAST_HART defines used to specify whi<br>value other than 0 if you do not want you |

| > 🗁 hal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            | 51 <sup>®</sup> /*                                                  |                                                                                                  |

| > 🗁 mpfs_hal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            | 52 * Markers used to indicate start<br>53 */                        | lup status of nart                                                                               |

| > 🖻 Debug                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | 54 #define HLS DATA IN WFI                                          | 0x12345678U                                                                                      |

| 📄 mpfs-blinky hw-emulation all-harts De                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bug.launch |                                                                     | 0/120-00/00                                                                                      |

The "MPFS\_HAL\_LAST\_HART" value is set to 4 by default as harts without a defined function will be put into WFI mode from the weakly linked function.

File Edit Source Refactor Navigate Search Project Git Run Window Help 11 🔳 코 작 2 여 i i i 2 수 수 수 수 이 🎄 - 🗘 - 🎝 - 🤣 - 🥔 - 🖉 - 🦽 - - - - -10 10 10 K + X + Ouick Access FP? - -- -S entry.S 🕱 💽 system startup.c 🛛 h mss sw config.h 🖶 Outline 😥 Expressions 🚟 Disassembly 🞄 Debug 😫 - -🍐 Project Explorer 🕱 23 .option norvc 🦗 i⇒ 🗢 .section .text.init,"ax", %progbits 24 25 .globl reset vector u54\_1.c 🝷 📾 mpfs-blinky Renode all-harts Start-platform-and-debug [Launch Group] 26 .globl \_start inc /usr/bin/mono 27 modules 28 reset\_vector: 📲 riscv64-unknown-elf-gdb 29 start: platform PolarFire-SoC-Renode-emulation-platform [Program] /\* Setup trap handler \*/ 30 🔻 🕞 config 🚚 /usr/bin/mono 31 la a4, trap vector 🕨 👝 hardware 32 csrw mtvec, a4 # initalise machine trap vector address mpfs-blinky Renode all-harts Debug [GDB OpenOCD Debugging] 33 /\* Make sure that mtvec is updated \*/ 🕨 👝 linker mpfs-blinky.elf [cores: 0,1,2,3,4] 34 1: 🕶 👝 software ▼ Phread #1 [machine-0.e51[0]] 1 [core: 0] (Suspended : Breakpoint) 35 csrr a5, mtvec Arivers 36 bne a4, a5, 1b reset vector() at entry.S:32 0x8000008 37 🔻 👝 mpfs hal Image: Provide the second s 38 /\* Disable and clear all interrupts \*/ 🕨 🖻 mss sw config.h Image: Provide the second s 39 li a2, MSTATUS MIE readme.txt # clear interrupt enable bit 40 csrc mstatus, a2 Thread #4 [machine-0.u54\_3[3]] 4 [core: 3] (Suspended : Container) 41 csrw mie, zero Arivers Provide the second s 42 csrw mip, zero 🕨 👝 hal 🚚 riscv64-unknown-elf-adb 43 # mscratch must be init to zero- we are not using scratch memory 🕶 👝 mpfs hal 44 csrw mscratch, zero 45 csrw mcause, zero 🕨 脑 atomic.h 46 csrw mepc, zero 🕨 🔝 bits.h 47 li x1, 0 48 li x2, 0 In encoding.h 49 li x3, 0 🕨 💦 entry.S li x4. 0 50 In mcall.h 51 li x5, 0 li x6.0 In mss clint.h Sreakpoints ☆ \* \* 28 -> \* = = = + - - = li x7, 0 54 li x8,0 🗹 🖉 [function: e51] [type: Temporary] (x)= Variables 🕱 📲 Registers 55 li x9.0 P entry.S [line: 39] 56 li x10,0 約 🦡 📄 📑 😁 🍸 57 li x11.0 P entry.S [line: 44] Name Type 🔳 X 🔆 📴 🖓 🖓 🖓 🖓 🖓 🖓 🚽 🖓 🕶 🗖 🕶 🗖 🕶 P entry.S [line: 86] 🖹 Problems 🔊 Tasks 📮 Console 🕱 🧶 Terminal 🛷 Search 😨 Debugger Console P entry.S [line: 103] PolarFire-SoC-Renode-emulation-platform [Program] /usr/bin/mono P entry.S [line: 116] 16:21:50.8270 [INFO] Loaded monitor commands from: /home/miv/Microsemi SoftConsole v6.2/renode/./scripts/monitor.py 16:21:51.4926 [INFO] Including script: /home/miv/Microsemi SoftConsole v6.2/renode-microchip-mods/scripts/polarfire-soc-generic-P entry.S [line: 120] 16:21:54.1326 [ERROR] Script: Renode has been started successfully and is ready for a qdb connection. (This is not an error) P entry.S [line: 124] P entry.S [line: 128] antry S Ilina 1321 Writable Smart Insert 32:1 Launching mpfs-blinky...ebug: (100%) 😱 📼 🕥 1 2 3 4 🗖 🎒 🥅 🖬 miv SC workspace....6.2.0.251 📄 🐠 📑 🛄 🍘 🚇 16:22 🛀 aterminal - 2 windows Renode - 2 windows

- The PolarFire<sup>®</sup> SoC Start Up Sequence

- Setting Breakpoints on Specific Harts

- Demo PolarFire <sup>®</sup> SoC Start Up Sequence

- MPFS\_HAL\_FIRST\_HART

- MPFS\_HAL\_LAST\_HART

### **Second Thursdays**

- Mar. 12 Webinar 11: Handling Binaries

- April 9 Webinar 12: Two Bare-Metal Applications on PolarFire<sup>®</sup> SoC

- May 14 Webinar 13: Linux<sup>®</sup> on Renode

- June 11 Webinar 14: Building Applications for Linux on PolarFire SoC

- July 9 Webinar 15: Real-Time (AMP Mode) on PolarFire SoC

# Thank You Any Questions?