### First / Second Thursdays

- Jan. 9 Webinar 9: Getting Started with PolarFire®SoC

- Feb. 13 Webinar 10: Introduction to the PolarFire SoC Baremetal Library

- Mar. 12 Webinar 11: Handling Binaries

- April 9 Webinar 12: Two Baremetal Applications on PolarFire SoC

- May 14 Webinar 13: Linux on Renode

- June 11 Webinar 14: Building Applications for Linux on PolarFire SoC

- July 9 Webinar 15: Real-Time (AMP Mode) on PolarFire SoC

### **Supporting Content**

### www.microsemi.com/Mi-V "Renode Webinar Series"

Webinar 1: Discover Renode for PolarFire® SoC Design and Debug

Webinar 2: How to Get Started with Renode for PolarFire SoC

Webinar 3: Learn to Debug a Bare-Metal PolarFire SoC Application with Renode

Webinar 4: Tips and Tricks for Even Easier PolarFire SoC Debug with Renode

Webinar 5: Add and Debug PolarFire SoC models with Renode

Webinar 6: Add and Debug Pre-Existing model in PolarFire SoC

Webinar 7: How to Write Custom Models

Webinar 8: What's New in SoftConsole v6.2

Getting Started with the RISC-V Based PolarFire® SoC FPGA Webinar Series Session 9: Getting Started with PolarFire® SoC

Hugh Breslin, Design Engineer Thursday Jan. 9, 2019

### **Agenda**

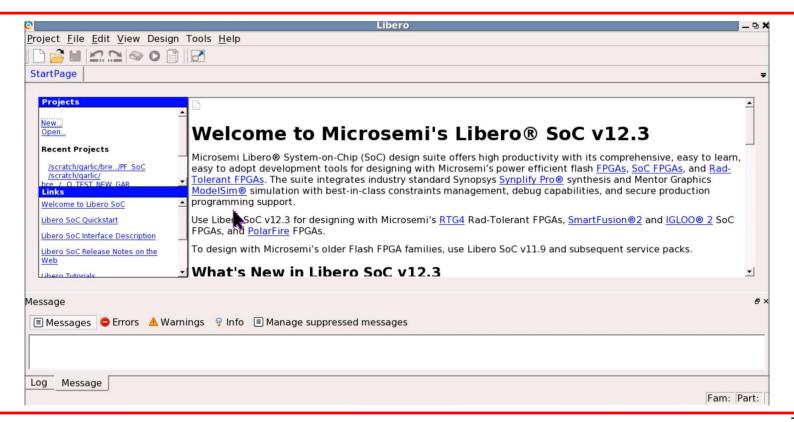

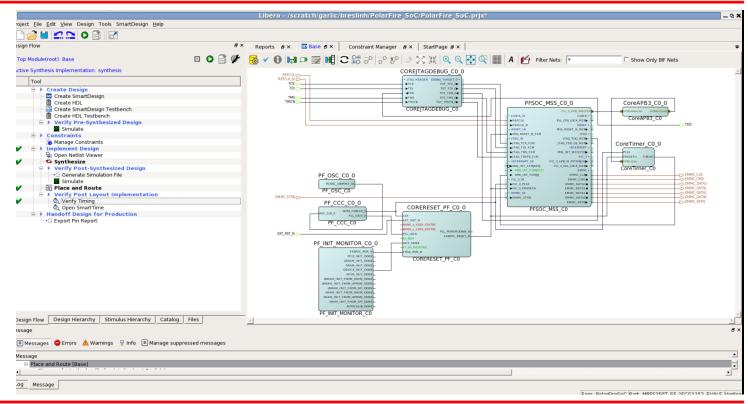

- Getting Started with Libero SoC v12.3

- Creating a PolarFire SoC Design in Libero SoC v12.3

- Modifying the Renode Model and MPFS Blinky

- www.microsemi.com/liberosoc

- Create a PolarFire SoC Project with an EAP license

- Libero SoC v12.3 released December 10<sup>th</sup>

- Libero SoC v12.0:

Software Tool of the Year 2019 WEAA

- World Electronics

Achievement Awards

Software Tool of the

Year.

- www.microsemi.com/polarfiresoc

- polarfiresoc@microchip.com

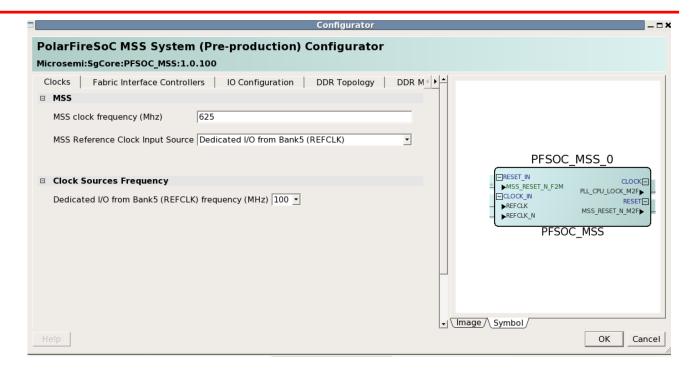

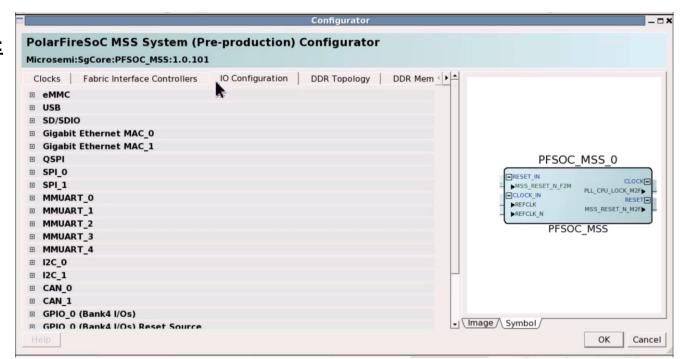

#### **Clocks tab:**

Set MSS clock frequency Select clock source Set reference frequency

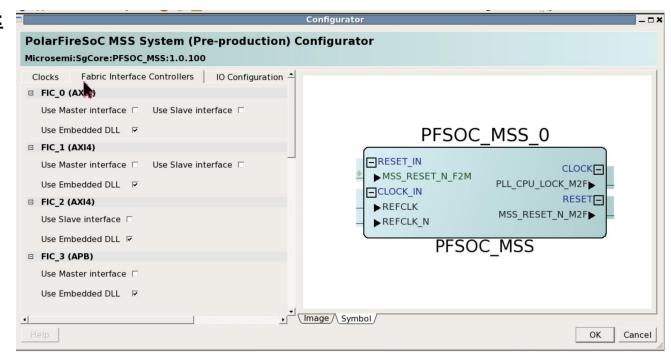

#### **Fabric Interface Controllers:**

#### FIC 0 AXI4

- Master

- Slave

#### FIC 1 AXI4

- Master

- Slave

#### FIC 2 AXI4

- Slave

#### FIC 3 APB

Master

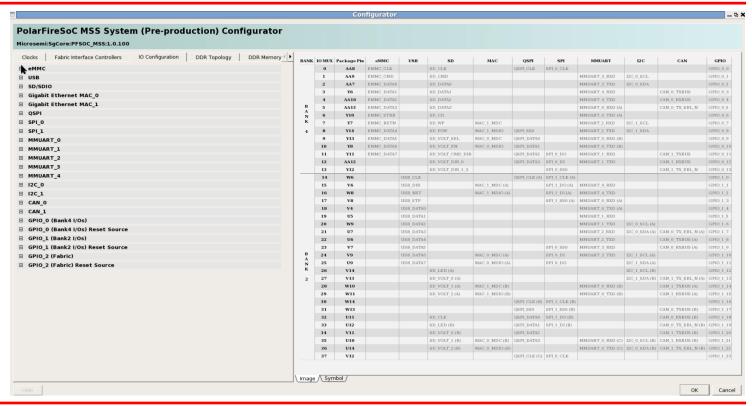

### IO Configurations Available:

- eMMC

- USB

- SD/SDIO

- GEM0 / 1

- QSPI

- SPI 0/1

- MMUART\_0/1/2/3/4

- I2C 0/1

- CAN\_0 / 1

- GPIO\_0/1/2

The "Image" tab highlights IOs in use and their configurations

###

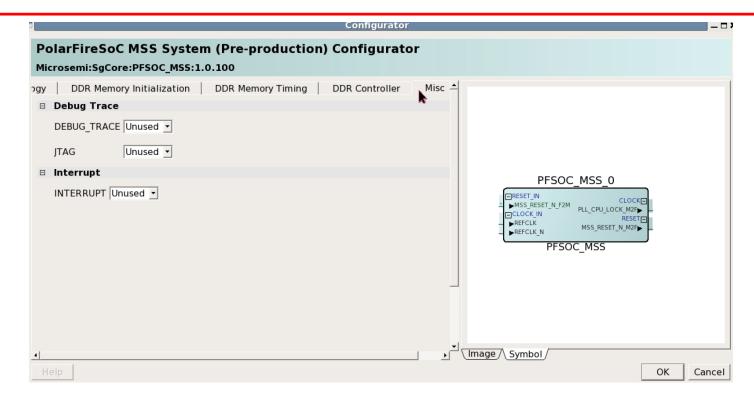

#### **Debug\_Trace:**

Expose UltraSoC Debug pins to the fabric

#### JTAG:

Expose fabric JTAG debug pins

#### **Interrupt:**

Expose 64 interrupt pins to the fabric

#### **Currently Available:**

- Synthesis

- Place and Route

- Timing Verification

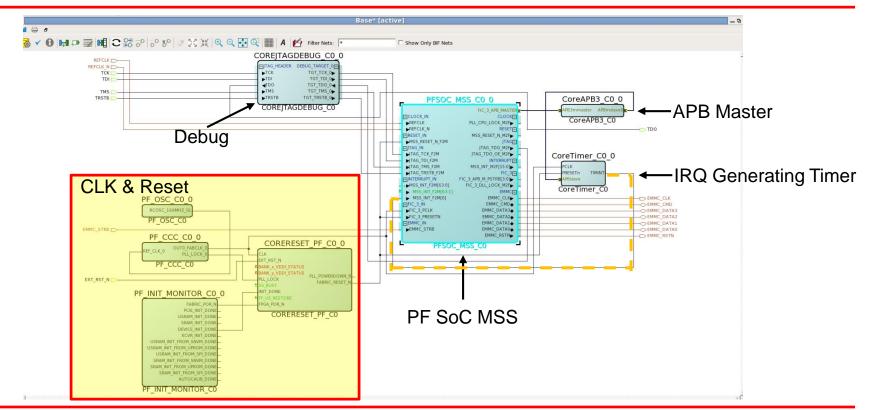

## Creating a PolarFire SoC Design in Libero SoC v12.3

## Creating a PolarFire SoC Design in Libero SoC v12.3

- Create the Project

- Configure the MSS

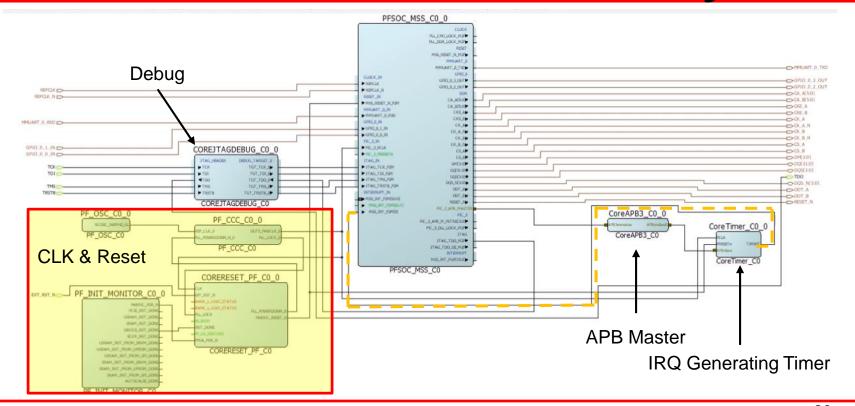

- Configure Fabric Clock and Reset

- Add Debug

- Add an Interrupt Generating Timer

## **Creating a PolarFire SoC Design in Libero SoC v12.3**

- The timer needs to be added to the CPU file

- It connects to sysbus directly there is no need for an apb master

- The FIC3 address is 0x40\_0000\_0000

- The timer interrupt needs to be connected to the fabric interrupts

```

vailable peripherals:

Launch Script

svsbus (SvstemBus)

cpu (RiscV32)

CPU File

ddr (MappedMemory)

gpioInputs (MiV_CoreGPIO)

user_switch_0 (Button)

Address: 0

user_switch_1 (Button)

Board File

user_switch_2 (Button)

gpioOutputs (MiV_CoreGPIO)

Address: 0

led1 (LED)

led2 (LED)

Address: 2

```

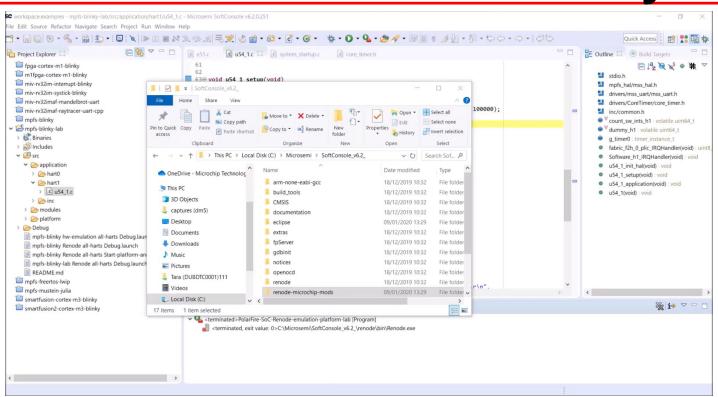

Drivers for the timer need to be added to the software project

The timer needs to be configured and started

The handler for the external interrupt to be used needs to be added to the software

### **Agenda**

- Getting Started with Libero SoC v12.3

- Creating a PolarFire SoC Design in Libero SoC v12.3

- Modifying the Renode Model and MPFS Blinky

# Thank You Any Questions?