Data Sheet

Jun. 19 – Ver. 1.0

# **POLARFIRE NVMe Host Recorder IP**

# Features

The LDS NVME HOST RECORDER IP has been done for beginners and expert in NVMe to drive NVMe PCIe SSD.

The register file interface simplify the management of the IP for CPU interface or State Machine interface using APB bus:

- PCIe RP and EP register configuration is done automatically.

- NVMe register configuration is done automatically.

- Able to manage 8 Name Spaces.

- Able to manage until 16 IO Queue to fit specific user requirement.

- Each IO Queue is independent.

- Able to manage 512Bytes and 4096Bytes sector size.

- Able to run nearly all Admin command in parallel of IO Queue.

- Many IO command already pre-defined to ease use of the IP.

- Configurable IO Queue buffer size to fit user memory requirement in case of small density FPGA: 256KB, 128KB, 64KB or 32KB.

- Able to read all PCIe RP and EP registers.

- Easy connection to Root Port PCIe IP through AXI bus.

When using a PCIe RP IP configured in Gen2 the system frequency is at 150MHz. When using a PCIe RP IP configured in Gen3 the system frequency is at 250MHz.

The source code format is available for ease of customization. The customization can be done by Logic Design Solutions and **DO254** documentation is available on request.

This IP can be customized according to specific needs (application-specific requirement). Any other pre-designed functions can be integrated into the FPGA. FPGA density and I/O requirements can be defined according to customer specification.

# **Design Package**

| Device Family    | MICROCHIP PolarFire FPGA<br>speed grade : 1                                                                                        |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| Package file     | <b>Source code or Source Encrypted.</b><br>Data Sheet, IP Interface Description and Constraint File.                               |  |

| Design Tool Used | MICROCHIP LIBERO SoC V12.0.                                                                                                        |  |

| Support          | Support provided by Logic Design Solutions 1 year e-mail and telephone su<br>from Logic Design Solutions included in the IP price. |  |

# Verification

The LDS NVME HOST RECORDER IP has been validated on the PolarFire Evaluation Kits (MPF300-EVAL\_KIT) and several disks. List of disk available on request.

### Performance

The demo provided makes a Disk Write and Read performance test on each disk connected.

A counter value is written on the disk and then read back and checked.

The performance depends on disk tested and memory configuration of the IP, especially for read performance. Performance are better with higher memory configuration.

As an example:

- Clock frequency 150MHz.

- PCIe Gen2 x 4 HHHL disk.

- o 100 Giga Byte data transfer.

- Sequential Write : 1060 MBytes/s

- Sequential Read : 1055 MBytes/s

# Utilization

| IP core only                |       |          |       |           |               |

|-----------------------------|-------|----------|-------|-----------|---------------|

| IP Configuration            | 4LUT  | USRAM 1K | FF    | LSRAM 18K | Logic Element |

| 1 Queue – 32KBytes Buffer   | 12000 | 317      | 7550  | 20        | 12500         |

| 1 Queue – 64KBytes Buffer   | 12500 | 317      | 8020  | 33        | 13000         |

| 1 Queue – 128KBytes Buffer  | 13900 | 317      | 9400  | 71        | 14370         |

| 1 Queue – 256KBytes Buffer  | 16220 | 317      | 11700 | 135       | 16750         |

|                             | [     | T        | [     | [         |               |

| 2 Queues – 32KBytes Buffer  | 15274 | 367      | 9900  | 33        | 15960         |

| 2 Queues – 64KBytes Buffer  | 16140 | 367      | 10840 | 59        | 16820         |

| 2 Queues – 128KBytes Buffer | 19070 | 367      | 13600 | 135       | 19752         |

| 2 Queues – 256KBytes Buffer | 23630 | 367      | 18220 | 263       | 24361         |

Until 16 Queues available.

# TABLE OF CONTENTS

| 1. | GENE           | RAL DESCRIPTION                                                                               | 4  |

|----|----------------|-----------------------------------------------------------------------------------------------|----|

| 1  | 1.1 STAT       | ге Масніле Демо                                                                               | 4  |

| 1  |                | J DEMO                                                                                        |    |

| 1  | I.3 POL        | ARFIRE ROOT PORT PCIE IP                                                                      |    |

|    | 1.3.1          | Block Diagram                                                                                 |    |

|    | 1.3.2          | Configuration of the PCIe IP in Libero Soc                                                    |    |

|    |                | STM_TEST MODULE                                                                               |    |

| 1  |                | GEN_CHECK MODULE                                                                              |    |

|    | 1.5.1          | Register map                                                                                  |    |

|    |                | P_NVME_HOST                                                                                   |    |

| ]  |                | NVME HOST REGISTER MAP                                                                        |    |

|    | 1.7.1          | Offset 00h: Configuration                                                                     |    |

|    | 1.7.2          | Offset 04h: Control                                                                           |    |

|    | 1.7.3          | Offset 08h: Status Admin                                                                      |    |

|    | 1.7.4          | Offset 0Ch: Status IO 1                                                                       |    |

|    | 1.7.5          | Offset 10h: Start Logical Block Low                                                           |    |

|    | 1.7.6<br>1.7.7 | Offset 14h: Start Logical Block High.                                                         |    |

|    | 1.7.7          | Offset 18h: Number Logical Block Low                                                          |    |

|    | 1.7.8<br>1.7.9 | Offset 1Ch: Number Logical Block High<br>Offset 20h – 5Ch: NVMe Admin Command 16x32-Bits FIFO |    |

|    | 1.7.9          | Offset 60h – 6Ch: NVMe Admin Command T0x52-Bits FIFO                                          |    |

|    | 1.7.11         | Offset 70h: Remaining Number of data to Transfer                                              |    |

|    | 1.7.12         | Offset 74h: Status IO 2                                                                       |    |

|    | 1.7.12         | Offset 78h: NVMe Admin Data Received FIFO – 4KBytes                                           |    |

|    | 1.7.13         | Offset 7Ch: NVMe Admin Data Received Control                                                  |    |

|    | 1.7.15         | Offset 80h: NVMe Admin Data Transmit FIFO – 4KBytes                                           |    |

|    | 1.7.16         | Offset 84h: NVMe Admin Data Transmit Control                                                  |    |

|    | 1.7.17         | Offset 88h: PCIe RP or PCIe EP address                                                        |    |

|    | 1.7.18         | Offset 8Ch: PCIe RP or PCIe EP read register                                                  |    |

| 2  |                | VERSION USED                                                                                  |    |

| 2. | TOOL           | VERSION USED                                                                                  |    |

| 3. | RECO           | MMENDED DESIGN EXPERIENCE                                                                     | 24 |

| 4. | AVAII          | ABLE SUPPORT PRODUCTS                                                                         | 24 |

| 5. | ORDE           | RING INFORMATION                                                                              | 24 |

| 6. | RELA           | FED INFORMATION                                                                               | 24 |

# 1. General Description

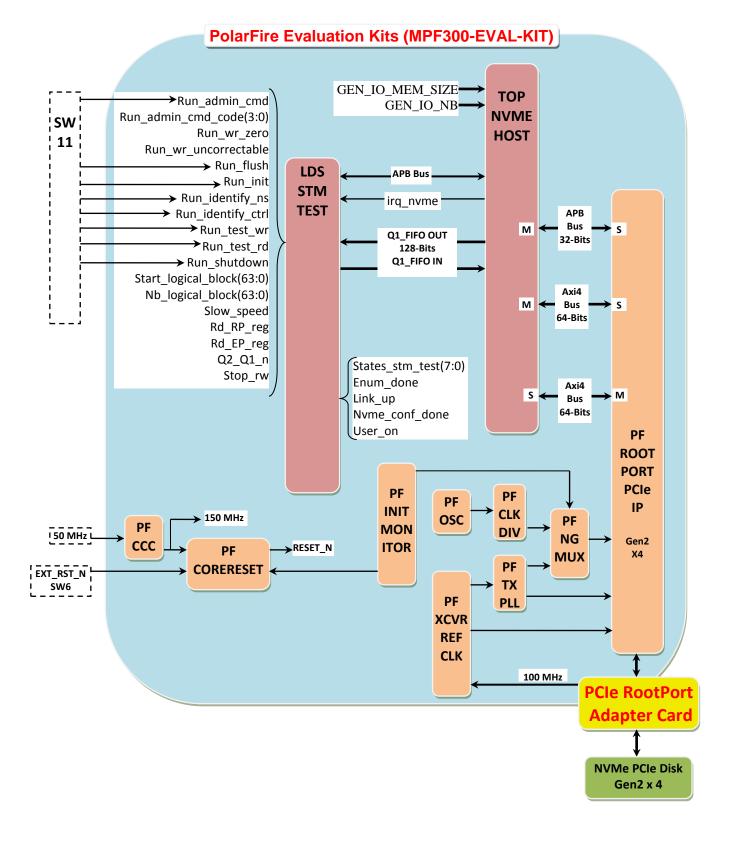

### 1.1 State Machine Demo

- The STM demo runs at 150MHz and its goal is to check performance during long transfer.

- You can run several commands through an external switch which run a state machine, please have a look on the demo documentation for details.

- The VHDL source code of the state machine is provided which enables the user to modify it to fit its project requirement.

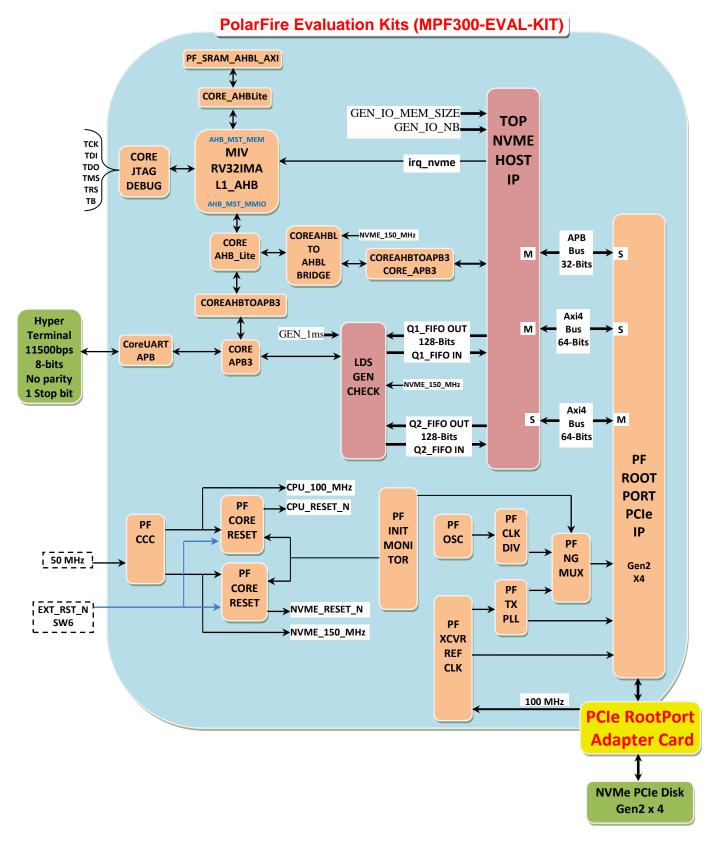

### 1.2 CPU Demo

- The RISC-V CPU runs at 100MHz and the NVMe data runs at 150MHz. The goal of the demo is to check performance during long transfer.

- You can run a write and read performance test through a User Interface on the Hyper Terminal, please have a look on the demo documentation for details.

- The C source code is provided which enables the user to modify it to fit its project requirement.

### **1.3 POLARFIRE ROOT PORT PCIe IP**

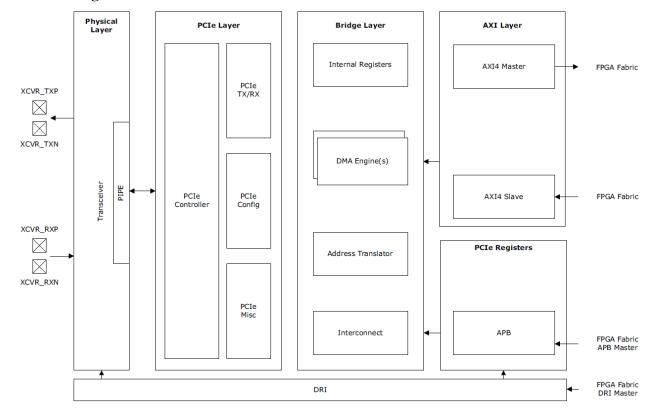

### 1.3.1 Block Diagram

Please read UG0685 to get details about this IP.

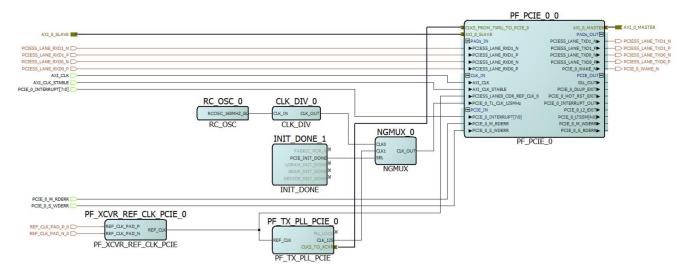

The SmartDesign representation of a complete PCIe example is the following:

### 1.3.2 Configuration of the PCIe IP in Libero Soc

### **General Settings:**

|                                                                                                                                                                                                                  | PCIe 0             | PCIe 1                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|

| CIe Controller                                                                                                                                                                                                   | Disabled           | Enabled               |

| Port Type Root Port                                                                                                                                                                                              |                    |                       |

| umber of Lanes x4                                                                                                                                                                                                |                    |                       |

| ane Rate                                                                                                                                                                                                         |                    | Gen2 (5.0 Gbps)       |

| eference Clock Frequency                                                                                                                                                                                         |                    | 100                   |

| DR Reference Clock Source                                                                                                                                                                                        |                    | Dedicated             |

| lumber of CDR Reference Clocks                                                                                                                                                                                   |                    | 1                     |

| <ul> <li>General Settings</li> <li>Use embedded DLL in fabric interesting</li> </ul>                                                                                                                             | erface <b>()</b>   |                       |

| Use embedded DLL in fabric inte                                                                                                                                                                                  |                    |                       |

|                                                                                                                                                                                                                  |                    | 5000 Mbps             |

| Use embedded DLL in fabric inte<br>Embedded DLL Jitter Range                                                                                                                                                     |                    | 5000 Mbps<br>2500 MHz |

| Use embedded DLL in fabric inte<br>Embedded DLL Jitter Range<br>TX PLL base data rate                                                                                                                            |                    |                       |

| Use embedded DLL in fabric inte<br>Embedded DLL Jitter Range<br>TX PLL base data rate<br>TX PLL bit clock frequency                                                                                              | Medium Low<br><br> |                       |

| <ul> <li>Use embedded DLL in fabric inte<br/>Embedded DLL Jitter Range<br/>TX PLL base data rate<br/>TX PLL bit clock frequency</li> <li>Optional Interfaces</li> <li>Enable APB slave interface (PCI</li> </ul> | Medium Low<br><br> |                       |

#### **Identification Settings:**

| General Identification Power Management Interrupts a | nd Auxiliary Settings   Master Settings   Slave Settings |

|------------------------------------------------------|----------------------------------------------------------|

|                                                      |                                                          |

|                                                      |                                                          |

|                                                      |                                                          |

|                                                      | PCIe 1                                                   |

| Vendor ID                                            | 0x11AA                                                   |

| Sub-System Vendor ID                                 | 0x0000                                                   |

| Revision ID                                          | 0x0000                                                   |

| Device ID                                            | 0x1556                                                   |

| Sub-System Device ID                                 | 0x0000                                                   |

| Class Code                                           | 0x0000                                                   |

#### **Power Management Settings:**

| General Identification                                          | Power Management                        | Interrupts and Auxilia | ary Settings  | Master Settings | Slave Settings  |

|-----------------------------------------------------------------|-----------------------------------------|------------------------|---------------|-----------------|-----------------|

|                                                                 | · - · · · · · · · · · · · · · · · · · · | interrupto una riaxin  | in y betanigo | Habter bettingb | bidte betailige |

|                                                                 |                                         |                        |               |                 |                 |

|                                                                 |                                         |                        |               |                 |                 |

|                                                                 |                                         |                        |               |                 |                 |

|                                                                 |                                         |                        |               |                 |                 |

|                                                                 |                                         |                        |               |                 |                 |

|                                                                 |                                         |                        |               |                 |                 |

|                                                                 |                                         |                        |               | PCIe 1          |                 |

| Number of FTS                                                   |                                         |                        |               | PCIe 1<br>63    |                 |

|                                                                 |                                         |                        |               |                 |                 |

| Number of FTS<br>LOs Acceptable Latency<br>Enable L1 Capability |                                         |                        |               | 63              |                 |

| LOs Acceptable Latency                                          |                                         |                        |               | 63<br>No limit  |                 |

| nterrupts and Auxiliary Settings:           |                                   |                 |                |

|---------------------------------------------|-----------------------------------|-----------------|----------------|

| General   Identification   Power Management | Interrupts and Auxiliary Settings | Master Settings | Slave Settings |

|                                             |                                   |                 |                |

|                                             |                                   |                 |                |

|                                             |                                   |                 |                |

|                                             |                                   |                 |                |

|                                             |                                   | PCIe 1          |                |

| PHY Reference Clock Slot                    |                                   | Slot            |                |

| Interrupts                                  |                                   | MSI1            |                |

| Expose Wake Signal                          |                                   | Disabled        |                |

| Transmit Swing                              |                                   | Full Swing      |                |

| De-Emphasis                                 |                                   |                 |                |

### Master Settings: Only BAR 0 is used.

| General   Identification   Power Management   Interrupts an | d Auxiliary Settings Master Settings Slave Settings |

|-------------------------------------------------------------|-----------------------------------------------------|

| 🗉 Bar O Table                                               |                                                     |

|                                                             |                                                     |

|                                                             |                                                     |

|                                                             | PCIe 1                                              |

| BAR Type                                                    | 32-bit memory                                       |

| BAR Size                                                    | 256 MB                                              |

| AXI Address (32 bit)                                        | 0x0000000                                           |

|                                                             |                                                     |

|                                                             |                                                     |

|                                                             |                                                     |

| 🗄 Bar 1 Table                                               |                                                     |

| 🕑 Bar 2 Table                                               |                                                     |

| 🗉 Bar 3 Table                                               |                                                     |

| 🗄 Bar 4 Table                                               |                                                     |

| 🗄 Bar 5 Table                                               |                                                     |

### Slave Settings: Only Slave 0 is used.

| General   Identification   Power Management   Interrupts an | d Auxiliary Settings   Master Settings   Slave Settings |  |  |  |  |

|-------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|

| □ Slave 0 Table                                             |                                                         |  |  |  |  |

|                                                             |                                                         |  |  |  |  |

| [                                                           |                                                         |  |  |  |  |

|                                                             | PCIe 1                                                  |  |  |  |  |

| State                                                       | Enabled                                                 |  |  |  |  |

| Size                                                        | 256 MB                                                  |  |  |  |  |

| AXI Address (32 bit)                                        | 0x4000000                                               |  |  |  |  |

| Translation Address (64 bit)                                | 0x000000040000000                                       |  |  |  |  |

|                                                             |                                                         |  |  |  |  |

| Slave 1 Table                                               |                                                         |  |  |  |  |

|                                                             |                                                         |  |  |  |  |

| E Slave 3 Table                                             |                                                         |  |  |  |  |

| Slave 4 Table                                               |                                                         |  |  |  |  |

| 🗉 Slave 5 Table                                             |                                                         |  |  |  |  |

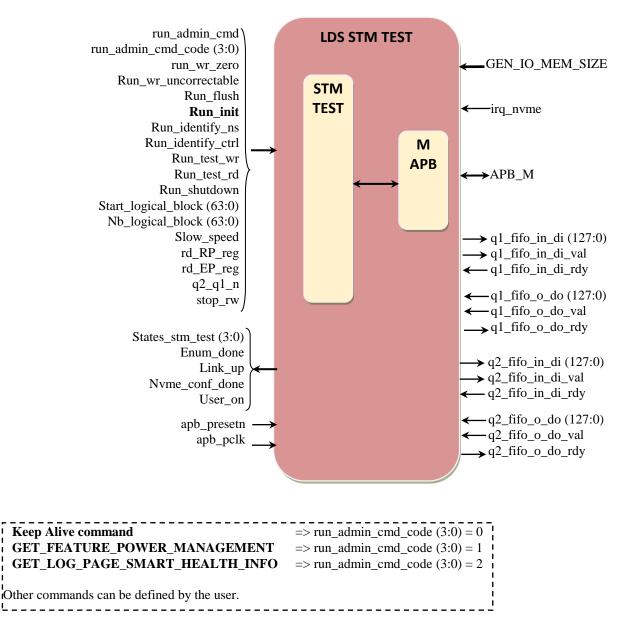

### 1.4 LDS\_STM\_TEST Module

A rising edge on one of the possible command runs it. After power-up or disk shutdown the first command to run is **Run\_init**.

The details of the State machine is provided in the demo data sheet.

The source code of this module is always provided. Hence, the user can use it for its project and modify it.

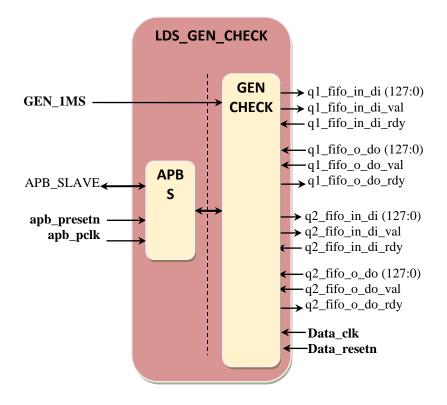

### 1.5 LDS\_GEN\_CHECK Module

The goal of this module is to generate a counter when writing to the disk and checking the value received when reading the disk.

When the "\_rdy" signal goes low, the "\_val" signal must go low as well immediately in a combinatorial way.

The registers are in the APB bus clock domain and the data test are in NVME\_HOST\_RECORDER IP clock domain.

This module is able to manage until two Queues. The VHDL source Code of this module is always provided.

The definition of the Generics is the following:

| GEN_1MS | integer := 150015; How many clock | period to get 1ms at the free | quency period - 150Mhz. |

|---------|-----------------------------------|-------------------------------|-------------------------|

|---------|-----------------------------------|-------------------------------|-------------------------|

### 1.5.1 Register map

All register are 32-bits wide

| Offset | Description                       |

|--------|-----------------------------------|

| 00h    | Control Register                  |

| 04h    | Low Performance Counter Register  |

| 08h    | High Performance Counter Register |

| 0Ch    | Performance Counter Register      |

| Bits | Туре  | Reset | Description                                                        |

|------|-------|-------|--------------------------------------------------------------------|

| 31:7 | RO    | 0     |                                                                    |

|      |       |       | Error on data received on Queue 2:                                 |

| 06   | RO    | 0     | <b>0</b> : No error has been detected on received data.            |

| 00   | ĸo    | 0     | 1: An error has been detected on received data.                    |

|      |       |       | Note: This bit is set to 0 on the rising edge of bit 04 or bit 05. |

|      |       |       | Generate Checking data on Queue 2:                                 |

| 05   | R/W   | 0     | 0: Reset Read counter.                                             |

|      |       |       | 1: Run Read counter.                                               |

|      |       |       | Generate write data on Queue 2:                                    |

| 04   | R/W   | 0     | <b>0</b> : Reset Write counter.                                    |

|      |       |       | 1: Run Write counter.                                              |

|      |       |       | Generate Slow speed Queue 1:                                       |

| 03   | R/W   | 0     | <b>0</b> : Slow speed mode inactive.                               |

| 05   | 10 11 | Ŭ     | 1: Slow speed mode active.                                         |

|      |       |       | Note: This mode generates data at 1/8 rate.                        |

|      |       |       | Error on data received on Queue 1:                                 |

| 02   | RO    | 0     | <b>0</b> : No error has been detected on received data.            |

| 02   | RO    | 0     | 1: An error has been detected on received data.                    |

|      |       |       | Note: This bit is set to 0 on the rising edge of bit 0 or bit 1.   |

|      |       |       | Generate Checking data on Queue 1:                                 |

| 01   | R/W   | 0     | 0: Reset Read counter.                                             |

|      |       |       | 1: Run Read counter.                                               |

|      |       |       | Generate write data on Queue 1:                                    |

| 00   | R/W   | 0     | <b>0</b> : Reset Write counter.                                    |

|      |       |       | 1: Run Write counter.                                              |

# 1.5.1.1 Offset 00h: Control Register

### 1.5.1.2 Offset 04h: Low Performance Counter Register

| Bits | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                               |

|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | RO   | 0     | Low Value of a 64-Bits Counter running at the frequency of the bloc.<br>It enables to calculate the writing and the reading performance according the frequency of the bloc.<br>In Gen2 the frequency is at 125MHz.<br>In Gen3 the frequency is at 250MHz.<br>Note: This register is set to 0 on the rising edge of bit 00 or bit 01 of Control Register. |

### 1.5.1.3 Offset 08h: High Performance Counter Register

| Bits | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | RO   | 0     | <ul> <li>High Value of a 64-Bits Counter running at the frequency of the bloc.</li> <li>It enables to calculate the writing and the reading performance according the frequency of the bloc.</li> <li>In Gen2 the frequency is at 125MHz.</li> <li>In Gen3 the frequency is at 250MHz.</li> <li>Note: This register is set to 0 on the rising edge of bit 00 or bit 01 of Control Register.</li> </ul> |

### 1.5.1.4 Offset 0Ch: Performance Counter Register

| Bits | Туре | Reset | Description                                                                                                                                                                                                                                                                                  |

|------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | RO   | 0     | <ul> <li>Value of a 32-Bits Counter running at 1Khz =&gt; 1ms.</li> <li>It enables to calculate the writing and the reading performance according the frequency of the bloc.</li> <li>Note: This register is set to 0 on the rising edge of bit 00 or bit 01 of Control Register.</li> </ul> |

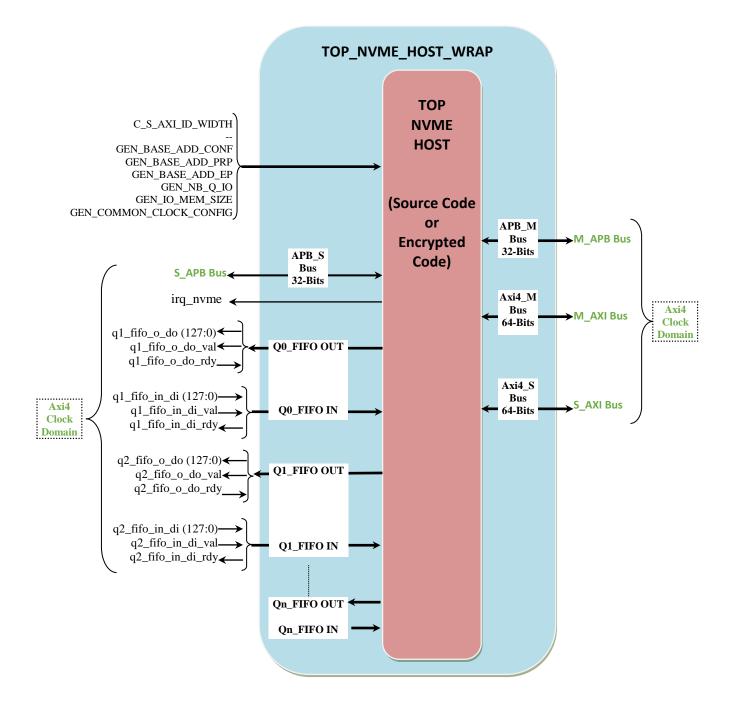

### 1.6 TOP\_NVME\_HOST

Until 16 Queues can be defined by Generics GEN\_NB\_Q\_IO.

When the "\_rdy" signal goes low, the "\_val" signal must go low as well immediately in a combinatorial way.

The **S\_APB Bus** enable CPU or State Machine to access to the registers of the NVME-HOST-RECORDER IP. All signals are on the same AXI4 clock domain.

| C_S_AXI_ID_WIDTH        | integer := 5; Width of ID of AXI4 Slave Bus                                   |

|-------------------------|-------------------------------------------------------------------------------|

|                         |                                                                               |

| GEN_BASE_ADD_CONF       | integer := 0; PCIe Root IP Registers Base address in the CPU space.           |

| GEN_BASE_ADD_PRP        | integer := 1342177280; x"50000000" Internal Buffer PCIe Base Address          |

| GEN_BASE_ADD_EP         | integer := 1073741824 ; x"40000000" End Point PCIe Base Address               |

| GEN_NB_Q_IO             | integer := 1; Two Queues                                                      |

| GEN_IO_MEM_SIZE         | integer := 32 256KB / 128KB / 64KB / 32KB / Internal Buffer size per Queue    |

| GEN_COMMON_CLOCK_CONFIG | integer := 1 – 1: Common PCIe Reference clock between Root Port and End Point |

The definition of the Generics is the following:

## 1.7 TOP NVME HOST Register map

All register are 32-bits wide

| Offset    | Description                                      |

|-----------|--------------------------------------------------|

| 00h       | Configuration                                    |

| 04h       | Control                                          |

| 08h       | Status Admin                                     |

| 0Ch       | Status IO 1                                      |

| 10h       | Start Logical Block Low                          |

| 14h       | Start Logical Block High                         |

| 18h       | Number Logical Block Low                         |

| 1Ch       | Number Logical Block High                        |

| 20h - 5Ch | NVMe Command – (16 x 32-Bits words) - Submission |

| 60h-6Ch   | NVMe Response – (4 x 32-Bits words) - Completion |

| 70h       | Remaining Number of data to Transfer             |

| 74h       | Status IO 2                                      |

| 78h       | NVMe Admin Data received FIFO – 4KBytes          |

| 7Ch       | NVMe Admin Data received Control                 |

| 80h       | NVMe Admin Data to transmit FIFO- 4KBytes        |

| 84h       | NVMe Admin Data to transmit Control              |

| 88h       | PCIe RP or PCIe EP address register              |

| 8Ch       | PCIe RP or PCIe EP read register                 |

| Bits  | Туре | Reset         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:17 | RO   | 0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 16    | R/W  | 0             | <ul> <li>Read Performance:</li> <li>0: Max performance.<br/>The reading of data by the user must be at least at a rate superior than half of the maximum read throughput of the disk.</li> <li>1: Average performance.<br/>Select this option if the user will read data at a rate less than half of the maximum read throughput of the disk.</li> </ul>                                                                                                                                                        |

| 15:08 | R/W  | 0             | LBA Data size supported:<br>The value is reported in terms of a power of two (2^n).<br>A value smaller than 9 (i.e.) 512 Bytes is not supported.<br>00 to 08: not supported<br>09: 512bytes by default LB_4K_512B_n=0<br>0A: 1KBytes<br>0B: 2KBytes<br>0C: 4KBytes. LB_4K_512B_n=1<br>0D: 8KBytes.<br><br>Note: This field is automatically updated at Power-up. This enable the user to know<br>immediately the LBA data Size of the disk.<br>Currently, the IP supports only 512 Bytes and 4KBytes selection. |

| 07:04 | R/W  | 0             | Number of IO Submission Queue and Completion Queue (NB_SQ_CQ_IO) requested:<br>Hardware dependent field.<br>Minimum is 1 and maximum cannot be greater than Number of Submission Queue and<br>Completion Queue (NB_SQ_CQ_IO) available.<br>This is a 0's based value. (0=>1)                                                                                                                                                                                                                                    |

| 03:00 | R    | Impl.<br>Spec | Number of IO Submission Queue and Completion Queue (NB_SQ_CQ_IO) available:<br>Hardware dependent field.<br>This is a 0's based value. (0=>1)                                                                                                                                                                                                                                                                                                                                                                   |

# 1.7.1 Offset 00h: Configuration

### 1.7.2 Offset 04h: Control

| Bits  | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:27 | RO   | 0     | Not used.                                                                                                                                                                                                                                                                                                                                                                                                |

| 26    | R/W  |       | <b>STOP_RW:</b> Will stop the current read or write command executed in the I/O QUEUE_NB. This bit must be set to 1 only if the status bit <b>user_on</b> equal 1. This bit is set to 0 automatically.                                                                                                                                                                                                   |

| 25    | R/W  | 0     | <b>Reset_RW_Admin_Queue_Fifo</b> : When set to 1, will reset the Write and Read Admin Queue FIFO. This bit is set to 0 automatically.                                                                                                                                                                                                                                                                    |

| 24:22 | R/W  | 0     | NSID: Define the Name Space ID accessed.<br>000: NSID 1<br>001: NSID 2<br><br>111: NSID 8<br>Note: If you need to manage more NS, please use the RUN_ADMIN_CMD option.                                                                                                                                                                                                                                   |

| 21    | R/W  | 0     | <b>RUN_IDENTIFY_NAMESPACE:</b> Will run an NVMe Identify command of the Namespace for the Admin Queue. The number of data received is 4KBytes.<br>The user does not need to configure any other register for this command.<br>This bit must be set to 1 only if the status bit <b>user_on</b> equal 1. This bit is set to 0 automatically.                                                               |

| 20    | R/W  | 0     | <b>Reset_Read_Queue_Fifo</b> : When set to 1, will reset the Read Queue FIFO from the queue number indicated by the <b>Reset_Queue_Fifo_NB</b> register to be sure no remaining data from a previous reading are still in. This bit is set to 0 automatically.                                                                                                                                           |

| 19:16 | R/W  | 0     | Reset_Queue_Fifo_NB:<br>0: Queue 1<br>1: Queue 2<br>                                                                                                                                                                                                                                                                                                                                                     |

| 15    | R/W  | 0     | F: Queue 16<br><b>Reset_Write_Queue_Fifo</b> : When set to 1, will reset the Write Queue FIFO from the queue number<br>indicated by the <b>Reset_Queue_Fifo_NB</b> register to be sure no remaining data from a previous<br>recording are still in. This bit is set to 0 automatically.                                                                                                                  |

| 14    | R/W  | 0     | RUN_WRITE_ZEROES: Will run a write zero command for the I/O QUEUE_NB, starting from<br>the 64-Bits Start Logical Block register for a number of Logical Block defined in the 64-Bits<br>Number Logical Block register.<br>This bit must be set to 1 only if the status bit user_on equal 1. This bit is set to 0 automatically.<br>Note: A logical block may be deallocated with a Write Zeroes command. |

| 13    | R/W  | 0     | RUN_WRITE_UNCORRECTABLE: Will run a write uncorrectable command for the I/O<br>QUEUE_NB, starting from the 64-Bits Start Logical Block register for only 16-Bits number of<br>Logical Block defined in the Number Logical Block_low register.<br>This bit must be set to 1 only if the status bit user_on equal 1. This bit is set to 0 automatically.                                                   |

| 12    | R/W  | 0     | <b>RUN_FLUSH:</b> Will run a Flush command for the <b>I/O QUEUE_NB</b> .<br>This bit must be set to 1 only if the status bit <b>user_on</b> equal 1. This bit is set to 0 automatically.                                                                                                                                                                                                                 |

| 11    | R/W  | 0     | <b>RUN_ADMIN_CMD:</b> Will run one Admin NVMe command defined in the <b>NVMe Admin</b><br><b>Command</b> register.<br>This bit must set to 1 only if the status bit <b>user_on</b> equal 1. This bit is set to 0 automatically.<br>The number of data transfer required in the NVMe Command must never be bigger than 4KBytes.                                                                           |

| 10    | R/W  | 0     | <b>RUN_IDENTIFY_CONTROLLER:</b> Will run a NVMe Identify command of the Controller disk for the Admin Queue. The number of data received is 4KBytes.<br>The user does not need to configure any other register for this command.<br>This bit must be set to 1 only if the status bit <b>user_on</b> equal 1. This bit is set to 0 automatically.                                                         |

| 09    | R/W  | 0     | <b>RUN_READ:</b> Will run a read command for the I/O QUEUE_NB, starting from the 64-Bits Start<br>Logical Block register for a number of Logical Block defined in the 64-Bits Number Logical<br>Block register.<br>This bit must be set to 1 only if the status bit user_on equal 1. This bit is set to 0 automatically.                                                                                 |

| 08    | R/W  | 0     | <b>RUN_WRITE:</b> Will run a write command for the <b>I/O QUEUE_NB</b> , starting from the <b>64-Bits</b><br><b>Start Logical Block</b> register for a number of Logical Block defined in the <b>64-Bits Number</b><br><b>Logical Block</b> register.<br>This bit must be set to 1 only if the status bit <b>user_on</b> equal 1. This bit is set to 0 automatically.                                    |

| 07:04 | R/W | 0 | I/O QUEUE_NB: indicates for which Submission/Completion Queue the command is related to.<br>0: I/O Queue 1<br>1: I/O Queue 2<br><br>F: I/O Queue 16                                         |

|-------|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03:02 | R   | 0 | Not used.                                                                                                                                                                                   |

| 01    | R/W | 0 | <ul> <li>run_shutdown:</li> <li>0: No effect.</li> <li>1: Run a disk Shut-down if the status bit user_on is set to 1.<br/>This bit is set to 0 automatically.</li> </ul>                    |

| 00    | R/W | 0 | <ul> <li>run_user:</li> <li>1: Enable the use of the NVMe block after a power up, a disk Shut-down or an error of PCIe enumeration.</li> <li>This bit is set to 0 automatically.</li> </ul> |

### 1.7.3 Offset 08h: Status Admin

| Bits  | Туре     | Reset | Description                                                                                                                                   |

|-------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 31:10 | RO       | 0     |                                                                                                                                               |

| 09    | RO       | 0     | admin_successful_command_completion:<br>0:<br>1: Completion Status Field ok.                                                                  |

| 08    | RO       | 0     | admin_fifo_cq_do_err:<br>0:<br>1: One Completion admin queue error occurred.                                                                  |

| 07    | RO       | 0     | <ul> <li>disk_down:</li> <li>0: Disk is not down.</li> <li>1: Disk is down. Wait for a run_user command.</li> </ul>                           |

| 06    | RO       | 0     | <ul><li>nvme_conf_err:</li><li>0: No error during the NVMe Configuration.</li><li>1: An error occurs during the NVMe Configuration.</li></ul> |

| 05    | RO       | 0     | Normal Shutdown_done<br>0: No Shutdown<br>1: Normal shutdown reached                                                                          |

| 04    | RWC<br>1 | 0     | <pre>admin_command_done:<br/>0: Irq_nvme_0 is set to 0<br/>1: Irq_nvme_0 is set to 1<br/>A write with 1 on this bit will reset the bit.</pre> |

| 03    | RO       | 0     | <ul><li>user_on:</li><li>0: Command cannot be sent to the NVMe Block.</li><li>1: Command can be sent to the NVMe Block.</li></ul>             |

| 02    | RO       | 0     | <ul><li>nvme_conf_done:</li><li>0: NVMe Configuration not done.</li><li>1: NVMe Configuration done</li></ul>                                  |

| 01    | RO       | 0     | link_up:<br>0: PCIe not link up.<br>1: PCIe link up.                                                                                          |

| 00    | RO       | 0     | enum_done:<br>0: PCIe Enumeration not done.<br>1: PCIe Enumeration done                                                                       |

A read of the register clears the bits except for the RWC1 bit 04.

### 1.7.4 Offset 0Ch: Status IO 1

| 31       RWC1       0       q8 fife sq. do err: One Submission IO queue error occurred.         30       RWC1       0       q8 fife sq. do err: One Completion IO queue error occurred.         32       RWC1       0       q8 command. done: A write with 1 on this bit will reset the bit.         31       RWC1       0       q8 command. done: A write with 1 on this bit will reset the bit.         35       RWC1       0       q7. fife sq. do err: One Completion IO queue error occurred.         26       RWC1       0       q7. fife sq. do err: One Completion IO queue error occurred.         27       RWC1       0       q7. fife sq. do err: One Completion IO queue error occurred.         28       RWC1       0       q7. fife sq. do err: One Submission IO queue error occurred.         28       RWC1       0       q6. fife sq. do err: One Submission IO queue error occurred.         21       RWC1       0       q6. fife sq. do err: One Completion Status Field ok         22       RWC1       0       q6. fife sq. do err: One Completion IO queue error occurred.         22       RWC1       0       q6. fife sq. do err: One Completion IO queue error occurred.         23       RWC1       0       q6. fife sq. do err: One Completion IO queue error occurred.         24       RWC1       0       q5. fife sq.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bits | Туре | Reset | Description                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------|

| 30       RWC1       0       q8 successful command_completion: Completion Status Field ok         29       RWC1       0       q8 site or completion IO queue error occurred.         28       RWC1       0       I: In prume_1 is set to 0         27       RWC1       0       q7. fifo sq. do err: One Submission IO queue error occurred.         26       RWC1       0       q7. fifo sq. do err: One Submission IO queue error occurred.         28       RWC1       0       q7. fifo sq. do err: One Submission IO queue error occurred.         28       RWC1       0       q7. fifo sq. do err: One Submission IO queue error occurred.         28       RWC1       0       q6. fifo sq. do err: One Submission IO queue error occurred.         28       RWC1       0       q6. fifo sq. do err: One Completion Status Field ok         21       RWC1       0       q6. fifo sq. do err: One Completion Status Field ok         22       RWC1       0       q6. fifo sq. do err: One Submission IO queue error occurred.         28       RWC1       0       q6. fifo sq. do err: One Submission IO queue error occurred.         29       RWC1       0       q6. fifo sq. do err: One Submission IO queue error occurred.         20       RWC1       0       q5. successful command completion: Completion Status Field ok                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | • •  |       |                                                                       |

| 29       RWC1       0       q8_ffo_cq_do_err: One Completion IO queue error occurred.         q8       command_done: A write with 1 on this bit will reset the bit.       0         28       RWC1       0       0         29       RWC1       0       0         20       0       0       1 frq nvmc_1 is set to 1         27       RWC1       0       0       7         21       RWC1       0       0       7         22       RWC1       0       0       7         23       RWC1       0       0       7         24       RWC1       0       16       fido_eq_do_err: One Submission IO queue error occurred.         23       RWC1       0       q6       fido_eq_do_err: One Submission IO queue error occurred.         23       RWC1       0       q6       fido_eq_do_err: One Submission IO queue error occurred.         24       RWC1       0       q6       fido_eq_do_err: One Submission IO queue error occurred.         24       RWC1       0       q6       fido_eq_do_err: One Completion Status Field ok         27       RWC1       0       q6       fido_eq_do_err: One Completion Status Field ok         28       RWC1       0 <t< td=""><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |      |       |                                                                       |

| RWC1         0         is set to 0           1         ing nyme_1 is set to 0         1: ing nyme_1 is set to 0           27         RWC1         0         if ing nyme_1 is set to 0           27         RWC1         0         if ing nyme_1 is set to 0           28         RWC1         0         if ing nyme_1 is set to 0           28         RWC1         0         if ing nyme_1 is set to 0           28         RWC1         0         if ing nyme_1 is set to 1           28         RWC1         0         if ing nyme_1 is set to 1           28         RWC1         0         if ing order.           29         RWC1         0         if ing order.           20         RWC1         0         if ing order.           21         RWC1         0         if ing order.           22         RWC1         0         if ing order.           23         RWC1         0         if ing order.           24         RWC1         0         if ing order.           26         RWC1         0         if ing order.           27         RWC1         0         if ing order.           28         RWC1         0         if ing order. </td <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      |       |                                                                       |

| 28         RWC1         0         0:         ftrg nyme_1 is set to 0           27         RWC1         0         47:         ftrg nyme_1 is set to 1           26         RWC1         0         47:         ftrg nyme_1 is set to 1           27         RWC1         0         47:         ftrg nyme_1 is set to 1           28         RWC1         0         47:         set to 0           29         RWC1         0         47:         set to 0           21         RWC1         0         47:         set to 0           23         RWC1         0         46:         ftrg nyme_1 is set to 0           23         RWC1         0         46:         ftrg nyme_1 is set to 1           23         RWC1         0         46:         ftrg nyme_1 is set to 1           24         RWC1         0         46:         ftrg nyme_1 is set to 1           25         RWC1         0         45:         ftrg nyme_1 is set to 1           26         RWC1         0         45:         ftrg nyme_1 is set to 1           27         RWC1         0         45:         ftrg nyme_1 is set to 1           37         RWC1         0         45: <th< td=""><td></td><td></td><td>-</td><td></td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      | -     |                                                                       |

| I: Irq nyme_1 is set to 127RWC10q7ffo. sq. do err: One Submission IO queue error occurred.26RWC10q7ffo. sq. do err: One Completion IO queue error occurred.25RWC100q7ffo. sq. do err: One Submission IO queue error occurred.24RWC100ffo. sq. do err: One Submission IO queue error occurred.23RWC100do ffo. sq. do err: One Submission IO queue error occurred.22RWC10q6ffo. sq. do err: One Submission IO queue error occurred.22RWC10q6ffo. sq. do err: One Submission IO queue error occurred.20RWC10q6ffo. sq. do err: One Submission IO queue error occurred.21RWC10q5ffo. sq. do err: One Submission IO queue error occurred.20RWC10q5ffo. sq. do err: One Submission IO queue error occurred.21RWC10q5ffo. sq. do err: One Submission IO queue error occurred.23RWC10q5ffo. sq. do err: One Submission IO queue error occurred.24RWC10q5ffo. sq. do err: One Submission IO queue error occurred.25regression1is set to 016RWC10q4ffo. sq. do err: One Submission IO queue error occurred.2600is set to 127RWC10q4ffo. sq. do err: One Submission IO queue error occurred.2814RWC10q4ffo.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28   | RWC1 | 0     |                                                                       |

| 27RWC10q7.fifo_sq_do_err: One Submission IO queue error occurred.26RWC10q7_successful_command_completion: Completion Status Field ok27RWC10q7.fifo_sq_do_err: One Completion IO queue error occurred.28RWC100fifo_sq_do_err: One Submission IO queue error occurred.29RWC10q6_fifo_sq_do_err: One Submission IO queue error occurred.21RWC10q6_fifo_sq_do_err: One Submission IO queue error occurred.22RWC10q6_fifo_sq_do_err: One Completion: Completion Status Field ok21RWC10q6_fifo_sq_do_err: One Completion IO queue error occurred.22RWC10q6_fifo_sq_do_err: One Submission IO queue error occurred.23RWC10q6_fifo_sq_do_err: One Submission IO queue error occurred.24RWC10q6_fifo_sq_do_err: One Submission IO queue error occurred.26RWC10q5_fifo_sq_do_err: One Completion: Completion Status Field ok27RWC10q5_fifo_sq_do_err: One Completion IO queue error occurred.28RWC10q4_fifo_sq_do_err: One Submission IO queue error occurred.29RWC10q4_fifo_sq_do_err: One Submission IO queue error occurred.29RWC10q5_fifo_sq_do_err: One Submission IO queue error occurred.38RWC10q4_fifo_sq_do_err: One Submission IO queue error occurred.38RWC10q4_fifo_sq_do_err: One Submission IO queue error occurred.39RWC10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -0   |      | Ũ     | 1 —                                                                   |

| 26       RWC1       0       q7_successful_command_completion: Completion Status Field ok         25       RWC1       0       q7_successful_command_dome: A write with 1 on this bit will reset the bit.         24       RWC1       0       0: frq nymc_1 is set to 1         23       RWC1       0       0: frq nymc_1 is set to 1         23       RWC1       0       q6_successful_command_completion: Completion Status Field ok         21       RWC1       0       q6_strong_dome: A write with 1 on this bit will reset the bit.         20       RWC1       0       q6_strong_dome: A write with 1 on this bit will reset the bit.         20       RWC1       0       q5_sfrlo_sq_do_err: One Submission IO queue error occurred.         20       RWC1       0       q5_sfrlo_sq_do_err: One Submission IO queue error occurred.         21       RWC1       0       q5_sfrlo_sq_do_err: One Submission IO queue error occurred.         20       RWC1       0       q5_sfrlo_sq_do_err: One Completion IO queue error occurred.         21       RWC1       0       q5_sfrlo_sq_do_err: One Completion IO queue error occurred.         21       RWC1       0       q5_sfrlo_sq_do_err: One Completion IO queue error occurred.         22       RWC1       0       q4_sfrlo_sq_do_err: One Completion IO queue error occurred.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27   | RWC1 | 0     |                                                                       |

| 25       RWC1       0 $q^7_{-command\_done:}$ A write with 1 on this bit will reset the bit.         24       RWC1       0       0: Irq avmc\_1 is set to 0         23       RWC1       0       q6_fifo_sq\_do_err: One Submission IO queue error occurred.         23       RWC1       0       q6_fifo_sq\_do_err: One Submission IO queue error occurred.         21       RWC1       0       q6_fifo_sq\_do_err: One Completion: Completion Status Field ok         21       RWC1       0       q6_fifo_sq\_do_err: One Submission IO queue error occurred.         20       RWC1       0       q6_fifo_sq\_do_err: One Submission IO queue error occurred.         20       RWC1       0       q5_fifo_sq\_do_err: One Submission IO queue error occurred.         21       RWC1       0       q5_fifo_sq\_do_err: One Submission IO queue error occurred.         28       RWC1       0       q5_fifo_sq\_do_err: One Submission IO queue error occurred.         29       RWC1       0       q5_fifo_sq\_do_err: One Submission IO queue error occurred.         29       RWC1       0       q5_fifo_sq\_do\_err: One Completion IS tatus Field ok         20       RWC1       0       q5_fifo\_sq\_do\_err: One Completion IS tatus Field ok         21       RWC1       0       q4_fifo\_sq\_do\_err: One Completion IS tatus Field ok                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |       |                                                                       |

| 24RWC10 $q_7$ _command_done: A write with 1 on this bit will reset the bit.24RWC10 $q_6$ fifo_sq_do_err: One Submission IO queue error occurred.23RWC10 $q_6$ fifo_sq_do_err: One Submission IO queue error occurred.21RWC10 $q_6$ fifo_sq_do_err: One Completion IO queue error occurred.21RWC10 $q_6$ fifo_sq_do_err: One Completion IO queue error occurred.20RWC10 $q_5$ fifo_sq_do_err: One Submission IO queue error occurred.20RWC10 $q_5$ fifo_sq_do_err: One Submission IO queue error occurred.21RWC10 $q_5$ fifo_sq_do_err: One Submission IO queue error occurred.20RWC10 $q_5$ fifo_sq_do_err: One Completion IO queue error occurred.21RWC10 $q_5$ fifo_sq_do_err: One Completion IO queue error occurred.28RWC10 $q_6$ fifo_sq_do_err: One Submission IO queue error occurred.29RWC10 $q_6$ fifo_sq_do_err: One Submission IO queue error occurred.20RWC10 $q_4$ fifo_sq_do_err: One Submission IO queue error occurred.21RWC10 $q_4$ fifo_sq_do_err: One Submission IO queue error occurred.24RWC10 $q_4$ fifo_sq_do_err: One Submission IO queue error occurred.24RWC10 $q_4$ fifo_sq_do_err: One Submission IO queue error occurred.24RWC10 $q_4$ fifo_sq_do_err: One Submission IO queue error occurred.25RWC10 $q_5$ fifo_sq_do_err: One Completion Status Field ok <td< td=""><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |      |       |                                                                       |

| 24         RWC1         0         0: Irq nyme_1 is set to 0           23         RWC1         0         q6. fflo_sq_do_err: One Submission IO queue error occurred.           22         RWC1         0         q6. fflo_sq_do_err: One Completion IO queue error occurred.           21         RWC1         0         q6. fflo_sq_do_err: One Completion IO queue error occurred.           21         RWC1         0         q6. fflo_sq_do_err: One Completion IO queue error occurred.           20         RWC1         0         q6. fflo_sq_do_err: One Submission IO queue error occurred.           20         RWC1         0         q5. fflo_sq_do_err: One Submission IO queue error occurred.           18         RWC1         0         q5. fflo_sq_do_err: One Completion IO queue error occurred.           18         RWC1         0         q5. fflo_sq_do_err: One Completion IO queue error occurred.           17         RWC1         0         q5. fflo_sq_do_err: One Submission IO queue error occurred.           16         RWC1         0         q5. fflo_sq_do_err: One Submission IO queue error occurred.           14         RWC1         0         q4. fflo_sq_do_err: One Submission IO queue error occurred.           14         RWC1         0         q4. fflo_sq_do_err: One Submission IO queue error occurred.           14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      |       |                                                                       |

| 1:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I:I: <td>24</td> <td>RWC1</td> <td>0</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24   | RWC1 | 0     |                                                                       |