# SmartFusion2, IGLOO2, RTG4 Tcl Commands Reference Guide Libero SoC v12.3

NOTE: PDF files are intended to be viewed on the printed page; links and cross-references in this PDF file may point to external files and generate an error when clicked. **View the online help included with software to enable all linked content.**

a MICROCHIP company

Microsemi Headquarters

One Enterprise, Aliso Viejo,

CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com www.microsemi.com

©2019 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

5-02-00529-5/12.19

# **Table of Contents**

| Table of Contents                           | 2  |

|---------------------------------------------|----|

| Introduction to Tcl Scripting               | 11 |

| Tcl Commands and Supported Families         | 11 |

| Tcl Command Documentation Conventions       | 11 |

| Project Manager Tcl Command Reference       | 13 |

| Basic Syntax                                | 17 |

| Special Characters                          | 17 |

| Sample Tcl Script                           | 17 |

| Types of Tcl commands                       | 18 |

| Variables                                   | 19 |

| Command substitution                        | 19 |

| Quotes and braces                           | 19 |

| Filenames                                   | 20 |

| Lists and arrays                            | 20 |

| Special arguments (command-line parameters) | 21 |

| Control structures                          |    |

| Print statement and Return values           | 22 |

| Running Tcl Scripts from the GUI            | 23 |

| Running Tcl Scripts from the Command Line   |    |

| Exporting Tcl Scripts                       | 25 |

| extended_run_lib                            | 26 |

| Sample Tcl Script - Project Manager         |    |

| Tcl Flow in the Libero SoC                  | 28 |

| Project Manager Tcl Commands                | 31 |

| add file to library                         |    |

| add_library                                 |    |

| add_profile                                 |    |

| add_modelsim_path                           |    |

| associate stimulus                          |    |

| build_design_hierarchy                      |    |

| change_link_source                          |    |

| change_vault_location                       |    |

| check fdc constraints                       |    |

| check_ndc_constraints                       |    |

| check pdc constraints                       |    |

| check sdc constraints                       |    |

| configure_core                              |    |

| configure_tool                              |    |

| create_and_configure_core        | 40 |

|----------------------------------|----|

| create_set                       | 41 |

| create_smartdesign               |    |

| delete_component                 | 42 |

| download_latest_cores            | 43 |

| export_ba_files                  | 43 |

| export_bitstream_file            | 44 |

| export_bsdl_file                 | 48 |

| export_component_to_tcl          | 48 |

| export_design_summary            | 49 |

| export_firmware                  | 49 |

| export_fp_pdc                    | 50 |

| export_ibis_file                 | 50 |

| export_io_pdc                    | 51 |

| export_job_data                  | 51 |

| export_netlist_file              | 52 |

| export_pin_reports               | 53 |

| export_prog_job                  | 53 |

| export_sdc_file                  | 55 |

| generate_component               | 55 |

| generate_sdc_constraint_coverage | 56 |

| get_libero_release               | 57 |

| get_libero_version               | 57 |

| get_tool_options                 | 58 |

| get_tool_state                   | 60 |

| import_component                 | 62 |

| import_component_data            | 62 |

| import_files (Libero SoC)        | 64 |

| loopback_test                    | 66 |

| new_project                      | 67 |

| open_smartdesign                 | 71 |

| organize_tool_files              | 71 |

| prbs_test                        | 72 |

| publish_block                    | 73 |

| rename_file                      | 74 |

| run_tool                         | 75 |

| save_smartdesign                 | 77 |

| select_libero_design_device      | 78 |

| set_as_target                    | 78 |

| set_live_probe                   | 79 |

| unset_as_target                  | 79 |

|                                  |    |

| SmartDesign Tcl Commands         |    |

| sd_add_pins_to_group             |    |

| sd_clear_pin_attributes          | 81 |

| sd_configure_core_instance       | 82 |

| sd_connect_instance_pins_to_ports     |     |

|---------------------------------------|-----|

| sd_connect_net_to_pins                | 83  |

| sd_connect_pins_to_constant           |     |

| sd_connect_pin_to_port                | 84  |

| sd_connect_pins                       | 85  |

| sd_create_bif_net                     | 86  |

| sd_create_bif_port                    | 86  |

| sd_create_bus_net                     | 88  |

| sd_create_bus_port                    | 88  |

| sd_create_pin_group                   | 89  |

| sd_create_pin_slices                  | 90  |

| sd_create_scalar_net                  | 90  |

| sd_create_scalar_port                 | 91  |

| sd_delete_instances                   | 91  |

| sd_delete_nets                        | 92  |

| sd_delete_pin_group                   | 92  |

| sd_delete_pin_slices                  | 93  |

| sd_delete_ports                       | 93  |

| sd_disconnect_instance                | 94  |

| sd_disconnect_pins                    | 94  |

| sd_duplicate_instance                 | 95  |

| sd_hide_bif_pins                      | 96  |

| sd_instantiate_component              | 96  |

| sd_instantiate_core                   | 97  |

| sd_instantiate_hdl_core               | 97  |

| sd_instantiate_hdl_module             | 98  |

| sd_instantiate_macro                  | 98  |

| sd_invert_pins                        | 99  |

| sd_mark_pins_unused                   | 99  |

| sd_remove_pins_from_group             | 100 |

| sd_rename_instance                    | 101 |

| sd_rename_net                         | 101 |

| sd_rename_pin_group                   | 102 |

| sd_rename_port                        | 102 |

| sd_save_core_instance_config          | 103 |

| sd_show_bif_pins                      | 103 |

| sd_update_instance                    | 104 |

| UDI Tel Commonde                      | 40. |

| HDL Tcl Commands                      |     |

| create_hdl_core                       |     |

| hdl_core_add_bif                      |     |

| hdl_core_assign_bif_signal            |     |

| hdl_core_delete_parameters            |     |

| hdl_core_extract_ports_and_parameters |     |

| hdl_core_remove_bif                   |     |

| hdl_core_rename_bif                   | 108 |

| hdl_core_unassign_bif_signal                    |     |

|-------------------------------------------------|-----|

| remove_hdl_core                                 | 109 |

| Command Tools                                   | 110 |

| CONFIGURE ACTIONS PROCEDURES                    |     |

| CONFIGURE CHAIN                                 |     |

| CONFIGURE PROG OPTIONS                          |     |

| CONFIGURE_PROG_OPTIONS_RTG4 (RTG4 only)         |     |

| FLASH FREEZE                                    |     |

| EXPORTNETLIST                                   |     |

| EXPORTSDF                                       |     |

| GENERATEPROGRAMMINGDATA                         |     |

| GENERATEPROGRAMMINGFILE                         |     |

| INIT LOCK                                       |     |

| PROGRAMDEVICE                                   |     |

| PLACEROUTE                                      |     |

| PROGRAM_OPTIONS (SmartFusion2 and IGLOO2)       |     |

| PROGRAM RECOVERY                                |     |

| PROGRAMMER INFO                                 |     |

| SIM POSTLAYOUT                                  |     |

| SPM                                             |     |

| SYNTHESIZE                                      |     |

| USER_PROG_DATA (SmartFusion2, IGLOO2)           |     |

| VERIFYPOWER                                     |     |

| VERIFYTIMING                                    |     |

|                                                 |     |

| SmartTime Tcl Commands                          | 134 |

| all_inputs                                      | 134 |

| all_outputs                                     | 134 |

| all_registers                                   | 135 |

| check_constraints                               | 135 |

| clone_scenario (SmartFusion2, IGLOO2, and RTG4) | 136 |

| create_clock                                    | 136 |

| create_generated_clock                          | 137 |

| create_scenario                                 | 139 |

| create_set                                      | 139 |

| expand_path                                     | 141 |

| get_cells                                       | 142 |

| get_clocks                                      | 143 |

| get_current_scenario                            | 144 |

| get_nets                                        | 144 |

| get_pins                                        | 145 |

| get_ports                                       | 146 |

| list_clock_groups                               | 146 |

| list_clock_latencies                            | 147 |

| list_clock_uncertainties                        | 147 |

| list_clocks              | 147 |

|--------------------------|-----|

| list disable timings     |     |

| list_false_paths         |     |

| list generated clocks    |     |

| list_input_delays        |     |

| list_max_delays          |     |

| list min delays          |     |

| list_multicycle_paths    |     |

| list objects             |     |

| list output delays       |     |

| list paths               |     |

| list scenarios           |     |

| read sdc                 |     |

| remove all constraints   |     |

| remove_clock             |     |

| remove clock groups      |     |

| remove clock latency     |     |

| remove_clock_uncertainty |     |

| remove disable timing    |     |

| remove false path        |     |

| remove generated clock   |     |

| remove input delay       |     |

| remove max_delay         |     |

| remove_min_delay         |     |

| remove_multicycle_path   |     |

| remove output delay      |     |

| remove scenario          |     |

| remove_set               |     |

| rename scenario          |     |

| report                   |     |

| save                     | 170 |

| set_clock_groups         | 170 |

| set_clock_latency        | 172 |

| set clock to output      |     |

| set_clock_uncertainty    | 174 |

| set_current_scenario     |     |

| set_disable_timing       | 176 |

| set_external_check       | 176 |

| set_false_path           | 177 |

| set_input_delay          | 178 |

| set_max_delay            | 179 |

| set_min_delay            | 180 |

| set_multicycle_path      | 181 |

| set_options              | 183 |

| set_output_delay         | 185 |

| write_sdc                | 186 |

| SmartPower Tcl Commands                         | 188 |

|-------------------------------------------------|-----|

| smartpower_add_new_scenario                     | 188 |

| smartpower_add_pin_in_domain                    | 188 |

| smartpower_battery_settings                     | 189 |

| smartpower_change_clock_statistics              | 190 |

| smartpower_change_setofpin_statistics           | 191 |

| smartpower_commit                               | 192 |

| smartpower_compute_vectorless                   | 192 |

| smartpower_create_domain                        | 193 |

| smartpower_edit_scenario                        | 193 |

| smartpower_import_vcd                           | 194 |

| smartpower_init_do                              | 196 |

| smartpower_init_set_clocks_options              | 198 |

| smartpower_init_set_combinational_options       | 199 |

| smartpower_init_set_enables_options             | 200 |

| smartpower_init_set_primaryinputs_options       | 200 |

| smartpower_init_set_registers_options           | 201 |

| smartpower_init_setofpins_values                | 201 |

| smartpower_remove_all_annotations               | 202 |

| smartpower_remove_file                          | 203 |

| smartpower_remove_pin_probability               | 204 |

| smartpower_remove_scenario                      | 204 |

| smartpower_report_power                         | 204 |

| smartpower_set_mode_for_pdpr                    | 212 |

| smartpower_set_operating_condition              | 213 |

| smartpower_set_operating_conditions             | 213 |

| smartpower_set_process                          | 214 |

| smartpower_set_temperature_opcond               | 215 |

| smartpower_set_voltage_opcond                   | 216 |

| smartpower_temperature_opcond_set_design_wide   | 217 |

| smartpower_temperature_opcond_set_mode_specific | 217 |

| smartpower_voltage_opcond_set_design_wide       | 218 |

| smartpower_voltage_opcond_set_mode_specific     | 219 |

|                                                 |     |

| FlashPro Express Tcl Commands                   |     |

| close_project                                   |     |

| complete_prog_job                               |     |

| configure_flashpro3_prg                         |     |

| configure_flashpro4_prg                         |     |

| configure_flashpro5_prg                         |     |

| configure_flashpro6_prg                         |     |

| create_job_project                              | 225 |

| dump_tcl_support                                | 226 |

| enable_serialization                            | 226 |

| get_job_status                                  | 227 |

| open_project                                    | 227 |

| oing_prg                               | 228 |

|----------------------------------------|-----|

| process_job_request                    |     |

| efresh_prg_list                        | 229 |

| emove_hsm_tickets                      | 229 |

| emove_prg                              | 230 |

| un_selected_actions                    | 231 |

| save_log                               | 231 |

| save_project                           | 232 |

| scan_chain_prg                         | 232 |

| select_serial_range                    | 233 |

| self_test_prg                          | 233 |

| set_hsm_params                         | 234 |

| set_prg_name                           | 234 |

| set_programming_action                 | 235 |

| set_programming_file                   | 235 |

| set_serialization_log_file             | 236 |

| 2 (D.L. T.L.)                          |     |

| SmartDebug Tcl Commands                |     |

| add_probe_insertion_point              |     |

| add_to_probe_group                     |     |

| construct_chain_automatically          |     |

| create_probe_group                     |     |

| ddr_read                               |     |

| ddr_write                              |     |

| delete_active_probe                    |     |

| enable_device                          |     |

| event_counter                          |     |

| export_smart_debug_data                |     |

| hb_control                             | 243 |

| requency_monitor                       | 245 |

| get_programmer_info                    |     |

| oad_active_probe_list                  | 246 |

| oopback_test                           | 246 |

| move_to_probe_group                    | 247 |

| orbs_test                              | 247 |

| program_probe_insertion                | 248 |

| ıngroup                                | 248 |

| ead_active_probe                       | 248 |

| ead_Isram (SmartFusion2, IGLOO2, RTG4) | 249 |

| ead_usram (SmartFusion2, IGLOO2, RTG4) | 250 |

| emove_from_probe_group                 | 251 |

| emove_probe_insertion_point            | 251 |

| un_selected_actions                    | 252 |

| save_active_probe_list                 | 252 |

|                                        | 253 |

| scan_chain_prg                         | 233 |

| set_debug_programmer                     | 254  |

|------------------------------------------|------|

| set_device_name                          | 254  |

| set_programming_action                   | 255  |

| set_programming_file                     | 256  |

| serdes_lane_reset                        | 256  |

| serdes_read_register                     | 257  |

| serdes_write_register                    | 258  |

| set_live_probe                           | 259  |

| ungroup                                  | 259  |

| unset_live_probe                         | 260  |

| write_active_probe                       | 260  |

| write_Isram (SmartFusion2, IGLOO2, RTG4) | 261  |

| write_usram (SmartFusion2, IGLOO2, RTG4) | 262  |

|                                          |      |

| Configure JTAG Chain Tcl Commands        |      |

| add_actel_device                         |      |

| add_non_actel_device                     | 264  |

| add_non_actel_device_to_database         |      |

| construct_chain_automatically            |      |

| copy_device                              | 266  |

| cut_device                               | 266  |

| enable_device                            | 267  |

| paste_device                             | 267  |

| remove_device                            |      |

| remove_non_actel_device_from_database    | 268  |

| select_libero_design_device              | 269  |

| set_bsdl_file                            | 269  |

| set_device_ir                            | 270  |

| set_device_name                          | 270  |

| set_device_order                         | 271  |

| set_device_tck                           | 271  |

| set_device_type                          | 272  |

| set_programming_action                   | 272  |

| set_programming_file                     | 273  |

| Additional Tal Commonda                  | 07.4 |

| Additional Tcl Commands                  |      |

| ssn_analyzer_set_pulse_width             |      |

| nvm_update_serialization_client          |      |

| nvm_update_storage_client                |      |

| select_programmer                        |      |

| set_programming_interface                |      |

| ssn_analyzer_noise_report                |      |

| ssn_analyzer_rerun_analysis              |      |

| ssn_analyzer_set_dontcare                |      |

| ssn_analyzer_set_pulse_width             |      |

| ssn_analyzer_set_static                  | 280  |

#### Tcl Commands Reference Guide

| ssn_analyzer_summary_report | 281 |

|-----------------------------|-----|

| update storage client       | 281 |

# **Introduction to Tcl Scripting**

Tcl, the Tool Command Language, pronounced *tickle*, is an easy-to-learn scripting language that is compatible with Libero SoC software. You can run scripts from either the Windows or Linux command line or store and run a series of commands in a \*.tcl batch file.

This section provides a quick overview of the main features of Tcl:

- Basic syntax

- Types of Tcl commands

- <u>Variables</u>

- Command substitution

- Quotes and braces

- Lists and arrays

- · Control structures

- · Print statement and Return values

- · Running Tcl scripts from the command line

- Exporting Tcl scripts

- Project Manager Tcl Commands

For complete information on Tcl scripting, refer to one of the books available on this subject. You can also find information about Tcl at web sites such as <a href="http://www.tcl.tk">http://www.tcl.tk</a>.

Libero SoC provides additional capabilities and built-in Tcl Commands:

- Running Tcl scripts from the command line

- Exporting Tcl scripts

- extended run lib

- · Tcl Commands as specified in this document

# Tcl Commands and Supported Families

When we specify a family name, we refer to the device family and all its derivatives, unless otherwise specified. See Supported Families in the Tcl command help topics for the families supported for a specific Tcl command.

# **Tcl Command Documentation Conventions**

The following table shows the typographical conventions used for the Tcl command syntax.

| Syntax Notation              | Description                                                                                                                                                                              |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| command - argument           | Commands and arguments appear in Courier New typeface.                                                                                                                                   |

| variable                     | Variables appear in blue, italic Courier New typeface. You must substitute an appropriate value for the variable.                                                                        |

| [-argumentvalue] [variable]+ | Optional arguments begin and end with a square bracket with one exception: if the square bracket is followed by a plus sign (+), then users must specify at least one argument. The plus |

| Syntax | Notation | Description                                                                                                     |

|--------|----------|-----------------------------------------------------------------------------------------------------------------|

|        |          | sign (+) indicates that items within the square brackets can be repeated. Do not enter the plus sign character. |

Note: All Tcl commands are case sensitive. However, their arguments are not.

## **Examples**

Syntax for the get clocks command followed by a sample command:

```

get_clocks variable

get clocks clk1

```

Syntax for the backannotate command followed by a sample command:

```

backannotate -name file_name -format format_type -language language -dir directory_name [-

netlist] [-pin]

backannotate -dir \

{..\design} -name "fanouttest ba.sdf" -format "SDF" -language "VERILOG" \

```

#### **Wildcard Characters**

You can use the following wildcard characters in names used in Tcl commands:

| Wildcard | What it Does                                                                                                                       |

|----------|------------------------------------------------------------------------------------------------------------------------------------|

| \        | Interprets the next character literally                                                                                            |

| ?        | Matches any single character                                                                                                       |

| *        | Matches any string                                                                                                                 |

| []       | Matches any single character among those listed between brackets (that is, [A-Z] matches any single character in the A-to-Z range) |

Note: The matching function requires that you add a slash (\) before each slash in the port, instance, or net name when using wildcards in a PDC command. For example, if you have an instance named "A/B12" in the netlist, and you enter that name as "A\\/B\*" in a PDC command, you will not be able to find it. In this case, you must specify the name as A\\\\/B\*.

# Special Characters [], {}, and \

Sometimes square brackets ([ ]) are part of the command syntax. In these cases, you must either enclose the open and closed square brackets characters with curly brackets ({ }) or precede the open and closed square brackets ([ ]) characters with a backslash (\). If you do not, you will get an error message.

For example:

```

pin_assign -port {LFSR_OUT[0]} -pin 15

or

pin assign -port LFSR OUT\[0\] -pin 180

```

Note: Tcl commands are case sensitive. However, their arguments are not.

## **Entering Arguments on Separate Lines**

To enter an argument on a separate line, you must enter a backslash (\) character at the end of the preceding line of the command as shown in the following example:

```

backannotate -dir \

{..\design} -name "fanouttest_ba.sdf" -format "SDF" -language "VERILOG" \

-netlist

```

#### See Also

Introduction to Tcl scripting

Basic syntax

# **Project Manager Tcl Command Reference**

A Tcl (Tool Command Language) file contains scripts for simple or complex tasks. You can run scripts from either the Windows or UNIX command line or store and run a series of Tcl commands in a \*.tcl batch file. You can also run scripts from within the GUI in Project Manager.

Note: Tcl commands are case sensitive. However, their arguments are not.

The following table lists some of the Tcl scripting commands supported by the Libero SoC Project Manager:

| Command                                              | Action                                                                                                             |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| add file to library                                  | Adds a file to a library in your project                                                                           |

| add library                                          | Adds a VHDL library to your project                                                                                |

| add_probe                                            | Adds a probe to an internal net in your design, using the original name from the optimized netlist in your design. |

| add modelsim path                                    | Adds a ModelSim simulation library to your project                                                                 |

| add profile                                          | Adds a profile; sets the same values as the Add or Edit Profile dialog box                                         |

| associate stimulus                                   | Associates a stimulus file in your project                                                                         |

| change link source                                   | Changes the source of a linked file in your project                                                                |

| check_hdl                                            | Checks the HDL in the specified file                                                                               |

| check_schematic                                      | Checks the schematic                                                                                               |

| close_project                                        | Closes the current project in Libero SoC                                                                           |

| configure tool<br>(SmartFusion2,IGLOO2,<br>and RTG4) | Tcl command to set the parameters for any tool called by Libero for the SmartFusion2, IGLOO2, and RTG4 families.   |

| create_links                                         | Creates a link (or links) to a file/files in your project                                                          |

| create_symbol                                        | Creates a symbol in a module                                                                                       |

| delete_files                                         | Deletes files from your Libero SoC project                                                                         |

| download_core                                        | Downloads a core and adds it to your repository                                                                    |

| Command                         | Action                                                                                   |

|---------------------------------|------------------------------------------------------------------------------------------|

| edit profile                    | Edits a profile; sets the same values as the Add or Edit<br>Profile dialog box           |

| export as link                  | Exports a file to another directory and links to the file                                |

| export ba files                 | Exports the backannotated files.                                                         |

| export_bitstream_file           | Configures parameters for your exported bitstream.                                       |

| export bsdl file                | Exports the BSDL to a specified file.                                                    |

| export design summary           | Exports an HTML file containing information about your root SmartDesign in your project. |

| export firmware                 | Exports design firmware configuration data.                                              |

| export fp_pdc                   | Exports the Floorplanning Physical Design Constraint (*.pdc) File.                       |

| export_io_pdc                   | Exports the I/O constraints Physical Design Constraint (*.pdc) File.                     |

| export_netlist_file             | Exports the netlist after the compile state has completed.                               |

| export profiles                 | Exports your tool profiles; performs the same action as the Export Profiles dialog box   |

| export prog job                 | Exports your programming job.                                                            |

| export script                   | Explicitly exports the Tcl command equivalents of the current Libero session.            |

| export sdc file                 | Exports the SDC (Synopsys Design Constraint) file for timing constraints.                |

| generate_ba_files               | Generates the back-annotate files for your desig.n                                       |

| generate_hdl_from_schema<br>tic | Generates an HDL file from your schematic.                                               |

| generate_hdl_netlist            | Generates the HDL netlist for your design and runs the design rule check.                |

| import component data           | Imports component data into an existing Libero project.                                  |

| import_files (Libero SoC)       | Imports files into your Libero SoC project                                               |

| import_vcd                      | Imports a VCD file into your project                                                     |

| new project                     | Creates a new project in the Libero SoC                                                  |

| open_project                    | Opens an existing Libero SoC project                                                     |

| organize_cdbs                   | Organizes the CDB files in your project                                                  |

| Command                                   | Action                                                                                           |

|-------------------------------------------|--------------------------------------------------------------------------------------------------|

| organize constraints                      | Organizes the constraint files in your project                                                   |

| organize_sources                          | Organizes the source files in your project                                                       |

| organize_tool_files                       | Specifies specific constraint files to be passed to and used by a Libero tool.                   |

| project_settings                          | Modifies project flow settings for your Libero SoC project                                       |

| read active probe                         | Reads active probe values from the device.                                                       |

| <u>refresh</u>                            | Refreshes your project, updates the view and checks for updated links and files.                 |

| remove_core                               | Removes a core from your project                                                                 |

| remove library                            | Removes a VHDL library from your project                                                         |

| remove_pin_enable_rate                    | Remove a pin enable rate                                                                         |

| remove profile                            | Deletes a tool profile                                                                           |

| rename_library                            | Renames a VHDL library in your project                                                           |

| rollback_constraints_from_a db            | Opens the ADB file, exports the PDC file, and then replaces it with the specified PDC file       |

| run_designer                              | Runs Designer with compile and layout options (if selected)                                      |

| run_drc                                   | Runs the design rule check on your netlist and generates an HDL file                             |

| run_simulation                            | Runs simulation on your project with your default simulation tool and creates a logfile          |

| run tool (SmartFusion2, IGLOO2, and RTG4) | Starts the specified tool.                                                                       |

| run_synthesis                             | Runs synthesis on your project and creates a logfile                                             |

| save_log                                  | Saves your Libero SoC log file                                                                   |

| save_project                              | Saves your project                                                                               |

| save project as                           | Saves your project with a different name                                                         |

| select_active_probe                       | Manages the current selection of active probe points to be used by active probe READ operations. |

| select profile                            | Selects a profile to use in your project                                                         |

| set_actel_lib_options                     | Sets your simulation library to default, or to another library                                   |

| Command                         | Action                                                            |

|---------------------------------|-------------------------------------------------------------------|

| set device (Project<br>Manager) | Sets your device family, die, and package in the Project Manager  |

| set live probe                  | Channels A and/or B to the specified probe point(s).              |

| set modelsim options            | Sets your ModelSim simulation options                             |

| set_option                      | Sets your synthesis options on a module                           |

| set user lib options            | Sets your user library options during simulation                  |

| set root                        | Sets the module you specify as the root                           |

| synplify                        | Runs Synplify in batch mode and executes a Tcl script.            |

| synplify_pro                    | Runs Synplify Pro in batch mode and executes a Tcl script.        |

| unlink                          | Removes a link to a file in your project                          |

| use_file                        | Specifies which file in your project to use                       |

| use source file                 | Defines a module for your project                                 |

| write active probe              | Sets the target probe point on the device to the specified value. |

# **Basic Syntax**

Tcl scripts contain one or more commands separated by either new lines or semicolons. A Tcl command consists of the name of the command followed by one or more arguments. The format of a Tcl command is:

```

command arg1 ... argN

```

The command in the following example computes the sum of 2 plus 2 and returns the result, 4.

```

expr 2 + 2

```

The **expr** command handles its arguments as an arithmetic expression, computing and returning the result as a string. All Tcl commands return results. If a command has no result to return, it returns an empty string.

To continue a command on another line, enter a backslash (\) character at the end of the line. For example, the following Tcl command appears on two lines:

```

import -format "edif" -netlist_naming "Generic" -edif_flavor "GENERIC" {prepi.edn}

```

Comments must be preceded by a hash character (#). The comment delimiter (#) must be the first character on a line or the first character following a semicolon, which also indicates the start of a new line. To create a multi-line comment, you must put a hash character (#) at the beginning of each line.

Note: Be sure that the previous line does not end with a continuation character (\). Otherwise, the comment line following it will be ignored.

# **Special Characters**

Square brackets ([]) are special characters in Tcl. To use square brackets in names such as port names, you must either enclose the entire port name in curly braces, for example, pin\_assign -port {LFSR\_OUT[15]} -iostd lvttl -slew High, or lead the square brackets with a slash (\) character as shown in the following example:

```

\label{lem:pin_assign_port_lfsr_outlimit} $$ pin_assign -port LFSR_OUT \setminus [15\] -iostd lvttl -slew High

```

# Sample Tcl Script

```

#Create a new project and set up a new design

new project -location {C:/sf2} -name {sf2} -project description {} -block mode 0 -

standalone_peripheral_initialization 0 \

-instantiate in smartdesign 1 -ondemand build dh 1 -hdl {VERILOG} -family {SmartFusion2}

-die {M2S010} -package {484 FBGA} -speed {STD} \

-die voltage {1.2} -part range {IND} -adv options {IO DEFT STD:LVCMOS 2.5V} -adv options

{RESTRICTPROBEPINS:1} -adv options {RESTRICTSPIPINS:0} \

-adv_options {TEMPR:IND} -adv_options {UNUSED_MSS_IO_RESISTOR_PULL:None} -adv_options

{VCCI 1.2 VOLTR:COM} -adv options {VCCI 1.5 VOLTR:COM} \

-adv options {VCCI 1.8 VOLTR:COM} -adv options {VCCI 2.5 VOLTR:COM} -adv options

{VCCI 3.3 VOLTR:COM} -adv options {VOLTR:IND}

#Import the component file

import component -file {C:/g4 ccf 119/component/work/top/top.cxf}

# generate the component

generate component -component name {top} -recursive 1

# build design hierarchy

build design hierarchy

#set the top level design name

set root -module {top::work}

#Import the pdc file

import_files -io_pdc {C:/g4_ccf_119/constraint/io/top.io.pdc}

# tun Synthesis

run tool -name {SYNTHESIZE}

```

```

# organize the constraint file

organize_tool_files -tool {PLACEROUTE} -file {C:/sf2/constraint/io/top.io.pdc} -module

{top::work} -input_type {constraint}

#run the Place and Route tool

run_tool -name {PLACEROUTE}

# run verify timing

run_tool -name {VERIFYTIMING}

#export the bitstream file

export_bitstream_file -file_name {top} -export_dir {C:\sf2\designer\top\export} -format

{STP DAT}

#save the design

save project

```

# Types of Tcl commands

This section describes the following types of Tcl commands:

- · Built-in commands

- · Procedures created with the proc command

#### **Built-in commands**

Built-in commands are provided by the Tcl interpreter. They are available in all Tcl applications. Here are some examples of built-in Tcl commands:

- Tcl provides several commands for manipulating file names, reading and writing file attributes, copying files, deleting files, creating directories, and so on.

- exec run an external program. Its return value is the output (on stdout) from the program, for example:

```

set tmp [ exec myprog ]

puts stdout $tmp

```

- You can easily create collections of values (lists) and manipulate them in a variety of ways.

- You can create arrays structured values consisting of name-value pairs with arbitrary string values for the names and values.

- You can manipulate the time and date variables.

- You can write scripts that can wait for certain events to occur, such as an elapsed time or the availability of input data on a network socket.

## Procedures created with the proc command

You use the proc command to declare a procedure. You can then use the name of the procedure as a Tcl command.

The following sample script consists of a single command named **proc**. The proc command takes three arguments:

- The name of a procedure (myproc)

- A list of argument names (arg1 arg2)

- The body of the procedure, which is a Tcl script

```

proc myproc { arg1 arg2 } {

# procedure body

}

myproc a b

```

# **Variables**

With Tcl scripting, you can store a value in a variable for later use. You use the set command to assign variables. For example, the following set command creates a variable named x and sets its initial value to 10.

```

set x 10

```

A variable can be a letter, a digit, an underscore, or any combination of letters, digits, and underscore characters. All variable values are stored as strings.

In the Tcl language, you do not declare variables or their types. Any variable can hold any value. Use the dollar sign (\$) to obtain the value of a variable, for example:

```

set a 1

set b $a

set cmd expr

set x 11

$cmd $x*$x

```

The dollar sign \$ tells Tcl to handle the letters and digits following it as a variable name and to substitute the variable name with its value.

#### **Global Variables**

Variables can be declared global in scope using the Tcl global command. All procedures, including the declaration can access and modify global variables, for example:

```

global myvar

```

# Command substitution

By using square brackets ([]), you can substitute the result of one command as an argument to a subsequent command, as shown in the following example:

```

set a 12

set b [expr $a*4]

```

Tcl handles everything between square brackets as a nested Tcl command. Tcl evaluates the nested command and substitutes its result in place of the bracketed text. In the example above, the argument that appears in square brackets in the second set command is equal to 48 (that is,  $12^* 4 = 48$ ).

Conceptually,

```

set b [expr $a * 4]

expands to

set b [expr 12 * 4]

and then to

set b 48

```

# Quotes and braces

The distinction between braces ({ }) and quotes (" ") is significant when the list contains references to variables. When references are enclosed in quotes, they are substituted with values. However, when references are enclosed in braces, they are not substituted with values.

Example

| With Braces                  | With Double Quotes           |

|------------------------------|------------------------------|

| set b 2                      | set b 2                      |

| set t { 1 \$b 3 }            | set t " 1 \$b 3 "            |

| set s { [ expr \$b + \$b ] } | set s " [ expr \$b + \$b ] " |

| With Braces     | With Double Quotes |

|-----------------|--------------------|

| puts stdout \$t | puts stdout \$t    |

| puts stdout \$s | puts stdout \$s    |

## **Filenames**

In Tcl syntax, filenames should be enclosed in braces { } to avoid backslash substitution and white space separation. Backslashes are used to separate folder names in Windows-based filenames. The problem is that sequences of "\n" or "\t" are interpreted specially. Using the braces disables this special interpretation and specifies that the Tcl interpreter handle the enclosed string literally. Alternatively, double-backslash "\n" and "\t" would work as well as forward slash directory separators "/n" and "/t". For example, to specify a file on your Windows PC at c:\newfiles\thisfile.adb, use one of the following:

```

{C:\newfiles\thisfile.adb}

C:\\newfiles\\thisfile.adb

"C:\\newfiles\\thisfile.adb"

C:/newfiles/thisfile.adb

"C:/newfiles/thisfile.adb"

```

If there is white space in the filename path, you must use either the braces or double-quotes. For example:

```

C:\program data\thisfile.adb

```

should be referenced in Tcl script as

```

{C:\program data\thisfile.adb} or "C:\\program data\\thisfile.adb"

```

If you are using variables, you cannot use braces {} because, by default, the braces turn off all special interpretation, including the dollar sign character. Instead, use either double-backslashes or forward slashes with double quotes. For example:

```

"$design name.adb"

```

Note: To use a name with special characters such as square brackets [], you must put the entire name between curly braces {} or put a slash character \ immediately before each square bracket.

The following example shows a port name enclosed with curly braces:

```

pin_assign -port {LFSR_OUT[15]} -iostd lvttl -slew High

```

The next example shows each square bracket preceded by a slash:

```

pin assign -port LFSR OUT\[15\] -iostd lvttl -slew High

```

# Lists and arrays

A list is a way to group data and handle the group as a single entity. To define a list, use curly braces { } and double quotes " ". For example, the following set command {1 2 3 }, when followed by the list command, creates a list stored in the variable "a." This list will contain the items "1," "2," and "3."

```

set a { 1 2 3 }

Here's another example:

set e 2

set f 3

set a [ list b c d [ expr $e + $f ] ]

puts $a

displays (or outputs):

```

b c d 5

Tcl supports many other list-related commands such as lindex, linsert, llength, lrange, and lappend. For more information, refer to one of the books or web sites available on this subject.

## **Arrays**

An array is another way to group data. Arrays are collections of items stored in variables. Each item has a unique address that you use to access it. You do not need to declare them nor specify their size.

Array elements are handled in the same way as other Tcl variables. You create them with the set command, and you can use the dollar sign (\$) for their values.

```

set myarray(0) "Zero"

set myarray(1) "One"

set myarray(2) "Two"

for {set i 0} {$i < 3} {incr i 1} {

Output:

Zero

One

Two</pre>

```

In the example above, an array called "myarray" is created by the set statement that assigns a value to its first element. The for-loop statement prints out the value stored in each element of the array.

# Special arguments (command-line parameters)

You can determine the name of the Tcl script file while executing the Tcl script by referring to the \$argv0 variable.

```

puts "Executing file $argv0"

```

To access other arguments from the command line, you can use the lindex command and the argv variable:

To read the the Tcl file name:

```

lindex $argv 0

```

To read the first passed argument:

```

lindex $argv 1

```

#### Example

```

puts "Script name is $argv0"; # accessing the scriptname

puts "first argument is [lindex $argv 0]"

puts "second argument is [lindex $argv 1]"

puts "third argument is [lindex $argv 2]"

puts "number of argument is [llength $argv]"

set des_name [lindex $argv 0]

puts "Design name is $des name"

```

# Control structures

Tcl control structures are commands that change the flow of execution through a script. These control structures include commands for conditional execution (if-then-elseif-else) and looping (while, for, catch).

An "if" statement only executes the body of the statement (enclosed between curly braces) if the Boolean condition is found to be true.

#### if/else statements

```

if { "$name" == "paul" } then {

...

# body if name is paul

} elseif { $code == 0 } then {

...

# body if name is not paul and if value of variable code is zero

```

```

} else {

...

# body if above conditions is not true

}

```

## for loop statement

A "for" statement will repeatedly execute the body of the code as long as the index is within a specified limit.

```

for { set i 0 } { $i < 5 } { incr i } {

...

# body here

}</pre>

```

## while loop statement

A "while" statement will repeatedly execute the body of the code (enclosed between the curly braces) as long as the Boolean condition is found to be true.

```

while { $p > 0 } {

...

}

```

#### catch statement

A "catch" statement suspends normal error handling on the enclosed Tcl command. If a variable name is also used, then the return value of the enclosed Tcl command is stored in the variable.

```

catch { open "$inputFile" r } myresult

```

# Print statement and Return values

#### **Print Statement**

Use the puts command to write a string to an output channel. Predefined output channels are "stdout" and "stderr." If you do not specify a channel, then puts display text to the stdout channel.

Note: The STDIN Tcl command is not supported by Microsemi SoC tools.

#### Example:

```

set a [ myprog arg1 arg2 ]

puts "the answer from myprog was $a (this text is on stdout)"

puts stdout "this text also is on stdout"

```

## **Return Values**

The return code of a Tcl command is a string. You can use a return value as an argument to another function by enclosing the command with square brackets [].

#### Example:

```

set a [ prog arg1 arg2 ]

```

The Tcl command "exec" will run an external program. The return value of "exec" is the output (on stdout) from the program.

```

Example:

set tmp [ exec myprog ]

puts stdout $tmp

```

# Running Tcl Scripts from the GUI

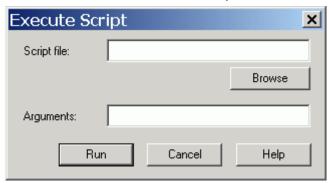

Instead of running scripts from the command line, you can use Execute Script dialog box to run a script in the software.

#### To run a Tcl script from the GUI:

1. In Libero SoC, from the File menu choose Execute Script.

Figure 1 Execute Script Dialog Box

- Click Browse to display the Open dialog box, in which you can navigate to the folder containing the script file to open. When you click Open, the software enters the full path and script filename into the Execute Script dialog box for you.

- 3. In the Arguments edit box, enter the arguments to pass to your Tcl script as shown in the following sample Execute Script dialog box. Separate each argument by a space character. For information about accessing arguments passed to a Tcl script, see "Running Scripts from the command line."

Figure 2 · Execute Script Dialog Box Example

4. Click Run.

Specify your arguments in the Execute Script dialog box. To get those argument values from your Tcl script, use the following:

```

puts "Script name: $argv0"

puts "Number of arguments: $argc"

set i 0

foreach arg $argv {

puts "Arg $i : $arg"

incr i

}

```

# Running Tcl Scripts from the Command Line

You can run Tcl scripts from your Windows or Linux command line as well as pass arguments to scripts from the command line.

Note: Tcl commands in this section are not case-sensitive.

#### To execute a Tcl script file in the Libero SoC Project Manager software from a shell command line:

At the prompt, type the path to the Microsemi SoC software installation location followed by the word "SCRIPT" and a colon, and then the name of the script file as follows:

#### For Linux:

```

<location of Libero SoC software installation>/bin/libero

script:<filename>.tcl

```

#### For Windows:

```

<location of Libero SoC software installation>\Designer\bin\libero.exe

script:<filename>.tcl

```

where <location of Microsemi SoC software> is the root directory in which you installed the Microsemi SoC software, and <filename> is the name, including a relative or absolute path, of the Tcl script file to execute. For example, to run the Tcl script file "myscript.tcl", type:

#### For Linux:

```

C:\libero\bin\libero script:myscript.tcl

```

#### For Windows:

```

C:/Microsemi/Libero/Designer/bin/libero.exe script:myscript.tcl

```

#### To pass arguments from the command line to your Tcl script file:

At the prompt, type the path to the Microsemi SoC software installation location followed by the SCRIPT argument:

#### For Linux:

```

<location of Microsemi SoC software>\bin\libero "SCRIPT_ARGS:<filename

arg1 arg2 ...>"

```

#### For Windows:

```

<location of Microsemi SoC software>/Designer/bin/libero.exe

"SCRIPT ARGS:<filename arg1 arg2 ...>"

```

where <location of Microsemi SoC software> is the root directory in which you installed the Microsemi SoC software, and "SCRIPT\_ARGS:<filename arg1 arg2 ...>" is the name, including a relative or absolute path, of the Tcl script file and arguments you are passing to the script file.

#### For example:

```

C:\libero\bin\libero SCRIPT:myscript.tcl "SCRIPT ARGS:one two three"

```

#### To obtain the output from the log file:

At the prompt, type the path to the Microsemi SoC software installation location followed by the SCRIPT, SCRIPT\_ARGS and LOGFILE arguments.

```

<location of Microsemi SoC software> SCRIPT:<filename>.tcl

"SCRIPT_ARGS:a b c" LOGFILE:<output.log>

```

#### where

- location of Microsemi SoC software is the root directory in which you installed the Microsemi SoC software.

- SCRIPT:<filename>.tcl is the name, including a relative or absolute path, of the

Tcl script file

- SCRIPT ARGS are the arguments you are passing to the script file

- output.log is the name of the log file

#### For example:

C:\libero\designer\bin\libero SCRIPT:testTCLparam.tcl "SCRIPT\_ARGS:a b

c" LOGFILE:testTCLparam.log

# **Exporting Tcl Scripts**

You can write out a Tcl script file that contains the commands executed in the current session. You can then use this exported Tcl script to re-execute the same commands interactively or in batch. You can also use this exported script to become more familiar with Tcl syntax.

You can export Tcl scripts from the Project Manager.

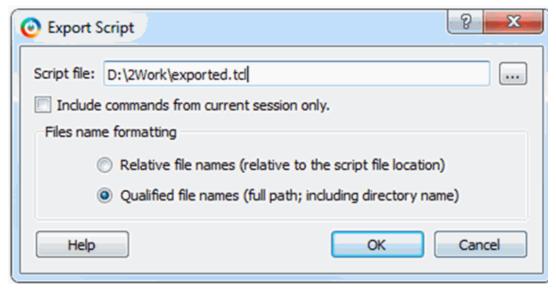

#### To export a Tcl session script from the Project Manager:

- 1. From the File menu, choose Export Script File. The Export Script dialog box appears.

- 2. Click **OK**. The **Script Export Options** dialog box appears:

Figure 3 · Script Export Options

- 3. Check the Include Commands from Current Design [Project] Only checkbox. This option applies only if you opened more than one design or project in your current session. If so, and you do not check this box, Project Manager exports all commands from your current session.

- 4. Select the radio button for the appropriate filename formatting. To export filenames relative to the current working directory, select Relative filenames (default) formatting. To export filenames that include a fully specified path, select Qualified filenames (full path; including directory name) formatting.

Choose **Relative filenames** if you do not intend to move the Tcl script from the saved location, or **Qualified filenames** if you plan to move the Tcl script to another directory or machine.

5. Click OK.

Project Manager saves the Tcl script with the specified filename.

#### Note

- When exporting Tcl scripts, Project Manager always encloses filenames in curly braces to ensure portability.

- Libero SoC software does not write out any Tcl variables or flow-control statements to the exported Tcl file, even if you had executed the design commands using your own Tcl script. The exported Tcl file only contains the tool commands and their accompanying arguments.

# extended run lib

Note: This is not a Tcl command; it is a shell script that can be run from the command line.

The extended\_run\_lib Tcl script enables you to run the multiple pass layout in batch mode from a command line.

```

$ACTEL_SW_DIR/bin/libero script:$ACTEL_SW_DIR/scripts/extended_run_lib.tcl

logfile:extended_run.log "script_args:-root path/designer/module_name [-n numPasses] [-

starting_seed_index_numIndex] [-compare_criteria_value] [-c clockName] [-analysis_value] [-

slack_criteria_value] [-stop_on_success] [-timing_driven|-standard] [-power_driven_value]

[-placer_high_effort_value]"

```

#### Note:

• There is no option to save the design files from all the passes. Only the (Timing or Power) result reports from all the passes are saved.

## **Arguments**

```

-root path/designer/module name

```

The path to the root module located under the designer directory of the Libero project.

```

[-n numPasses]

```

Sets the number of passes to run. The default number of passes is 5.

```

[-starting seed index numIndex]

```

Indicates the specific index into the array of random seeds which is to be the starting point for the passes. Value may range from 1 to 100. If not specified, the default behavior is to continue from the last seed index that was used.

```

[-compare criteria value]

```

Sets the criteria for comparing results between passes. The default value is set to frequency when the –c option is given or timing constraints are absent. Otherwise, the default value is set to violations.

| Value      | Description                                                                                                                                                                                             |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| frequency  | Use clock frequency as criteria for comparing the results between passes. This option can be used in conjunction with the -c option (described below).                                                  |

| violations | Use timing violations as criteria for comparing the results between passes. This option can be used in conjunction with the -analysis, -slack_criteria and - stop_on_success options (described below). |

| power      | Use total power as criteria for comparing the results between passes, where lowest total power is the goal.                                                                                             |

```

[-c clockName]

```

Applies only when the clock frequency comparison criteria is used. Specifies the particular clock that is to be examined. If no clock is specified, then the slowest clock frequency in the design in a given pass is used. The clock name should match with one of the Clock Domains in the Summary section of the Timing report.

```

[-analysis value]

```

Applies only when the timing violations comparison criteria is used. Specifies the type of timing violations (the slack) to examine. The following table shows the acceptable values for this argument:

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| max   | Examines timing violations (slack) obtained from maximum delay analysis. This is the default. |

| Value | Description                                                              |

|-------|--------------------------------------------------------------------------|

| min   | Examines timing violations (slack) obtained from minimum delay analysis. |

[-slack criteria value]

Applies only when the timing violations comparison criteria is used. Specifies how to evaluate the timing violations (slack). The type of timing violations (slack) is determined by the -analysis option. The following table shows the acceptable values for this argument:

| Value | Description                                                                                                                                                                                                                                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| worst | Sets the timing violations criteria to Worst slack. For each pass obtains the most amount of negative slack (or least amount of positive slack if all constraints are met) from the timing violations report. The largest value out of all passes will determine the best pass. This is the default.                                               |

| tns   | Sets the timing violations criteria to Total Negative Slack (tns). For each pass it obtains the sum of negative slack values from the first 100 paths from the timing violations report. The largest value out of all passes determines the best pass. If no negative slacks exist for a pass, then the worst slack is used to evaluate that pass. |

[-stop on success]

Applies only when the timing violations comparison criteria is used. The type of timing violations (slack) is determined by the -analysis option. Stops running the remaining passes if all timing constraints have been met (when there are no negative slacks reported in the timing violations report).

[-timing driven|-standard]

Sets layout mode to timing driven or standard (non-timing driven). The default is -timing\_driven or the mode used in the previous layout command.

[-power driven *value*]

Enables or disables power-driven layout. The default is off or the mode used in the previous layout command. The following table shows the acceptable values for this argument:

| Value | Description                       |

|-------|-----------------------------------|

| off   | Does not run power-driven layout. |

| on    | Enables power-driven layout.      |

[-placer\_high\_effort value]

Sets placer effort level. The default is off or the mode used in the previous layout command. The following table shows the acceptable values for this argument:

| Value | Description                        |

|-------|------------------------------------|

| off   | Runs layout in regular effort.     |

| on    | Activates high effort layout mode. |

#### Return

A non-zero value will be returned on error.

## **Supported Families**

SmartFusion2, IGLOO2, RTG4

## **Exceptions**

None

# Sample Tcl Script - Project Manager

The following Tcl commands create a new project and set your project options.

#### SmartFusion2, IGLOO2, RTG4:

```

#Create a new project and set up a new design

new project -location {C:/sf2} -name {sf2} -project_description {} -block_mode 0 -

standalone peripheral initialization 0 \

-instantiate in smartdesign 1 -ondemand build dh 1 -hdl {VERILOG} -family {SmartFusion2}

-die {M2S010} -package {484 FBGA} -speed {STD} \

-die_voltage {1.2} -part_range {IND} -adv_options {IO_DEFT_STD:LVCMOS 2.5V} -adv options

{RESTRICTPROBEPINS:1} -adv_options {RESTRICTSPIPINS:0} \

-adv options {TEMPR:IND} -adv options {UNUSED MSS IO RESISTOR PULL:None} -adv options

{VCCI 1.2 VOLTR:COM} -adv options {VCCI 1.5 VOLTR:COM} \

-adv options {VCCI 1.8 VOLTR:COM} -adv options {VCCI 2.5 VOLTR:COM} -adv options

{VCCI 3.3 VOLTR:COM} -adv options {VOLTR:IND}

#Import the component file

import_component -file {C:/g4_ccf_119/component/work/top/top.cxf}

# generate the component

generate component -component name {top} -recursive 1

# build design hierarchy

build design hierarchy

#set the top level design name

set root -module {top::work}

#Import the pdc file

import_files -io_pdc {C:/g4_ccf_119/constraint/io/top.io.pdc}

# tun Synthesis

run tool -name {SYNTHESIZE}

# organize the constraint file

organize tool files -tool {PLACEROUTE} -file {C:/sf2/constraint/io/top.io.pdc} -module

{top::work} -input_type {constraint}

#run the Place and Route tool

run tool -name {PLACEROUTE}

# run verify timing

run tool -name {VERIFYTIMING}

#export the bitstream file

export bitstream file -file name {top} -export dir {C:\sf2\designer\top\export} -format

{STP DAT}

#save the design

save project

```

# Tcl Flow in the Libero SoC

Use the following commands to manage and build your project in the Libero SoC.

## **Design Flow in the Project Manager**

The Tcl commands below outline the entire design flow. Once you create a project in the Project Manager you can use the commands below to complete every operation from synthesis to generating an HDL netlist. Click any command to go to the command definition.

```

run_synthesis [-logfile name]

run_simulation [-logfile name]

check hdl -file filename

check_schematic -file filename

create_symbol [-module module]

export_io_constraints_from_adb -adb filename -output outputfilename

generate_ba_files -adb filename

generate_hdl_from_schematic [-module modulename]

generate_hdl_netlist [-netlist filename] [-run_drc "TRUE | FALSE"]

rollback_constraints_from_adb -adb filename -output output_filename

run_designer [-logfile filename] [-script "script to append"] [-append_commands "commands to execute"] [-adb "new | open | default"] [-compile "TRUE | FALSE"] [-layout "TRUE |

FALSE"] [-export_ba "TRUE | FALSE"]

run drc [-netlist file] [-gen hdl "TRUE | FALSE"]

```

## Manage Profiles in the Project Manager

```

add profile -name profilename -type "synthesis | simulation | stimulus | flashpro |

physynth | coreconfig" -tool profiletool -location tool_location [-args tool_parameters]

[-batch "TRUE | FALSE"]

edit profile -name profilename -type "synthesis | simulation | stimulus | flashpro |

physynth | coreconfig" -tool profiletool -location tool_location [-args tool_parameters]

[-batch "TRUE | FALSE"] [-new_name name]

export profiles -file name [-export "predefined | user | all"]

remove profile -name profile_name

select profile -name profile name

```

## **Linking Files**

```

change link source -file filename -path pathname

create links [-hdl_source file]* [-stimulus file]* [-sdc file]* [-pin file]* [-dcf file]*

[-gcf file]* [-pdc file]* [-crt file]* [-vcd file]*

export as link -file filename -path link_path

unlink -file file [-local local_filename]

```

## **Set Simulation Options in the Project Manager**

```

add modelsim path -lib library_name [-path library_path] [-remove " "]

```

## Set Device in the Project Manager

```

set device [-family family] [-die die] [-package package]

```

#### Miscellaneous Operations in the Project Manager

```

project settings [-hdl "VHDL | VERILOG"] [-auto_update_modelsim_ini "TRUE | FALSE"] [-

auto_update_viewdraw_ini "TRUE | FALSE"] [-block_mode_"TRUE | FALSE"] [-

```

```

auto_generate_synth_hdl "TRUE | FALSE"] [-auto_run_drc "TRUE | FALSE"] [-

auto_generate_viewdraw_hdl "TRUE | FALSE"] [-auto_file_detection "TRUE | FALSE"]

refresh

set option [-synth "TRUE | FALSE"] [-module "module_name"]

remove_core__name

```

# **Project Manager Tcl Commands**

# add\_file\_to\_library

Tcl command; adds a file to a library in your project.

```

add_file_to_library

-library name

-file name

```

## **Arguments**

```

-library name

```

Name of the library where you wish to add your file.

-file name

Specifies the new name of the file you wish to add (must be a full pathname).

## **Supported Families**

SmartFusion2 IGLOO2 RTG4

## **Example**

Add a file named foo.vhd from the ./project/hdl directory to the library 'my\_lib'

```

add_file_to_library -library my_lib -file ./project/hdl/foo.vhd

```

#### See Also

```

add library

remove library

rename library

```

Project Manager Tcl Command Reference

# add library

Tcl command; adds a VHDL library to your project.

```

add_library

-library name

```

## **Arguments**

```

-library name

```

Specifies the name of your new library.

# **Supported Families**

SmartFusion2 IGLOO2 RTG4

## **Example**

Create a new library called 'my\_lib'.

add library -library my lib

#### See Also

remove library

rename library

Project Manager Tcl Command Reference

# add\_profile

Tcl command; sets the same values as the Add or Edit Profile dialog box. The newly added profile becomes the active tool profile for the specified *type* of tool.

add\_profile -name profilename -type value -tool profiletool -location tool\_location [-args

tool parameters] [-batch value]

## **Arguments**

-name profilename

Specifies the name of your new profile.

-type value

Specifies your profile type, where value is one of the following:

| Value      | Description                       |

|------------|-----------------------------------|

| synthesis  | New profile for a synthesis tool  |

| simulation | New profile for a simulation tool |

| stimulus   | New profile for a stimulus tool   |

| flashpro   | New FlashPro tool profile         |

-tool profiletool

Name of the tool you are adding to the profile.

-location tool location

Full pathname to the location of the tool you are adding to the profile.

-args tool\_parameters

Profile parameters (if any).

-batch *value*

Runs the tool in batch mode (if TRUE). Possible values are:

| Value | Description                            |

|-------|----------------------------------------|

| TRUE  | Runs the profile in batch mode         |

| FALSE | Does not run the profile in batch mode |

# **Supported Families**

SmartFusion2

IGLOO2

RTG4

## **Example**

Create a new FlashPro tool profile called 'myflashpro' linked to a FlashPro installation in my c:\programs\actel\flashpro\bin directory

```

add_profile -name myflashpro -type flashpro -tool flashpro.exe -location

c:\programs\actel\flashpro\bin\flashpro.exe -batch FALSE

```

#### See Also

Project Manager Tcl Command Reference

# add\_modelsim\_path

Tcl command; adds a ModelSim simulation library to your project.

```

add modelsim path -lib library name [-path library path] [-remove " "]

```

## **Arguments**

```

-lib library_name

Name of the library you want to add.

-path library_path

Path to library that you want to add.

-remove " "

Name of library you want to remove (if any).

```

## **Supported Families**

SmartFusion2 IGLOO2 RTG4

## **Example**

Add the ModelSim library 'msim\_update2' located in the c:\modelsim\libraries directory and remove the library 'msim\_update1':

```

add_modelsim_path -lib msim_update2 [-path c:\modelsim\libraries] [-remove msim_update1]

```

#### See Also

Project Manager Tcl Command Reference

# associate stimulus

Tcl command; associates a stimulus file in your project.

```

associate_stimulus

[-file name] *

[-mode value]

-module value