# Reference Clocks for RTG4 SerDes REFCLK Inputs and Interface Circuits

Author: Lang Trinh and Jim Steward Microchip Technology Inc.

## INTRODUCTION

This Application Note describes various Vectron clock sources and interface circuits that can be used to drive the Reference Clock (REFCLK) Inputs of the SerDes Blocks of the RTG4 radiation-tolerant FPGA.

The Microchip RTG4 (Radiation-Tolerant Generation4) FPGA (Field Programmable Gate Array) can receive clock signals in two types of clock inputs:

- 1. Clock signals into the RTG4 general purpose and dedicated clock input pins, for use as a clock to the logic in the Digital Fabric.

- 2. Clock signals into the SerDes Blocks Reference Clock input pins, which input a reference clock for use by the dedicated high-speed SerDes Blocks on chip.

Of the two types of clock inputs, RTG4 REFCLK Inputs will be examined for this Application Note. The RTG4 REFCLK Inputs can be programmed by a FPGA designer to one of the various receiver types (differential or single-ended signal), and each has logic level requirements that will need direct interface or translation interface circuit connections to work properly when used with a standard clock driver (See Table 3). Information for providing clock input to the RTG4 Digital Fabric (type '1' above) is not presented here, but it can be connected with a standard driver clock the same as providing clock input to the RTG4 REFCLK receivers.

In addition to listing and discussing these devices, this Application Note also summarizes the RTG4 REFCLK Inputs specification logic levels required for the clock source drivers with output logic levels presented in Table 3. The Application Note also shows setups and measurements with some typical waveforms tested in the RTG4 DevKit, to provide confidence that the solutions do work in hardware.

## **CLOCKS FOR DRIVING RTG4 FPGA REFCLK INPUTS**

The following Vectron differential signal crystal oscillators are recommended for use with the RTG4 FPGA REFCLK receivers:

- LVDS (See Setup Figure 2 and Figure 4):

- DOC203679, Oscillator Specification, Hybrid Clock for Hi-Rel Standard, LVDS Output

- DOC206903, Oscillator Specification, Hybrid Clock for Hi-Rel Standard, 300krad Tolerant, LVDS Output

- LVPECL (See Setup Figure 7, Figure 9, and Figure 11):

- DOC203810, Oscillator Specification, Hybrid Clock for Hi-Rel Standard, LVPECL Output

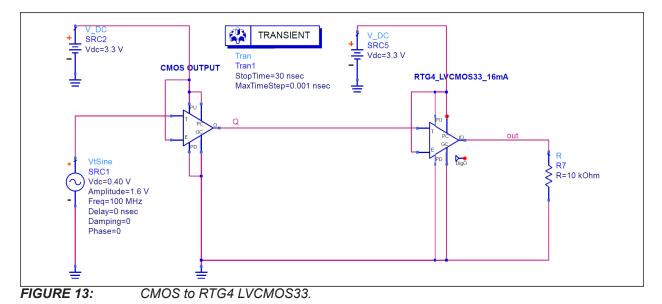

- CMOS (See Figure 13):

- OS-68338, Oscillator Specification, Hybrid Clock, Hi-Rel Standard, CMOS Output (3.3V supply, 100krad)

- DOC206379, Oscillator Specification, Hybrid Clock for Hi-Rel Standard, 300krad Tolerant CMOS (3.3V supply, 300krad)

- DOC204900, Oscillator Specification, Hybrid Clock for Hi-Rel Standard, High Frequency CMOS (2.5V/3.3V supply, 100krad)

## **RTG4 FPGA REFCLK INPUTS**

The RTG4 REFCLK Inputs can be configured, by the FPGA designer, to any one of the IO Standards listed below (Reference: Table 5 of UG0567 User Guide, RTG4 FPGA High-Speed Serial Interfaces).

| SERDES_VDDI Supply  | 3.3V           | 2.5V            | 1.8V           |

|---------------------|----------------|-----------------|----------------|

|                     | LVTTL/LVCMOS33 | LVCMOS25        | LVCMOS18       |

|                     | LVDS33         | LVDS25 (Note 1) | SSTL18-Class 1 |

| Supported Stondardo | LVPECL         | RSDS            | SSTL18-Class 2 |

| Supported Standards | RSDS           | Mini-LVDS       | HSLT18-Class 1 |

|                     | Mini-LVDS      | SSTL25-Class 1  | _              |

|                     | —              | SSTL25-Class 2  | —              |

#### TABLE 1: INPUT CONFIGURATION OPTIONS

**Note 1:** For LVDS33 and LVDS25, designers should reference RGT4 I/O Users Guide and *DS0131 RTG4 FPGA data sheet* for correct termination and common-mode recommendations to achieve optimal jitter performance.

2: HCSL inputs are supported directly with LVDS I/O STD inputs from the Libero. There is no specific HCSL I/O STD available in Libero and designs requiring HCSL are supported by using the LVDS25 I/O standard.

Programming the I/O Standard will also set the corresponding REFCLK Inputs type. The following popular REFCLK Inputs are presented in this Application Note with recommendations:

- LVDS25\_ODT: ODT improves the signaling environment by reducing the electrical discontinuities introduced with off-die termination; thus, it enables reliable operation at higher signaling rates (Microchip\_RTG4\_FPGA\_IO\_us-er\_Guide\_UG0741\_V4). This also provides the common-mode noise rejection on the transmission lines all the way to the receiver with the built-in ODT to reduce noise emission and noise interferences. An LVDS or LVPECL clock (interface circuit needed) can be used to drive the LVDS25\_ODT.

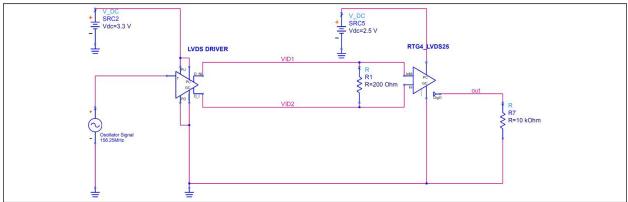

- LVDS25: It is recommended to use LVDS25\_ODT for best waveform and jitter performance. When LVDS25 is used an external differential termination is required. An external differential termination resistor of  $200\Omega$  (typical) may be implemented to improve the V<sub>ID</sub> minimum requirement margin when using with a standard LVDS driver. The  $200\Omega$  load must be placed as close as possible to the RTG4 receiver input pins for better waveform and jitter performance.

- LVDS33: This is not recommended for use due to the minimum V<sub>ID</sub> requirement of 0.50V, which is higher than a standard LVDS output differential voltage of 0.34V and is also higher than the minimum LVPECL output differential voltage of 0.470V according to Table 3.

- LVPECL33: This is not recommended for use due to the V<sub>ICM</sub> requirement of 1.8V maximum, which is lower than the standard LVPECL output common mode voltage of 2.0V, and due to the V<sub>ID</sub> requirement of 0.600V minimum, which is higher than the minimum LVPECL output differential voltage of 0.470V according to Table 3.

- LVCMOS33/LVCMOS25: This is recommended for use. These are single-ended REFCLK Inputs, requiring no

interface translating circuit for simple direct connections to reduce component count. OS-68338 3.3V clock up to

100 MHz can be used for driving LVCMOS33. The 300-krad DOC203679 3.3V clock up to 80 MHz can be used for

driving LVCMOS33. For faster speed, the high frequency 2.5V/3.3V CMOS clock of DOC204900 up to 125 MHz

can be used for driving LVCMOS25 (used with 2.5V clock) or LVCMOS33 (used with 3.3V clock). The max operating frequency of the high frequency CMOS DOC204900 is 160 MHz, but the application is limited to 125 MHz due

to the high input capacitance 20 pF max of the RTG4 receiver. This application limit is based on the output sink/

source current capability of the oscillator clocks and the capacitive load (20 pF in this case), using the power dissipation formula.

$P = C \times V_{CC}^{2} \times f = V_{CC} \times I_{C}$  $I_{C} = C \times V_{CC} \times f$

Capacitive-Load Power Consumption is calculated via the following equation.

#### **EQUATION 1:**

Where:

C = The load capacitance.

f = The signal frequency.

$I_C$  = The dynamic consumption current.

For example, at 125 MHz and 3.0V supply, the consumption current is calculated as 20 pF x 3.0V x 125 MHz = 7.5 mA, as expected to be lower than the recommended sink/source current of 12 mA (Reference: TI 54AC00-SP, output buffer used in the DOC204900 oscillator).

## **RTG4 REFCLK INPUT VOLTAGE SPECIFICATIONS AND DRIVER OUTPUT DATA**

The input voltage requirements of the RTG4 REFCLK Inputs are listed in Table 2 to provide the specification limits to the driver output data presented in Table 3.

|                      |                   |        |                          |       |                 | · /                       |        |

|----------------------|-------------------|--------|--------------------------|-------|-----------------|---------------------------|--------|

| REFCLK               | Supply            |        | V <sub>ID</sub> (Note 2) |       |                 | V <sub>ICM</sub> (Note 2) |        |

| Input                | Voltage<br>(VDDI) | Min.   | Тур.                     | Max.  | Min.            | Тур.                      | Max.   |

| LVDS25_ODT           | 2.5V ±5%          | 0.20V  | 0.35V                    | 2.40V | 0.05V           | 1.25V                     | 1.50V  |

| LVDS25               | 2.5V ±5%          | 0.20V  | 0.35V                    | 2.40V | 0.05V           | 1.25V                     | 2.20V  |

| LVDS33<br>(Note 3)   | 3.3V ±5%          | 0.50V  |                          | 2.40V | 0.60V           | 1.25V                     | 1.80V  |

| LVPECL33<br>(Note 3) | 3.3V ±5%          | 0.60V  |                          | 2.40V | 0.60V           | _                         | 1.80V  |

|                      |                   |        | V <sub>IL</sub>          |       | V <sub>IH</sub> |                           |        |

| LVCMOS25             | 2.5V ±5%          | -0.30V |                          | 0.70V | 1.7V            |                           | 2.625V |

| LVCMOS33             | 3.3V ±5%          | -0.30V | —                        | 0.80V | 2.0V            | —                         | 3.450V |

TABLE 2: RTG4 SERDES REFCLK INPUT VOLTAGE SPECIFICATIONS (Note 1)

Note 1: See Microchip RTG4\_FPGA data sheet for more details on SerDes REFCLK Input Voltage Specifications.

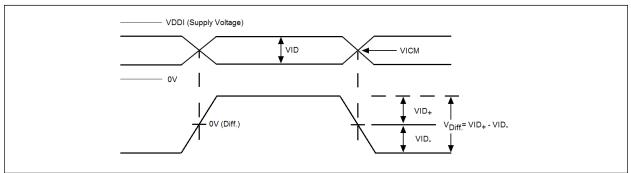

2: Figure 1 depicts the V<sub>ID</sub> and V<sub>ICM</sub> for the differential inputs. Note that V<sub>ID</sub> is half of V<sub>Diff</sub>, and is equivalent to a single-ended signal referenced from one input to ground.

**3:** Do not use LVDS33 and LVPECL33 as explained in the RTG4 FPGA REFCLK INPUTS section for LVDS33 and LVPECL33. These specification limits compared with the output data ranges in Table 3 are used to support this conclusion.

FIGURE 1: V<sub>ID</sub> and V<sub>ICM</sub> for Differential Inputs.

Also, the  $V_{ICM}$  and  $V_{ID}$  have to meet the conditions of the formulas below:

#### EQUATION 2:

$$V_{ICM} + (V_{ID}/2) < VDDI + 0.4V$$

and

$$V_{ICM} - (V_{ID}/2) > -0.3 V$$

| Setup                 | Interface Configuration                             | ,      | V <sub>ID</sub> (Note 2 | )      | V <sub>ICM</sub> (Note 2) |                 |        |  |

|-----------------------|-----------------------------------------------------|--------|-------------------------|--------|---------------------------|-----------------|--------|--|

| Figure                |                                                     | Min.   | Тур.                    | Max.   | Min.                      | Тур.            | Max.   |  |

| Figure 2<br>(Note 3)  | LVDS to LVDS25_ODT<br>Direct Interface              | 0.250V | 0.340V                  | 0.450V | 1.125V                    | 1.250V          | 1.450V |  |

| Figure 4<br>(Note 4)  | LVDS to LVDS25<br>200Ω Termination                  | 0.520V | 0.610V                  | 0.720V | 1.125V                    | 1.350V          | 1.500V |  |

| Figure 7<br>(Note 5)  | LVPECL to LVDS25_ODT<br>V <sub>ICM</sub> 3.3V-Bias  | 0.470V | 0.800V                  | 0.950V | Note 5                    | 1.240V          | Note 5 |  |

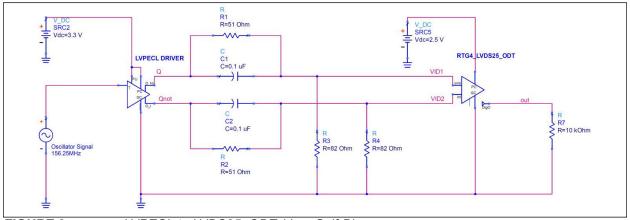

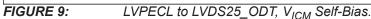

| Figure 9<br>(Note 6)  | LVPECL to LVDS25_ODT<br>V <sub>ICM</sub> Self-Bias  | 0.470V | 0.800V                  | 0.950V | 1.030V                    | 1.233V          | 1.437V |  |

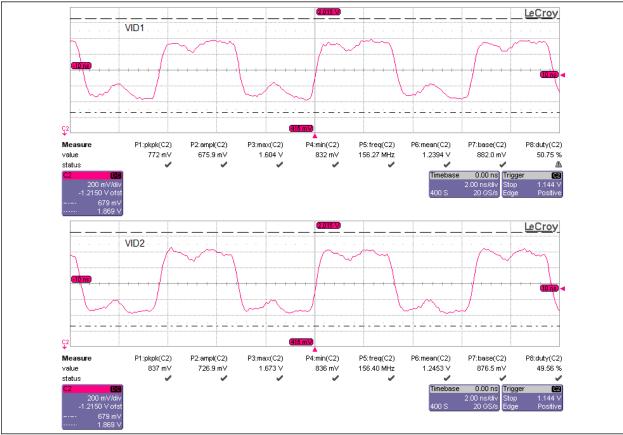

| Figure 11<br>(Note 7) | LVPECL to LVDS25_ODT<br>V <sub>ICM</sub> Self-Bias2 | 0.289V | 0.493V                  | 0.586V | 1.030V                    | 1.233V          | 1.437V |  |

|                       | —                                                   |        | VIL                     |        |                           | V <sub>IH</sub> |        |  |

| Figure 13<br>(Note 8) | CMOS to LVCMOS33                                    | 0.297V | 0.330V                  | 0.363V | 2.673V                    | 2.970V          | 3.267V |  |

| (Note 8)              | CMOS to LVCMOS25                                    | 0.237V | 0.250V                  | 0.263V | 2.138V                    | 2.250V          | 2.363V |  |

### TABLE 3: CLOCK DRIVER INTERFACE CONFIGURATION AND OUTPUT DATA (Note 1)

**Note 1:** Output Data is recorded as V<sub>ID</sub> and V<sub>ICM</sub> to be consistent with the RTG4 REFCLK Inputs Voltage references. See the Setup Figures and resulted waveforms for details on the clock source use and interface circuits. Also see the Jitter Measurements section for additional information.

- 2:  $V_{ID}$  and  $V_{ICM}$  are referenced to Ground.  $V_{ID}$  is a single-ended signal measured at the input of the RTG4 receiver to correspond with the specification  $V_{ID}$  of the RTG4 REFCLK Inputs (see Note 2 of Table 2). All the logic levels also meet the conditions of the formulas required for the RTG4 REFCLK Inputs:  $V_{ICM} + (V_{ID}/2) < VDDI + 0.4V$  and  $V_{ICM} (V_{ID}/2) > -0.3V$ .

- **3:** Setup Figure 2: The V<sub>ID</sub> and V<sub>ICM</sub> limits are defined by the output voltage levels from Table 2 of Vectron DOC203679 for standard LVDS.

- 4: Setup Figure 4: The typical values of V<sub>ID</sub> and V<sub>ICM</sub> are determined by measurements.

- 5: Setup Figure 7: The V<sub>ID</sub> range is determined using the output voltage levels from Table 2 of Vectron DOC203810, "Output Voltage:  $V_{OH} = V_{CC} 1.085$  to  $V_{CC} 0.880$ ,  $V_{OL} = V_{CC} 1.830$  to  $V_{CC} 1.555$ ". The biasing network resistors (R3 to R6) and its supply voltage will determine the V<sub>ICM</sub> range for this scheme.

- 6: Setup Figure 9: The V<sub>ID</sub> range is determined using the output voltage levels from Table 2 of Vectron DOC203810, "Output Voltage:  $V_{OH} = V_{CC} 1.085$  to  $V_{CC} 0.880$ ,  $V_{OL} = V_{CC} 1.830$  to  $V_{CC} 1.555$ ". The LVPECL output common mode voltage is calculated as  $V_{CC} 1.3V$ . With a  $V_{CC}$  of 3.3V ±10%, the  $V_{ICM}$  ranges from 1.030V to 1.437V for this interface scheme with the resistor nominal values.

- 7: Setup Figure 11: The V<sub>ID</sub> range is determined using the output voltage levels from Table 2 of Vectron DOC203810, "Output Voltage:  $V_{OH} = V_{CC} 1.085$  to  $V_{CC} 0.880$ ,  $V_{OL} = V_{CC} 1.830$  to  $V_{CC} 1.555$ ", and through the voltage divider, the 51 $\Omega$  and 82 $\Omega$  resistor network. The LVPECL output common mode voltage is calculated as  $V_{CC} 1.3V$ . With a  $V_{CC}$  of 3.3V ±10%, the  $V_{ICM}$  ranges from 1.030V to 1.437V for this interface scheme with the resistor nominal values.

- 8: Setup Figure 13: The V<sub>IL</sub> and V<sub>IH</sub> range is determined by the standard CMOS logic levels as V<sub>IL</sub> = V<sub>CC</sub> x 0.1 and V<sub>IH</sub> = V<sub>CC</sub> x 0.9, where V<sub>CC</sub> is the supply voltage 3.3V ±10% or 2.5V ±5%.

### **General Recommendations and Summary**

- 1. When an external resistor like the 200Ω termination for differential driving is used, it must be placed as close as possible to the differential receiver input pins. Otherwise, waveform and jitter will greatly degrade.

- 2. RTG4 differential receiver must be terminated at the inputs either with an external resistor (100Ω or 200Ω) or with ODT (RTG4 On-Die Termination) for all clock driver types for best waveform and jitter performance.

- 3. The clock oscillator driver should be placed as close as possible to the input pins of the RTG4 receiver to help reduce interferences and minimize reflection on the transmission line due to possible impedance mismatching.

- 4. It is recommended to use the drivers and interface circuits listed in Table 3. Do not use the RTG4 REFCLK Inputs LVDS33 and LVPECL33.

|                  | RTG4         |               |                 | Vectron 0              | Clock Drive       | r                 |                                     |

|------------------|--------------|---------------|-----------------|------------------------|-------------------|-------------------|-------------------------------------|

| Signal Type      | REFCLK Input | Clock<br>Type | Spec<br>Drawing | Radiation<br>Tolerance | Supply<br>Voltage | Max.<br>Frequency | Termination<br>Circuit              |

|                  | LVDS25_ODT   | LVDS          | DOC203679       | 100 krad               | 3.3V              | 200 MHz           | Direct Interface                    |

|                  | LVD325_0D1   | LVDS          | DOC206903       | 300 krad               | 3.3V              | 200 MHz           | Figure 2                            |

| Differential     | LVDS25_ODT   | LVPECL        | DOC203810       | 50 krad<br>(ELDRS)     | 3.3V              | 700 MHz           | Figure 7,<br>Figure 9,<br>Figure 11 |

|                  | LVDS25       | LVDS          | DOC203679       | 100 krad               | 3.3V              | 200 MHz           | 200Ω, Figure 4                      |

|                  | LVDS25       |               | DOC206903       | 300 krad               | 3.3V              | 200 MHz           | 20032, Figure 4                     |

|                  | LVDS33       | Do Not Use    |                 |                        |                   |                   |                                     |

|                  | LVPECL33     |               |                 | Do N                   | lot Use           |                   |                                     |

|                  |              |               | OS-68338        | 100 krad               | 3.3V              | 100 MHz           |                                     |

| Single           | LVCMOS33     | CMOS          | DOC204900       | 100 krad               | 3.3V              | 125 MHz           | Direct Interface<br>Figure 13       |

| Single-<br>Ended |              |               | DOC206379       | 300 krad               | 3.3V              | 80 MHz            | i iguic i o                         |

|                  | LVCMOS25     | CMOS          | DOC204900       | 100 krad               | 2.5V              | 125 MHz           | Direct Interface<br>Figure 13       |

TABLE 4:

RTG4 REFCLK INPUTS AND CLOCK DRIVER MATRIX

For differential signal application, the only choice for RTG4 to set to is LVDS25\_ODT (used with LVDS or LVPECL clock driver) or LVDS25 (used with LVDS clock driver and external  $200\Omega$  termination). The CMOS single-ended signal solution offers the best Total Jitter and Deterministic Jitter performance (See Jitter Measurements Table 5, Table 6, and Table 7), simple direct interface and options to use either the 2.5V or 3.3V supply, but speed is limited to 100 MHz (OS-68338), 80 MHz (DOC206379) and 125 MHz (DOC204900) for the three Vectron CMOS clocks.

## **CIRCUIT INTERFACE AND DATA**

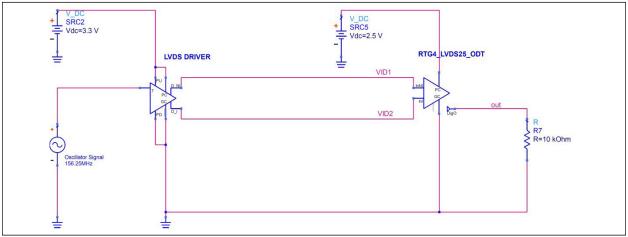

FIGURE 2:

LVDS to RTG4 LVDS25\_ODT, Direct Interface.

**FIGURE 3:** Measured Waveforms, LVDS to LVDS25\_ODT, Direct Interface (Waveforms Measured on RTG4 DevKit).

- **Note 1:** A LeCroy active probe ZS1500 1.5 GHz was used for the measurements. VID1 and VID2 were measured with reference to Ground at room temperature.

- 2: See Figure 2 for the setup diagram. The oscillator clock driver (1204R156M25000BF used) was mounted on the RTG4 DevKit in place of the REFCLK 125 MHz (disabled and isolated) and the whole board was tested over temperature from -40°C to +85°C with Microchip EPCS Demo GUI software used to check for the error-free transmission loop.

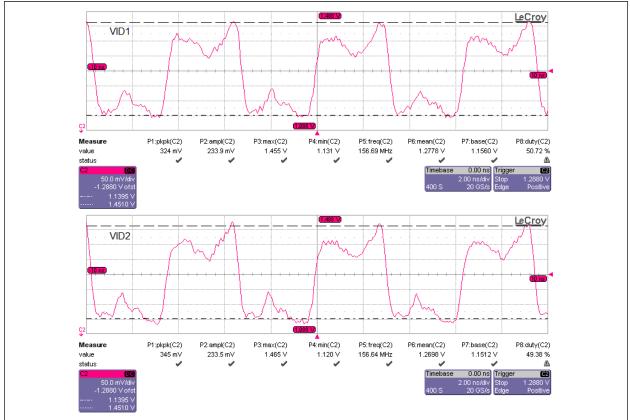

FIGURE 4: LVDS to RTG4 LVDS25 External 200Ω Termination.

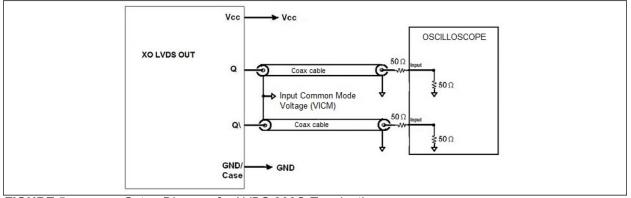

FIGURE 5: Setup Diagram for LVDS 200Ω Termination.

- **Note 1:** This test setup was used to measure the waveforms for the diagram Figure 4 to present here in place of the waveforms measured on the RTG4 DevKit. The waveforms measured on the DevKit using the setup of Figure 4 were not so representative because the 200Ω load resistor used with the RTG4 LVDS25 couldn't be placed as close to the receiver inputs as recommended to obtain good waveforms.

- 2: The load was placed at the input of the oscilloscope for better waveform measurements. Only half of the signal was measured using this setup. The  $50\Omega$  series resistors connected via the oscilloscope ground form a load of  $200\Omega$  between two outputs of the LVDS oscillator. The clock source used was 1204R156M25000BF.

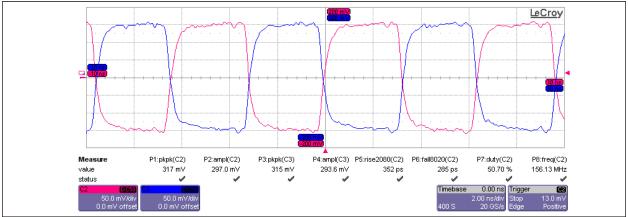

**FIGURE 6:** Measured Waveforms, LVDS to LVDS25, External 200 $\Omega$  Termination (Waveforms Measured with Bench Fixture and 50 $\Omega$  Coax Cables).

**Note 1:** The actual signal is two times the measured value, as explained in Figure 5. Waveform was measured at room temperature.

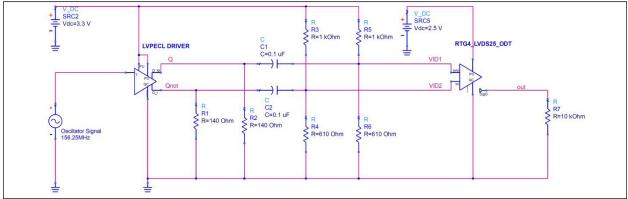

FIGURE 7: LVPECL to LVDS25\_ODT, V<sub>ICM</sub> 3.3V-Bias.

- **Note 1:** Use 1 k $\Omega$  for R4 and R6 if a supply voltage of 2.5V is used for the biasing network.

- 2: C1 and C2 of 0.1 µF not only serve as a DC block, but also provide a full LVPECL differential signal swing to drive the receiver with little attenuation. The AC-coupling capacitors should have low ESR and low inductance at targeted clock frequency.

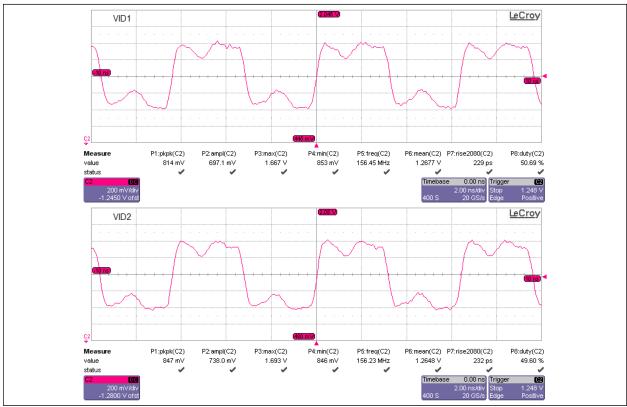

**FIGURE 8:** Measured Waveforms, LVPECL to LVDS25\_ODT, V<sub>ICM</sub> 3.3V-Bias (Waveforms Measured on RTG4 DevKit).

- **Note 1:** A LeCroy active probe ZS1500 1.5 GHz was used for the measurements. VID1 and VID2 were measured with reference to Ground at room temperature.

- 2: See Figure 7 for the setup diagram. The oscillator clock driver (1304R156M25000BF used) was mounted on the RTG4 DevKit in place of the REFCLK 125 MHz (disabled and isolated) for testing.

- **Note 1:** This V<sub>ICM</sub> Self-Bias Termination is an alternative to that of Figure 7. This scheme requires no external supply voltage for the biasing and saves two resistors over that of Figure 7.

- **2:** C1 and C2 of 0.1 µF provide a full LVPECL differential signal swing to drive the receiver with little attenuation. The AC-coupling capacitors should have low ESR and low inductance at targeted clock frequency.

**FIGURE 10:** Measured Waveforms, LVPECL to LVDS25\_ODT, V<sub>ICM</sub> Self-Bias (Waveforms Measured on RTG4 DevKit).

- **Note 1:** A LeCroy active probe ZS1500 1.5 GHz was used for the measurements. VID1 and VID2 were measured with reference to Ground at room temperature.

- 2: See Figure 9 for the setup diagram. The oscillator clock driver (1304R156M25000BF used) was mounted on the RTG4 DevKit in place of the REFCLK 125 MHz (disabled and isolated) for testing.

FIGURE 11: LVPECL to LVDS\_ODT, V<sub>ICM</sub> Self-Bias2.

**Note 1:** This V<sub>ICM</sub> Self-Bias termination is similar to the setup of Figure 9 without the coupling capacitors C1 and C2. The driver output signal is divided down by the resistor network but is still large enough to drive the RTG4 LVDS25\_ODT. The rad-hard oscillator 1304R156M25000BF can be used for the clock source.

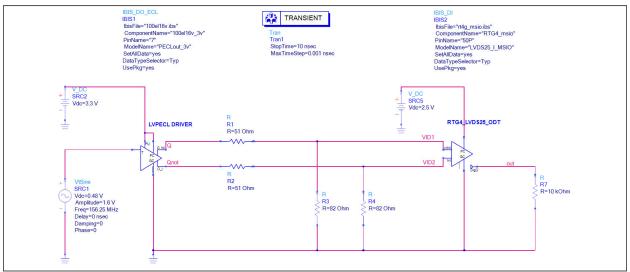

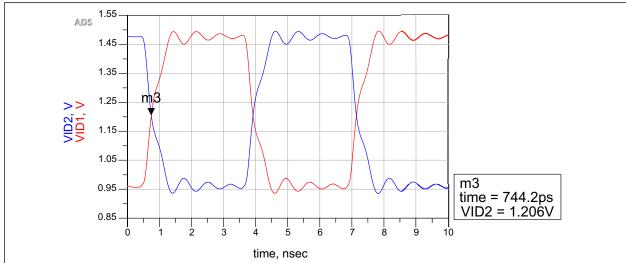

**FIGURE 12:** Simulated Waveforms, LVPECL to LVDS25\_ODT, V<sub>ICM</sub> Self-Bias2 (Keysight ADS 2017 software used).

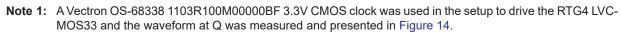

Measured Waveforms, CMOS CLOCK (OS-68338 100 MHz) to LVCMOS33.

- **Note 1:** A LeCroy active probe ZS1500 1.5 GHz was used for the measurement. The waveform was measured at the output of the clock driver at room temperature.

- 2: See Figure 13 for the setup diagram. The oscillator clock driver (1103R100M00000BF used) was mounted on the RTG4 DevKit in place of the REFCLK 125 MHz (disabled and isolated) for testing.

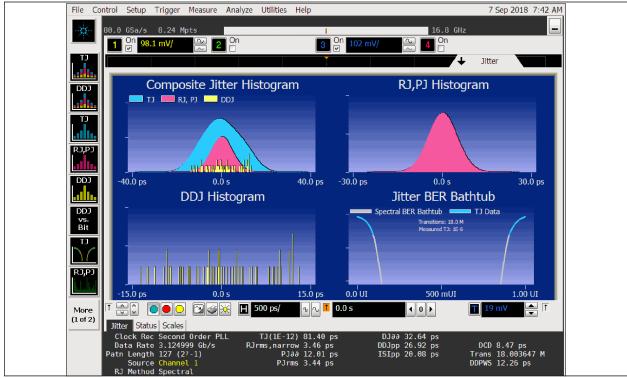

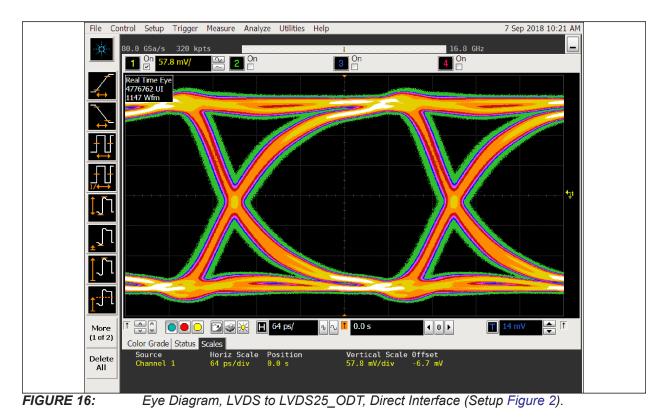

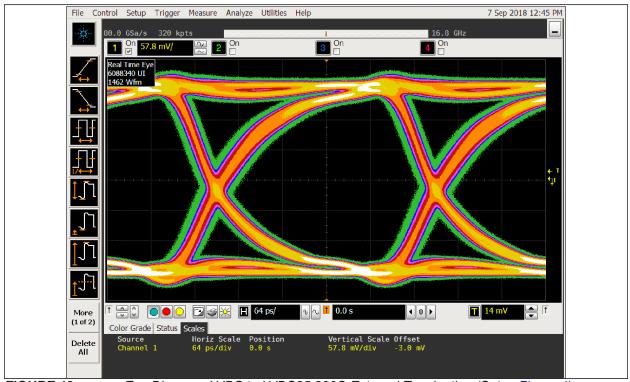

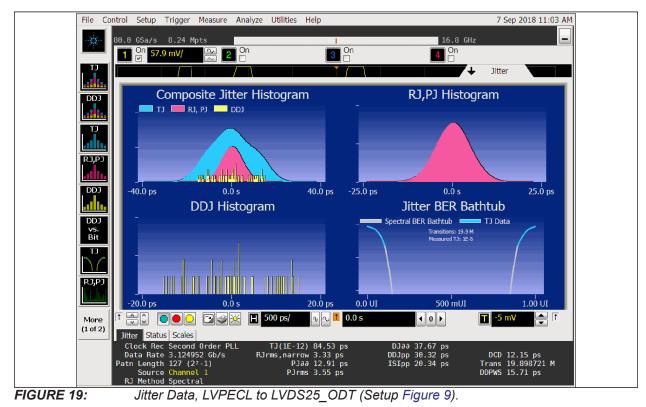

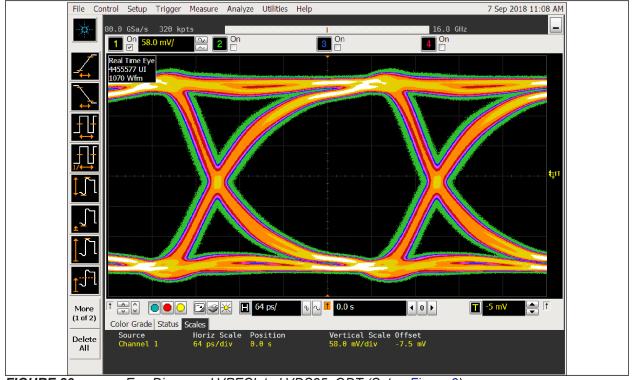

## JITTER MEASUREMENTS

Within each transmitter of the SerDes, the time base provided by the reference clock to the TXPLL directly affects the quality of the SerDes serial output data. The jitter and phase variations present on the reference clock the TXPLL receives will also appear on the high-speed serial data stream it produces. The following data represents the jitter content of the high-speed serial data from the SerDes using the various reference clock schemes. The data below shows the quality of a 3.125 Gbps PRBS7 data stream transmitted with the discussed reference clock solutions.

FIGURE 15:

Jitter Data, LVDS to LVDS25\_ODT, Direct Interface (Setup Figure 2).

File Control Setup Trigger Measure Analyze Utilities Help 7 Sep 2018 12:15 PM 16.8 GHz 80.0 GSa/s 8.24 Mpts 3 On 🚬 2 On 4 On 1 On 89.4 mV/ Jitter Ŧ RJ,PJ Histogram Composite Jitter Histogram DDJ 🛛 TJ 💻 RJ, PJ 🔛 DDJ עריו עוויוע ווייען 0.0 s -50.0 ps 0.0 s -30.0 ps DDJ 50.0 ps 30.0 ps **DDJ Histogram** Jitter BER Bathtub DDJ ectral BER Bathtub 🛛 💳 TJ Data Transitions: 14.1 M Measured TJ: 1E-6 vs. Bit TŤ. RJ,P. 0.0 UI 500 mUI 1.00 UI -20.0 ps 20.0 ps 0.0 s າມ 🕠 🚹 0.0 s H 64 ps/ T -5 mV **e** T ◀ 0 ▶ More (1 of 2) Jitter Color Grade Status Scales Clock Rec Second Order PLL Data Rate 3.124948 Gb/s Path Length 127 (27-1) Source Channel 1 RJ Method Spectral TJ(1E-12) 93.45 ps RJrms,narrow 3.48 ps PJ∂∂ 14.20 ps PJrms 3.58 ps DJ∂∂ 44.51 ps DDJpp 36.67 ps ISIpp 19.39 ps DCD 18.48 ps Trans 14.055446 M DDPWS 17.16 ps

FIGURE 17:

Jitter Data, LVDS to LVDS25 200Ω External Termination (Setup Figure 4).

# AN3216

FIGURE 18:

Eye Diagram, LVDS to LVDS25 200 $\Omega$  External Termination (Setup Figure 4).

DS00003216A-page 14

FIGURE 20: Eye Diagram, LVPECL to LVDS25\_ODT (Setup Figure 9).

The following tables present the study done by the Microsemi characterization team, comparing SerDes transmit jitter to different RefClk types.

| TABLE 5: | JITTER DATA, RTG4 SERDES OUTPUT AT 3.125 GBPS FOR ALL REFCLK |

|----------|--------------------------------------------------------------|

|          | STANDARDS                                                    |

| Device<br>Number | Temp. | Voltage<br>Condition | Parameter                  | LVDS<br>2.5V | LVCMOS<br>2.5V | LVCMOS<br>3.3V | SSTL<br>1.8V | SSTL<br>2.5V | HSTL<br>1.8V |

|------------------|-------|----------------------|----------------------------|--------------|----------------|----------------|--------------|--------------|--------------|

|                  | 125°C | Min.                 | Total Jitter (mUI)         | 318          | 309            | 306            | 481          | 371          | 445          |

|                  | 125 C | IVIITI.              | Deterministic Jitter (mUI) | 257          | 266            | 265            | 438          | 328          | 403          |

| 902              | 25°C  | Turn                 | Total Jitter (mUI)         | 343          | 289            | 287            | 355          | 406          | 358          |

| 902              | 25 0  | Тур.                 | Deterministic Jitter (mUI) | 291          | 246            | 247            | 315          | 366          | 318          |

|                  | –55°C | Max                  | Total Jitter (mUI)         | 257          | 263            | 273            | 340          | 458          | 316          |

|                  | -55 C | Max.                 | Deterministic Jitter (mUI) | 221          | 222            | 232            | 304          | 414          | 275          |

|                  | 405%0 | 5°C Min.             | Total Jitter (mUI)         | 309          | 304            | 301            | 429          | 362          | 453          |

|                  | 125 C |                      | Deterministic Jitter (mUI) | 250          | 263            | 259            | 386          | 317          | 409          |

| 905              | 25°C  | Ture                 | Total Jitter (mUI)         | 325          | 287            | 286            | 371          | 458          | 364          |

| 905              | 25 0  | Тур.                 | Deterministic Jitter (mUI) | 275          | 251            | 246            | 334          | 422          | 326          |

|                  | EE°O  | Max                  | Total Jitter (mUI)         | 336          | 265            | 277            | 307          | 423          | 320          |

|                  | –55°C | Max.                 | Deterministic Jitter (mUI) | 297          | 226            | 237            | 270          | 381          | 278          |

|                  | 405%0 | N.Alia               | Total Jitter (mUI)         | 350          | 320            | 294            | 402          | 435          | 435          |

|                  | 125°C | Min.                 | Deterministic Jitter (mUI) | 286          | 276            | 250            | 357          | 391          | 390          |

| 011              | 25°C  | Ture                 | Total Jitter (mUI)         | 332          | 303            | 301            | 427          | 451          | 333          |

| 911              | 25 0  | Тур.                 | Deterministic Jitter (mUI) | 273          | 257            | 253            | 384          | 407          | 291          |

|                  | EE°O  | Max                  | Total Jitter (mUI)         | 320          | 277            | 264            | 312          | 385          | 331          |

|                  | –55°C | Max.                 | Deterministic Jitter (mUI) | 278          | 239            | 223            | 271          | 342          | 293          |

| Device<br>Number | Temp. | Voltage<br>Condition | Parameter                  | LVDS<br>2.5V | LVCMOS<br>2.5V | LVCMOS<br>3.3V | SSTL<br>1.8V | SSTL<br>2.5V                                                                                                                           | HSTL<br>1.8V |

|------------------|-------|----------------------|----------------------------|--------------|----------------|----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------|

|                  | 125°C | Min.                 | Total Jitter (mUI)         | 202          | 164            | 168            | 188          | 188                                                                                                                                    | 224          |

|                  | 125 C | IVIII.               | Deterministic Jitter (mUI) | 164          | 135            | 129            | 157          | 159                                                                                                                                    | 216          |

| 000              | 2500  |                      | Total Jitter (mUI)         | 200          | 143            | 146            | 181          | 214                                                                                                                                    | 241          |

| 902              | 25°C  | Тур.                 | Deterministic Jitter (mUI) | 170          | 117            | 120            | 151          | 185                                                                                                                                    | 213          |

|                  | –55°C | Max                  | Total Jitter (mUI)         | 169          | 161            | 148            | 186          | 186                                                                                                                                    | 231          |

|                  | -55 C | Max.                 | Deterministic Jitter (mUI) | 136          | 135            | 122            | 159          | 159                                                                                                                                    | 168          |

| 125°             | 105%0 | Min                  | Total Jitter (mUI)         | 174          | 165            | 167            | 187          | 194                                                                                                                                    | 217          |

|                  | 125 C | Min.                 | Deterministic Jitter (mUI) | 146          | 131            | 136            | 153          | 166                                                                                                                                    | 190          |

| 005              | 2500  | _                    | Total Jitter (mUI)         | 189          | 144            | 147            | 173          | 190                                                                                                                                    | 242          |

| 905              | 25°C  | Тур.                 | Deterministic Jitter (mUI) | 163          | 118            | 118            | 147          | 161                                                                                                                                    | 196          |

|                  | –55°C | Max                  | Total Jitter (mUI)         | 157          | 152            | 146            | 190          | 187                                                                                                                                    | 229          |

|                  | -55 C | Max.                 | Deterministic Jitter (mUI) | 130          | 127            | 120            | 161          | 158                                                                                                                                    | 156          |

|                  | 105%0 | Min                  | Total Jitter (mUI)         | 193          | 185            | 184            | 200          | 223                                                                                                                                    | 252          |

|                  | 125°C | Min.                 | Deterministic Jitter (mUI) | 166          | 151            | 147            | 169          | 177                                                                                                                                    | 190          |

| 011              | 05%0  | <b>T</b>             | Total Jitter (mUI)         | 182          | 163            | 175            | 197          | 2.5V       188       159       214       185       186       159       194       166       190       161       187       158       223 | 215          |

| 911              | 25°C  | Тур.                 | Deterministic Jitter (mUI) | 151          | 131            | 143            | 164          | 163                                                                                                                                    | 159          |

|                  | EE°O  | Max                  | Total Jitter (mUI)         | 159          | 145            | 150            | 208          | 199                                                                                                                                    | 182          |

|                  | –55°C | Max.                 | Deterministic Jitter (mUI) | 134          | 119            | 118            | 166          | 169                                                                                                                                    | 155          |

#### TABLE 6: JITTER DATA, RTG4 SERDES OUTPUT AT 2.5 GBPS FOR ALL REFCLK

# TABLE 7:JITTER DATA, RTG4 SERDES OUTPUT AT 1.25 GBPS FOR ALL REFCLK<br/>STANDARDS

| Device<br>Number | Temp. | Voltage<br>Condition | Parameter                  | LVDS<br>2.5V | LVCMOS<br>2.5V | LVCMOS<br>3.3V | SSTL<br>1.8V | SSTL<br>2.5V | HSTL<br>1.8V |

|------------------|-------|----------------------|----------------------------|--------------|----------------|----------------|--------------|--------------|--------------|

|                  | 125°C | Min.                 | Total Jitter (mUI)         | 92           | 106            | 99             | 134          | 95           | 114          |

|                  | 125 C | IVIIII.              | Deterministic Jitter (mUI) | 73           | 85             | 80             | 114          | 66           | 91           |

| 000              | 25%0  | Ture                 | Total Jitter (mUI)         | 100          | 99             | 99             | 88           | 99           | 108          |

| 902              | 25°C  | Тур.                 | Deterministic Jitter (mUI) | 16           | 77             | 76             | 68           | 76           | 79           |

|                  | 55%0  | Maria                | Total Jitter (mUI)         | 97           | 93             | 94             | 114          | 91           | 106          |

|                  | –55°C | Max.                 | Deterministic Jitter (mUI) | 78           | 73             | 72             | 90           | 65           | 84           |

|                  | 125°C | Min.                 | Total Jitter (mUI)         | 100          | 100            | 106            | 97           | 122          | 130          |

|                  | 125 C |                      | Deterministic Jitter (mUI) | 76           | 74             | 87             | 69           | 90           | 101          |

| 905              | 05%0  | Trans                | Total Jitter (mUI)         | 90           | 97             | 104            | 103          | 103          | 99           |

| 905              | 25°C  | Тур.                 | Deterministic Jitter (mUI) | 66           | 70             | 83             | 79           | 80           | 77           |

|                  | 55%0  | Maria                | Total Jitter (mUI)         | 98           | 87             | 91             | 115          | 98           | 100          |

|                  | –55°C | Max.                 | Deterministic Jitter (mUI) | 79           | 67             | 70             | 93           | 71           | 74           |

|                  | 405%0 | Min                  | Total Jitter (mUI)         | 82           | 108            | 117            | 137          | 730          | 155          |

|                  | 125°C | Min.                 | Deterministic Jitter (mUI) | 65           | 79             | 97             | 105          | 101          | 107          |

| -                | 05%0  | <b>T</b>             | Total Jitter (mUI)         | 115          | 115            | 776            | 108          | 110          | 146          |

| 911              | 25°C  | Тур.                 | Deterministic Jitter (mUI) | 90           | 83             | 85             | 72           | 82           | 116          |

|                  | 55%0  | Maria                | Total Jitter (mUI)         | 99           | 96             | 104            | 111          | 117          | 91           |

|                  | –55°C | Max.                 | Deterministic Jitter (mUI) | 75           | 78             | 81             | 78           | 90           | 62           |

### Hardware and Software Tools Used

The RTG4 Development Kit was used for testing the reference clocks and for waveform measurements. The RTG4 Development Kits on-board REFCLK CCLD-033-50-125.000 oscillator was disabled, isolated, and replaced with the Vectron clock driver LVPECL or LVDS along with the interface circuit for each testing of the clock types. Also, in-house test fixtures were developed for the specific tests of LVDS with a  $200\Omega$  load.

Microchip Software Libero SoC V11.9 was used to program the RTG4 Development Kits, loading project designs and setting the SerDes REFCLK Input receiver type for testing with the corresponding clock. Microchip EPCS Demo GUI was used to check the signal quality by testing the error-free data loop between the RTG4 transmitter and receiver of the SerDes block, and also to verify the clock circuit connections in the RTG4 development board.

Keysight ADS 2017 was used to generate circuit diagrams and for simulations when needed; IBIS models used in the simulations were Microsemi RTG4 REFCLK Receiver rt4g\_msio.ibs, Micrel Semiconductor ibisTop\_100el16 in sc07p07el0160a, Aeroflex/Cobham ut54lvds031lvucc.ibs, and Fairchild ACT3301 cgs3311m 3\_3V.ibs.

## **REFERENCES, RELATED WEBSITES, AND DATA SHEETS**

- Microchip Hi-Rel Clock Oscillators (XO): https://www.vectron.com/products/space/space.htm

- Microchip RTG4 Radiation-Tolerant FPGAs: https://www.microsemi.com/product-directory/rad-tolerant-fpgas/ 3576-rtg4#documents

- Microchip DS0131 Data Sheet RTG4 FPGA: https://www.microsemi.com/document-portal/doc\_view/135193ds0131-rtg4-fpga-datasheet

- Microchip RTG4 Development Kits: https://www.microsemi.com/product-directory/dev-kits-solutions/3865-rtg4-kits

- Microchip DG0624 Demo Guide RTG4 FPGA SerDes EPCS Protocol Design: https://www.microsemi.com/document-portal/doc\_download/135196-dg0624-rtg4-fpga-serdes-epcs-protocol-design-libero-soc-v11-9-sp1-demoguide

- Microchip UG0567, RTG4 FPGA High Speed Serial Interfaces User Guide: https://www.microsemi.com/document-portal/doc\_download/134409-ug0567-rtg4-fpga-high-speed-serial-interfaces-user-guide

- Microchip SY100EL16V: https://www.microchip.com/wwwproducts/en/SY100EL16V

- Cobham HiRel Microelectronics, UT54LVDS031LV/E Quad Driver: https://www.cobhamaes.com/pagesproduct/ prods-hirel-lvds.cfm

- Keysight Technologies, Advanced Design Systems (ADS): https://www.keysight.com/en/pc-1297113/advanceddesign-system-ads?cc=US&lc=eng

- TI SN54AC00-SP Radiation Hardened Quad 2 Input NAND Gate: http://www.ti.com/lit/ds/symlink/sn54ac00sp.pdf

# AN3216

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2019, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-5009-2

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000 China - Chengdu

Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138 China - Zhuhai

Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631 India - Pune

Tel: 91-20-4121-0141 Japan - Osaka

Tel: 81-6-6152-7160 Japan - Tokyo

Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301 Korea - Seoul

Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Singapore Tel: 65-6334-8870

Taiwan - Hsin Chu Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

Taiwan - Taipei Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

**EUROPE**

Austria - Wels

Tel: 43-7242-2244-39

Tel: 45-4450-2828

Fax: 45-4485-2829

Tel: 358-9-4520-820

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching

Tel: 49-2129-3766400

Germany - Heilbronn

Germany - Karlsruhe

Tel: 49-7131-72400

Tel: 49-721-625370

Germany - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Germany - Rosenheim

Tel: 49-8031-354-560

Israel - Ra'anana

Italy - Milan

Italy - Padova

Tel: 972-9-744-7705

Tel: 39-0331-742611

Fax: 39-0331-466781

Tel: 39-049-7625286

Tel: 49-8931-9700

Germany - Haan

Finland - Espoo

France - Paris

Fax: 43-7242-2244-393

Denmark - Copenhagen

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820