## UG0638 User Guide SmartFusion2, IGLOO2, RTG4 SmartDebug Software v12.2

NOTE: PDF files are intended to be viewed on the printed page; links and cross-references in this PDF file may point to external files and generate an error when clicked. View the online help included with software to enable all linked content.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email:

sales.support@microsemi.com www.microsemi.com

©2019 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Powerover-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

5-02-00638-5/08.19

## **Table of Contents**

| Table of Contents                                                            | 2     |

|------------------------------------------------------------------------------|-------|

| Welcome to SmartDebug                                                        | 4     |

| Introduction to SmartDebug                                                   |       |

| Use Models                                                                   |       |

| Supported Families, Programmers, and Operating Systems                       |       |

| Supported Tools                                                              |       |

|                                                                              |       |

| Getting Started with SmartDebug                                              | 6     |

| Using SmartDebug                                                             | 6     |

| Running SmartDebug in Demo Mode                                              | 6     |

| Create Standalone SmartDebug Project                                         | 7     |

| Import from DDC File (created from Libero)                                   |       |

| SmartDebug User Interface                                                    | 9     |

| Programming Connectivity and Interface                                       | 11    |

| Selecting Devices for Debug                                                  | 14    |

| View Device Status                                                           | 14    |

| Embedded Flash Memory (NVM) Content Dialog Box (SmartFusion2 and IGLOO2 Only | /) 16 |

|                                                                              |       |

| Debugging                                                                    |       |

| Debug FPGA Array                                                             |       |

| Hierarchical View                                                            |       |

| Netlist View                                                                 |       |

| Live Probes                                                                  |       |

| Active Probes                                                                |       |

| Probe Grouping (Active Probes Only)                                          |       |

| Memory Blocks                                                                |       |

| Probe Insertion (Post-Layout)                                                |       |

| Event Counter                                                                |       |

| Frequency Monitor                                                            |       |

| FPGA Hardware Breakpoint Auto Instantiation                                  |       |

| User Clock Frequencies                                                       |       |

| Pseudo Static Signal Polling                                                 |       |

| Debug SERDES (SmartFusion2, IGLOO2, and RTG4)                                |       |

| Debug SERDES – Loopback Test                                                 |       |

| Debug SERDES – PRBS Test                                                     |       |

| Debug SERDES – PHY Reset                                                     | 65    |

| SmartDebug Tcl Support                                                       | 66    |

| Frequently Asked Questions                                                   | 67    |

| Embedded Flash Memory (NVM) - Failure when Programming/Verifying              | 67 |

|-------------------------------------------------------------------------------|----|

| Analog System Not Working as Expected                                         | 67 |

| ADC Not Sampling the Correct Value                                            | 67 |

| How do I unlock the device security so I can debug?                           | 68 |

| How do I export a report?                                                     | 68 |

| How do I generate diagnostic reports for my target device?                    | 68 |

| How do I monitor a static or pseudo-static signal?                            | 68 |

| How do I force a signal to a new value?                                       | 69 |

| How do I count the transitions on a signal?                                   | 70 |

| How do I monitor or measure a clock?                                          | 71 |

| How do I perform simple PRBS and loopback tests?                              | 73 |

| How do I read LSRAM or USRAM content?                                         |    |

| How do I change the content of LSRAM or USRAM?                                | 74 |

| How do I read the health check of the SERDES?                                 | 76 |

| Where can I find files to compare my contents/settings?                       | 76 |

| What is a UFC file? What is an EFC file?                                      | 76 |

| Is my FPGA fabric enabled?                                                    | 77 |

| Is my Embedded Flash Memory (NVM) programmed?                                 | 77 |

| How do I display Embedded Flash Memory (NVM) content in the Client partition? | 77 |

| How do I know if I have Embedded Flash Memory (NVM) corruption?               | 77 |

| Why does Embedded Flash Memory (NVM) corruption happen?                       | 77 |

| How do I recover from Embedded Flash Memory corruption?                       | 77 |

| What is a JTAG IR-Capture value?                                              | 78 |

| What does the ECC1/ECC2 error mean?                                           | 78 |

| What happens if invalid firmware is loaded into eNVM in SmartFusion2 devices? | 78 |

| Can I compare serialization data?                                             | 78 |

| Can I tell what security options are programmed in my device?                 | 78 |

| How do I interpret data in the Device Status report?                          | 78 |

| How do I interpret data in the Flash Memory (NVM) Status Report?              | 79 |

| Device Status Report                                                          | 80 |

| IDCode                                                                        |    |

| User Info                                                                     | 80 |

| Device State                                                                  | 81 |

| Factory Data                                                                  | 81 |

## **Welcome to SmartDebug**

## Introduction to SmartDebug

Design debug is a critical phase of FPGA design flow. Microsemi's SmartDebug tool complements design simulation by allowing verification and troubleshooting at the hardware level. SmartDebug provides access to non-volatile memory (eNVM), SRAM, SERDES, and probe capabilities. Microsemi SmartFusion2 System-on-chip (SoC) field programmable gate array (FPGA), IGLOO2 FPGA, and RTG4 FPGA devices have built-in probe logic that greatly enhance the ability to debug logic elements within the device. SmartDebug accesses the built-in probe points through the Active Probe and Live Probe features, which enables designers to check the state of inputs and outputs in real-time without re-layout of the design.

## **Use Models**

SmartDebug can be run in the following modes:

- Integrated mode from the Libero Design Flow

- Standalone mode

- Demo mode

### **Integrated Mode**

When run in integrated mode from Libero, SmartDebug can access all design and programming hardware information. No extra setup step is required. In addition, the Probe Insertion feature is available in Debug FPGA Array.

To open SmartDebug in the Libero Design Flow window, expand **Debug Design** and double-click **SmartDebug Design**.

### **Standalone Mode**

SmartDebug can be installed separately in the setup containing FlashPro Express and Job Manager. This provides a lean installation that includes all the programming and debug tools to be installed in a lab environment for debug. In this mode, SmartDebug is launched outside of the Libero Design Flow. When launched in standalone mode, you must to go through SmartDebug project creation and import a Design Debug Data Container (DDC) file, exported from Libero, to access all debug features in the supported devices.

**Note**: In standalone mode, the Probe Insertion feature is not available in FPGA Array Debug, as it requires incremental routing to connect the user net to the specified I/O.

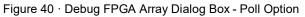

### **Demo Mode**

Demo mode allows you to experience SmartDebug features (Active Probe, Live Probe, Memory Blocks, SERDES) without connecting a board to the system running SmartDebug.

**Note:** SmartDebug demo mode is for demonstration purposes only, and does not provide the functionality of integrated mode or standalone mode.

Note: You cannot switch between demo mode and normal mode while SmartDebug is running.

### Standalone Mode Use Model Overview

In the main use model for standalone SmartDebug, the DDC file must be generated from Libero and imported into a SmartDebug project to obtain full access to the device debug features. Alternatively, SmartDebug can be used without a DDC file with a limited feature set.

## Supported Families, Programmers, and Operating Systems

Programming and Debug: SmartFusion2, IGLOO2, and RTG4

Programmers: FlashPro3, FlashPro4, FlashPro5, FlashPro6

Operating Systems: Windows 7, Windows 10, RHEL 6.x, RHEL 7.x, Cent OS 6, and Cent OS 7

## **Supported Tools**

The following table lists device family support for SmartDebug tools.

| SmartDebug Support per Device Family                    | SmartFusion2 | IGLOO2 | RTG4 |

|---------------------------------------------------------|--------------|--------|------|

| Live Probes                                             | х            | x      | х    |

| Active Probes                                           | х            | x      | х    |

| Memory Debug                                            | х            | x      | x    |

| Probe Insertion (available only through Libero flow)    | х            | x      | x    |

| View Flash Memory Content                               | х            | x      |      |

| Debug SERDES                                            | х            | x      | х    |

| FPGA Hardware Breakpoint (Needs FHB Auto Instantiation) | х            | x      | x    |

| Event Counter (Needs FHB Auto Instantiation)            | х            | x      | x    |

| Frequency Monitor (Needs FHB Auto Instantiation)        | х            | х      | х    |

Note: "X" indicates the tool is supported.

## **Getting Started with SmartDebug**

This topic introduces the basic elements and features of SmartDebug. If you are already familiar with the user interface, proceed to the Solutions to Common Issues Using SmartDebug or Frequently Asked Questions sections.

SmartDebug enables you to use JTAG to interrogate and view embedded silicon features and device status (FlashROM, Security Settings, Embedded Flash Memory (NVM)).

See Using SmartDebug for an overview of the use flow.

You can use the debugger to:

- Get device status and view diagnostics

- Use the Embedded Flash Memory Debug GUI to read out and compare your content with your original files

## Using SmartDebug

The most common flow for SmartDebug is:

- 1. Create your design. You must have a FlashPro programmer connected to use SmartDebug.

- 2. Expand **Debug Design** and double-click **Smart Debug Design** in the Design Flow window. SmartDebug opens for your target device.

- 3. Click View Device Status to view the device status report and check for issues.

- 4. Examine individual silicon features, such as FPGA debug.

## Running SmartDebug in Demo Mode

Demo mode allows you to experience SmartDebug features (Active Probe, Live Probe, Memory Blocks, SERDES) without connecting a board to the system running SmartDebug.

**Note:** SmartDebug demo mode is for demonstration purposes only, and does not provide the functionality of integrated mode or standalone mode.

Note: You cannot switch between demo mode and normal mode while SmartDebug is running.

If programming hardware is not detected when you invoke SmartDebug, you will see the following.

| SmartDebug (DEMO MODE)                   | - 0                                 | $\times$ |

|------------------------------------------|-------------------------------------|----------|

| <u>F</u> ile <u>V</u> iew <u>H</u> elp   |                                     |          |

| Device: M2S/M2GL010(T S TS) (M2GL010T)   | Programmer: simulation (simulation) | Ţ        |

| * SMARTDEBUG IS RU                       | NNING IN DEMO MODE *                |          |

| ID code read from device: HARDWARE NOT C | ONNECTED                            |          |

| View Device Status                       | Debug FPGA Array                    |          |

| View Flash Memory Content                | Debug SERDES                        |          |

|                                          |                                     |          |

| Log                                      |                                     |          |

| 🔳 Messages 🛛 😣 Errors 🗼 Warnings 🌐 Info  |                                     |          |

|                                          |                                     |          |

|                                          |                                     |          |

Figure 1 · SmartDebug in Demo Mode Example

### See Also

Active Probes Live Probes Memory Blocks Debug SERDES - Loopback Test Debug SERDES - PRBS Test

## Create Standalone SmartDebug Project

A Standalone SmartDebug project can be configured in two ways:

- Import DDC files exported from Libero

- Construct Automatically

From the SmartDebug main window, click **Project** and choose **New Project**. The Create SmartDebug Project dialog box opens.

| Create    | SmartDebug Projec                                     | t                  |                    |          | × |

|-----------|-------------------------------------------------------|--------------------|--------------------|----------|---|

| Name:     | sdebug1                                               |                    |                    |          |   |

| Location: | C:/Users                                              |                    |                    |          |   |

| Constru   | ct JTAG chain for the                                 | project            |                    |          |   |

| Conn      | ected programmers:                                    | S201YQST1V         | •                  | Refresh  |   |

|           |                                                       |                    |                    |          | - |

|           | mport DDC File: ade <u>.</u><br>Design debug data wil |                    | srcs/RAM_Logical_V | /iew.ddc |   |

| L         | mport DDC File: ade <u>.</u><br>Design debug data wil | be imported with . | srcs/RAM_Logical_V | /iew.ddc |   |

| L         | Design debug data wil                                 | be imported with . | srcs/RAM_Logical_V | /iew.ddc |   |

| L         | Design debug data wil                                 | be imported with . | srcs/RAM_Logical_V | /iew.ddc |   |

Figure 2 · Create SmartDebug Project Dialog Box

## Import from DDC File (created from Libero)

When you select the **Import from DDC File** option in the Create SmartDebug Project dialog box, the Design Debug Data of the target device and all hardware and JTAG chain information present in the DDC file exported in Libero are automatically inherited by the SmartDebug project. The programming file information loaded onto other Microsemi devices in the chain is also transferred to the SmartDebug project.

Debug data is imported from the DDC file (created through Export SmartDebug Data in Libero) into the debug project, and the devices are configured using data from the DDC file.

If the DDC version and software version are not compatible, project creation is not allowed, and you must run **Generate SmartDebug FPGA Array Data**. Then click **Export SmartDebug Data** to export a new DDC file and use it for project creation.

### **Construct Automatically**

When you select the **Construct Automatically** option, a debug project is created with all the devices connected in the chain for the selected programmer. This is equivalent to Construct Chain Automatically in FlashPro.

### **Configuring a Generic Device**

For Microsemi devices having the same JTAG IDCODE (i.e., multiple derivatives of the same Die—for example, M2S090T, M2S090TS, and so on), the device type must be configured for SmartDebug to enable relevant features for debug. The device can be configured by loading the programming file, by manually selecting the device using Configure Device, or by importing DDC files through Programming Connectivity and Interface. When the device is configured, all debug options are shown.

For debug projects created using Construct Automatically, you can use the following options to debug the devices:

- Load the programming file Right-click the device in Programming Connectivity and Interface.

- Import Debug Data from DDC file Right-click the device in Programming Connectivity and Interface.

The appropriate debug features of the targeted devices are enabled after the programming file or DDC file is imported.

### **Connected FlashPRO Programmers**

The drop-down lists all FlashPro programmers connected to the device. Select the programmer connected to the chain with the debug device. At least one programmer must be connected to create a standalone SmartDebug project.

Before a debugging session or after a design change, program the device through Programming Connectivity and Interface.

### See Also

Programming Connectivity and Interface View Device Status Export SmartDebug Data (from Libero)

## SmartDebug User Interface

You can start standalone SmartDebug from the Libero installation folder or from the FlashPRO installation folder. **Windows:**

<Libero Installation folder>/Designer/bin/sdebug.exe

<FlashPRO Installation folder>/bin/sdebug.exe

Linux:

<Libero Installation folder>/ bin/sdebug

<FlashPRO Installation folder>/bin/sdebug

| SmartDebug                                                                                                                                       |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Project View Tools                                                                                                                               |     |

| 🗋 🚔 н 💩                                                                                                                                          |     |

| SmartDebug Projects New Open Recent Projects C:\SmartDebug\test\test5 C:\SmartDebug\test\test3 C:\SmartDebug\test\test2 C:\SmartDebug\test\test1 |     |

| Log                                                                                                                                              | 8 × |

| Messages 😵 Errors 🗼 Warnings 👔 Info                                                                                                              |     |

Figure 3 · Standalone SmartDebug Main Window

### Project Menu

The Project menu allows you to do the following:

- Create new SmartDebug projects (Project > New Project)

- Open existing debug projects (Project > Open Project)

- Execute SmartDebug-specific Tcl scripts (Project > Execute Script)

- Export SmartDebug-specific commands to a script file (Project > Export Script File)

- See a list of recent SmartDebug projects (Project > Recent Projects).

#### Log Window

SmartDebug displays the Log window by default when it is invoked. To suppress the Log window display, click the View menu and toggle **View Log**.

The Log window has four tabs:

Messages - displays standard output messages

**Errors** – displays error messages

Warnings - displays warning messages

Info – displays general information

#### **Tools Menu**

The Tools menu includes Programming Connectivity and Interface and Programmer Settings options, which are enabled after creating or opening a SmartDebug project.

## Programming Connectivity and Interface

To open the Programming Connectivity and Interface dialog box, from the standalone SmartDebug Tools menu, choose **Programming Connectivity and Interface**. The Programming Connectivity and Interface dialog box displays the physical chain from TDI to TDO.

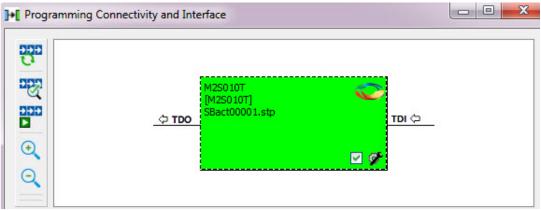

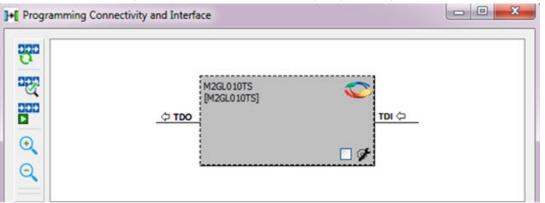

Figure 4 · Programming Connectivity and Interface Dialog Box – Project created using Import from DDC File All devices in the chain are disabled by default when a standalone SmartDebug project is created using the **Construct Automatically** option in the Create SmartDebug Project dialog box.

Figure 5 · Programming Connectivity and Interface window – Project created using Construct Automatically The Programming Connectivity and Interface dialog box includes the following actions:

• Construct Chain Automatically - Automatically construct the physical chain.

Running Construct Chain Automatically in the Programming Connectivity and Interface removes all existing debug/programming data included using DDC/programming files. The project is the same as a new project created using the Construct Chain Automatically option.

- Scan and Check Chain Scan the physical chain connected to the programmer and check if it matches the chain constructed in the scan chain block diagram.

- Run Programming Action Option to program the device with the selected programming procedure.

When two devices are connected in the chain, the programming actions are independent of the device. For example, if M2S090 and M2GL010 devices are connected in the chain, and the M2S090 device is to be programmed and t

he M2GL010 device is to be erased, both actions can be done at the same time using the Run Programming Action option.

- Zoom In Zoom into the scan chain block diagram.

- **Zoom Out** Zoom out of the scan chain block diagram.

### **Hover Information**

The device tooltip displays the following information if you hover your cursor over a device in the scan chain block diagram:

- **Name:** User-specified device name. This field indicates the unique name specified by the user in the Device Name field in Configure Device (right-click **Properties**).

- Device: Microsemi device name.

- Programming File: Programming file name.

- **Programming action:** The programming action selected for the device in the chain when a programming file is loaded.

- IR: Device instruction length.

- **TCK:** Maximum clock frequency in MHz to program a specific device; standalone SmartDebug uses this information to ensure that the programmer operates at a frequency lower than the slowest device in the chain.

| Ф <b>ТDO</b> (2) | <b>\$</b>           |             | м25050T 🍋 ты 🔅 |

|------------------|---------------------|-------------|----------------|

|                  | → □ æ               | M2S050T (2) | • 🛛 🗲          |

|                  | Device:             | M2S050T     |                |

|                  | File:               |             |                |

|                  | Programming action: |             |                |

|                  | IR:                 | 8           |                |

|                  | TCK:                | 10000000    | -              |

### **Device Chain Details**

The device within the chain has the following details:

- User-specified device name

- Device name

- Programming file name

- Programming action Select **Enable Device for Programming** to enable the device for programming. Enabled devices are green, and disabled devices are grayed out.

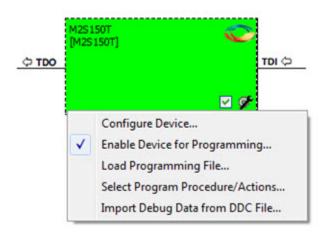

### **Right-click Properties**

The following options are available when you right-click a device in the Programming Connectivity and Interface dialog box.

**Set as Libero Design Device** - The user needs to set Libero design device when there are multiple identical Libero design devices in the chain.

Configure Device - Ability to reconfigure the device.

- Family and Die: The device can be explicitly configured from the Family, Die drop-down.

- Device Name: Editable field for providing user-specified name for the device.

**Enable Device for Programming** - Select to enable the device for programming. Enabled devices are shown in green, and disabled devices are grayed out.

Load Programming File - Load the programming file for the selected device.

Select Programming Procedure/Actions- Option to select programming action/procedures for the devices connected in the chain.

- Actions: List of programming actions for your device.

- **Procedures**: Advanced option; enables you to customize the list of recommended and optional procedures for the selected action.

Import Debug Data from DDC File - Option to import debug data information from the DDC file.

Note: This option is supported when SmartDebug is invoked in standalone mode.

The DDC file selected for import into device must be created for a compatible device. When the DDC file is imported successfully, all current device debug data is removed and replaced with debug data from the imported DDC file.

The JTAG Chain configuration from the imported DDC file is ignored in this option.

If a programming file is already loaded into the device prior to importing debug data from the DDC file, the programming file content is replaced with the content of the DDC file (if programming file information is included in the DDC file).

### **Debug Context Save**

Debug context refers to the user selections in debug options such as Debug FPGA Array, Debug SERDES, and View Flash Memory Content. In standalone SmartDebug, the debug context of the current session is saved or reset depending on the user actions in Programming Connectivity and Interface.

The debug context of the current session is retained for the following actions in Programming Connectivity and Interface:

- Enable Device for Programming

- Select Programming Procedure/Actions

- Scan and Check Chain

- Run Programming Action

The debug context of the current session is reset for the following actions in Programming Connectivity and Interface:

• Auto Construct – Clears all the existing debug data. You need to reimport the debug data from DDC file.

- Import Debug Data from DDC file

- Configure Device Renaming the device in the chain

- Configure Device Family/Die change

- Load Programming File

## Selecting Devices for Debug

Standalone SmartDebug provides an option to select the devices connected in the JTAG chain for debug. The device debug context is not saved when another debug device is selected.

| <b>P</b>         | · 8                                                                                                                    |             |                  |   |

|------------------|------------------------------------------------------------------------------------------------------------------------|-------------|------------------|---|

| M25/M2<br>M25/M2 | 2GL090(T[TS]TV) (M2GL090TS)<br>2GL090(T[TS]TV) (M2GL090TS)<br>2GL010(T[S]TS) (M2GL010TS)<br>read from device: 1F8071CF | Programmer: | 93536 (usb93536) | • |

|                  | View Device Status                                                                                                     |             | Debug FPGA Array |   |

|                  | View Flash Memory Content                                                                                              | ]           | Debug SERDES     |   |

### **View Device Status**

Click **View Device Status** in the standalone SmartDebug main window to display the Device Status Report. The Device Status Report is a complete summary of IDCode, device certificate, design information, programming information, digest, and device security information. Use this dialog box to save or print your information for future reference.

| Device Status:<br>IDCode (read from the device                                                                                                                                               | e) (HEX): 1f807                                                                                                                                                                                                         | lcf                                   |                               |             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|-------------|

| Device Certificate                                                                                                                                                                           |                                                                                                                                                                                                                         |                                       |                               |             |

| Family:                                                                                                                                                                                      | Smart                                                                                                                                                                                                                   | Fusion2                               |                               |             |

| Die:                                                                                                                                                                                         |                                                                                                                                                                                                                         | 5090                                  |                               |             |

| Design Information                                                                                                                                                                           |                                                                                                                                                                                                                         |                                       |                               |             |

| Design Name:                                                                                                                                                                                 |                                                                                                                                                                                                                         | SYS_SERDES                            |                               |             |

|                                                                                                                                                                                              | um (HEX): 53AA                                                                                                                                                                                                          |                                       |                               |             |

| Design Version                                                                                                                                                                               |                                                                                                                                                                                                                         | 0                                     |                               |             |

| Back Level:                                                                                                                                                                                  | 0<br>age: 1.2V                                                                                                                                                                                                          |                                       |                               |             |

| Operating volt<br>Internal Oscilla                                                                                                                                                           |                                                                                                                                                                                                                         | z                                     |                               |             |

| Digest Information                                                                                                                                                                           |                                                                                                                                                                                                                         |                                       |                               |             |

| Fabric Digest (                                                                                                                                                                              |                                                                                                                                                                                                                         | 2634b094bc5aa066<br>78130fa81a31dcb45 |                               |             |

| eNVM_0 Diges                                                                                                                                                                                 |                                                                                                                                                                                                                         | 13000b662a86aea6a<br>9034344d1a266241 |                               |             |

| ARM CortexM3<br>ARM CortexM3<br>ARM CortexM3<br>ARM CortexM3<br>ARM CortexM3<br>ARM CortexM3<br>ARM CortexM3<br>Factory test m<br>Power on resel<br>System Contro<br>Programming Information | access to eSRAM<br>access to eSRAM<br>access to eSRAM<br>access to eNVM_C<br>access to eNVM_C<br>access to DDR bri<br>access to DDR bri<br>ode access: Allowe<br>celay: 100m<br>access to DDR bri<br>ode access: Allowe | s                                     | tected.<br>tected.<br>tected. |             |

| Cycle count:                                                                                                                                                                                 | 333                                                                                                                                                                                                                     |                                       |                               |             |

| VPP Range:<br>Temp Range:                                                                                                                                                                    | HIGH                                                                                                                                                                                                                    | (VPP >= 3.3V)                         |                               |             |

| *Algorithm Ver<br>* Programmer                                                                                                                                                               |                                                                                                                                                                                                                         | FlashPro 5                            |                               |             |

| * Software Ver                                                                                                                                                                               |                                                                                                                                                                                                                         | ro v11.6                              |                               |             |

| * Programming                                                                                                                                                                                | Software: FlashP                                                                                                                                                                                                        | ro                                    |                               |             |

|                                                                                                                                                                                              | File Type: STAPL                                                                                                                                                                                                        |                                       |                               |             |

| IOTE: * - The above Information is only r                                                                                                                                                    |                                                                                                                                                                                                                         |                                       | hrough JTAG or SPI            | Slave mode. |

Figure 6 · Device Status Report

### **IdCode**

IDCode read from the device under debug.

### **Device Certificate**

Device certificate displays Family and Die information if device certificate is installed on the device.

If the device certificate is not installed on the device, a message indicating that the device certificate may not have been installed is shown.

### **Design Information**

Design Information displays the following:

- Design Name

- Design Checksum

- Design Version

- Back Level (SmartFusion2 and IGLOO2 only)

- Operating Voltage (SmartFusion2 and IGLOO2 only)

- Internal Oscillator (SmartFusion2 and IGLOO2 only)

### **Digest Information**

Digest Information displays Fabric Digest, eNVM\_0 Digest and eNVM\_1 Digest (for M2S090 and M2S150 devices only) computed from the device during programming. eNVM Digest is shown when eNVM is used in the design.

### **Device Security Settings**

Note: For RTG4 devices, only Lock Bit information is displayed.

Device Security Settings indicate the following:

- Factory test mode access

- Power on reset delay

- System Controller Suspend Mode

- In addition, if custom security options are used, Device Security Settings indicate:

- User Lock segment is protected

- User Pass Key 1/2 encrypted programming is enforced for the FPGA Array

- User Pass Key 1/2 encrypted programming is enforced for the eNVM\_0 and eNVM\_1

- SmartDebug write access to Active Probe and AHB mem space

- SmartDebug read access to Active Probe, Live Probe & AHB mem space

- UJTAG access to fabric

### **Programming Information**

Programming Information displays the following:

- Cycle Count

- VPP Range

- Temp Range

- Algorithm Version

- Programmer

- Software Version

- Programming Software

- Programming Interface Protocol

- Programming File Type

# Embedded Flash Memory (NVM) Content Dialog Box (SmartFusion2 and IGLOO2 Only)

The NVM content dialog box is divided into two sections:

- View content of Flash Memory pages (as shown in the figure below)

- Check page status and identify if a page is corrupted or if the write count limit has exceeded the 10-year retention threshold

Choose the eNVM page contents to be viewed by specifying the page range (i.e., start page and the end page) and click **Read from Device** to view the values.

You must click Read from Device each time you specify a new page range to update the view.

Specify a page range if you wish to examine a specific set of pages. In the Retrieved Data View, you can enter an Address value (such as 0010) in the Go to Address field and click the corresponding button to go directly to that address. Page Status information appears to the right.

### **Contents of Page Status**

- ECC1 detected and corrected

- ECC2 detected

- Write count of the page

- If write count has exceeded the threshold

- If the page is used as ROM (first page lock)

- Overwrite protect (second page lock)

- Flash Freeze state (deep power down)

| tetrieve Flash Memory Content f                                                                                                                                                                                    | rom Device:                             |                                        |                                                             |                                                  |                                        |                                        |                                  |                                        |                                        |                                        |                                             |                                             |                                        |                                        |                                        |                                        |                                        |                                        |                                        |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------|-------------------------------------------------------------|--------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|---------------------------------------------|---------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|---|

| Select <page range=""> •</page>                                                                                                                                                                                    |                                         | 2                                      | Read from                                                   | Device                                           |                                        |                                        |                                  |                                        |                                        |                                        |                                             |                                             |                                        |                                        |                                        |                                        |                                        |                                        |                                        |   |

| Start Page: 10                                                                                                                                                                                                     |                                         | (address 0                             | x500)                                                       |                                                  |                                        |                                        |                                  |                                        |                                        |                                        |                                             |                                             |                                        |                                        |                                        |                                        |                                        |                                        |                                        |   |

| End Page: 20                                                                                                                                                                                                       |                                         | (11 pages,                             | 1408 byte                                                   | s)                                               |                                        |                                        |                                  |                                        |                                        |                                        |                                             |                                             |                                        |                                        |                                        |                                        |                                        |                                        |                                        |   |

| itest Content Retrieved from Detrieved Content: from Page 10 to                                                                                                                                                    |                                         | 8 bytes startin                        | ig from add                                                 | iress OxS                                        | 00                                     |                                        |                                  |                                        |                                        |                                        |                                             |                                             |                                        |                                        |                                        |                                        | Man.                                   | lan 18 16:41                           | 155 2016                               |   |

| en Al Page Status                                                                                                                                                                                                  |                                         | Go to Addres                           | s (hex):                                                    |                                                  |                                        |                                        | Go                               | I                                      |                                        |                                        |                                             |                                             |                                        |                                        |                                        |                                        |                                        |                                        |                                        |   |

| atus for Page #10:                                                                                                                                                                                                 |                                         |                                        |                                                             |                                                  |                                        |                                        |                                  |                                        |                                        |                                        | Co                                          | ntent                                       |                                        |                                        |                                        |                                        |                                        |                                        | _                                      |   |

|                                                                                                                                                                                                                    |                                         | Page Numbe                             | r   Address                                                 | -                                                | 1.1                                    | 1 2                                    | 1.1                              | 1.4                                    | 1.0                                    | 1.7                                    |                                             |                                             | 1 0                                    | 1.1                                    | 1 .                                    | Lc                                     | 1 0                                    | 1 0                                    | 1 6                                    | - |

|                                                                                                                                                                                                                    |                                         | Page Numbe                             | r   Address<br>00500                                        | 0                                                | 1<br>F6                                | 02                                     | 3                                | 91                                     | 42                                     | 6<br>08                                | D1                                          | 03                                          | 9<br>F8                                | A 98                                   | 20                                     | 42                                     | 0<br>F4                                | е<br>80                                | F 71                                   |   |

| on recoverable data error detected:                                                                                                                                                                                |                                         | _                                      |                                                             | 4                                                |                                        | -                                      | 3<br>02<br>10                    | -                                      | -                                      |                                        | 7                                           | 8                                           | _                                      |                                        | _                                      | -                                      | and property lies                      | of the party little                    | -                                      |   |

| on recoverable data error detected:<br>htte counter over threshold:<br>htte count:                                                                                                                                 | False<br>False<br>152                   | 10                                     | 00500                                                       | 4F<br>C3                                         | F6                                     | 02                                     |                                  | 91                                     | 42                                     | 06                                     | 7<br>D1                                     | 8<br>D3                                     | F8                                     | 98                                     | 20                                     | 42                                     | F4                                     | 80                                     | 71                                     |   |

| ion recoverable data error detected:<br>inte counter over threshold:<br>inte count:<br>be as ROM:<br>hoerwrite Protect:                                                                                            | False<br>False<br>152<br>Off<br>Not set | 10                                     | 00500                                                       | 0<br>∉<br>€                                      | F6<br>F8                               | 02<br>98                               | 10                               | 91<br>D3                               | 42<br>78                               | 06<br>98                               | 7<br>D1<br>60                               | 8<br>D3<br>25                               | F8<br>F0                               | 98<br>80                               | 20<br>65                               | 42<br>C3                               | F4<br>F8                               | 80<br>98                               | 71<br>50                               |   |

| ion recoverable data error detected:<br>inte counter over threshold:<br>inte count:<br>be as ROM:<br>hoerwrite Protect:                                                                                            | False<br>False<br>152<br>Off            | 10<br>10<br>10                         | 00500<br>00510<br>00520                                     | 0<br>∉<br>€<br>₽₽                                | F6<br>F8<br>F6                         | 02<br>98<br>00                         | 10<br>53                         | 91<br>D3<br>CE                         | 42<br>F8<br>F2                         | 06<br>98<br>00                         | 7<br>D1<br>60<br>03                         | 8<br>D3<br>25<br>SD                         | F8<br>F0<br>69                         | 98<br>80<br>45                         | 20<br>65<br>F4                         | 42<br>C3<br>00                         | F4<br>F8<br>70                         | 80<br>98<br>58                         | 71<br>50<br>61                         |   |

| ion recoverable data error detected:<br>Nite counter over threshold:<br>Vinte count:<br>Joe as RCM:<br>Dierwrite Protect:                                                                                          | False<br>False<br>152<br>Off<br>Not set | 10<br>10<br>10<br>10                   | 00500<br>00510<br>00520<br>00530                            | 0<br>4F<br>C3<br>4E<br>FF<br>D6                  | F6<br>F8<br>F6<br>F7                   | 02<br>98<br>00<br>2E                   | 10<br>53<br>F#                   | 91<br>D3<br>CE<br>40                   | 42<br>F8<br>F2<br>F2                   | 06<br>98<br>00<br>84                   | 7<br>D1<br>60<br>03<br>63                   | 8<br>03<br>25<br>50<br>00                   | F8<br>F0<br>69<br>F2                   | 98<br>80<br>45<br>00                   | 20<br>65<br>F4<br>03                   | 42<br>C3<br>00<br>00                   | F4<br>F8<br>70<br>22                   | 80<br>98<br>58<br>D1                   | 71<br>50<br>61<br>18                   |   |

| ion recoverable data error detected:<br>Wite counts over threshold:<br>Wite count:<br>los as RCM:<br>verwrite Protect:                                                                                             | False<br>False<br>152<br>Off<br>Not set | 10<br>10<br>10<br>10                   | 00500<br>00510<br>00520<br>00530<br>00540                   | 0<br>4<br>€<br>FF<br>D6<br>82                    | F6<br>F8<br>F6<br>F7<br>58             | 02<br>98<br>00<br>25<br>40             | 10<br>53<br>FF<br>68             | 91<br>D3<br>CE<br>40<br>08             | 42<br>78<br>72<br>72<br>72<br>32       | 06<br>98<br>00<br>84<br>00             | 7<br>D1<br>60<br>03<br>63<br>18             | 8<br>D3<br>25<br>50<br>C0<br>35             | F8<br>F0<br>69<br>F2<br>60             | 98<br>80<br>45<br>00<br>D1             | 20<br>65<br>F4<br>03<br>58             | 42<br>C3<br>00<br>00<br>46             | F4<br>F8<br>70<br>22<br>68             | 80<br>98<br>58<br>D1<br>08             | 71<br>50<br>61<br>18<br>32             |   |

| ion recoverable data error detected:<br>inte counter over threshold:<br>inte count:<br>be as ROM:<br>hoerwrite Protect:                                                                                            | False<br>False<br>152<br>Off<br>Not set | 10<br>10<br>10<br>10<br>10<br>10       | 00500<br>00510<br>00520<br>00530<br>00540<br>00550          | 0<br>4F<br>C3<br>4€<br>PF<br>D6<br>82<br>00      | F6<br>F8<br>F6<br>F7<br>58<br>F5       | 02<br>98<br>00<br>25<br>40<br>A0       | 10<br>53<br>FF<br>68<br>7F       | 91<br>D3<br>CE<br>40<br>08<br>0E       | 42<br>F8<br>F2<br>F2<br>32<br>60       | 06<br>98<br>00<br>84<br>00<br>F2       | 7<br>D1<br>60<br>03<br>63<br>18<br>D1       | 8<br>03<br>25<br>50<br>00<br>35<br>84       | F8<br>F0<br>69<br>F2<br>60<br>F5       | 98<br>80<br>45<br>00<br>D1<br>E0       | 20<br>65<br>F4<br>03<br>58<br>2F       | 42<br>C3<br>00<br>00<br>46<br>09       | F4<br>F8<br>70<br>22<br>68<br>D3       | 80<br>98<br>58<br>D1<br>08<br>42       | 71<br>50<br>61<br>18<br>32<br>F2       |   |

| Recoverable ECC1 error detected:<br>Kon-ecoverable data error detected:<br>Wite countor over detected:<br>Wite countor over threshold:<br>Wite and ECC<br>Base and ECC<br>Determine Products<br>Reshiftmene state: | False<br>False<br>152<br>Off<br>Not set | 10<br>10<br>10<br>10<br>10<br>10<br>10 | 00500<br>00510<br>00520<br>00530<br>00540<br>00550<br>00560 | 0<br>4<br>C3<br>4€<br>PF<br>D6<br>B2<br>00<br>FB | F6<br>F8<br>F6<br>F7<br>58<br>F5<br>01 | 02<br>98<br>00<br>2E<br>40<br>A0<br>C4 | 10<br>53<br>FF<br>68<br>7F<br>F2 | 91<br>D3<br>CE<br>40<br>08<br>08<br>02 | 42<br>F8<br>F2<br>F2<br>52<br>60<br>01 | 06<br>98<br>00<br>84<br>00<br>F2<br>01 | 7<br>D1<br>60<br>03<br>63<br>18<br>D1<br>24 | 8<br>D3<br>25<br>50<br>C0<br>35<br>B4<br>0C | F8<br>F0<br>69<br>F2<br>60<br>F5<br>60 | 98<br>80<br>45<br>00<br>D1<br>E0<br>4A | 20<br>65<br>F4<br>03<br>58<br>2F<br>68 | 42<br>C3<br>00<br>00<br>46<br>09<br>12 | F4<br>F8<br>70<br>22<br>68<br>D3<br>F0 | 80<br>98<br>58<br>D1<br>08<br>42<br>02 | 71<br>50<br>61<br>18<br>32<br>F2<br>0F |   |

Figure 7 · Flash Memory Dialog Box for a SmartFusion2 Device (SmartDebug)

The page status gets updated when you:

- Click Page Range

- Click a particular cell in the retrieved eNVM content table

- Scroll pages from the keyboard using the Up and Down arrow keys

- Click Go to Address (hex)

The retrieved data table displays the content of the page range selection. If content cannot be read (for example, pages are read-protected, but security has been erased or access to eNVM private sectors), Read from Device reports an error.

Click View Detailed Status for a detailed report on the page range you have selected.

For example, if you want to view a report on pages 1-3, set the Start Page to 1, set the End Page to 3, and click **Read from Device**. Then click **View Detailed Status**. The figure below is an example of the data for a specific page range.

| from Page 1 to Page 3, 384 bytes starting from                                                                      | address 0x80 as of Thu J                                           | lan 07 14:49:29 2016                                       | Save 🖉 🚰 Print                  |

|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------|---------------------------------|

| Page Status Summary [Page 1 to 3]                                                                                   |                                                                    |                                                            |                                 |

| Total number of pages with ECC.<br>Total number of pages with write<br>FlashMemory Check PASSED for [ Page 1 to 3 ] |                                                                    |                                                            |                                 |

| Flash Memory Page Status [Page 1 to 3]                                                                              |                                                                    |                                                            |                                 |

|                                                                                                                     |                                                                    |                                                            |                                 |

| Non recoverable<br>Write counter o<br>Write count:<br>Use as ROM:<br>Overwrite Prote<br>FlashFreeze sta             | e data error detected: Fr<br>ver threshold: Fr<br>3<br>o<br>ect: N | alse                                                       | correct due to OEPB is not set. |

| FlashMemory Page #2:                                                                                                | C1 error detected: Fa                                              | alse                                                       |                                 |

| Non recoverable<br>Write counter o<br>Write count:<br>Use as ROM:<br>Overwrite Prote                                | e data error detected: Fa<br>ver threshold: Fa<br>3<br>0<br>ect: N | alse<br>alse<br>3 *** This value may be in<br>ff<br>ot set | correct due to OEPB is not set. |

| FlashFreeze sta<br>FlashMemory Page #3:                                                                             | ite: Fa                                                            | alse                                                       |                                 |

| Recoverable EC                                                                                                      | e data error detected: Fr<br>wer threshold: Fr<br>3<br>0<br>ect: N | alse                                                       | correct due to OEPB is not set. |

|                                                                                                                     |                                                                    |                                                            |                                 |

Figure 8 · Flash Memory Details Dialog Box (SmartDebug)

## Debugging

## **Debug FPGA Array**

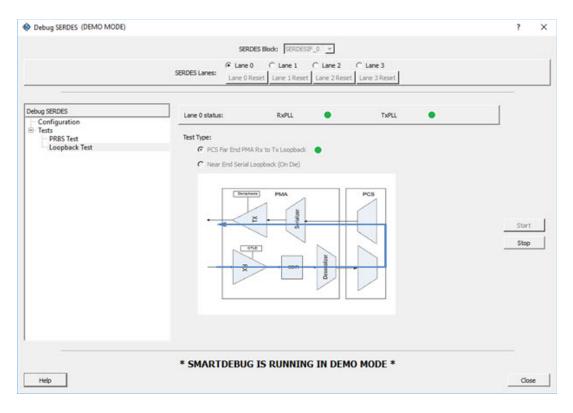

In the Debug FPGA Array dialog box, you can view your Live Probes, Active Probes, Memory Blocks, and Insert Probes (Probe Insertion).

The Debug FPGA Array dialog box includes the following four tabs:

- Live Probes

- <u>Active Probes</u>

- Memory Blocks

- Probe Insertion

It also includes the FPGA Hardware Breakpoint (FHB) controls, consisting of the following tabs:

- "Event Counter" on page 38

- "Frequency Monitor" on page 41

- "User Clock Frequencies" on page 52

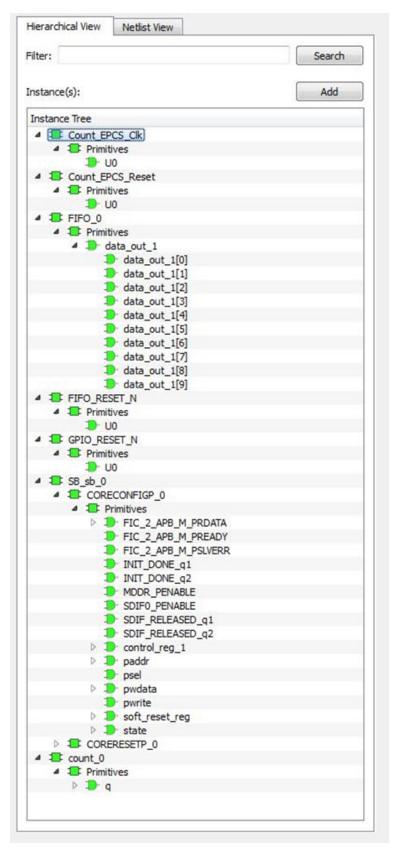

## **Hierarchical View**

The Hierarchical View lets you view the instance level hierarchy of the design programmed on the device and select the signals to add to the Live Probes, Active Probes, and Probe Insertion tabs in the Debug FPGA Array dialog box. Logical and physical Memory Blocks can also be selected.

- Instance Displays the probe points available at the instance level.

- **Primitives** Displays the lowest level of probeable points in the hierarchy for the corresponding component —i.e., leaf cells (hard macros on the device).

You can expand the hierarchy tree to see lower level logic.

Signals with the same name are grouped automatically into a bus that is presented at instance level in the instance tree.

The probe points can be added by selecting any instance or the leaf level instance in the Hierarchical View. Adding an instance adds all the probe able points available in the instance to Live Probes, Active Probes, and Probe Insertion.

Figure 9 · Hierarchical View

#### Search

In Live Probes, Active Probes, Memory Blocks, and the Probe Insertion UI, a search option is available in the Hierarchical View. You can use wildcard characters such as \* or ? in the search column for wildcard matching.

Probe points of leaf level instances resulting from a search pattern can only be added to Live Probes, Active Probes, and the Probe Insertion UI. You cannot add instances of search results in the Hierarchical View.

### **Netlist View**

The Netlist View displays a flattened net view of all the probe-able points present in the design, along with the associated cell type.

| Filter:                       | Sear | ch |

|-------------------------------|------|----|

| Vet(s):                       | Add  | 1  |

| Name                          | Туре | -  |

| count_0_q[0]:count_0/q[0]:Q   | DFF  |    |

| count_0_q[10]:count_0/q[10]:Q | DFF  |    |

| count_0_q[11]:count_0/q[11]:Q | DFF  |    |

| count_0_q[12]:count_0/q[12]:Q | DFF  |    |

| count_0_q[13]:count_0/q[13]:Q | DFF  |    |

| count_0_q[14]:count_0/q[14]:Q | DFF  |    |

| count_0_q[15]:count_0/q[15]:Q | DFF  |    |

| count_0_q[16]:count_0/q[16]:Q | DFF  |    |

| count_0_q[17]:count_0/q[17]:Q | DFF  |    |

| count_0_q[18]:count_0/q[18]:Q | DFF  |    |

| count_0_q[19]:count_0/q[19]:Q | DFF  |    |

| count_0_q[1]:count_0/q[1]:Q   | DFF  |    |

| count_0_q[2]:count_0/q[2]:Q   | DFF  |    |

| count_0_q[3]:count_0/q[3]:Q   | DFF  |    |

| count_0_q[4]:count_0/q[4]:Q   | DFF  |    |

| count_0_q[5]:count_0/q[5]:Q   | DFF  |    |

| count_0_q[6]:count_0/q[6]:Q   | DFF  |    |

| count_0_q[7]:count_0/q[7]:Q   | DFF  |    |

| count_0_q[8]:count_0/q[8]:Q   | DFF  |    |

| count_0_q[9]:count_0/q[9]:Q   | DFF  | 4  |

Figure 10 · Netlist View

### Search

A search option is available in the Netlist View for Live Probes, Active Probes, and Probe Insertion. You can use wildcard characters such as \* or ? in the search column for wildcard matching.

## **Live Probes**

Live Probes is a design debug option that uses non-intrusive real time scoping of up to two probe points with no design changes.

The Live Probes tab in the Debug FPGA Array dialog box displays a table with the probe names and pin types.

Note: SmartFusion2 and IGLOO2 support two probe channels, and RTG4 supports one probe channel.

### **SmartFusion2 and IGLO02**

Two probe channels (ChannelA and ChannelB) are available. When a probe name is selected, it can be assigned to either ChannelA or ChannelB.

You can assign a probe to a channel by doing either of the following:

- Right-click a probe in the table and choose Assign to Channel A or Assign to Channel B.

- Click the **Assign to Channel A** or **Assign to Channel B** button to assign the probe selected in the table to the channel. The buttons are located below the table.

When the assignment is complete, the probe name appears to the right of the button for that channel, and SmartDebug configures the ChannelA and ChannelB I/Os to monitor the desired probe points. Because there are only two channels, a maximum of two internal signals can be probed simultaneously.

Click the **Unassign Channels** button to clear the live probe names to the right of the channel buttons and discontinue the live probe function during debug.

Note: At least one channel must be set; if you want to use both probes, they must be set at the same time.

|                                                    | FPGA Array debug data                                              |                                            |

|----------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------|

| View Netlist View                                  | Live Probes Active Probes Memory Blocks                            |                                            |

| ilter: Search                                      |                                                                    | Delete All                                 |

| et(s): Add                                         |                                                                    | Name                                       |

| Inst_CLK0_Top/Inst_CLK(                            | :Inst_CLK0_Top/Inst_CLK0_B2/Inst_CLK0_B3/Inst_CLK0_B4/Inst_CLK0_B3 | Assign to Channel A<br>Assign to Channel B |

| Inst_CLK0_Top/Inst_CLK(                            |                                                                    |                                            |

| Inst_CLK0_Top/Inst_CLK(<br>Inst_CLK0_Top/Inst_CLK( | ۲ III                                                              |                                            |

| Inst_CLK0_Top/Inst_CLK(                            | Assign to Channel A ->                                             |                                            |

| Inst_CLK0_Top/Inst_CLK(                            | Assign to Channel B ->                                             |                                            |

| Inst_CLK0_Top/Inst_CLK( +                          | Unassign Channels                                                  |                                            |

Figure 11 · Live Probes Tab (SmartFusion2 and IGLOO2) in SmartDebug FPGA Array Dialog Box

### RTG4

One probe channel (Probe Read Data Pin) is available for RTG4 for debug. When a probe name is selected, it can be assigned to the Probe Channel (Probe Read Data Pin).

You can assign a probe to a channel by doing either of the following:

- Right-click a probe in the table and choose Assign to Probe Read Data Pin.

- Click the **Assign to Probe Read Data Pin** button to assign the probe selected in the table to the channel. The button is located below the table.

Click the **Unassign probe read data pin** button to clear the live probe name to the right of the channel button and discontinue the live probe function during debug.

The Active Probes READ/WRITE overwrites the settings of Live Probe channels (if any).

| Active Probes Selection                                                                           | × FPGA Array debug data                                       |                            |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------|

| lierarchical View Netlist View                                                                    | Live Probes Active Probes Memory Blocks                       |                            |

| ilter: Search                                                                                     |                                                               | Delete Delete All          |

| nstance(s): Add                                                                                   | Name                                                          | Туре                       |

| Instance Tree                                                                                     | LED_ctrl_0/pb1_reg1:LED_ctrl_0/pb1_reg1:Q                     | DFF                        |

| ▲ == LED_ctrl_0                                                                                   | LED_ctrl_0/pb1_reg2:LED_ctrl_0/pb1_reg2:Q Ass                 | ign to probe read data pin |

| <ul> <li>Primitives</li> <li>p- counter</li> <li>pb1_reg1</li> </ul>                              | LED_ctrl_0/pb2_reg1:LED_ctrl_0/pb2_reg1:Q                     | DFF                        |