# UG0758 User Guide PolarFire FPGA Design Flow Libero SoC v12.2

NOTE: PDF files are intended to be viewed on the printed page; links and cross-references in this PDF file may point to external files and generate an error when clicked. **View the online help included with software to enable all linked content.**

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email:

sales.support@microsemi.com www.microsemi.com

©2019 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

5-02-00758-10/08.19

# **Table of Contents**

| Libero SoC Introduction                                      | 4  |

|--------------------------------------------------------------|----|

| Welcome to Microsemi's Libero® SoC v12.2                     | 4  |

| Licensing and Additional Resources                           | 4  |

| Libero SoC PolarFire Design Flow                             | 13 |

| Constraint Flow and Design Sources                           | 16 |

| File Types in Libero SoC                                     | 18 |

| Software Tools - Libero SoC                                  | 19 |

| Libero Design Flow                                           | 21 |

| Starting the Libero GUI                                      | 21 |

| Design Report                                                | 22 |

| Using the New Project Wizard to Start a Project              | 23 |

| Create and Verify Design                                     | 29 |

| Create SmartDesign                                           | 29 |

| Create Core from HDL                                         | 36 |

| Designing with HDL                                           | 38 |

| Designing with Block Flow                                    | 39 |

| Create New SmartDesign Testbench                             | 39 |

| HDL Testbench                                                | 40 |

| Verify Pre-Synthesized Design - RTL Simulation               | 41 |

| Libero SoC Constraint Management                             | 45 |

| Invocation of Constraint Manager From the Design Flow Window | 45 |

| Libero SoC Design Flow                                       | 45 |

| Introduction to Constraint Manager                           | 46 |

| Import a Constraint File                                     | 50 |

| Constraint Types                                             | 54 |

| Constraint Manager – I/O Attributes Tab                      | 55 |

| Constraint Manager – Timing Tab                              | 57 |

| Derived Constraints                                          | 59 |

| Constraint Manager – Floor Planner Tab                       | 60 |

| Constraint Manager – Netlist Attributes Tab                  | 61 |

| Implement Design                                             | 63 |

| Synthesize                                                   | 63 |

| Verify Post-Synthesized Design                               | 68 |

| Compile Netlist                                              | 69 |

| Constraint Flow in Implementation                 |     |

|---------------------------------------------------|-----|

| Place and Route                                   | 75  |

| Multiple Pass Layout Configuration                | 79  |

| Resource Usage                                    | 81  |

| Global Net Report                                 | 83  |

| Verify Post Layout Implementation                 | 87  |

| Configure Hardware                                | 99  |

| Programming Connectivity and Interface            | 99  |

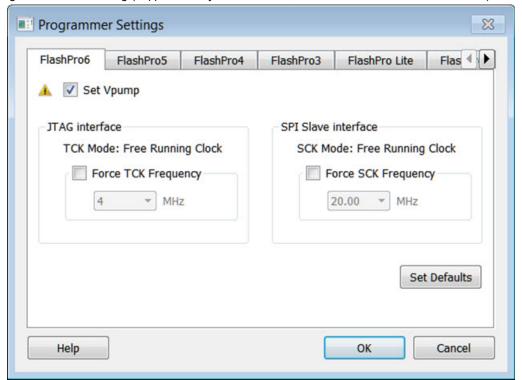

| Programmer Settings                               | 10  |

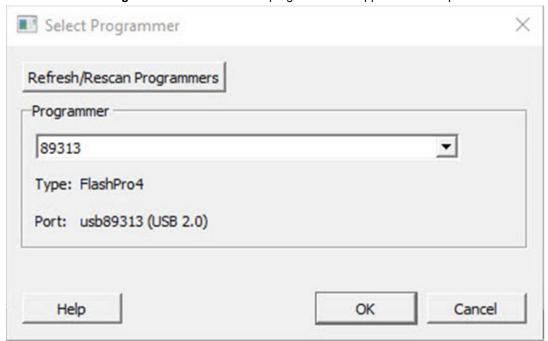

| Select Programmer                                 | 103 |

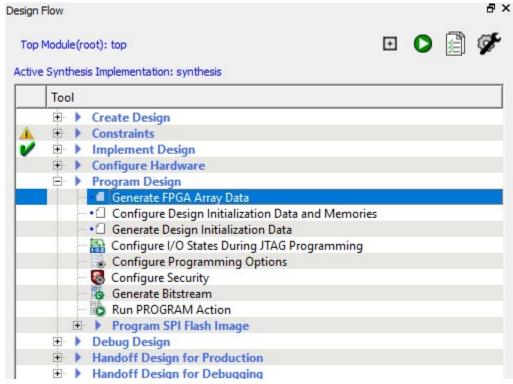

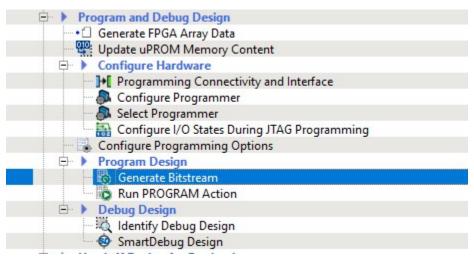

| Program Design                                    | 104 |

| Generate FPGA Array Data                          | 104 |

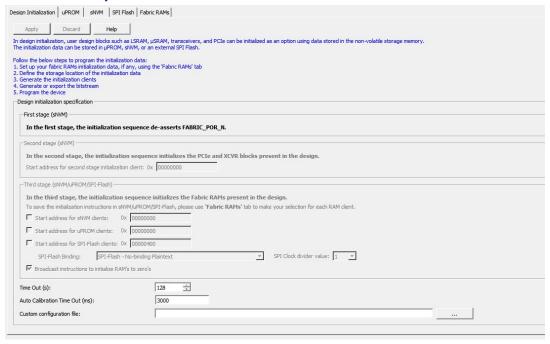

| Configure Design Initialization Data and Memories | 104 |

| Generate Design Initialization Data               | 124 |

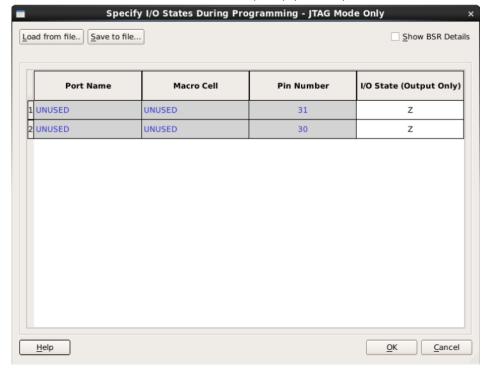

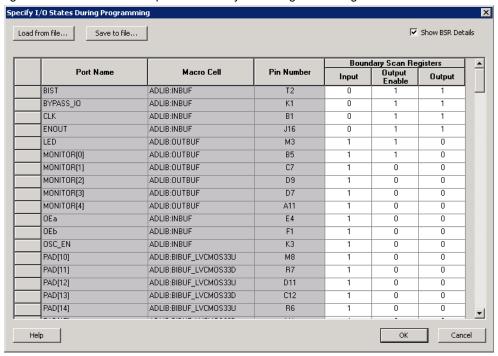

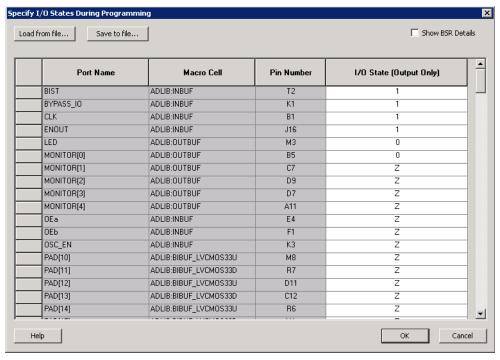

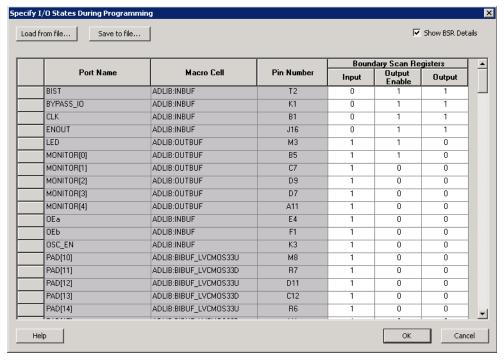

| Configure I/O States During JTAG Programming      | 124 |

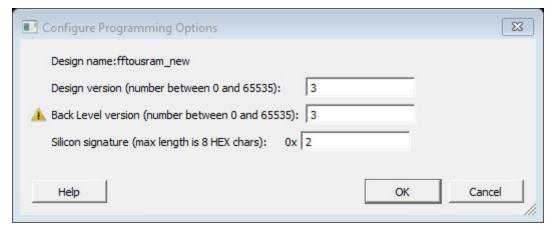

| Configure Programming Options                     | 125 |

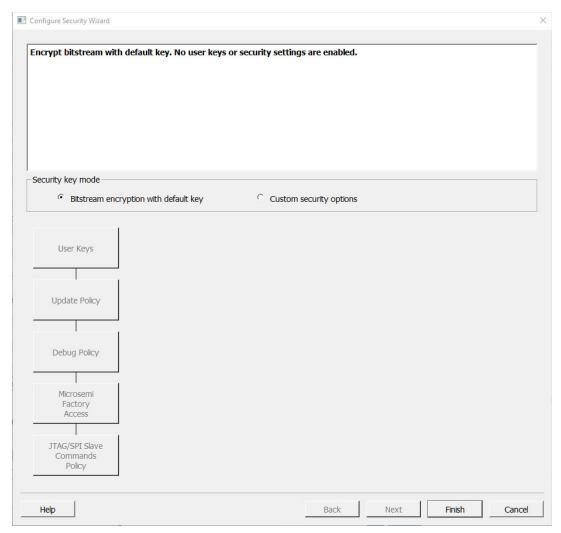

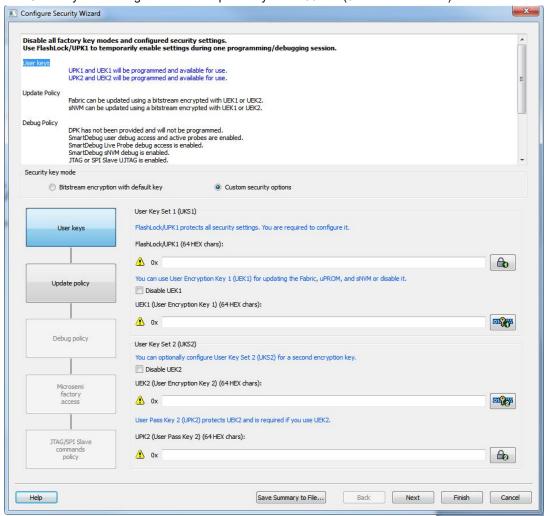

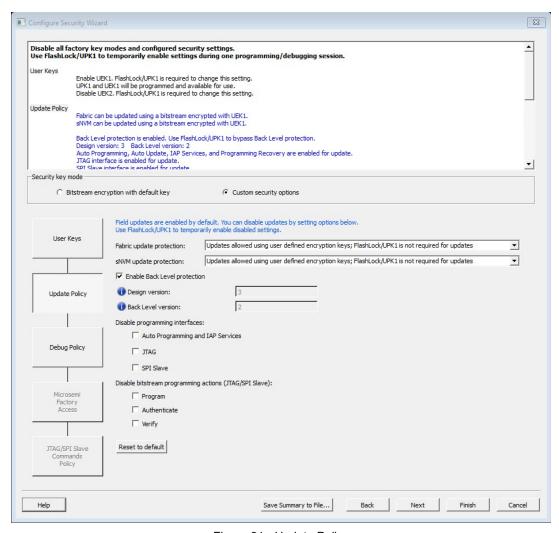

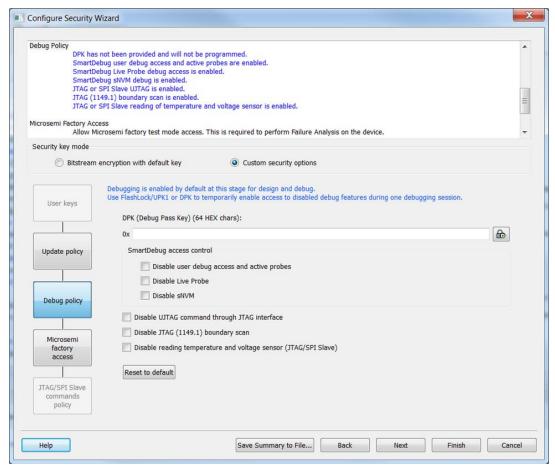

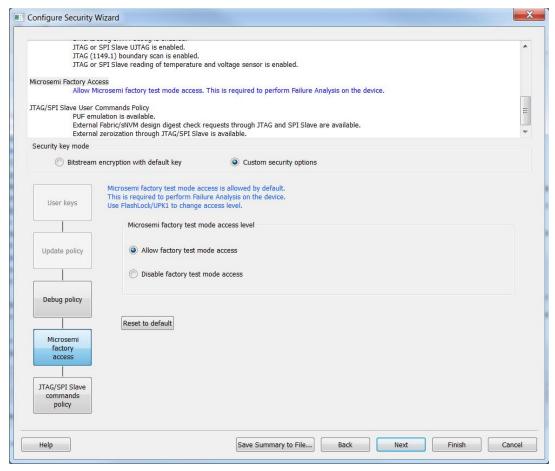

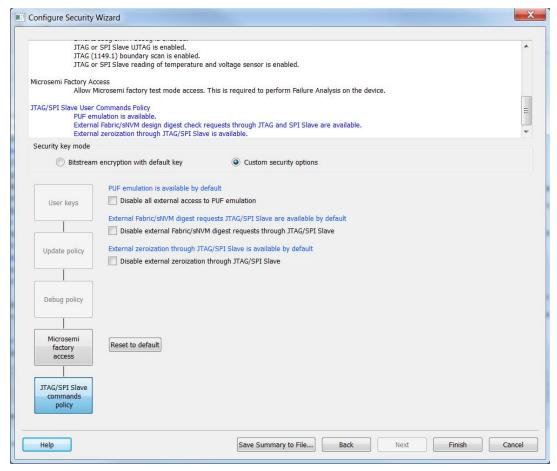

| Configure Security                                | 126 |

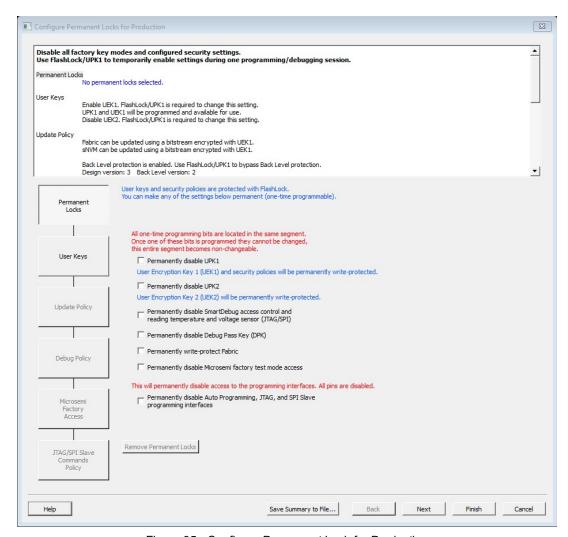

| Configure Permanent Locks for Production          | 136 |

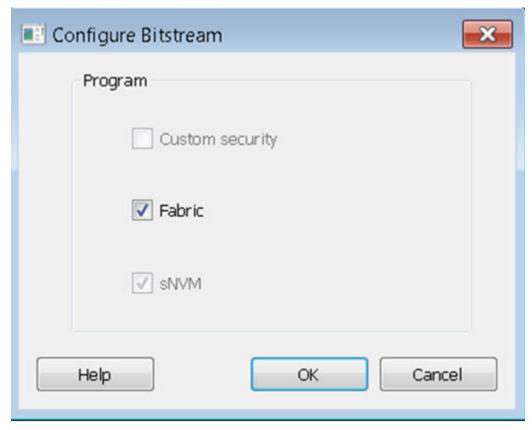

| Configure Bitstream                               | 138 |

| Generate Bitstream                                | 139 |

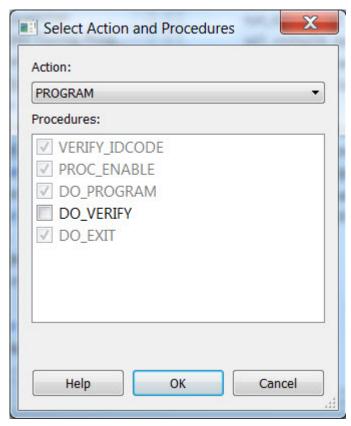

| Run Programming Device Actions                    | 140 |

| Program SPI Flash Image                           | 148 |

| Debug Design                                      | 152 |

| Generate SmartDebug FPGA Array Data               | 152 |

| SmartDebug                                        |     |

| Identify Debug Design                             | 150 |

| Handoff Design for Production                     |     |

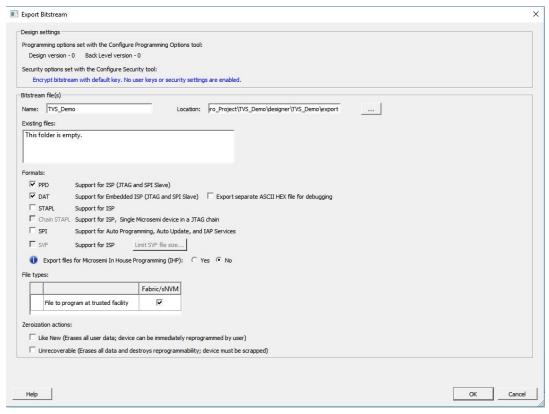

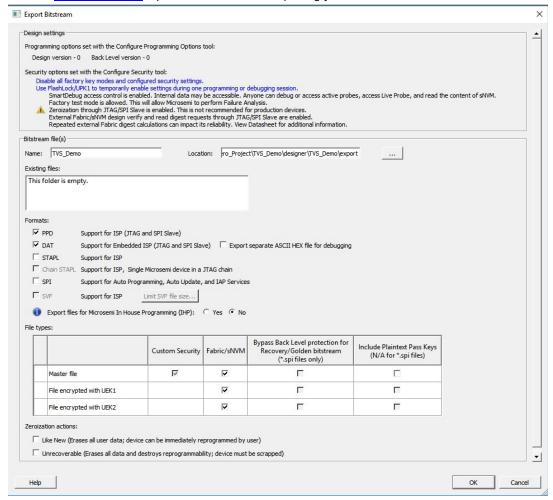

| Export Bitstream                                  |     |

| Export FlashPro Express Job                       |     |

| Export Job Manager Data                           |     |

| Export SPI Flash Image                            |     |

| Export Pin Report                                 |     |

| Export BSDL File                                  |     |

| Export IBIS Model                                 | 170 |

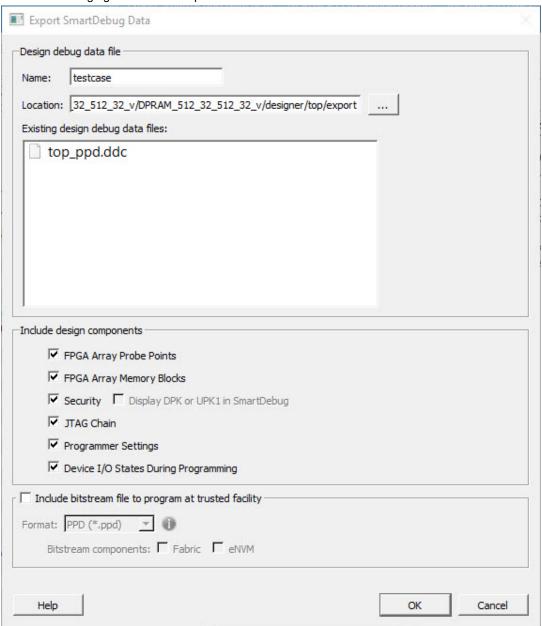

| Export SmartDebug Data (Libero SoC)               | 173 |

| References                                        | 175 |

## **Libero SoC Introduction**

## Welcome to Microsemis Libero SoC v12.2

Microsemi Libero® System-on-Chip (SoC) design suite offers high productivity with its comprehensive, easy to learn, easy to adopt development tools for designing with Microsemi's power efficient flash FPGAs, SoC FPGAs, and Rad-Tolerant FPGAs. The suite integrates industry standard Synopsys Synplify Pro® synthesis and Mentor Graphics ModelSim® simulation with best-in-class constraints management, debug capabilities, and secure production programming support.

#### **More Information**

To access datasheets and silicon user guides, visit <a href="www.microsemi.com">www.microsemi.com</a>, select the relevant product family and click the **Documentation** tab. Tutorials, Application Notes, <a href="Development Kits & Boards">Development Kits & Boards</a> are listed in the **Design Resources** tab.

Click the following links for additional information:

- Libero SoC- <u>Learn more about Libero SoC</u> including Release Notes, a complete list of devices/packages, and timing and power versions supported in this release.

- Programming Learn more about Programming Solutions

- Power Calculators <u>Find XLS-based estimators for device families</u>

- Licensing Learn more about Libero licensing

## Licensing and Additional Resources

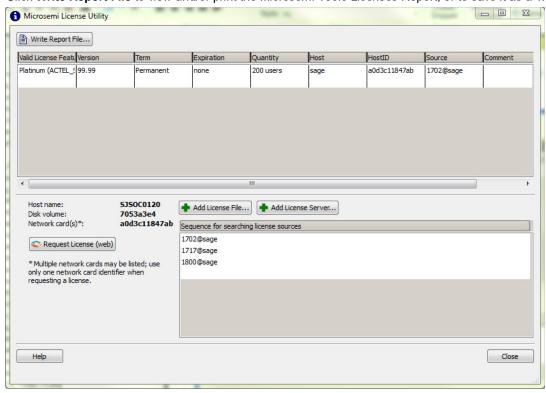

### **Microsemi License Utility**

The Microsemi License Utility enables you to check and update your license settings for the Libero SoC software. It displays your current license settings, the license host-id for the current host, and allows you to add a new license file to your settings.

To start the Microsemi License Utility, run it from **Start > All Programs > Microsemi Libero SoC v**x.xx> **Microsemi License Utility**.

To request a license, click **Request License** to go to the Microsemi license website. You can select and copy (right-click, **Copy**) the disk volume value displayed in the window and paste the value into the Microsemi license web form.

The following licenses are available:

- 1-year Platinum Purchased license that supports all devices

- 1-year Gold Purchased licenses that supports a smaller set of devices than Platinum

- 1-year Silver Free license that supports a smaller set of devices than Gold

- 30-day Evaluation Free license that supports all devices but programming is disabled

When you have received your license file, follow the instructions and save the license to your local disk. In the Microsemi License Utility window, click **Add License File** and browse/select the license file from your disk. If you are using a floating license, click **Add License Server** and enter the Port Number and Name of the license server host.

The list of features for which you are licensed will show all versions, but your license must have a version equal to or greater than your design tools release version in order for the libero.exe and designer.exe tools to run.

The list at the lower right shows the order in which the license files are read, with the first file read at the top of the list

Click Write Report File to view and/or print the Microsemi Tools Licenses Report, or to save it as a TXT file.

Figure 1 · Microsemi License Utility

The <u>Microsemi Libero SoC License Information Web Page</u> provides additional licensing-related information including links to troubleshooting and FAQ documents.

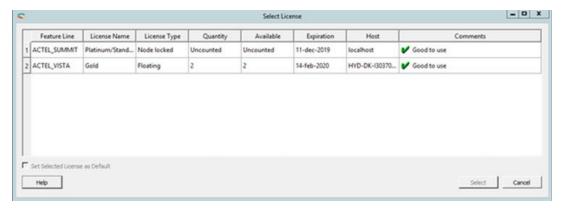

#### **License Selection**

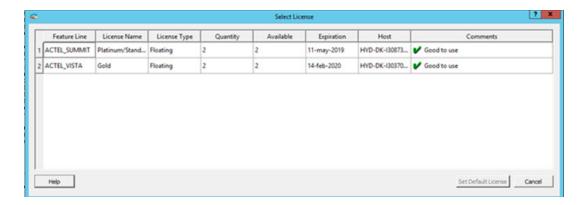

This topic describes the Select License and License Details dialog boxes.

### **Select License Dialog Box**

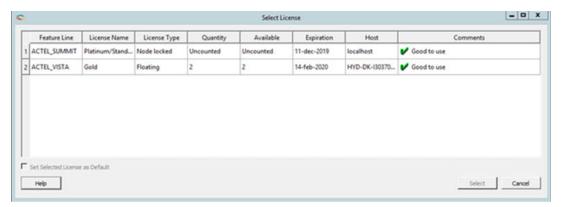

The Select License dialog box appears when there is more than one license available and a default license has not been selected. Available licenses are displayed in list format, and you can select the feature license you want to use.

Figure 2 · Select License Dialog Box

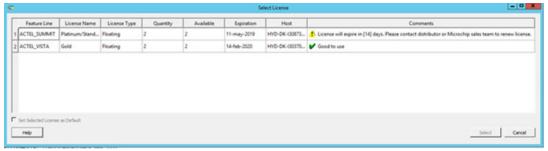

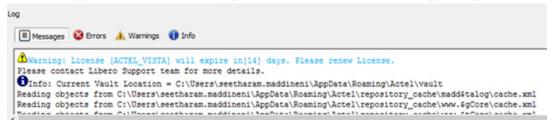

If a license will expire within 15 days, you will see a warning in the Comments field of the dialog box and also in the Log window, as shown in the examples below.

Figure 3 · Select License Dialog Box with License Expiration Warning Message

Figure 4 · Log Window with License Expiration Warning Message

#### **Actions**

Click **Select** to use the selected license to invoke Libero. This button is disabled by default, and is enabled once a License is selected.

Click Cancel to close the license selection window and exit Libero.

Click Help to open the online help topic for License Selection.

Check the **Set Selected License as Default** check box to save the selected license as the default license to be used for future sessions.

Selecting this option skips the license selection step for future sessions. This option can be used if you want to use the same license features for future sessions.

#### **License Types**

The **License Type** column indicates whether an available license is a Node Locked license or a Floating or Server-based license.

The total number of licenses and number of available licenses are shown in the **Quantity** and **Available** columns, respectively.

Floating or Server-based Licenses can be used by multiple users, depending on the number of seats available.

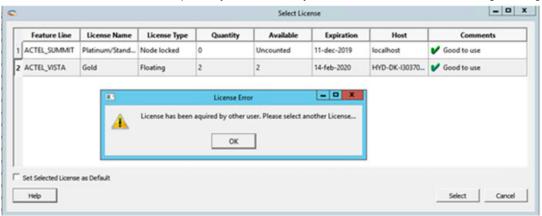

If there are no valid licenses available, the following message appears:

If a selected license has been acquired by another user, you will be notified with the following message:

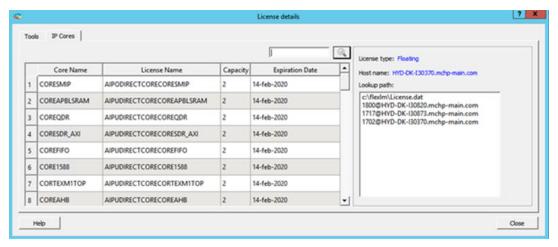

## **License Details Dialog Box**

The License Details dialog box has two tabs:

- Tools

- IP Cores

#### **Tools**

The Tools tab displays tool license details.

## **IP Cores**

The IP Cores tab displays IP Cores license details, as shown in the following example.

Figure 5 · IP Cores License Details

#### **Actions**

Click Close to close the current dialog box.

Click Help to open the online help topic for License Selection.

Click Filter to search for the pattern specified in the text edit box. Filtered rows will be shown in the Cores table.

Lookup Path: Shows the list of License hosts included in the LM\_LICENSE\_FILE.

#### **Additional License Information**

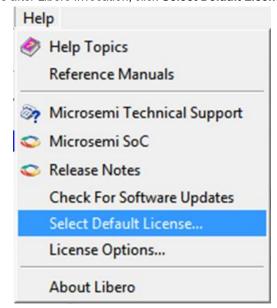

#### Set Default License After Libero Invocation

This Libero Help menu option sets/updates the default Libero license and allows it to be used for future sessions. To set the default license after Libero invocation, click **Select Default License**, as shown below.

The Select License dialog box appears, as shown in the example below.

#### **Actions**

Click **Set Default License** to set the default Libero license. You can also double-click the license row to set the default license. This button is enabled if you select any row in the list of licenses.

Click Cancel to close the default license selection window without performing any action.

Click **Help** to open the online help document for License Selection.

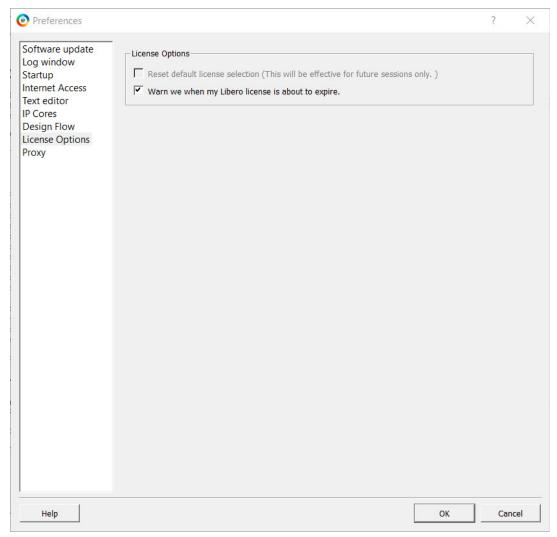

#### **Set License Options in Libero Preferences Dialog Box**

To set license options in the Libero Preferences dialog box, click **Project > Preferences**.

Figure 6 · License Options in Libero Preferences Dialog Box

**Reset Default License Selection:** This check box is enabled only when there is a default license available. When this check box is checked, the default license will be cleared and the check box will be disabled.

"Warn we when my Libero license is about to expire": This check box enables/disables Notification of License expiry. If the selected license expiry date is within 15 days, a popup message appears.

This option can be used only when the expiry date is more than 5 days and less than 15 days.

General Information about Microsemi's FPGA & SoC products is available here.

### **Information About PolarFire Technology**

More information about PolarFire Technology is available here.

## **Information About Supported Families**

Table 1 · Product Families and Derivatives

| Device<br>Family | Family<br>Derivatives | Description                                                                                                                         |

|------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| <u>PolarFire</u> | N/A                   | New FPGA family that delivers the lowest power at mid-range densities, and is optimized for cost while providing high end features. |

#### Information About Libero SoC PolarFire Software

More information about Libero SoC PolarFire Software is available here.

## **Application Notes and Tutorials**

Application Notes and Tutorials for PolarFire can be found <u>here on the Documentation tab of the PolarFire</u> Technology page.

## Online Help - Libero SoC

This online help system is designed to open in the HTML Help Viewer – Microsoft's Help window for viewing compiled HTML Help. If you do not have the HTML Help Viewer components installed on your system, you can view it with Microsoft's Internet Explorer browser (use version 4.x or later for complete functionality).

### **Viewing HTML Files on Linux**

You may need to set your LINUX\_HTMLREADER variable such that it enables a HTML viewer. For example:

setenv LINUX HTMLREADER /usr/bin/firefox

If you do not set this variable then some HTML files, such as the help, will not be available from within software.

#### See Also

Navigation tabs

User's Guides

### **Using Navigation tabs**

Libero SoC online Help, which is generated using Microsoft HTML Help, includes the following navigation tabs:

#### Contents

The Contents tab displays books and pages that represent the categories of information in the online Help system. When you click a closed book, it opens to display its content (sub-books and pages). When you click an open book, it closes. When you click pages, you select topics to view in the right-hand pane of the HTML Help viewer.

#### Search

The Search tab enables you to search for words in the Help system and locate topics containing those words. Full-text searching looks through every word in the online Help to find matches. When the search is completed, a list of topics is displayed so you can select a specific topic to view.

### **Reading User Guides**

Libero SoC includes online manuals. The online manuals are in PDF format and available from Libero SoC Start Menu. Note that PDF files are for printing and viewing offline; use the online help to view user support on your workstation.

From the Start menu, choose **All Programs > Microsemi > Libero SoC > Libero SoC Reference Manuals** You must have Adobe Acrobat Reader or similar PDF viewer to open and view the PDF user guides.

#### **Viewing PDF Files on Linux**

You may need to set your LINUX\_PDFREADER variable such that it enables a PDF viewer. For example:

setenv LINUX PDFREADER /usr/bin/kpdf

If you do not set this variable then some PDF files, such as the SmartTime User's Guide, will not be available from within software.

## Microsemi SoC Products Group Headquarters

Microsemi Corporation is a supplier of innovative programmable logic solutions, including field-programmable gate arrays (FPGAs) based on antifuse and flash technologies, high-performance intellectual property (IP) cores, software development tools, and design services targeted for the high-speed communications, application-specific integrated circuit (ASIC) replacement, and radiation-tolerant markets.

| Address: | Microsemi SoC Products Group<br>3870 North First Street<br>San Jose, CA 95134 |

|----------|-------------------------------------------------------------------------------|

| Phone:   | 408-643-6000                                                                  |

#### **Contact Information**

For the most up-to-date contact information, check the <u>Microsemi Home Page</u>.

Contact information for FPGAs & SoCs can be found at the <u>FPGAs and SoCs Support Page</u>

If you do not have internet access, the following information was accurate at the time of publication:

- Technical Support

- Web: <a href="https://soc.microsemi.com/mycases">https://soc.microsemi.com/mycases</a>

- Phone (NA): 800.262.1060

- Phone (Int'l): +1 650.313.4460

- Email: soc\_tech@microsemi.com

- Customer (non-technical) Support

- Phone: +1 650.318.2470

- Email: customer.service@microsemi.com

- Sales Support

- For pricing, order status and lead time information for all Microsemi SoC products, contact your Microsemi Sales Representative

- Technical Support for RH and RT FPGAs that are regulated by International Traffic in Arms Regulations (ITAR)

- Phone (NA): 888.988.ITAR

- Phone (Int'l): +1 650.318.4900

- Email: soc\_tech\_itar@microsemi.com

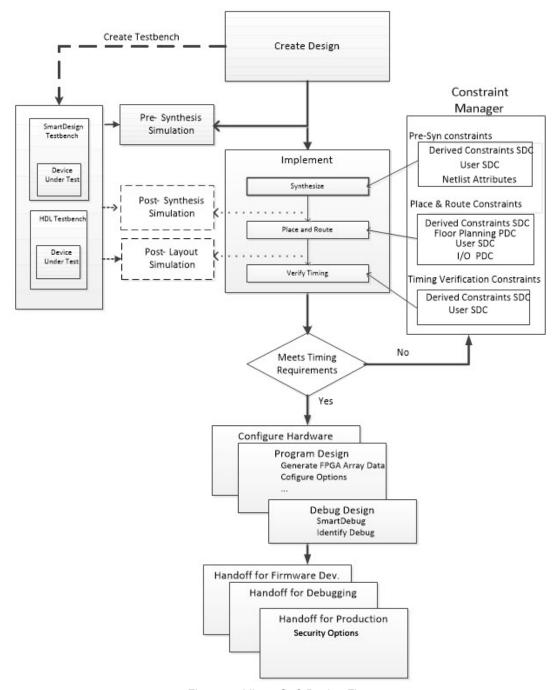

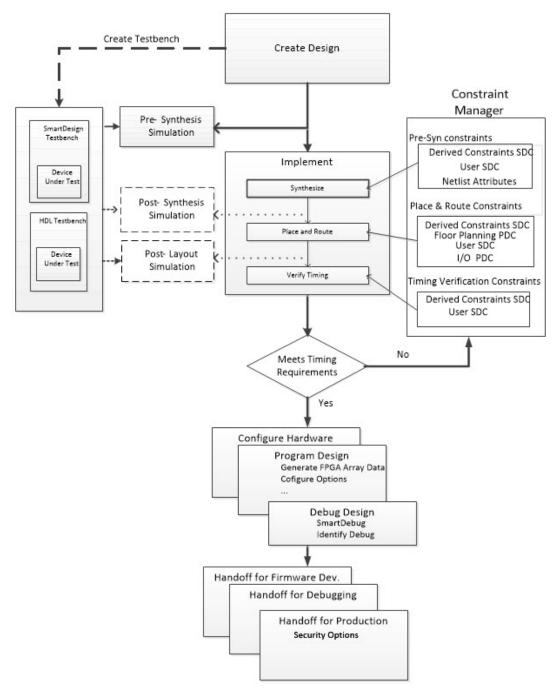

## Libero SoC PolarFire Design Flow

Figure 7 · Libero SoC Design Flow

## **Create Design**

Create your design with any or all of the following design capture tools:

- Create SmartDesign

- Create HDL

- Create SmartDesign Testbench (optional, for simulation only)

- Create HDL Testbench (optional, for simulation only)

Once the design is created, you can invoke simulation for pre-synthesis verification.

It is also possible to click the button, to execute the Libero SoC software through Place and Route with default settings. However, this bypasses constraint management.

#### **Constraints**

#### Manage Constraints

In the FPGA design world, constraint files are as important as design source files. Constraint files are used throughout the FPGA design process to guide FPGA tools to achieve the timing and power requirements of the design. For the synthesis step, SDC timing constraints set the performance goals whereas non-timing FDC constraints guide the synthesis tool for optimization. For the Place-and-Route step, SDC timing constraints guide the tool to achieve the timing requirements whereas Physical Design Constraints (PDC) guide the tool for optimized placement and routing (Floorplanning). For Static Timing Analysis, SDC timing constraints set the timing requirements and design-specific timing exceptions for static timing analysis.

Libero SoC provides the Constraint Manager as the cockpit to manage your design constraint needs. This is a single centralized graphical interface for you to create, import, link, check, delete, edit design constraints and associate the constraint files to design tools in the Libero SoC environment. The Constraint Manager allows you to manage constraints for SynplifyPro synthesis, Libero SoC Placeand-Route and the SmartTime Timing Analysis throughout the design process.

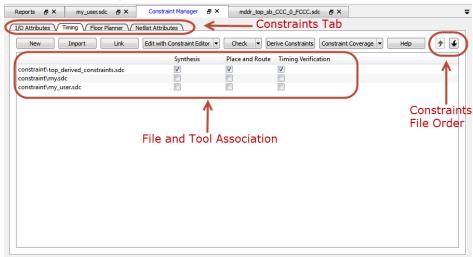

#### Invocation of Constraint Manager From the Design Flow Window

After project creation, double-click Manage Constraints in the Design Flow window to open the Constraint Manager.

Figure 8 · Constraint Manager

- See Also

- Constraint Manager

- New Project Wizard to import/link design constraints when creating new projects

### **Implement**

- Open Netlist Viewer (User Guide)

- Synthesize Double-click Synthesize to run synthesis on your design with the default settings. The

constraints associated with Synthesis in the Constraint Manager are passed to Synplify.

- Verify Post-Synthesis Implementation (Simulate)

- <u>Place and Route</u> Place and Route takes the design constraints from the Constraint Manager and

runs with default settings. This is the last step in the push-button design flow execution.

- Verify Post Layout Implementation

- Verify Timing Right click and select <u>Configure Options</u> to specify a timing report with your desired conditions.

- Open SmartTime

- Verify Power

- Open SSN Analyzer

### **Configure Hardware**

- Programming Connectivity and Interface Organizes your programmer(s) and devices.

- <u>Configure Programmer</u> Opens your programmer settings; use if you wish to program using settings other than default.

- Select Programmer

- <u>Device I/O States During Programming</u> Sets your device I/O states during programming; use if your design requires that you change the default I/O states.

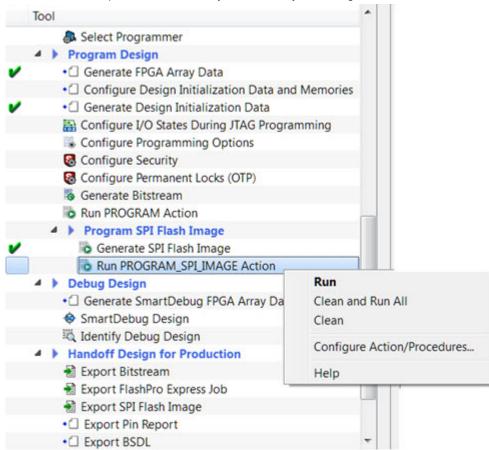

## **Program Design**

- Generate FPGA Array Data

- Configure Design and Memory Initialization

- Configure I/O States During JTAG Programming

- Configure Programming Options

- Configure Security Wizard

- Configure Permanent Locks (OTP)

- Generate Bitstream

- Run PROGRAM Action

- Program SPI Flash Image

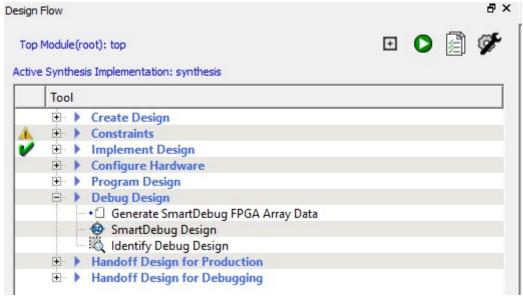

#### **Debug Design**

- SmartDebug (User Guide)

- Identify Debug Design

### **Handoff Design for Production**

- Export Bitstream

- Export SPI Flash Image

- Export FlashPro Express Job

- Export Job Manager Data

- Export Pin Report

- Export BSDL

- Export IBIS Model

## Handoff Design for Debugging (Export SmartDebug Data)

## Constraint Flow and Design Sources

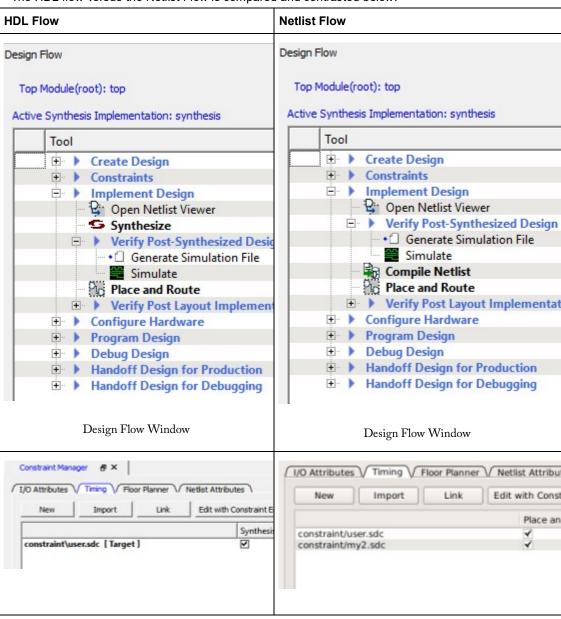

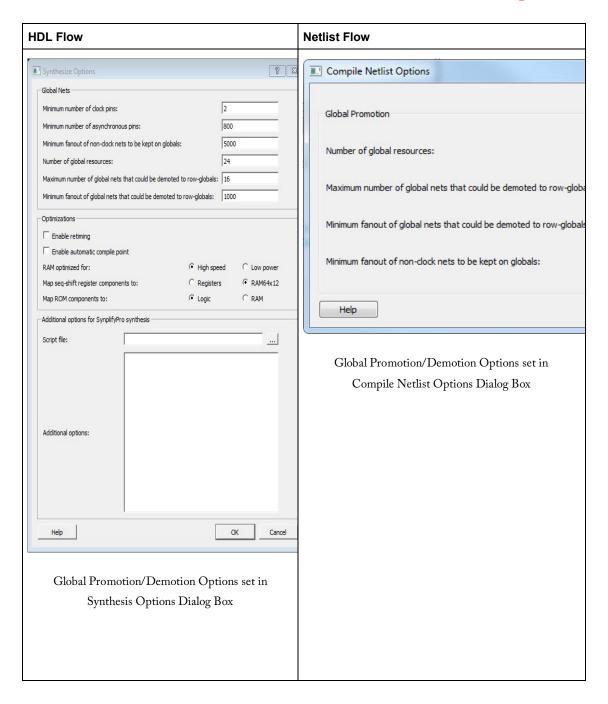

The Constraint Flow supports HDL and Netlist design sources. The Libero SoC Design Flow window and the Constraint Manager are context-sensitive to the type of design sources: HDL or Netlist.

## **Constraint Flow for HDL designs**

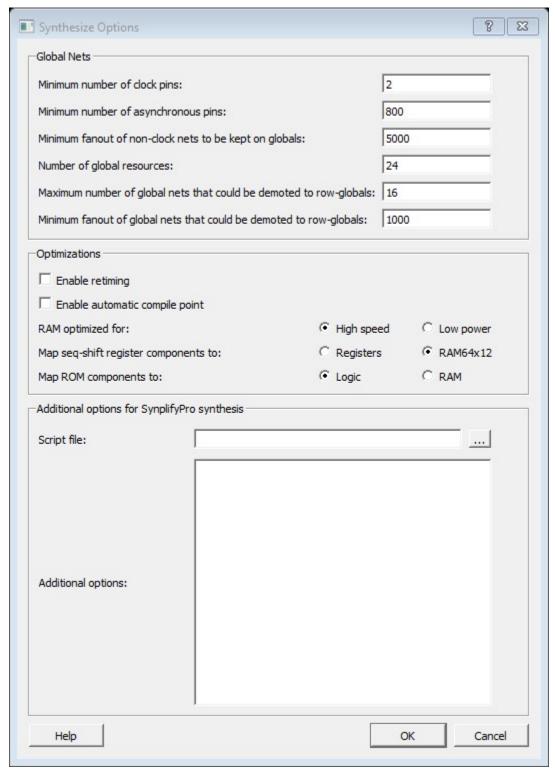

When the design source is HDL, the Design Flow window displays Synthesis as a design step. The Constraint Manager also makes available Synthesis as a target to receive timing constraints and netlist attribute constraints. The options to promote or demote global resources of the chip are set in the Synthesis options.

## **Constraint Flow for EDIF designs**

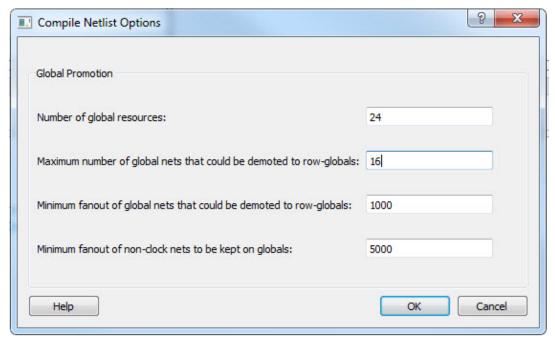

When the design source is a Netlist, the Design Flow window displays Compile Netlist as a design step. Timing constraints can be passed to Place and Route and Timing Verification only.

The options to promote or demote global resources of the chip are set in the Compile Netlist options.

The HDL flow versus the Netlist Flow is compared and contrasted below.

| HDL Flow                                   | Netlist Flow                          |

|--------------------------------------------|---------------------------------------|

| Constraint Manager                         | Constraint Manager                    |

| Constraint Manager                         | I/O Attributes                        |

| Synthesis  constraint\user.sdc [ Target ]  |                                       |

| Constraint Manager - Check *.fdc and *.ndc | Constraint Manager - Check *.ndc only |

Figure 9 · HDL vs. Netlist Flow

## File Types in Libero SoC

When you create a new project in Libero SoC it automatically creates new directories and project files. Your project directory contains all of your local project files. When you <u>import</u> files from outside your current project, the files are copied into your local project folder.

The Project Manager enables you to manage your files as you import them. If you want to store and maintain your design source files and design constraint files in a central location outside the Project location, Libero gives you the option to link them to your Libero project folders when you first create your project. These linked files are not copied but rather linked to your project folder.

Depending on your project preferences and the version of Libero SoC you installed, the software creates directories for your project.

The top level directory (project\_name>) contains your \*.prjx file; only one \*.prjx file is enabled for each Libero SoC project. If you associate Libero SoC as the default program with the \*.prjx file (Project > Preferences > Startup > Check the default file association (.prjx) at startup), you can double-click the \*.prjx file to open the project with Libero SoC.

**component** directory - Stores your SmartDesign components (SDB and CXF files) and the \*\_manifest.txt file for each design components in your Libero SoC project. Refer to the \*\_manifest.txt file if you want to run synthesis, simulation, and firmware development with your own point tools outside the Libero SoC environment. For each design component, Libero SoC generates a <component\_name>\_manifest.txt file which stores the file name and location of:

- HDL source files to be used for synthesis and simulations

- Stimulus files and configuration files for simulation

- Firmware files for software IDE tools

- Configuration files for programming

- · Configuration files for power analysis.

**constraint** directory - All your constraint files (SDC timing constraint files, floorplanning PDC files, I/O PDC files, Netlist Attributes NDC files)

**designer** directory - \*\_ba.sdf, \*\_ba.v(hd), STP, PRB (for Silicon Explorer), TCL (used to run designer), impl.prj\_des (local project file relative to revision), designer.log (logfile)

hdl directory - all hdl sources. \*.vhd if VHDL, \*.v and \*.h if Verilog

simulation directory - meminit.dat, modelsim.ini filesfiles and \*.vec file, run.do file for simulation.

smartgen directory - GEN files and LOG files from generated cores

stimulus directory - BTIM, Verilog, and VHDL stimulus files

**synthesis** directory - \*.**vm** (**Verilog Netlist output**), \*\_syn.prj (Synplify log file), \*.psp (Precision project file), \*.srr (Synplify logfile), precision.log (Precision logfile), \*.tcl (used to run synthesis) and many other files generated by the tools (not managed by Libero SoC)

viewdraw directory - viewdraw.ini files

#### **Internal Files**

Libero SoC generates the following internal files. They may or may not be encrypted. They are for Libero SoC housekeeping and are not for users.

| File                      | File Extension | Remarks                 |

|---------------------------|----------------|-------------------------|

| Routing Segmentation File | *.seg          |                         |

| Combiner Info             | *.cob          |                         |

| Hierarchical Netlist      | *.adl          |                         |

| Flattened Netlist         | *.afl          |                         |

| map file                  | *.map          | Fabric Programming File |

## Software Tools - Libero SoC

The Libero SoC integrates design tools, streamlines your design flow, manages design and log files, and passes design data between tools.

For more information on Libero SoC tools, visit:

https://www.microsemi.com/products/fpga-soc/design-resources/design-software/libero-soc#overview

| Function                                                                                                       | Tool                       | Company            |

|----------------------------------------------------------------------------------------------------------------|----------------------------|--------------------|

| Project Manager, HDL Editor, Core Generation                                                                   | Libero SoC                 | Microsemi<br>SoC   |

| Synthesis                                                                                                      | Synplify® Pro ME           | Synopsys           |

| Simulation                                                                                                     | ModelSim® ME<br><b>Pro</b> | Mentor<br>Graphics |

| Timing/Constraints, Power Analysis, Netlist Viewer, Floorplanning, Package Editing, Place-and-Route, Debugging | Libero SoC                 | Microsemi<br>SoC   |

**Project Manager**, **HDL Editor** targets the creation of HDL code. HDL Editor supports VHDL and Verilog with color, highlighting keywords for both HDL languages.

**Synplify Pro ME** from Synopsys is integrated as part of the design package, enabling designers to target HDL code to specific devices.

Microsemi SoC software package includes:

- Chip Planner displays I/O and logic macros in your design for floorplanning

- Netlist Viewer design schematic viewer

- SmartPower power analysis tool

- SmartTime static timing analysis and constraints editor

ModelSim ME **Pro** from Mentor Graphics enables source level verification so designers can verify HDL code line by line. Designers can perform simulation at all levels: behavioral (or pre-synthesis), structural (or post-synthesis), dynamic simulation. (ModelSim **ME Pro** is supported in Libero Gold and Platinum only.)

## **Libero Design Flow**

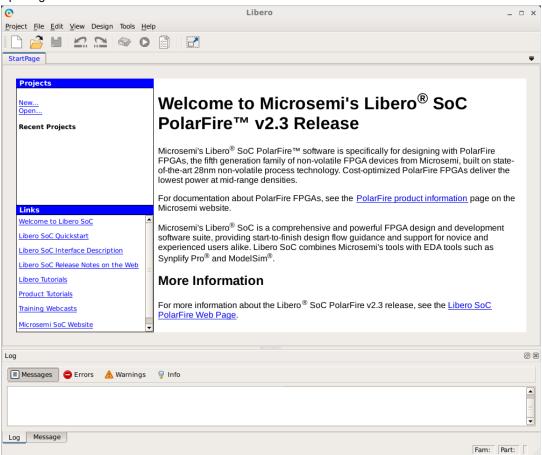

## Starting the Libero GUI

When starting Libero SoC GUI, the user will be presented with the option of either creating a new project, or opening an old one.

Figure 10 · Libero SoC Start-up GUI

- Clicking on Open ... opens a pre-existing Libero SoC project.

- Clicking on *New...* starts the <u>New Project Wizard</u>. Upon completion of the wizard, a new Libero SoC project is created and opened.

Having opened a project, the Libero SoC GUI presents a Design Flow window on the left hand side, a log and message window at the bottom, and project information windows on the right. Below we see the GUI of a newly created project with only the top level Design Flow Window steps visible.

Figure 11 · Design Flow Window

## **The Design Flow Window**

The Design Flow Window for each technology family may be slightly different. The Constraint Flow choice made during new project creation may also affect the exact elements of design flow. However, all flows include some version of the following design steps:

- Create

- Constrain

- Implement

- Configure Hardware

- Program Design

- Debug Design

- Handoff

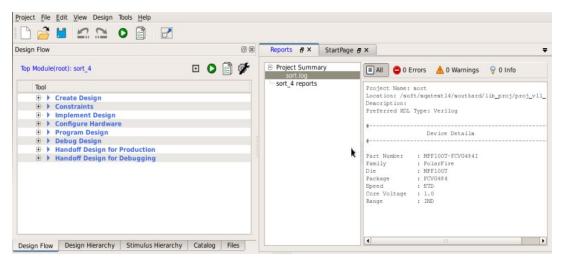

## **Design Report**

The Design Report Tab lists all the reports available for your design, and displays the selected report.

Reports are added automatically as you move through design development. For example, Timing reports are added when you run timing analysis on your design. The reports are updated each time you run timing analysis.

If the Report Tab is not visible, you can expose it at any time by clicking on the main menu item **Design > Reports**

If a report is not yet listed, you may have to create it manually. For example, you must invoke **Verify Power** manually before its report will be available.

Reports for the following steps are available for viewing here:

- Project Summary

- Synthesize

- Place and Route

- Verify Timing

- Verify Power

- Programming

- Generate FPGA Array Data

- Generate Bitstream

- Export

- Export Pin Report

• Export BSDL File

## Using the New Project Wizard to Start a Project

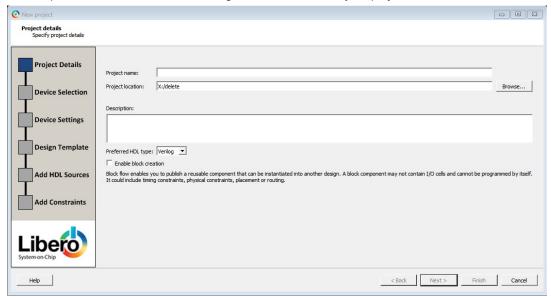

## **New Project Creation Wizard - Project Details**

You can create a Libero SoC project using the New Project Creation Wizard. You can use the pages in the wizard to:

- Specify the project name and location

- · Select the device family and parts

- Set the I/O standards

- Import HDL source files and/or design constraint files into your project

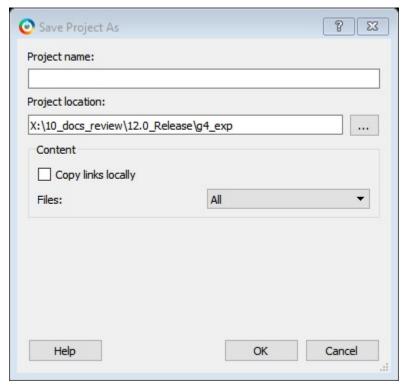

Figure 12 · Libero SoC New Project Creation Wizard

## **Project**

Project Name - Identifies your project name; do not use spaces or reserved Verilog or VHDL keywords.

Project Location – Identifies your project location on disk.

**Description** – General information about your design and project. The information entered appears in your Datasheet Report View.

**Preferred HDL type** - Sets your HDL type: Verilog or VHDL. Libero-generated files (SmartDesigns, SmartGen cores, etc.) are created in your specified HDL type. Libero SoC supports mixed-HDL designs.

**Enable Block Creation** - Enables you to build blocks for your design. These blocks can be assembled in other designs, and may have already completed Layout and been optimized for timing and power performance for a specific Microsemi device. Once optimized, the same block or blocks can be used in multiple designs.

When you are finished, click **Next** to proceed to the Device Selection page.

#### See Also

New Project Creation Wizard - Device Selection

New Project Creation Wizard - Device Settings

New Project Creation Wizard - Add HDL Source Files

New Project Creation Wizard - Add Constraints

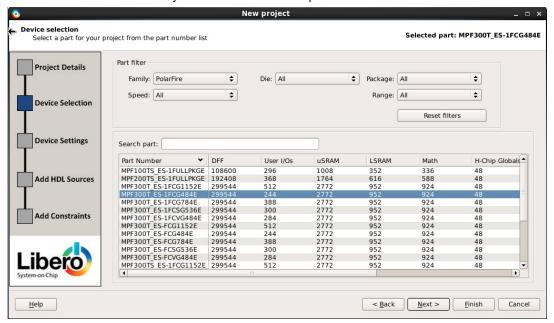

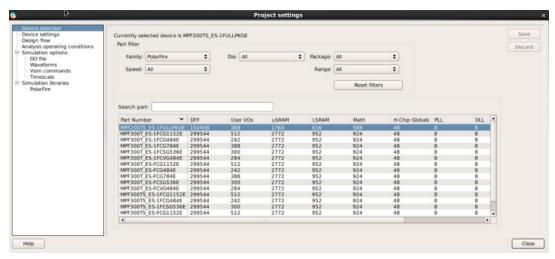

### **New Project Creation Wizard – Device Selection**

The Device Selection page is where you specify the Microsemi device for your project. Use the filters and drop-down lists to refine your search for the right part to use for your design.

This page contains a table of all parts with associated FPGA resource details generated as a result of a value entered in a filter.

When a value is selected for a filter:

- The parts table is updated to reflect the result of the new filtered value.

- All other filters are updated, and only relevant items are available in the filter drop-down lists.

For example, when PolarFire is selected in the Family filter:

- The parts table includes only PolarFire parts.

- The Die filter includes only PolarFire dies in the drop-down list for Die.

Figure 13 · New Project Creation Wizard - Device Selection Page

Family – Specify the Microsemi device family. Only devices belonging to the family are listed in the parts table.

**Die / Package / Speed** - Select your device die, package, and speed grade. Use the Die/Package/Speed filters to help in selection. The Die/Package/Speed grades available for selection depend on the level of Libero SoC license (Evaluation/Silver/Gold/Platinum) - refer to the <u>Libero SoC Licensing Web Page</u> for details.

**Range** - Define the voltage and temperature ranges a device may encounter in your application. Tools such as SmartTime, SmartPower, timing-driven layout, power-driven layout, the timing report, and back-annotated simulation are affected by operating conditions.

Supported ranges include:

- All All ranges

- EXT All parts that support operating temperature range from 0 to 100 degrees Celsius

- IND All parts that support operating temperature range from -40 to 100 degrees Celsius

Note: Supported operating condition ranges vary according to your device and package.

Refer to your device datasheet to find your recommended temperature range.

Reset Filters - Reset all filters to the default ALL option except Family.

Search Parts – Enter a character-by-character search for parts. Search results appear in the parts table.

When Device Selection is completed, click on:

- Next to proceed to the <u>Device Settings</u> page OR

- Finish to complete New Project Creation with all remaining defaults.

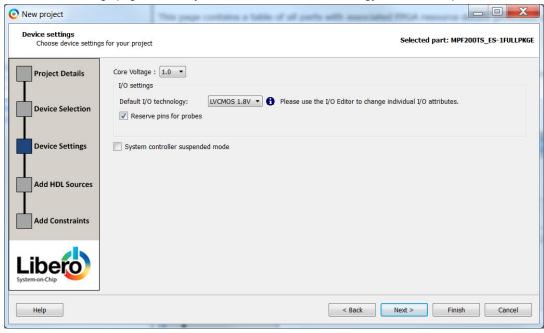

## **New Project Creation Wizard – Device Settings**

The Device Settings page is where you set the Device I/O Technology and Reserve pins for Probes.

Figure 14 · New Project Creation Wizard – Device Settings Page

Core Voltage - Set the core voltage for your device.

**Default I/O Technology** - Set all your I/Os to a default value. You can change the values for individual I/Os in the I/O Attribute Editor. The I/O Technology available is family-dependent.

Reserve Pins for Probes - Reserve your pins for probing if you intend to debug using SmartDebug.

When you are finished, click **Next** to proceed to the next page, or click **Finish** to complete New Project Creation with all remaining defaults.

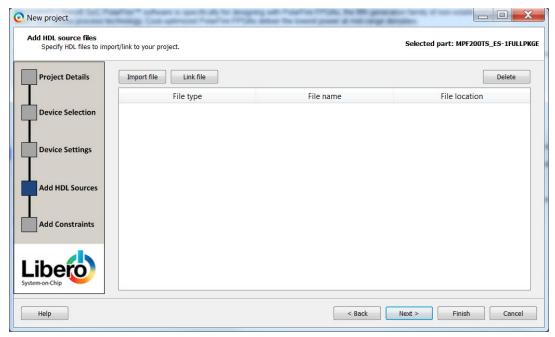

## **New Project Creation Wizard - Add HDL Source Files**

The Add HDL Source Files page is where you add HDL design source files to your Libero SoC project. The HDL source files can be imported or linked to the Libero SoC Project.

Figure 15 · New Project Creation Wizard - Add HDL Source Files Page

**Import File** – Navigate to the disk location of the HDL source. Select the HDL file and click **Open**. The HDL file is copied to the Libero Project in the <pri>pri\_folder>/hdl folder.

**Link File** – Navigate to the disk location of the HDL source. Select the HDL file and click **Open**. The HDL file is linked to the Libero Project. Use this option if the HDL source file is located and maintained outside of the Libero project.

**Delete** - Delete the selected HDL source file from your project. If the HDL source file is linked to the Libero project, the link will be removed.

When Add HDL Sources is completed, click on:

- Next to proceed to the <u>Add Constraints</u> page OR

- Finish to complete New Project Creation.

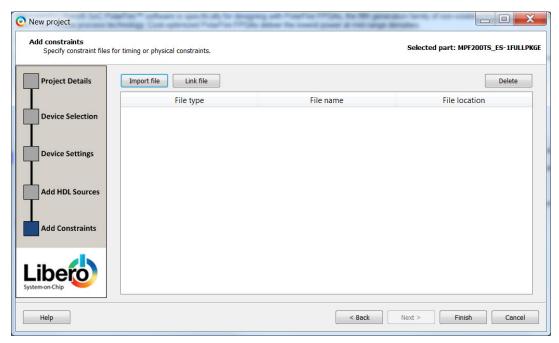

## **New Project Creation Wizard - Add Constraints**

The Add Constraints page is where you add Timing constraints and Physical Constraints files to your Libero SoC project. The constraints file can be imported or linked to the Libero SoC Project.

Figure 16 · New Project Creation Wizard - Add Constraints Page

**Import File** – Navigate to the disk location of the constraints file. Select the constraints file and click **Open**. The constraints file is copied to the Libero Project in the cprj\_folder>/constraint folder.

**Link File** – Navigate to the disk location of the constraints file. Select the constraints file and click **Open**. The constraints file is linked to the Libero Project. Use this option if the constraint file is located and maintained outside of the Libero project.

**Delete** - Remove the selected constraints file from your project. If the constraints file is linked to the Libero project, the link will be removed.

When Add Constraints is completed, click on:

• Finish to complete New Project Creation.

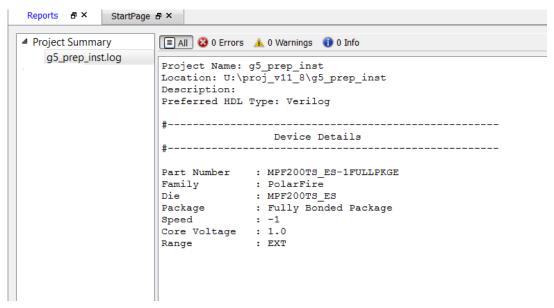

The **Reports** tab displays the result of the New Project creation.

Figure 17 · Reports Tab

## **Create and Verify Design**

Create your design with any or all of the following design capture tools:

- Create SmartDesign

- Create HDL

- <u>Create SmartDesign Testbench</u> (optional, for simulation only)

- Create HDL Testbench (optional, for simulation only)

## Create SmartDesign

## **About SmartDesign**

SmartDesign is a visual block-based design creation/entry tool for the instantiation, configuration and connection of Microsemi IPs, user-generated IPs, custom/glue-logic HDL modules. This tool provides a canvas for instantiating and stitching together design objects. The final result from SmartDesign is a design-rule-checked and automatically abstracted synthesis-ready HDL file. A generated SmartDesign can be the entire FPGA design or a component subsystem to be re-used in a larger design.

The following design objects can be instantiated in the SmartDesign Canvas:

- Microsemi IP Cores

- · User-generated or third-party IP Cores

- · HDL design files

- HDL + design files

- Basic macros

- Other SmartDesign components (\*.cxf files) generated from SmartDesign in the current Libero SoC project

or may be imported from other Libero SoC projects.

- Re-usable design blocks (\*.cxz files) published from Libero SoC

For more information see the **SmartDesign User Guide**.

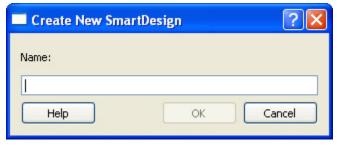

#### **Create New SmartDesign**

This SmartDesign component may be the top level of the design or it may be used as a lower level SmartDesign component (after successful generation) in another design.

From the File menu, choose New > SmartDesign or in the Design Flow window or double-click Create SmartDesign. The Create New SmartDesign dialog box opens.

Figure 18 · Create New SmartDesign Dialog Box

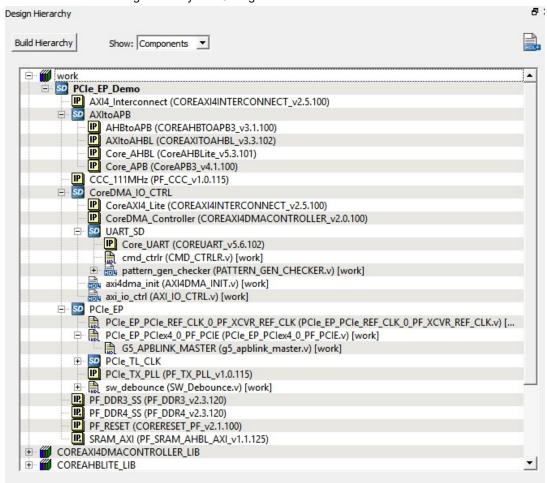

2. Enter a name and click OK. The component appears in the Design Hierarchy tab of the Design Explorer. **NOTE:** The component name you choose much be unique in your project

For more information see the **SmartDesign User Guide**.

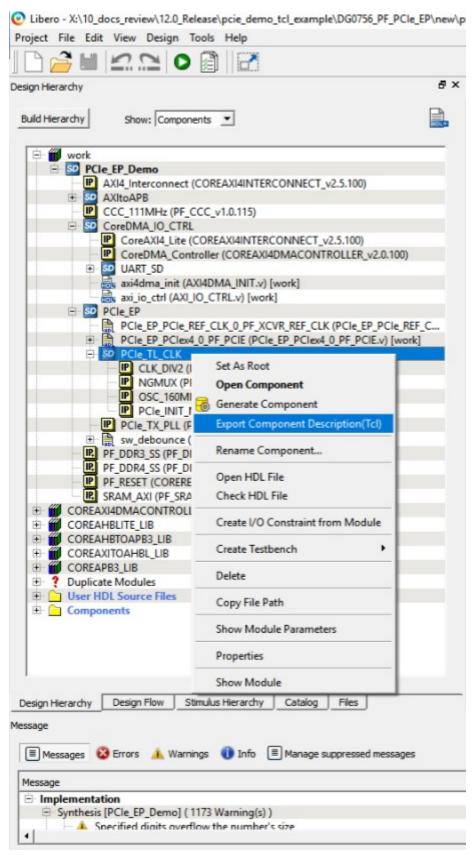

## **Export Component Description(Tcl)**

Components such as SmartDesign components, configured cores and HDL+ cores can be separately exported as Tcl with the Export Component Description option. To export a SmartDesign component, configured core or HDL+ core as Tcl, right click the component and choose "Export Component Description(Tcl)" option

Note: The Export Component Description(TcI) option is not supported for the SmartFusion2/IGLOO2 MSS component and the System Builder component.

Figure 19 · Export As TCL option for SmartDesign Component

Figure 20 · Export Script Dialog Box

Click the Browse button to specify the location where you wish to export the Tcl file and then click OK.

### **Examples**

#### Example exported Tcl script for a SmartDesign Component(PCle\_TL\_CLK)

```

# Creating SmartDesign PCIe TL CLK

set sd name { PCIe TL CLK}

create smartdesign -sd name ${sd name}

# Disable auto promotion of pins of type 'pad'

auto promote pad pins -promote all 0

# Create top level Ports

sd create scalar port -sd name ${sd name} -port name {CLK 125MHz} -port direction {IN}

sd create scalar port -sd name ${sd name} -port name {TL CLK} -port direction {OUT}

sd create scalar port -sd name ${sd name} -port name {DEVICE INIT DONE} -port direction

{OUT}

# Add CLK DIV2 0 instance

sd instantiate component -sd name ${sd name} -component name {CLK DIV2} -instance name

{CLK DIV2 0}

# Add NGMUX 0 instance

sd_instantiate_component -sd_name ${sd_name} -component_name {NGMUX} -instance_name

{NGMUX 0}

# Add OSC 160MHz 0 instance

sd instantiate component -sd name ${sd name} -component name {OSC 160MHz} -instance name

{OSC 160MHz 0}

# Add PCIe INIT MONITOR 0 instance

sd instantiate component -sd name ${sd name} -component name {PCIe INIT MONITOR} -

instance name {PCIe INIT MONITOR 0}

sd_mark_pins_unused -sd_name ${sd_name} -pin_names {PCIe_INIT_MONITOR 0:FABRIC POR N}

sd mark pins unused -sd name ${sd name} -pin names {PCIe INIT MONITOR 0:USRAM INIT DONE}

sd_mark_pins_unused -sd_name ${sd_name} -pin_names {PCIe_INIT_MONITOR_0:SRAM_INIT_DONE}

sd mark pins unused -sd name ${sd name} -pin names {PCIe INIT MONITOR 0:XCVR INIT DONE}

sd mark pins unused -sd name ${sd name} -pin names

{PCIe INIT MONITOR 0:USRAM INIT FROM SNVM DONE}

sd mark pins unused -sd name ${sd name} -pin names

{PCIe INIT MONITOR 0:USRAM INIT FROM UPROM DONE}

sd mark pins unused -sd name ${sd name} -pin names

{PCIe INIT MONITOR 0:USRAM INIT FROM SPI DONE}

sd mark pins unused -sd name ${sd name} -pin names

{PCIe INIT MONITOR 0:SRAM INIT FROM SNVM DONE}

sd mark pins unused -sd name ${sd name} -pin names

{PCIe INIT MONITOR 0:SRAM INIT FROM UPROM DONE}

sd mark pins unused -sd name ${sd name} -pin names

{PCIe INIT MONITOR 0:SRAM INIT FROM SPI DONE}

sd_mark_pins_unused -sd_name ${sd_name} -pin_names {PCIe_INIT_MONITOR 0:AUTOCALIB DONE}

# Add scalar net connections

```

```

sd_connect_pins -sd_name ${sd_name} -pin_names {"NGMUX_0:CLK1" "CLK_125MHz" }

sd_connect_pins -sd_name ${sd_name} -pin_names {"CLK_DIV2_0:CLK_OUT" "NGMUX 0:CLK0" }

sd connect pins -sd name ${sd name} -pin names {"PCIe INIT MONITOR 0:DEVICE INIT DONE"

"DEVICE_INIT_DONE" }

sd connect pins -sd name ${sd name} -pin names {"CLK DIV2 0:CLK IN"

"OSC 160MHz 0:RCOSC 160MHZ CLK DIV" }

sd connect pins -sd name ${sd name} -pin names {"NGMUX 0:SEL"

"PCIe INIT MONITOR 0:PCIE INIT DONE" }

sd connect pins -sd name ${sd name} -pin names {"NGMUX 0:CLK OUT" "TL CLK" }

# Re-enable auto promotion of pins of type 'pad'

auto_promote_pad_pins -promote_all 1

# Save the smartDesign

save smartdesign -sd name ${sd name}

# Generate SmartDesign PCIe_TL_CLK

generate component -component name ${sd name}

Example exported Tcl script for a System Builder Core(PF DDR3 SS).

# Exporting core PF DDR3 SS to TCL

# Create design TCL command for core PF DDR3 SS

create and configure core -core vlnv {Actel:SystemBuilder:PF DDR3:2.3.120} -

component name {PF DDR3 SS} -params {\

"ADDRESS MIRROR: false" \

"ADDRESS_ORDERING:CHIP_ROW_BANK_COL" \

"AUTO SELF REFRESH:1" \

"AXI ID WIDTH:6" \

"AXI WIDTH:64" \

"BANKSTATMODULES:4" \

"BANK ADDR WIDTH:3" \

"BURST LENGTH:0" \

"CAS ADDITIVE LATENCY:0" \

"CAS LATENCY:9" \

"CAS WRITE LATENCY:7" \

"CCC PLL CLOCK MULTIPLIER:6" \

"CLOCK DDR:666.666" \

"CLOCK PLL REFERENCE:111.111" \

"CLOCK RATE:4" \

"CLOCK USER:166.6665" \

"COL ADDR WIDTH:11" \

"DLL ENABLE:1" \

"DM MODE:DM" \

"DQ DQS GROUP SIZE:8" \

"ENABLE ECC:0" \

"ENABLE INIT INTERFACE: false" \

"ENABLE LOOKAHEAD PRECHARGE ACTIVATE: false" \

"ENABLE PAR ALERT:false" \

"ENABLE REINIT:false" \

"ENABLE TAG IF:false" \

"ENABLE USER ZQCALIB:false" \

"EXPOSE TRAINING DEBUG IF:false" \

"FABRIC INTERFACE: AXI4" \

"FAMILY:26" \

"MEMCTRLR INST NO:1" \

"MEMORY FORMAT: COMPONENT" \

```

```

"MINIMUM READ IDLE:1" \

"ODT ENABLE RD RNK0 ODT0:false" \

"ODT ENABLE RD RNK0 ODT1:false" \

"ODT_ENABLE_RD_RNK1_ODT0:false" \

"ODT ENABLE RD RNK1 ODT1:false" \

"ODT ENABLE WR RNK0 ODT0:true" \

"ODT ENABLE WR RNK0 ODT1:false" \

"ODT_ENABLE_WR_RNK1_ODT0:false" \

"ODT ENABLE WR RNK1 ODT1:true" \

"ODT RD OFF SHIFT:0" \

"ODT RD ON SHIFT:0" \

"ODT_WR_OFF_SHIFT:0" \

"ODT WR ON SHIFT:0" \

"OUTPUT DRIVE STRENGTH:RZQ6" \

"PARAM IS FALSE:false" \

"PARTIAL ARRAY SELF REFRESH: FULL" \

"PHYONLY:false" \

"PIPELINE:false" \

"QOFF:0" \

"QUEUE DEPTH:3" \

"RDIMM LAT:0" \

"READ BURST TYPE:SEQUENTIAL" \

"ROW ADDR WIDTH:16" \

"RTT NOM:DISABLED" \

"RTT WR:OFF" \

"SDRAM NB RANKS:1" \

"SDRAM NUM CLK OUTS:1" \

"SDRAM TYPE:DDR3" \

"SELF REFRESH TEMPERATURE:NORMAL" \

"SHIELD ENABLED:true" \

"SIMULATION MODE: FAST" \

"TDQS ENABLE: DISABLE" \

"TGIGEN ADD PRESET WIDGET:true" \

"TIMING DH:150" \

"TIMING DQSCK:400" \

"TIMING DQSQ:200" \

"TIMING DQSS:0.25" \

"TIMING_DS:75" \

"TIMING DSH:0.2" \

"TIMING DSS:0.2" \

"TIMING FAW:30" \

"TIMING IH:275" \

"TIMING INIT:200" \

"TIMING IS:200" \

"TIMING MODE:0" \

"TIMING MRD:4" \

"TIMING QH:0.38" \

"TIMING QSH:0.38" \

"TIMING RAS:36" \

"TIMING RC:49.5" \

"TIMING RCD:13.5" \

"TIMING REFI:7.8" \

```

```

"TIMING RFC:350" \

"TIMING RP:13.5" \

"TIMING RRD:7.5" \

"TIMING RTP:7.5" \

"TIMING WR:15" \

"TIMING WTR:5" \

"TURNAROUND RTR DIFFRANK:1" \

"TURNAROUND RTW DIFFRANK:1" \

"TURNAROUND WTR DIFFRANK:1" \

"TURNAROUND WTW DIFFRANK:0" \

"USER POWER DOWN:false" \

"USER SELF REFRESH:false" \

"WIDTH:16" \

"WRITE LEVELING: ENABLE" \

"WRITE RECOVERY:5" \

"ZQ CALIB PERIOD:200" \

"ZO CALIB TYPE:0" \

"ZQ CALIB TYPE TEMP:0" \

"ZQ CAL INIT TIME:512" \

"ZQ CAL L TIME:256" \

"ZQ CAL S TIME:64" } -inhibit configurator 0

# Exporting core PF_DDR3_SS to TCL done

Example exported Tcl script for a HDL+ core

# Exporting core pattern gen checker to TCL

# Exporting Create HDL core command for module pattern gen checker

create hdl core -file

{X:/10 docs review/12.0 Release/pcie demo tcl example/DG0756 PF PCIe EP/new/project/hdl/

PATTERN_GEN_CHECKER.v} -module {pattern_gen_checker} -library {work} -package {}

# Exporting BIF information of HDL core command for module pattern gen checker

Example exported Tcl script for a SgCore(PF TX PLL)

# Exporting core PCIe TX PLL to TCL

# Exporting Create design command for core PCIe TX PLL

create and configure core -core vlnv {Actel:SgCore:PF TX PLL:1.0.115} -component name

{PCIe_TX_PLL} -params {\

"CORE:PF TX PLL" \

"FAMILY:26" \

"INIT:0x0" \

"PARAM IS FALSE:false" \

"SD EXPORT HIDDEN PORTS:false" \

"TxPLL AUX LOW SEL:true" \

"TxPLL AUX OUT:125" \

"TxPLL CLK 125 EN:true" \

"TxPLL DYNAMIC RECONFIG INTERFACE EN:false" \

"TxPLL EXT WAVE SEL:0" \

"TxPLL_FAB_LOCK_EN:false" \

"TxPLL FAB REF:200" \

"TxPLL JITTER MODE SEL:10G SyncE 32Bit" \

"TxPLL MODE:NORMAL" \

"TxPLL_OUT:2500.000" \

"TxPLL REF:100" \

"TxPLL SOURCE:DEDICATED" \

"TxPLL SSM DEPTH:0" \

```

```

"TxPLL_SSM_DIVVAL:1" \

"TxPLL_SSM_DOWN_SPREAD:false" \

"TxPLL_SSM_FREQ:64" \

"TxPLL_SSM_RAND_PATTERN:0" \

"VCOFREQUENCY:1600" } -inhibit_configurator 1

# Exporting core PCIe TX PLL to TCL done

```

## **Generating a SmartDesign Component**

Before your SmartDesign component can be used by downstream processes, such as synthesis and simulation, you must generate it.

Click the Generate button to generate a SmartDesign component

Note: The generated HDL file will be deleted when your SmartDesign design is modified and saved to ensure synchronization between your SmartDesign component and its generated HDL file.

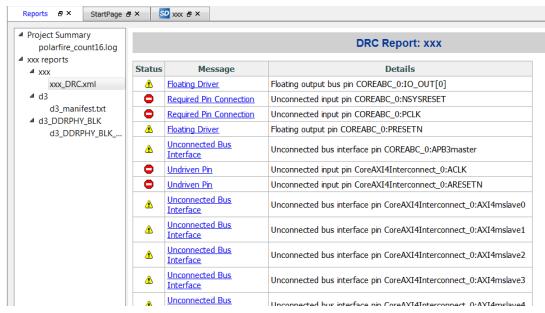

Generating a SmartDesign component may fail if there are any <u>DRC errors</u>. DRC errors must be corrected before you generate your SmartDesign design.

If the ports of a sub-design have changed, then the parent SmartDesign component will be annotated with the icon in the Design Hierarchy tab of the Design Explorer.

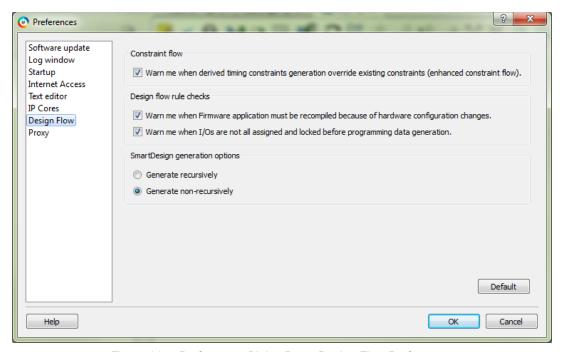

### Generate Recursively vs. Non-Recursively

These options are set in the Project Preference Dialog Box - Design Flow Preferences section.

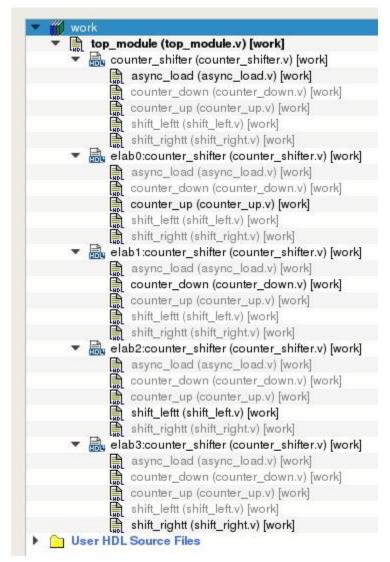

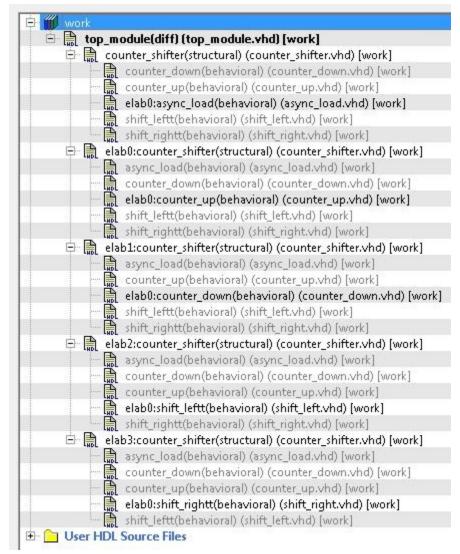

- In the "Recursive generation" mode, the **Generate** button will attempt to generate all sub-design SmartDesigns, depth first. The parent SmartDesign will only be generated if all the sub-designs are generated successfully.

- In the "Non-Recursive generation" mode, the **Generate** button will only attempt to generate the specified SmartDesign. The generation can be marked as successful even if a sub-design is un-generated (either never attempted or unsuccessful). An un-generated component will be annotated with the icon in the Design Hierarchy tab of the Design Explorer.

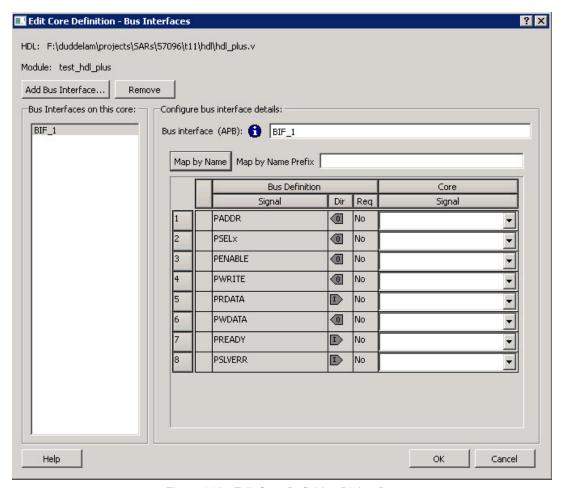

# Create Core from HDL

You can instantiate any HDL module and connect it to other blocks inside SmartDesign. However, there are situations where you may want to extend your HDL module with more information before using it inside SmartDesign.

- If you have an HDL module that contains configurable parameters or generics.

- If your HDL module is intended to connect to a processor subsystem and has implemented the appropriate bus protocol, then you can add a bus interface to your HDL module so that it can easily connect to the bus inside of SmartDesign.

## To create a core from your HDL:

- 1. Import or create a new HDL source file; the HDL file appears in the Design Hierarchy.

- Select the HDL file in the Design Hierarchy and click the HDL+ icon or right-click the HDL file and choose Create Core from HDL.

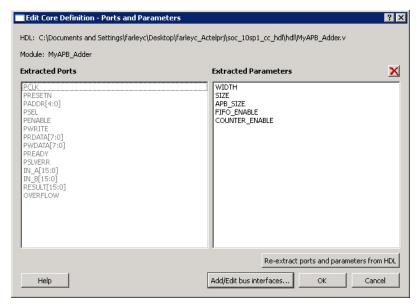

- The **Edit Core Definition Ports and Parameters** dialog appears. It shows you which ports and parameters were extracted from your HDL module.

- 3. Remove parameters that are not intended to be configurable by selecting them from the list and clicking the X icon. Remove parameters that are used for internal variables, such as state machine enumerations. If you removed a parameter by accident, click **Re-extract ports and parameters from HDL file** to reset the list so it matches your HDL module.

Figure 21 · Edit Core Definition - Ports and Parameters Dialog Box

4. (Optional) Click **Add/Edit Bus Interfaces** to <u>add bus interfaces</u> to your core.

After you have specified the information, your HDL turns into an HDL+ icon in the Design Hierarchy. Click and drag your HDL+ module from the Design Hierarchy to the **Canvas**.

If you added bus interfaces to your HDL+ core, then it will show up in your SmartDesign with a bus interface pin that can be used to easily connect to the appropriate bus IP core.

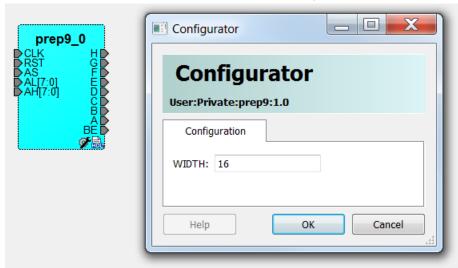

If your HDL+ has configurable parameters then double-clicking the object on the Canvas (or right-click and select **Configure**) invokes a configuration dialog that enables you to set these values. On generation, the specific configuration values per instance are written out to the SmartDesign netlist.

Figure 22 · HDL+ Instance and Configuration Dialog Box

You can right-click the instance and choose Modify HDL to open the HDL file inside the text editor.

## **Edit Core Definition**

You can edit your core definition after you created it by selecting your HDL+ module in the design hierarchy and clicking the HDL+ icon.

### **Remove Core Definition**

You may decide that you do not want or need the extended information on your HDL module. You can convert it back to a regular HDL module. To do so, right-click the HDL+ in the Design Hierarchy and choose **Remove Core Definition**. After removing your definition, your instances in your SmartDesign that were referencing this core must be updated. Right-click the instance and choose **Replace Component for Instance**.

# Designing with HDL

#### **Create HDL**

Create HDL opens the HDL editor with a new VHDL or Verilog file. Your new HDL file is saved to your /hdl directory; all modules created in the file appear in the Design Hierarchy.

You can use VHDL and Verilog to implement your design.

#### To create an HDL file:

- 1. In the Design Flow window, double-click Create HDL. The Create new HDL file dialog box opens.

- Select your HDL Type. Choose whether or not to Initialize file with standard template to populate your file with default headers and footers. The HDL Editor workspace opens.

- 3. Enter a **Name**. Do not enter a file extension; Libero SoC adds one for you. The filename must follow Verilog or VHDL file naming conventions.

- 4. Click OK.

After creating your HDL file, click the Save button to save your file to the project.

## **Using the HDL Editor**

The HDL Editor is a text editor designed for editing HDL source files. In addition to regular editing features, the editor provides keyword highlighting, line numbering and a syntax checker.

You can have multiple files open at one time in the HDL Editor workspace. Click the tabs to move between files.

#### Editing

Right-click inside the HDL Editor to open the Edit menu items. Available editing functions include cut, copy, paste, Go to line, Comment/Uncomment Selection and Check HDL File. These features are also available in the toolbar.

#### Saving

You must save your file to add it to your Libero SoC project. Select **Save** in the File menu, or click the **Save** icon in the toolbar.

#### **Printing**

**Print** is available from the File menu and the toolbar.

Note: To avoid conflicts between changes made in your HDL files, Microsemi recommends that you use one editor for all of your HDL edits.

### **HDL Syntax Checker**

#### To run the syntax checker:

In the **Files** list, double-click the HDL file to open it. Right-click in the body of the HDL editor and choose **Check HDL File**.

The syntax checker parses the selected HDL file and looks for typographical mistakes and syntactical errors. Warning and error messages for the HDL file appear in the Libero SoC Log Window.

## **Commenting Text**

You can comment text as you type in the HDL Editor, or you can comment out blocks of text by selecting a group of text and applying the Comment command.

#### To comment or uncomment out text:

- 1. Type your text.

- Select the text.

- 3. Right-click inside the editor and choose Comment Selection or Uncomment Selection.

#### Find

In the File menu, choose **Find** and the Find dialog box appears below the Log/Message window. You can search for a whole word or part of a word, with or without matching the case.

You can search for:

- Match Case

- · Match whole word

- · Regular Expression

The Find to Replace function is also supported.

## **Column Editing**

Column Editing is supported. Press ALT+click to select a column of text to edit.

## **Importing HDL Source Files**

#### To import an HDL source file:

- In the Design Flow window, right-click Create HDL and choose Import Files. The Import Files window appears.

- 2. Navigate to the drive/folder that contains the HDL file.

- 3. Select the file to import and click Open.

Note: SystemVerilog (\*.sv), Verilog (\*.v) and VHDL (\*.vhd/\*.vhdl) files can be imported.

## Mixed-HDL Support in Libero SoC

You must have ModelSim **ME Pro** to use mixed HDL in the Libero SoC. You must also have Synplify Pro to synthesize a mixed-HDL design.

When you <u>create a project</u>, you must select a preferred language. The HDL files generated in the flow are created in the preferred language.

The language used for simulation is the same language as the last compiled testbench. (For example, if tb\_top is in Verilog, <fam>.v is compiled.)

If your preferred language is Verilog, the post-synthesis and post-layout netlists are in Verilog 2001.

# Designing with Block Flow

For information about designing with Block Flow, see <u>Designing with Blocks for Libero SoC Enhanced Constraint Flow</u>.

# Create New SmartDesign Testbench

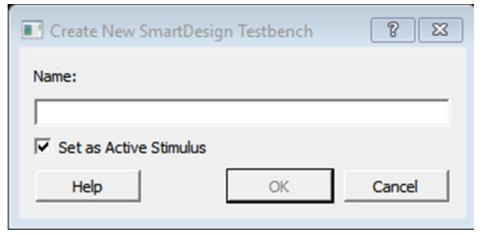

The SmartDesign Testbench component may be the top level of the design or it may be used as a lower level SmartDesign Testbench component (after successful generation) in another design.

1. From the File menu, choose **New > SmartDesign Testbench**, or in the Design Flow window double-click **Create SmartDesign Testbench**. The Create New SmartDesign Testbench dialog box opens.

Figure 23 · Create New SmartDesign Testbench

Enter a name, select the Set as Active Stimulus radio button if you want have this SmartDesign Testbench

as your active stimulus, and click OK. The component appears in the Stimulus Hierarchy tab of the Design

Explorer.

Note: The component name you choose much be unique in your project.

For more information see the **SmartDesign User Guide**.

# **HDL** Testbench

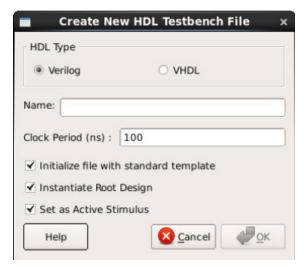

You can create a HDL Testbench by right-clicking a SmartDesign in the Design Hierarchy and choosing **Create Testbench > HDL**.

HDL Testbench automatically instantiates the selected SmartDesign into the Component.

You can also double-click **Create HDL Testbench** to open the Create New HDL Testbench dialog box. The dialog box enables you to create a new testbench file and gives you the option to include standard testbench content and your design data.

## **HDL Type**

Set your HDL Type: Verilog or VHDL for the testbench.

#### Name

Specify a testbench file name. A \*.v or a \*.vhd file is created and opened in the HDL Editor.

## **Clock Period (ns)**

Enter a clock period in nanoseconds (ns) for the clock to drive the simulation. The default value is 100 ns (10 MHz). Libero creates in the testbench a SYSCLK signal with the specified frequency to drive the simulation.

**Set as Active Stimulus** sets the HDL Testbench as the stimulus file to use for simulations. The active stimulus file/testbench is included in the run.do file that Libero generates to drive the simulation. Setting one testbench as the Active Stimulus is necessary when there are multiple testbenches in the stimulus hierarchy.

**Initialize with Standard Template** adds boilerplate for a minimal standard test module. This test module does not include an instantiation of the root module under test.

**Instantiate Root Design** Creates a test module that includes an instance of the root module under test, and clocking logic in the test module which drives the base clock of the root module under test.

Figure 24 · Create New HDL Testbench File Dialog Box

```

Created by Microsemi SmartDesign Mon Mar 27 15:07:29 2017

Testbench Template

This is a basic testbench that instantiates your design with basic

5

clock and reset pins connected. If your design has special

-- clock/reset or testbench driver requirements then you should

6

-- copy this file and modify it.

8

10 -

11

-- Company: <Name>

12

13

-- File: counter_tb.vhd

-- File history:

<Revision number>: <Date>: <Comments>

16

<Revision number>: <Date>: <Comments>

17

<Revision number>: <Date>: <Comments>

18

19

-- Description:

20

21

22

-- <Description here>

23

-- Targeted device: <Family::PolarFire> <Die::MPF200TS_ES> <Package::Fully Bonded Package>

24

-- Author: <Name>

25

26

27

28

29

library ieee;

30

use ieee.std_logic_1164.all;

31

32 mentity counter_tb is

33

end counter_tb;

35 Farchitecture behavioral of counter_tb is

36

37

constant SYSCLK_PERIOD : time := 100 ns; -- 10MHZ

38

39

signal SYSCLK : std_logic := '0';

40

signal NSYSRESET : std_logic := '0';

42 E

```

Figure 25 · HDL Testbench Example - VHDL, Standard Template and Root Design Enabled

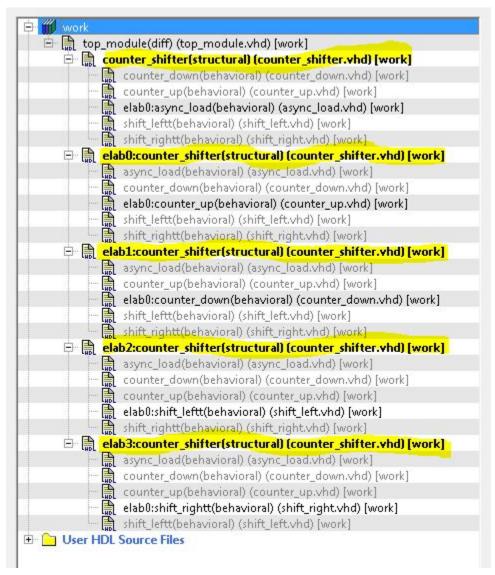

# Verify Pre-Synthesized Design - RTL Simulation

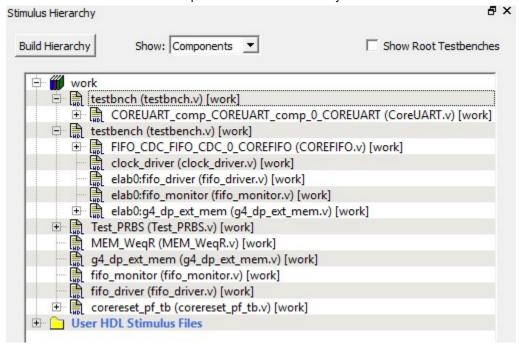

To perform pre-synthesis simulation, double-click **Simulate** under Verify Pre-Synthesized Design in the Design Flow window. Alternatively, in the Stimulus Hierarchy right-click the testbench and choose **Simulate Pre-Synth Design > Run**.

The default tool for RTL simulation in Libero SoC **PolarFire** is ModelSim ME Pro. ModelSim ME works with all levels of Libero SoC license (Eval, Silver, Gold and Platinum) whereas ModelSim Pro ME works with all levels of Libero SoC license except Silver.

ModelSim ME and ModelSim ME Pro are custom editions of ModelSim PE that are integrated into Libero SoC's design environment. ModelSim for Microsemi is an OEM edition of Mentor Graphics ModelSim tools. ModelSim ME Pro supports mixed VHDL, Verilog, and SystemVerilog simulation but ModelSim ME does not. Both ModelSim editions only work with Microsemi simulation libraries and they are supported by Microsemi.

Other editions of ModelSim are supported by Libero SoC. To use other editions of ModelSim, do not install ModelSim ME from the Libero SoC media.

Note: ModelSim for Microsemi includes online help and documentation. After starting ModelSim, click the *Help* menu.

See the following topics for more information on simulation in Libero SoC:

- Simulation Options

- Selecting a Stimulus File for Simulation

- Selecting additional modules for simulation

- · Performing Functional Simulation

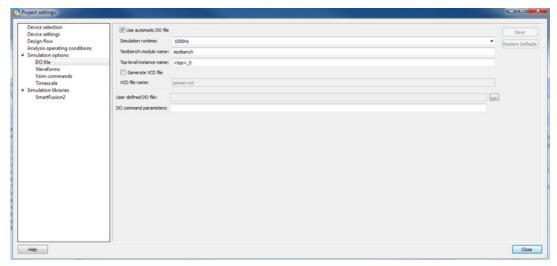

## **Project Settings: Simulation - Options and Libraries**

Using this dialog box, you can set change how Libero SoC handles Do files in simulation, import your own Do files, set simulation run time, and change the DUT name used in your simulation. You can also change your library mapping.

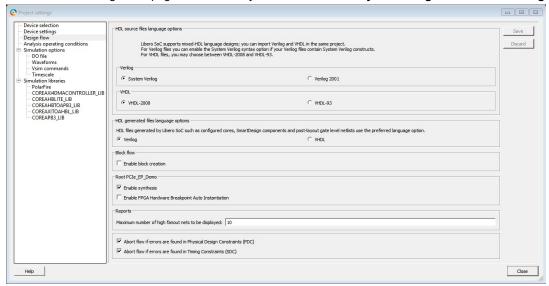

To access this dialog box, from the **Project** menu choose **Project Settings** and click to expand **Simulation options** or **Simulation libraries**.

For **Simulation options** click the option you wish to edit: **DO file**, **Waveforms**, **Vsim commands**, **Timescale**. For **Simulation libraries** click on the library you wish to change the path for.

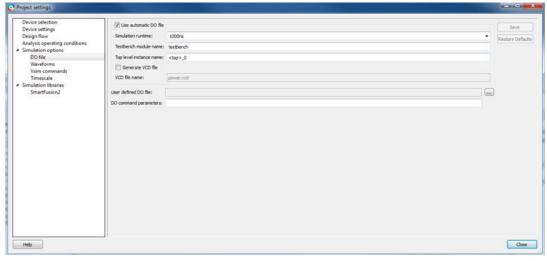

Figure 26 · Project Settings: DO File

#### DO file

- Use automatic DO file Select if you want the Project Manager to automatically create a DO file that will enable you to simulate your design.

- **Simulation Run Time** Specify how long the simulation should run. If the value is 0, or if the field is empty, there will not be a run command included in the run.do file.

- **Testbench module name** Specify the name of your testbench entity name. Default is "testbench," the value used by WaveFormer Pro.

- **Top Level instance name -** Default is <top\_0>, the value used by WaveFormer Pro. The Project Manager replaces <top> with the actual top level macro when you run simulation (presynth/postsynth/postlayout).

- Generate VCD file Click the checkbox to generate a VCD file.

- VCD file name Specifies the name of your generated VCD file. The default is power.vcd; click power.vcd and type to change the name.

- User defined DO file Enter the DO file name or click the browse button to navigate to it.

- DO command parameters Text in this field is added to the DO command.

#### Waveforms

- Include DO file Including a DO file enables you to customize the set of signal waveforms that will be displayed in ModelSim.

- Display waveforms for You can display signal waveforms for either the top-level testbench or for the

design under test. If you select top-level testbench then Project Manager outputs the line 'add wave

/testbench/\*' in the DO file run.do. If you select DUT then Project Manager outputs the line 'add wave

/testbench/DUT/\*' in the run.do file.

- Log all signals in the design Saves and logs all signals during simulation.

#### Vsim Commands

- **Resolution The default is 1ps.**Some custom simulation resolutions may not work with your simulation library. Consult your simulation help for more information on how to work with your simulation library and detect infinite zero-delay loops caused by high resolution values.

- Additional options Text entered in this field is added to the vsim command.

- SRAM ECC Simulation -

- Two options can be added to specify the simulated error and correction probabilities of all ECC SRAMs in the design.

- -gERROR\_PROBABILITY=<value>, where 0 <= value <= 1</li>

- -gCORRECTION\_PROBABILITY=<value>, where 0 <= value <= 1</li>

- During Simulation, the SB\_CORRECT and DB\_DETECT flags on each SRAM block will be raised based on generated random numbers being below the specified <value>s.

### **Timescale**

- **TimeUnit** Enter a value and select s, ms, us, ns, ps, or fs from the pull-down list, which is the time base for each unit. The default setting is ns.

- Precision Enter a value and select s, ms, us, ns, ps, or fs from the pull-down list. The default setting is ps.

## **Simulation Libraries**

- Restore Defaults- Sets the library path to default from your Libero SoC installation.

- **Library path** Enables you to change the mapping for your simulation library (both Verilog and VHDL). Type the pathname or click the Browse button to navigate to your library directory.

## Selecting a Stimulus File for Simulation

Before running simulation, you must associate a testbench. If you attempt to run simulation without an associated testbench, the Libero SoC Project Manager asks you to associate a testbench or open Model *Sim* without a testbench.

#### To associate a stimulus:

1. Run simulation or in the Design Flow window under Verify Pre-Synthesized Design right-click **Simulate** and choose **Organize Input Files > Organize Stimulus Files**. The Organize Stimulus Files dialog box appears.

2. Associate your testbench(es):

In the Organize Stimulus Files dialog box, all the stimulus files in the current project appear in the Source Files in the Project list box. Files already associated with the block appear in the Associated Source Files list box.

In most cases you will only have one testbench associated with your block. However, if you want simultaneous association of multiple testbench files for one simulation session, as in the case of PCI cores, add multiple files to the Associated Source Files list.

- To add a testbench: Select the testbench you want to associate with the block in the Source Files in the Project list box and click Add to add it to the Associated Source Files list.

- To remove a testbench: To remove or change the file(s) in the Associated Source Files list box, select the file(s) and click **Remove**.

- To order testbenches: Use the up and down arrows to define the order you want the testbenches compiled. The top level-entity should be at the bottom of the list.

- 3. When you are satisfied with the Associated Source Files list, click OK.

## **Selecting Additional Modules for Simulation**

Libero SoC passes all the source files related to the top-level module to simulation.

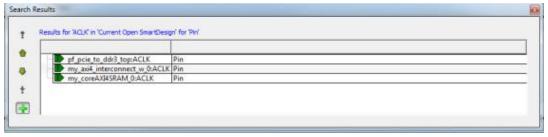

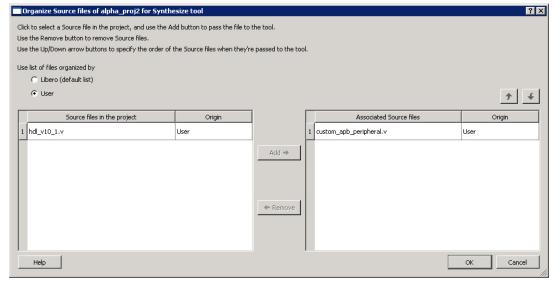

If you need additional modules in simulation, in the Design Flow window right-click **Simulate** and choose **Organize Input Files > Organize Source Files**. The Organize Files for Simulation dialog box appears.

Select the HDL modules you wish to add from the Simulation Files in the Project list and click **Add** to add them to the Associated Stimulus Files list

# **Performing Functional Simulation**

#### To perform functional simulation:

- 1. Create your testbench.

- Right-click Simulate (in the Design Flow window, Implement Design > Verify Post-Synthesis Implementation > Simulate) and choose Organize Input Files > Organize Simulation Files from the right-click menu.

In the Organize Files for Source dialog box, all the stimulus files in the current project appear in the Source Files in the Project list box. Files already associated with the block appear in the Associated Source Files list box.

In most cases you will only have one testbench associated with your block. However, if you want simultaneous association of multiple testbench files for one simulation session, as in the case of PCI cores, add multiple files to the Associated Source Files list.

- To add a testbench: Select the testbench you want to associate with the block in the Source Files in the Project list box and click Add to add it to the Associated Source Files list.

- To remove a testbench: To remove or change the file(s) in the Associated Source Files list box, select the file(s) and click **Remove**.

- 3. When you are satisfied with the Associated Simulation Files list, click **OK**.

- To start ModelSim ME Pro, right-click Simulate in the Design Hierarchy window and choose Open Interactively.

- ModelSim starts and compiles the appropriate source files. When the compilation completes, the simulator runs for 1 and the Wave window opens to display the simulation results.

- 5. Scroll in the Wave window to verify that the logic of your design functions as intended. Use the zoom buttons to zoom in and out as necessary.

- 6. From the File menu, select Quit.

# **Libero SoC Constraint Management**

In the FPGA design world, constraint files are as important as design source files. Constraint files are used throughout the FPGA design process to guide FPGA tools to achieve the timing and power requirements of the design. For the synthesis step, SDC timing constraints set the performance goals whereas non-timing FDC constraints guide the synthesis tool for optimization. For the Place-and-Route step, SDC timing constraints guide the tool to achieve the timing requirements whereas Physical Design Constraints (PDC) guide the tool for optimized placement and routing (Floorplanning). For Static Timing Analysis, SDC timing constraints set the timing requirements and design-specific timing exceptions for static timing analysis.

Libero SoC provides the Constraint Manager as the cockpit to manage your design constraint needs. This is a single centralized graphical interface for you to create, import, link, check, delete, edit design constraints and associate the constraint files to design tools in the Libero SoC environment. The Constraint Manager allows you to manage constraints for SynplifyPro synthesis, Libero SoC Place-and- Route and the SmartTime Timing Analysis throughout the design process.

# Invocation of Constraint Manager From the Design Flow Window

After project creation, double-click **Manage Constraints** in the Design Flow window to open the Constraint Manager.

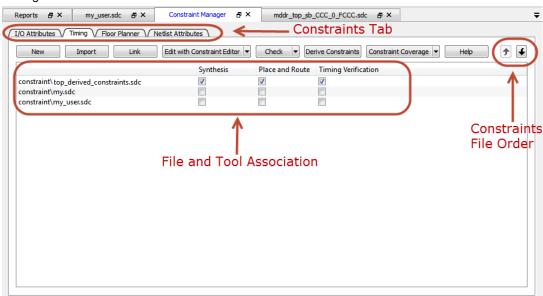

Figure 27 · Constraint Manager

# Libero SoC Design Flow

The Constraint Manager is Libero SoC's single centralized Graphical User Interface for managing constraints files in the design flow.

Figure 28 · Constraint Manager in Libero SoC Design Flow

# Introduction to Constraint Manager

# **Synthesis Constraints**

The Constraint Manager manages these synthesis constraints and passes them to SynplifyPro:

- Synplify Netlist Constraint File (\*.fdc)

- Compile Netlist Constraint File (\*.ndc)

- SDC Timing Constraints (\*.sdc)

• Derived Timing Constraints (\*.sdc)

## **Synplify Netlist Constraints (\*.fdc)**

These are non-timing constraints that help SynplifyPro optimize the netlist. From the Constraint Manager Netlist Attribute tab import (Netlist Attributes > Import) an existing FDC file or create a new FDC file in the Text Editor (Netlist Attributes > New > Create New Synplify Netlist Constraint). After the FDC file is created or imported, click the checkbox under synthesis to associate the FDC file with Synthesis.

## **Compile Netlist Constraints (\*.ndc)**

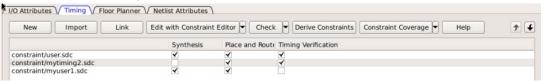

These are non-timing constraints that help Libero SoC optimize the netlist by combining I/Os with registers. I/Os are combined with a register to achieve better clock-to-out or input-to-clock timing. From the Constraint Manager Netlist Attribute tab import (Netlist Attributes > Import) an existing NDC file or create a new NDC file in the Text Editor (Netlist Attributes > New > Create New Compile Netlist Constraint). After the NDC file is created or imported, click the checkbox under synthesis to associate the NDC file with Synthesis.

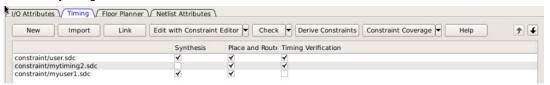

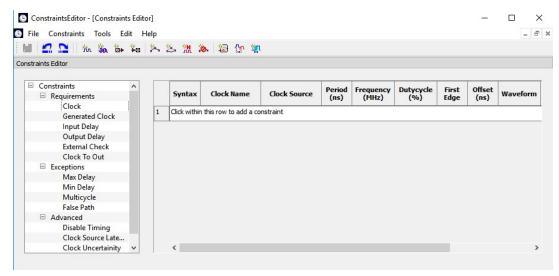

# **SDC Timing Constraints (\*.sdc)**

These are timing constraints to guide SynplifyPro to optimize the netlist to meet the timing requirements of the design. From the Constraint Manager Timing tab, import (**Timing > Import**) or create in the Text Editor (**Timing > New**) a new SDC file. After the SDC file is created or imported, click the checkbox under synthesis to associate the SDC file with Synthesis.

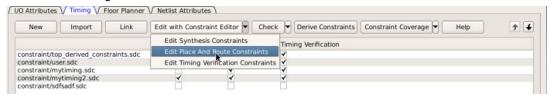

After the synthesis step, you may click **Edit with Constraint Editor > Edit Synthesis Constraints** to edit existing constraints or add new SDC constraints.

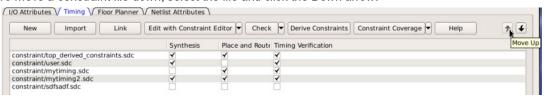

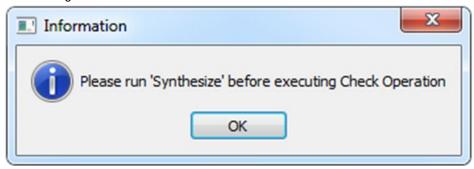

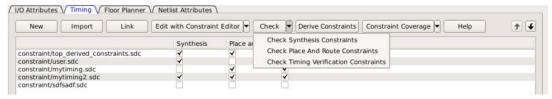

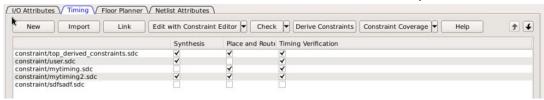

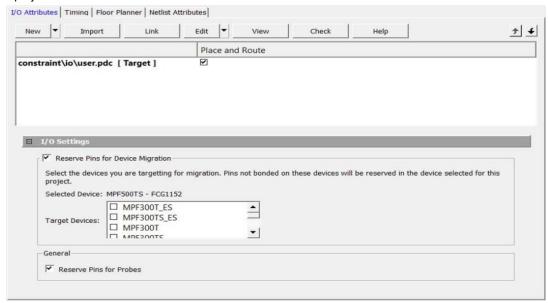

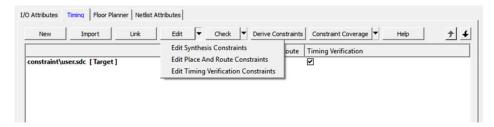

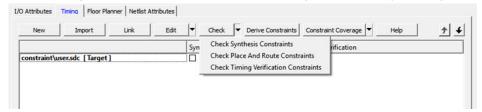

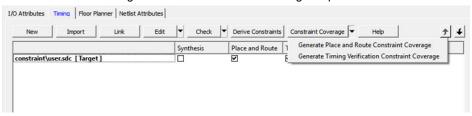

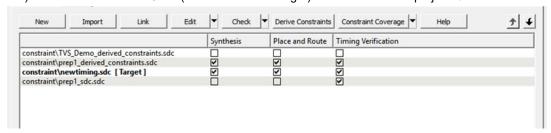

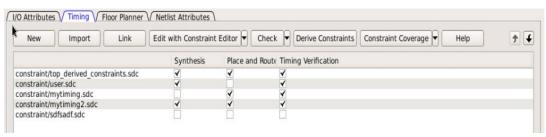

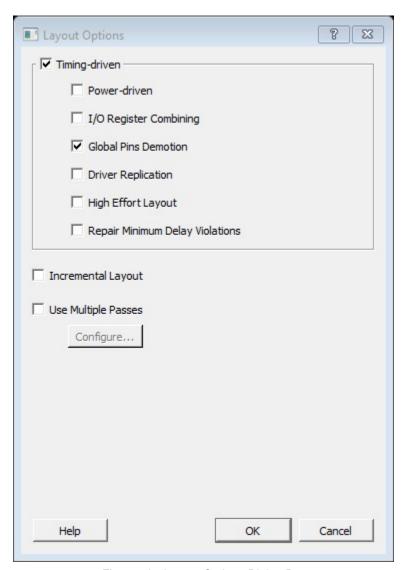

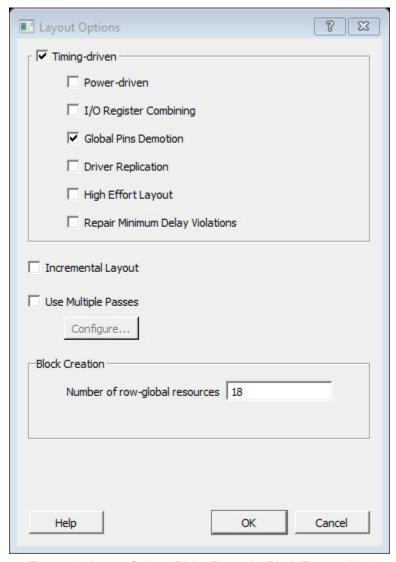

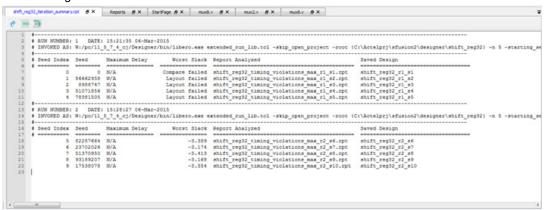

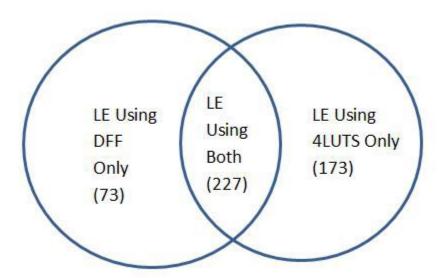

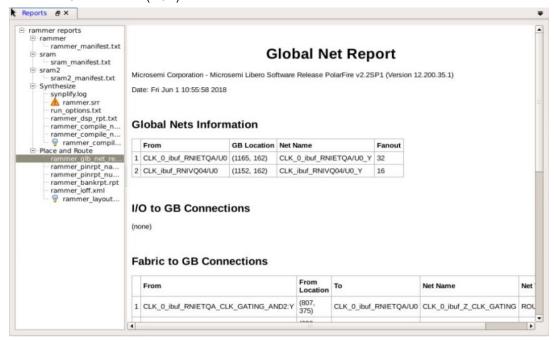

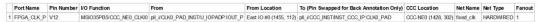

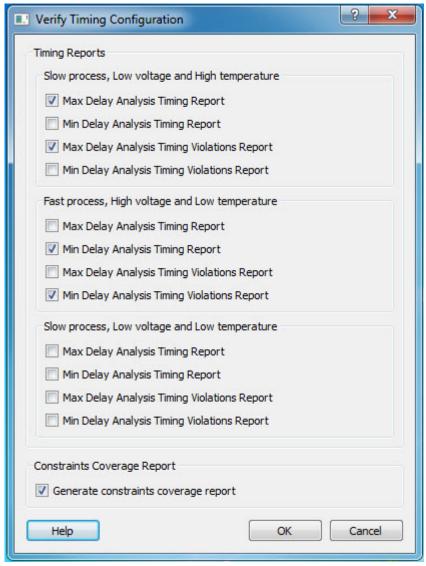

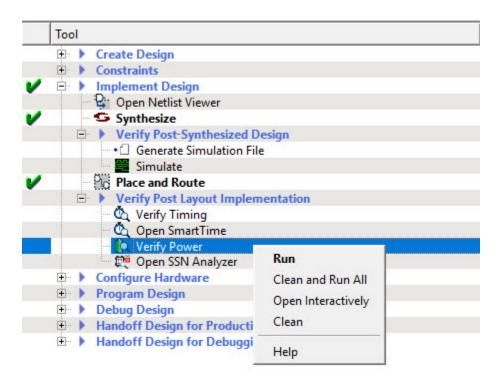

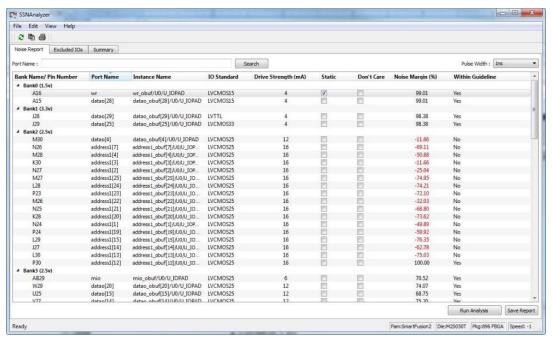

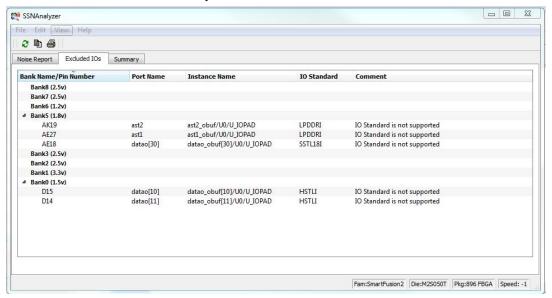

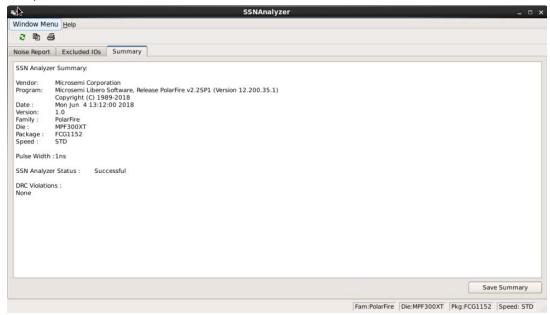

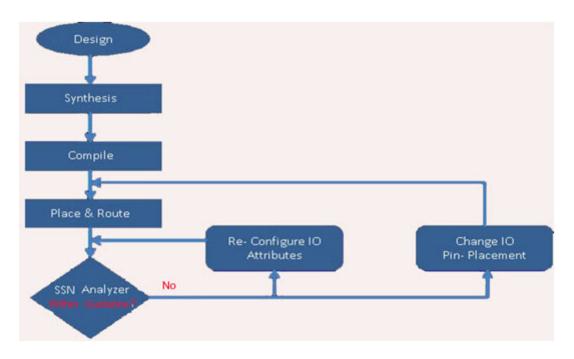

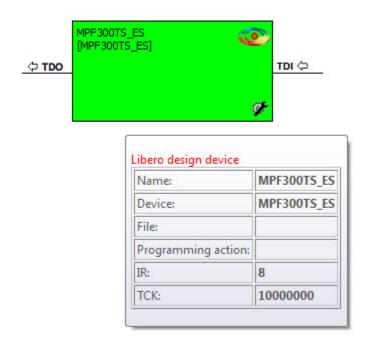

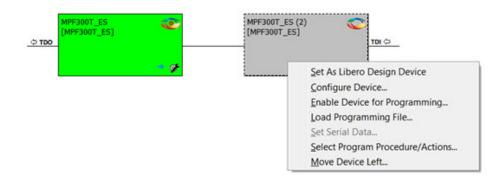

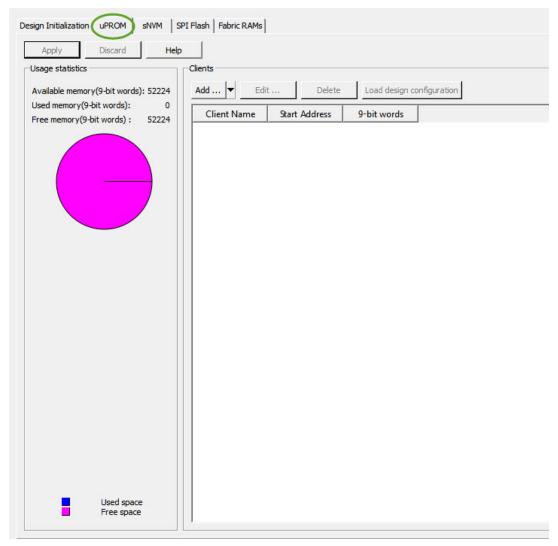

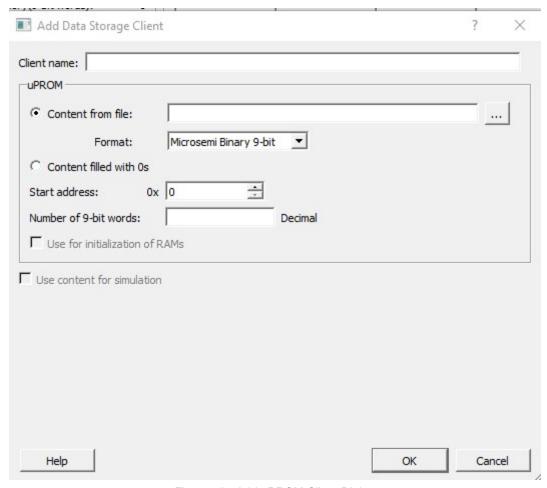

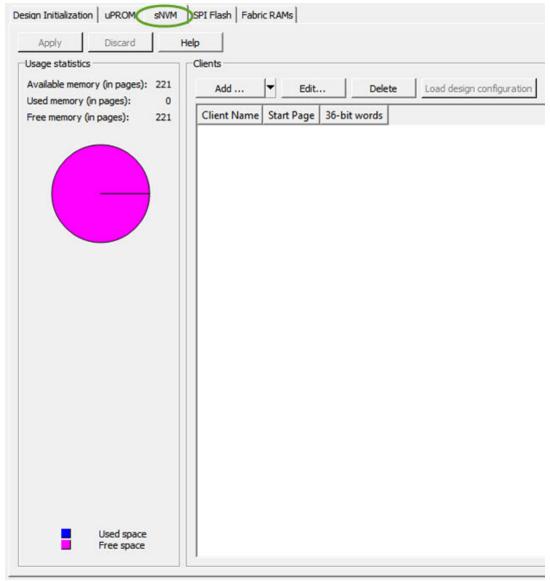

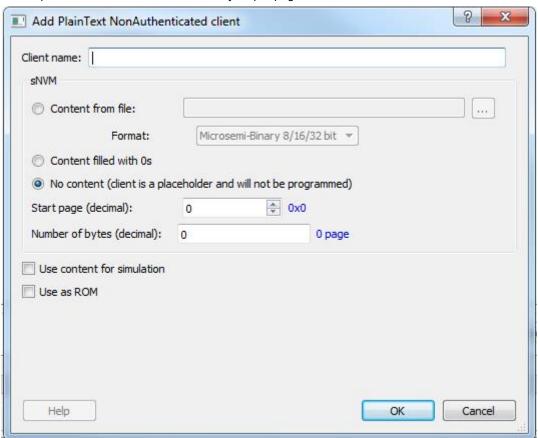

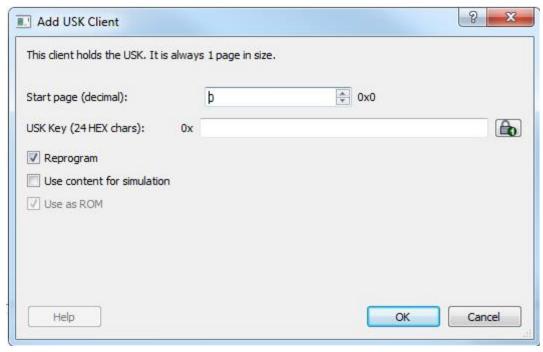

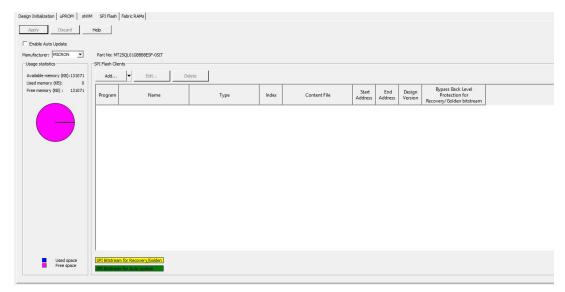

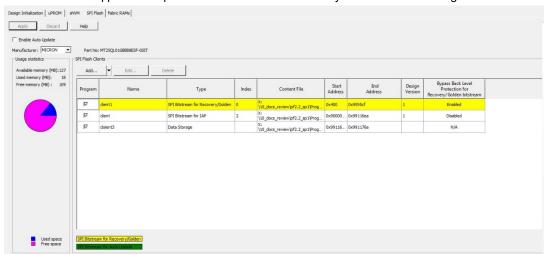

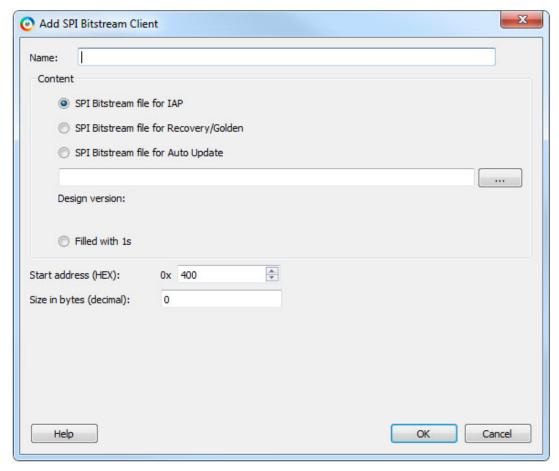

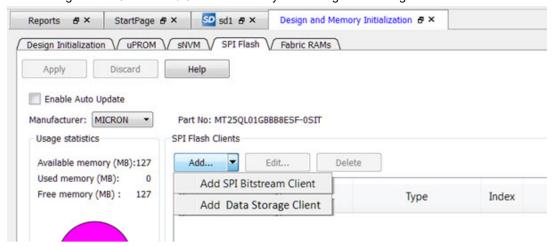

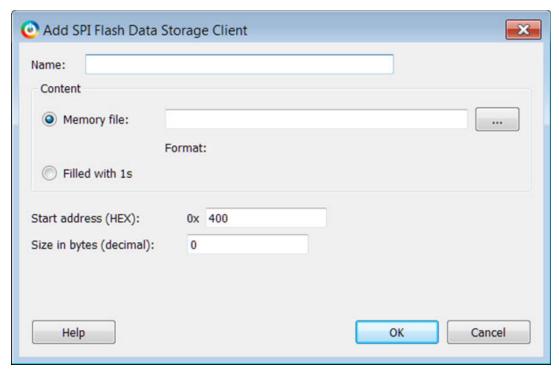

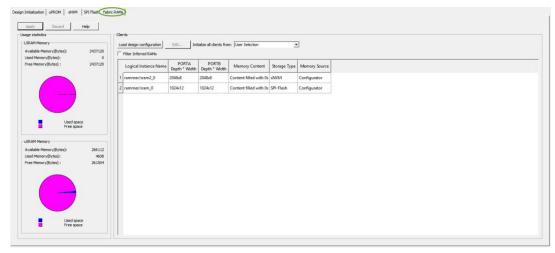

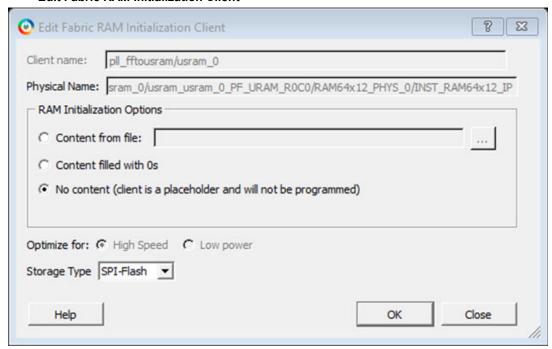

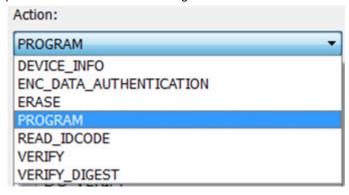

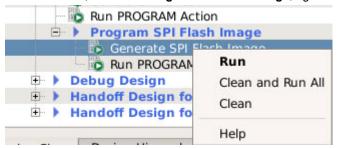

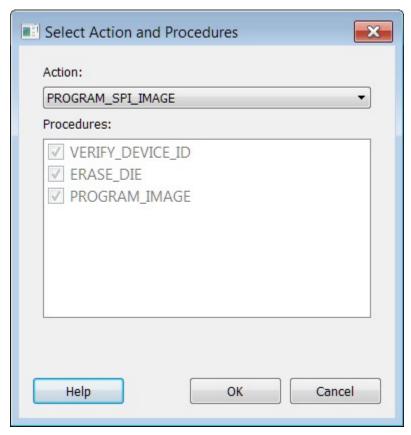

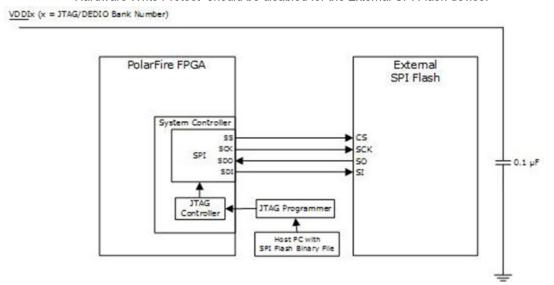

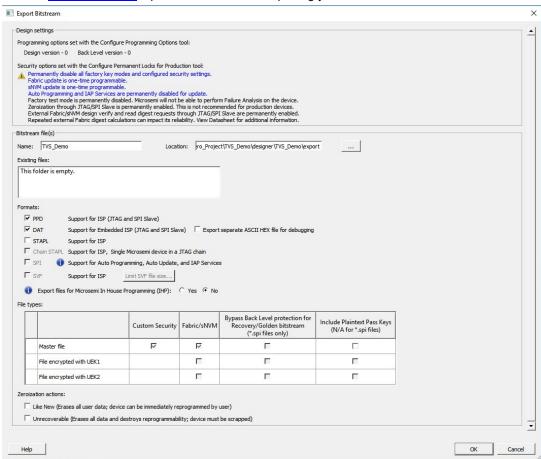

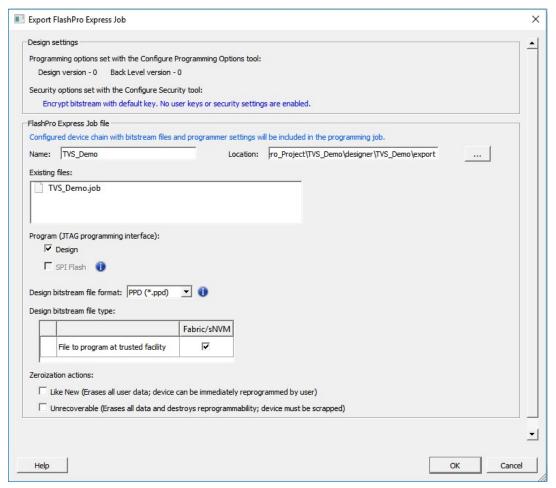

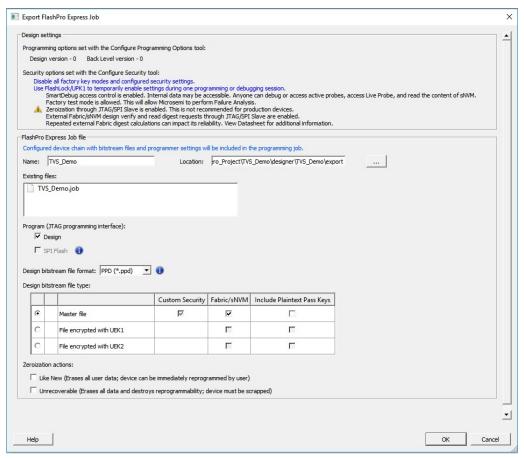

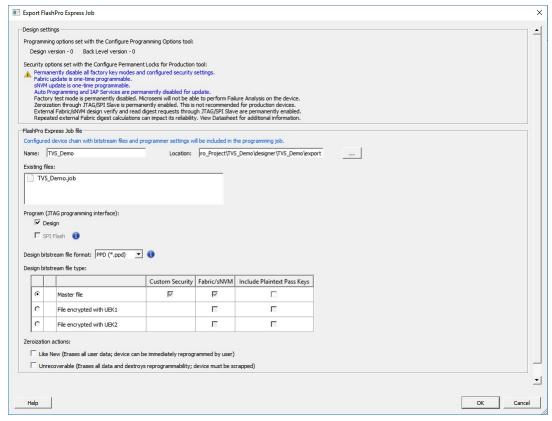

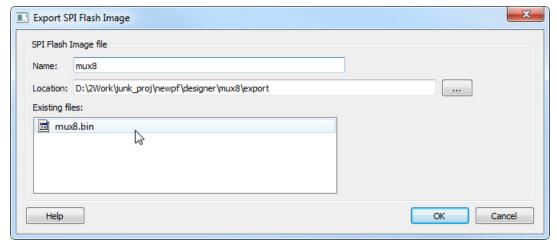

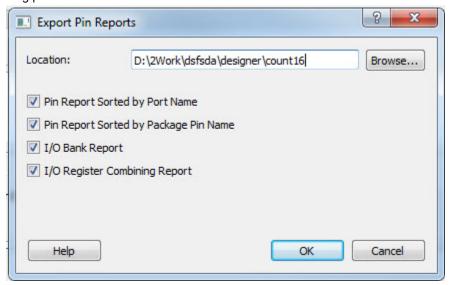

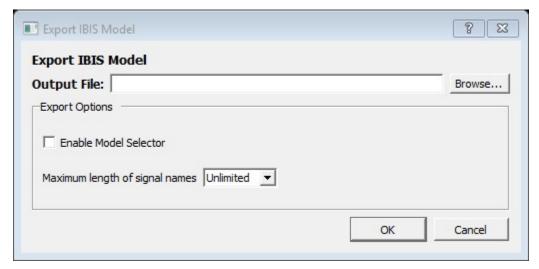

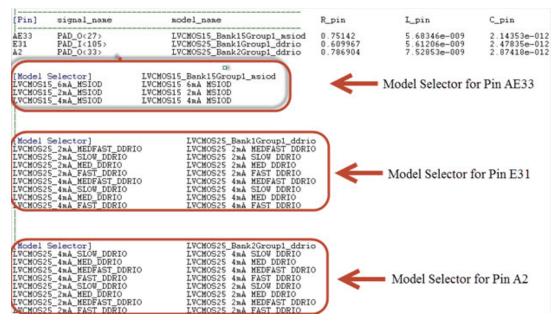

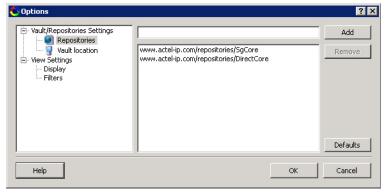

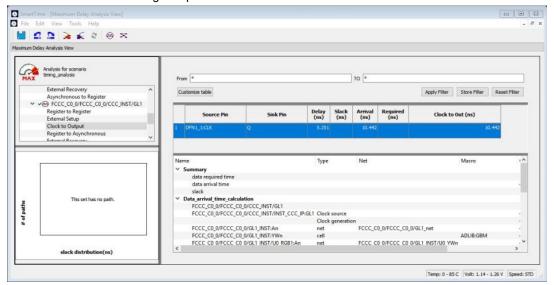

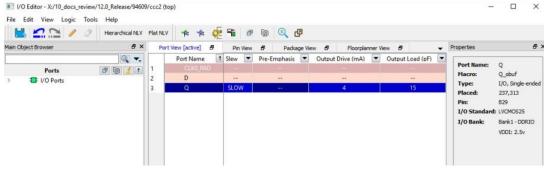

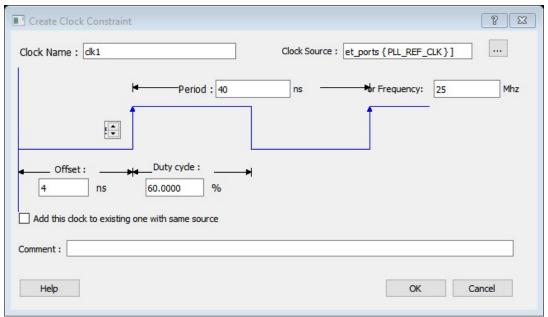

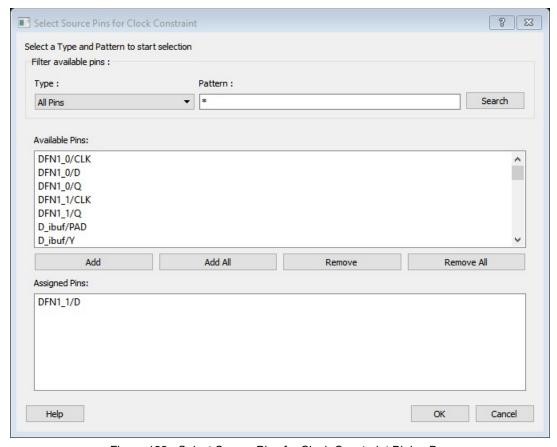

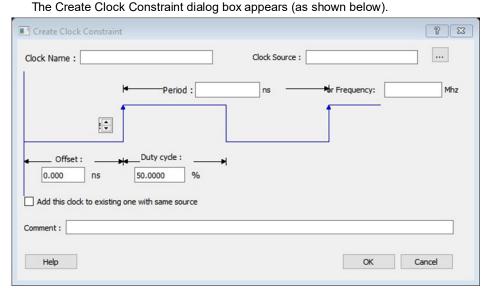

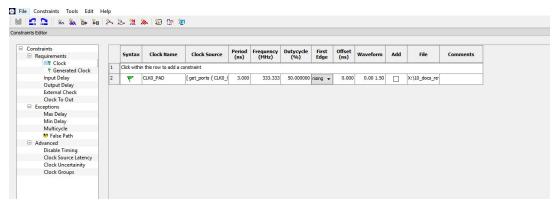

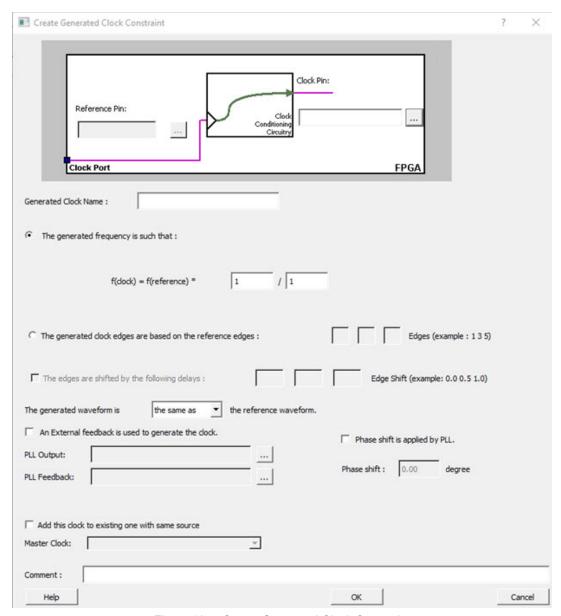

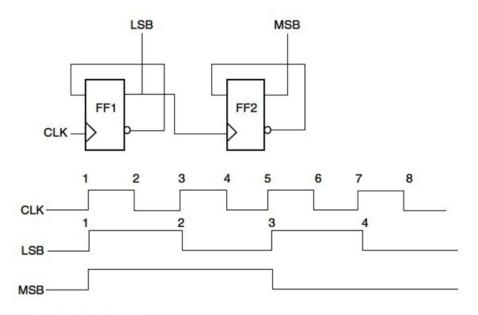

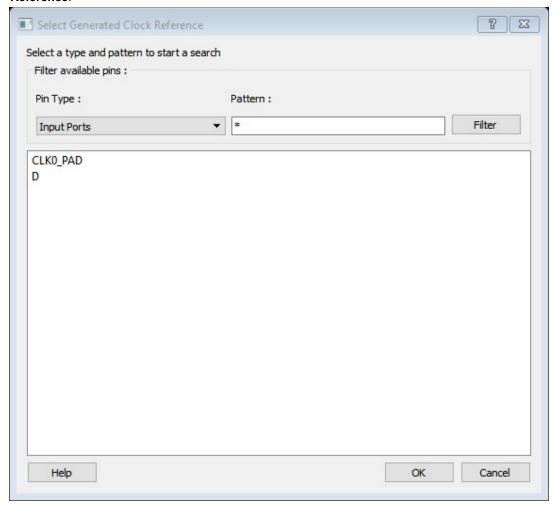

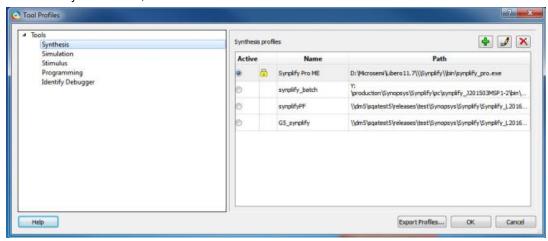

## **Derived Timing Constraints (\*.sdc)**