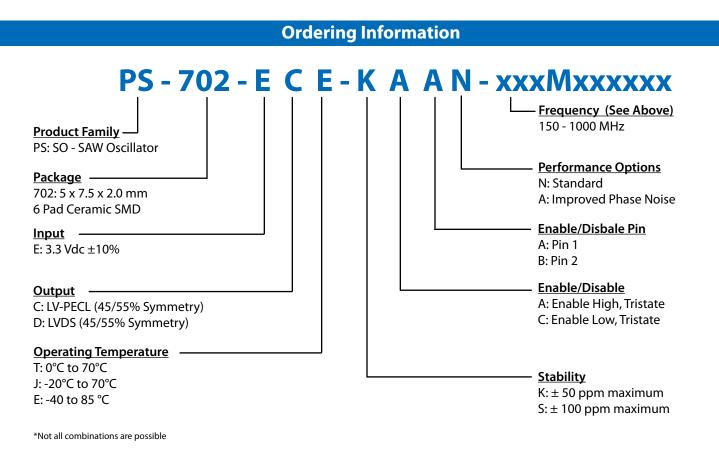

## Description

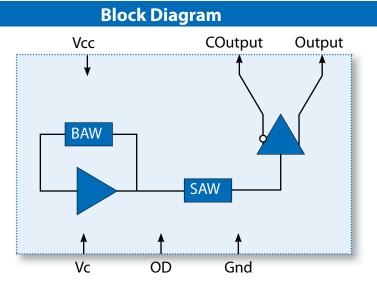

The PS-702 is a SAW Based Clock Oscillator that achieves low phase noise and very low jitter performance. The PS-702 is housed in an industry standard 6-Pad leadless ceramic package that is hermetically sealed. Packaging options include bulk or tape and reel.

### **Features**

- Industry Standard Package, 5.0 x 7.5 x 2.0 mm

- ASIC Technology For Ultra Low Jitter

0.100 ps-rms typical across 12 kHz to 20 MHz BW

0.120 ps-rms typical across 50 kHz to 80 MHz BW

- Output Frequencies from 150 MHz to 1 GHz

- 3.3 V Operation

- LV-PECL or LVDS Configuration with Fast Transition Times

- Complementary Outputs

- Output Disable Feature

- Improved Temperature Stability over Standard SAW XO

- Product is free of lead and compliant to EC RoHS Directive (Pb)

# Applications

- Reference Clock for Wired and Wireless Products <u>Description</u> <u>Standard</u>

- 1-2-4 Gigabit Fibre Channel

- 10 Gigabit Fibre Channel

- 10 Gigubit Hbre end

10 GbE LAN / WAN

- OC-192

- SONET / SDH

/ireless Products Standard INCITS 352-2002 INCITS 364-2003 IEEE 802.3ae ITU-T G.709

GR-253-CORE Issue4

## **Performance Specifications**

| Table 1: Electrical Performance                          |                  |                      |                       |                      |          |  |  |  |  |

|----------------------------------------------------------|------------------|----------------------|-----------------------|----------------------|----------|--|--|--|--|

| Parameter                                                | Symbol           | Min                  | Typical               | Maximum              | Units    |  |  |  |  |

| Supply                                                   |                  |                      |                       |                      |          |  |  |  |  |

| Voltage <sup>2,3</sup>                                   | V <sub>cc</sub>  | 2.97                 | 3.3                   | 3.63                 | V        |  |  |  |  |

| Current (No Load) <sup>3</sup>                           | I <sub>cc</sub>  |                      | 55                    | 70                   | mA       |  |  |  |  |

| Frequency                                                |                  |                      |                       |                      |          |  |  |  |  |

| Nominal Frequency <sup>1,2</sup>                         | f <sub>N</sub>   | 150                  |                       | 1000                 | MHz      |  |  |  |  |

| Frequency Stability <sup>1, 2</sup><br>(Ordering Option) | $f_{STAB}$       |                      | ±50, ±100             |                      | ppm      |  |  |  |  |

| Aging <sup>6,8</sup>                                     |                  |                      |                       | 10                   | ppm      |  |  |  |  |

|                                                          |                  | Outputs              |                       |                      |          |  |  |  |  |

| Mid Level - LVPECL <sup>2,3</sup>                        |                  | V <sub>cc</sub> -1.4 | V <sub>cc</sub> -1.25 | V <sub>cc</sub> -1.0 | V        |  |  |  |  |

| Swing - LVPECL <sup>2,3</sup>                            |                  | 450                  | 600                   | 750                  | mV-pp    |  |  |  |  |

| Mid Level - LVDS <sup>2,3</sup>                          |                  |                      | V <sub>cc</sub> -1.2  |                      | V        |  |  |  |  |

| Swing - LVDS <sup>2,3</sup>                              |                  | 250                  | 450                   |                      | mV-pp    |  |  |  |  |

| Current <sup>6</sup>                                     | I <sub>out</sub> |                      |                       | 20                   | mA       |  |  |  |  |

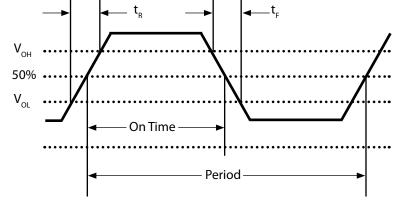

| Rise Time <sup>5, 6</sup>                                | t <sub>R</sub>   |                      |                       | 500                  | ps       |  |  |  |  |

| Fall Time <sup>5, 6</sup>                                | t <sub>F</sub>   |                      |                       | 500                  | ps       |  |  |  |  |

| Symmetry <sup>2,3</sup>                                  | SYM              | 45                   | 50                    | 55                   | %        |  |  |  |  |

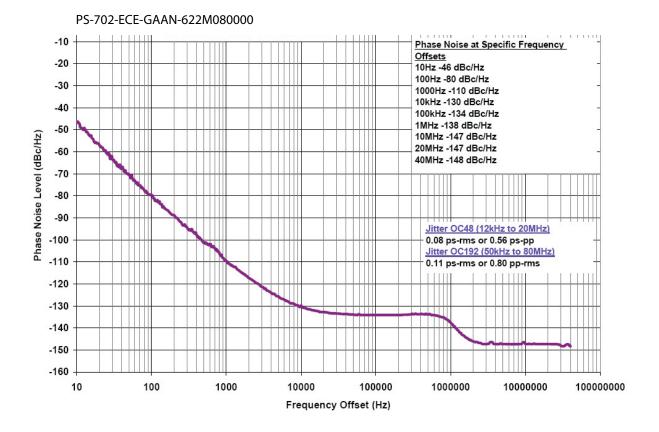

| Jitter <sup>6,7</sup><br>(12 kHz - 20 MHz BW) 622.08 MHz | ¢٦               |                      | 0.100                 | 0.250                | ps-rms   |  |  |  |  |

| Jitter <sup>6,7</sup><br>(50 kHz - 80 MHz BW) 622.08 MHz | φJ               |                      | 0.120                 | 0.300                | ps-rms   |  |  |  |  |

| Period Jitter <sup>9</sup> , RMS (622.08 MHz)            | φJ               |                      | 2.5                   | 3.0                  | ps-rms   |  |  |  |  |

| Period Jitter <sup>9</sup> , Peak - Peak (622.08 MHz)    | φJ               |                      | 16                    | 24                   | ps pk-pk |  |  |  |  |

| Operating Temperature <sup>1</sup>                       | T <sub>OP</sub>  | 0/7                  | 0, -20/70 or -40      | /85                  | °C       |  |  |  |  |

| Package Size                                             |                  |                      | 5.0 x 7.5 x 2.0       |                      | mm       |  |  |  |  |

1] See Standard Frequencies and Ordering Information tables (Pg 7) for more specific information

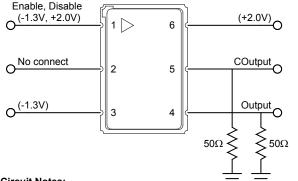

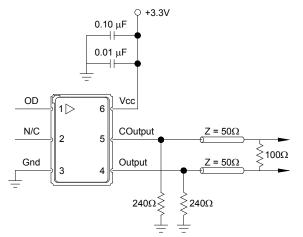

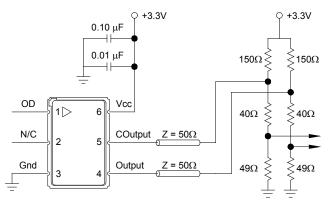

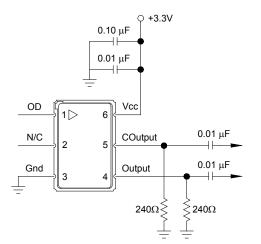

2] Parameters are tested with production test circuit below (Fig 1).

3] Parameters are tested at ambient temperature with test limits guard-banded for specified operating temperature.

4] Measured as the maximum deviation from the best straight-line fit, per MIL-0-55310.

5] Measured from 20% to 80% of a full output swing (Fig 2).

6] Not tested in production, guaranteed by design, verified at qualification.

7] Integrated across stated bandwidth per GR-253-CORE Issue4.

8] Tested with Vc = 0.3V to 3.0V unless otherwise stated in part description

9] Broadband Period Jitter measured using Lecroy Wavemaster 8600A 6 GHz Oscilloscope, 250K samples taken

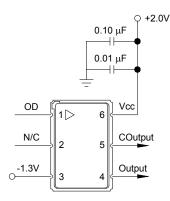

#### **Test Circuit Notes:**

1) To Permit 50 $\Omega$  Measurement of Outputs, all DC Inputs are Biased Down 1.3V. 2) All Voltage Sources Contain Bypass Capacitors to Minimize Supply Noise. 3) 50 $\Omega$  Terminations are Within Test Equipment.

### Fig 1: Test Circuit

### Fig 2: LV-PECL Waveform

| Absolute Maximum Ratings      |                  |            |          |  |  |  |  |

|-------------------------------|------------------|------------|----------|--|--|--|--|

| Parameter Symbol Ratings Unit |                  |            |          |  |  |  |  |

| Power Supply                  | V <sub>cc</sub>  | 0 to 4     | V        |  |  |  |  |

| Output Current                | I <sub>out</sub> | 25         | mA       |  |  |  |  |

| Storage Temperature           | TS               | -55 to 125 | °C       |  |  |  |  |

| Soldering Temp/Time           | T <sub>LS</sub>  | 260 / 40   | °C / sec |  |  |  |  |

Stresses in excess of the absolute maximum ratings can permanently damage the device. Functional operation is not implied at these or any other conditions in excess of conditions represented in the operational sections of this datasheet. Exposure to absolute maximum ratings for extended periods may adversely affect device reliability. Permanent damage is also possible if OD or Vc is applied before Vcc.

### **Suggested Output Load Configurations**

**LV-PECL to LV-PECL:** For short transmission lengths, the power consumption could be reduced by removing the  $100\Omega$  resistor and doubling the value of the pull down resistors.

**Functional Test:** Allows standard power supply configuration. Since AC coupled, the LV-PECL levels cannot be measured.

**LV-PECL to LVDS:** Restricted for short transmission lengths. Configuration may require modification depending on LVDS receiver.

**Production Test:** Allows direct DC coupling into  $50\Omega$  measurement equipment. Must bias the power supplys as shown. Similar to Figure 1.

# **Typical Characteristics - Phase Noise**

#### Page4 of 7

### Reliability

VI qualification includes aging at various extreme temperatures, shock and vibration, temperature cycling, and IR reflow simulation. The PS-702 family is capable of meeting the following qualification tests:

| Environmental Compliance |                          |  |  |  |  |

|--------------------------|--------------------------|--|--|--|--|

| Parameter                | Conditions               |  |  |  |  |

| Mechanical Shock         | MIL-STD-883, Method 2002 |  |  |  |  |

| Mechanical Vibration     | MIL-STD-883, Method 2007 |  |  |  |  |

| Solderability            | MIL-STD-883, Method 2003 |  |  |  |  |

| Gross and Fine Leak      | MIL-STD-883, Method 1014 |  |  |  |  |

| Resistance to Solvents   | MIL-STD-883, Method 2016 |  |  |  |  |

## **Handling Precautions**

Although ESD protection circuitry has been designed into the PS-702 proper precautions should be taken when handling and mounting. VI employs a human body model (HBM) and a charged device model (CDM) for ESD susceptibility testing and design protection evaluation.

| ESD Ratings            |            |                          |  |  |  |  |

|------------------------|------------|--------------------------|--|--|--|--|

| Model                  | Conditions |                          |  |  |  |  |

| Human Body Model 1500V |            | MIL-STD-883, Method 3015 |  |  |  |  |

| Man Man Model          | 200V       | V/JESD22-A115-A          |  |  |  |  |

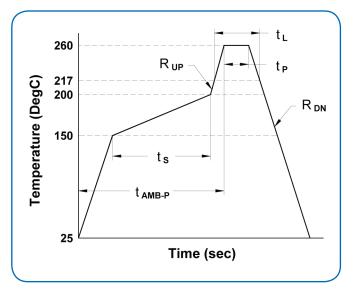

| Reflow Profile (IPC/JEDEC J-STD-020C) |                    |                         |  |  |  |  |

|---------------------------------------|--------------------|-------------------------|--|--|--|--|

| Parameter                             | Value              |                         |  |  |  |  |

| PreHeat Time                          | t <sub>s</sub>     | 60 sec Min, 180 sec Max |  |  |  |  |

| Ramp Up                               | R <sub>up</sub>    | 3 °C/sec Max            |  |  |  |  |

| Time Above 217 °C                     | t                  | 60 sec Min, 150 sec Max |  |  |  |  |

| Time To Peak Temperature              | T <sub>AMB-P</sub> | 480 sec Max             |  |  |  |  |

| Time at 260 °C                        | t <sub>P</sub>     | 20 sec Min, 40 sec Max  |  |  |  |  |

| Ramp Down                             | R <sub>DN</sub>    | 6 °C/sec Max            |  |  |  |  |

The device is qualified to meet the JEDEC standard for Pb-Free assembly. The temperatures and time intervals listed are based on the Pb-Free small body requirements. The PS-702 device is hermetically sealed so an aqueous wash is not an issue.

Termination Plating: Electroless Gold Plate over Nickel Plate

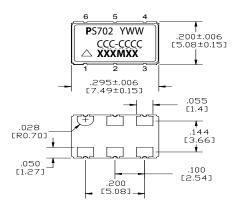

# **Outline Drawing & Pad Layout**

| Pin Out |                       |                                                                                                  |  |  |  |  |  |

|---------|-----------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin     | Symbol                | Function                                                                                         |  |  |  |  |  |

| 1       | NC or OE <sup>1</sup> | NC or<br>Enable = LV-CMOS logic 0 or Ground<br>Disable = LV-CMOS logic 1<br>**see Note 1 below** |  |  |  |  |  |

| 2       | NC or OE <sup>1</sup> | NC or<br>Enable = LV-CMOS logic 0 or Ground<br>Disable = LV-CMOS logic 1<br>**see Note 1 below** |  |  |  |  |  |

| 3       | GND                   | Case and Electrical Ground                                                                       |  |  |  |  |  |

| 4       | Output                | Output                                                                                           |  |  |  |  |  |

| 5       | COutput               | Complementary Output                                                                             |  |  |  |  |  |

| 6       | V <sub>cc</sub>       | Power Supply Voltage (3.3V $\pm 10\%$ )                                                          |  |  |  |  |  |

Note 1: For proper operation disable pin can not be left floating and a pin1 or pin 2 enable option must be ordered. See page 7 for alternative input logic operation

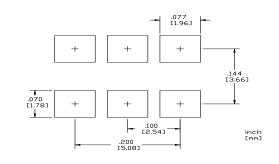

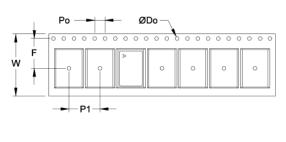

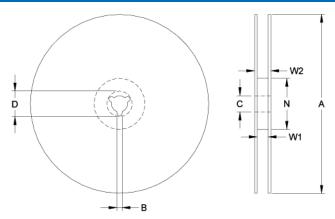

# Tape & Reel (EIA-481-2-A)

| Tape Dimensions (mm) |     |     |     | Reel Dimensions (mm) |     |                 |     |     |      |     |      |      |       |

|----------------------|-----|-----|-----|----------------------|-----|-----------------|-----|-----|------|-----|------|------|-------|

| Dimension            | W   | F   | Do  | Ро                   | P1  | P1 A B C D N W1 |     |     |      |     | W1   | W2   | # Per |

| Tolerance            | Тур | Тур | Тур | Тур                  | Тур | Тур             | Min | Тур | Min  | Min | Тур  | Max  | Reel  |

| PS-702               | 16  | 7.5 | 1.5 | 4                    | 8   | 178             | 1.5 | 13  | 20.2 | 50  | 16.4 | 22.4 | 200   |

|            | Standard Output Frequencies (MHz) |            |            |            |            |            |            |  |  |

|------------|-----------------------------------|------------|------------|------------|------------|------------|------------|--|--|

| 155M520000 | 156M250000                        | 160M000000 | 162M000000 | 175M000000 | 187M500000 | 200M000000 | 212M500000 |  |  |

| 240M000000 | 245M760000                        | 250M000000 | 260M000000 | 268M800000 | 300M000000 | 311M040000 | 312M500000 |  |  |

| 320M000000 | 324M000000                        | 350M000000 | 375M000000 | 384M000000 | 389M600000 | 390M625000 | 400M000000 |  |  |

| 480M000000 | 491M520000                        | 500M000000 | 531M250000 | 532M000000 | 533M000000 | 537M600000 | 622M080000 |  |  |

| 625M000000 | 635M040000                        | 637M500000 | 640M000000 | 644M531300 | 657M421900 | 666M514300 | 669M326600 |  |  |

| 672M162700 | 690M569200                        | 693M483000 | 704M380600 | 707M352700 | 720M000000 | 742M434700 | 768M000000 |  |  |

| 796M875000 | 800M000000                        | 901M120000 | 1000M00000 |            |            |            |            |  |  |

Frequencies not shown are available upon request.

Microsemi Headquarters

Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 email: sales.support@microsemi.com

www.microsemi.com

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications are verified and verify the same testing end with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent ngths, licenses, or any other IP rights, whether with regard to such information in tise of or any products and service and yrut mote.

62018 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.