# Package Miniaturization

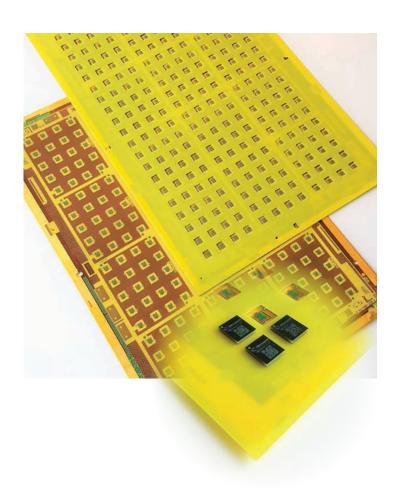

Large Area Panel Molding

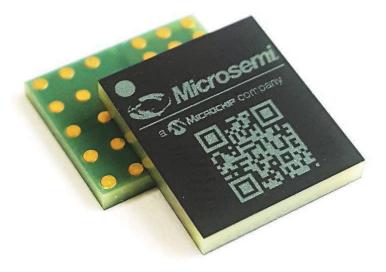

Microsemi's Large Area Panel Molding provides a low cost of entry, fast turnaround, flexible package size design alternative to standard Injection Molding. Adapted from Microsemi's embedded die technology, the LAPM process is based on 18" × 12" printed circuit board laminates, offering a scalable manufacturing process across all production volumes.

Customers looking to develop packaged parts often face tough decisions on justification of package tooling and the risk of having to make costly adjustments prior to moving in to volume production. The LAPM process requires minimal tooling, thus lowering development costs and providing a faster time to samples.

The technology provides additional packaging benefits of using thermally matched materials by allowing the same material to be used for the substrate and over-molding, minimising stress throughout the package during thermal cycling.

Microsemi's Large Area Panels allow customers limitless possibilities in package shape and size, which would normally be uneconomical by standard methods.

#### **Features**

- Low cost of entry no expensive tooling

- Fast turnaround time standard PCB process

- Flexible size and shape large panels allow for economic and scalable production at any package size

- Thermally matched package materials

- Internal interconnect Bare die (flip chip or wire bond), BGA, SMT components

### **Applications**

- Medical Implants

- Wearables

- Military

- Security

- Industrial

## **Package Miniaturization**

## Large Area Panel Molding

| Module Parameters           |                                                                                    |

|-----------------------------|------------------------------------------------------------------------------------|

| Minimum substrate thickness | 100 µm core                                                                        |

| Minimum feature size        | 75 µm                                                                              |

| Minimum module XY size      | Flip chip die XY dimensions + 1 mm<br>Wire bond pad + 200 µm                       |

| Minimum module<br>height    | Flip chip = Core + (die height + 10%)<br>Wire bond = Core + wire bond height + 10% |

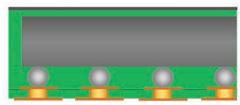

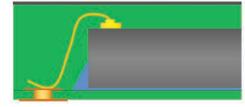

| Die interconnect            | Flip chip and wire bond                                                            |

| Components                  | Bare die, packaged parts and SMT components                                        |

| Marking                     | Laser and label                                                                    |

| Traceability                | Yes                                                                                |

| Packaging                   | JEDEC tray or tape and reel                                                        |

| Footprint                   | Land Grid Array (LGA)                                                              |

LAPM Flip Chip Module - Single Core

LAPM Wire-bond Module - Single Core

| Test Group                            | Test Standard                                                     | Result   |

|---------------------------------------|-------------------------------------------------------------------|----------|

| Moisture sensitivity preconditioning: | JESD22-A113F, IPC/JEDEC J-STD-020 Level 3                         | <b>✓</b> |

| Temperature cycling                   | -40°C to 60°C, 5 cycles                                           |          |

| Bake                                  | 125 °C for 24h                                                    |          |

| Moisture soak                         | 40 hrs, 60 °C/60%RH                                               |          |

| 3X reflow                             | JESD22-A113F, 260°C                                               |          |

| Thermal stress:                       |                                                                   |          |

| Low temperature storage               | –40°C, 72h                                                        | <b>√</b> |

| High temperature storage              | 125°C, 72h                                                        |          |

| Temperature cycling                   | MIL-STD-883 Method 1010, Condition B, -55 °C to 125 °C, 20 cycles |          |

| Mechanical stress:                    |                                                                   |          |

| Mechanical shock                      | MIL-STD-883 Method 2002, Condition B, 5 shocks, 1500 g            | <b>√</b> |

| Mechanical vibration                  | MIL-STD-883 Method 2007, Condition A, 20–2000 Hz, 20 G            |          |

| Constant acceleration                 | MIL-STD-883 Method 2001, 10,000 G                                 |          |

| Exposure:                             |                                                                   |          |

| Resistance to solvents                | MIL-STD-883 Method 2016                                           | <b>√</b> |

| ESD                                   | MIL-883 Method 3015, 1000V HBM                                    |          |

| Assembly:                             |                                                                   |          |

| Component shear                       | MIL-STD-883 Method 2019/2011                                      | ✓        |

| External physical dimensions          | MIL-883 Method 2016                                               |          |

| Solderability                         | MIL-STD-883 Method 2003.8/2022.2                                  |          |

| lonic cleanliness                     | IPC-TM-650                                                        |          |

#### Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Sales: +1 (949) 380-6136

Fax: +1 (949) 215-4996

email: sales.support@microsemi.com

www.microsemi.com

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold bereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

©2018 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.