# UG0603 User Guide RTG4 FPGA Timing Constraints (Classic Constraint Flow) Libero SoC v11.8 SP4

Power Matters."

Power Matters."

Microsemi Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2018 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

5-02-00603-2/07.18.

# **Table of Contents**

| Introduction                                         | 4    |

|------------------------------------------------------|------|

| Using Synopsys Design Constraints                    |      |

| Object Access                                        | 6    |

| Timing Exceptions                                    | 7    |

| Timing Constraints and Design Flow                   | 8    |

| Timing Constraints for Synplify Pro                  | 8    |

| SCOPE and Using the Forward Annotated SDC            | . 13 |

| Timing Constraints for Timing-Driven Place and Route | . 16 |

| Improving Placer Performance                         | . 21 |

| Constraints for RTG4 IP Blocks                       | . 24 |

| Oscillators                                          | . 24 |

| RTG4 Fabric Clock Conditioning Circuit (CCC)         | . 25 |

| High Speed Serial Interface (SERDES) Block           | . 27 |

# Introduction

In designing FPGA synchronous digital designs, from design entry to physical implementation, rarely do you achieve the required timing performance of the design without iteration. You often must go through numerous iterations of the design cycle—HDL design capture, synthesis, physical implementation (Place and Route) and Timing Analysis—to achieve timing closure.

Setting Timing Constraints and performing Timing Analysis are the two most important steps in design iterations towards timing closure.

For RTG4 designs, Microsemi recommends setting timing constraints for both synthesis and place and route steps. You must first set the timing assertion constraints; see "Timing Assertions" on page 7.

If timing performance is not met in the first iteration, consider setting additional and more advanced timing constraints in the second and subsequent iterations. See "Timing Exceptions" on page 8.

# 1 – Using Synopsys Design Constraints

The Synopsys® Design Constraint (SDC) is a Tcl-based format used by Synopsys tools to specify the design intent and timing constraints. Microsemi supports a variation of the SDC format for constraints management.

You can use the following types of SDC commands when creating SDC constraints for RTG4 designs:

- Object Access

- Timing Assertions

- Timing Exceptions

## **Object Access**

SDC timing constraints apply to specific design objects. Table 1-1 summarizes the object access commands supported by SmartTime (the Microsemi static timing analysis tool incorporated with the place and route tools). Refer to the SmartTime online help for more information.

| Table 1-1 • Ob | iect Access | Commands | Supported b | v SmartTime |

|----------------|-------------|----------|-------------|-------------|

|                |             | oommunus | ouppoiled b |             |

| Design Object     | Command(s)                         |

|-------------------|------------------------------------|

| Cells / Instances | get_cells                          |

| Clocks            | get_clocks                         |

| Nets              | get_nets                           |

| Pins              | get_pins                           |

| Ports             | get_ports, all_inputs, all_outputs |

| Registers         | all_registers                      |

## Implicit vs. Explicit Specification

In general, SDC commands include design objects as an argument. SDC supports both implicit and explicit object specification.

When the tool determines the object type by searching for the object, it is called an implicit object specification. When the object type is specified (to avoid ambiguity) using a nested object access command, it is called an explicit object specification.

For example: If you have a net named 'my\_net1', the implicit specification is my\_net1 and the explicit specification is [get\_nets my\_net1].

Not all design objects are applicable to all SDC commands. Each SDC command accepts a pre-defined set of design objects as arguments. Microsemi recommends that you use the explicit object specification method to avoid ambiguity regarding object type. If multiple object types are returned after searching an implicit specification, the object types are prioritized based on the tool's priority object list.

Refer to the SmartTime online help for more information.

## Wild Card Characters

Table 1-2 lists the wild card characters available for use in SDC commands.

| Wild Card | Function                                |

|-----------|-----------------------------------------|

| ١         | Interprets the next character literally |

| *         | Matches any string                      |

Note: The matching function requires that you add a backslash (\) before each slash in the pin names in case the slash does not denote the hierarchy in your design.

## **Hierarchy and Pin Separators**

Synplify Pro software defaults to the use of '.' (period) as both the hierarchy and pin separators for timing constraints.

For example: [get\_pins {top\_level.blockA.instance123.my\_pin}]

To change the hierarchy separator from the default '.' (period) to the '/' (forward slash), use the command: set\_hierarchy\_separator { / }

SmartTime software defaults to the use of '/' as a design hierarchy separator and ":" as the pin separator character.

For example: [get\_pins {top\_level/blockA/instance123:my\_pin}]

Notice that '/' is the hierarchy separator used to indicate that 'instance123' is present in the design hierarchy below top\_level ' blockA. The ":" pin separator identifies 'my\_pin' on 'instance123'.

## **Bus Naming Conventions**

All buses in the SDC file must use the Verilog-style naming convention name[index].

For example: [get\_ports addr\_bus\_out[1]]

If you want to specify the constraint on the entire bus, you can use [get\_port addr\_bus\_out].

## Comments

You can add comments to an SDC file by preceding the comment line with a pound sign (#). # This is a comment line

## **Timing Assertions**

Timing assertions are intended to capture your design timing requirements. They include the following SDC commands:

- Clock Period/Frequency

- create\_clock

- create\_generated\_clock

- Input / Output Delay

- set\_input\_delay

- set\_output\_delay

- set\_external\_check

- set\_clock\_to\_output

- Clock-to-clock Uncertainty

- set\_clock\_uncertainty

- Clock Source Latency

- set\_clock\_latency

Refer to "Timing Constraints and Design Flow" on page 9 for the Timing Assertion SDC commands Synplify Pro and SmartTime support.

## **Timing Exceptions**

Use timing exceptions to identify design paths that require the default single cycle timing relationships to be overridden. SDC commands for timing exceptions include:

- · False path

- set\_false\_path

- Multicycle path

- set\_multicycle\_path

- Maximum delay path

- set max delay

- Minimum delay path

- set\_min\_delay

- Disabled timing arcs

- set\_disable\_timing

## **Timing Exceptions and Precedence Order**

When the same timing path has more than one timing exception constraint, SmartTime honors the timing constraint with the highest precedence and ignores the other timing exceptions according to the order of precedence shown in Table 1-3. Synplify Pro honors the timing constraints according to Precedence Order in Table 1-4.

#### Table 1-3 • Timing Exception - Precedence Order for SmartTime

| Timing Exceptions                   | Order of Precedence |

|-------------------------------------|---------------------|

| set_disable_timing                  | 1                   |

| set_false_path                      | 2                   |

| set_maximum_delay/set_minimum_delay | 3                   |

| set_multicycle_path                 | 4                   |

#### Table 1-4 • Timing Exception - Precedence Order for Synplify Pro

| Timing Exceptions           | Order of Precedence |

|-----------------------------|---------------------|

| set_false_path              | 1                   |

| set_max_delay/set_min_delay | 2                   |

| set_multicycle_path         | 3                   |

# 2 – Timing Constraints and Design Flow

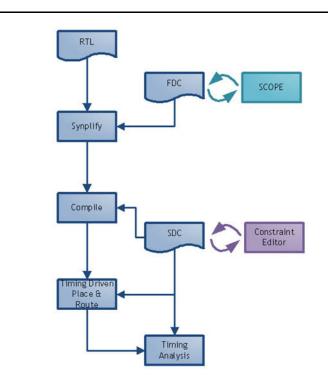

This chapter describes where to specify timing constraints and perform timing analysis in the Libero design flow (Figure 2-1). Microsemi recommends that you supply Synplify Pro and SmartTime with adequate and complete timing constraints. Also, you must review the timing reports from both Synplify Pro and SmartTime to ensure that the design has been constrained properly and is meeting the timing goals.

#### Figure 2-1 • Timing Constraints in the Design Flow

Libero tools (Timing Driven Place and Route and SmartTime) support a subset of Synopsys SDC timing constraints relevant for FPGA designs.

Microsemi recommends that you create two sets of timing constraints in the Libero flow:

- FDC timing constraints for synthesis with Synplify Pro.

- SDC timing constraints for the Libero Timing Driven Place and Route and SmartTime phases.

## **Timing Constraints for Synplify Pro**

### **Overview**

Synplify Pro supports the FPGA Design Constraints (FDC) format. The FDC format includes:

- A subset of the Synopsys SDC standard for timing constraints

- · Legacy timing constraint format supported by Synplify Pro

You can provide timing constraints to Synplify Pro by:

- Importing the timing constraint file(s) into the Libero project. Identify the timing constraint file(s) to be passed to Synplify Pro in Libero GUI. Right click the file(s) and choose Use for Synthesis. For details about importing timing constraints in the Libero GUI, refer to the Libero online help.

- Creating the timing constraints using the SCOPE (Synthesis Constraints Optimization Environment) GUI available in Synplify Pro software. Constraints created using SCOPE are saved to a constraints file using the FDC format.

## **Supported Synplify Pro Timing Constraints**

The following timing constraints are supported by Synplify Pro for FPGA synthesis:

- create\_clock

- create\_generated\_clock

- set\_input\_delay

- set\_output\_delay

- set\_false\_path

- set\_multicycle\_path

- set\_max\_delay

- set\_clock\_latency

- set\_clock\_uncertainty

Refer to the Synplify Pro for Microsemi Reference Manual for details on the options and arguments,.

## **Constraints for Design Requirements**

Synthesis software uses timing constraints to make trade-offs that lead to optimum use of resources to achieve requested timing goals. Timing constraints are essential to ensure that the right choices are made by the synthesis tool while performing logic and mapping optimizations of the design.

Microsemi recommends that you include Clock Constraints and Input and Output Delay Constraints.

There are two types of clock constraints:

- create\_clock

- create\_generated\_clock

To define the design clocks for RTG4 designs,:

- Use create\_clock constraint to identify and constrain oscillators and primary input ports used as clocks.

- Use create\_generated\_clock constraint to identify and constrain fabric CCC output pins used as clocks.

#### FDC Example with create\_clock and create\_generated\_clock

In the example below a combination of create\_clock and create\_generated\_clock constraints are used to define the required clock constraints.

First, the clock source is identified as the input port clk\_in at 50 MHz.

Then this clock source is used to generate a 200 MHz clock (clk\_core) using a CCC:

```

# Input Port 'clk_in' @ 50MHz is the clock source

create_clock -name {input_clock} \

-period 20 \

-waveform {0 10} \

[get_ports clk_in]

# CCC generates clk_core using clk_in as the source

# clk_core @ 200MHZ

create_generated_clock -name { clk_core }

-divide_by 1 -multiply_by 4\

-source [get_ports clk_in] \

[get_pins { clk_generator.FCCC_0.CCC_INST.GL1 }]

```

- Note: The backslash "\" character is part of Tcl syntax. It breaks a long single command into multiple lines.

- Note: Synplify Pro software defaults to the use of '.' (period) as the hierarchy separator for timing constraints. Use the set\_hierarchy\_separator command in the FDC file to redefine the hierarchy separator character. For example:set\_hierarchy\_separator {/}

The divide\_by and multiply\_by factors are derived from the PLL diagram displayed on the 'Advanced' tab of the fabric CCC configurator. Synplify Pro software defaults to 100 MHz required clock frequency for all clocks missing a timing constraint.

#### FDC Example with set\_input\_delay and set\_output\_delay

In this example, set\_input\_delay and set\_output\_delay constraints are used to define the required input and output delay timing constraints. These constraints are required to define the timing budget required for the I/O Interface.

In this example, all constraints use clk\_core from the previous example as the reference clock.

The input delay on input port(s) data\_bus\_in\_clk\_core is 2.5ns (max) and 1.0ns (min).

The output delay on output port(s) data\_bus\_out\_clk\_core is 3.0ns (max) and 1.5ns (min).

```

# input delays

set_input_delay -clock [get_clocks clk_core] \

-max 2.5 \

[get_ports {data_bus_in_clk_core*}]

set_input_delay -clock [get_clocks clk_core] \

-min 1.0 \

[get_ports {data_bus_in_clk_core*}]

# output delays

set_output_delay -clock [get_clocks clk_core]\

-max 3.0 \

[get_ports {data_bus_out_clk_core*}]

set_output_delay -clock [get_clocks clk_core] \

-min 1.5 \

[get_ports {data_bus_out_clk_core*}]

```

### **Constraint Checker**

Microsemi recommends that you validate FDC or timing constraints after you import or create them. This is especially important if the timing constraints file is imported.

Synplify Pro provides a constraint checker utility that you can use to validate the SDC timing constraints. The constraint checker is accessible from the project menu (**Run > Constraint Check**) inside the Synplify Pro GUI. It generates a constraint check report (\*\_cck.rpt) with details about any issues with timing constraints. The summary section should indicate that no issues were found with the timing constraints.

Use the constraint checker report to fix mistakes related to incorrect syntax or object names. For details about the Synplify Pro Constraint Checker, refer to the Synplify Pro for Microsemi User Guide.

## **Constraints for Optimizing Your Design**

Once timing constraints are checked, Microsemi recommends that you use the timing analysis feature in Synplify Pro to determine if all the required design constraints have been provided. You can use the list of violating design paths in the timing report to identify any missing or inaccurate timing constraints.

Note: Since the design is not yet placed, the timing report uses estimates based on wire load models for net delays. This is the reason that timing violations at this stage may or may not appear after place and route.

Microsemi recommends that you go through one pass of the entire design flow including Timing Driven Place and Route before adding timing exceptions for synthesis. You can then use the more accurate post place and route timing analysis report to determine required constraints.

Clock, Input and Output Delay constraints are the minimum set of required timing constraints for all designs. Some designs may require additional timing constraints known as timing exceptions. For example:

- False Paths (set\_false\_path),

- Multicycle Paths (set\_multicycle\_path)

- Maximum Path Delay (set\_max\_delay)

You can use timing exceptions to identify design paths that require the default single cycle timing relationships to be overridden. You must guide the synthesis tool optimizations by identifying design paths that:

- Do not have a timing relationship (set\_false\_path)

- Have a timing relationship that is not a single cycle (set\_multicycle\_path or set\_max\_delay)

#### Precedence

To resolve timing constraint conflicts when multiple timing exceptions are applied to the same design object, the following precedence rules apply:

set\_disable\_timing takes precedence over all other timing exception constraints.

False Path constraint takes precedence over Maximum Path Delay/Minimum Path Delay or Multicycle Path constraint.

Maximum Path Delay/Minimum Path Delay constraint takes precedence over Multicycle Path constraint.

| Timing Exception                      | Precedence Order |

|---------------------------------------|------------------|

| set_disable_timing                    | 1                |

| set_false_path                        | 2                |

| set_maximum_delay / set_minimum_delay | 3                |

| set_multicycle_path                   | 4                |

Table 2-1 • Object Access Commands Supported by SmartTime

## **Optimizing for Timing Versus Area**

When you run Synplify Pro synthesis, the tool first compiles the design and then maps it to the Microsemi technology cells.

By default, Synplify Pro automatically makes efficient trade-offs between area and timing performance to achieve the best results. However, you can guide Synplify Pro to optimize the design for timing performance at the expense of area. Conversely, you can guide Synplify Pro to optimize the design for area at the expense of timing performance.

Generally speaking, optimizing for timing performance consumes more FPGA resources (area) and optimizing for area often means larger delays (weaker timing performance). You must weigh your timing performance needs against your area needs to determine what works best for your design.

Refer to Chapter 10 of the Synplify Pro for Microsemi User Guide for more information on optimization options.

### Post-Synthesis Timing Analysis with Synplify Pro

Synplify Pro generates a timing report after synthesis is complete. After running synthesis, click the **View Log** button to open the log file in Synplify Pro.

The synthesis log file is also available from Libero SoC, under Synthesize in the Reports pane.

The file is located under the synthesis directory with the \*.srr extension and viewable in Libero SoC. Click the **File** tab in your Libero SoC Project. Expand the Synthesis file group. Double-click the \*.srr file to open

it in the Libero SoC Editor View pane. Scroll down to the section entitled START OF TIMING REPORT (Figure 2-2).

|                               |      | NUMBER SAME MORE MAD MORE READ                                                         |                        |                |                    |                |             |          | -Critica                                                                                                        |

|-------------------------------|------|----------------------------------------------------------------------------------------|------------------------|----------------|--------------------|----------------|-------------|----------|-----------------------------------------------------------------------------------------------------------------|

| nd file Edit View Design Book |      |                                                                                        |                        |                |                    |                |             |          |                                                                                                                 |

| 20000                         | 1 21 |                                                                                        |                        |                |                    |                |             |          |                                                                                                                 |

|                               | 8×   | M1,M08,Jup av # X (Ext) M08, to # X (Ends Similar # X                                  |                        |                |                    |                |             |          |                                                                                                                 |

| 🔁 deligner                    | - 14 | + - 2                                                                                  |                        |                |                    |                |             |          |                                                                                                                 |

| familier                      |      |                                                                                        |                        |                |                    |                |             |          |                                                                                                                 |

| 1.0                           |      | 881                                                                                    |                        |                |                    |                |             |          |                                                                                                                 |

| a simulation                  |      | AAJ                                                                                    |                        |                |                    |                |             |          |                                                                                                                 |

| anadgen                       |      | 555 44444 STRAT OF TIMING REPORT 444441                                                |                        |                |                    |                |             |          |                                                                                                                 |

| - stimulus                    |      | 154 # Timing Report written on Thu Peb 20 09:03:15 2014                                |                        |                |                    |                |             |          |                                                                                                                 |

| aunthesis                     |      | 354                                                                                    |                        |                |                    |                |             |          |                                                                                                                 |

| 1 a backup                    |      | 887                                                                                    |                        |                |                    |                |             |          |                                                                                                                 |

| - comp                        |      | DIE Top views H3 NDCR top                                                              |                        |                |                    |                |             |          |                                                                                                                 |

| 1 40                          |      | 113 Requested Trequency: 100.0 Mts                                                     |                        |                |                    |                |             |          |                                                                                                                 |

| MOMOR Squale                  |      | 545 Mire load mode: top                                                                |                        |                |                    |                |             |          |                                                                                                                 |

| In MD MOOR sup for            |      | 145 Paths requested: 5                                                                 |                        |                |                    |                |             |          |                                                                                                                 |

| In MO MOOR top hem            |      | 143 Constraint File(s):<br>143 BF: MT105 (Tuning report estimates glace and route dat. | There are the state of |                |                    |                |             |          |                                                                                                                 |

| MI MOOR Sup-map               |      | 145 08: MT325 (Timing report estimates place and route data                            | . F18448 1958 4        | e ere place at | a source straining | report for the | tas esasted |          |                                                                                                                 |

| In NO MOOR me sap             | 1.1  | AND REA MEADE CLOCK CONSTRAINTS COVER ONLY FF-50-FF paths                              | Associated with        | the slace.     |                    |                |             |          |                                                                                                                 |

| In NO MOOR top or             |      | 344                                                                                    |                        |                |                    |                |             |          |                                                                                                                 |

| MD.MODR.top.ord               |      | 167                                                                                    |                        |                |                    |                |             |          |                                                                                                                 |

| In MO MOOR INC. AND           |      | 141                                                                                    |                        |                |                    |                |             |          |                                                                                                                 |

| In MO.MODR. Nep.arr           |      | 348 Berformatce Summary                                                                |                        |                |                    |                |             |          |                                                                                                                 |

| AD MOMORAL AND                |      | 7.41                                                                                   |                        |                |                    |                |             |          |                                                                                                                 |

| In MD MODR May stok opt       |      | 871                                                                                    |                        |                |                    |                |             |          |                                                                                                                 |

| MI MODE top all all           |      | 172 Worst Alars in Gasigni 2.243                                                       |                        |                |                    |                |             |          |                                                                                                                 |

| MILMOOR may symbols           |      | 174. Horry Place in Depiger 2.243                                                      |                        |                |                    |                |             |          |                                                                                                                 |

| In NO MODR me synat           |      | 878                                                                                    | Requested.             | Estimated      | Requested.         | Estimated      |             | Clock    | Clerk                                                                                                           |

| MI MOOR NO SUNDAVIAL          |      | 516 Plasting Clock                                                                     | Frequency              | Frequency      | Ferland            | Period         | SLauk       | Type     | Group                                                                                                           |

| > _ physical plus             |      | 877                                                                                    | ***********            |                |                    |                |             |          |                                                                                                                 |

| The rest, MU MOOR hep-amater  | 23.1 | ATH MS MODE COD & FOODISLO net inferred clock                                          | 100.0 MM               | 477.5 3058     | 18.000             | 2.094          | 7,904       | LATerres | Inferred clayer                                                                                                 |

| h of MI MOOR hap meansion     |      | 179 N3 NDDE FAROEC 0 OBC/RCORC 25_519662_CCC_ARTerres_slark                            | 100.0 30%#             | 297.9 Mile     | 10,000             | 2.813          | 7,487       | LACETTES | Inferred_diagen                                                                                                 |

| nur, aptions. Int             |      | 180 HS NOOD HES FIG 2 APR N PCLK LARSPEER BLOOM                                        | 100.0 1008             | 168.0 1018     | 10.000             | 8.982          | 2.253       | LASseres | Inferred clayro                                                                                                 |

| anthemeter.                   |      | 111 2/4148                                                                             | 100.0 MKs              |                | 10.000             |                |             | #y#Sell  | #/#tem_classous                                                                                                 |

| thinking .                    |      | 343                                                                                    |                        |                |                    |                |             |          | Contraction of the second s |

#### Figure 2-2 • Synplify Pro \*.srr File Open in Libero SoC

The Synplify Pro timing report is broken into the following sections:

- Performance Summary

- Clock Relationships

- Interface Information

- · Detailed Report for Clocks

Use the synthesis timing report to confirm:

- Constraints are being picked up and applied as expected.

- · The design does not have any significant timing violations

Since the design is not yet placed, the synthesis timing report estimates net delays using wire load models. However, the cell delays used in the timing report are accurate.

A setup timing violation can be considered significant, if the path delay excluding the net delay exceeds the required time. This is usually an indication that either the timing requirement is unrealistic or the design path requires additional pipelining. In either case, it is highly unlikely that a design path with cell delays exceeding required time will meet the timing goal after place and route.

#### **Timing Exceptions**

If the post-synthesis timing analysis reports that the design does not meet timing specifications for clock speed or I/O delays, Microsemi recommends that you use timing exceptions to help synthesis.

Microsemi recommends that you go through one pass of the entire design flow, including Timing Driven Place and Route, before adding timing exceptions for synthesis. You can then use the more accurate post place and route timing analysis report to determine required constraints.

Use false path timing constraints to identify specific design paths that do not propagate logic level changes and should not be considered during timing analysis. The synthesis tool ignores design paths identified using this constraint for logic and mapping optimizations.

Use Multicycle Path, False Path and Maximum Path Delay timing constraints to identify design paths that have a timing relationship different from the default single cycle relationship. The synthesis tool uses the new relationship for optimizations.

Multicycle Path and False Path constraints typically result in relaxing the original single clock cycle timing requirement. The Maximum Path Delay constraint can result in relaxing or tightening the original timing requirement based on the time value specified by the user.

## FDC Examples

```

# False Path

set_false_path -from [get_ports uart_ctrl]

```

# Maximum Path Delay

set\_max\_delay -to [get\_ports {ram\_rd\_enable}] 4.0

# Multicycle Path

```

set_multicycle_path 4 -to [get_ports {I2C*}]

```

## **SCOPE and Using the Forward Annotated SDC**

You can use SCOPE from Synplify Pro to enter constraints for the synthesis step. After synthesis, Synplify Pro generates a \*\_sdc.sdc file, which contains the forward annotated timing constraints. Refer to "Using the Forward Annotated SDC" on page 16 for details. The recommended flow is to create separate constraints for Synthesis and Timing-Driven Place and Route steps.

## **Timing Constraint Entry Using SCOPE**

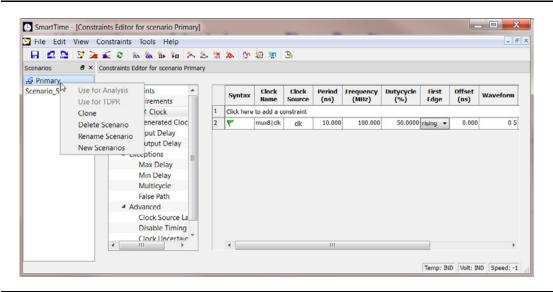

SCOPE is an editor provided with Synplify Pro to enter and manage timing constraints and synthesis attributes (Figure 2-3).

|     | 🐮 💷       |                      | <b>€ 0 6 0 0</b><br>R ≜ 3 8 4 |             |                  | 9 <del>9</del> 1 | 1 4 4 4        | 000       | <i>N N N</i> <u>A</u> 1 | 2 15    |   |

|-----|-----------|----------------------|-------------------------------|-------------|------------------|------------------|----------------|-----------|-------------------------|---------|---|

| rre | t Design: | <top level=""></top> |                               | - 10        | heck Constraints | ]                |                |           |                         |         |   |

|     | Enable    | Name                 | Object                        | Period      | Waveform         | Add              | Clock Group    | Latency   | Uncertainty             | Comment |   |

|     |           |                      |                               |             |                  |                  |                |           |                         |         | _ |

|     |           |                      |                               |             |                  |                  |                |           |                         |         |   |

|     |           |                      |                               |             |                  |                  |                |           |                         |         |   |

|     |           |                      |                               |             |                  |                  |                |           |                         |         |   |

|     |           |                      |                               |             |                  |                  |                |           |                         |         |   |

|     |           |                      |                               |             |                  |                  |                |           |                         |         |   |

|     |           |                      |                               |             |                  |                  |                |           |                         |         |   |

|     |           |                      |                               |             |                  |                  |                |           |                         |         |   |

|     |           |                      |                               |             |                  |                  |                |           |                         |         |   |

| 0   |           |                      |                               |             |                  |                  |                |           |                         |         |   |

| 1   |           |                      |                               |             |                  |                  |                |           |                         |         |   |

| 2   |           |                      |                               |             |                  |                  |                |           |                         |         |   |

| Clo | te Ge     | nerated Clocks       | collections Inputs/Outp       | uts Registe | rs Delay Pat     | hs Attrib        | utes I/O Stand | dards Com | pile Points TCL View    |         | _ |

#### Figure 2-3 • SCOPE Constraints Editor

The three types of constraints common to most designs are:

- **Clock Constraints** All synchronous designs are driven by some kind of clocks. Timing violations such as setup and hold time violations are meaningless without a clock constraint.

- **Input and Output Delay Constraints** The Input and Output delays makes allowance for path delays external to the FPGA. These constraints are part of the delay budgeting requirement.

- **Exceptions** When a design fails to meet timing requirements, you may need more advanced constraints to bring the design to timing closure. When applied to specific paths in the design, these timing exceptions override the default behavior of Synplify Pro when these timing paths are considered during optimization.

Before entering any constraints, first compile the design in Synplify Pro (**Run > Compile Only**). Performing compile inside Synplify Pro pre-populates SCOPE with object names. This could save you time and effort entering object names.

### Prefix Identifiers Supported by SCOPE and FDC

Synplify Pro uses object identifiers defined in the following table for constraints defined in SCOPE or FDC files (Table 2-2).

| Prefix Identifier (FDC) | SDC Equivalent | Design Objects to be applied                     |

|-------------------------|----------------|--------------------------------------------------|

| v: design_name          | n/a            | Modules                                          |

| c: clock_name           | get_clocks     | Clocks                                           |

| i: instance_name        | get_cells      | Instances                                        |

| p: <i>port_name</i>     | get_ports      | Ports                                            |

| t: pin_name             | get_pins       | Hierarchical ports or pins of instantiated cells |

| b: bus_name             | get_pins       | Bits of a bus                                    |

| n: net_name             | get_nets       | Net names                                        |

#### Table 2-2 • Prefix Identifiers and Design Objects

### **Clock Constraints**

There are two types of clock constraints: create\_clock and create\_generated\_clock. SCOPE has two separate tabs for these two constraints.

Use the Clocks tab to identify the clock sources (create\_clock). Refer to Figure 2-4.

| P  |        |                         | oject Run Analysi |              | -           |          |                     |          |              |             |   |

|----|--------|-------------------------|-------------------|--------------|-------------|----------|---------------------|----------|--------------|-------------|---|

|    |        |                         |                   |              |             | 9 10- MM | 444                 | 00 00 0  | 0 0 11 0     | 9 R         |   |

|    |        | n: <top level=""></top> | ₩ ;               |              | Constraints |          |                     |          |              |             |   |

|    | Enable | Name                    | Object            | Period       | Waveform    | Add      | Clock Group         | Latency  | Uncertainty  | Comment     | ŀ |

| 1  | •      | input_clock             | p: clk_in         | 20           | 0 10        | •        | <default></default> |          |              |             | ŀ |

| 2  |        |                         |                   |              |             |          |                     |          |              |             |   |

| 3  | 1      |                         |                   |              |             |          |                     |          |              |             |   |

| 4  | 1      |                         |                   |              |             |          |                     |          |              |             |   |

| 5  | 1      |                         |                   |              |             |          |                     |          |              |             |   |

| 6  |        |                         |                   |              |             |          |                     |          |              |             |   |

| 7  | 1      |                         |                   |              |             |          |                     |          |              |             |   |

| Cl | ocks   | Generated Clocks        | Collections In    | puts/Outputs | Registers   | Delay    | Paths Attri         | butes I/ | /O Standards | Compile Poi | 1 |

Figure 2-4 • Clocks Tab

Use the Generated Clocks tab to identify the generated clocks (create\_generated\_clock) in the design. Refer to Figure 2-5.

| ę   |              |             |             | nalysis HDL-Analyst Options Wind   |               |                | • • • • • •         |                   |                     |        |     | _6      |

|-----|--------------|-------------|-------------|------------------------------------|---------------|----------------|---------------------|-------------------|---------------------|--------|-----|---------|

| 1   |              |             |             |                                    |               | 6 2 2 2        | Q 23 d D R          |                   |                     |        |     |         |

|     |              |             | 8 3 2       |                                    |               |                |                     |                   |                     |        |     |         |

| rre | nt Design: < | Top Level>  |             | ▼ V)Chec                           | k Constraints |                |                     |                   |                     |        |     |         |

|     | Enable       | Name        | Source      | Object                             | Master Clock  | Generate Type  | Generate Parameters | Generate Modifier | Modifier Parameters | Invert | Add | Comment |

|     | *            | clk_core    | p:clk_in    | t clk_generator.FCC_0.CCC_INST.GL1 |               | multiply_by    | 4                   |                   |                     |        |     |         |

|     |              |             |             |                                    |               |                |                     |                   |                     |        |     |         |

| 1   |              |             |             |                                    |               |                |                     |                   |                     |        |     |         |

| 1   |              |             |             |                                    |               |                |                     |                   |                     |        |     |         |

| 1   |              | -           | -           |                                    |               |                |                     |                   |                     |        |     |         |

| 1   |              | -           |             |                                    |               |                |                     |                   |                     |        |     |         |

| 1   |              |             |             |                                    |               |                |                     |                   |                     |        |     |         |

| 1   |              |             |             |                                    |               |                |                     |                   |                     |        |     |         |

| -   |              |             |             |                                    |               |                |                     |                   |                     |        |     |         |

| .lo | cks Gener    | ated Clocks | Collections | Inputs/Outputs Registers Dela      | ay Paths At   | tributes I/O S | Standards Compile i | Points TCL View   |                     |        |     |         |

Figure 2-5 • Generated Clocks Tab

For RTG4 designs:

- Oscillators or Clock Input ports are typical clock sources.

- Fabric CCC outputs are typical generated clocks.

Synplify Pro supports an advanced copy and paste feature. It is possible to copy objects from the schematic views and paste their names into SCOPE.

For example: Highlight the output terminal pin of the oscillator (in the RTL view schematic), copy (CTRL + C) and then paste (CTRL + V) into SCOPE.

### I/O Delay Constraints

Clock constraints are not sufficient to constrain I/O ports. Use input and output delay constraints (set\_input\_delay, set\_output\_delay) constraints to specify I/O constraints. Navigate to the Inputs/Outputs tab in SCOPE to do so (Figure 2-6).

| Ņ    | # 0      | 10 10 10 1                         | B 4 6 4 9 8 8             | 303            |              | -) Q, Q,  | 0,0,0    | * * * *             |            |           |       |         |

|------|----------|------------------------------------|---------------------------|----------------|--------------|-----------|----------|---------------------|------------|-----------|-------|---------|

| Ð    | II 0-0   | PRR A                              | ಿ ೧ 🚺 👂 🖗 😁 🛤             |                |              |           |          |                     |            |           |       |         |

| urre | nt Desig | n: <pre><top level=""></top></pre> |                           | - ( <b>/</b> a | heck Constra | ints      |          |                     |            |           |       |         |

|      | Enable   | Delay Type                         | Port                      | Rise           | Fall         | Max       | Min      | Clock               | Clock Fall | Add Delay | Value | Comment |

| 1    | •        | input                              | p:data_bus_in_clk_core*   |                |              | •         |          | c:clk_core          |            |           | 2.5   |         |

| 2    | •        | input                              | p:data_bus_in_clk_core*   |                |              |           | •        | c:clk_core          |            |           | 1.0   |         |

| 3    | 4        | output                             | p:data_bus_out_clk_core*  |                |              | •         |          | c:clk_core          |            |           | 3.0   |         |

| 4    | 4        | output                             | p:data_bus_out_clk_core*  |                |              |           | 4        | c:clk_core          |            |           | 1.5   |         |

| 5    |          |                                    |                           |                |              |           |          |                     |            |           |       |         |

| 5    |          |                                    |                           |                |              |           |          |                     |            |           |       |         |

| 1    |          |                                    |                           |                |              |           |          |                     |            |           |       |         |

| 3    |          |                                    |                           |                |              |           |          |                     |            |           |       |         |

| Clo  | cks      | Generated Clocks Coll              | ections Inputs/Outputs Re | gisters (      | Delay Paths  | Attribute | ¢ 1/0 St | tandards Compile Po | ints TCL   | View      |       |         |

Figure 2-6 • Inputs/Outputs Tab

### **Constraint Checker**

To check the constraints entered so far, click on the **Check Constraints** button on the menu bar. Synplify Pro generates a clock constraint check report (\*\_cck.rpt). The summary should indicate that no issues are found with the timing constraints.

Constraint checker is also accessible from the Project menu (Project > Run > Constraint Check).

### Exceptions

Some designs require additional timing constraints known as timing exceptions, such as:

- set\_false\_path

- set\_max\_delay

- set\_multicycle\_path

To enter timing exceptions in SCOPE navigate to the Delay Paths tab. After saving the file, from the **File** menu choose **Close** to return to the Project view.

## **Using the Forward Annotated SDC**

After synthesis, Synplify Pro generates a SDC file that you can use for the remaining steps in the Libero flow. This file (with extension \*\_sdc.sdc) is available under Timing Constraints in the Libero Project view.

By default, this file is not used by Libero. The recommended flow is to create separate constraints for Synthesis and Timing-Driven Place and Route steps.

Users must review the file contents of the Synplify generated forward annotated file before enabling the file for implementation. To enable a SDC file for Timing-Driven Place and Route, right-click the file and choose **Use for Compile**. Libero uses this SDC file for the remaining steps in design flow, starting from Compile.

#### Limitations

- The forward annotated SDC file from Synplify Pro does not include any set\_clock\_latency constraints present in the original user SDC file.

- Synplify Pro does not automatically generate clock constraints for oscillators or CCC instances. You must supply accurate clock constraints (create\_clock, create\_generated\_clock) to Synplify Pro. These constraints are then forward annotated in the \*\_sdc.sdc file.

## **Timing Constraints for Timing-Driven Place and Route**

Libero tools (Timing Driven Place and Route and SmartTime) support a subset of Synopsys SDC timing constraints relevant for FPGA designs. To set timing constraints, you can use:

- SmartTime Constraint Wizard

- SmartTime Constraint Editor

- SDC file(s)

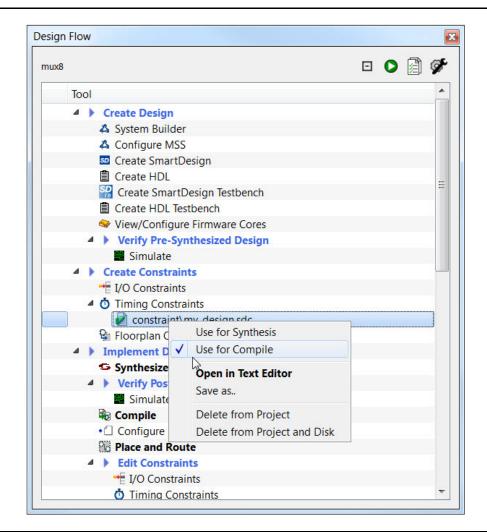

To organize the timing constraint files, use the "Organize Constraint Files" dialog box. When importing a SDC file for Timing Driven Place and Route, make sure to include it for use by the Compile tool. To enable a SDC file already imported in Libero, right-click on the file and choose **Use for Compile** (refer to Figure 2-7).

Figure 2-7 • SDC File for Compile

## **Timing-Driven Place and Route Constraints**

SmartTime Timing Analysis supports the following set of SDC timing constraints:

- create\_clock

- create\_generated\_clock

- set\_input\_delay

- set\_output\_delay

- set\_external\_clock

- set\_clock\_to\_output

- set\_false\_path

- set\_multicycle\_path

- set\_max\_delay

- set\_min\_delay

- set\_clock\_latency

- set\_clock\_uncertainty

- set\_disable\_timing

For details on the options and arguments of the SDC commands, refer to the SmartTime online help.

## **Constraints for Design Requirements**

Microsemi recommends that you use the following flow to enter timing constraints:

- 1. SmartTime Constraint Wizard Identify clocks, input and output delay constraints

- 2. I/O Attributes Editor Provide complete I/O attributes information for the design

- 3. Generate and analyze the Constraints Coverage report

#### SmartTime Constraint Wizard

SmartTime includes a Constraint Wizard that enables quick and easy entry for clock and I/O constraints (Figure 2-8).

| Introduction                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Overall clock<br>constraint<br>Overall I/O<br>constraint<br>Specific clock<br>constraints<br>Generated clock<br>constraints<br>Specific input<br>constraints<br>Specific output<br>constraints | The constraints created by the Wizard can be modified later from<br>the Constraints Editor.<br>You can use the Wizard sequentially by clicking Nest at each<br>screen.<br>Alternatively, you can access each individual step in the Wizard by<br>cloking a step in the Constraint Wizard flow, available on the left<br>column of this window.<br>All steps in this Wizard are optional. Click Finish et any time to skip<br>the remaining steps. |  |

| Summary                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

#### Figure 2-8 • SmartTime Constraint Wizard

Invoke the Constraint Wizard from SmartTime (Tool > Constraint Wizard).

The Constraint Wizard enables you to add constraints in the following order:

- 1. Overall clock constraint

- 2. Overall I/O constraint

- 3. Specific clock constraints

- 4. Generated clock constraints

- 5. Specific input constraints

- 6. Specific output constraints

Use the Overall constraint tabs to set default constraints for clocks and I/Os.

The default constraints can be overridden by the Specific constraints for clocks and I/Os.

#### **Clock Constraints**

Use the Specific clock and Generated clock constraint tabs for:

- Oscillators used as clock sources.

- Fabric CCC outputs used as generated clocks

Clocks from other sources

### I/O Constraints

Use the Overall I/O constraint tab to set default constraints for all input and output ports in the design. The default I/O constraints can be overridden in the Specific input and Specific output constraint tabs for selected ports.

For details about the Constraint Wizard, refer to the SmartTime online help.

### I/O Attributes and the I/O Attribute Editor

Timing performance of I/O paths is significantly influenced by the I/O attributes.

Use the I/O Attribute Editor feature in the MultiView Navigator (MVN) tool to provide complete I/O attribute information for the design.

For details about the I/O Attribute Editor, refer to the MultiView Navigator online help.

#### Constraint Coverage

It is important to generate a Constraints Coverage Report (Figure 2-9), because the timing report only analyzes timing performance for design paths with timing constraints. Timing paths without timing constraints may have timing violations and are not be reported. Invoke the Constraint Coverage report from SmartTime Analyzer (**Tools > Reports > Constraint Coverage**).

| File Actions Help                                                                                                                    |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                            |                                                                                                                                                |     |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| martTime Version                                                                                                                     | n v11.3                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                            |                                                                                                                                                |     |

| Design                                                                                                                               |                                                                                                          | aa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                            |                                                                                                                                                |     |

| Family                                                                                                                               |                                                                                                          | SmartFusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | n2                                         |                                                                                                                                                |     |

| Die                                                                                                                                  |                                                                                                          | M2S100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                            |                                                                                                                                                |     |