# TU0827 Tutorial PolarFire FPGA Debugging Using Splash Kit

Power Matters."

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

© 2018 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

# Contents

| 1 | Revis | sion History                                                       | 1 |

|---|-------|--------------------------------------------------------------------|---|

|   | 1.1   | Revision 1.0                                                       |   |

| 2 | Polar | Fire FPGA Debugging Using Splash Kit                               |   |

|   | 2.1   | Design Requirements                                                |   |

|   | 2.2   | Prerequisites                                                      |   |

|   | 2.3   | Demo Design                                                        |   |

|   | 2.4   | Clocking Structure                                                 |   |

|   | 2.5   | Programming the Device                                             |   |

|   | 2.6   | Launching SmartDebug from Libero                                   |   |

|   | 2.7   | Debugging the Design                                               |   |

|   |       | 2.7.1 View Device Status                                           |   |

|   |       | 2.7.2 Debug FPGA Array                                             |   |

|   |       | 2.7.3 Debug µPROM                                                  |   |

|   |       | 2.7.4         sNVM Debug           2.7.5         Debug TRANSCEIVER |   |

|   | 2.8   | Conclusion                                                         |   |

| 3 | Appe  | endix: Known Issues                                                |   |

|   | 3.1   | Probe Points Write Issue                                           |   |

|   | 3.2   | Data Traffic Errors on XCVR Lanes in CDR Mode                      |   |

| 4 | Appe  | endix: References                                                  |   |

# **Figures**

| Figure 1  | SmartDebug Top-Level Blocks            | 3 |

|-----------|----------------------------------------|---|

| Figure 2  | XCVR_Debug Overall Design Blocks       | 4 |

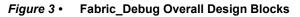

| Figure 3  | Fabric_Debug Overall Design Blocks     | 4 |

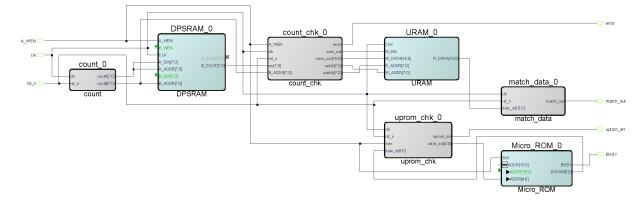

| Figure 4  | Clocking Structure                     | 5 |

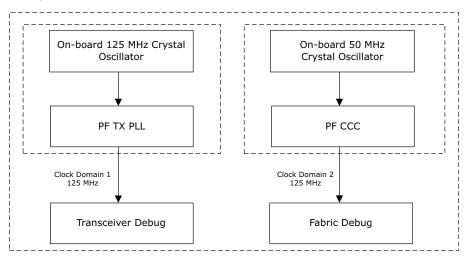

| Figure 5  | Board Setup                            | 3 |

| Figure 6  | Programming the Device                 | 3 |

| Figure 7  | Launching SmartDebug Design            | 3 |

| Figure 8  | SmartDebug Window Debug Options        | 7 |

| Figure 9  | Device Status Report Sample            | 7 |

| Figure 10 | Debug FPGA Array—Live Probes           | 3 |

| Figure 11 | Debug FPGA Array—Active Probes         | 9 |

| Figure 12 | Pseudo-static Signal Polling           |   |

| Figure 13 | Debug FPGA Array—Memory Blocks         | C |

| Figure 14 | Memory Blocks—Read Block               |   |

| Figure 15 | Memory Blocks—Write Block              | 1 |

| Figure 16 | Debug FPGA Array—Probe Insertion       | 1 |

| Figure 17 | µPROM Debug                            | 2 |

| Figure 18 | sNVM Debug                             | 2 |

| Figure 19 | sNVM Debug—Client View                 |   |

| Figure 20 | Secured NVM Details                    |   |

| Figure 21 | sNVM Debug—Page View                   | 4 |

| Figure 22 | Configuration Report                   | 4 |

| Figure 23 | Debug TRANSCEIVER—Smart BERT 15        |   |

| Figure 24 | Smart BERT—Error Counter               | 5 |

| Figure 25 | Debug TRANSCEIVER—Loopback Modes 16    | 3 |

| Figure 26 | Static Pattern Transmit                |   |

| Figure 27 | Recommended Settings for Eye Monitor   | 7 |

| Figure 28 | Debug TRANSCEIVER—Eye Monitor          | 3 |

| Figure 29 | Signal Integrity                       |   |

| Figure 30 | Programming Connectivity and Interface | ) |

# **Tables**

| Table 1 | Design Requirements | . 2 |

|---------|---------------------|-----|

| Table 2 | Jumper Settings     | . 5 |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the current publication.

## 1.1 Revision 1.0

The first publication of this document.

# 2 PolarFire FPGA Debugging Using Splash Kit

Design debug is a critical phase of the FPGA design flow. Microsemi's SmartDebug enables debugging of PolarFire devices in real time, and it does not require any other internal logic analyzer (ILA).

SmartDebug supports the following features:

- Device Status View

- FPGA Array Debug

- sNVM Debug

- µPROM Debug

- Transceiver Debug

These features enable designers to check the state of inputs and outputs in real time, without any relayout of the design.

The built-in probe points of the PolarFire device and the probe capabilities of SmartDebug enable the real-time debug features.

SmartDebug provides the following capabilities:

- Live probes: Two dedicated probes can be configured to observe a probe point. The probe point may be any output of a register. After selecting the probe points, the probe data can be sent to two dedicated pins (PROBE\_A and PROBE\_B). You can connect an oscilloscope to the probe pins and monitor the signal status.

- Active probes: It allows dynamic asynchronous read and write to a flip-flop or probe point. This

enables user to quickly observe the output of the logic internally, or to quickly experiment on how the

logic is affected by writing to a probe point.

- **Debug memory:** SmartDebug provides the Memory Blocks tab to dynamically and asynchronously read from and write to a selected FPGA fabric SRAM block.

- sNVM debug capabilities: It enables reading each page or multiple pages from sNVM.

- **Probe insertion:** It is a post-layout process that enables you to insert probes into the design and gets the signals out to the FPGA package pins to evaluate and debug the design.

- TRANSCEIVER debug capabilities: It makes debugging of high-speed serial designs simple. The SmartDebug JTAG interface extends access to configure, control, and observe XCVR operations and is accessible in every TRANSCEIVER design. The designs are implemented using the Libero System Builder to incorporate the TRANSCEIVER block enabling XCVR access from the SmartDebug. The Debug TRANSCEIVER window displays real-time system and the lane status information. XCVR configurations are supported with TCL scripting, allowing access to the entire XCVR register map for real-time customized tuning.

This tutorial provides a demo design to demonstrate SmartDebug's capabilities, which are used to perform real-time signal integrity testing and debugging.

## 2.1 Design Requirements

The following table lists the hardware, software, and IP requirements for this demo design.

#### Table 1 • Design Requirements

| Requirement                                                                                                                                                         | Version                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Operating system                                                                                                                                                    | 64-bit Windows 7 or 10 |

| Hardware                                                                                                                                                            |                        |

| PolarFire Splash Kit (MPF300TS-1FCG484EES)<br>– PolarFire Splash Board<br>– 12 V/5 A power adapter and cord<br>– USB 2.0 A to mini-B cable for UART and programming | Rev 2 or later         |

Table 1 • Design Requirements (continued)

| Requirement                       | Version |

|-----------------------------------|---------|

| Software                          |         |

| Libero <sup>®</sup> SoC PolarFire | v2.1    |

| IP                                |         |

| PF_INIT_MONITOR                   | 2.0.101 |

| CORERESET_PF                      | 2.1.100 |

| PF_XCVR_REF_CLK                   | 1.0.103 |

| PF_TX_PLL                         | 1.0.109 |

| PF_XCVR_REF_CLK                   | 1.0.103 |

| PF_CCC                            | 1.0.112 |

| CORESMARTBERT                     | 2.0.106 |

| PF_UPROM                          | 1.0.108 |

| PF_URAM                           | 1.1.107 |

| PF_DPSRAM                         | 1.1.110 |

## 2.2 **Prerequisites**

Before you start:

- 1. Download the design files from the following link: http://soc.microsemi.com/download/rsc/?f=mpf\_tu0827\_liberosocpolarfirev2p1\_df

- Download and install Libero SoC PolarFire v2.1 from the following location: https://www.microsemi.com/products/fpga-soc/design-resources/design-software/libero-soc-polarfire#downloads

# 2.3 Demo Design

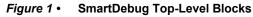

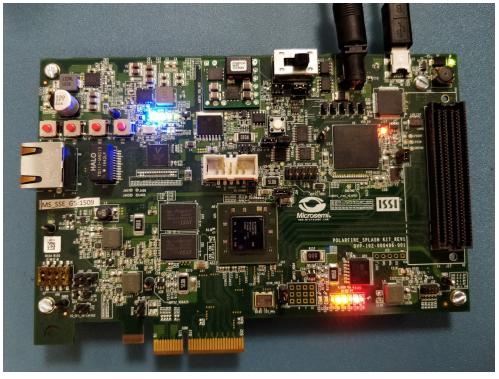

The design consists of five main blocks: the XCVR debug block (XCVR\_Debug), the fabric debug block (Fabric\_Debug), PF\_INIT\_MON block, PF\_CCC, and Reset\_des\_sync\_0 as shown in Figure 1, page 3.

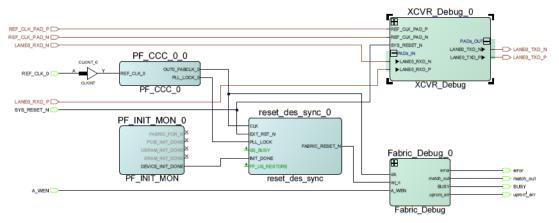

XCVR\_Debug: The XCVR\_Debug block demonstrates SmartDebug's real-time signal integrity (SI) testing and debugging capabilities to test and debug the PolarFire transceiver. The XCVR\_Debug block consists of a CoreSmartBERT core along with TX\_PLL and XCVR\_REF\_CLK macros. It implements the PolarFire transceiver in PMA mode.

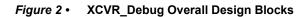

Fabric\_Debug: The Fabric\_Debug block demonstrates several FPGA fabric debug features of SmartDebug. First, it demonstrates SmartDebug's FPGA array debugging capabilities using a counter that loads a counting pattern into the LSRAM instance (DPSRAM). The data value of the LSRAM block is the same as the address value of the block. On the read side of the LSRAM, a count checker (count\_chk) ensures that the count progresses as expected. If there is an error, the output (error) is latched high. Second, the Fabric\_Debug block demonstrates the debug µPROM feature of SmartDebug using a µPROM instance. Third, the Fabric\_Debug block demonstrates how to set live probes to monitor an internal user-selected point on the device in real time, and how to set active probes for dynamic asynchronous read and write to a flip-flop or probe point. These features help to quickly observe the output of the logic internally or quickly experiment to determine how the logic is affected by writes to a probe point. Lastly, the Fabric\_Debug block demonstrates SmartDebug's capabilities to read and modify fabric SRAM content in real-time.

The PF\_CCC block generates 125 MHz clock. Fabric\_Debug logic works on this clock.

The PF\_INIT\_MON block checks the status of device initialization. When the initialization of SRAM and  $\mu$ PROM is completed, the IP asserts DEVICE\_INIT\_DONE signal. This signal is tied with an external reset and PLL lock.

The reset\_des\_sync\_0 block is an instantiation of CoreRESET\_PF IP. It synchronizes the de-assertion of asynchronous reset.

# 2.4 Clocking Structure

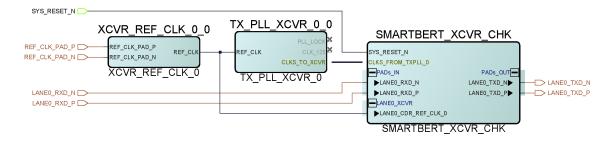

The reference design has two clock domains. As shown in the following illustration, clock domain 1, used for transceiver debug, runs at 125 MHz, and clock domain 2, used for fabric debug, runs at 125 MHz.

#### Figure 4 • Clocking Structure

## 2.5 **Programming the Device**

Before programming the device, SmartBERT probe related constraints need to be generated. The SmartDebug reads and writes to probe points associated with the SmartBERT IP for debugging. JTAG write to some probe points are not working as expected. This is a known issue. A software workaround is provided to determine the working probe points. The constraints need to be updated by following the steps mentioned in Appendix: Known Issues, page 20.

The following steps describe how to program the device on a PolarFire Splash Kit.

1. Ensure that the following jumper settings are followed.

Note: Power-down the board before making the jumper connections.

| Jumper             | Description                                                       |

|--------------------|-------------------------------------------------------------------|

| J11                | Close pin 1 and 2 for programming through FTDI chip               |

| J5, J6, J7, J8, J9 | Close pin 2 and 3 for programming the PolarFire FPGA through FTDI |

| J10                | Open pin 1 and 2 for programming through the FTDI SPI             |

| J4                 | Short pin 1 and 2 for manual power switching using SW1            |

| J3                 | Open pin 1 and 2 for 1.0 V                                        |

2. Connect the power supply cable to the **J2** connector on the board.

3. Connect the USB cable from the Host PC to the **J1** (FTDI port) on the board.

4. Power on the board using the **SW1** slide switch.

#### Figure 5 • Board Setup

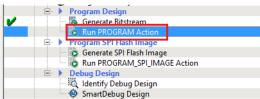

In the **Design Flow** window, select **Run PROGRAM Action**, as shown in the following figure. This programs the design into the device.

#### Figure 6 • Programming the Device

# 2.6 Launching SmartDebug from Libero

On the Design Flow window, double-click SmartDebug Design, as shown in the following figure.

#### Figure 7 • Launching SmartDebug Design

The **SmartDebug** window is displayed, as shown in the following figure.

#### Figure 8 • SmartDebug Window Debug Options

| -         | • •                             |                                       |    |

|-----------|---------------------------------|---------------------------------------|----|

| 🕸 SmartE  | Jebug                           | -                                     | ×  |

| File View | Help                            |                                       |    |

| Device: 🕅 | IPF300T_ES (MPF300T_ES)         | Programmer: E200 IRUX6Y (E200 IRUX6Y) | Ŧ  |

| ID        | code read from device: 2F8131CF |                                       |    |

|           | View Device Status              | Debug FPGA Array                      |    |

|           | Debug UPROM                     | Debug SNVM                            |    |

|           |                                 | Debug TRANSCEIVER                     |    |

|           |                                 |                                       |    |

| Log       |                                 |                                       | ē× |

| Messa     | ages 😵 Errors 🗼 Warnings   info |                                       |    |

|           |                                 |                                       |    |

# 2.7 Debugging the Design

Debugging the device involves the following:

- View Device Status, page 7

- Debug FPGA Array, page 8

- Debug µPROM, page 12

- sNVM Debug, page 12

- Debug TRANSCEIVER, page 14

### 2.7.1 View Device Status

The View Device Status option provides the device status report. It summarizes the device information, programmer information, design information, factory serial number, and security information, if any are set. To view the device status report, click **View Device Status** in the **SmartDebug** window. The following figure shows a sample of the device status information.

#### Figure 9 • Device Status Report Sample

| <b>&gt;</b>     | Device                                                 | Status Report                                                        | ? ×     |

|-----------------|--------------------------------------------------------|----------------------------------------------------------------------|---------|

| Device: MPF3007 | _ES (MPF300T_ES) Programmer: E2001RUX6Y                | r (E200 1RUX6Y) Save                                                 | 🖨 Print |

| Device Status:  |                                                        |                                                                      |         |

|                 | IDCode (read from the device) (HEX):                   | 2F8131CF                                                             |         |

|                 | Device Certificate                                     |                                                                      |         |

|                 | Certificate is valid .                                 |                                                                      |         |

|                 | Design Information                                     |                                                                      |         |

|                 | Design Name:                                           | SmartDebug_Top                                                       |         |

|                 | Design checksum (HEX):<br>Design Version:              | 1E72<br>0                                                            |         |

|                 | Design version:                                        | 0                                                                    |         |

|                 | Digest Information                                     |                                                                      |         |

|                 | Fabric Digest (HEX):                                   | 088bf736dd80439dfc9245f6682e3474<br>bbfc71d71f9f0844a840cfe51e74b781 |         |

|                 | SNVM Digest (HEX):                                     | 55b852781b9995a44c939b64e441ae27<br>24b96f99c8f4fb9a141cfc9842c4b0e3 |         |

|                 | Device Security Settings                               |                                                                      |         |

|                 | Programming Information                                |                                                                      |         |

|                 | Cycle count:                                           | 102                                                                  |         |

|                 | *Algorithm Version:                                    | 1                                                                    |         |

|                 | * Programmer:                                          | FlashPro 5                                                           |         |

|                 | * Software Version:<br>* Programming Software:         | FlashPro version not available<br>FlashPro Express                   |         |

|                 | * Programming Software:<br>* Programming Interface Pro |                                                                      |         |

|                 | * Programming File Type:                               | STAPL                                                                |         |

| NOTE: * - The a | bove Information is only relevant if the device        | was programmed through JTAG or SPI Slave mode.                       |         |

| Help            |                                                        |                                                                      | Close   |

## 2.7.2 Debug FPGA Array

The Debug FPGA Array provides an interface to probe the user logic implemented in the logic elements (LEs) of the FPGA using active and live probes, read-write access to the fabric flip-flops, and read-write access to the memories implemented using LSRAMs/URAMs. Probe insertion allows assignment of the internal signals to the assigned or unassigned pins. These signals can be monitored using the oscilloscope in real-time. The Debug FPGA Array supports the following four features:

- Live Probes

- Active Probes

- Memory Blocks

- Probe Insertion

#### 2.7.2.1 Live Probes

Live Probes enables the monitoring of two internal signals at a time in the design without having to repeat place and route. PolarFire devices have two dedicated live probe channels (for example, pin H6 and G6 of PolarFire MPF300TS device).

To use Live Probes, reserve pins using **Reserve Pins for Probes** under **Constraints Manager** in Libero SoC PolarFire. If you do not reserve pins for live probes, the live probe I/O's function as GPIOs and are used for routing nets in the design. The following figure shows the **Live Probes** tab.

Figure 10 • Debug FPGA Array—Live Probes

| Hierarchical View Netlist View |        | Live Probes Active Probes Memory Blocks Probe Insert        | tion                 |            |

|--------------------------------|--------|-------------------------------------------------------------|----------------------|------------|

| Filter:                        | Search |                                                             | Delete               | Delete All |

|                                |        | Name                                                        | Туре                 | • •        |

| Instance(s):                   | Add    | Fabric_Debug_0/count_0_coutA[7]:Fabric_Debug_0/count_0/cout | A[7]:Q DFF           |            |

|                                |        | Fabric_Debug_0/count_0_coutA[6]:Fabric_Debug_0/count_0/cout | A[6]:Q DFF           |            |

| E Serdes_Debug_0               |        | Fabric_Debug_0/count_0_coutA[5]:Fabric_Debug_0/count_0/cout | A[5]:Q DFF           |            |

|                                |        | Fabric_Debug_0/count_0_coutA[4]:Fabric_Debug_0/count_0/cout | A[4]:Q DFF           | -          |

|                                |        | Assign to Channel A -> Fabric_Debug_0/count_0_coutA[7]:Fa   | abric_Debug_0/count_ | Unassign   |

|                                |        | Assign to Channel B ->                                      |                      | Unassign   |

|                                |        |                                                             |                      |            |

|                                |        |                                                             |                      |            |

### 2.7.2.2 Active Probes

Active Probes enables to read or change the values of probe points in a design through JTAG. Active Probes dynamically and asynchronously read or write to any logic element register bit. The probe points of a design are selected using active probes. Active probes are useful for a quick observation of an internal signal. All of the probe points for the design are displayed in **Hierarchical View** and **Netlist View** in the left pane of the **Active Probes** tab.

- Hierarchical View: Available probe points are listed in hierarchical order.

- Netlist View: Available probe points are listed with the Name and Type, which are physical locations

of flip-flops.

To add probe points to a list:

- 1. Select the Active Probes tab in the right pane. The probe signals are displayed in the left pane.

- 2. Select the probe points that you want to add from the Hierarchical View or Netlist View in the left pane.

- 3. Right-click the selected points and click **Add** to add them to the **Active Probes**. You can also add the selected probe points by clicking Add in the top-right corner of the left pane. The probes signals can be filtered with the **Filter** option.

- 4. Click Read Active Probes to read the content of the registers added to the window.

Figure 11 • Debug FPGA Array—Active Probes

| 1                                 | Debug FPGA Array                                        |                 |            | - 🗆 🗙       |

|-----------------------------------|---------------------------------------------------------|-----------------|------------|-------------|

|                                   |                                                         |                 |            |             |

| Live/Active Probes Selection      | FPGA Array debug data                                   |                 |            |             |

| Hierarchical View Netlist View    | Live Probes Active Probes Memory Blocks Probe Insertion |                 |            |             |

| Filter: Search                    | + - + + Save                                            | Load            | Delete     | Delete All  |

|                                   |                                                         | Туре            | Read Value | Write Value |

| Instance(s):Add                   | error_c:Fabric_Debug_0/count_chk_0/error:Q              | DFF             | 0          |             |

| Fabric Debug_0     H III URAM 0 0 | Eabric_Debug_0/count_chk_0/match_cnt[7:0]               | DFF             | 8'h71      | 8'h         |

|                                   | Read Active Probes Save Active Probes' Data Write       | e Active Probes |            |             |

| Help                              |                                                         |                 |            | Close       |

5. To use pseudo static signal polling, on the **Active Probes** tab, right-click any probe point and select **Poll**, as shown in the following figure.

Static signal polling is used to check whether the logical bit value is changed to expected polled value.

Figure 12 • Pseudo-static Signal Polling

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Debug IPGK Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | - 0      | •                                                                | Pseudo-static signal polling                                                                                                                                      | 7 ×                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| in the blocks of X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | POLins blog blo<br>Lachder Athender   Neury Bols   hdetaeter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     | Deine al | Signal : error_cPabric_Debug_5)<br>Poling Setup<br>IP Poli for 0 | kount_shk_SherroriQ<br>(* Poli for 1                                                                                                                              |                             |

| Internet/         AU           0         60 (der, 2)         0           0         60 (der, 2)         0           0         60 (der, 2)         0           0         80 (der, 2)         0 | References from the second sec | 97 (A) (A)          |          |                                                                  | d once per second. It should be used for penudo-static signals that<br>it penudo-static signal poling, did the Help button.<br>Start Palling <u>Start Palling</u> | t do not change frequently. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | laarkisehdaa jaarkisehdaa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | L. With Ache Public |          | Heb                                                              |                                                                                                                                                                   | Close                       |

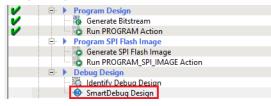

### 2.7.2.3 Memory Blocks

SmartDebug provides the Memory Blocks tab to dynamically and asynchronously read from and write to a selected FPGA fabric SRAM block. Memory blocks are categorized into two views:

- Physical View—shows the actual memory view of the RAM in FPGA

- Logical View—shows a logical representation of RAM block

Using the Memory Blocks tab, you can select the required memory block to:

- Read

- Capture a snapshot of the memory

- Modify memory values, and then write the values back to that block

To read and write memory blocks:

- 1. Select the **Memory Blocks** tab in the right pane of the SmartDebug window.

- 2. View the memory blocks in the left pane in the Hierarchical View.

- 3. Select the memory block in the left pane and click **select** in the top-right corner of the pane.

- 4. Right-click the selected memory block and click **Add**.

The following figure shows the Memory Blocks tab in Debug FPGA Array window.

Figure 13 • Debug FPGA Array—Memory Blocks

| Debug FPGA Array                                                                                      |                                                                                             |   |   |   |                |               |              |                |              |              |                |             |              |              | - 0            |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---|---|---|----------------|---------------|--------------|----------------|--------------|--------------|----------------|-------------|--------------|--------------|----------------|

| Memory Blocks Selection     Image: Selection       Filter:     Select       Memory Blocks:     Select | FPGA Array debug data<br>Live Probes Active Pro<br>User Design Memory Block:<br>Data Width: |   |   |   | PSRAM_0/Fabric | c_Debug_DPSRA | M_0_DPSRAM_) | <_0/Fabric_Deb | oug_DPSRAM_0 | _DPSRAM_K_Fe | abric_Debug_DP | SRAM_0_DPSR | AM_K_0_PF_DP | SRAM_R0C0/IN | NST_RAM1K20_IP |

| Instance Tree                                                                                         | 0 1                                                                                         | 2 | 3 | 4 | 5              | 6             | 7            | 8              | 9            | A            | В              | С           | D            | E            | F              |

|                                                                                                       |                                                                                             |   |   |   |                | Read Block    | Save Bloc    | k Data         | Write Block  |              |                |             |              |              |                |

| Help                                                                                                  |                                                                                             |   |   |   |                |               |              |                |              |              |                |             |              |              | Close          |

5. Click **Read Block**. The specified memory block is read as shown in the following figure.

Figure 14 • Memory Blocks—Read Block

| ter: Search                                          | Live Prob              | es Active          | Probes M               | emory Blocks | Probe Inser   | tion ]      |               |             |            |               |             |             |              |              |              |             |           |          |

|------------------------------------------------------|------------------------|--------------------|------------------------|--------------|---------------|-------------|---------------|-------------|------------|---------------|-------------|-------------|--------------|--------------|--------------|-------------|-----------|----------|

| mory Blocks: Select                                  | User Desi<br>Data Widt | gn Memory B<br>ih: | lock: Fabric<br>10-bit |              | ric_Debug_DPS | RAM_0_DPSRA | M_0/Fabric_De | ebug_DPSRAM | 0_DPSRAM_K | 0/Fabric_Debu | Ig_DPSRAM_0 | DPSRAM_K_Fa | bric_Debug_D | PSRAM_0_DPSF | XAM_K_0_PF_0 | PSRAM_R0C0/ | INST_RAM1 | <20_IP   |

| stance Tree                                          |                        | 0                  | 1                      | 2            | 3             | 4           | 5             | 6           | 7          | 8             | 9           | A           | B            | С            | D            | E           | F         | <b>_</b> |

| Fabric_Debug_0  Fabric_DPSRAM_1_0  Fabric_DPSRAM_1_0 | 0000                   | 000                | 001                    | 002          | 003           | 004         | 005           | 006         | 007        | 008           | 009         | 00A         | 006          | 00C          | 00D          | 00E         | 00F       |          |

| P DPSRAM_1_DPS     Primitives                        | 0010                   | 010                | 011                    | 012          | 013           | 014         | 015           | 016         | 017        | 018           | 019         | 01A         | 0 1B         | 01C          | 0 1D         | 01E         | 01F       |          |

| INST_R     Fabric_Debug_DPSRAM     Fabric_Debug_DPSR | 0020                   | 020                | 021                    | 022          | 023           | 024         | 025           | 026         | 027        | 028           | 029         | 02A         | 028          | 02C          | 02D          | 02E         | 02F       |          |

| Pabric_Debug_DPsk     Fabric_Debug_D     Primitives  | 0030                   | 030                | 031                    | 032          | 033           | 034         | 035           | 036         | 037        | 038           | 039         | 03A         | 038          | 03C          | 03D          | 03E         | 03F       |          |

|                                                      | 0040                   | 040                | 041                    | 042          | 043           | 044         | 045           | 046         | 047        | 048           | 049         | 04A         | 048          | 04C          | 04D          | 04E         | 04F       | -        |

|                                                      |                        |                    |                        |              |               |             | _             | Read Block  | Save Block | Data          | Write Block |             |              |              |              |             |           |          |

|                                                      |                        |                    |                        |              |               |             |               |             |            |               |             |             |              |              |              |             |           |          |

- 6. Enter a hexadecimal value in the memory block locations and click **Write Block** to write content into memory.

- **Note:** The counter writes to the SRAM constantly. To prevent the overwrite of the changes that are forced into the SRAM, the writing is stopped by forcing A\_WEN signal value to low through DIP1 (first switch of SW8). This drives a SELECT of a MUX that selects between high and low inputs. When DIP1 is asserted, A\_WEN becomes low, which prevents any write from the counter to the SRAM block.

7. Switch On DIP1, enter a hexadecimal value in the memory block location(s) and click Write Block to write the modified value to the SRAM, as shown in the following figure.

Figure 15 • Memory Blocks—Write Block

- The error LED(P8) light turns on, indicating an error in the counting pattern. 8.

- 9 Go to Active Probes tab, read the value of error signal, it should show '1'. To use static signal polling, right-click error c:Fabric Debug 0/count chk 0/error:Q and select Poll (Poll for 0), as shown in Figure 12, page 9.

- 10. Move DIP1 to off state to resume the write operation from the counter to the SRAM. This overwrites the error that was injected into the SRAM. Check the status of LED, it must turn off. Hit the Poll for 0, User value match message should appear on the polling window. Close the Pseudo-static signal polling window.

- 11. The content of the SRAM can be rechecked by clicking **Read Block** in the **Memory Blocks** tab.

#### 2.7.2.4 Probe Insertion

Probe insertion is a post-layout debug process that enables internal nets in the FPGA design to be routed to unused or used I/Os. Nets are selected and assigned to probes using the Probe Insertion tab in SmartDebug. The rerouted design is reprogrammed automatically by Libero into the FPGA, where an external logic analyzer or oscilloscope can be used to view the activity of the probed signal. The following figure shows the Probe Insertion tab in the Debug FPGA Array window.

Figure 16 • Debug FPGA Array—Probe Insertion

| e Insertion Data Selection     | ₽×     | FPGA Array debug da | ta                                                              |

|--------------------------------|--------|---------------------|-----------------------------------------------------------------|

| Hierarchical View Netlist View |        | Live Probes Ac      | tive Probes Memory Blocks Probe Insertion                       |

| Filter:                        | Search |                     | Delete All                                                      |

|                                |        | Net                 | Driver                                                          |

| Instance(s):                   | Add    | B_DOUT_c[15]        | Fabric_Debug_0/DPSRAM_1_0/DPSRAM_1_0/DPSRAM_1_DPSRAM_1_0_PF_DPS |

| Instance Tree                  |        | B_DOUT_c[14]        | Fabric_Debug_0/DPSRAM_1_0/DPSRAM_1_0/DPSRAM_1_DPSRAM_1_0_PF_DPS |

| A_WEN_ibuf     Fabric_Debug_0  |        | B_DOUT_c[13]        | Fabric_Debug_0/DPSRAM_1_0/DPSRAM_1_0/DPSRAM_1_DPSRAM_1_0_PF_DPS |

|                                |        | B_DOUT_c[12]        | Fabric_Debug_0/DPSRAM_1_0/DPSRAM_1_0/DPSRAM_1_DPSRAM_1_0_PF_DPS |

|                                |        | B_DOUT_c[11]        | Fabric_Debug_0/DPSRAM_1_0/DPSRAM_1_0/DPSRAM_1_DPSRAM_1_0_PF_DPS |

| 🕀 🎫 Serdes_Debug_0             |        | •                   | • • • • • • • • • • • • • • • • • • •                           |

|                                |        |                     | Insert probe(s) and program the device Run                      |

|                                |        |                     |                                                                 |

|                                |        |                     | Insert probe(s) and program the device Run                      |

## 2.7.3 Debug µPROM

SmartDebug enables debugging  $\mu$ PROM and reading its  $\mu$ PROM contents. The clients added in the design can be debugged using the SmartDebug Debug  $\mu$ PROM feature.

- 1. Click **Debug μPROM** in the **SmartDebug** window. The **μPROM Debug** window is displayed as shown in the following figure.

- Select Initialization in the User Design View tab and then click Read from Device to read the μPROM content. Check whether the content provided in uprom.mem file (part of design stimulus files) matches with the data read from μPROM.

Figure 17 • µPROM Debug

| Client       | 1     | Start Address |   |   |   |   |   |       | Number of w | vords |          |          |          |          |          |   |

|--------------|-------|---------------|---|---|---|---|---|-------|-------------|-------|----------|----------|----------|----------|----------|---|

| nitializatio | on Ot | ×0            | 3 |   |   |   |   |       |             |       |          |          |          |          |          |   |

|              |       |               |   |   |   |   |   |       |             |       |          |          |          |          |          |   |

|              |       |               |   |   |   |   |   |       |             |       |          |          |          |          |          |   |

|              |       |               |   |   |   |   |   |       |             |       |          |          |          |          |          |   |

|              |       |               |   |   |   |   |   |       |             |       |          |          |          |          |          |   |

|              |       |               |   |   |   |   |   |       |             |       |          |          |          |          |          |   |

|              |       |               |   |   |   |   |   |       |             |       |          |          |          |          |          |   |

|              |       |               |   |   |   |   |   |       |             |       |          |          |          |          |          |   |

|              |       |               |   |   |   |   |   |       |             |       |          |          |          |          |          |   |

|              |       |               |   |   |   |   |   |       |             |       |          |          |          |          |          |   |

| Davie        |       |               |   |   |   |   |   |       |             |       |          |          |          |          |          |   |

| om Device    | 2     |               |   |   |   |   |   |       |             |       |          |          |          |          |          |   |

|              | 2     | 1             | 2 | 3 | 4 | 5 | 6 | 7     | 8           | 9     | A        | В        | c        | D        | E        | F |

|              |       | 1             | 2 | 3 | 4 | 5 | 6 | 7 107 | 8           | 9     | A<br>10A | B<br>108 | C<br>10C | D<br>100 | E<br>10E | F |

|              | 0     |               |   |   | - |   |   |       |             |       |          | -        |          |          |          |   |

**Note:** PolarFire devices have a single user programmable read only memory (μPROM) row located at the bottom of the fabric, providing up to 459 Kb of non-volatile, read-only memory. The address bus is 16 bits wide, and the read data bus is 9-bit wide. μPROM is used to store the configuration data, which is used by Fabric logic to process.

### 2.7.4 sNVM Debug

sNVM Debug feature enables reading from the sNVM during debug. Debug Pass Key is required to carry out SNVM\_DEBUG instruction. This feature supports debugging of non-authenticated plain text, authenticated plain text, and clients cipher authenticated.

- 1. Click **Debug SNVM** in the **SmartDebug** window.

- 2. Click the **Client View** tab. The client view details are listed—Client Names, Start Page, Number of Bytes, Write Cycles, Page Type, Used as ROM, and USK Status.

- 3. Select a client from the list in the **Client View** and click **Read from Device** as shown in the following figure.

#### Figure 18 • sNVM Debug

|   | ist $ abla$            | Start Page | End Page | Number of Bytes | write cycles | Page Type  | Used as ROM | USK status |  |

|---|------------------------|------------|----------|-----------------|--------------|------------|-------------|------------|--|

|   | _STAGE_2_3_SNVM_CLIENT |            |          |                 |              |            | No          |            |  |

|   | Page 8                 | 8          |          | 252             | 127          | Plain Text | No          | N/A        |  |

|   | Page 7                 | 7          |          | 252             | 127          | Plain Text | No          | N/A        |  |

|   | Page 6                 | 6          |          | 252             | 132          | Plain Text | No          | N/A        |  |

|   | Page 5                 | 5          |          | 252             | 134          | Plain Text | No          | N/A        |  |

| J | Page 4                 | 4          |          | 252             | 139          | Plain Text | No          | N/A        |  |

| F | Page 3                 | 3          |          | 252             | 199          | Plain Text | No          | N/A        |  |

|   | Page 2                 | 2          |          | 252             | 201          | Plain Text | No          | N/A        |  |

|   | Page 1                 | 1          |          | 252             | 201          | Plain Text | No          | N/A        |  |

|   | Page 0                 | 0          |          | 252             | 320          | Plain Text | No          | N/A        |  |

|   | _STAGE_1_SNVM_CLIENT   | 219        | 220      |                 |              |            | No          |            |  |

|   | Page 220               | 220        |          | 252             | 335          | Plain Text | No          | N/A        |  |

The following figure shows the **Client View** window.

#### Figure 19 • sNVM Debug—Client View

| Client Vie                 | ew Page View                                                                                                         | \                                                                                            |                            |                |      |               |               |               |                    |         |            |         |           |               |               |

|----------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------|----------------|------|---------------|---------------|---------------|--------------------|---------|------------|---------|-----------|---------------|---------------|

| Refresh                    | n Client Details                                                                                                     |                                                                                              |                            |                |      |               |               |               |                    |         |            |         |           |               |               |

| Client L                   | List                                                                                                                 | V S                                                                                          | art Page                   | End Pag        | e    | Number of E   | Bytes W       | rite cycles   | Page T             | [ype    | Used as RO | M US    | SK status |               |               |

|                            | T_STAGE_2_3_SN                                                                                                       | /M_CLIENT 0                                                                                  |                            | 3              |      |               |               |               |                    |         | No         |         |           |               |               |

|                            | Page 3                                                                                                               | 3                                                                                            |                            |                |      | 252           | 18            |               | Plain 1            |         | No         | N       |           |               |               |

|                            | Page 2                                                                                                               | 2                                                                                            |                            | _              |      | 252           | 18            |               | Plain 1            |         | No         | N       |           |               |               |

|                            | Page 0                                                                                                               | 1                                                                                            |                            | _              |      | 252           | 18            |               | Plain 1<br>Plain 1 |         | No         | N/      |           |               |               |

|                            | n Device<br>Intent Retrieved                                                                                         |                                                                                              |                            | IENT".         |      |               |               |               |                    |         |            |         |           | Thu Nov 3     | 30 17:04:     |

|                            | ntent Retrieved                                                                                                      |                                                                                              |                            | IENT".         |      | Vie           | ew All Pag    | e Status      |                    |         |            |         |           | Thu Nov 3     | 30 17:04:     |

|                            | ntent Retrieved                                                                                                      | IIT_STAGE_2                                                                                  |                            | <b>IENT</b> *. | 5    | <br>6         | ew All Pag    | je Status     | 9                  | A       | В          | с       | D         | Thu Nov :     | 30 17:04:     |

|                            | ntent Retrieved                                                                                                      | 11 <b>T_STAGE_2</b>                                                                          | .3_5NVM_CL                 |                | 5 00 |               |               |               | 9 02               | A<br>00 | B          | C<br>08 | D<br>00   |               |               |

| etrieved C                 | Content: Client "II<br>0 1                                                                                           | 11T_STAGE_2                                                                                  | 3_5NVM_CL                  | 4              | -    | 6             | 7             | 8             | -                  |         | -          |         |           | E             | F             |

| etrieved C                 | ontent Retrieved<br>Content: Client "II<br>0 1<br>02 00                                                              | 11T_STAGE_2<br>2<br>0 06<br>0 06                                                             | 3_5NVM_CL                  | 4 10           | 00   | 6<br>E6       | 7             | 8             | 02                 | 00      | BO         | 08      | 00        | E<br>11       | F<br>01       |

| etrieved C<br>0000<br>0010 | Intent Retrieved           Content: Client "II           0         1           02         00           02         00 | IIT_STAGE_2           2           0         06           0         06           0         06 | 3_5NVM_CL<br>3<br>C0<br>C0 | 4<br>10<br>03  | 00   | 6<br>E6<br>00 | 7<br>00<br>00 | 8<br>02<br>02 | 02                 | 00      | BO         | 08      | 00        | E<br>11<br>11 | F<br>01<br>01 |

4. Click **View All Page Status** to view the page status such as Write Cycle Count, Page Type, Use as ROM, and Data Read Status as shown in the following figure.

Figure 20 • Secured NVM Details

| 0                                                           | Secured NVM Details |      | ? ×      |

|-------------------------------------------------------------|---------------------|------|----------|

|                                                             |                     | Save | 🖨 Print  |

| Secured Flash Memory Content [SNVM Pages ]<br>sNVM Page #0: |                     |      | -        |

| Page Status:                                                |                     |      |          |

| Write Cycle Count:                                          | 330                 |      |          |

| Page Type:                                                  | Plaintext           |      |          |

| Use as ROM:                                                 | Off                 |      |          |

| Data Read Status:                                           | Success             |      |          |

| sNVM Page #1:                                               |                     |      |          |

| Page Status:                                                |                     |      |          |

| Write Cycle Count:                                          | 211                 |      |          |

| Page Type:                                                  | Plaintext           |      |          |

| Use as ROM:                                                 | Off                 |      |          |

| Data Read Status:                                           | Success             |      |          |

| sNVM Page #2:                                               |                     |      |          |

| Page Status:                                                |                     |      |          |

| Write Cycle Count:                                          | 211                 |      |          |

| Page Type:<br>Use as ROM:                                   | Plaintext<br>Off    |      |          |

| Data Read Status:                                           | Off<br>Success      |      |          |

| sNVM Page #3:                                               | Success             |      |          |

| Page Status:                                                |                     |      |          |

| Write Cycle Count:                                          | 209                 |      |          |

| Page Type:                                                  | Plaintext           |      |          |

| Use as ROM:                                                 | Off                 |      |          |

| Data Read Status:                                           | Success             |      |          |

| sNVM Page #4:                                               |                     |      |          |

| Page Status:                                                |                     |      |          |

| Write Cycle Count:                                          | 142                 |      |          |

| Page Type:                                                  | Plaintext           |      |          |

| Use as ROM:                                                 | Off                 |      |          |

| Data Read Status:                                           | Success             |      |          |

| sNVM Page #5:                                               |                     |      |          |

| Page Status:                                                | 107                 |      |          |

| Write Cycle Count:                                          | 137                 |      |          |

| Page Type:<br>Use as ROM:                                   | Plaintext<br>Off    |      |          |

| Data Read Status:                                           | Success             |      |          |

| sNVM Page #6:                                               | JULLESS             |      |          |

| Page Status:                                                |                     |      |          |

| Write Cycle Count:                                          | 135                 |      |          |

| Page Type:                                                  | Plaintext           |      |          |

| Use as ROM:                                                 | Off                 |      |          |

| Data Read Status:                                           | Success             |      | <b>•</b> |

| 1                                                           |                     |      | 1        |

| Help                                                        |                     |      | Close    |

|                                                             |                     |      |          |

- 5. Click the **Page View** tab in the **sNVM Debug** window, Page view displays the client details of the required pages. You can read pages from 0-220 in the page view.

- 6. Enter the page number that you want to read in the **Start Page** and **Number of Bytes** in the respective boxes.

- 7. Click Check Page Status. The page status information is displayed as shown in the following figure.

Figure 21 • sNVM Debug—Page View

|          |                       |                 |                                |              | sNVM        | Debug      | - 🗆 🔜    |

|----------|-----------------------|-----------------|--------------------------------|--------------|-------------|------------|----------|

| sNVM Del | ebug<br>t View \ Page | : View          |                                |              |             |            |          |

| Star     | rt page:<br>d Page:   | 0               | Check Page St<br>( 103 Pages ) | atus         |             |            |          |

| Pag      | age List              | Number of Bytes | Page Type                      | Write Cycles | Used as ROM | USK Status | <b>^</b> |

|          | Page 0                | 252             | Plain Text                     | 307          | No          | N/A        |          |

|          | Page 1                | 252             | Plain Text                     | 188          | No          | N/A        | •        |

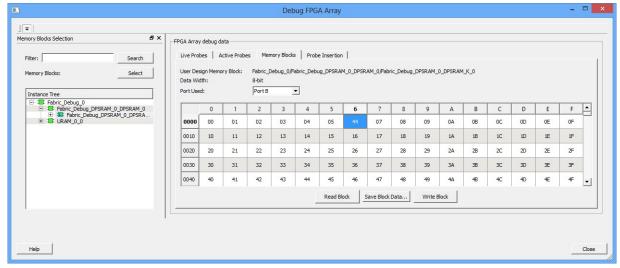

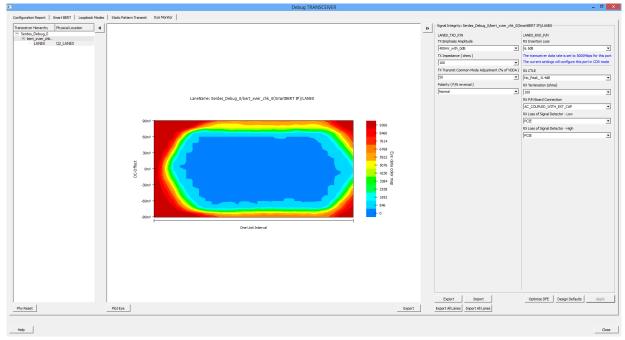

### 2.7.5 Debug TRANSCEIVER

SmartDebug enables transceiver debugging, which includes checking lane functionality and health for different settings of lane parameters. To access the debug transceiver feature, select **Debug TRANSCEIVER** in the **SmartDebug** window. Debug Transceiver supports the following features:

- Configuration Report

- SmartBERT

- Loopback Modes

- Static Pattern Transmit

- Eye Monitor

### 2.7.5.1 Configuration Report

The Configuration Report feature creates a report that shows the physical location, Tx and Rx PLL lock status, and data width of all enabled transceiver lanes. This report includes the following lane parameters:

- Physical Location: Physical location of the transceiver lanes in the system.

- **Tx PMA Ready**: Tx lane of the transceiver is powered up and ready for transactions.

- **Rx PMA Ready**: Rx lane is powered up and ready for transactions.

- **TX PLL**: TX PLL of the transceiver is locked.

- **RX PLL**: RX PLL of the transceiver is locked.

- Data Width: Configured data width of the corresponding lanes in the transceiver.

The following figure shows Configuration Report tab.

#### Figure 22 • Configuration Report

| Lanes             | Serdes_Debug_0/bert_xvier_chk_0(SmartBERT IP) |         |

|-------------------|-----------------------------------------------|---------|

|                   |                                               |         |

| Physical Location | Q2_LANE0                                      |         |

| Tx PMA Ready      |                                               |         |

| Rx PMA Ready      |                                               |         |

| TX PLL            |                                               |         |

| RX PLL            |                                               |         |

| Data Width        | 40 bit                                        |         |

|                   |                                               |         |

|                   |                                               |         |

|                   |                                               |         |

|                   |                                               |         |

|                   |                                               |         |

|                   |                                               |         |

|                   |                                               | Refresh |

### 2.7.5.2 SmartBERT

SmartBERT enables you to run diagnostic tests on the transceiver lanes. SmartBERT uses the PRBS generator and checker functionality available in each transceiver lane to determine the bit error rate (BER) of a lane. The various PRBS patterns supported are PRBS7, PRBS9, PRBS15, PRBS23, and PRBS31. Near-end loopback can be performed using one of these PRBS patterns.

To run SmartBERT in Debug TRANSCEIVER, follow these steps:

- 1. Select the SmartBERT tab in the Debug TRANSCEIVER window.

- 2. Select the Pattern from the drop-down list.

- 3. Select the **EQ-NearEnd** check box to enable internal loop back, (this step can be ignored if external loop back is enabled).

- 4. Click **Start**. It enables both transmitter and the receiver for a particular lane and for a particular PRBS pattern. The following figure shows the status of the TXPLL, RXPLL, Lock to Data, Data rate, and the BER.

Figure 23 • Debug TRANSCEIVER—Smart BERT

| <b>L</b>                                                               |         |                                                         |                                                                                                                | Deb        | ug TRA | NSCEIV | ER           |                        |                  |                                                                                                                                                                    |                                          |

|------------------------------------------------------------------------|---------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------|--------|--------|--------------|------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Configuration Report Smart BERT Loopbad                                | k Modes | Static Pattern Transmit   Eye Monitor                   |                                                                                                                |            |        |        |              |                        |                  |                                                                                                                                                                    |                                          |

| Transceiver Hierarchy Physical Location                                |         |                                                         | Pattern                                                                                                        | EO-NearEnd | TX PLL | RX PLL | Lock to Data | Cumulative Error Count | Data Rate (Gbps) | -Signal Integrity                                                                                                                                                  |                                          |

| E State: Debug 0<br>E State: Debug 0<br>E Horizone<br>E LANEO Q2 LANEO |         | Serder, Debug, O'bert, wier, chi, O'SmartBERT (P)/LANED | PEE223GaveERT P)  PEE233GaveERT P) PEE233GaveERT P) PEE233GaveERT P) PEE233GaveERT P) PEE23 PEE23 PEE23 PEE531 | T Enable   | •      | •      | •            | o                      | 5                | TX<br>TX Trybalas Angliade<br>[J00m] sin _0.00<br>TX Impediance (dvins)<br>TX Taranti Common Mode Adjustment (% of VIDA<br>Si<br>Polarity (P)Trevensal )<br>Pormal | No_Peak_+10.7dB<br>RX Termination (ohms) |

| Phy Reset                                                              |         | 4 Start                                                 |                                                                                                                |            |        |        |              |                        | Stop             | Export Import Optin<br>Export Al Lanes                                                                                                                             | nize DFE Design Defaults Apply           |