# AC471 Application Note PolarFire FPGA Auto Update and In-Application Programming Using Splash Kit

а 🔨 Міскоснір company

Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2018 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# а от Містозеті.

# Contents

| 1 | Revision History                                                                                                                                                                                                                                                           | 1                                            |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2 | PolarFire FPGA Auto Update and In-Application Programming using Splash Kit                                                                                                                                                                                                 | 3<br>5<br>6<br>8<br>9                        |

| 3 | iberoDesign Flow21.1Synthesize.2.2Place and Route.2.3.2.1Resource Utilization.2.3Verify Timing.2.4Generate FPGA Array Data.2.5Configure Design Initialization Data and Memories.2.6Configure Programming Options.2.7Generate Bitstream.2.8Run PROGRAM Action.2             | 23<br>23<br>23<br>23<br>23<br>24<br>26<br>27 |

| 4 | Programming the Device Using FlashPro Software                                                                                                                                                                                                                             | 9                                            |

| 5 | Serial Terminal Emulation Program Setup                                                                                                                                                                                                                                    | 0                                            |

| 6 | Running the Demo       31         Programming the SPI Flash Using Fabric Logic       3         .2       Running Auto Update       3         .3       Running Authentication       3         .4       Running Auto Programming       3         .5       Running IAP       3 | 2<br>4<br>4<br>5                             |

| 7 | ppendix: Programming On-board SPI Flash Using Libero                                                                                                                                                                                                                       | 7                                            |

| 8 | oppendix: References                                                                                                                                                                                                                                                       | 8                                            |

# **Figures**

| Figure 1  | Core System Services IP Interfacing with Fabric User Logic | . 3 |

|-----------|------------------------------------------------------------|-----|

| Figure 2  | Firmware catalog                                           | . 4 |

| Figure 3  | PolarFire Programming Design Block Diagram                 |     |

| Figure 4  | Accessing On-board SPI Flash Using Fabric                  | . 7 |

| Figure 5  | SPI Flash Memory                                           | . 7 |

| Figure 6  | Top Level Libero Design                                    | . 8 |

| Figure 7  | PF_INIT_MONITOR Configuration                              | . 9 |

| Figure 8  | PF_CCC_0 Input Clock Configuration                         |     |

| Figure 9  | PF_CCC_0 Output Clock Configuration                        | 10  |

| Figure 10 | Mi-V Configuration                                         | 11  |

| Figure 11 | UART Configuration                                         | 12  |

| Figure 12 | PF_SRAM_AHBL_AXI Configuration                             | 13  |

| Figure 13 | CoreGPIO_0 Configuration                                   | 14  |

| Figure 14 | CoreSPI Configuration                                      | 15  |

| Figure 15 | CoreSysService_PF Configuration                            | 16  |

| Figure 16 | Memory Map                                                 | 17  |

| Figure 17 | CoreAHBLite_0 Configuration                                | 18  |

| Figure 18 | CoreAHBLite_1 Configuration                                | 19  |

| Figure 19 | CoreAPB3_0 Configuration                                   | 20  |

| Figure 20 | Clocking Structure                                         | 21  |

| Figure 21 | Libero Design Flow Options                                 | 22  |

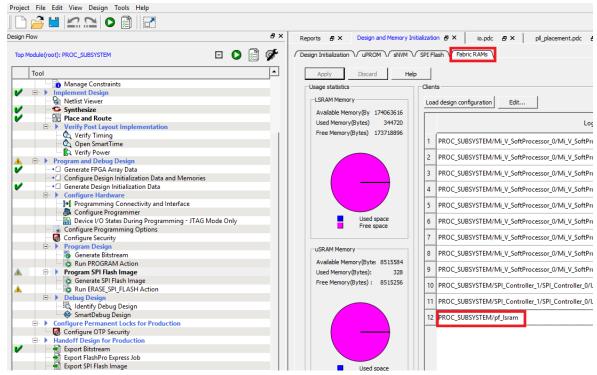

| Figure 22 | Design and Memory Initialization                           | 24  |

| Figure 23 | Fabric RAMs Tab                                            | 25  |

| Figure 24 | Edit Fabric RAM Initialization Client                      | 25  |

| Figure 25 | Apply Fabric RAM Content                                   | 26  |

| Figure 26 | Configure Programming Options                              |     |

| Figure 27 | Generate Bitstream—Configure Bitstream Options             | 27  |

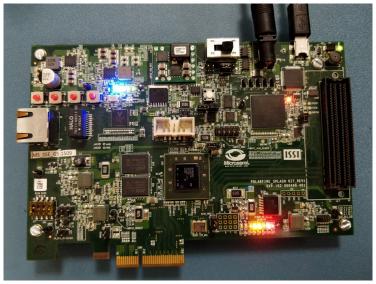

| Figure 28 | Board Setup                                                | 28  |

| Figure 29 | COM Port Number                                            | 30  |

| Figure 30 | Select Serial as the Connection Type                       | 30  |

| Figure 31 | PuTTY Configuration                                        |     |

| Figure 32 | Authentication and Programming Options                     | 32  |

| Figure 33 | Authentication Error                                       | 32  |

| Figure 34 | Erasing SPI Flash                                          | 33  |

| Figure 35 | Command Prompt Status                                      | 34  |

| Figure 36 | Auto Update                                                |     |

| Figure 37 | Successful Bitstream Authentication                        |     |

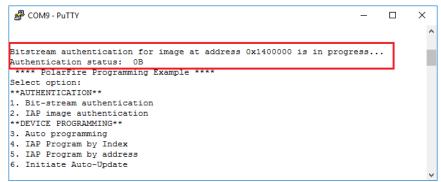

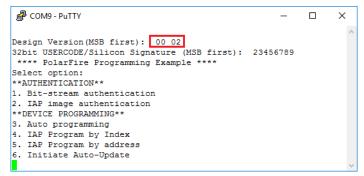

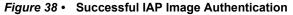

| Figure 38 | Successful IAP Image Authentication                        |     |

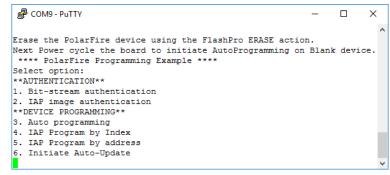

| Figure 39 | Notifying ERASE Action                                     | 35  |

| Figure 40 | Successful Auto Programming                                | 35  |

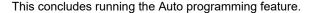

| Figure 41 | Successful IAP at Index 2                                  |     |

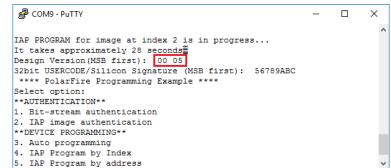

| Figure 42 | Successful IAP by Address                                  |     |

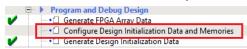

| Figure 43 | Configure Design Initialization Data and Memories Option   |     |

| Figure 44 | SPI Flash Tab                                              |     |

| Figure 45 | SPI Flash Programming                                      | 37  |

# **Tables**

| Table 1 | System Services Descriptor                       |

|---------|--------------------------------------------------|

| Table 2 | Design Requirements                              |

| Table 3 | I/O Signals                                      |

| Table 4 | Resource Utilization                             |

| Table 5 | Jumper Settings for PolarFire Device Programming |

| Table 6 | Jumper Settings for PolarFire Device Programming |

| Table 7 | Programming Images                               |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the current publication.

# 1.1 Revision 2.0

The document was updated for Libero SoC PolarFire v2.2 release.

# 1.2 Revision 1.0

The first publication of this document.

# 2 PolarFire FPGA Auto Update and In-Application Programming using Splash Kit

PolarFire<sup>®</sup> FPGAs support the SPI master programming mode for auto update and in-application programming (IAP). In this programming mode, the programming images are stored in an external SPI flash memory.

Auto update—on power-up, if the version of the update image is found to be different from the current programmed version, the System Controller reads the update image bitstream from the external SPI flash memory and programs the device.

IAP—the user application initiates the program action and the System Controller reads the bitstream from the external SPI flash memory to program the device.

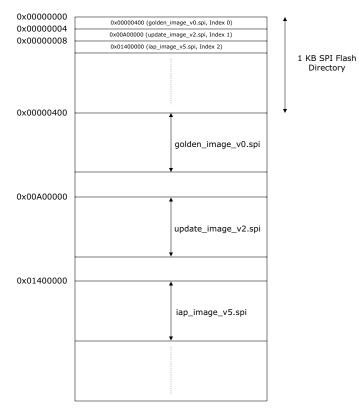

The System Controller supports fetching programming images from SPI Flash device based on the Index value or direct addressing. The SPI directory contains the start addresses of the programming images.

The following components of PolarFire devices are programmable:

- FPGA fabric

- Secure non-volatile memory (sNVM)

- User security settings (keys, passcodes, and locks)

This document explains how to use the accompanying design to demonstrate the auto update and IAP features on the PolarFire Splash kit.

The on-board 1 GB Micron SPI flash device is connected to System Controller SPI and can be programmed using the fabric logic or Libero<sup>®</sup> SoC PolarFire software. For more information about programming the on-board SPI flash using Libero, see Appendix: Programming On-board SPI Flash Using Libero, page 37.

This application note includes the Mi-V soft processor, which initiates the system service requests for the device programming and enables the CoreSysService\_PF IP core to access the System Controller. For more information about the design implementation, and the necessary blocks and IP cores instantiated in Libero SoC PolarFire, see Demo Design, page 6.

This design can be programmed using any of the following options:

- Using the pre-generated.stp file: To program the device using the.stp file provided along with the design, see Programming the Device Using FlashPro Software, page 29.

- Using Libero SoC PolarFire: To program the device using Libero SoC PolarFire, see Libero Design Flow, page 22.

This design can be used as a reference to build a fabric design with programming features.

# 2.1 CoreSysService\_PF IP Overview

System Controller actions are initiated by the fabric logic through the system service interface (SSI) of the System Controller. The fabric logic requires the CoreSysService\_PF IP for initiating the system services. A service request interrupt to the System Controller is triggered when the fabric user logic writes a 16-bit system service descriptor to the SSI. The lower seven bits of the descriptor specify the service to be performed. The upper nine bits specify the address offset (0–511) in the 2 KB mailbox RAM. The mailbox address specifies the service-specific data structure used for any additional inputs or outputs for the service. The fabric logic must write additional parameters to the mailbox before requesting a system service. The following table lists the system service descriptor bits.

#### Table 1 • System Services Descriptor

| Descriptor Bit | Value     |

|----------------|-----------|

| 15:7           | MBOXADDR  |

| 6:0            | SERVICEID |

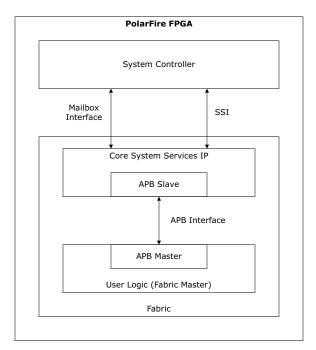

SSI consists of an asynchronous command-response interface that transfers a system service command from the fabric master to the System Controller and the status from the System Controller to the fabric master. The following figure shows how the CoreSysService\_PF IP Interfaces with the fabric logic.

#### *Figure 1* • Core System Services IP Interfacing with Fabric User Logic

The system services driver and the sample SoftConsole project are generated from Firmware Catalog as shown Figure 2, page 4.

In this design, the sample SoftConsole project is migrated to SoftConsole v5.2. The Mi-V soft processor is compatible with only SoftConsole v5.2 or later. The application files <code>main.c</code> and <code>hw\_platform.h</code> are modified to provide the programming user options, system clock frequency, and APB peripheral addresses.

#### Figure 2 • Firmware catalog

| 🞯 Firmware Catalog                     |                                       | _                                       |              |

|----------------------------------------|---------------------------------------|-----------------------------------------|--------------|

| File View Tools Help                   |                                       |                                         |              |

| View ( <u>52/160</u> ):                | Veb repositories                      | <u>Search</u> by all fields ( <u>52</u> |              |

| ✓ display only the latest version of a |                                       |                                         |              |

|                                        |                                       |                                         |              |

| Name                                   |                                       | 🛆 Version                               |              |

| Core10100_AHBAPB Driver                |                                       | 4.0.102                                 |              |

| Core16550 Driver                       |                                       | 2.3.100                                 |              |

| CoreAl Driver                          |                                       | 3.0.101                                 |              |

| CoreAhbNvm Driver                      |                                       | 2.1.102                                 |              |

| CoreDDRTip_PF Driver                   |                                       | 1.0.100                                 |              |

| CoreGPIO Driver                        |                                       | 3.2.101                                 |              |

| Corel2C Driver                         |                                       | 3.2.101                                 |              |

| CoreInterrupt Driver                   |                                       | 2.1.102                                 |              |

| CoreLPC Driver                         |                                       | 2.1.101                                 |              |

| CoreMACFilter Driver                   |                                       | 2.1.100                                 |              |

| CoreMMC Driver                         |                                       | 2.0.100                                 |              |

| CorePWM Driver                         |                                       | 2.3.101                                 |              |

| CoreSDLC Driver                        |                                       | 2.1.100                                 |              |

| CoreSPI Driver                         |                                       | 3.2.101                                 |              |

| CoreSysServices_PF Driver              | 1981 6                                | 2.0.102                                 |              |

| CoreTSE Driver                         | 🔛 Generate                            | 2.3.100                                 |              |

| CoreTimer Driver                       | X Remove from vault                   | 2.3.101                                 |              |

| CoreUARTapb Driver                     |                                       | 3.2.101                                 |              |

| CoreWatchdog Driver                    | Show details                          | 2.2.100                                 |              |

| Hardware Abstraction Layer (HAI        | <b>V</b>                              | 2.3.102                                 |              |

| PolarFire PCle Driver                  | Open documentation                    | 1.0.100 (*)                             |              |

| PolarFire Serdes Driver                | Generate sample project 🔸             | RISC-V SoftConsole v5.1                 | PolarFire Sy |

| PolarFire User Crypto Driver           |                                       | SoftConsole VS.1                        | PolarFire Sy |

| Documentation:                         |                                       |                                         |              |

| CoreSysServices PF Driver UG.pdf       |                                       |                                         | _            |

| CoreSysServices PF Driver RN.pdf       |                                       |                                         |              |

|                                        |                                       |                                         |              |

| Description: Bare metal software d     | river for CoreSysServices_PF Soft IP. |                                         |              |

| Supports all the services supported b  | W CoreSysServices DE Soft ID          |                                         |              |

| Device and design information service  |                                       |                                         |              |

| Design services                        |                                       |                                         | <b>•</b>     |

|                                        |                                       |                                         |              |

| New cores are available for do         | wnload Download them now!             |                                         | 🔛 Generate   |

|                                        |                                       |                                         |              |

|                                        |                                       |                                         |              |

|                                        |                                       |                                         | //           |

# 2.2 Design Requirements

The following table lists the resources required to run the design.

| Requirement                                                                                                                                                                                                                 | Version                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Operating System                                                                                                                                                                                                            | Windows 7, 8.1, or 10                   |

| Hardware                                                                                                                                                                                                                    |                                         |

| PolarFire Splash Kit (MPF300TS-1FCG484EES)<br>– PolarFire Splash board<br>– 12 V, 5 A AC power adapter and cord<br>– USB 2.0 A to mini-B cable for universal<br>asynchronous receiver-transmitter (UART) and<br>programming | Rev 2 or later                          |

| Host PC                                                                                                                                                                                                                     |                                         |

| Software                                                                                                                                                                                                                    |                                         |

| FlashPro                                                                                                                                                                                                                    | 12.200.30.10                            |

| Libero SoC PolarFire Design Suite                                                                                                                                                                                           | 2.2                                     |

| Serial Terminal Emulation Program                                                                                                                                                                                           | PuTTY or HyperTerminal<br>www.putty.org |

| IP                                                                                                                                                                                                                          |                                         |

| PF_INIT_MONITOR                                                                                                                                                                                                             | 2.0.103                                 |

| PF_CCC                                                                                                                                                                                                                      | 1.0.113                                 |

| CoreJTAGDEBUG                                                                                                                                                                                                               | 2.0.100                                 |

| CORESET_PF                                                                                                                                                                                                                  | 2.1.100                                 |

| Mi-V soft processor (MIV_RV32IMA_L1_AHB)                                                                                                                                                                                    | 2.0.100                                 |

| COREAHBLite                                                                                                                                                                                                                 | 5.3.101                                 |

| COREAHBTOAPB3                                                                                                                                                                                                               | 3.1.100                                 |

| CoreAPB3                                                                                                                                                                                                                    | 4.1.100                                 |

| CoreUARTapb                                                                                                                                                                                                                 | 5.6.102                                 |

| CoreGPIO                                                                                                                                                                                                                    | 3.2.102                                 |

| CoreSysService_PF                                                                                                                                                                                                           | 2.3.116                                 |

| CORESPI                                                                                                                                                                                                                     | 5.1.104                                 |

| PF_SRAM_AHBL_AXI                                                                                                                                                                                                            | 1.1.125                                 |

| PF SPI macro                                                                                                                                                                                                                |                                         |

|                                                                                                                                                                                                                             |                                         |

#### Table 2 • Design Requirements

Note: Any serial terminal emulation program can be used. PuTTY is used in this application note.

# 2.3 **Prerequisites**

#### Before you start:

- Download the design files from the following location: http://soc.microsemi.com/download/rsc/?f=mpf\_ac471\_liberosocpolarfirev2p2\_df

- Download and install Libero SoC PolarFire v2.2 on the host PC from the following location. https://www.microsemi.com/products/fpga-soc/design-resources/design-software/libero-socpolarfire#downloads

The latest versions of ModelSim and Synplify Pro are included in the Libero SoC PolarFire installation package.

# 2.4 Demo Design

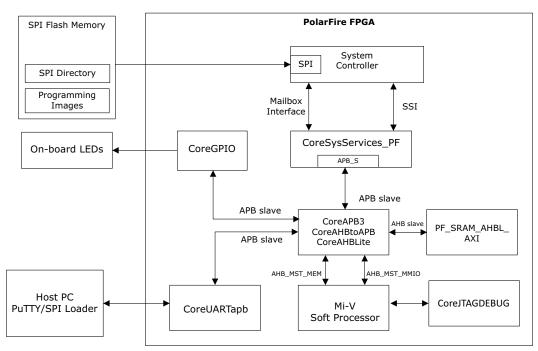

The following steps describe the data flow in the design:

- 1. The host PC sends the system service requests to CoreUARTapb block through the UART Interface.

- 2. The Mi-V soft processor initializes the System Controller using the CoreSysService\_PF IP and sends the requested system service command to the System Controller.

- The System Controller executes the system service command by reading the bitstream images from the external SPI flash and sends the relevant response to the CoreSysService\_PF IP over the mailbox interface.

- 4. The Mi-V processor receives the service response and forwards the data to the UART interface.

The following figure shows the block diagram of the PolarFire programming design.

#### Figure 3 • PolarFire Programming Design Block Diagram

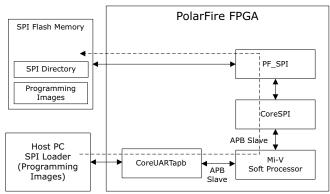

To initiate auto update or IAP system service request, the on-board SPI flash must be programmed with programming images. The fabric logic interfaces to the on-board SPI flash using SPI controller and PF\_SPI macro. When the System Controller's SPI is enabled and configured as master, the System Controller hands over the control of the SPI to the fabric on device power-up. The fabric logic programs the on-board SPI flash with flash directory and programming images using UART interface. The programming images are transfered from the host PC using SPI flash loader (spi\_loader.exe).

The on-board SPI flash can be programmed using fabric logic as shown in the following figure.

#### Figure 4 • Accessing On-board SPI Flash Using Fabric

---- Loading programming files into SPI Flash memory from host PC

The following figure shows the SPI flash memory with directory and programming images.

#### Figure 5 • SPI Flash Memory

When System Controller receives programming or authentication system service from fabric user logic, the System Controller fetches the programming images from the on-board SPI flash to execute the service request. In this application note, the following system services are initiated on user request.

- Bitstream authentication

- IAP image authentication

- Auto update

- IAP

For more information about the preceding services, see the UG0714: PolarFire FPGA Programming User Guide.

### 2.4.1 Design Implementation

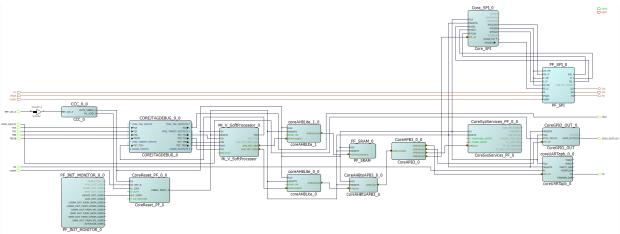

The following figure shows the top-level Libero design of the PolarFire system services design.

The following table lists the important I/O signals of the design.

#### Table 3 • I/O Signals

| Signal        | Description                                            |

|---------------|--------------------------------------------------------|

| REF_CLK_0     | Input 50 MHz clock from the on-board 50 MHz oscillator |

| resetn        | On-board reset push-button for the PolarFire device    |

| RX            | Input signals received from the serial UART terminal   |

| ТХ            | Output signals transmitted to the serial UART terminal |

| GPIO_OUT[3:0] | On-board LED outputs                                   |

| GPIO_IN[3:0]  | To interface on-board DIP switches.                    |

### 2.4.2 IP Configuration

The following sections describe the IP cores used in the design and their configurations. The other IP cores retain the default configuration.

#### 2.4.2.1 **PF\_INIT\_MONITOR**

The PolarFire Initialization Monitor gets the status of device initialization including the LSRAM initialization. The following figure shows PF\_INIT\_MONITOR configuration.

Figure 7 • PF\_INIT\_MONITOR Configuration

| Configurator                                  | - 0                                |

|-----------------------------------------------|------------------------------------|

| PolarFire Initialization Monitor Configurator |                                    |

| crosemi:SgCore:PF_INIT_MONITOR:2.0.103        |                                    |

| Bank Monitor Simulation Options               | <u> </u>                           |

| Simulation Options                            |                                    |

| FABRIC_POR_N assertion delay (ns)             | DE INIT MONITOR O                  |

|                                               | PF_INIT_MONITOR_0                  |

| PCIE_INIT_DONE assertion delay (ns) 4         | FABRIC_POR_N                       |

| USRAM_INIT_DONE assertion delay (ns) 5        | PCIE_INIT_DONE-                    |

| SRAM_INIT_DONE assertion delay (ns) 6         | USRAM_INIT_DONE                    |

|                                               | SRAM_INIT_DONE<br>DEVICE_INIT_DONE |

| DEVICE_INIT_DONE assertion delay (ns) 7       | XCVR_INIT_DONE                     |

| Calibration monitor                           | USRAM_INIT_FROM_SNVM_DONE          |

| BANK 0_CALIB_STATUS assertion delay (ns)      | USRAM_INIT_FROM_UPROM_DONE         |

|                                               | USRAM_INIT_FROM_SPI_DONE           |

| BANK_1_CALIB_STATUS assertion delay (ns) 1    | SRAM_INIT_FROM_SNVM_DONE           |

| BANK_2_CALIB_STATUS assertion delay (ns)      | SRAM_INIT_FROM_UPROM_DONE          |

|                                               | SRAM_INIT_FROM_SPI_DONE            |

| BANK_4_CALIB_STATUS assertion delay (ns) 1    | AUTOCALIB_DONE                     |

| BANK_5_CALIB_STATUS assertion delay (ns) 1    | PF_INIT_MONITOR                    |

| BANK_6_CALIB_STATUS assertion delay (ns) 1    |                                    |

| BANK_7_CALIB_STATUS assertion delay (ns)      |                                    |

|                                               | ▼ Symbol                           |

| Help 🔻                                        | OK Cancel                          |

### 2.4.2.2 Instantiating CLKINT

From the Catalog, drag the CLKINT macro to SmartDesign. This macro is required as a 50 MHz clock oscillator with an accuracy of +/-50 ppm is available on the board. This clock oscillator is connected to the FPGA fabric to provide a system reference clock. The pin number of the 50 MHz oscillator is H7, and the pin name is GPIO239PB5/CLKIN\_W\_2/CCC\_SW\_CLKIN\_W\_2/CCC\_SW\_PLL0\_OUT0. When the pin is not hardwired to the PLL reference clock input, use CLKINT macro to promote it to global clock network.

### 2.4.2.3 **PF\_CCC\_0** Configuration

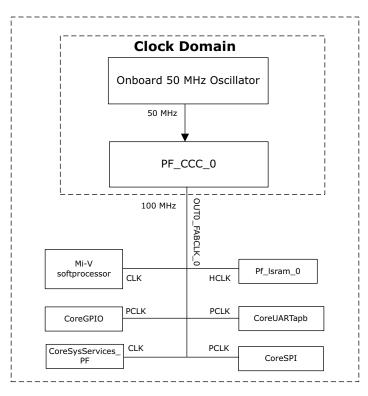

The PolarFire Clock Conditioning Circuitry (CCC) block takes an input clock of 50 MHz from the on-board oscillator passed through CLKINT and generates a 100 MHz fabric clock to the Mi-V processor subsystem and other peripherals. The following figures show the input and output clock configurations.

| Figure 8 • | PF_CCC_0 Input Clock Configuration |

|------------|------------------------------------|

|            | Configurator                       |

| Configurator                                                             | - 🗆 ×                  |

|--------------------------------------------------------------------------|------------------------|

| Clock Conditioning Circuitry (CCC)                                       |                        |

| Microsemi:5gCore:PF_CCC:1.0.113                                          |                        |

| <b>_</b>                                                                 |                        |

| Configuration PLL-Single                                                 |                        |

| Clock Options PLL Output Clocks                                          |                        |

| Input Frequency                                                          |                        |

| Input Frequency 50 MHz 🗌 Badkup Clock                                    |                        |

| Bandwidth High 💌                                                         |                        |

| Delay Lines                                                              |                        |

| Enable Delay Line                                                        |                        |

| C Feedback Clock Delay Delay Steps: 1                                    |                        |

| 6 Backup Clock Delay                                                     | PF_CCC_0               |

|                                                                          | OUTO_FABCLK_0          |

| Power / Jitter                                                           | -REF_CLK_0 PLL_LOCK_0- |

| Minimize ätter                                                           | PF_CCC                 |

| C Minimize VCO*                                                          | PF_CCC                 |

| C Minimize Power                                                         |                        |

| Feedback Mode                                                            |                        |

| Post-VCO 💌                                                               |                        |

| E Features                                                               |                        |

| Integer Mode                                                             |                        |

| SSCG Modulation                                                          |                        |

| Enable Dynamic Reconfiguration Interface (DRI)                           |                        |

| Export PowerDown Port     Wait For PLL Lock Before Exiting Flash *Freeze |                        |

| Wait Für FLL Lück bei vie Exiang Hash Freeze                             |                        |

|                                                                          | Symbol                 |

| Log                                                                      |                        |

| 🗐 Messages 😣 Errors 🗼 Warnings 🌐 Info                                    |                        |

|                                                                          |                        |

|                                                                          |                        |

| Help -                                                                   | OK Cancel              |

Figure 9 • PF\_CCC\_0 Output Clock Configuration

| Configurator                                                                         | - 🗆 X                     |

|--------------------------------------------------------------------------------------|---------------------------|

| Clock Conditioning Circuitry (CCC)                                                   |                           |

| Microsemi:SgCore:PF_CCC:1.0.113                                                      |                           |

| Configuration PLL-Single                                                             |                           |

|                                                                                      | -                         |

| Clock Options PLL Output Clocks                                                      |                           |

| For best results, put the highest frequency first.                                   |                           |

| Output Clock 0                                                                       | PF_CCC_0                  |

| ✓ Enabled                                                                            | -REF_CLK_0 OUT0_FABCLK_0- |

|                                                                                      | PF CCC                    |

| Requested Frequency 100 MHz C Actual Lower 100 MHz C Actual Higher 100 MHz           | 11_000                    |

| Requested Phase 0 Degrees C Actual Lower 0 Degrees C Actual Higher 0 Degrees         |                           |

| Dynamic Phase Shifting     Expose Enable Port     Enable Bypass     REF_PREDIV     Y |                           |

| Fabric Clock Fabric Clock (Gated)                                                    |                           |

|                                                                                      | Symbol                    |

| log                                                                                  |                           |

| 🔳 Messages 😵 Errors 🗼 Warnings 🎁 Info                                                |                           |

|                                                                                      |                           |

|                                                                                      |                           |

|                                                                                      |                           |

| Help •                                                                               | OK Cancel                 |

### 2.4.2.4 Mi-V Soft Processor Configuration

The Mi-V soft processor Reset Vector Address is set to 0x8000\_0000 from default value 0x6000\_0000. After device reset, the processor executes the application from LSRAM, which is mapped to 0x80000000, Hence, the Reset Vector Address is set to 0x80000000 as shown in the following figure.

In the Mi-V processor memory map, the 0x8000\_0000 to 0x8FFF\_FFFC range is defined for AHB memory interface and the 0x6000\_0000 to 0x7FFF\_FFFF range is defined for AHB I/O interface.

#### Figure 10 • Mi-V Configuration

| Configurator                             |          | -   |      | ×  |

|------------------------------------------|----------|-----|------|----|

| Mi-V RV32IMA_L1_AHB C                    | onfigura | tor |      |    |

| Microsemi:MiV:MIV_RV32IMA_L1_AHB:2.0.100 |          |     |      |    |

| Configuration                            |          |     |      |    |

| Reset Vector Address: 0x8000             | 0x0      |     | 0    |    |

|                                          |          |     |      |    |

|                                          |          |     |      |    |

|                                          |          |     |      |    |

|                                          |          |     |      |    |

|                                          |          |     |      |    |

|                                          | 0        |     | Cano | -1 |

| Help 🔹                                   | 0        |     | Cano | ei |

### 2.4.2.5 CoreUARTapb

The CoreUARTapb IP is connected to Mi-V soft processor as an APB slave. It interfaces with the host PC for UART communication. The default configuration settings of the CoreUARTapb IP are shown in the following figure:

- TX FIFO: Disabled by default.

- The UART transmit state machine immediately begins to transmit data and continues transmission until the data buffer is empty in normal mode. If **TX FIFO** is enabled, it continues to transmit until **TX FIFO** is empty. In this design, normal mode (without FIFO) is selected.

- RX FIFO: Disabled by default.

- The UART receive state machine stores the data in receive data buffer if FIFO is not enabled.

- Configuration: Set to Programmable by default.

#### Figure 11 • UART Configuration

| CoreUARTapb Configurator         DiscosemicDirectCore:CoreUARTapb:5.6.102         Configuration         TX FIFO:       Disable TX FIFO ▼         RX FIFO:       Disable TX FIFO ▼         Configuration:       Programmable ▼         Baud Value:       1         Character Size:       7 bits ▼         Parity:       Parity Disabled ▼         RX Legacy Mode:       Disabled ▼         FIFO Implementation:       In RAM ▼         Baud Value Precision       ■         Enable Extra Precision:       ■         Fractional Part of Baud Value:       +0.0 ▼         Testbench:       User ▼         License:       C Obfuscated       © RTL | Configurator           |                     | -  |     | ×   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------|----|-----|-----|

| Configuration TX FIFO: Disable TX FIFO  RX FIFO: Disable RX FIFO  Configuration: Programmable  Baud Value: 1 Character Size: 7 bits  Parity: Parity Disabled  Parity: Parity Disabled  RX Legacy Mode: Disabled  FIFO Implementation: In RAM  Baud Value Precision Enable Extra Precision:  Fractional Part of Baud Value: +0.0  Testbench: User  License: C Obfuscated C RTL                                                                                                                                                                                                                                                                  | CoreUARTap             | b Configurator      |    |     |     |

| Core Configuration TX FIFO: Disable TX FIFO  RX FIFO: Disable RX FIFO  Configuration: Programmable Baud Value: 1 Character Size: 7 bits Parity: Parity Disabled RX Legacy Mode: Disabled RX Legacy Mode: Disabled FIFO Implementation: In RAM Baud Value Precision Enable Extra Precision: Fractional Part of Baud Value: $+0.0$ Testbench: User  Configuration: RTL                                                                                                                                                                                                                                                                           | Microsemi:DirectCore:C | CoreUARTapb:5.6.102 |    |     |     |

| TX FIFO: Disable TX FIFO   RX FIFO: Disable RX FIFO   Configuration: Programmable   Baud Value: 1   Character Size: 7 bits   Parity: Parity Disabled   RX Legacy Mode: Disabled   FIFO Implementation: In RAM   Enable Extra Precision:                                                                                                                                                                                                                                                                                                                                                                                                        | Configuration          |                     |    |     |     |

| RX FIFO: Disable RX FIFO  Configuration: Programmable Baud Value: 1 Character Size: 7 bits Parity Disabled Parity: Parity Disabled RX Legacy Mode: Disabled FIFO Implementation: In RAM Baud Value Precision Enable Extra Precision: Fractional Part of Baud Value: +0.0 Testbench: User License: C Obfuscated   RTL                                                                                                                                                                                                                                                                                                                           | Core Configuration     |                     |    |     |     |

| Configuration: Programmable<br>Baud Value: 1<br>Character Size: 7 bits<br>Parity: Parity Disabled<br>RX Legacy Mode: Disabled<br>FIFO Implementation: In RAM<br>Baud Value Precision<br>Enable Extra Precision:<br>Fractional Part of Baud Value: +0.0<br>Testbench: User<br>License: C Obfuscated  RTL                                                                                                                                                                                                                                                                                                                                        | TX FIFO:               | Disable TX FIFO 💌   |    |     |     |

| Baud Value: 1<br>Character Size: 7 bits<br>Parity: Parity Disabled<br>RX Legacy Mode: Disabled<br>FIFO Implementation: In RAM<br>Baud Value Precision<br>Enable Extra Precision:<br>Fractional Part of Baud Value: $\pm 0.0$<br>Itestbench: User<br>License: C Obfuscated C RTL                                                                                                                                                                                                                                                                                                                                                                | RX FIFO:               | Disable RX FIFO     |    |     |     |

| Character Size: 7 bits<br>Parity: Parity Disabled<br>RX Legacy Mode: Disabled<br>FIFO Implementation: In RAM<br>Baud Value Precision<br>Enable Extra Precision:<br>Fractional Part of Baud Value: $+0.0$<br>Testbench: User<br>License: O Obfuscated  RTL                                                                                                                                                                                                                                                                                                                                                                                      | Configuration:         | Programmable 💌      |    |     |     |

| Parity: Parity Disabled<br>RX Legacy Mode: Disabled<br>FIFO Implementation: In RAM<br>Baud Value Precision<br>Enable Extra Precision:<br>Fractional Part of Baud Value: +0.0<br>Testbench: User<br>License: C Obfuscated C RTL                                                                                                                                                                                                                                                                                                                                                                                                                 | Baud Value:            | 1                   |    |     |     |

| RX Legacy Mode: Disabled  FIFO Implementation: In RAM  Baud Value Precision Enable Extra Precision: Fractional Part of Baud Value: +0.0  Testbench: User  License:  Obfuscated  RTL                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Character Size:        | 7 bits 👻            |    |     |     |

| FIFO Implementation: In RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Parity:                | Parity Disabled 💌   |    |     |     |

| Baud Value Precision<br>Enable Extra Precision:<br>Fractional Part of Baud Value: +0.0<br>Testbench: User<br>License: C Obfuscated © RTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RX Legacy Mode:        | Disabled 💌          |    |     |     |

| Enable Extra Precision:<br>Fractional Part of Baud Value: +0.0<br>Testbench: User<br>License: ^ Obfuscated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FIFO Implementation    | n: In RAM           |    |     |     |

| Enable Extra Precision:<br>Fractional Part of Baud Value: +0.0<br>Testbench: User<br>License: ^ Obfuscated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |                     |    |     |     |

| Fractional Part of Baud Value: +0.0<br>Testbench: User<br>License: ^ Obfuscated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                     |    |     |     |

| Testbench: User I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        |                     |    |     |     |

| License: C Obfuscated @ RTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Fractional Part of Ba  | aud Value: +0.0 💌   |    |     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Testbench: User 💌      |                     |    |     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | License: 🔿 Obfuscated  | • RTL               |    |     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                     |    |     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                     |    |     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                     |    |     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                     |    |     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                     |    |     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                     |    |     |     |

| DEU UK L CADCEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Help •                 |                     | ок | Can | rel |

The SoftConsole application programs the baud rate, character size, and the parity configuration using the UART driver. If the **Fixed** option is selected, the user application can not overwrite these parameters.

### 2.4.2.6 CoreJTAGDEBUG

The CoreJTAGDebug IP connects the Mi-V soft processor to the JTAG header for debugging.

#### 2.4.2.7 **PF\_SRAM\_AHBL\_AXI** Configuration

The PF SRAM AHBL AXI IP is the main memory of the Mi-V processor, and it gets initialized with the user application from µPROM. It is connected to Mi-V soft processor as an AHB slave. LSRAM is configured for the following settings:

- Optimize for: By default, Low power is selected. It optimizes the LSRAM macro for low power. If design demands high speed memory access, High Speed can be selected.

- Fabric Interface type: By default, AHBLite is selected. The Mi-V soft processor is AHB based, so the SRAM is interfaced to the processor using AHB bus for code execution.

- Memory depth: This field is set to 65536 words to accommodate an application of up to 256 KB into • LSRAM. The present application is below 50 KB so this can fit into either sNVM or µPROM. In this design, µPROM is selected as data storage client. The following figure shows the PE SRAM AHRI AXI (I SRAM 0) IP configuration

| igure 12 • PF_SRAM_AHBL_AXI Configuration                                                                         |                   |

|-------------------------------------------------------------------------------------------------------------------|-------------------|

| PF_SRAM_AHBL_AXI Microsemi:SystemBuilder:PF_SRAM_AHBL_AXI:1.1.125                                                 |                   |

| Port settings Memory Initialization Settings                                                                      |                   |

| Optimize for C High Speed C Low power<br>SRAM type SRAM<br>Memory Depth( in words ) 65536<br>Use Native Interface | SRAM_AHB_AXI_UI_0 |

| Interface Settings  Fabric Interface type AHBLite Data Width 32                                                   | HCLK<br>HRESETN   |

| AXI4 interface options Address Width 32 Width of ID 8  Vite Interface                                             | AHBSlaveInterface |

| Read Interface                                                                                                    | SRAM_AHB_AXI_UI   |

#### Fi

Symbol

### 2.4.2.8 CoreGPIO\_0 Configuration

The CoreGPIO IP controls the on-board LEDs using GPIOs. It is connected to Mi-V soft processor as an APB slave. The configuration settings of the COREGPIO\_0 IP are as follows:

#### In the Global Configurations pane:

- APB Data width is set to 32

- The design uses 32-bit data width for APB read and write data.

- Number of I/Os is set to 4

- The design controls 2 on-board LEDs for output and 2 DIP Switches for input.

- **I/O Bit:** The following list shows the sub-options under I/O Bit option.

- Output on reset: Set to 0.

- Fixed Config: Yes

- **I/O type:** As shown in the following figure, first two I/Os are configured as output and the last two I/Os are configured as input.

- **Note:** The first two I/Os configured as output are used by the design and last two I/Os are not used. The I/Os are interfaced to on-board LEDS and DIP switches.

- Interrupt Type: Disabled

- When I/O states change, no interrupt is required for the application.

The following figure shows the CoreGPIO\_0 configuration.

#### Figure 13 • CoreGPIO\_0 Configuration

| III Configurator                                                                                                                  | - |       | × |

|-----------------------------------------------------------------------------------------------------------------------------------|---|-------|---|

| CoreGPIO Configurator                                                                                                             |   |       |   |

| Microsemi:DirectCore:CoreGPI0:3.2.102                                                                                             |   |       |   |

| Configuration                                                                                                                     |   |       | - |

| Global Configuration       APB Data Width:     32       Single-bit interrupt port:     Disabled       Output enable:     Internal |   |       |   |

| I/O bit 0<br>Output on Reset: 0  Fixed Config:  I/O Type: Output Interrupt Type: Disabled                                         | • |       |   |

| I/O bit 1<br>Output on Reset: 0  Fixed Config:  I/O Type: Output Interrupt Type: Disabled                                         | • |       |   |

| I/O bit 2         Output on Reset:       Image: Tripped Config:         I/O Type:       Input Interrupt Type:         Disabled    | • |       |   |

| I/O bit 3         Output on Reset:       Image: Trived Config:         I/O Type:       Input Interrupt Type:         Disabled     | • |       | - |

|                                                                                                                                   | ж | Cance | 1 |

### 2.4.2.9 CoreSPI Configuration

The CoreSPI is used to program the external SPI flash using Mi-V processor. PF\_SPI macro interfaces the fabric logic to the external SPI flash, which is connected to System Controller.

- APB Data Width: select 32 as APB data width in the design is 32-bit. The default value is 8.

- Mode: select Motorola Mode (default) as the target SPI slave (VSC Phy) supports Motorola mode.

- Frame Size: enter 8. The default value is 4.

- FIFO Depth: enter 32 to store maximum frames (Tx and Rx) in FIFO. The default value is 4.

- **Clock Rate**: enter 16. The default value is 8. The SPI clock becomes system clock/ 2\*(16+1).

- **Keep SSEL active**: enabled to keep the slave peripheral active between back to back data transfers.

The following figure shows the CoreSPI configurator.

#### Figure 14 • CoreSPI Configuration

| Configurator                                              | -  |     |     |

|-----------------------------------------------------------|----|-----|-----|

| CoreSPI Configurator                                      |    |     |     |

| ficrosemi:DirectCore:CORESPI:5.1.104                      |    |     |     |

| Configuration                                             |    |     |     |

| vPB Data Width: ○ 8 ○ 16 ● 32                             |    |     |     |

| - SPI Configuration                                       |    |     |     |

| Mode:      O Motorola Mode      O TI Mode      O NSC Mode |    |     |     |

| Frame Size (4-32): 8                                      |    |     |     |

| FIFO Depth (1-32): 32                                     |    |     |     |

| Clock Rate (0-255): 16                                    |    |     |     |

| -Motorola Configuration                                   |    |     |     |

| Keep SSEL active 🔽                                        |    |     |     |

| Transfer Mode: C Normal C Custom                          |    |     |     |

| Free running dock                                         |    |     |     |

| Jumbo frames                                              |    |     |     |

| NSC Specific Configuration Standard                       |    |     |     |

| estbench: User                                            |    |     |     |

| icense: RTL                                               |    |     |     |

|                                                           |    |     |     |

|                                                           |    |     |     |

|                                                           |    |     |     |

|                                                           |    |     |     |

|                                                           |    |     |     |

|                                                           |    |     |     |

| Help 🔻                                                    | ОК | Can | cel |

### 2.4.2.10 CoreSysService\_PF Configuration

CoreSysServices IP provides access to the System Controller. It is connected to Mi-V soft processor as an APB slave. By default, all the service check boxes are selected. The application can initiate these selected services. CoreSysServices IP is configured as shown in the following figure.

| Figure 15 • | CoreSys | Service_ | PF | Configuration |

|-------------|---------|----------|----|---------------|

|-------------|---------|----------|----|---------------|

| Configurator                                                            | -      |       | ×  |

|-------------------------------------------------------------------------|--------|-------|----|

| CoreSysServices_PF Configurator                                         |        |       |    |

| Microsemi:DirectCore:CORESYS5ERVICE5_PF;2.3.116                         |        |       |    |

| Configuration                                                           |        |       |    |

| Device and Design Information Services                                  |        |       |    |

| Serial Number Service: 🔽 UserCode Service: 🔽                            |        |       |    |

| Design Version Service: 🔽 Device Certificate Service: 🔽                 |        |       |    |

| Read Digest Service: 🔽 Query Security Service: 🔽                        |        |       |    |

| Read Debug Info Service: 🔽                                              |        |       |    |

| Design Services                                                         |        |       |    |

| Bitstream Authentication Service: 🔽 IAP Image Authentication Service: 🔽 |        |       |    |

| Data Security Services                                                  |        |       | -1 |

| Digital Signature Service: 🔽 Secure NVM Write Service: 🔽                |        |       |    |

| Secure NVM Read Service: 🔽 PUF Emulation Service: 🔽                     |        |       |    |

| Nonce Service:                                                          |        |       |    |

| FlashFreeze Services                                                    |        |       | -1 |

| Flash Freeze Service: 🔽 FlashFreeze Timeout Value                       | 000000 |       |    |

| FlashFreeze Mailbox Address 0x100 Enable 2MHZ Osc (during Flash Freeze) |        |       |    |

| Fabric Services                                                         |        |       | -1 |

| Digest Check Service: 🔽 IAP Service: 🔽                                  |        |       |    |

| IAP Auto Update Service:                                                |        |       |    |

| Testbench: User 🔽                                                       |        |       |    |

| License: RTL                                                            |        |       |    |

|                                                                         |        |       |    |

|                                                                         |        |       |    |

|                                                                         |        |       |    |

| Help 👻                                                                  | ОК     | Cance | 2  |

### 2.4.2.11 Design Memory Map

The Mi-V processor bus interface memory map is shown in the following figure.

#### Figure 16 • Memory Map

| 🕺 Modify Memory Map                           |            |                         |                | ×   |

|-----------------------------------------------|------------|-------------------------|----------------|-----|

| Select Bus to View or<br>Assign Peripheral(s) | ,          | Assign peripherals to a | ddresses on bu | us: |

| CoreAHBLite 0                                 | Address    | Periphe                 | ral            |     |

| CoreAHBLite_1_0                               | 0x60000000 | CoreUARTapb_0:AP        | B_bif          | 1   |

|                                               | 0x60001000 | CoreGPIO_OUT:APE        | _bif           |     |

|                                               | 0x60002000 | core_sys_services_0:    | APBSlave       |     |

|                                               | 0x60003000 | SPI_Controller_1:AP     | B_bif          |     |

|                                               |            |                         |                |     |

| Help                                          |            | OK                      | Cancel         |     |

| SD Modify Memory Map                          |            |                         |                | ×   |

| Select Bus to View or<br>Assign Peripheral(s) | ,          | Assign peripherals to a | ddresses on bi | us: |

| CoreAHBLite_0                                 | Address    | Periphe                 | ral            |     |

| CoreAHBLite_1_0                               | 0x80000000 | pf_lsram_0:AHBSlav      | elnterface     |     |

|                                               | <b></b>    |                         |                |     |

|                                               |            |                         |                |     |

|                                               |            |                         |                |     |

|                                               |            |                         |                |     |

|                                               |            |                         |                |     |

|                                               |            |                         |                |     |

| Help                                          |            | ОК                      | Cancel         |     |

#### 2.4.2.11.1 CoreAHBLite Configuration

Two instances of CoreAHBLite are used in this design. The following figures show the configurations of CoreAHBLite\_0 and CoreAHBLite\_1 IP cores. The CoreAHBLite\_0 interfaces with the APB peripherals to the Mi-V processor at 0x6000\_0000.

#### *Figure 17* • CoreAHBLite\_0 Configuration

| Configurator                            |             |                       |                          |              |                             |            |                        | -  |     | ×   |

|-----------------------------------------|-------------|-----------------------|--------------------------|--------------|-----------------------------|------------|------------------------|----|-----|-----|

| CoreAHBLite Config                      | urato       | r                     |                          |              |                             |            |                        |    |     |     |

| Microsemi:DirectCore:CoreAHBLite:5.     | 3.101       |                       |                          |              |                             |            |                        |    |     |     |

| Configuration                           |             |                       |                          |              |                             |            |                        |    |     | _   |