SG3561A

## POWER FACTOR CONTROLLER

DATA SHEET

#### **DESCRIPTION**

This monolithic integrated circuit provides all the necessary functions for designing an active power factor correction circuit in conjunction with off-line power converters. Although the IC is optimized for electronic ballast applications, it can also be used in switched mode AC-DC power converters. Included in the 8-pin DIP package are; an under voltage lockout with a micropower startup with a 2V hysteresis, an internal temperature compensated bandgap reference, a unity gain stable error amplifier, one quadrant multiplier stage, a current sense comparator and a totem

pole output stage for directing driving of the power MOSFET. In addition to the above, an internal logic circuit detects the zero crossing of the inductor current and maintains discontinuous current mode of operation such that it allows no current gaps to appear. This type of operation provides a higher P.F. correction, as well as lower harmonic distortion over the fixed frequency discontinuous current mode. The SG3561A is characterized for operation over the ambient temperature range of -25°C to +85°C.

IMPORTANT: For the most current data, consult MICROSEMI's website: http://www.microsemi.com

#### **KEY FEATURES**

- MICRO-POWER START-UP MODE (250µA typ.)

- LOW OPERATING CURRENT CONSUMPTION

- INTERNAL 1.5% REFERENCE

- TOTEM POLE OUTPUT STAGE

- AUTOMATIC CURRENT LIMITING OF BOOST STAGE

- DISCONTINUOUS MODE OF OPERATION WITH NO CURRENT GAPS

- NO SLOPE COMPENSATION REQUIRED

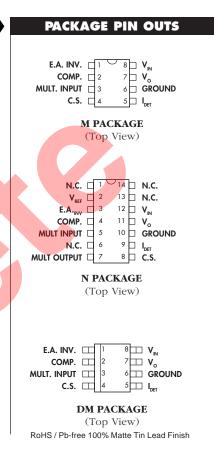

- AVAILABLE IN 8 & 14-PIN

PLASTIC DIP AND 8-PIN SOIC

PACKAGE

- SEE LX1562/1563 FOR NEW DESIGNS

### PRODUCT HIGHLIGHT

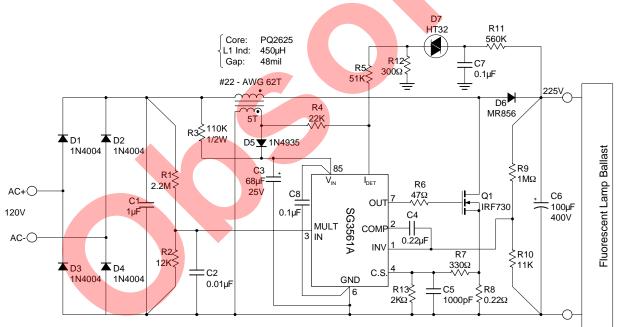

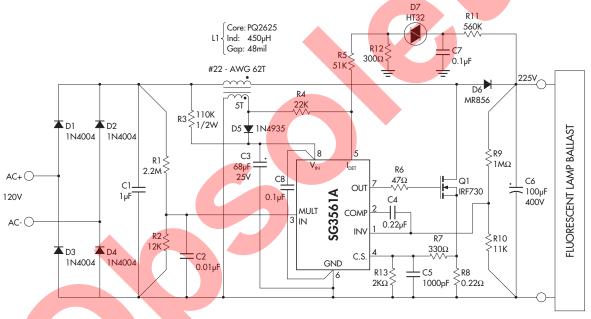

TYPICAL APPLICATION OF THE SG3561A IN AN 80W

FLUORESCENT LAMP BALLAST WITH A CTIVE POWER FACTOR CONTROL

| <b>)</b> |                     | PACK                 | AGE ORDER INFO                               |                          |  |  |

|----------|---------------------|----------------------|----------------------------------------------|--------------------------|--|--|

|          | T <sub>A</sub> (°C) | Plastic DIP<br>8-Pin | Plastic DIP<br>14-Pin                        | DM Plastic SOIC<br>8-Pin |  |  |

|          | I <sub>A</sub> (C)  | RoHS Compliant / Pb- | RoHS Compliant / Pb-free Transition DC: 0503 |                          |  |  |

|          | -25 to 85           | SG3561AM             | SG3561AN                                     | SG3561ADM                |  |  |

Note: Available in Tape & Reel. Append the letters "TR" to the part number. (i.e. SG3561AM-TR)

### NOT RECOMMENDED FOR NEW DESIGNS

| ABSOLUTE MAXIMUM RATINGS (Note 1)                                                                      |

|--------------------------------------------------------------------------------------------------------|

| Supply Voltage (V <sub>N</sub> )0.3V to 28V                                                            |

| Peak Driver Output Current±500mA                                                                       |

| Driver Output Clamping Diodes                                                                          |

| $V_{o} > V_{cc}$ or $V_{o} < -0.3V$                                                                    |

| Detector Clamping Diodes                                                                               |

| $V_{DET} > 6V \text{ or } V_{DET} < 0.9V \dots \pm 10 \text{mA}$                                       |

| Error Amp, Multiplier, and Comparator Input Voltages0.3V to 6V                                         |

| Detector Input Voltage (Note 2)                                                                        |

| Operating Junction Temperature                                                                         |

| Plastic (M, N and DM Packages)                                                                         |

| Storage Temperature Range65°C to 150°C                                                                 |

| Peak Package Solder Reflow Temp. (40 seconds max. exposure)260°C (+0,-5)                               |

|                                                                                                        |

| Note 1. Values beyond which damage may occur. All voltages are specified with respect to               |

| ground, and all currents are positive into the specified terminal.  Note 2. With no limiting resistor. |

## THERMAL DATA M PACKAGE: THERMAL RESISTANCE-JUNCTION TO AMBIENT, $\theta_{10}$ 95°C/W THERMAL RESISTANCE-JUNCTION TO AMBIENT, $\theta_{IA}$ 65°C/W DM PACKAGE: THERMAL RESISTANCE-JUNCTION TO AMBIENT, $\theta_{\text{JA}}$ 165°C/W

Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ . The  $\theta_{JA}$  numbers are guidelines for the thermal performance of the device/pc-board

system. All of the above assume no ambient airflow.

### NOT RECOMMENDED FOR NEW DESIGNS

| RECOMMENDED OPERATING CONDITIONS (Note 3) |                 |          |                 |            |        |  |  |  |

|-------------------------------------------|-----------------|----------|-----------------|------------|--------|--|--|--|

| Parameter                                 | Symbol          | Recommen | ded Operating ( | Conditions | Units  |  |  |  |

| raidiletei                                | Symoon          | Min.     | Тур.            | Max.       | Ullits |  |  |  |

| Supply Voltage Range                      | V <sub>IN</sub> | 11       |                 | 25         | ٧      |  |  |  |

| Peak Driver Output Current                |                 |          | ±300            |            | mA     |  |  |  |

| Operating Ambient Temperature Range:      |                 |          |                 |            |        |  |  |  |

| SG3561A                                   | T <sub>A</sub>  | -25      |                 | 85         | °C     |  |  |  |

Note 3. Range over which the device is functional.

## ELECTRICAL CHARACTERISTICS

(Unless otherwise specified, these specifications apply over the operating ambient temperatures for the SG3561A with -25°C  $\leq$  T<sub>A</sub>  $\leq$  +85°C; V<sub>IN</sub>=12V. Low duty cycle pulse testing techniques are used which maintains junction and case temperatures equal to the ambient temperature.)

| Parameter                             | Symbol   | Test Conditions                             |       | SG3561 | Ą     | Units |

|---------------------------------------|----------|---------------------------------------------|-------|--------|-------|-------|

| Faidilletei                           | Sylliooi | lest conditions                             | Min.  | Тур.   | Max.  | Unit  |

| Under-Voltage Lockout Section         |          |                                             |       |        |       |       |

| Start Threshold Voltage               |          |                                             | 9.2   | 10     | 10.8  | ٧     |

| UV Lockout Hysteresis                 |          |                                             | 1.6   | 2.0    | 2.4   | ٧     |

| Supply Current Section                |          |                                             |       |        |       | _     |

| Start-Up Supply Current               |          | $V_{IN} < V_{TH}$                           |       | 0.25   | 0.5   | mA    |

| Operating Supply Current              |          | V <sub>IN</sub> = 12V, Output Not Switching |       | 6      | 12    | mA    |

| Dynamic Operating Supply Current      | AVE      | $V_{IN} = 12V, 50KHz, CGS = 1000pF$         |       | 10     | 15    | mA    |

| Reference Section (Note 4)            |          |                                             |       |        |       |       |

| Initial Accuracy                      |          | $I_{REF} = 0mA$ , $T_J = 25$ °C             | 2.463 | 2.50   | 2.538 | ٧     |

| Line Regulation                       |          | $12V < V_{IN} < 25V$                        |       | 0.1    | 10    | m۷    |

| Load Regulation                       |          | $0 < I_{REF} < 2mA$                         |       | 0.1    | 10    | m۷    |

| Temperature Stability                 |          |                                             |       | 20     |       | m۷    |

| Error Amplifier Section               |          |                                             |       |        |       |       |

| Input Offset Voltage (Note 4)         |          |                                             | -15   |        | 15    | m۷    |

| Input Bias Current                    |          |                                             | -2    | -0.1   |       | μA    |

| Large Signal Open Loop Voltage Gain   |          | (Note 4)                                    | 60    | 86     |       | dB    |

| Slew Rate                             |          |                                             |       | 0.6    |       | v/µse |

| Power Supply Rejection Ratio (Note 4) |          |                                             | 60    | 86     |       | dB    |

| Output Source Current                 |          | $V_{OH} = 3.5V$                             | 2     |        |       | mA    |

| Output Sink Current                   |          | $V_{OL} = 9.0V$                             | 2     |        |       | mA    |

| Output Voltage Range (Note 6)         |          | No Load on E.A. Output                      | 1.2   |        | 4     | ٧     |

| Unity Gain Ban <mark>dwidt</mark> h   |          |                                             |       | 1.0    |       | MHz   |

| Phase Margin                          |          |                                             |       | 57     |       | ۰     |

(Electrical Characteristics continued next page.)

## NOT RECOMMENDED FOR NEW DESIGNS

| Davamatav                               | C. mala al | Test Conditions                             |                  | SG3561A | 4                   | Units |

|-----------------------------------------|------------|---------------------------------------------|------------------|---------|---------------------|-------|

| Parameter                               | Symbol     | lest Conditions                             | Min.             | Тур.    | Max.                | Units |

| Multiplier Section                      |            |                                             |                  |         |                     |       |

| M1 Input Voltage Range                  |            |                                             | 0                |         | 2                   | ٧     |

| M2 Input Voltage Range                  |            |                                             | V <sub>REF</sub> |         | V <sub>REF</sub> +1 | ٧     |

| Input Bias Current (M1)                 |            |                                             | -2               |         | 2                   | μA    |

| Multiplier Gain (Note 5), (Note 4)      |            | $V_{M1} = 1V, V_{EA0} = 3.5V$               | 0.52             | 0.65    | 0.78                | /V    |

|                                         |            | $V_{M1} = 2V, V_{EA0} = 3.5V$               |                  | 0.65    |                     | /V    |

| Multiplier Gain Temperature Stability   |            |                                             |                  | -0.2    |                     | %/°C  |

| Maximum Multiplier Output Voltage       |            | $V_{M1} = 1V, V_{EAO} > 4V$                 |                  | 0.9     |                     | ٧     |

|                                         |            | $V_{M1} = 2V, V_{EAO} > 4V$                 |                  | 1.8     |                     | ٧     |

| <b>Current Sense Comparator Section</b> | n          |                                             |                  |         |                     |       |

| Input Bias Current                      |            | $0V \le V_{CS} \le 1.7V$                    | -5               | 1       | 5                   | μΑ    |

| Current Sense Delay to Output           |            | E.A. <sub>OUT</sub> = 3.7V                  |                  | 200     | 500                 | ns    |

| Detect Section                          | •          |                                             |                  |         | •                   |       |

| Input Voltage Threshold                 |            |                                             | 1                | 1.3     | 1.6                 | ٧     |

| Hysteresis                              |            |                                             |                  | 175     |                     | m۷    |

| Input LO Clamp Voltage                  |            | $I_{DET} = 100\mu A$                        |                  |         | 0.95                | ٧     |

| Input HI Clamp Voltage                  |            | $I_{DET} = 3mA$                             | 6.1              | 7.1     |                     | ٧     |

| Input Current                           |            | $1V \le V_{DET} \le 6V$                     | -10              |         | 10                  | μΑ    |

| Input HI/LO Clamp Diode Current         |            | $V_{DET} < 0.9V, V_{DET} > 6V$              |                  |         | ±3                  | mA    |

| Output Driver Section                   | •          |                                             | -                | •       | •                   |       |

| Output High Voltage                     |            | $I_L = -10 \text{mA}, V_{IN} = 12 \text{V}$ | 7                | 9       |                     | ٧     |

| Output Low Voltage                      |            | $I_L = 10 \text{mA}, V_{IN} = 12 \text{V}$  |                  | 0.8     | 1.5                 | ٧     |

| Output Rise Time                        |            | $C_1 = 1000pF$                              |                  | 100     | 200                 | ns    |

| Output Fall Time                        |            | C <sub>1</sub> = 1000pF                     |                  | 90      | 200                 | ns    |

Notes: 4. Because the reference is not brought out externally, these specifications are tested at probe only, and cannot be tested on the packaged part. They are guaranteed by design, and shown for illustrative purposes only.

5.

$$K = \frac{V_{MO}}{(V_{MI}) \times (V_{EA0} - V_{REF})}$$

6. This parameter, although guaranteed, is not tested in production.

## NOT RECOMMENDED FOR NEW DESIGNS

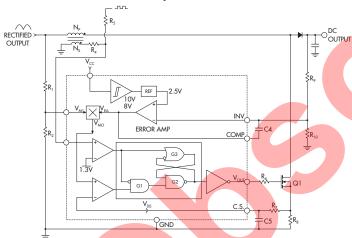

## BLOCK DIAGRAM / PIN DESCRIPTIONS \*MULT OUT UVLO VIN (8) REF 2.5V 10V (2V HYST) mINV 1) COMP 2 V<sub>M1</sub> CURRENT DETECT LOGIC -⑦ V₀ MULT IN 3 C.S. 4 HI<sub>DET</sub> (5) 777 \* Available only in 14-pin package. 6 GND

## **FUNCTIONAL DESCRIPTION**

| Pin              | # | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IN</sub>  | 8 | Input supply voltage. $V_{IN} \le 8V$ $I_{IN} \le 0.5 \text{mA}$ $V_{IN \text{ MAX}} < 25 \text{V}$ $V_{IN} \ge 10 \text{V}$ $I_{IN} \le 15 \text{mA}$                                                                                                                                                                                                                                                                                |

| GND              | 6 | Input supply voltage return. Must always be the lowest potential of all the pins.                                                                                                                                                                                                                                                                                                                                                     |

| INV              | 1 | Inverting input of the Error Amplifier. The output of the Boost converter should be resistively divided to 2.5V and connected to this pin.                                                                                                                                                                                                                                                                                            |

| COMP             | 2 | The output of the Error Amplifier. A feedback compensation network is placed between this pin and the INV pin.                                                                                                                                                                                                                                                                                                                        |

| MULT             | 3 | Input to the multiplier stage. The full-wave rectified AC is divided to less than 2V and is connected to this pin.                                                                                                                                                                                                                                                                                                                    |

| C.S.             | 4 | Input to the PWM comparator. Current is sensed in the Boost stage MOSFET by a resistor in the source lead, and is fed to this pin through a low-pass filter                                                                                                                                                                                                                                                                           |

| l <sub>DET</sub> | 5 | A current driven logic input with internal clamp. A second winding on the Boost inductor senses the flyback voltage associated with the zero crossing of the inductor current and feeds it to the $I_{\text{DET}}$ pin through a limiting resistor. The logic circuit processes this signal, such that the converter operates in a discontinuous conduction current mode, where there is no current gap between the switching cycles. |

| V <sub>o</sub>   | 7 | PWM output pin. A totem-pole output stage specially designed for direct driving the MOSFET.                                                                                                                                                                                                                                                                                                                                           |

### NOT RECOMMENDED FOR NEW DESIGNS

### FIGURE INDEX

## **Application Information**

#### FIGURE #

- 1. GENERAL APPLICATION CIRCUIT

- 2. START UP CIRCUITRY

- 3. START UP VOLTAGE

- 4. REFERENCE VOLTAGE vs. TEMPERATURE

- 5. TYPICAL COMPENSATION CIRCUIT

- 6. MULTIPLIER CIRCUIT

- 7. CURRENT SENSE CIRCUIT

- 8. I<sub>DETECT</sub> INPUT CIRCUIT

- 9. TYPICAL START UP CIRCUIT USING DIAC

- 10. IDETECT LOGIC CIRCUIT

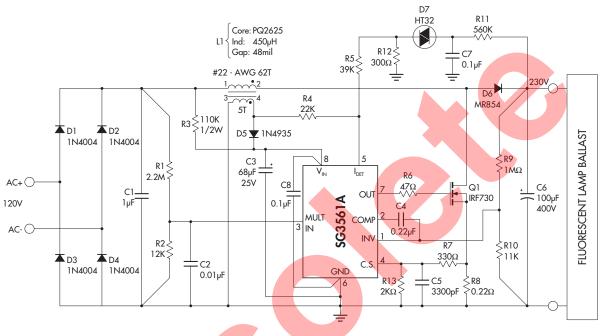

- 11. TYPICAL APPLICATION WITH 120V INPUT

- 12. INDUCTOR CURRENT

- 13. CURRENT DETECT EXAMPLE

### **Typical Applications**

#### FIGURE #

- 14. TYPICAL APPLICATION OF THE SG3561A IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL 120V

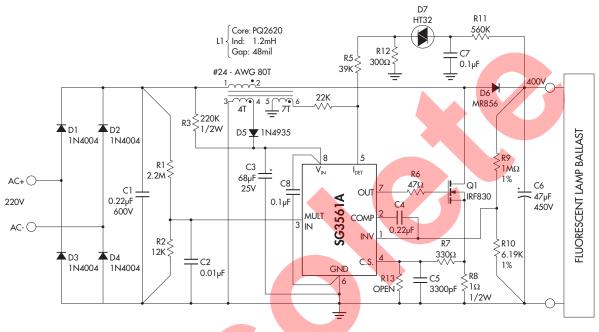

- 15. TYPICAL APPLICATION OF THE SG3561A IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL 220V

- 16. TYPICAL APPLICATION OF THE SG3561A IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL 277V\

- 17. TYPICAL APPLICATION OF THE \$G33561A IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL 277V (BUCK BOOST APPLICATION)

## NOT RECOMMENDED FOR NEW DESIGNS

### APPLICATION INFORMATION

#### **FUNCTIONAL DESCRIPTION**

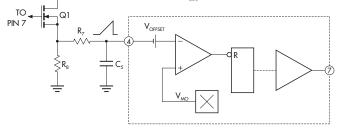

The operation of the circuit is best described by referring to the diagram in Figure 1.

The multiplier stage generates an output voltage  $(V_{MO})$  from the rectified waveform of the AC input  $(V_{MI})$  and the amplitude of the error amplifier output  $(V_{EA})$ . This voltage controls the peak inductor current by turning the power MOSFET off at a threshold, where the current sense voltage  $(V_{CS})$  reaches a given nominal value. This causes the power MOSFET to latch-off until the current in the inductor drops to zero. Once this happens, the secondary winding of the inductor changes its voltage polarity, and gets detected by an internal comparator stage. The polarity of the windings are chosen such that a low  $I_{DET}$  voltage turns on the power MOSFET and maintains operation until the above process repeats itself. An external trigger voltage to the IDET is required to start-up the converter until the auxiliary winding of the inductor takes over the operation.

FIGURE 1 — GENERAL APPLICATION CIRCUIT

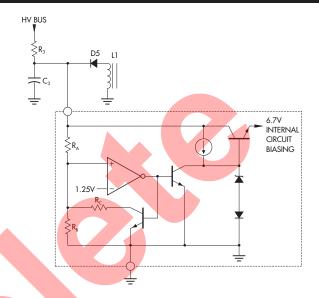

#### UNDERVOLTAGE LOCKOUT

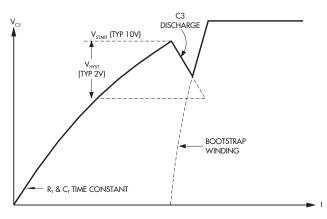

The purpose of the undervoltage lockout is to perform two functions: 1) to maintain a low quiescent current during power-up, 2) to guarantee that the IC is fully functional before the output stage is activated. To realize this, a micropower comparator with a start-up threshold of 10V and a built-in hysteresis of 2V is incorporated. This comparator acts as a switch for the pre-regulator stage, which supplies a stable bias to the internal circuitry of the IC. Figure 2 shows a simplified schematic of this section, as well as the external components required, inorder to generate bootstraping voltage from the secondary winding of inductor. The operation of the circuitry is as follows.

FIGURE 2 — START UP CIRCUITRY

Start-up capacitor  $C_3$  is first charged by the current through resistor  $R_3$ . Once this voltage exceeds 10V, then the IC starts operating, requiring more supply current than  $R_3$  can provide. This causes the energy stored in the capacitor to supply the IC with the operating current until the bootstrap winding on L1 takes over the power to maintain operation.

FIGURE 3 — START UP VOLTAGE

$$V_{\text{START}} = 1.25 \left[ \frac{R_{\text{A}}}{R_{\text{B}} || R_{\text{C}}} + 1 \right] \quad V_{\text{HYST}} = 1.25 \frac{R_{\text{A}}}{R_{\text{C}}}$$

## NOT RECOMMENDED FOR NEW DESIGNS

### **APPLICATION INFORMATION**

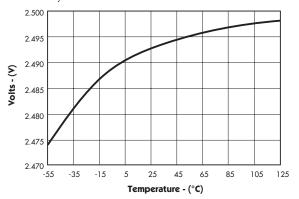

#### **VOLTAGE REFERENCE**

The voltage reference is a low drift bandgap design which provides a stable +2.5V output with ±1.5% initial tolerance. This pin is internally connected to the non-inverting input of error amplifier and is only available in a 14-pin package. It can provide up to 2mA of current for powering any external circuitries and is not internally current limited.

FIGURE 4 — REFERENCE VOLTAGE vs. TEMPERATURE

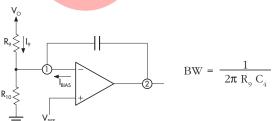

#### **ERROR AMPLIFIER**

The error amplifier is an internally compensated PNP input stage with access to the inverting input and output pin. The N.I. input is internally connected to the voltage reference and is available only in a 14-pin package. The amplifier is designed for an open loop gain of 85dB, along with a typical bandwidth of 1MHz and 57 degrees of phase margin. The amplifier's input bias current (2µA max.) results in a DC error in output voltage. In order to minimize this effect, the current flow in resistor R<sub>0</sub> must be much greater than the bias current; As an example, for a 1% error in output, the current must be at least 200µA. The error amp output is provided for an external compensation of the feedback loop. This compensation is typically just a capacitor connected between this pin and the inverting input pin. The compensation capacitor is designed to set the bandwidth such that it adequately rejects the low frequency ripple which is present at the output voltage.

FIGURE 5 — TYPICAL COMPENSATION CIRCUIT

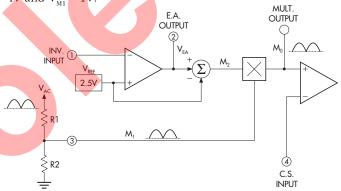

#### **MULTIPLIER**

The SG3561A features a one quadrant multiplier stage having two inputs: one is internally driven by a DC voltage (this being the difference of E.A. output and  $V_{\mbox{\tiny REF}}$  (M2)), and the other (M1) is available for external connection. The output is internally tied to an input of the PWM comparator. The rectified AC input is typically divided down to less than 1V and is connected to the "M1" input by a resistor divider. The output of the multiplier which is a function of both inputs, controls the inductor peak current during each cycle of operation.

The multiplier is mostly linear if the M1 input is limited to less than 1V and the E.A. output is kept below 3.5V (under all specified load and line conditions). The output clamps to a maximum value of 0.9V typically if the E.A. output is higher than 4V and  $V_{\rm M1}$  = 1V.

FIGURE 6 — MULTIPLIER CIRCUIT

$$\begin{aligned} \mathbf{X} &= \frac{\mathbf{V}_{\text{M0}}}{\mathbf{V}_{\text{M1}} \left(\mathbf{V}_{\text{EA}} - \mathbf{V}_{\text{REF}}\right)} & \text{where:} \quad \mathbf{K} &\equiv \text{Gain} \\ \mathbf{V}_{\text{M0}} &\equiv \text{Mult. Output} \\ \mathbf{V}_{\text{M1}} &\equiv \text{Mult. Input} \\ \mathbf{V}_{\text{EA}} &\equiv \text{E.A. Output} \end{aligned}$$

#### **CURRENT SENSE COMPARATOR / PWM LATCH**

Current Sense comparator is configured as a PNP input differential stage with one input internally tied to the multiplier output and the other available for current sensing. Current is converted to voltage using an external sense resistor in a series with the power MOSFET (Q1). When voltage across this resistor exceeds the threshold set by the multiplier output, the current sense comparator terminates the gate drive to Q1, as well as resetting the PWM latch. The latch ensures that the output remains in a low state once the switch current falls back to zero.

An offset is built into current sense input to ensure that the output remains in a low state when the load is removed from the output of the converter. This offset is guaranteed to be higher than the multiplier offset during the above condition.

## NOT RECOMMENDED FOR NEW DESIGNS

### APPLICATION INFORMATION

#### **CURRENT SENSE COMPARATOR / PWM LATCH** (continued)

Sense resistor  $\boldsymbol{R}_{8}$  is designed according to the following formula:

where:  $K \equiv Gain$   $V_{MO} \equiv Mult. \ Output \ under min. \ line \ condition$   $V_{M1} \equiv Mult. \ Input$   $V_{FA} \equiv E.A. \ Output$

R7 and C5 form a low pass filter to eliminate the leading edge current spike.

FIGURE 7 — CURRENT SENSE CIRCUIT

#### **PWM DRIVER STAGE**

The SG3561A output driver is designed for direct driving of power MOSFETs. It is a totem pole stage with ±0.5A peak current capability. This typically results in a 100 nanosecond rise and fall times into a 1000pF capacitive load. Additionally, the output is held low during the under voltage condition to ensure that the power MOSFET remains in the off state.

### **CURRENT DETECT LOGIC**

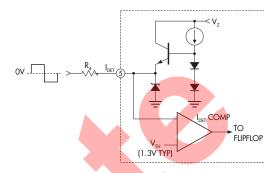

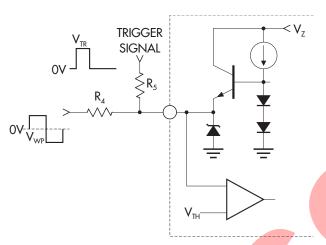

The function of "current detect logic" is to sense the operating state of the boose inductor and to enable the output driver accordingly. To achieve this, the downward slope of the inductor current is detected by monitoring the voltage across a separate winding and is connected to the detector input ( $I_{\rm DET}$ ) pin. Once the inductor current drops to zero, the sensed voltage reverses, setting the  $I_{\rm DET}$  input to a low-level, thus enabling the output driver. Since this is a negative voltage, a level shifter as shown in Figure 8 is provided to prevent the  $I_{\rm DET}$  pin from going below the ground. The maximum current drawn from this pin must be limited to less than 3mA.

A high level voltage occurs when the inductor discharges. Referring to Figure 9, once the C.S. comparator inhibits the output driver and resets the flip-flop, the inductor voltage reverses and sets the  $I_{\rm DET}$  pin to a high level. This ensures the reset instruction of the current sense comparator and reduces its noise susceptibility. An internal zener diode with maximum current capability of 3mA limits the positive voltage swing to 7 volts typically.

FIGURE 8 — I INPUT CIRCUIT

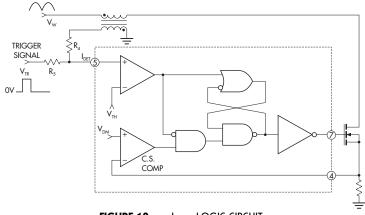

Since the output driver is inhibited during the power-on cycle, an external trigger signal is required to start-up the converter before the  $I_{\rm DET}$  winding takes over the operation. The trigger signal can be derived either from the second stage of the converter (i.e. the ballast voltage generator), or if stand alone operation is desired from a circuit as shown in Figure 9. Additionally, this signal should be low enough that the voltage from the detector winding is allowed to dominate during the normal operation.

The equations below describe the selection of  $R_4$  and  $R_5$  in Figure 10.

$$2500 \ V_{wp} \ge R_{_4} \ge 400 V_{wp} \qquad \text{where} \ V_{wp} \equiv \text{Peak detector} \\ R_{_5} = 0.8 \ R_{_4} \bigg( \frac{V_{_{TR}}}{1.6} \bigg) \qquad V_{_{TR}} \equiv \text{Trigger voltage} \\ V_{_{TR}} \square \square \square Q_{_{RES}} R_{_5} \qquad Q_{_{C_7}} Q_$$

FIGURE 9 — TYPICAL START UP CIRCUIT USING DIAC

FIGURE 10 - I<sub>DETECT</sub> LOGIC CIRCUIT

## NOT RECOMMENDED FOR NEW DESIGNS

### **APPLICATION INFORMATION**

#### TYPICAL APPLICATION

The application circuit shown in Figure 11 uses the SG3561A as the controller to implement a boost type power factor regulator. The IC controls the regulator, such that the inductor current is always operating in a discontinuous conduction mode with no current gaps. This mode of operation has several advantages over the fixed frequency discontinuous conduction mode: 1) The switching frequency adjusts itself to the AC line envelope, causing a sinusoidal current draw, 2) Since there is no current gap between the switching cycles, the inductor voltage does not oscillate, causing less radiated noise, 3) The lower peak inductor current causes less power dissipation in the power MOSFET.

A set of formulas have been derived specifically for this mode, and are used throughout the design procedure:

The following are specifications for the boost converter:

Input Voltage Range Output Voltage Output Power Efficiency

Power Factor

Total Harmonic Distortion

- 100 to 130V RMS

- 230V DC

- 80W

95% at full load

> 0.99 at full load

< 10% at full load

FIGURE 11 — TYPICAL APPLICATION WITH 120V INPUT

#### **OUTPUT VOLTAGE REQUIREMENT**

Since the converter is a boost type topology, it requires the output voltage to always be higher than the input voltage. It is recommended to choose this voltage at least 15% higher than the maximum input voltage.

$$V_0 \ge 1.15 * 130 \sqrt{2} = 211 \text{ Volts}$$

#### **INDUCTOR PEAK CURRENT**

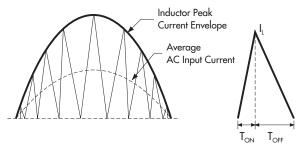

It can be shown by referring to Figure 12 that the inductor peak current is always twice the average input current.

FIGURE 12 — INDUCTOR CURRENT

## NOT RECOMMENDED FOR NEW DESIGNS

### **APPLICATION INFORMATION**

### **INDUCTOR PEAK CURRENT** (continued)

$$\begin{split} &I_{_{\mathrm{IN(1)}}} &= \sum \!\! \mathrm{AVE} \left[ I_{_{\mathrm{L}}} \left( t \right) \right] \\ &I_{_{\mathrm{IN}}} &= \frac{1}{T} \left[ \frac{\left( I_{_{\mathrm{L}}} \right) \left( T \right)}{2} \right] \cdot \frac{I_{_{\mathrm{L}}}}{2} \\ &I_{_{\mathrm{IN(Peak)}}} &= I_{_{\mathrm{P}}} = \frac{I_{_{\mathrm{LP}}}}{2} \end{split}$$

I<sub>IP</sub> = Inductor peak current at peak input voltage.

Maximum peak input current can be calculated by using:

$$I_{p} = \frac{2P_{O}}{\eta V_{p}}$$

where:  $\eta \equiv \text{Converter efficiency}$  $V_p \equiv \text{Peak AC input voltage}$

assuming:

$$\eta = 95\%$$

,  $P_{O} = 80$ W,  $V_{Pmin} = 100\sqrt{2} = 141$

$I_{P} = \frac{2*80}{(.95)(141)} = 1.2$ A

$I_{LP/min AC} = 2*1.2 = 2.4$ A

#### **INDUCTOR DESIGN**

The most important part of the circuit is to design the energy storage element. To do this, we use the following equation to calculate the inductance value:

$$L_{1} = \frac{.95 \left(\frac{230 \cdot 120 \sqrt{2}}{230}\right) 20 * 10^{-6} * (120 \sqrt{2})^{2}}{4 * 80} = 448 \mu H$$

Once the inductance is calculated, we can either use the area product method (AP) or other  $K_g$  (based on copper losses method), for selecting proper core. In this example, we apply the  $K_g$  approach using the following steps:

**Step 1:** Calculate

$$K_g$$

using

$$K_{g} = \frac{\Omega}{P_{CU}} \left( \frac{L_{l}I_{LP}^{2}}{B} \right)^{2}$$

where:  $L_1 \equiv Required inductance$

$\Omega \equiv 1.724 * 10^{-8} \,\mathrm{m}$

$B \equiv Maximum flux density$

$I_{_{LP}} \equiv Maximum peak inductor current <math>P_{_{CII}} \equiv Maximum copper dissipation$

#### **INDUCTOR DESIGN** (continued)

Assume:

$$P_{CU} = 1.6W$$

(2% of total output)

$$K_g = \frac{1.724*10^{-8}}{1.6} \left[ \frac{450*10^{-6}*(2.4)^2}{0.15} \right]^2 = 3.21*10^{-12} \text{ m}^5$$

$$K_g/core = k \frac{A_w A_E^2}{I_w}$$

where:  $k \equiv \text{Winding coefficient (typ. k=0.4)}$

$A_{w} \equiv Bobbin \text{ window area}$   $A_{E} \equiv Effective \text{ core area}$   $I_{w} \equiv Mean \text{ length per turn}$

$$K_g$$

factor for TDK PQ2625:

$A_W = 47.7 \text{mm}^2$

$A_E = 118 \text{mm}^2$

$I_W = 56.2 \text{mm}$

$$K_g = 0.4 \frac{(47.7) (118)^2}{56.2} (mm)^5 = 4.7 * 10^{-12} m^5$$

### **Step 3:** Determine number of turns.

$$N = \frac{L I_{LP}}{B A_E}$$

$$N = \frac{450 * 10^{-6} * 2.4}{0.15 * 118 * 10^{-6}} = 61 \text{ turns}$$

$$A_{WIRE} = k \frac{A_W}{N} = 0.4 \frac{47.7}{61} = 0.31 \text{mm}^2$$

$$= 480 \text{mil}^2$$

choose #22 AWG with  $r = 0.0165\Omega$ /feet resistance.

$$R_{w} = N * I_{w} * r$$

$$R_{w} = 0.185\Omega$$

### Step 4: Calculate air gap.

$$I_{g} = \frac{\mu_{o} N^{2} A_{E}}{L}$$

$$I_{q} = \frac{4\pi * 10^{-7} * (61)^{2} * 118 * 10^{-6}}{450 * 10^{-6}} = 0.122cm = 48 \text{ mil}$$

Step 5:

$$N_s \approx N_p \frac{V_s}{V_o}$$

$N_s = 61 \frac{15}{230} = 4T$  where:  $V_s \equiv$  secondary voltage

$\rm N_{\rm s}$  may be adjusted to account for the drop in start-up capacitor.

## NOT RECOMMENDED FOR NEW DESIGNS

### APPLICATION INFORMATION

#### **POWER MOSFET SELECTION**

The voltage rating of MOSFET and rectifier must be higher than the maximum value of the output voltage.

$$V_{DS} \ge 1.2 V_{OMAX}$$

$V_{DS} \ge 282 V$

The RMS current can be approximated by multiplying the RMS current at the peak of the line by 0.7.

$$\begin{split} I_{RMS} &= 0.7 \; I_{LP} \; \sqrt{D/3} \qquad D \equiv \text{On-time duty cycle} \\ D &= 0.39 \; \text{at V}_{AC} = 100 \text{V} \\ I_{LPI} &= 2.4 \text{A} \\ I_{RMS} &= (0.7) \; (2.4) \; (\sqrt{.39/3}) = 0.61 \text{A} \\ R_{DS} &\leq \frac{P_{DC}}{I_{RMS}^2} \qquad I_{RMS} / \text{triangle} = I_{LP} \; \sqrt{D/3} \\ P_{DC} &\equiv \text{allowable power dissipation} \end{split}$$

$R_{DS} \le \frac{1}{0.61}$  = 1.6 $\Omega$ choose IRF730 with  $R_{DS} = 1\Omega$  and  $V_{DS} = 400V$ .

#### CURRENT SENSE AND MULTIPLIER COMPONENT SELECTION

Resistors  $R_1$  and  $R_2$  are selected such that the peak voltage at M1 input (pin 3) is 1V at the maximum line voltage.

$$\frac{R_1}{R_2} = V_{AC \text{ PEAK}} - 1$$

$\frac{R_1}{R_2} = 183$  if  $\mathbf{R_1} = \mathbf{2.2M}$  then  $R_2 = 12K$

The value of R<sub>s</sub> can be selected using the following equations:

$$V_{M0}$$

= k  $V_{M2} * V_{M1}$   $V_{M1}$  = Maximum voltage at M1 input under min. line condition

$$V_{M0} = (0.75) (3.5 - 2.5) (0.77) = 0.58$$

$R_8 = \frac{V_{MO}}{I_{1p}} = \frac{0.58}{2.4} = \frac{0.58}{2.4} = 0.24\Omega$  choose  $R_8 = 0.22\Omega$

To eliminate the turn-on current spike, a low pass filter with a high corner frequency must be designed such that:

$$R_7C_4 \ge 1.6T$$

Turn-on Spike if  $T = 100$ nsec  $R_7C_4 \ge 0.16\mu$ sec  $T$  assuming  $T$  assuming  $T$  assuming  $T$  assuming  $T$  as  $T$  assuming  $T$  as  $T$  assuming  $T$  as  $T$  and  $T$  as  $T$  as  $T$  as  $T$  as  $T$  as  $T$  as  $T$  and  $T$  as  $T$

The values of  $R_7$  and  $C_4$  may be optimized further based on each specific application. Additionally  $R_{13}$  can be used to adjust the overall loop gain in order to maintain regulation at the minimum input voltage.

#### ERROR AMPLIFIER COMPONENT SELECTION

The values of  $R_9$  and  $R_{10}$  are calculated based on the operating output voltage. The value of  $C_5$  is mainly selected to reject the 120Hz ripple associated with the output voltage. Lack of adequate ripple rejection causes input current distortion; however, too much rejection will make a slow loop response and a high voltage overshoot during the turn-on.

$$\frac{R_o}{R_{10}} = \frac{V_o}{V_{REF}} - 1$$

$$\frac{R_o}{R_{10}} = \frac{230}{2.5} - 1 = 91$$

assuming  $R_o = 1M\Omega$  Then:  $R_{10} = 11K$

For output voltages higher than 250V, safety regulations may require two ¼W resistors to be placed in series.

Assuming a 40dB rejection at 120Hz:

$$\begin{aligned} & \text{Gain} = \frac{1}{2\pi \text{ f R}_9 \text{ C}_5} & \text{Gain}/120\text{Hz} \leq 0.01 \\ & \text{C}_5 \geq \frac{100}{2\pi(120)(10^6)} & \\ & \text{C}_5 \geq 0.133\mu\text{f} & \text{choose C}_5 = 0.22\mu\text{f} \\ & \text{BW} = \frac{1}{2\pi \text{ R}_9 \text{ C}_5} = \frac{1}{2\pi (10^6)(.22*10^{-6})} = 0.72\text{Hz} \end{aligned}$$

#### INPUT RECTIFIER AND CAPACITOR SELECTION

The current through each diode is a half-wave rectified sine wave. The maximum current happens at minimum line with a peak value of 1.2A.

$$I_{AVE} = \frac{I_{PEAK}}{\pi} = \frac{1.2}{\pi} = 0.38A$$

choose 1N4004 with 1A rating.

$$\begin{split} P_{DISS} &= (I_{AVE}) \ (V_p) = 0.38 * 0.9 = 0.344W \\ T_J &= T_A + P_D \ x \ \theta_{JA} & assuming \ \theta_{JA} = 65 ^{\circ}\text{C/W for 1/8"} \\ & lead \ length. \end{split}$$

$$T_r = 80 + (.344)(65) = 102$$

°C

### NOT RECOMMENDED FOR NEW DESIGNS

#### APPLICATION INFORMATION

#### **INPUT RECTIFIER AND CAPACITOR SELECTION** (continued)

Assuming  $\varphi$  is the percentage of allowable input current ripple, C, can be calculated using the following equations:

$$R_{EFF} = \frac{2 P_O}{\eta I_D^2}$$

$$C_{1} \ge \frac{1}{\phi 2\pi R_{EFF} f_{SW}}$$

$C_1 \ge \frac{1}{\varphi 2\pi R_{EFF} f_{SW}}$   $f_{SW} \equiv Switching frequency of inductor current$ at peak input voltage.

if  $\varphi = 3\%$

$$R_{EFF} = \frac{2 * 80}{(.95)(1.2)^2} = 117\Omega$$

$$C_1 \ge \frac{1}{(.03)(2\pi)(117)(50000)} = 0.9\mu F$$

choose 1µF, 250V capacitor.

#### **BIAS SUPPLY COMPONENT SELECTION**

A bleeding resistor (R<sub>2</sub>) off of either output voltage or capacitor C, can be selected such that it provides sufficient start-up current for the IC, as well as charging the start-up capacitor C<sub>2</sub>.

$$R_{3} = \frac{V_{P \text{ MIN}}}{I_{ST}}$$

$$R_{3} = \frac{140}{0.5 * 10^{-3}} = 280K$$

$\begin{array}{ll} R_3 = \frac{V_{P\,MIN}}{I_{ST}} & I_{ST} & \equiv Start\text{-up current} \\ R_3 = \frac{140}{0.5*10^{-3}} = 280 \text{K} & V_{P\,MIN} & \equiv Peak\ AC\ voltage\ at \\ P_{R3} = \frac{V_{IN\,MAX}}{R_3} \leq 0.25 \text{W} & V_{IN\,MAX} & \equiv Max.\ RMS\ input \end{array}$

$$P_{R3} = V_{IN MAX} \over R_3 \le 0.25 V$$

$$R_3 \ge 4V_{IN\ MAX}^2$$

$$280K \ge R_3 \ge 68K$$

choose R<sub>3</sub> = 110K

The start-up capacitor must be chosen such that it supplies power to the IC until the voltage on the bootstrap winding exceeds the start threshold (this is typically around 10 volts). C<sub>3</sub> must also be designed to have low ripple voltage at twice the line frequency.

$$C_3 (\Delta V_R) \ge \frac{I}{2 f_{LINE} \Delta V_R}$$

$\begin{array}{c} C_{_{3}} \; (\Delta V_{_{R}}) \geq \frac{I}{2 \; f_{_{LINE}} \; \Delta V_{_{R}}} & I \; \equiv \text{Operating current} \\ f_{_{LINE}} \; \equiv \text{Line frequency} \\ \Delta V_{_{r}} \; \equiv \text{Ripple voltage} \\ C_{_{3}} \; (\Delta T) \geq \; \frac{I\Delta T}{\Delta V_{_{H}}} & \Delta T \; \equiv \text{Time allowed for bootstrap} \\ & \text{winding to reach start-up} \end{array}$

$$C_3 (\Delta V_R) \ge \frac{15 * 10^{-3}}{2 * 60 * 2} = 62 \mu F$$

assuming  $\Delta T = 2ms$

$$C_3 (\Delta T) \ge \frac{15 * 10^{.3} * 2 * 10^{.3}}{1.8V} = 17 \mu f$$

choose  $C_3 = 68 \mu F$ .

### **OUTPUT CAPACITOR SELECTION**

There are mainly two criterias for selecting the output capacitor: A large enough capacitance to maintain a low ripple voltage, and a low ESR value in order to prevent high power dissipation due

The output capacitance can be approximated from the following equation:

$$C_6 \ge \frac{I_{DC}}{2\pi f_{LINE} \Delta V}$$

$C_6 \ge \frac{I_{DC}}{2\pi f_{IINE} \Delta V}$  where:  $I_{DC} \equiv DC$  output current  $\Delta V \equiv Output$  ripple

$$I_{DC} = \frac{80}{230} = 0.348A$$

assuming 5% peak to peak ripple,

$$C_6 \ge \frac{0.348}{2\pi (60) (11.5)} = 81 \mu F$$

choose  $C_6 = 100 \mu F$ .

#### **CURRENT DETECT COMPONENT SELECTION**

The values of R4 and R5 can be calculated using the following equations:

$$400V_{WP} \ge R_4 \ge 2500V_{WP}$$

$$R_5 = 0.8R_4 \left( \frac{V_{TR}}{1.6} \right)$$

where:

$V_{WP} \equiv Maximum detector winding voltage$

$V_{TR} \equiv Trigger voltage$

## NOT RECOMMENDED FOR NEW DESIGNS

## APPLICATION INFORMATION

#### **CURRENT DETECT COMPONENT SELECTION** (continued)

Assuming  $V_{WP}$  = 15V and peak trigger voltage from the start-up circuitry is 7V, the values  $R_4$  and  $R_5$  using above formulas are:

$$6\mathrm{K}\Omega \leq \mathrm{R}_{_{4}} \leq 37.5\mathrm{K}\Omega$$

choose

$$R_4 = 22K$$

$$R5 = 0.8 (22) \left( \frac{7}{1.6} - 1 \right) = 59.4 \text{K}\Omega$$

choose

$$R_5 = 51K$$

FIGURE 13 — CURRENT DETECT EXAMPLE

### NOT RECOMMENDED FOR NEW DESIGNS

## TYPICAL APPLICATIONS

## 120V

Pin numbers are for 8-pn dip package.

FIGURE 14 — TYPICAL APPLICATION OF THE SG3561A IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL.

| Electrical Specification 120VAC Input — 230VDC / 80W Output                                                                 |                                                                                                                                                                                                            |                                                            |                                              |                                                                                                        |        |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------|--------|--|--|

| Ref.                                                                                                                        | Component                                                                                                                                                                                                  | Manuf.                                                     | Ref.                                         | Component                                                                                              | Manuf. |  |  |

| IC<br>L1<br>Q1<br>D1-D4<br>D5<br>D6<br>D7<br>R1<br>R2<br>R3<br>R4<br>R5<br>R6<br>R7<br>R8<br>R9<br>R10<br>R11<br>R12<br>R13 | SG3561AM PQ2625/H7C1 Core IRF730, 400V 1N4004, Diode, 1A 1N4935, Diode, 1A MR854, 3A, 400V HT32, DIAC 2.2MΩ 12KΩ 110K, ½W 22K 51K 47Ω 330Ω 0.22Ω, ½W - Carbon type 1MΩ, 1% Res 11KΩ, 1% Res 560KΩ 300Ω 2KΩ | Linfinity<br>TDK<br>I.R.<br>Motorola<br>Motorola<br>TECCOR | C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C8 | 1μF/250V<br>0.01μF/50V<br>68μF/25V<br>0.22μF/50V<br>3300pF/50V<br>100μF/400V<br>0.1μF/50V<br>0.1μF/50V |        |  |  |

### NOT RECOMMENDED FOR NEW DESIGNS

## TYPICAL APPLICATIONS

### 220V

#### Pin numbers are for 8-pn dip package.

FIGURE 15 — TYPICAL APPLICATION OF THE SG3561A IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL.

| Ref.                                                                                                                        | Component                                                                                                                                                                                      | Manuf.                                                     | Ref.                                         | Component                                                                                                | Manuf. |

|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------|--------|

| IC<br>L1<br>Q1<br>D1-D4<br>D5<br>D6<br>D7<br>R1<br>R2<br>R3<br>R4<br>R5<br>R6<br>R7<br>R8<br>R9<br>R10<br>R11<br>R12<br>R13 | SG3561A PQ262/H7C1 Core IRF830, 500V 1N4004, Diode, 1A 1N4935, Diode, 1A MR856, 3A, 600V HT32, DIAC 2.2MΩ 12KΩ 220K, ½W 22K 39K 47Ω 330Ω 1Ω, ½W - Carbon type 1MΩ, 1% Res 2.7MΩ 560KΩ 300Ω 2KΩ | Linfinity<br>TDK<br>I.R.<br>Motorola<br>Motorola<br>Teccor | C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C8 | 0.22µF/600V<br>0.01µF/50V<br>68µF/25V<br>0.22µF/50V<br>3300pF/50V<br>47µF/450V<br>0.1µF/50V<br>0.1µF/50V |        |

### NOT RECOMMENDED FOR NEW DESIGNS

## TYPICAL APPLICATIONS

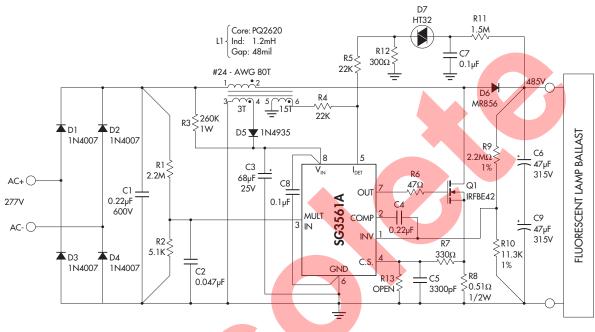

### 277V

#### Pin numbers are for 8-pn dip package.

FIGURE 16 — TYPICAL APPLICATION OF THE SG3561A IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL.

| Ref.                                                                                                          | Component                                                                                                                                                                                                                   | Manuf.                                                     | Ref.                                             | Component                                                                                                 | Manuf. |

|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------|

| IC<br>L1<br>Q1<br>D1-D4<br>D5<br>D6<br>D7<br>R1<br>R2<br>R3<br>R4<br>R5<br>R6<br>R7<br>R8<br>R9<br>R10<br>R11 | SG3561A PQ2620/H7C1 Core IRFBE42, 600V 1N4007, Diode, 1A 1N4935, Diode, 1A MR856, 3A, 600V HT32, DIAC 2.2MΩ 5.1KΩ 260KΩ, 1W 22KΩ 22KΩ 47Ω 330Ω 0.51Ω, $\frac{1}{2}$ W - Carbon type 2.2MΩ, 1% Res 11.3KΩ, 1% Res 1.5KΩ 300Ω | Linfinity<br>TDK<br>I.R.<br>Motorola<br>Motorola<br>TECCOR | C1<br>C2<br>C3<br>C4<br>C5<br>C6, C9<br>C7<br>C8 | 0.22µF/600V<br>0.047µF/50V<br>68µF/25V<br>0.22µF/50V<br>3300pF/50V<br>47µF/315V<br>0.1µF/50V<br>0.1µF/50V |        |

D2 الا-1N4007 ĂD1

J3 D4 1N4007 " **▲** D3

AC+ O

AC- ()-

277V

1N4007

C1 -

0.22µF 600V

1N4007

R1 \$ 2.2M 1%

\_\_ C2

0.033µF

R2 7.5K ≶

1%

C3 68µF

25V

C9

0.1µF

IC1

GND

MULT 3 IN

SG3561A SOND COMP

INV

## POWER FACTOR CONTROLLER

### NOT RECOMMENDED FOR NEW DESIGNS

TYPICAL APPLICATIONS

#### 277V - Buck Boost Application Pin numbers are for 8-pn dip package. FLUORESCENT LAMP BALLAST Core: PQ2620 L1 { Ind: 1.2mH R5 22K Ş 230V 100µF 2 Gap: 48mil 400V MUR480 or #24 - AWG 80T BYW96D 3 4T 4 5 7T 6 R4 -√√√ 22K D6 499K < R3 \bigsim 150K 2W D5 🛨 1N4935 1% R13

499K

1%

R12 | 12.7K

IC2

-^/^ 12.7K

1%

0.033µF

R10

\$130K

1/2W

₹ 499K 1%

- C8

0.033µF

FIGURE 17 — TYPICAL APPLICATION OF THE SG3561A IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL.

| l                     |                   |            |        |                          |        |

|-----------------------|-------------------|------------|--------|--------------------------|--------|

| Electrico<br>Specific |                   | t — 230VDC | / 80W  | Output                   |        |

| Ref.                  | Component         | Manuf.     | Ref.   | Component                | Manuf. |

| IC                    | SG3561A           | Linfinity  | C1     | 0.22µF/600V              |        |

| IC2                   | LM358N            |            | C2     | 0.033 <sub>µ</sub> F/50V |        |

| L1                    | PQ2620/H7Cl Core  | TDK        | C3     | 68µF/25V                 |        |

| Q1                    | IRFPE52, 800V     | I.R.       | C4     | 0.22µF/50V               |        |

| D1-D4                 | 1N4007, Diode, 1A | Motorola   | C5     | 3300pF/50V               |        |

| D5                    | 1N4935, Diode, 1A | Motorola   | C6     | 100µF/400V               |        |

| D6                    | BYW96D, 4A, 800V  |            | C7, C8 | 0.033µF/50V              |        |

| R1                    | 2.2MΩ, 1%         |            | C9     | 0.1µF/50V                |        |

| R2                    | 7.5KΩ, 1%         |            |        |                          |        |

| R3                    | 150K, 2W          |            |        |                          |        |

| R4                    | 22kΩ              |            |        |                          |        |

| R5                    | 22K               |            |        |                          |        |

| R6                    | 22Ω               |            |        |                          |        |

| R7                    | 330Ω              |            |        |                          |        |

| R8                    | 0.22Ω, ½W         |            |        |                          |        |

| R9                    | 20K               |            |        |                          |        |

| R10                   | 130K              |            |        |                          |        |

| R11                   | 12.7K, 1%         |            |        |                          |        |

| R12                   | 12.7K, 1%         |            |        |                          |        |

| R13, 14               |                   |            |        |                          |        |

| R15, 16               | 499K, 350V        |            |        |                          |        |

### NOT RECOMMENDED FOR NEW DESIGNS

## TYPICAL APPLICATIONS

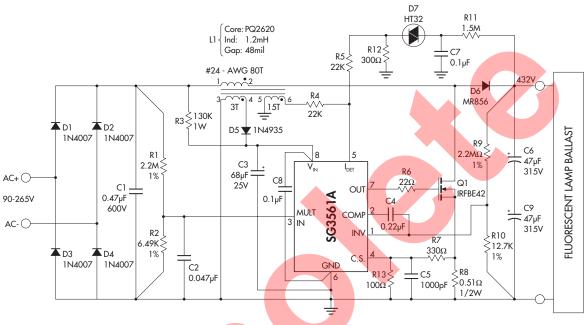

### 90 - 265V

Pin numbers are for 8-pn dip package.

FIGURE 18 — TYPICAL APPLICATION OF THE SG3561A IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL.

| Electrico<br>Specific |                                                    | - 432VDC                       | / 80W              | Output                               |        |

|-----------------------|----------------------------------------------------|--------------------------------|--------------------|--------------------------------------|--------|

| Ref.                  | Component                                          | Manuf.                         | Ref.               | Component                            | Manuf. |

| IC<br>L1              | SG3561A<br>PQ2620/H7C1 Core                        | Linfinity<br>TDK               | C1<br>C2           | 0.47μF/600V<br>0.047μF/50V           |        |

| Q1<br>D1-D4           | IRFBE42, 600V<br>1N4007, Diode, 1A                 | I.R.<br>Motorola               | C3<br>C4           | 68μF/25V<br>0.22μF/50V               |        |

| D5<br>D6<br>D7        | 1N4935, Diode, 1A<br>MR856, 3A, 600V<br>HT32, DIAC | Motorola<br>Motorola<br>TECCOR | C5<br>C6, C9<br>C7 | 1000pF/50V<br>47μF/315V<br>0.1μF/50V |        |

| R1<br>R2              | 2.2MΩ, 1%<br>6.49K, 1%                             | TECCOR                         | C8                 | 0.1µF/50V                            |        |

| R3<br>R4              | 130K, 1W<br>22kΩ                                   |                                |                    |                                      |        |

| R5<br>R6              | 22K<br>22Ω                                         |                                |                    |                                      |        |

| R7<br>R8              | 330Ω<br>0.51Ω, ½W - Carbon type                    |                                |                    |                                      |        |

| R9<br>R10             | $2.2M\Omega$ , 1% Res $12.7K\Omega$ , 1% Res       |                                |                    |                                      |        |

| R11<br>R12<br>R13     | 1.5KΩ<br>300Ω<br>100Ω                              |                                |                    |                                      |        |