# UG0586 User Guide RTG4 FPGA Clocking Resources

a MICROCHIP company

#### Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revisi | on His         | tory                        | 1    |

|---|--------|----------------|-----------------------------|------|

|   | 1.1    | Revision       | n 11.0                      | 1    |

|   | 1.2    | Revision       | n 10.0                      | 1    |

|   | 1.3    | Revision       | n 9.0                       | 1    |

|   | 1.4    | Revision       | n 8.0                       | 1    |

|   | 1.5    | Revision       | n 7.0                       | 1    |

|   | 1.6    | Revision       | n 6.0                       | 1    |

|   | 1.7    |                | n 5.0                       |      |

|   | 1.8    | Revision       | n 4.0                       | 2    |

|   | 1.9    | Revision       | n 3.0                       | 2    |

|   | 1.10   |                | n 2.0                       |      |

|   | 1.11   | Revision       | n 1.0                       | 2    |

| _ | OL 1:  | Б              |                             | 0    |

| 2 |        | •              | sources Overview            |      |

|   | 2.1    |                | ction                       |      |

|   | 2.2    | Clocking       | g Scheme Overview           | 4    |

| 3 | FPGA   | Fabric         | Global Network Architecture | 6    |

|   | 3.1    |                | tion                        |      |

|   | 3.2    |                | Network Architecture        |      |

|   |        | 3.2.1          | SerDes Output Clocks        |      |

|   |        | 3.2.2          | Dedicated Global I/Os       |      |

|   |        | 3.2.3          | Fabric CCC                  |      |

|   |        | 3.2.4<br>3.2.5 | Global Buffer (GB)          |      |

|   | 3.3    |                | Recommendations             |      |

|   | 3.3    | 3.3.1          | Global Macros               |      |

|   |        | 3.3.2          | Managing Global Signals     |      |

|   |        | 3.3.3          | Place and Route             |      |

|   |        | 3.3.4          | Global Net Clock Jitter     |      |

|   | 3.4    | SmartPo        | ower Usage Tips             | 24   |

| 4 | On-Ch  | nin Osc        | cillator                    | 26   |

|   | 4.1    |                | otion                       |      |

|   | 4.2    |                | nal Description             |      |

|   | 4.3    |                | Use On-Chip Oscillator      |      |

|   |        |                |                             |      |

| 5 | Fabric | Clock          | Conditioning Circuitry      | . 28 |

|   | 5.1    | Introduc       | etion                       |      |

|   |        | 5.1.1          | Features                    |      |

|   | 5.2    | •              | -Level Block Diagram        |      |

|   | 5.3    |                | CCC Locations               |      |

|   | 5.4    |                | nal Description             |      |

|   |        | 5.4.1<br>5.4.2 | Fabric CCC Clock Sources    |      |

|   |        | 5.4.2<br>5.4.3 | Fabric CCC Clock Sources    |      |

|   |        | 5.4.4          | GPMUX                       |      |

|   |        | 5.4.5          | GPD                         |      |

|   |        | 5.4.6          | SRG                         | 42   |

|     | 5.4.7  | Clock Gating Logic (CGL)                                                | 44 |

|-----|--------|-------------------------------------------------------------------------|----|

|     | 5.4.8  | RX Clock Recovery (SpaceWire)                                           |    |

| 5.5 | How to | Use SpaceWire Mode and Glitch Filter Mode using RX Clock Recovery Block | 47 |

| 5.6 | Guidel | ines for using CCC with Simultaneous Switching Registers                | 48 |

| 5.7 | Fabric | CCC Configuration                                                       | 49 |

|     | 5.7.1  | Fabric CCC Static Configuration                                         | 49 |

|     | 5.7.2  | Fabric CCC Dynamic Configuration                                        | 49 |

| 5.8 | Fabric | CCC Configuration Registers                                             | 49 |

|     | 5.8.1  | Fabric CCC Configuration Registers Bit Definitions                      | 51 |

|     | 5.8.2  | Fabric CCCs Multiplexers Selection Control                              | 58 |

| 5.9 | How to | Use Fabric CCC(s)                                                       | 60 |

|     | 5.9.1  | Basic                                                                   | 60 |

|     | 5.9.2  | Advanced Options                                                        | 60 |

|     | 5.9.3  | PLL Options                                                             |    |

|     | 5.9.4  | PLL/CCC Configuration Register Report                                   |    |

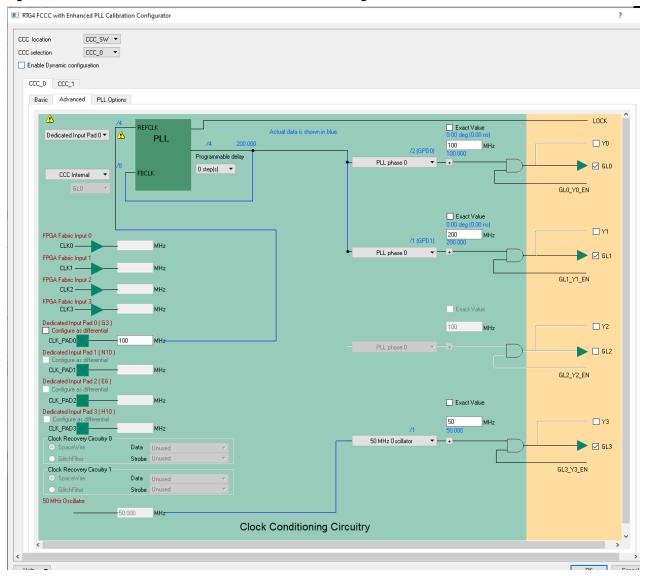

|     | 5.9.5  | Using RTG4 FCCC with Enhanced PLL Calibration                           |    |

|     | 5.9.6  | Simulation Support                                                      | 77 |

# **Figures**

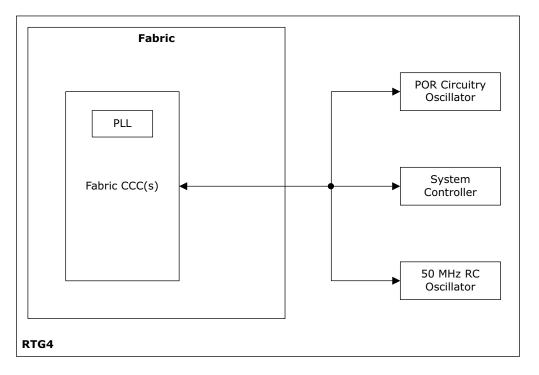

| Figure 1  | Clocking Scheme Overview                                                   | . 4 |

|-----------|----------------------------------------------------------------------------|-----|

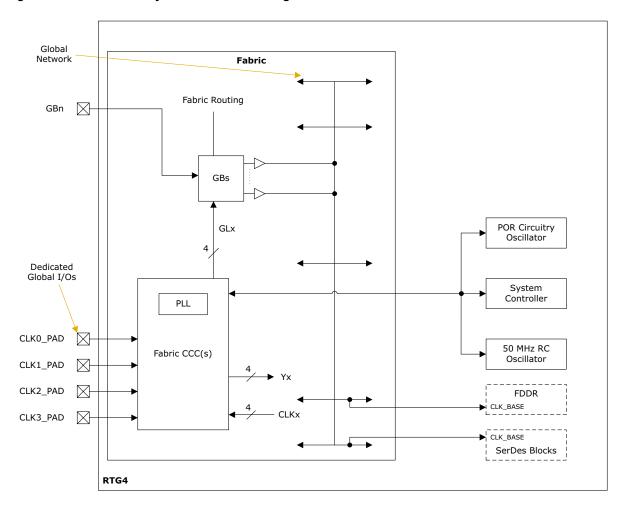

| Figure 2  | Global Signal Routing                                                      | . 7 |

| Figure 3  | Global Network Architecture for RT4G150 Devices                            |     |

| Figure 4  | Dedicated Global I/Os (SouthWest corner) Assignment in and RT4G150 Devices | . 9 |

| Figure 5  | Various Sources Feeding Global Buffers                                     |     |

| Figure 6  | Row Global Signals Driving Clusters                                        |     |

| Figure 7  | Synthesize Options Dialog Box                                              |     |

| Figure 8  | Example of Global Net Report 1                                             |     |

| Figure 9  | Example of Global Net Report 2                                             |     |

| Figure 10 | SmartPower Window                                                          |     |

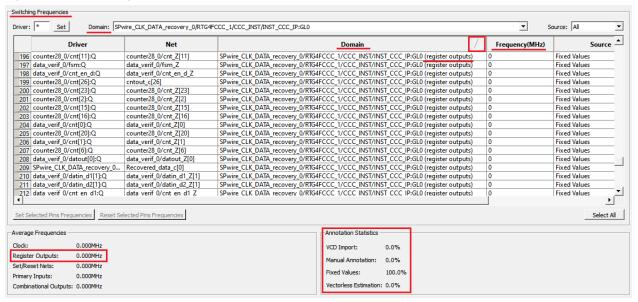

| Figure 11 | Switching Frequencies                                                      |     |

| Figure 12 | RTG4 On-Chip Oscillator Clock Sourcing Capabilities                        |     |

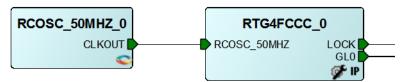

| Figure 13 | 50 MHz RC Oscillator and Fabric CCC Connectivity                           |     |

| Figure 14 | Fabric CCC System-Level Block Diagram                                      |     |

| Figure 15 | Fabric CCC Locations in the RTG4 Devices                                   |     |

| Figure 16 | Fabric CCC Block Diagram                                                   |     |

| Figure 17 | Fabric PLL Circuitry                                                       |     |

| Figure 18 | GPMUX Input Clock Sources                                                  |     |

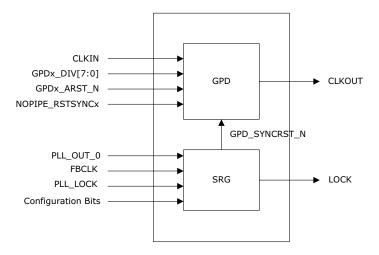

| Figure 19 | GPD Block Diagram                                                          |     |

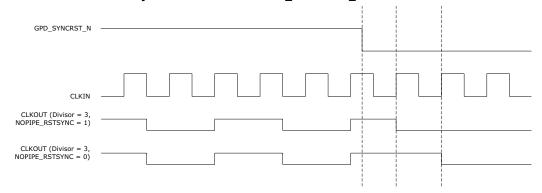

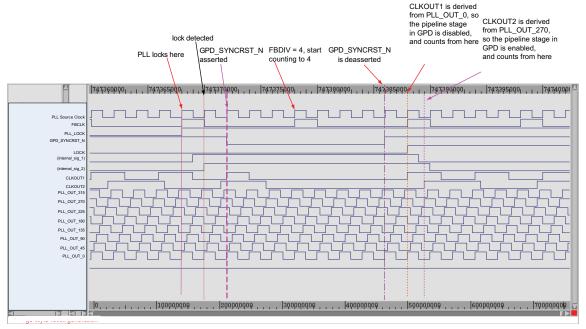

| Figure 20 | Assertion of GPD Synchronous Reset – GPD_SYNCRST_N                         |     |

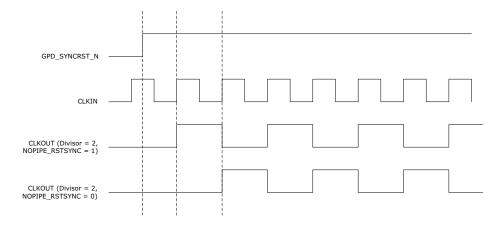

| Figure 21 | Releasing of GPD Synchronous Reset – GPD_SYNCRST_N                         |     |

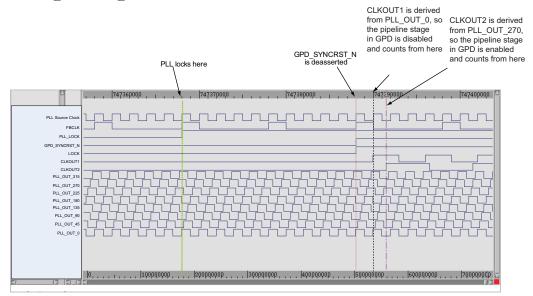

| •         | GPD_SYNCRST_N Released after PLL Locks                                     |     |

| Figure 22 | GPD Output Resynchronization after PLL Locks                               |     |

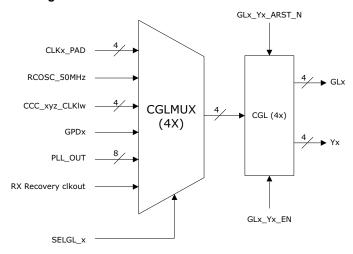

| Figure 23 | CGLMUX Block Diagram                                                       |     |

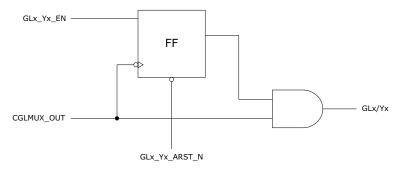

| Figure 24 | CGL Circuit                                                                |     |

| Figure 25 |                                                                            |     |

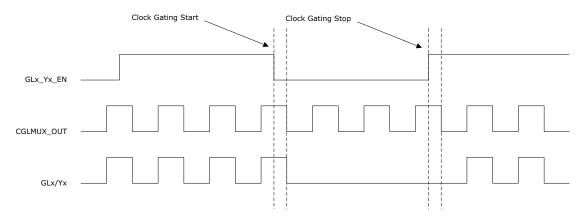

| Figure 26 | CGL Operation Waveform                                                     |     |

| Figure 27 | SpaceWire Rx Clock Recovery Block Diagram                                  |     |

| Figure 28 | SpaceWire Rx Clock Recovery Waveform                                       |     |

| Figure 29 | SpaceWire                                                                  |     |

| Figure 30 | Glitch Filter                                                              |     |

| Figure 31 | Advanced Options                                                           |     |

| Figure 32 | PLL Options                                                                |     |

| Figure 33 | Design Window                                                              |     |

| Figure 34 | PLL/CCC Configuration Report File                                          |     |

| Figure 35 | CCC Registers Configuration Report                                         |     |

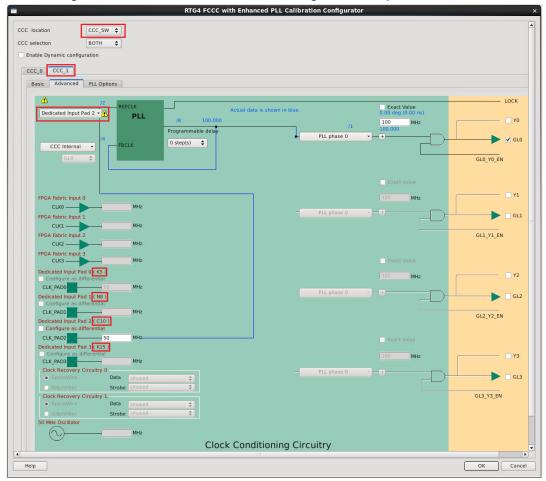

| Figure 36 | Selecting CCC Being Instantiated in Enhanced PLL Calibration Core          |     |

| Figure 37 | Package Pin Number Shown on Advanced Configuration Tab per CCC             |     |

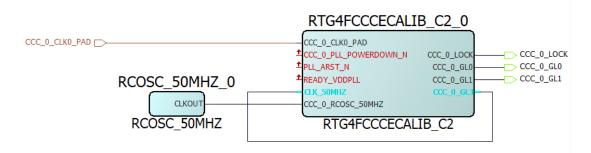

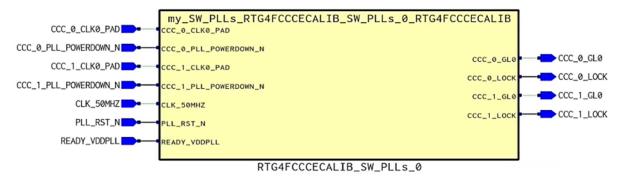

| Figure 38 | Graphical Example of Generated RTG4FCCC with Enhanced PLL Calibration      |     |

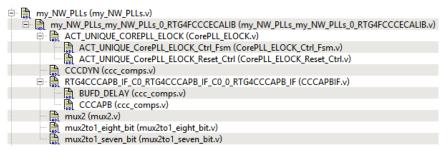

| Figure 39 | HDL Module Hierarchy for RTG4 FCCC with Enhanced PLL Calibration           |     |

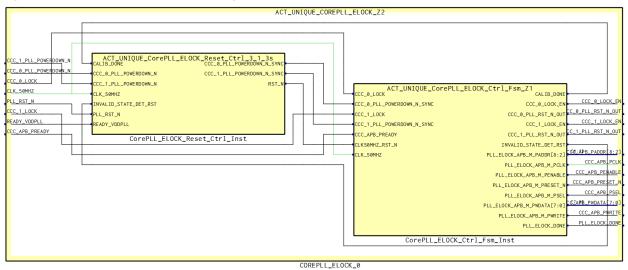

| Figure 40 | CorePLL_ELOCK Block Diagram                                                |     |

| Figure 41 | RTG4 FCCC with Enhanced PLL Calibration Configuration Report               |     |

| Figure 42 | Example SmartDesign Canvas with the HDL+ Component                         |     |

| Figure 43 | Output Clocks Settings                                                     |     |

| Figure 44 | Fabric CCC Reference Clock Selection                                       |     |

| Figure 45 | Fabric CCC and On-chip Oscillator Connectivity                             |     |

| Figure 46 | Fabric CCC Configuration                                                   |     |

| Figure 47 | Dedicated Global I/O Selection                                             |     |

| Figure 48 | PLL Auto-Reset Circuit                                                     |     |

| Figure 49 | PLL Auto-Reset Circuit HDL Files                                           |     |

| Figure 50 | RTG4 FCCC with Enhanced PLL Calibration Configurator                       |     |

| Figure 51 | FCCC Calibration SmartDesign                                               | 81  |

# **Tables**

| Table 1  | Maximum Clocking Resources for RTG4 Family Devices                      |    |

|----------|-------------------------------------------------------------------------|----|

| Table 2  | Maximum Global Resources for RTG4 Devices                               |    |

| Table 3  | Global Buffers Assignment to Fabric CCC Global Outputs                  | 12 |

| Table 4  | Global Buffers Assignment to SerDes Blocks                              | 13 |

| Table 5  | Global Macros                                                           | 14 |

| Table 6  | Effective Device Flip-Flop Toggle Rate                                  | 20 |

| Table 7  | Estimation of Worst-Case Clock Jitter for a - 1 Speed Grade RTG4 Design | 21 |

| Table 8  | Fabric CCC Port Description                                             | 31 |

| Table 9  | Dedicated Global I/Os Connections to the Fabric CCC/PLLs                | 35 |

| Table 10 | Control Signals for PLL Output and Power State                          | 40 |

| Table 11 | Fabric CCC Register Map                                                 |    |

| Table 12 | FCCC RFMUX CR                                                           |    |

| Table 13 | FCCC RFDIV CR                                                           | 51 |

| Table 14 | FCCC FBMUX CR                                                           | 51 |

| Table 15 | FCCC_FBDIV_CR                                                           | 51 |

| Table 16 | FCCC_CGLMUX0_CR                                                         |    |

| Table 17 | FCCC_CGLMUX1_CR                                                         |    |

| Table 18 | FCCC CGLMUX2 CR                                                         |    |

| Table 19 | FCCC_CGLMUX3_CR                                                         | 52 |

| Table 20 | FCCC_GPMUX0_CR                                                          |    |

| Table 21 | FCCC_GPMUX1_CR                                                          |    |

| Table 22 | FCCC_GPMUX2_CR                                                          | 53 |

| Table 23 | FCCC_GPMUX3_CR                                                          | 53 |

| Table 24 | FCCC_GPD0_CR                                                            |    |

| Table 25 | FCCC_GPD1_CR                                                            |    |

| Table 26 | FCCC_GPD2_CR                                                            | 54 |

| Table 27 | FCCC_GPD3_CR                                                            |    |

| Table 28 | FCCC_PLL_CR0                                                            | 54 |

| Table 29 | FCCC_PLL_CR1                                                            | 54 |

| Table 30 | FCCC_PLL_CR2                                                            | 55 |

| Table 31 | FCCC_PLL_CR3                                                            | 55 |

| Table 32 | FCCC_GPDS_SYNC_CR                                                       | 55 |

| Table 33 | FCCC_PLL_CR4                                                            | 55 |

| Table 34 | FCCC_PLL_CR5                                                            |    |

| Table 35 | FCCC_GPD0_SYNC_CR                                                       | 56 |

| Table 36 | FCCC_PLL_CR6                                                            | 56 |

| Table 37 | FCCC_PLL_CR7                                                            | 56 |

| Table 38 | FCCC_GPD1_SYNC_CR                                                       | 57 |

| Table 39 | FCCC_GPD2_SYNC_CR                                                       | 57 |

| Table 40 | FCCC_GPD3_SYNC_CR                                                       | 58 |

| Table 41 | FCCC_PDLY_CR                                                            | 58 |

| Table 42 | FCCC_RX_RECOVERY_CR                                                     | 58 |

| Table 43 | Fabric CCCs Multiplexers Selection Control                              |    |

## 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the current publication.

### 1.1 Revision 11.0

The following is a summary of the changes in revision 11.0 of this document.

- Information about Using RTG4 FCCC with Enhanced PLL Calibration, page 66 was updated.

- Information about Enhanced PLL Calibration Fabric IP, page 69 was updated.

- Information about Performing Dynamic CCC Configuration with RTG4FCCCECALIB, page 74 was added

- Information about PLL\_ARST\_N port was updated. See Table 8, page 31, Table 10, page 40, and PLL Options, page 62.

- Updated RCLKINT symbol. See Table 5, page 14.

### 1.2 Revision 10.0

The following is a summary of the changes in revision 10.0 of this document.

- Information about Global Net Clock Jitter, page 19 was updated.

- Information about SmartPower Usage Tips, page 24 was added.

- Information about driving CLK\_50MHz pin was updated. See Use Model 4: PLL in Triple Module Redundant (TMR) Mode, page 80.

- Information about programmable delay value was corrected. See RDLY and FBDLY, page 38.

### 1.3 **Revision 9.0**

Information about Global Net Clock Jitter, page 19 was added.

#### 1.4 Revision 8.0

The following is a summary of the changes in revision 8.0 of this document.

- Added section Using RTG4 FCCC with Enhanced PLL Calibration, page 66.

- Added section Selecting CCC Location and CCC Instance(s) being Configured, page 66.

- Added section Enhanced PLL Calibration Fabric IP, page 69.

- Added section Selecting CCC GLx Outputs to Ensure Placement Success, page 73

- Updated section How to Use SpaceWire Mode and Glitch Filter Mode using RX Clock Recovery Block, page 47

- Updated Table 28, page 54

- Updated section PLL Options, page 62

### 1.5 **Revision 7.0**

The following is a summary of the changes in revision 7.0 of this document.

- Information about PLL external feedback was updated. See PLL Core, page 37.

- Information about Lock Generation Circuit, page 39 was updated.

- Information about lock controls was updated. See PLL Options, page 62.

- Information about LOCKWIN signal was updated. See Table 28, page 54.

### 1.6 **Revision 6.0**

The following is a summary of the changes in revision 6.0 of this document.

- Information about GPD, page 41 was updated.

- Information about READY VDDPLL signal was added. See PLL Options, page 62.

- Information about Triple Module Redundant (TMR) mode was added. See Use Model 4: PLL in Triple Module Redundant (TMR) Mode, page 80.

- Information about programmable delay step was updated. See RDLY and FBDLY, page 38.

- Information about GPD Operating Modes, page 43 was updated.

- Information about Clock Gating Logic (CGL), page 44 was updated.

- Information about de-glitching filter was added. See How to Use SpaceWire Mode and Glitch Filter Mode using RX Clock Recovery Block, page 47.

### 1.7 **Revision 5.0**

The following is a summary of the changes in revision 5.0 of this document.

- Information about internal and external feedback of PLL was updated. See PLL Core, page 37.

- Information about clock gating logic was updated. See Clock Gating Logic (CGL), page 44.

- Information about global network architecture for RTG4 150 devices was updated. See Figure 3, page 8.

### 1.8 Revision 4.0

Information about global buffers assignment to SerDes block was added, see Table 4, page 13.

### 1.9 **Revision 3.0**

The following is a summary of the changes in revision 3.0 of this document.

- Removed reference to RT4G075 device.

- Updated RX Clock Recovery (SpaceWire), page 46.

- Updated Note in Global Macros, page 13.

- Updated Figure 18, page 40 and Figure 24, page 45.

- Updated Table 43, page 59.

- Information about Design automation was added, see Managing Global Signals, page 14.

- Information about CQ352 package device was added, see CCC/PLL Restrictions for the CQ352 Package Devices, page 36.

- Information about PLL external feedback was updated, see PLL Core, page 37.

- · Updated Lock Generation Circuit, page 39.

- Information about clock gating logic was updated, see Clock Gating Logic (CGL), page 44.

- Information about switching registers was added, see Guidelines for using CCC with Simultaneous Switching Registers, page 48.

- Information about how to use SpaceWire mode and glitch filter mode was added, see How to Use SpaceWire Mode and Glitch Filter Mode using RX Clock Recovery Block, page 47.

- Updated Fabric CCC Dynamic Configuration, page 49.

- Updated MUX selection input 8, 9, 10, and 11 in Table 43, page 59.

- Information about PLL/CCC configuration registers was added, see PLL/CCC Configuration Register Report, page 64.

### 1.10 **Revision 2.0**

The following is a summary of the changes in revision 2.0 of this document.

- Added How to Use On-Chip Oscillator, page 27.

- Added How to Use SpaceWire Mode and Glitch Filter Mode using RX Clock Recovery Block, page 47 and How to Use Fabric CCC(s), page 60.

- Updated Figure 14, page 29 and Figure 15, page 30.

- Updated the document with FTC inputs (SAR 63141).

### 1.11 Revision 1.0

Revision 1.0 was the first publication of this document.

# 2 Clocking Resources Overview

### 2.1 Introduction

This chapter provides an overview of the RTG4 FPGA clocking resources and device clocking scheme. The following table lists the maximum number of clocking resources available on each RTG4 family device.

Table 1 • Maximum Clocking Resources for RTG4 Family Devices

|                                          | RTG4 Device Part Number |

|------------------------------------------|-------------------------|

| Resource                                 | RT4G150                 |

| 50 MHz RC oscillator <sup>1</sup>        | 1                       |

| Fabric CCCs <sup>2</sup>                 | 8                       |

| Global buffers                           | 24                      |

| Dedicated global I/Os                    | 36                      |

| SerDes global clock outputs <sup>3</sup> | 12                      |

- 1. Radiation-hardened RC Oscillator.

- Each CCC has a dedicated radiation-hardened triple redundant PLL for clock synchronization and clock synthesis.

- 3. SerDes global output clocks are not SET mitigated.

The on-chip RC oscillator is a high-precision hardened 50 MHz embedded RC Oscillator that can be used in conjunction with the on-chip CCCs to generate clocks of varying frequencies and phases. Refer to the On-Chip Oscillator, page 26 for more information.

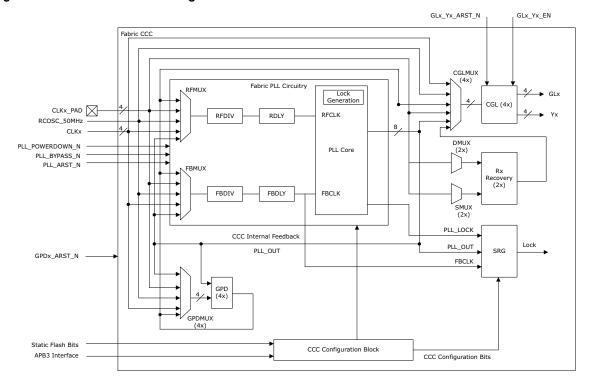

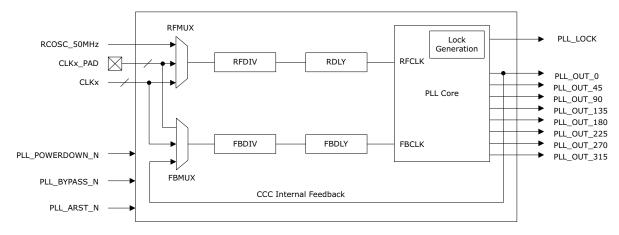

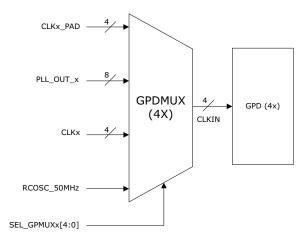

The RTG4 fabric CCC is radiation hardened and can generate four different clock outputs with a maximum frequency of 400 MHz. Each fabric CCC has a radiation hardened dedicated triple redundant PLL for flexible clocking in the FPGA fabric. In addition, each CCC includes clock gating logic and general purpose clock dividers that are all radiation hardened. Fabric CCCs can also provide a base reference clock to the on-chip hard IP blocks: FDDR and high-speed serial interfaces. Refer to the Fabric Clock Conditioning Circuitry, page 28 for more information.

The RTG4 FPGA fabric offers a low-skew radiation hardened global network that provides effective clock distribution throughout the FPGA fabric and has extensive support for multiple clock domains. The global network is composed of global buffers (GB) to distribute low-skew clock signals or high-fanout nets to all fabric resources. RTG4 devices have a total of 24 GBs where each GB produces 24 global clock signals to the left and 24 global clock signals to the right for a total of 48 half-chip global networks, refer to the preceding table.

Dedicated global I/Os drive the GBs directly and are the primary source for connecting external clock inputs to the internal global clock network. There are 36 dedicated global I/Os. Refer to the FPGA Fabric Global Network Architecture, page 6 for more information about the global network and dedicated global I/Os.

The Libero SoC design software provides clock management macros for static configuration of the CCCs.

### 2.2 Clocking Scheme Overview

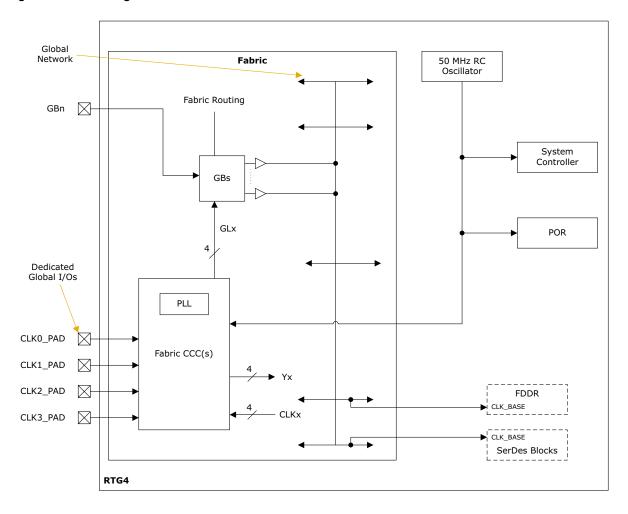

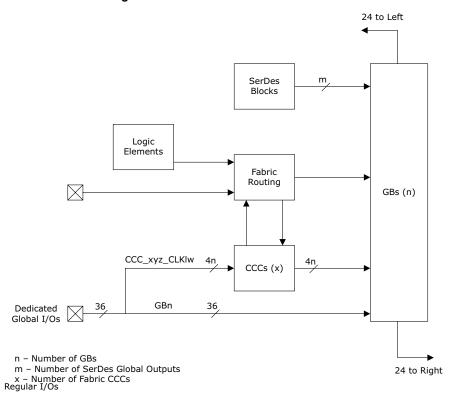

The following figure shows the top-level RTG4 device clocking scheme. It shows the inputs and outputs for one fabric CCC; each fabric CCC has a similar set of inputs and outputs.

Figure 1 • Clocking Scheme Overview

The GBs in the FPGA fabric distribute global signals to the entire FPGA fabric with low-skew. As shown in the preceding figure, GBs can be driven from multiple sources:

- Dedicated global I/Os

- Fabric CCCs

- FPGA fabric routing

All 36 dedicated global I/Os have direct access to the GBs. Out of the 36 dedicated global I/Os, 32 can reach the fabric CCC. It is also possible to access the GBs from a regular I/O or an FPGA fabric internal signal through the FPGA fabric routing. The four global clock outputs (GLx, x = 0 to 3) of each fabric CCC have radiation-hardened hardwired connection to the GBs. In addition to global clock outputs (GLx), the equivalent four core clocks (Yx, x = 0 to 3) can drive the fabric routing resources in the FPGA fabric.

The on-chip oscillator—50 MHz RC oscillator—has hardwired connections to the System Controller, power-on-reset (POR), and all the fabric CCCs.

Each fabric CCC can have an independent reference clock from one of the following clock sources:

- Four dedicated global I/Os (CLKw\_PAD, w = 0 to 3)

- FPGA fabric inputs (CLKx, x = 0 to 3)

- · On-chip oscillator

Each fabric CCC has its own dedicated global I/Os. For instance, a dedicated global I/O belongs to the northeast side CCCs is referred to as CCC\_NEz\_CLKIw, where z represents CCC number and w represents one of the four associated dedicated global I/Os (CLKw\_PAD). The dedicated global I/Os have a hardwired connection to the fabric CCCs whereas the FPGA fabric inputs are routed through FPGA fabric routing nets. It must be noted that there is a delay due to the fabric routing that a net goes through before reaching the reference input of a CCC. Refer to the Dedicated Global I/Os, page 8 for more information.

The base clocks (CLK\_BASE) to the on-chip hard IP blocks (FDDR and SerDes blocks) must come through the FPGA fabric. For the FDDR, the CLK\_BASE is the base clock to the FDDR clock controller. The clock controller generates aligned clocks to all the FDDR sub-blocks for proper operation and synchronous communication with user logic in the FPGA fabric.

For the SerDes block, the CLK\_BASE is used for the AXI3 Master and Slave interfaces. It is also used as the reference clock to the SPLL, which is used to achieve interface timing across the fabric to SERDESIF. Each base clock can be generated from any one of the fabric CCCs or a clock source (internal or external) through the global network. The FDDR and SerDes blocks subsystems also have their own clock controllers with a dedicated radiation-hardened PLL for generating the required clocks. Refer to the UG0573: RTG4 FPGA High Speed DDR Interfaces User Guide and UG0567: RTG4 FPGA High Speed Serial Interfaces User Guide for more information about FDDR and SERDESIF clocking.

### 3 FPGA Fabric Global Network Architecture

### 3.1 Introduction

The RTG4 FPGA fabric offers a low-skew fully SET hardened global network for effective distribution of high-fanout nets including clock signals. The global network has an extensive support for multiple clock domains. This chapter describes the global network architecture and global resources. For information about how to implement asynchronous resets in RTG4 devices, see *UG0741: RTG4 FPGA I/O User Guide*

### 3.2 Global Network Architecture

The RTG4 global network is a tightly coupled, hardwired, radiation hardened, and dedicated routing network between the following global resources:

- Dedicated Global I/Os

- Fabric CCC

- Global Buffer (GB)

- · Row Global Buffers (RGB)

The following table lists the maximum global resources available in the RTG4 devices.

Table 2 • Maximum Global Resources for RTG4 Devices

| Resource                                 | RT4G150 Device |

|------------------------------------------|----------------|

| Fabric CCCs <sup>1</sup>                 | 8              |

| Global buffers (GB)                      | 24             |

| Dedicated global I/Os                    | 36             |

| SerDes global clock outputs <sup>2</sup> | 12             |

Each CCC has a dedicated radiation-hardened triple redundant PLL for clock synchronization and clock synthesis.

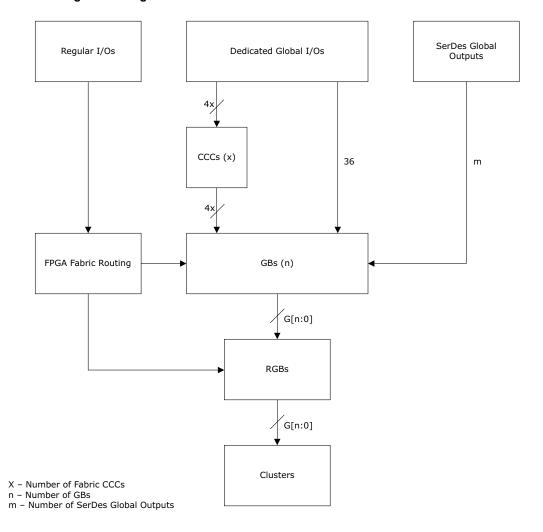

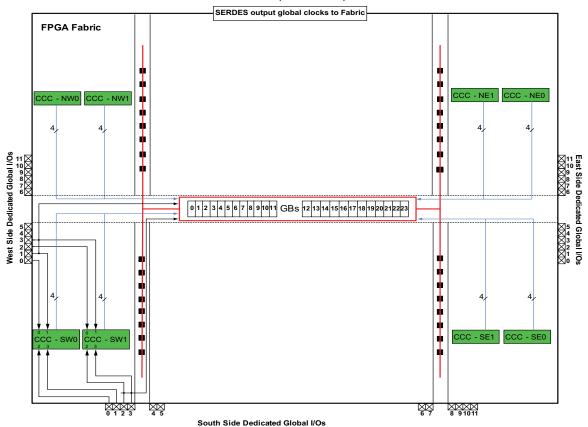

The RTG4 devices use two vertical stripes and 24 GBs (2VS24), eight fabric CCCs (two in each corner of I/O ring), and 36 dedicated external global I/Os global network architecture. The 24 GBs can drive 24 global clocks to the left and 24 global clocks to the right producing a total of 48 half-chip globals or a left and right pair can be used to send a global low-skew clock signal to the entire device.

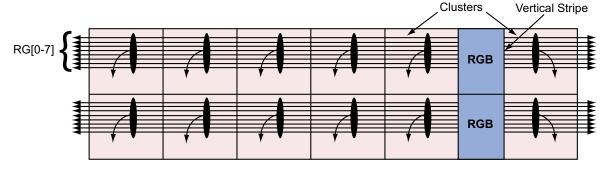

Figure 2, page 7 shows the global signal routing hierarchy to logic clusters. Refer to the *UG0574: RTG4 FPGA Fabric User Guide* for more information on the fabric logic cluster. Global signals reach the logic clusters through row global signals (RGs) generated by an associated row global buffer (RGB). RGBs are located on the vertical stripes and can drive any input of the 4-input LUT and/or any input of the STMR-D flip-flop except the ADn and SD inputs which must be connected to a power net (GND or VCC). RGBs can be accessed from GBs and FPGA fabric routing. GBs can be accessed from dedicated global I/Os, CCC global outputs, SerDes global output, and the FPGA fabric routing. GBs can also be accessed through FPGA fabric routing and from clocks coming from regular I/Os.

<sup>2.</sup> SerDes global output clocks are not SET mitigated.

Figure 2 • Global Signal Routing

The following figure shows the global network architecture for RTG4 family devices.

Figure 3 • Global Network Architecture for RT4G150 Devices

### 3.2.1 SerDes Output Clocks

In the RTG4150 device, there are a total of 11 different clocks generated out of each SerDes block when the block is configured in EPCS mode. These clock outputs are available to the fabric for data exchange between the fabric and the SerDes block. The output clocks use the regular routing through the fabric. In this case, these clocks are not SET mitigated. You have an option to select, using the SerDes block configurator in the software, two out of the 11 different clocks to be routed onto a hardwired global clock network that drives into the GB. Those two globally routed clocks will be SET mitigated and will use the dedicated global clock network. For more information on SerDes output clocks and SerDes radiation hardening, refer to the SerDes Block Network in EPCS section in the *UG0567: RTG4 FPGA High Speed Serial Interfaces User Guide*.

Note: However, the source of these two clocks from the SerDes will not be radiation hardened.

0 1 2 3 4 5

#### 3.2.2 Dedicated Global I/Os

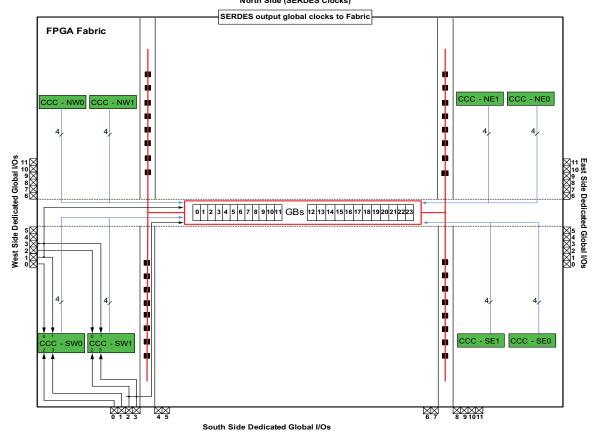

The RTG4 user I/Os are grouped into multi-standard I/Os (MSIO and MSIOD) and DDRIOs. Some of these user I/Os, referred to as dedicated global I/Os, are dual-use I/Os that are capable of driving the global routing network or local routing network. Dedicated global I/Os can be used to bring in external clock signals as inputs to the FPGA fabric. Dedicated global I/Os can be used as regular I/Os, as either input or output for any design signal, if they are not utilized for clocking. Dedicated global I/Os are located on each of the three sides (south, east, and west) of the FPGA fabric.

All 36 dedicated global I/Os have direct access to GBs. Out of 36 dedicated global I/Os, there are 32 that can reach the fabric CCC. Each fabric CCC has four dedicated global I/Os as inputs and can drive up to four GBs. Each of the four CCC outputs can drive up to 3 GBs. As such, each CCC can drive up to 12 different GBs. The dedicated global I/Os connect to fabric CCCs and GBs through a hardwired connection. When MSIO or MSIOD input buffers are used to drive the GBs or CCC blocks, the input buffers and associated clock wiring is radiation hardened if the dedicated clock routes are used.

Dedicated global I/Os are routed to GBs by the Libero SoC routing software as follows:

- If a dedicated global I/O, which has direct access to GBs is selected, the routing software directly

routes the dedicated global I/O input to an associated GB. There are no routing delays associated

with this dedicated connection. If a regular I/O is used instead, then there will be routing delays

associated with that connection.

- If a dedicated global I/O, which has direct access to a fabric CCC (CCC macro instantiated in the design with input source selected as dedicated global I/O) is selected, the routing software selects an associated fabric CCC. In this case, the outputs of the fabric CCC reach the associated GBs.

The 2VS24 global network architecture has 36 dedicated global I/Os, which can access GBs directly or through CCCs. The following figure shows the dedicated global I/Os assignment in the lower left corner of the FPGA fabric in RT4G150 devices. The remaining dedicated global I/Os are assigned to CCCs and/or GBs as shown in Table 3, page 12.

Figure 4 • Dedicated Global I/Os (SouthWest corner) Assignment in and RT4G150 Devices

North Side (SERDES Clocks)

### 3.2.2.1 Naming Conventions for Dedicated Global I/Os

Due to the comprehensive and flexible nature of dedicated global I/Os, a naming scheme is used to provide the detailed information on each I/O.

The dedicated global I/O uses the generic name IOxyBz/GBn/CCC\_xyz\_CLKIw or IOxyBz/GBn\_n/CCC\_xyz\_CLKIw, where:

- IO: Type of I/O—MSIO, MSIOD, or DDRIO

- x: I/O pair number

- y: Differential I/O polarity—P (positive) or N (negative)

- · Bz: Bank number

- GBn: Dedicated global I/Os that drive the GBs directly, where n is 0 to 23

- GBn\_n: Dedicated global I/O that drives different Gs instead of one direct GB. For example,

GB0 11 means that this particular global I/O can drive any one of the GBs 0 to 11.

- CCC xyz CLKlw represents the dedicated global I/Os that drive GBs through CCCs, where:

- xy: Location—NE, SW, SE, or NW

- z: CCC number—0 or 1

- I: Clock input

- w: One of the four dedicated global I/Os associated with each CCC—CLKI0, CLKI1, CLKI2, or CLKI3

Some of the dedicated global I/Os are multiplexed with hard IP blocks such as FDDR. These multiplexed or multi-function dedicated global I/Os act as regular I/Os and cannot be used for accessing the global network or CCCs when the associated hard IP block is enabled in the design. Refer to the DS0130: RTG4 Pin Descriptions for more information on the functions supported by the dedicated global I/Os. The name of a pin shows the functionalities for which that pin can be configured and used.

Example pin name: DDRIO94PB0/FDDR\_E\_ADDR15/GB12\_23/CCC\_NE0\_CLKI3

The above example pin is a multi-purpose I/O, which is configured as an FDDR I/O (FDDR\_E\_ADDR15) when the FDDR is enabled. If FDDR is not used in the design, this I/O can be configured as dedicated global I/O which can drive the CCC\_NE0\_CLKI3 input port of CCC\_NE0 or directly drive one of the GB 12 to 23 (GB12\_23).

Table 3, page 12 shows the corresponding GB number of each CCC global (GL#) drivers.

### 3.2.2.2 Dedicated Global I/O Voltage Standards

Dedicated global I/Os are located in different I/O banks with each bank having its own supply and ground pins. The voltage standards supported by dedicated global I/Os are based on the I/O bank it is located in. The voltage standard for a dedicated global I/O can be set using I/O Editor available in the Libero SoC software. Refer to the "Supported Voltage Standards" table in the *UG0574: RTG4 FPGA Fabric User Guide* for I/O standards supported by each I/O bank. Dedicated global I/Os can be configured in Single-ended mode or Differential mode. Differential mode is implemented with a fixed I/O pair and cannot be split with adjacent I/Os. According to the naming convention, differential I/O pairs are denoted with an I/O pair number and their polarity (P and N). In Single-ended mode, the I/O pair operates as two independent I/Os. All the configuration and data inputs/outputs are separate and use names ending with P and N to differentiate between the I/Os.

### 3.2.2.3 Unused Dedicated Global I/O Configuration

Unused dedicated global I/Os behave similarly to unused regular User I/Os. When regular User I/Os (MSIO, MSIOD, DDRIO) are not used, the Libero SoC software configures the I/O as input buffer disabled, output buffer tristated with weak pull-up. For the I/Os unused conduction and recommendations, refer to the RTG4 CG1657 Package Pin Assignment Table.

#### 3.2.3 Fabric CCC

Fabric CCCs enable flexible clocking schemes to the logic implemented in the FPGA fabric, and can also provide the base clock for on-chip hard IP blocks—FDDR and SerDes blocks. Each fabric CCC operates with a dedicated radiation-hardened triple redundant PLL and generates clock signals of varying frequency and phase. Each fabric CCC generates up to four different global clocks (GL0, GL1, GL2, and GL3) and four core clocks (Y0, Y1, Y2, and Y3).

The generated global clocks drive GBs and core clocks drive the local routing resources in the FPGA fabric. The fabric CCCs core clock outputs (Yx) can be used to drive internal logic without using global network resources. Core clocks (Yx) introduce additional delay because of FPGA fabric routing. Core clocks are useful when global network resources must be conserved and utilized for other timing-critical paths. The GBs associated with the global clock outputs (GLx) are available to user logic, if the global clock outputs are disabled. Each fabric CCC has four dedicated global I/Os as inputs. Each fabric CCC output (GLx/Yx), as well as the reference clock, can be driven from any one of these four dedicated global I/Os.

Fabric CCCs are labeled according to their location in the FPGA fabric floor plan. For instance, the fabric CCCs located in the northeast corner are labeled CCC-NE0 and CCC-NE1. Refer to the Fabric Clock Conditioning Circuitry, page 28 for more information on fabric CCCs. The entire CCC block is hardened with the exception of the clock inputs from the fabric, delay line, and feedback dividers. RFDIV and FBDIV, which are not hardened.

Note: Any SET pulses on the delay lines are filtered by the PLL.

### 3.2.4 Global Buffer (GB)

The global buffer (GB) is a multiplexer that generates an independent global signal. The global signal can drive all fabric resources with low-skew. The GBs can be driven from multiple sources such as dedicated global I/Os, fabric CCCs, SerDes blocks, and fabric routing. For example, an input signal connected to a dedicated global I/O can route directly to a GB or through a CCC. Input signals connected to regular I/Os or any internal logic module can also be connected to the GB through fabric routing. The following figure shows the sources feeding into GBs which finally feed into RGBs through G[0-23] to span the complete fabric area.

GBs can also be fed through regular I/Os, in which case the signals are first routed to fabric routing and then reach the GBs. Any signal generated from logic modules can reach GBs through fabric routing.

Figure 5 • Various Sources Feeding Global Buffers

The following table shows the assignment of fabric CCC global outputs (GLx, x = 0 to 3) to the global buffers. Each global output of the fabric CCC is associated with three global buffers. For instance, GB0 can be accessed from GL0 of any one of the four fabric CCCs present on the west side.

Table 3 • Global Buffers Assignment to Fabric CCC Global Outputs

| CCC-SW0 | CCC-SW1 | CCC-NW0 | CCC-NW1 | CCC-SE0 | CCC-SE1 | CCC-NE0 | CCC-NE1 | GB Numbe     |

|---------|---------|---------|---------|---------|---------|---------|---------|--------------|

| GL0     |         |         |         |         |         |         |         | 0, 4, 8      |

|         | GL0     |         |         |         |         |         |         | <del>_</del> |

|         |         | GL0     |         |         |         |         |         | <del>_</del> |

|         |         |         | GL0     |         |         |         |         | <del>_</del> |

| GL1     |         |         |         |         |         |         |         | 1, 5, 9      |

|         | GL1     |         |         |         |         |         |         | _            |

|         |         | GL1     |         |         |         |         |         | _            |

|         |         |         | GL1     |         |         |         |         | _            |

| SL2     |         |         |         |         |         |         |         | 2, 6, 10     |

|         | GL2     |         |         |         |         |         |         |              |

|         |         | GL2     |         |         |         |         |         | _            |

|         |         |         | GL2     |         |         |         |         | _            |

| GL3     |         |         |         |         |         |         |         | 3, 7, 11     |

|         | GL3     |         |         |         |         |         |         | <del>_</del> |

|         |         | GL3     |         |         |         |         |         | <del>_</del> |

|         |         |         | GL3     |         |         |         |         | _            |

|         |         |         |         | GL0     |         |         |         | 12, 16, 20   |

|         |         |         |         |         | GL0     |         |         | <del>_</del> |

|         |         |         |         |         |         | GL0     |         | _            |

|         |         |         |         |         |         |         | GL0     | <del>_</del> |

|         |         |         |         | GL1     |         |         |         | 13,17, 21    |

|         |         |         |         |         | GL1     |         |         | <del>_</del> |

|         |         |         |         |         |         | GL1     |         | _            |

|         |         |         |         |         |         |         | GL1     | <del>_</del> |

|         |         |         |         | GL2     |         |         |         | 14, 18, 22   |

|         |         |         |         |         | GL2     |         |         | _            |

|         |         |         |         |         |         | GL2     |         | _            |

|         |         |         |         |         |         |         | GL2     | _            |

|         |         |         |         | GL3     |         |         |         | 15, 19, 23   |

|         |         |         |         |         | GL3     |         |         | _            |

|         |         |         |         |         |         | GL3     |         | _            |

|         |         |         |         |         |         |         | GL3     | _            |

The following table lists the assignment of global buffers to the SerDes blocks.

Table 4 • Global Buffers Assignment to SerDes Blocks

| SerDes block | GB Number |

|--------------|-----------|

| SERDES_0     | 0, 2      |

| SERDES_1     | 4, 6      |

| SERDES_2     | 8, 10     |

| SERDES_3     | 12, 14    |

| SERDES_4     | 16, 18    |

| SERDES_5     | 20, 22    |

### 3.2.5 Row Global Buffers (RGB)

RGBs are situated on the vertical stripes of the global network architecture inside the FPGA fabric. Each RGB drives logic clusters, consisting of 12 logic modules, located on left and right branches using RGs, refer the following figure. The global signals from the GBs are routed to RGBs, which are then fed into the clusters through RGs. Each GB has access to all RGBs available on the vertical stripes as the global network is segmented. Each RGB is independent and can be driven by fabric routing in addition to being driven by GBs. This facilitates the use of RGBs to drive regional clocks spanning a small fabric area. RGBs drive 1/2 the width of the device - either to the centered left or centered right.

Figure 6 • Row Global Signals Driving Clusters

### 3.3 Design Recommendations

In general, Microchip recommends that all clocks in a design must be routed using the global routing resources in the device. This ensures that clock skew is minimized throughout the design. Furthermore, global resource usage ensures that predictable levels of clock jitter can be accounted for during static timing analysis. This guideline should be applied when selecting clock input pin assignments, when selecting CCC reference clock assignments, and when generating clocks inside the FPGA. The following sections provide recommendations for using the global network in a design.

#### 3.3.1 Global Macros

Global macros can be used for assigning signals to the global network. The following table shows the global macros available for the RTG4 devices. The CLKBUF macro allows you to route the clock coming from the dedicated global I/Os to GBs. Dedicated global I/Os, which have direct access to GBs are available as input pads to these macros. The CLKINT macro route the internal clock signals to GBs through FPGA fabric routing. The RCLKINT macro route the internal clock signals to RGBs through FPGA fabric routing.

**Note:** Clock nets that are generated and routed in the fabric up to the RCLKINT (RGB) entry point are not radiation hardened. Once the generated nets get to the RGB entry point, from that point forward they are fully hardened. It is fully hardened, if the entry point to the RGB is coming from the GB.

Table 5 • Global Macros

| Macro Name      | Description                                                                                                                                                             | Functional Symbol |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| CLKBUF          | To drive a clock signal coming from input pad to a global buffer.                                                                                                       | PAD Y             |

| CLKINT          | To drive a global buffer from FPGA fabric routing.                                                                                                                      | A Y               |

| CLKINT_PRESERVE | Similar to CLKINT, but the signals routed through the CLKINT_PRESERVE macro will never be demoted or optimized by the Libero Compile tool.                              | A Y               |

| RCLKINT         | To drive a row global net from FPGA fabric.                                                                                                                             | A Y               |

| CLKBUF_DIFF     | To drive a clock signal coming from differential input pad to a global buffer. Use <b>Libero SoC I/O Constraint Editor</b> to select the desired differential standard. | PADP Y            |

In addition to these global macros, the CCC macros global outputs (GLx) also drive the GBs. Dedicated global I/Os and their I/O standard can be assigned using **I/O Constraint Editor** in the Libero SoC software. The Libero place-and-route software runs the pre-layout checker and checks the validity of dedicated global I/O assignment.

A regular I/O can be routed to the global network through the FPGA fabric. To allow regular I/O to access the global network, the CLKINT macro can be instantiated or PDC constraints can be used to promote signals from regular I/O or internal signal to the global network.

### 3.3.2 Managing Global Signals

Assigning high fan-out nets to the global clock network is an effective way of reducing routing congestion and minimizing skew. Due to its high propagation delays, the global clock network is not recommended for use in timing-critical data paths.

The clock macros can be used for assigning signals to the global clock network:

- The CLKBUF and CLKBUF\_DIFF macro connects a Dedicated global I/O to GB. Dedicated global I/Os have direct hardwired routing to GBs.

- The CLKINT macro connects fabric routed signal to GB. The CLKINT macro must be used to connect a regular I/O to GB through the FPGA fabric.

- The RCLKINT macro connects a fabric routed signal to RGB.

The CCCs and transceivers drive GBs through hardwired routing.

The Libero SoC software supports automated global buffer allocation to minimize the user intervention. The allocation strategy for global buffers employs the following priority:

- User-inserted global clock macros

- Clock nets

- Asynchronous reset/set nets

- Very high fan-out nets

In Libero tool, the default fan-out threshold for global net promotion is larger for data pins (pins involved in register-to-register paths) than asynchronous logic pins (pins involved in register-to-asynchronous paths).

Due to this, the automated design flow is more likely to employ global nets on register-to-asynchronous paths than register-to-register paths. The reasoning for this is that asynchronous pins are not normally timing-critical, and routing them on global nets reduce routing congestion. However, register-to-asynchronous paths are functionally equivalent to register-to-register paths from the perspective of achieving timing closure. As a result, when designing register-to-asynchronous paths, ensure that timing critical connections do not unnecessarily employ global nets.

If a design contains a failing register-to-asynchronous timing path, check if the path drives a global net in SmartTime. This is done by examining the path and looking for a GB between its launching and latching registers. If a GB is present, you may be able to improve the likelihood of timing closure by demoting the net to a fabric-routed net. An asynchronous net can be demoted by increasing the fan-out threshold of asynchronous pins above the fan-out of the asynchronous net. Alternatively, you can manually adjust the RTL by moving timing-critical pins from high-fanout asynchronous nets to lower fan-out nets.

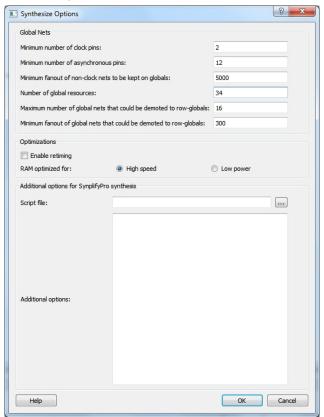

Users have the option of setting the minimum fan-out for automatic global assignment. The fan-out threshold values are set in the Libero tool to automate clock pin promotion to global nets. In the Libero Design Flow window, expand Implement Design, right-click Synthesize, and choose Configure Options. This opens the Synthesize Options dialog box, as shown in the following figure.

Figure 7 • Synthesize Options Dialog Box

The following options specify the threshold value for nets promotion or demotion:

- Minimum number of clock pins Specifies the fan-out threshold value for clock pin promotion.

The default value is 2.

- Minimum number of asynchronous pins Specifies the fan-out threshold value for Asynchronous pin promotion. The default value is 12. This feature is not available in the RT4G150 ES device.

- Minimum fan-out of non-clock nets to be kept on globals Specifies the fan-out threshold value for data pin promotion to global resources. It is the minimum fan-out of non-clock (data) nets to be kept on global nets (no demotion). The default value is 5,000 (must be between 1,000 and 200,000). If you run out of global resources for your design, increase this number. If a CLKINT net with fan-out less than this threshold value has data pins along with some clock or asynchronous reset/set pin, move all the data pins to the CLKINT driver net.

- Number of global resources Specifies the number of global resources to be used in the design. The default value is 34 and you could increase its value up to 48.

- Maximum number of global nets that could be demoted to row-globals Specifies the

maximum number of global nets that could be demoted to RGB resources. The default value is 16.

**Minimum fan-out of global nets that could be demoted to row-globals** – Specifies the minimum fan-out of global nets that could be demoted to RGB resources. The default value is 300.

It is undesirable to have high fan-out clock nets demoted using RGB resources because it may result in high skew. If you run out of global resources for your design, reduce this number to allow more globals to be demoted to RGB resources.

**Note:** Hardwired connections to global resources, such as connections from CCCs and Dedicated Global I/Os cannot be controlled by synthesize options.

After synthesis, the compiler tool performs the following steps to assign nets to global buffers:

- 1. Sorting all CLKINT nets in the following priority order.

- Fan-out, only if fan-out ≥ threshold value specified by minimum fanout of non-clock nets to be kept on globals

- Number of clock pins

- Number of asynchronous reset/set pins

- Number of data pins

- 2. Determining the number of GB resources available for CLKINT nets after allocating them to any of the CLKBUF, CLKBUF\_DIFF, and CLKINT\_PRESERVE.

- Demoting CLKINT nets from the sorted list that are beyond the limit specified by the number of global resources.

- If such a net has at least the number of pins specified by minimum fanout of global nets that

could be demoted to row-globals, replace the CLKINT with an RCLKINT macro. Limit the

number of nets demoted to RCLKINT to the count specified by maximum number of global nets

that could be demoted to row-globals.

- Otherwise, merge the net with the driver of the CLKINT.

The HDL source file or SmartDesign schematic is the preferred place for defining which signals must be assigned to a global network using global macro instantiation. A signal with high-fanout may have logic replication, if it is not promoted to a global during synthesis.

### 3.3.3 Place and Route

Place and Route step aligns placement of I/Os, CCC, and GB resources while preserving any user locked placement, finding feasible I/O bank technology solution and optimizing the number of hardwired connections to reduce clock insertion delays. An I/O may be hardwired to a GB as well as route directly to data pins in the fabric.

The CLKINT nets are mapped to GB resources and the placement algorithm resolves the GB bandwidth per vertical half. The RCLKINT nets are mapped to RGB resources with routed inputs and the placement algorithm resolves the RGB bandwidth along with RGRESET bandwidth per row.

The power-driven option optimizes the number of rows occupied by a global net or a local clock net, resulting drop in performance (on average).

After performing the place and route, a report of global nets is generated. User can open the report tab to view the global net report. The user should review the generated global net report to understand and minimize clocks that are routed on the FPGA fabric routing instead of global routing resources. The following figures show an example of global net report.

Figure 8 • Example of Global Net Report 1

#### Global Nets Information

|   | From    | GB Location | Net Name                             | Fanout |

|---|---------|-------------|--------------------------------------|--------|

| 1 | GBR[1]  | (709, 153)  | CLK_18_ibuf_RNI7605/U0_YWn           | 2266   |

| 2 | GBR[12] | (720, 153)  | CLK_12_ibuf_RNI1837/U0_Ywn           | 623    |

| 3 | GBL[19] | (727, 154)  | CLK_12_ibuf_RNIVQ04/U0_Y             | 558    |

| 4 | GBL[7]  | (715, 154)  | MTD_0/CCC_0/CCC_INST/INST_CCC_IP:GL0 | 512    |

| 5 | GBL[0]  | (708, 154)  | FCCC_2/CCC_INST/INST_CCC_IP:GL0      | 256    |

| 6 | GBL[3]  | (711, 154)  | FCCC_2/CCC_INST/INST_CCC_IP:GL1      | 128    |

| 7 | GBL[11] | (719, 154)  | I7/I0/I4/vcxclk_1_5m                 | 64     |

| 8 | GBL[2]  | (710, 154)  | I7/I0/I4/clk 3 088m 0                | 32     |

#### I/O to GB Connections

|   | Port Name | Pin # | I/O Function    | From                     | From  | Loc | cation   |      | To       |

|---|-----------|-------|-----------------|--------------------------|-------|-----|----------|------|----------|

| 1 | CLK_18    | K5    | MSIOD119PB7/GB1 | CLK_18_ibuf/U0/U_IOIN:Y  | West  | IO  | #2(0,    | 58)  | GBR [1]  |

| 2 | CLK_12    | A17   | DDRIO76PB0/GB12 | CLK_12_ibuf/U0/U_IOPAD:Y | North | IO  | #6(564,  | 205) | GBR [12] |

| 3 | CLK       | F27   | MSIO335PB4/GB19 | CLK ibuf/U0/U IOPAD:Y    | South | IO  | #9(1134, | 1)   | GBL[19]  |

#### Fabric to GB Connections

|   | From                   | From  | Location | TO       | Net name              | Net type | Fanout |

|---|------------------------|-------|----------|----------|-----------------------|----------|--------|

| 1 | I7/I0/I4/vcxclk_1_5m:Q | (361, | 61)      | GBR [11] | I7/I0/I4/vcxclk_1_5m  | ROUTED   | 2      |

| 2 | I7/I0/I4/clk 3 088m:Q  | (368, | 61)      | GBR [7]  | I7/I0/I4/clk 3 088m 0 | ROUTED   | 3      |

#### Figure 9 • Example of Global Net Report 2

#### CCC to GB Connections

|   | From                                 | From<br>Location     | То     | Net Name            | Net Type  | Fanout |

|---|--------------------------------------|----------------------|--------|---------------------|-----------|--------|

| 1 | MTD_0/CCC_0/CCC_INST/INST_CCC_IP:GL0 | CCC-NW0<br>(0, 254)  | GBL[7] | MTD_0/CCC_0/GL0_net | HARDWIRED | 1      |

| 2 | FCCC_2/CCC_INST/INST_CCC_IP:GL0      | CCC-NW1<br>(18, 254) | GBL[0] | FCCC_2/GL0_net      | HARDWIRED | 1      |

| 3 | FCCC_2/CCC_INST/INST_CCC_IP:GL1      | CCC-NW1<br>(18, 254) | GBL[3] | FCCC_2/GL1_net      | HARDWIRED | 1      |

#### CCC Input Connections

| From                                                          | From<br>Location | То                                       | CCC<br>Location        | Net Name                           | Net Type | Eanout |

|---------------------------------------------------------------|------------------|------------------------------------------|------------------------|------------------------------------|----------|--------|

| SERDES_IF2_0/SERDESIF_INST/INST_S<br>ERDESIF_IP:EPCS_RXCLK[1] | (12, 2)          | FCCC_2/CCC_INS<br>T/INST_CCC_IP:CL<br>K0 | CCC-NW1<br>(18, 254)   | SERDES_IF2_<br>0_EPCS_3_RX<br>_CLK | ROUTED   | 1      |

| SERDES_IF2_0/SERDESIF_INST/INST_S<br>ERDESIF_IP:EPCS_RXCLK_1  | (12, 2)          | FCCC_0/CCC_INS<br>T/INST_CCC_IP:CL<br>K0 | CCC-NE1<br>(1014, 254) | SERDES_IF2_<br>0_EPCS_1_RX<br>_CLK | ROUTED   | 1      |

#### Local Clock Nets to RGB Connections

| Port<br>Name | Pin<br>Number | I/O Function | From                                                   | From Location | Net Name                                                     | Eanout | RGB<br>Location | Local<br>Eanout |

|--------------|---------------|--------------|--------------------------------------------------------|---------------|--------------------------------------------------------------|--------|-----------------|-----------------|

| l -          | -             | -            | SYSCLK/PROC_IF/reset_ctl_1/reset_bits_RNIP<br>LVN[0]:Y | (229, 36)     | SYSCLK/PR<br>OC_IF/reset_<br>ctl_1/reset_bit<br>s_RNIPLVN[0] |        | (219, 3)        | 2               |

### 3.3.4 Global Net Clock Jitter

The RTG4 global network is hardened against Single Event Transients (SETs). The global network employs glitch filtering and physical triplication to mitigate radiation induced clock glitches. The glitch filtering slows the internal clock edge rates to boost SET immunity. However, a consequence of this radiation mitigation is reduced noise tolerance of the global network.

Disturbances in the RTG4 Power Delivery Network (PDN) can contribute to an increase in global network clock jitter.

There are two distinct contributors to increased clock jitter:

- The PDN's inability to meet large transient current demands under extreme design toggle rates. This

can occur regardless of the clock frequencies in the user design.

- Design operation with a large amount of logic toggling simultaneously at the PDN resonance frequency, which typically ranges from 10 MHz to 40 MHz, depending on the specific board design.

Depending on the aggressor clock frequency, either one of these two effects at a time can contribute to increased global net clock jitter. The aggressor clock domain can induce jitter on unrelated victim clock domains. Therefore, the victim clock domains must also consider global net clock jitter.

To address the first contributor above, the RTG4 core voltage supply (VDD) must always be maintained within ± 5% of 1.2 V at the device package pins, during design operation. The operating voltage specification includes the regulator DC variation plus any power supply ripple over the customer design frequencies, as measured at the device package pins. For information about operating voltage specification, see *DS0131: RTG4 FPGA Datasheet*. The VDD ripple during design operation can be measured for specific designs and boards to ensure that it conforms to the datasheet specifications.

Typically, designs operate with a continuous noise floor and a relatively low simultaneous Flip-Flop (FF) toggle rate, which helps to spread the current demand over time. However, designs with abnormally high toggle rates, greater than 15% of the total device Flip-Flops toggling simultaneously in the same direction, increase the instantaneous current demand on the VDD supply. Furthermore, if that large quantity of simultaneously switching FFs periodically starts and stops with a low enable rate, it can cause a large transient current demand on the PDN as the logic is re-enabled. Depending on the amount of fabric logic that starts toggling simultaneously when the enable is asserted, the transient current demand on the PDN can cause the VDD to dip below the datasheet limits. To avoid extra global net clock jitter, ensure that the VDD is always maintained within the datasheet limits during design operation.

Regarding the second contributor to global net clock jitter, it is related to the percentage of the 151,824 FFs in the device that toggle simultaneously, in the same direction, at a given clock edge, when that clock domain operates within the 10 MHz to 40 MHz range. In typical designs, the average FF toggle rate per clock domain does not exceed ~25%. Specific boards and designs might require higher toggle rates, but support for that level of operation should be confirmed by design specific VDD variation and clock jitter measurements taken on the user board with the design operating at its maximum switching activity. To help quantify the FF toggle rate for a given clock domain, consider the following example:

If a clock domain drives 30% of the 151,824 total available FFs in the RTG4 fabric, and if the average FF toggle rate within that domain is 25%, it equates to only a 7.5% effective toggle rate in the device (assuming no other clock domains are switching simultaneously).

For information about maximum period jitter specifications on the RTG4 Global Network for various FF toggle rates within the device, see *DS0131: RTG4 FPGA Datasheet*. This specification on RTG4 global net clock jitter is a worst-case maximum period jitter that applies across the supported RTG4 silicon process, voltage, and temperature range. The period jitter is useful for analysis at the boundary of the device, such as an interfaces to other devices using common clocking topology instead of source-synchronous clocking. Similarly, period jitter is useful for static timing analysis of inter-clock domain paths. For Static Timing Analysis (STA) of FPGA fabric internal paths, such as register-to-register paths in a single clock domain, it is more realistic to use cycle-to-cycle jitter. Using period jitter during STA of internal reg-to-reg paths in a single clock domain is overly conservative and can create artificial timing violations.

There are several characteristics to consider regarding this PDN disturbance induced RTG4 global net clock jitter:

- These PDN disturbances impact the entire FPGA fabric including both the clock and data paths. This

avoids potential skew issues that can arise when clock and data slow down independently.

- All FFs within a clock domain see the same delayed/advanced clock edge for a given cycle.

- Data transfers within a single clock domain do not fail due to this added clock jitter.

- Silicon characterization of victim logic clocked by a victim global clock surrounded by a jitter stress design shows:

- The maximum frequency achieved in hardware still exceeds the maximum performance reported by SmartTime Static Timing Analysis software.

- Zero hold time failures are created in silicon when using the shortest (intra-cluster) data path or a data path spanning multiple fabric rows.

- Global net clock jitter on FPGA fabric data path does not induce SerDes data bit errors at 2.5Gbps (STD speed grade) or 3.125Gbps (-1 speed grade)

Apply the following guidelines when accounting for clock jitter:

Table 6 • Effective Device Flip-Flop Toggle Rate<sup>1</sup>

| Effective Flip-Flop<br>Toggle Rate<br>(% of device FFs) | CCC PLL<br>Used? | Jitter to use in STA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15% or Less                                             | Yes              | Whichever is larger of global net clock Jitter or CCC/PLL output clock jitter, as per DS0131: RTG4 FPGA Datasheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                         | No               | Whichever is larger of global net clock Jitter or input buffer clock jitter, as per DS0131: RTG4 FPGA Datasheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Greater than 15%                                        | Yes              | Typical designs are expected to have less than 30% device FF utilization per                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         | No               | clock domain, and an average FF toggle rate less than 25% within the domain for an Effective Device Flip-Flop Toggle Rate of <7.5%. For designs with >15% Effective FF Toggle percentage, measure the global net clock jitter from an output pin using the oscilloscope clock jitter measurement package with the design operating at maximum switching activity. Internal fabric reg-to-reg paths can use jitter data from the RTG4 FPGA Datasheet, with the Root Sum Squares (RSS) method to add the contribution from the input I/O buffer or PLL to the global net clock jitter. External interfaces should account for the measured period jitter during STA. |

<sup>1.</sup> Product of FF percentage used of total FFs in the device and Average FF Toggle Rate for a given clock domain.

As an example of the methodology used to calculate the clock jitter constraints with each clock domain in the RTG4 design, consider the RTG4 design summarized in the following table, for a - 1 speed grade RTG4 device:

Table 7 • Estimation of Worst-Case Clock Jitter for a - 1 Speed Grade RTG4 Design

| Clock<br>Domain | Frequency<br>(MHz) | Clock<br>Path to FF                       | Sequential<br>Loads | Estimated<br>FF Toggle<br>Rate within<br>Domain –<br>Parameter A | % Utilization<br>of Total<br>Device FFs –<br>Parameter B | Effective<br>FF Toggle<br>Rate (% of<br>total<br>device FF)<br>– A% of B |                                   | Worst-Case<br>Clock Jitter<br>from<br>domain (ps)<br>pk-to-pk <sup>1</sup> | Clock Jitter<br>to use in                              |

|-----------------|--------------------|-------------------------------------------|---------------------|------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------|

| Clk_0           | 156.25             | CLKBUF to<br>GB                           | 40,000              | 30%                                                              | 26.4%                                                    | 7.9%                                                                     | Async                             | 524.4                                                                      | 525                                                    |

| Clk_1           | 125                | CLKBUF to<br>GB                           | 38,000              | 30%                                                              | 25%                                                      | 7.5%                                                                     | Async                             | 500                                                                        | 525                                                    |

| Clk_2           | 20                 | CLKBUF to<br>FCCC PLL<br>to GB            | 15,000              | 25%                                                              | 10%                                                      | 2.5%                                                                     | Sync with Clock_3 Async to others | 1000 + 1.45<br>* Input_Jitter                                              | 1000 + 1.45<br>* Input_Jitter                          |

| Clk_3           | 80                 | CLKBUF to<br>FCCC PLL<br>to GB            | 15,000              | 15%                                                              | 10%                                                      | 1.5%                                                                     | Sync with Clock_2 Async to others | 250 + 1.45 *<br>Input_Jitter                                               | Max of<br>{525,<br>OR 250 +<br>1.45 *<br>Input_Jitter} |

| Clk_4           | 25                 | LVDS33<br>CLKBUF to<br>GB (VID ≥<br>VICM) | 10,000              | 18%                                                              | 6.6%                                                     | 1.2%                                                                     | Async                             | 1600                                                                       | 1600                                                   |

For information about Fabric PLL Output Clock Jitter Specification, Maximum MSIO Input Buffer Jitter Added to Input Clocks Directly Driving Globals, and RTG4 Global Network - Max Period Jitter, see RTG4 FPGA Datasheet, revision B or later.

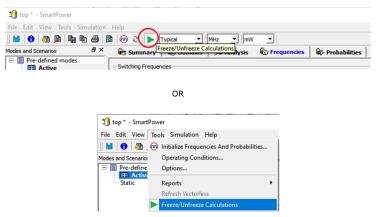

The design described in Table 7, page 21 provides an example showing the impact of various jitter sources on each individual clock domain and on victim clock domains that might otherwise have less clock jitter than the aggressor clock domain. The key factor in this analysis is using a relatively accurate estimate of the average FF toggle rate for the sequential logic in each clock domain. This can be estimated in SmartPower using the Vectorless Analysis technique. Furthermore, performing a gate-level simulation using a comprehensive testbench with realistic design toggle/activity rates can generate a VCD file that can be imported into SmartPower to initialize the toggle rate for all internal nodes. When the estimated FF toggle rate within each domain is available, it can be converted into the effective FF toggle percentage of the total number of device FFs (151,824) by multiplying against the percentage of the total device FF used in that domain. Typical designs do not exceed a 15% effective simultaneous FF toggle rate (in the same direction) out of the 151,824 FFs in the device, but it is design specific, depending on whether it is a control logic or high-speed data path logic. Therefore, the *RTG4 FPGA Datasheet* provides conservative, worst-case global net clock jitter characterization data that should be used carefully, to prevent excessive timing closure difficulty.

For example, Clk\_0 has a 30% FF toggle rate within the clock domain, and it uses 40,000 or 26.4% of the 151,824 total FFs available in the device. Therefore, if 30% of the 40,000 FFs switch at each active Clk\_0 edge, the effective FF toggle percentage is 12,000 FFs out of 151,824 total, or 7.9%. In other words, this is 30% (Parameter A) of the 26.4% FFs used in the device (Parameter B) which gives 0.3\*26.4%=7.9% effective FF toggle percentage. With that effective FF toggle rate, the Global Network Max Period Jitter for 7.5% FF Toggle percentage on a -1 speed grade specifies 500 ps worst-case period jitter. For information about Global Network Max period Jitter, see RTG4 FPGA Datasheet, revision B or later. Since 7.9% is more than the datasheet datapoint of 7.5%, linear interpolation indicates that 524.4 ps

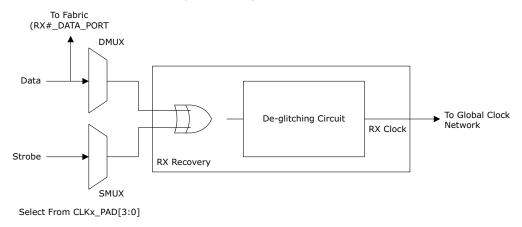

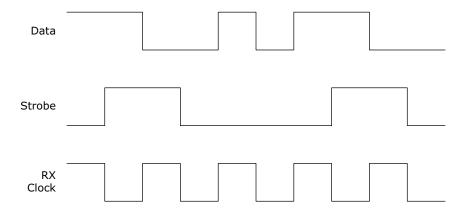

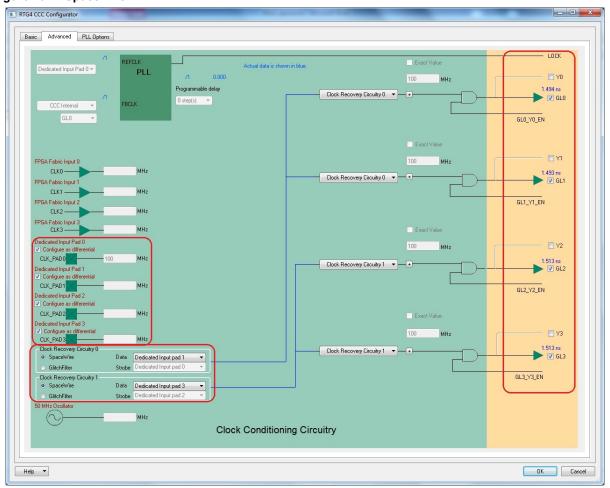

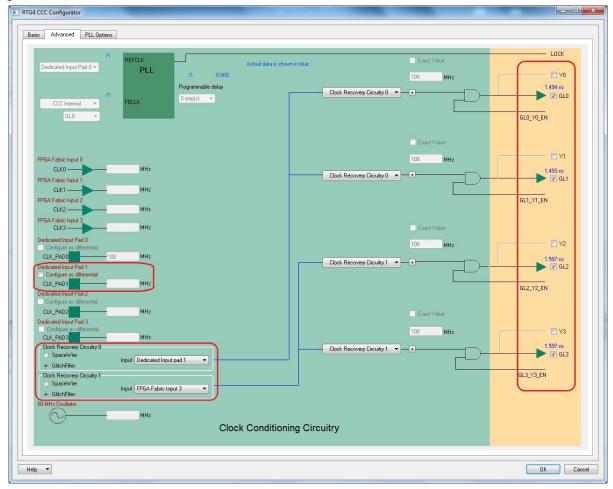

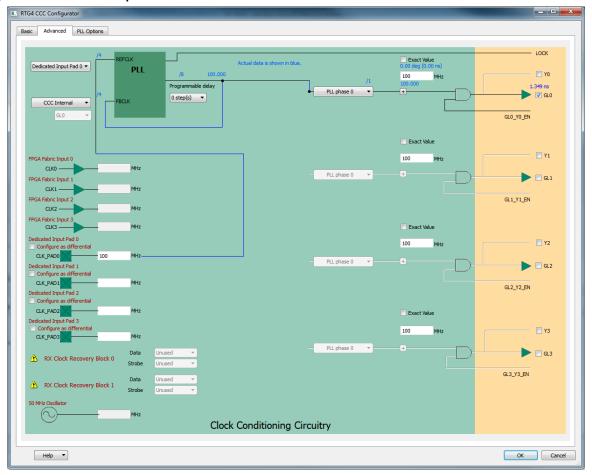

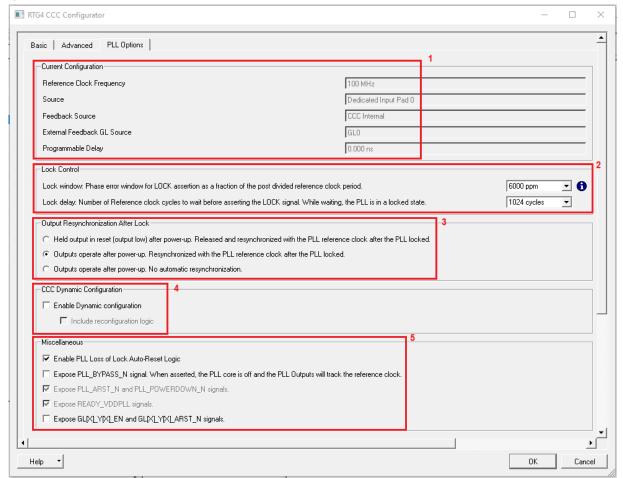

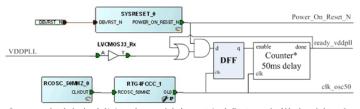

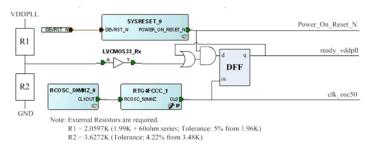

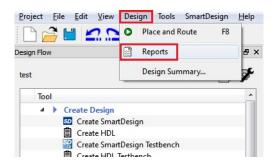

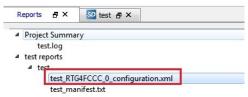

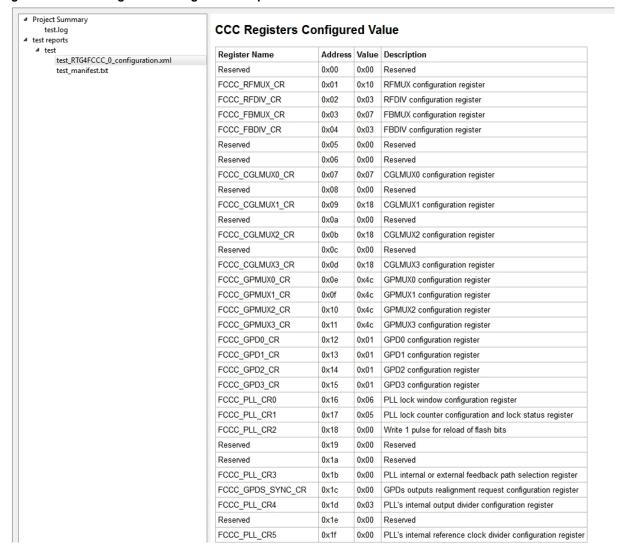

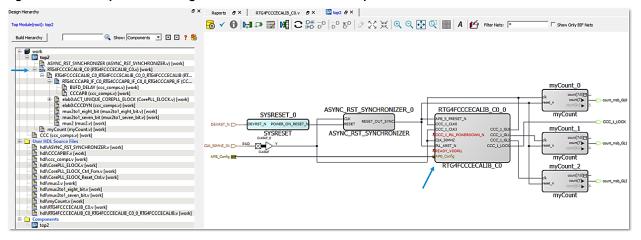

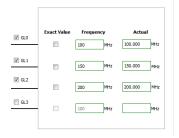

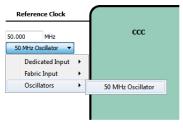

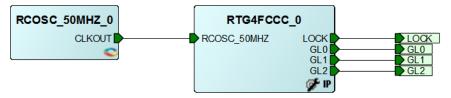

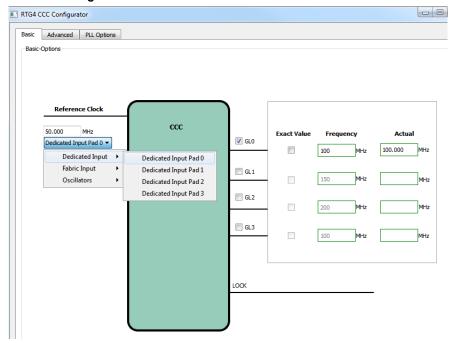

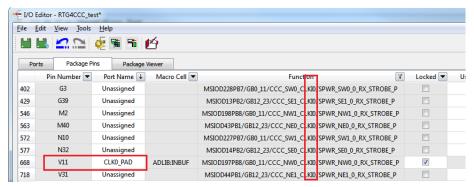

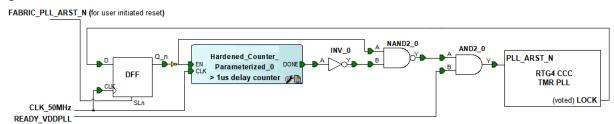

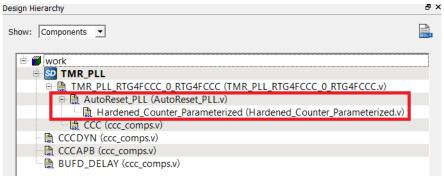

worst-case period jitter can be used. This is written as 525 ps to make it easier when writing clock uncertainty constraints. If it is assumed that this clock enters the RTG4 with an MSIO standard other than a 3.3V differential input, the input buffer jitter added to the clock that directly drives the global network is 128 ps peak-to-peak (which is 2% of the clock period).