# SmartDesign v8.4 User's Guide

### Actel Corporation, Mountain View, CA 94043

© 2008 Actel Corporation. All rights reserved.

Printed in the United States of America

Release: July 2008

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### Trademarks

Actel and the Actel logotype are registered trademarks of Actel Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc.

Mentor Graphics, Precision RTL, Exemplar Spectrum, and Leonardo Spectrum are registered trademarks of Mentor Graphics, Inc.

WaveFormer Lite is a registered trademark of SynaptiCAD, Inc.

Synplify is a registered trademark of Synplicity, Inc.

Sun and Sun Workstation, SunOS, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc

Synopsys is a registered trademark of Synopsys, Inc.

Verilog is a registered trademark of Open Verilog International.

Viewlogic, ViewSim, ViewDraw and SpeedWave are trademarks or registered trademarks of Viewlogic Systems, Inc.

Windows is a registered trademark and Windows NT is a trademark of Microsoft Corporation in the U.S. and other countries.

UNIX is a registered trademark of X/Open Company Limited.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

| SmartDesign                                                     |    |

|-----------------------------------------------------------------|----|

| SmartDesign Design Flow                                         |    |

| Using Existing Projects with SmartDesign                        |    |

| SmartDesign Frequently Asked Questions                          |    |

| General Questions                                               |    |

| Instantiating your SmartDesign                                  | 9  |

| Working in SmartDesign.                                         |    |

| Working with Processor-Based Designs in SmartDesign             | 9  |

| Making your Design Look Nice                                    | 9  |

| Generating your Design                                          | 10 |

| General Questions                                               | 10 |

| Instantiating Your SmartDesign                                  | 10 |

| Working in SmartDesign                                          | 10 |

| Working with Processor-Based Designs in SmartDesign             | 12 |

| Making Your Design Look Nice                                    | 13 |

| Generating Your Design                                          | 13 |

| Getting Started with SmartDesign                                | 15 |

| Creating a New SmartDesign Component                            |    |

| Opening an Existing SmartDesign Component                       | 15 |

| Saving/Closing a SmartDesign Component                          | 16 |

| Importing a SmartDesign Component                               | 16 |

| Deleting a SmartDesign Component from the Libero IDE Project    |    |

| Memory Maps / Data Sheet                                        | 16 |

| Modify Memory Map Dialog Box                                    | 18 |

| Finding Files in SmartDesign                                    | 18 |

| SmartDesign User Interface                                      | 19 |

| SmartDesign User Interface Overview                             | 19 |

| Canvas View                                                     | 21 |

| Canvas Overview                                                 | 21 |

| Displaying Connections on the Canvas                            | 23 |

| Making Connections Using the Canvas                             |    |

| Simplifying the Display of Pins on an Instance using Pin Groups | 26 |

| Bus Instances                                                   | 27 |

| Adding Graphic Objects                                          | 28 |

| Auto-Arranging Instances                                        | 31 |

| Auto-Arrange Connections                                                | 31 |

|-------------------------------------------------------------------------|----|

| Replace Version for Instance                                            | 31 |

| Slicing                                                                 | 32 |

| Exposing Driver Pins                                                    | 32 |

| Instance Properties                                                     | 33 |

| Rename Net                                                              | 33 |

| Organizing Your Design on the Canvas                                    | 34 |

| Grid                                                                    | 35 |

| Grid Overview                                                           | 35 |

| Display Panel                                                           | 37 |

| Connection Panel                                                        | 39 |

| Instance-Instance View                                                  | 41 |

| Instance-Instance View                                                  | 41 |

| Adding and Removing Fields                                              | 42 |

| Sorting with Fields                                                     | 43 |

| Making Connections Using the Grid                                       | 44 |

| Connecting Multiple Pins (Connection Panel)                             | 45 |

| Net-Instance View                                                       | 47 |

| Connect to an Existing Net (Net-Instance View)                          | 48 |

| Make New Connection (Net-Instance View)                                 | 49 |

| Filtering Views                                                         | 50 |

| Schematic View                                                          | 51 |

| Schematic Overview                                                      | 51 |

| Page Splitting                                                          | 52 |

| Zooming                                                                 | 52 |

| Creating a SmartDesign                                                  | 53 |

| Adding Components and Modules (Instantiating)                           | 53 |

| Adding a SmartDesign Component in a Higher-level Design (Instantiating) | 53 |

| Adding Top Level Ports / Renaming External Pads in a SmartDesign        | 53 |

| Connecting Instances                                                    | 55 |

| Automatic Connections                                                   | 55 |

| Manual Connections                                                      | 55 |

| Deleting Connections                                                    | 56 |

| Top-Level Connections                                                   | 56 |

| Bus Interfaces                                                          | 57 |

| About Bus Interfaces                                                    | 57 |

| Using Bus Interfaces in SmartDesign                                     | 59 |

| Adding Bus Interfaces to SmartDesign Components  | 60         |

|--------------------------------------------------|------------|

| Adding Bus Interfaces to SmartDesign Instances   | 61         |

| Removing Bus Interfaces from Instances           | 61         |

| Viewing Bus Interface Properties                 | 62         |

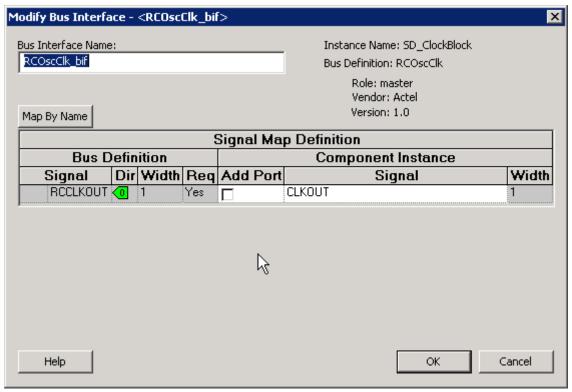

| Modifying Bus Interface Details                  | 64         |

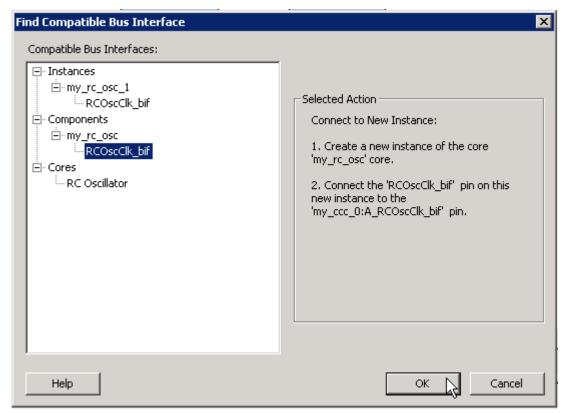

| Finding Compatible Bus Interfaces                | 64         |

| Actel Bus Interfaces                             | 66         |

| DirectCore Bus Interfaces                        | 67         |

| Default Tie-Offs with Bus Interfaces             | 67         |

| Tying Off (Disabling) Unused Bus Interfaces      | 68         |

| Required vs. Optional Bus Interfaces             | 68         |

| Promoting Bus Interfaces to Top-Level            | 69         |

| Incremental Design                               | <b>7</b> 1 |

| Reconfiguring a Component                        | 72         |

| Fixing an Out-of-Date Instance                   | 72         |

| Replacing Components                             | 73         |

| Design State Management                          | 73         |

| Connectivity Checker                             | 75         |

| Generating a SmartDesign Component               | 76         |

| Synthesizing the SmartDesign Component           |            |

| Simulating the SmartDesign Component             | 77         |

| Reference                                        | 79         |

| SmartDesign Menu                                 | 79         |

| Canvas Menu                                      | 80         |

| Grid Menu                                        | 80         |

| Schematic Menu                                   | 82         |

| SmartDesign Glossary                             | 81         |

| Canvas Icons                                     | 83         |

| Grid - Display Panel Icons                       | 88         |

| Grid - Connection Panel Icons.                   | 90         |

| Schematic Symbols                                | 92         |

| Using the HDL Editor                             |            |

| Product Support                                  | 93         |

| Customer Service                                 | 93         |

| Actel Customer Technical Support Center          | 93         |

| Actel Technical Support                          | 93         |

| Website                                          | 93         |

| Contacting the Customer Technical Support Center | 92         |

# **SmartDesign**

SmartDesign has been re-designed to enable faster creation of simple to complex System on Chip (SoC) designs including processor/bus based and Fusion mixed signal designs. Complete FPGA systems and subsystems can be designed in minutes by selecting from Actel's core libraries, making quick and error-free connections, and automatically creating a synthesis ready HDL file.

### **Key Features**

- Visual block-based design creation tool

- Replaces CoreConsole for processor, bus-based, and DirectCore subsystem creation

- Quickly select, configure, and connect proven functional blocks from Libero IDE Project Manager <u>Catalog</u>:

DirectCores, Smartgen Cores, and Actel cells

- Import and connect user generated IP, Designer Blocks, and custom/glue-logic HDL modules including ViewDraw schematics

- SmartGuide guidance suggests compatible interfaces and notes required peripherals

- All construction is performed on a single <u>Canvas</u>

- All pins/ports are exposed and ready for connection on the Canvas

- Automatic or simple point-and-click manual connections

- Design-rule check disallows improper connections or unconnected ports

- Dynamic audit system informs of out-of-date configurations

- Automatic abstraction to synthesis-ready HDL: Verilog or VHDL

- Efficient construction of complex processor, bus based, Fusion mixed signal, and simple designs

- Complete FPGA SoC, FPGA subsystem, or embedded SmartDesign-in-SmartDesign

SmartDesign supports all Actel product families.

# **SmartDesign Design Flow**

SmartDesign enables you to stitch together design blocks of different types (HDL, IP, etc) and generate a top-level design. The Files tab lists your SmartDesign files in alphabetical order.

You can build your design using SmartDesign with the following steps:

Step One – Instantiating components: In this step you will <u>add one or more building blocks</u>, HDL modules, components, and schematic modules from the project manager to your design. The components can be Designer blocks, SmartGen cores (cores generated from the core catalog), and IP cores.

#### SmartDesign

Step Two – Connecting bus interfaces: In this step, you can <u>add connectivity via standard bus interfaces</u> to your design. This step is optional and can be skipped if you prefer manual connections. Components generated from the Catalog in Project Manager may include pre-defined interfaces that allow for <u>automatic connectivity</u> and design rule checking when used in a design.

Step Three – Connecting instances: The <u>Canvas</u> allows you to create manual connections between ports of the instances in your design. Unused ports can be <u>tied off</u> to GND or VCC (disabled); input buses can be <u>tied to a constant</u>, and you can leave an output open by <u>marking it as unused</u>.

Step Four – Validating the SmartDesign component: Verify the connectivity of your design using the Connectivity Check feature. This feature opens a special grid where design errors and warnings are organized by type and message. You can fix the errors and warnings directly in the grid. You must run the Connectivity Check again after you make your connections to check for new errors and warnings.

Step Five – Generating the SmartDesign component: In this step, you generate a top-level (Top) component and its corresponding HDL file. This component can be used by downstream processes, such as synthesis and simulation, or you can add your SmartDesign HDL into another SmartDesign.

You can save your SmartDesign at any time.

# Using Existing Projects with SmartDesign

You can use existing Libero<sup>®</sup> Integrated Design Environment (IDE) projects with available building blocks in the project to assemble a new SmartDesign design component. You do not have to migrate existing top-level designs to SmartDesign and there is no automatic conversion of the existing design blocks to the SmartDesign format.

Note: SmartGen cores used in previous versions of software will work in SmartDesign, but they will NOT include standard bus interfaces if they are available. Bus interfaces (BIFs) can be recovered by regenerating the core in the latest software.

Examples of cores with standard BIFs: ASB, Flash Memory System Builder, VRPSM, AMBA DirectCore(s), and similar.

# **SmartDesign Frequently Asked Questions**

The collection of SmartDesign Frequently Asked Questions are useful for anyone that is new to SmartDesign. All the information listed below is explained in detail in other sections of the help, but the information is summarized here for easy reference. Click any question to go to the corresponding explanation.

# **General Questions**

- 1. What is SmartDesign?

- 2. How do I create my first SmartDesign?

# Instantiating your SmartDesign

- 1. Where is the list of cores that I can instantiate into my SmartDesign?

- 2. How do I instantiate cores into my SmartDesign?

- 3. I have a block that I wrote in VHDL (or Verilog); can I use that in my SmartDesign?

# Working in SmartDesign

- 1. How do I make connections?

- 2. Auto Connect didn't connect everything for me; how do I make manual connections?

- 3. How do I connect a pin to the top level?

- 4. Oops, I just made a connection mistake. How do I disconnect two pins?

- 5. <u>I need to apply some simple 'glue' logic between my cores. How do I do that?</u>

- 6. My logic is a bit more complex than inversion and tie offs what else can I do?

- 7. How do I create a new top level port for my design?

- 8. How do I rename one of my instances?

- 9. How do I rename my top level port?

- 10. How do I rename my group pins?

- 11. I need to reconfigure one of my Cores; can I just double click the instance?

- 12. I want more Canvas space to work with!

# Working with Processor-Based Designs in SmartDesign

- 1. How do I connect my peripherals to the bus?

- 2. How do I view the Memory Map of my design?

- 3. How do I simulate my processor design?

- 4. I have my own HDL block that I want to connect as a peripheral on the AMBA bus. How can I do that?

# Making your Design Look Nice

- 1. Can the tool automatically place my instances on the Canvas to make it look nice?

- 2. My design has a lot of connections, and the nets are making my design hard to read. What do I do?

- 3. My instance has too many pins on it, how can I minimize that?

- 4. Oops, I missed one pin that needs to be part of that group? How do I add a pin after I already have the group?

- 5. I have a pin that I don't want inside the group, how do I remove it?

- 6. How can I better see my design on the Canvas?

# **Generating your Design**

- 1. Ok, I'm done connecting my design, how do I 'finish' it so that I can proceed to synthesis?

- 2. I get a message saying it's unable to generate my SmartDesign due to errors, what do I do? What's the Connectivity Checker?

- 3. Is there an easy way for me to tie off multiple pins at once?

# **General Questions**

#### What is SmartDesign?

SmartDesign is a design entry tool. It's the first tool in the industry that can be used for designing System on a Chip designs, custom FPGA designs or a mixture of both types in the same design. A SmartDesign can be the entire FPGA design, part of a larger SmartDesign, or a user created IP that can be stored and reused multiple times. It's a simple, intuitive tool with powerful features that enables you to work at the abstraction level at which you are most comfortable.

It can connect blocks together from a variety of sources, verify your design for errors, manage your memory map, and generate all the necessary files to allow you to simulate, synthesize, and compile your design.

#### How do I create my first SmartDesign?

From the Project Manager Project Flow window, in the Design Entry Tools section, click the SmartDesign icon:

# Instantiating Your SmartDesign

Where is the list of Cores that I can instantiate into my SmartDesign?

The list of available cores is displayed in the <u>Project Manager Catalog</u>. This catalog contains all DirectCore IP, SmartGen cores, and Actel macros (cells).

#### How do I instantiate cores into my SmartDesign?

Drag and drop the core from the <u>Catalog</u> onto your SmartDesign <u>Canvas</u>. The configurator for that core opens automatically. Choose your configurations, click OK, and an instance of your core appears on the SmartDesign Canvas.

### I have a block that I wrote in VHDL (or Verilog); can I use that in my SmartDesign?

Yes! Import your HDL file into the Project Manager (File > Import Files). After you do this, your HDL module will appear in the Project Manager Hierarchy. Then, drag-and-drop it from the Hierarchy onto your SmartDesign Canvas.

# Working in SmartDesign

How do I make connections?

Let SmartDesign do it for you. Right-click the Canvas and choose Auto Connect.

#### Auto Connect didn't connect everything for me, how do I make manual connections?

- 1. Select the pins you want connected by using the mouse and the CTRL key.

- 2. Right-click one of the selected pins and choose Connect.

- 3. For bus interface pins you can do the same thing, OR: Right click a bus interface pin, choose Find Compatible Bus Interfaces. A dialog box will display a list of the compatible bus interfaces in the design that you can connect to. Choose the bus interface you want to connect to from the list and click OK.

#### How do I connect a pin to the top level?

Right-click the pin and choose **Promote to Top Level**. You can even do this for multiple pins at a time, just select all the pins you want to promote, right-click one of the pins and choose **Promote to Top Level**. All your selected pins will be promoted to the top level.

#### Oops, I just made a connection mistake. How do I disconnect two pins?

Use CTRL+Z to undo your last action. If you want to undo your 'undo', hit redo (CTRL+Y).

To disconnect pins you can:

- Right-click the pin you want to disconnect and choose Disconnect

- Select the net and hit the delete key

#### I need to apply some simple 'glue' logic between my cores. How do I do that?

For basic inversion of pins, you can right-click a pin and choose **Invert**. An inverter will be placed at this pin when the design is generated. You can also right-click a pin and choose Tie Low or Tie High if you want to connect the pin to either GND or VCC.

To tie an input bus to a constant, right-click the bus and choose **Tie to Constant**. To mark an output pin as unused, right-click the pin and choose **Mark as Unused**.

To clear these, just right-click on the pin again and choose Clear Attribute.

#### My logic is a bit more complex than inversion and tie offs - what else can I do?

You have full access to the Actel library cells, including AND, OR, and XOR logic functions. These are located in the <a href="Project Manager Catalog">Project Manager Catalog</a>, listed under Actel Cells. Drag the logic function you want onto your SmartDesign Canvas.

### How do I create a new top level port for my design?

Scroll your design all the way to the left. Right-click the block on the far left of your Canvas (this represents the top level of your design) and choose Add Port.

#### How do I rename one of my instances?

Double-click the instance name on the Canvas and it will become editable. The instance name is located directly above the instance on the Canvas.

#### How do I rename my top level port?

Right-click the port you want to rename and choose Modify Port.

### SmartDesign

### How do I rename my group pins?

Double-click the group pin name in the instance and it will become editable.

#### I need to reconfigure one of my Cores, can I just double click the instance?

Yes.

#### I want more Canvas space to work with!

Maximize your workspace (CTRL-W), and your Canvas will maximize within the Project Manager. Hit CTRL-W again if you need to see your Hierarchy or Catalog.

# Working with Processor-Based Designs in SmartDesign

### How do I connect my peripherals to the bus?

Make sure you have the proper bus core that is compatible with your peripheral instantiated in the design. Click **Auto** Connect and SmartDesign will automatically form the connections.

#### But I need my peripheral at a specific address or slot.

Right-click the Canvas and choose **Modify Memory Map** to invoke the Modify Memory Map dialog that enables you to set a peripheral to a specific address on the bus.

The bus core will show the slot numbers on the bus interface pins. These slot numbers correspond to a memory address on the bus.

Verify that your peripheral is mapped to the right bus address by viewing your design's Memory Map.

### How do I view the Memory Map of my design?

In the Project Manager menu bar, choose SmartDesign > Show Memory Map/Data Sheet. This creates a datasheet of your design, including the pin out, cores used, and memory map.

The memory map section will also show the memory details of each peripheral, including any memory mapped registers.

#### How do I simulate my processor design?

SmartDesign automatically generates the necessary Bus Functional Model (BFM) scripts required to simulate your processor based design. A top level testbench for your SmartDesign is generated automatically as well.

Create your processor design, generate it, and you will be able to simulate it in ModelSim.

#### I have my own HDL block that I want to connect as a peripheral on the AMBA bus. How can I do that?

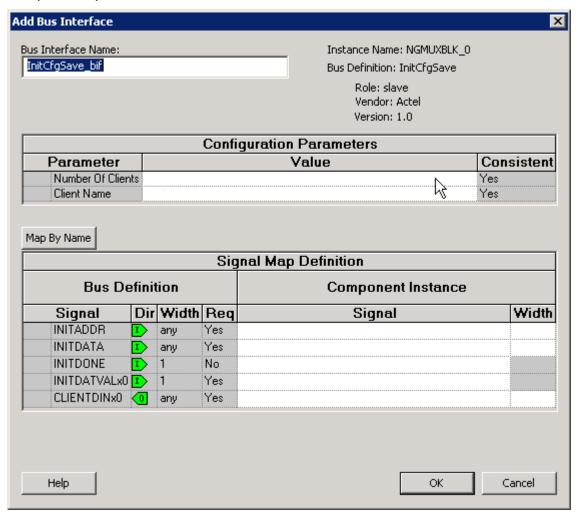

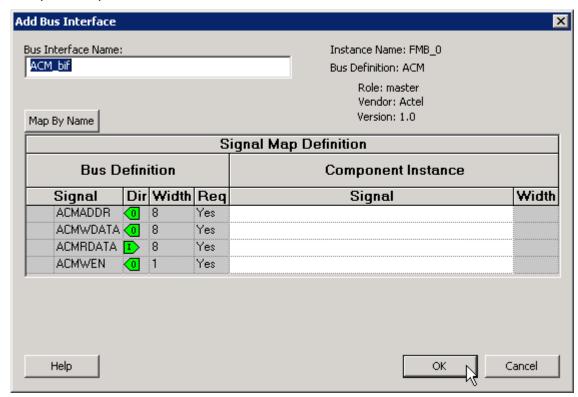

If your block has all the necessary signals to interface with the AMBA bus protocol (ex: address, data, control signals) then:

- 1. In the Project Manager Catalog (inside the Bus Definitions tab), find the AHB or APB slave interface.

- 2. Drag this bus definition onto your instance on the Canvas. A dialog box opens, asking you to map the signals on your instance to the required bus definition signals. Complete this mapping and click OK.

Now your instance has a proper AMBA bus interface on it. You can manually connect it to the bus or let Auto Connect find a compatible connection.

# Making Your Design Look Nice

Can the tool automatically place my instances on the Canvas to make it look nice?

Yes. Right-click the Canvas white space and choose Auto Arrange Instances.

My design has a lot of connections, and the nets are making my design hard to read. What do I do?

You can disable the display of the nets in the menu bar (Canvas > Nets). This automatically hides all the nets in your design.

You can still see how pins are connected by selecting a connected pin, the net will automatically be visible again.

You can also selectively show certain nets, so that they are always displayed, just right click on a connected pin and choose Show Net.

My instance has too many pins on it; how can I minimize that?

Try grouping functional or unused pins together. For example, on the CoreInterrupt there are 8 FIQSource\* and 32 IRQSource\* pins, group these together since they are similar in functionality.

To group pins: Select all the pins you want to group, then right-click one of the pins and choose Add pins to group.

If a pin is in a group, you are still able to use it and form connections with it. Expand the group to gain access to the pin.

Oops, I missed one pin that needs to be part of that group? How do I add a pin after I already have the group?

Select the pin you want to add and the group pin, right-click and choose Add pins to <name> group.

I have a pin that I don't want inside the group, how do I remove it?

Right-click the pin and choose Ungroup selected pins.

How can I better see my design on the Canvas?

There are zoom icons in the toolbar:

From left to right, they are: Zoom in, Zoom out, Zoom to fit, and Zoom range. You can also maximize your workspace with CTRL-W.

# **Generating Your Design**

Ok, I'm done connecting my design, how do I 'finish' it so that I can proceed to synthesis?

In the Project Manager toolbar, click the Generate Design icon or right-click the Canvas and choose Generate Design.

I get a message saying it's unable to generate my SmartDesign due to errors, what do I do? What's the Connectivity Checker?

### SmartDesign

In the Project Manager toolbar, click the Connectivity Checker icon:

The connectivity checker will give you a list of all the errors and warnings in your design, including unconnected input pins, required pin connections, configuration incompatibilities between cores, etc.

Errors are shown with a small red octagon and must be corrected before you can generate, warnings may be ignored.

### What does this error mean? How do I fix it?

Review the Connectivity Checker topic for an explanation of errors in the Connectivity Checker and steps to resolve them.

### Is there an easy way for me to tie off multiple pins at once?

Yes, if you are in the Connectivity Checker grid, you can select multiple pins by highlighting the rows that they are in. Multi-selecting works just like your typical spreadsheet editor.

Once all the pins have been selected, right-click one of the pin names and choose Tie Low or Tie High. Make sure you only have input pins selected otherwise the menu item won't be enabled.

# **Getting Started with SmartDesign**

# Creating a New SmartDesign Component

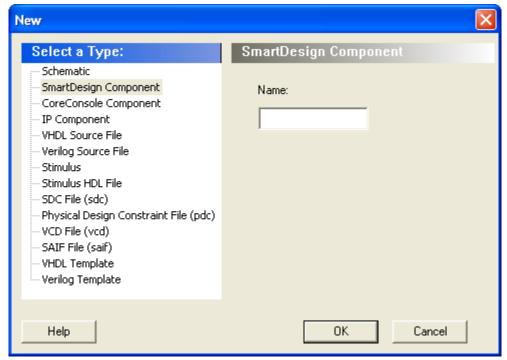

1. From the **File** menu, choose **New** or press the **SmartDesign** button in the Project Manager Project Flow window. The **New** dialog box opens (see figure below - file types vary depending on your project settings).

Figure 1 · New Dialog Box

Select SmartDesign Component, enter a component name and click OK. The component appears in the

<u>Hierarchy</u> tab of the Design Explorer. Also, the main window displays the design <u>Canvas</u>.

Note: The component name must be unique in your project.

# Opening an Existing SmartDesign Component

### To open an existing component do one of the following:

- In the Design Explorer, click the Hierarchy tab and double-click the component you want to open.

- In the Design Explorer, from the Files tab, expand the Components list and double-click the component you

want to open.

The main window displays the SmartDesign Canvas for the SmartDesign component.

# Saving/Closing a SmartDesign Component

To save the current SmartDesign design component, from the File menu, choose Save <component\_name>. Saving a SmartDesign component only saves the current state of the design; to generate the HDL for the design refer to Generating a SmartDesign component.

To close the current SmartDesign component without saving, from the File menu, choose Close. Select NO when prompted to save.

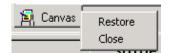

You can also close a SmartDesign component by right-clicking the name of the SmartDesign tab in the work area window and choosing **Close**, as in the figure below.

Figure 2 · Close a SmartDesign

# Importing a SmartDesign Component

Importing an existing SmartDesign component into a SmartDesign project will not automatically import the sub-components of that imported SmartDesign component.

You must import each sub-component separately.

After importing the sub-components, you must open the SmartDesign component and <u>replace</u> each sub-component so that it references the correct component in your project.

# Deleting a SmartDesign Component from the Libero IDE Project

### To delete a SmartDesign component from the project:

- 1. In the Design Explorer, click the Hierarchy tab.

- Select the SmartDesign component that you want to delete. Right-click the component name and select Delete

from Project or Delete from Disk and Project, or click the Delete key to delete from project.

# Memory Maps / Data Sheet

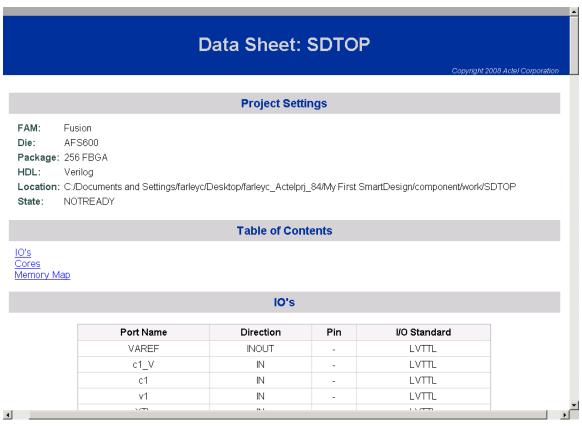

If your design contains standard Bus Instances such as the DirectCore AMBA bus cores, CoreAPB or CoreAHB, then you can view the Memory Map Configuration of your design. To do so, from the SmartDesign menu, choose Show Memory Map / Data Sheet.

The design's memory map is determined by the connections made to the bus component. A bus component is divided into multiple slots for slave peripherals or instances to plug into. Each slot represents a different address location and range to the Master of the bus component.

16

The datasheet reports the memory map of the different subsystems of your design, where a subsystem is any independent bus structure with a Master and Slave peripheral attached.

Connecting peripherals to busses can be accomplished using the normal SmartDesign connectivity options:

- Auto-Connect the system finds compatible bus interfaces and connects them together

- The Modify Memory Map dialog box

- <u>Canvas</u> Make connections between your blocks.

- Finding compatible bus interfaces

Your application and design requirements dictate which address location (or slots) is most suitable for your bus peripherals. For example, the memory controller should be connected to Slot0 of the CoreAHB bus because on Reset, the processor will begin code execution from the bottom of the memory map.

The Memory Map View opens your default web browser to display the memory map information. An example is shown in the figure below.

Figure 3 · Example Memory Map

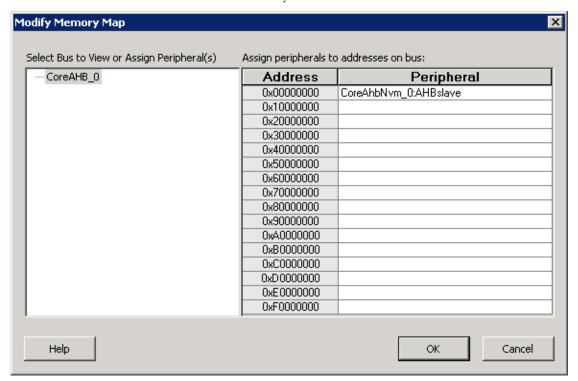

# **Modify Memory Map Dialog Box**

The Modify Memory Map dialog box (shown in the figure below) enables you to connect peripherals to buses via a drop-down menu. To open the dialog box, right-click on the Canvas or specific bus instance and choose **Modify** Memory Map.

This dialog simplifies connecting peripherals to specific base addresses on the bus. The dialog shows all the busses in the design; select a bus in the left pane to assign or view the peripherals on a bus. Busses that are bridged to other busses are shown beneath the bus in the hierarchy.

Figure 4 · Modify Memory Map Dialog Box

Click the Peripheral drop-down menu to select the peripheral you wish to assign to each address. To remove (unassign) a peripheral from an address, click the drop-down and select the empty element.

Click OK to create the connections between the busses and peripherals in the design.

# Finding Files in SmartDesign

Use the Find Window to search for ports, nets, or instances in SmartDesign.

Searching for ports / nets / instances in SmartDesign highlights the objects on the Canvas.

# **SmartDesign User Interface**

# **SmartDesign User Interface Overview**

The SmartDesign tool is integrated into the Libero IDE Project Manager.

The <u>Canvas</u> is the main work area for SmartDesign. The Canvas view displays a high-level block diagram of your design.

The <u>Grid</u> and <u>Schematic</u> views are available from the SmartDesign menu in the Project Manager. These views are not required to complete your design.

The Grid displays your design in a configurable spreadsheet, enabling you to specify detailed connections for each instance in your SmartDesign.

The Schematic View displays your design elements with port names, busses, and nets.

Changes made in one view will immediately be reflected in all other views, enabling you to quickly make and see changes to your design.

You can close each view by right-clicking the name of the view inside the SmartDesign tab and choosing Close.

Figure 5 · Close the Active View

To re-open any view, from SmartDesign menu choose Show Canvas View, Show Grid View, or Show Schematic View.

# **Canvas View**

# **Canvas Overview**

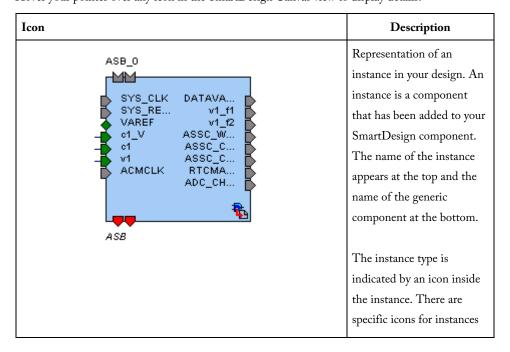

The SmartDesign Canvas is like a whiteboard where functional blocks from various sources can be assembled and connected; interconnections between the blocks represent nets and busses in your design.

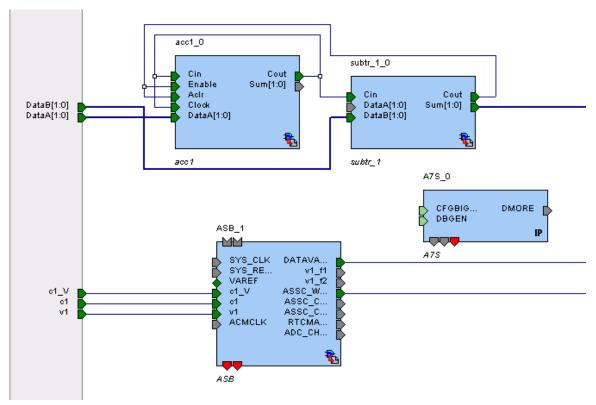

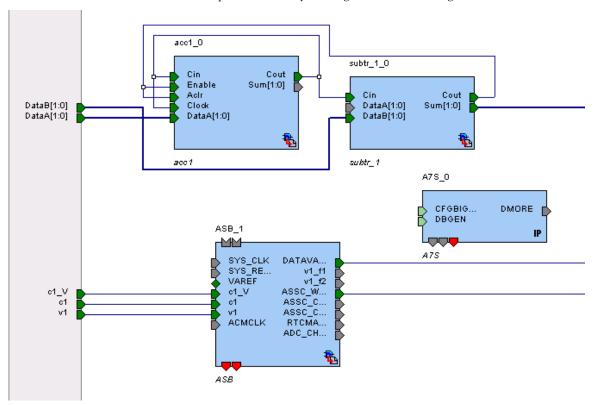

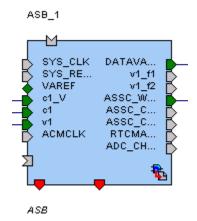

You can use the Canvas to manage connections, set attributes, add or remove components, etc. The Canvas displays all the pins for each instance (as shown in the figure below).

The Canvas enables you to drag a component from the <u>Hierarchy</u>, <u>Files</u> list, or a core from the <u>Catalog</u> and add an instance of that component or core in the design. Some blocks (such as Basic Blocks) must be configured and generated before they are added to your Canvas. When you add/generate a new component it is automatically added to your Hierarchy.

To connect two pins on the Canvas, select any two pins on the Canvas (Ctrl + click to select a pin), right-click one of the pins you selected and choose Connect. The Connect is disabled if you attempt to illegally connect two pins.

Click the Maximize Work Area button to hide the other windows and show more of the Canvas. Click the button again to return the work area to the original size.

The Canvas displays bus pins with a + sign (click to expand the list) or - (click to hide list). If you <u>add a slice</u> on a bus the Canvas adds a + to the bus pin.

Components can be <u>reconfigured</u> any time by double-clicking the instance on the Canvas. You can also <u>add bus</u> <u>interfaces to instances</u> using this view. In the Canvas view, you can <u>add graphic objects and text</u> to your design.

Inputs and bi-directional pins are shown on the left of components, and output pins are shown on the right.

### Canvas View

Figure 6 · SmartDesign Canvas

# See Also

Canvas icons

The Canvas shows the instances, pins, and nets in your design (as shown in the figure below).

Figure 7 · Components in SmartDesign

Scalar net connections are shown in blue; bus net connections are dark blue.

### **Pin and Attribute Icons**

Unconnected pins that do not require a connection are gray.

Unconnected pins that require a connection are red.

Unconnected pins that have a default tie-off are pale green.

Connected pins are green.

Right-click a pin to assign an attribute.

Pins assigned attributes are shown with an icon, as shown in the table below.

Table 1 · Pin Attribute Icons

| Attribute      | Icon |

|----------------|------|

| Tie Low        | •    |

| Tie High       | •    |

| Invert         | -    |

| Mark as Unused | ×    |

See the Canvas Icons reference page for definitions for each element on the Canvas.

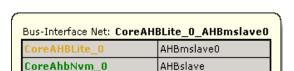

Each connection made using a <u>bus interface</u> is shown in a separate connection known as a 'bus-interface net' (shown in brown lines).

Move the mouse over a bus interface to display its details (as shown below).

Hover over a bus interface net to see details (as shown below).

# Making Connections Using the Canvas

Use the Canvas to make connections between instances.

To connect two pins on the Canvas, select any two (Ctrl + click to select a pin), right-click one of the pins you selected and choose Connect. Illegal connections are disabled; the Connect menu option is unavailable.

# **Promoting Ports to Top Level**

To automatically promote a port to top level, select the port, right-click, and choose **Promote To Top Level**. This automatically creates top-level ports of that name and connects the selected ports to them. If a port name already exists, a choice is given to either connect to the existing ports or to create a new port with a name <port name>\_<i> where i = 1...n.

Double-click a top-level port to rename it.

Bus slices cannot be automatically promoted to top level. You must create a top level port of the bus slice width and then manually connect the bus slice to the newly created top level port.

# **Tying Off Input Pins**

To tie off ports, select the port, right-click and choose Tie High or Tie Low.

# **Tying to Constant**

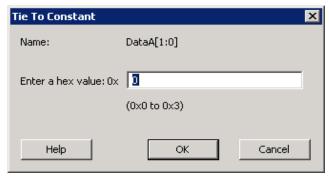

To tie off bus ports to a constant value, select the port, right-click and choose **Tie to a Constant**. A dialog appears (as shown in the figure below) and enables you to specify a hex value for the bus.

To remove the constant, right-click the pin and choose Clear Attribute or Disconnect.

Figure 8 · Tie to Constant Dialog Box

# **Making Driver and Bus Interface Pins Unused**

Driver or bus interface pins can be marked unused (floating/dangling) if you do not intend to use them as a driver in the design. If you mark a pin as unused the Connectivity Checker does not return Floating Driver or Unconnected Bus Interface messages on the pin.

Once a pin is explicitly marked as unused it cannot be used to drive any inputs. The unused attribute must be explicitly removed from the pin in order to connect it later. To mark a driver or bus interface pin as unused, right-click the driver or bus interface pin and choose <u>Mark as Unused</u>.

# Simplifying the Display of Pins on an Instance using Pin Groups

The Canvas enables you to group and ungroup pins on a single instance to simplify the display. This feature is useful when you have many pins in an instance, or if you want to group pins at the top level. Pin groups are cosmetic and affect only the Canvas view; other SmartDesign views and the underlying design are not affected by the pin groups.

Grouping pins enables you to:

- Hide pins that you have already connected

- Hide pins that you intend to work on later

- Group pins with similar functionality

- Group unused pins

- Promote several pins to Top Level at once

#### To group pins:

- 1. Ctrl + click to select the pins you wish to group. If you try to click-and-drag inside the instance you will move the instance on the canvas instead of selecting pins.

- 2. Right-click and choose Add pins to group to create a group. Click + to expand a group. The icon associated with the group indicates if the pins are connected, partially connected, or unconnected (as shown in the figure below).

Figure 9 · Groups in an Instance on the Canvas

To add a pin to a group, Ctrl + click to select both the pin and the group, right-click and choose Add pin to group.

#### To ungroup pins:

- 1. Click + to expand the group.

- 2. Right-click the pin you wish to remove from the group and choose **Ungroup selected pins**. Ctrl + click to select and remove more than one pin in a group.

A group remains in your instance after you remove all the pins. It has no effect on the instance; you can leave it if you wish to add pins to the group later, or you can right-click the group and choose **Delete** to remove it from your instance.

If you delete a group from your instance any pins still in the group are unaffected.

### To promote a group to Top level:

- 1. Create a group of pins.

- 2. Right-click the group and choose Promote to Top level.

# **Bus Instances**

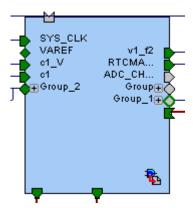

Bus Components in the Actel Core Catalog, such as CoreAHB or CoreAPB, implement an on-chip bus fabric. When these components are instantiated into your canvas they are displayed as horizontal or vertical lines. Double-click the bus interfaces of your component to edit the connections.

Figure 10 · Bus Instance in SmartDesign

# **Positioning Busses on the Canvas**

You may want to adjust the positioning and orientation of a bus on your canvas in order to organize the display of your design.

### **Rotating Busses**

Bus instances can be rotated ninety degrees (they must be horizontal or vertical). To rotate a bus instance ninety degrees left or right, right-click the black bar and choose **Shape** > **Rotate Left** (or Rotate Right).

### **Flipping Busses**

You can flip a bus along the horizontal or vertical axis. To flip a bus, right-click the black bar and choose **Shape > Flip Horizontal** (or Flip Vertical). Flipping a bus instance along an axis flips ALL the instances directly connected to the bus instance, except those that are connected to another bus instance.

# **Adding Graphic Objects**

You can document your design by adding comments and notations directly on the Canvas.

The Canvas toolbar (see figure below) enables you to add and modify decorative graphic objects, such as shapes, labels, lines, and arrows on the Canvas.

Figure 11 · Canvas Toolbar

# **Adding and Deleting Lines and Shapes**

#### To add a line or a shape:

- 1. Select the line or shape button.

- 2. Click, drag and release on the Canvas. The table below provides a description of each button.

| Button | Description |

|--------|-------------|

|        | Line        |

| . >    | Arrow       |

|        | Rectangle   |

| 0      | Ellipse     |

Note: Hold the Shift key to constrain line and arrow to 45 degree increments or constrain the proportions of the rectangle (square) or ellipse (circle).

### To change the line and fill properties:

- 1. Select the element(s), right-click it, and choose Properties.

- Select Line to modify the color, style and width of the line.

- Select Fill to modify the crosshatch and the foreground and background colors.

- 2. Click OK.

To delete a line or shape, select the object and press Delete.

# **Adding Text**

To add text, select the text tool A and click the Canvas to create a text box. To modify the text, double-click the text box and then type.

### To modify the text box properties:

- 1. Select the text box, right-click it, and choose Properties.

- Select **Text** to modify the text alignment.

- Select Line to modify the color, style and width of the line.

- Select Fill to modify the crosshatch and the foreground and background colors.

- Select **Font** to modify the font properties.

- 2. Click OK.

# **Adding Images**

# To add an image to the canvas:

- 1. Select the image button . The Open dialog box opens.

- 2. Select the image you want to add and click OK.

- 3. Select the image and place it in the desired location.

### **Rotating Elements**

Select the element(s) you want to rotate and click the appropriate rotate button. See the table below for a description of each button.

| Button   | Description         |

|----------|---------------------|

| O        | Free rotate         |

| <b>A</b> | Rotate to the left  |

| 4        | Rotate to the right |

# **Flipping Elements**

Select the element(s) you want to flip and click the appropriate flip button. See the table below for a description of each button.

| Button   | Description       |

|----------|-------------------|

| <b>4</b> | Flip vertically   |

| 4        | Flip horizontally |

# **Aligning Elements**

Select two or more elements on the Canvas and click the appropriate align button. See the table below for a description of each button.

| Button   | Description  |

|----------|--------------|

| <u> </u> | Align top    |

| 砂        | Align middle |

| <u> </u> | Align bottom |

|          | Align left   |

| 串        | Align center |

|          | Align right  |

# **Grouping Graphic Objects**

Objects on the Canvas can be grouped and ungrouped.

To group two or more elements, select the elements, right-click, and choose Grouping > Group.

To ungroup two or more elements, select the elements, right-click, and choose Grouping > Ungroup.

# **Ordering Elements (Z-order)**

Elements on the Canvas can be positioned in front or in back of each other.

To change the order of the element(s), select the element and from the right-click menu, choose **Order** and select one of the available options: **Bring to Front, Send to Back, Bring Forward,** or **Send Backward**.

# **Auto-Arranging Instances**

The Auto Arrange Instances button arranges the instances on the Canvas. You can also right-click the Canvas and choose Auto Arrange Instances from the right-click menu.

# **Locking Instance Position**

You can lock the placement of any instance on the Canvas. Right-click an instance and choose Lock Location to lock the placement. When you lock placement, the Auto Arrange Instances option has no effect on the instance.

To unlock an instance, right-click the instance and choose Unlock Location.

#### See Also

Bus instances

Auto-routing connections

# **Auto-Arrange Connections**

The Auto Arrange Connections button arranges the connections between instances. The way connections are drawn is highly dependent on the placement of the instances on the Canvas. The top-level connections are shown connected to the Top Level instance (green boxes).

Auto-arranging connections does not move instances; it places the nets between instances.

To auto-arrange your connections, right-click the canvas and choose Auto arrange connections.

Note: Select a placement for your instances that is reasonable with respect to connections before using Auto Route.

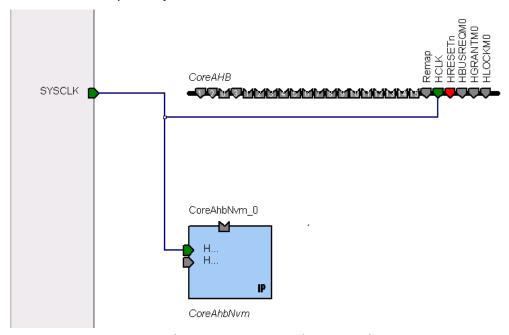

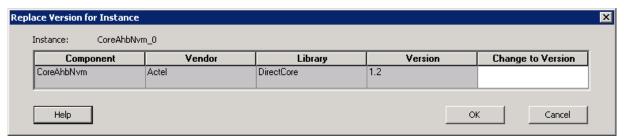

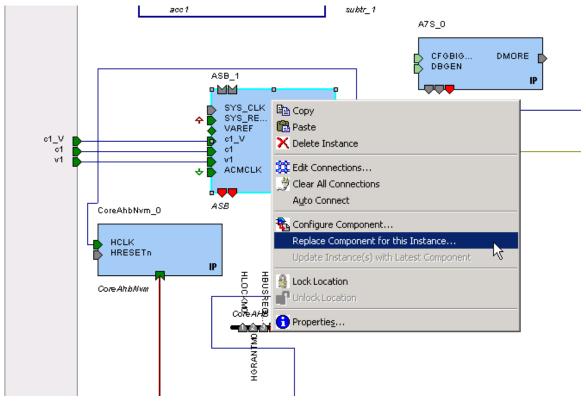

# **Replace Version for Instance**

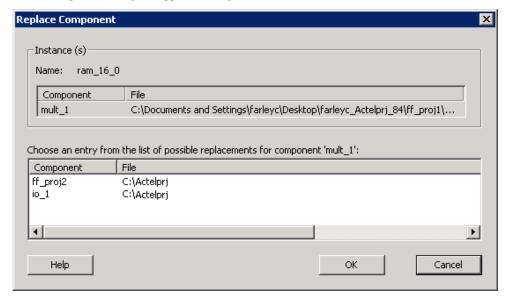

You can use the Replace Version for Instance dialog box (shown in the figure below) to restore or update version instances on your canvas without creating a new instance and losing your connections.

Figure 12 · Replace Version for Instance Dialog Box

#### To change the version of an instance:

1. From the right-click menu choose Replace Component for this Instance. The Replace Version for Instance dialog box appears.

#### Canvas View

2. Choose a new version from the Change to Version drop-down menu. Click OK.

# Slicing

Bus ports can be sliced or split using Slicing. Then the sliced ports can be connected as regular ports.

#### To create a slice:

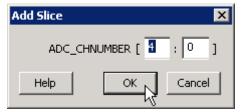

1. Select a bus port, right-click, and choose Add Slice. This brings up the Add Slice dialog box (see figure below).

Figure 13 · Add Slice Dialog Box

2. Enter the parameters for the slice and click **OK**.

Note: Once a slice is created, other bus ports or slices of compatible size can be connected to it. Overlapping slices cannot be created for IN and INOUT ports on instances or top-level OUT ports.

To remove a slice, select the slice, right-click, and choose Delete Slice.

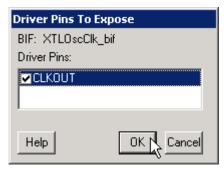

# **Exposing Driver Pins**

Pins that are contained as part of a bus interface will automatically be filtered out of the display. These ports are considered to be connected and used as part of a bus interface.

However, there are situations where you may wish to use the ports that are part of the bus interface as an individual port, in this situation you can choose to expose the pin from the bus interface.

The only ports that are allowed to be exposed are Driver Pins. Driver pins are outputs on instances or inputs on the top-level. See <u>Top-level connections</u> for more information.

### To expose a driver pin:

1. Select a bus interface port, right-click, and choose Expose Driver Pin. The Expose Driver Pin dialog box appears (as shown below).

Figure 14 · Expose Driver Pin Dialog Box

2. Click the checkbox associated with the driver pin you want to expose. Once the port is exposed it appears in the Grid and is available for individual connection.

To un-expose a driver pin, right-click the exposed port and choose Hide BIF Driver Pin.

# **Instance Properties**

Right-click a component instance and choose **Properties** to view the Name, Instance Name, and port information - name/direction-.

This dialog box is useful if you want to view the list of Port Names available in the instance from the Canvas view instead of the Grid.

### **See Also**

Grid overview

Display panel

Connection panel

# Rename Net

#### To rename a net:

- Right-click the net on the Canvas and choose Rename Net. This opens the Rename Net dialog box.

- 2. Type in a new name for the net.

Note: The system automatically assigns net names to nets if they are not explicitly specified. Once you have specified a name for a net, that name will not be over-written by the system.

#### **Automatic Names of Nets**

Nets are automatically assigned names by the tool according to the following rules:

#### In order of priority

- 1. If user named then name = user name

- 2. If net is connected to top-level port then name = port name; if connected to multiple ports then pick first port

- If the net has no driver, then name = net\_[i]

- 4. If the net has a driver, name = instanceName\_driverpinName

### Slices

For slices, name = instanceName\_driverpinName\_sliceRange; for example u0\_out1\_4to6.

#### GND and VCC Nets

The default name for GND/VCC nets is net\_GND and net\_VCC.

#### **Expanded Nets for Bus Interface Connections**

Expanded nets for bus interface connections are named busInterfaceNetName\_<i>\_driverPinName.

# Organizing Your Design on the Canvas

You may find it easier to create and navigate your SmartDesign if you organize and label the instances and busses on the Canvas.

You can show and hide nets, lock instances, rotate busses, group and ungroup pins, rename instances / groups / pins, and auto-arrange instances.

#### To organize your design:

- Click the <u>Auto-Arrange button</u> to automatically arrange instances on the Canvas. SmartDesign's auto-arrange feature optimizes instance location according to connections and instance size.

- 2. Right-click any instance and choose <u>Lock Location</u> to fix the placement. Auto-Arrange will not move any instances that are locked.

- 3. Click Auto-Arrange again to further organize any unlocked instances. Continue arranging and locking your instances until you are satisfied with the layout on the Canvas.

#### If your design becomes too cluttered:

- Hide the display of nets by de-selecting Canvas > Nets. This hides all the scalar and bus nets on your Canvas.

You can also right-click a pin and choose Show Net (or Hide Net) to show/hide individual nets. Note that

selecting a pin will make the corresponding net temporarily visible.

- Group your pins. It may help to group pins that are functionally similar, or to group pins that are already

connected or will be unused in your design.

#### To further customize your design's appearance:

- 1. Double-click the names of instances to add custom names. For example, it may be useful to rename an instance based on a value you have set in the instance: the purpose of an instance named 'array\_adder\_bus\_width\_5' is easier to remember than 'array\_adder\_0'.

- Right-click any bus and choose Shape > Rotate Left or Right to change the bus orientation (horizontal or vertical). Click and drag the bus to a new location and lock, if necessary.

# **Grid**

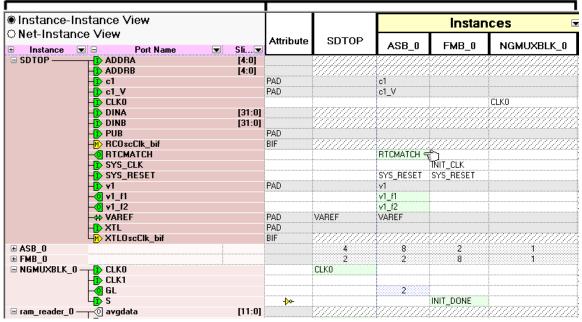

# **Grid Overview**

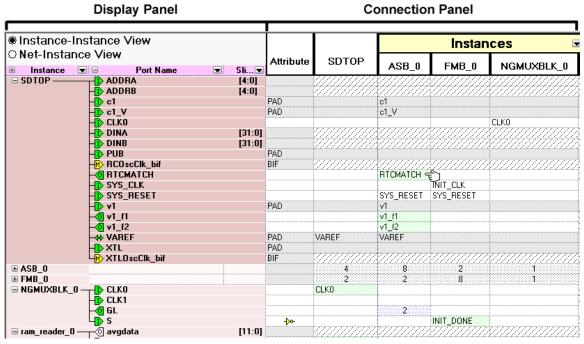

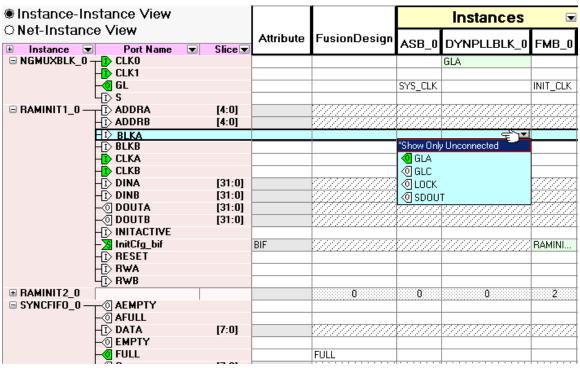

The Grid (see image below) provides a mechanism for making manual connections between building blocks in your design. The grid displays your design in a spreadsheet for sorting and filtering, enabling you to quickly access and manipulate any subset of your design.

The Grid shows block instances vertically and horizontally on the spreadsheet, such that the port rows on the spreadsheet intersect with port columns. Each intersection of rows and ports on the spreadsheet provides a connection opportunity.

The grid is divided into two panels, the Display panel and the Connection panel.

The Grid offers two different views: the <u>Instance-Instance view</u> and the <u>Net-Instance view</u>. The behavior of the two panels is the same in both views.

The default display of the Grid shows connections between all the instances in your design in an Instance-Instance view.

Actel recommends that you work with only a subset of the instances in the current design when making manual connections. This greatly reduces the information displayed in the Grid view and makes it easier to create manual connections.

Click the Maximize Work Area button to hide the other windows and show more of the Grid.

To create new Grids with just a subset of instances, select the instances between which you are making connections on the Canvas, then right-click and choose Edit Connections. A new Grid will be displayed, with only those instances and the top-level. When you are done making connections, right-click the grid view name tab and close the subset view.

To further simplify the data search in the grid and to make connections efficiently, use <u>Filtering</u>, <u>Hierarchical sort</u> in the <u>instance-instance view</u>, and the find unconnected ports (Hide All Connected Ports) features.

#### **Display Panel**

#### **Connection Panel**

Figure 15 · Grid (Instance-Instance View)

To switch to Net-Instance view, click the Net-Instance view radio button.

To reset to the default view, from the Grid menu, choose Reset Instance [Net] View to Default.

#### **See Also**

Grid - Display panel icons

Grid - Connection panel icons

36

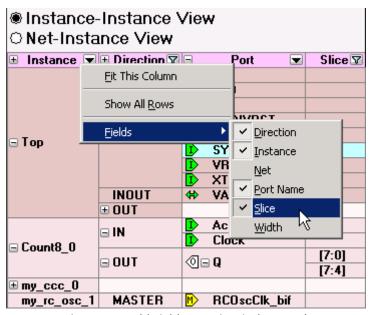

### **Display Panel**

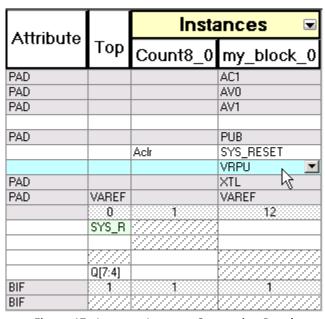

You can use the fields in the Display panel to manage content. To add or remove a field, right-click the field title (such as Instance in the image below) and from the right-click menu choose Fields. New fields appear to the right of the fields already shown. To filter the list of nets or instances in the Display panel, use the <u>Custom Filter</u>.

Figure 16 · Instance-Instance View Display Panel

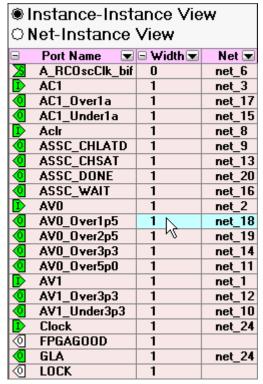

The Display panel may list the following fields:

- Instance: Displays instances in the current design.

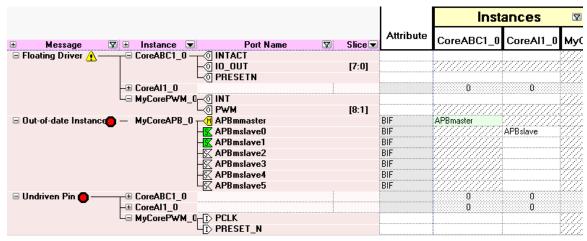

- Direction: Displays the port direction and bus interface type. Port directions are defined as IN, OUT and INOUT, bus interfaces are shown as MASTER, SLAVE, and SYSTEM.

- Port Name: Lists port names for all instances. Also displays an icon that indicates if the port is connected (green), disconnected (white), partially connected (green and white), input (I), output (O), master (yellow M), INOUT (small horizontal arrows), a system bif, or slave (S).

- Slice: Displays bit order (i.e. [7:0]) of busses and slices. Slice is not available for scalars and bus interfaces.

- Width: Displays the size of the bus for any bus port. One for a scalar and zero for a bus interface port.

- Net: Identifies the net for each instance connection.

#### Grid

Click the plus button 🖹 to expand the information listed for the selected instance or direction. Click the minus button 🖹 to collapse the information displayed for the selected instance or direction. You can <u>add and remove fields</u> to meet your needs.

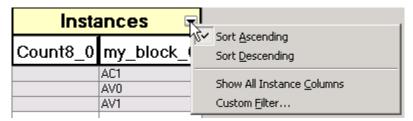

Use the filter button to filter the contents of each column. To sort the content of a column, click the Filter button and select Sort Ascending or Sort Descending. Choose Custom Filter to open the Custom Filter dialog box. You can use the Custom Filter dialog box to choose the nets, instances and slices you wish to display.

Right-click the column heading and choose Fit This Column To Data to expand (or shrink) the column to match the column width to the size of the field name.

#### **Promoting Ports to Top Level**

To automatically promote a port to top level, select the port, right-click, and choose **Promote To Top Level**. This automatically creates top-level ports of that name and connects the selected ports to them. If a port name already exists, a choice is given to either connect to the existing ports or to create a new port with a name <port name>\_<i> where i = 1...n.

Bus slices cannot be automatically promoted to top level. You must create a top level port of the bus slice width and then manually connect the bus slice to the newly created top level port.

#### **Tying Off Input Pins**

Click in the Grid Attribute column and select Invert, Tie Low, or Tie High to tie the Port.

#### **Making Driver and Bus Interface Pins Unused**

Driver or bus interface pins can be marked unused (floating/dangling) if you do not intend to use them as a driver in the design. If you mark a pin as unused the Connectivity Checker does not return Floating Driver or Unconnected Bus Interface messages on the pin.

Once a pin is explicitly marked as unused it cannot be used to drive any inputs. The unused attribute must be explicitly removed from the pin in order to connect it later. To mark a driver or bus interface pin as unused:

- Right-click the driver or bus interface pin and choose Mark as Unused

- In the Grid Attribute column, click the attribute and select Mark as Unused

### **Finding Unconnected and Partially Connected Ports**

The grid allows you to quickly find all the unconnected ports in your design. To filter the grid to only show these ports, from the SmartDesign menu, choose Grid > Hide All Connected Ports.

#### **Compatibility Rules**

- If the port selected on the row is a top-level port with a direction IN or an instance port with direction OUT, all ports of direction IN and INOUT on the instances are compatible with it.

- If the port selected on the row is a top-level port with direction OUT or instance port with direction IN or INOUT, all ports with direction IN are compatible with it.

- Bus ports or slices are only compatible with bus ports or slices of equal size.

- If there are no compatible connections between a port in the row area and an instance in the column area, the cell is shaded and unavailable.

- The pull-down menu in the cells only lists compatible ports.

#### **See Also**

Connection panel

Making connections

Filtering views

Grid - Display panel icons

### **Connection Panel**

The Connection panel (the area to the right side of the grid) shows the Attribute column, the "top" (top-level), and the Port Name to which the port is connected (if any).

Figure 17 · Instance-Instance Connection Panel

#### Grid

Use the filter button to <u>filter</u> and select which columns you wish to view, or to sort the contents of the columns in ascending or descending order.

#### **Attribute Column**

The attribute column specifies additional properties of a port on the instance. These are:

PAD - Indicates that the port is a chip-level package pin. In SmartDesign, these ports are automatically promoted to the top-level and are read only.

BIF - Indicates that the port is a Bus Interface.

GND — Tie the port to logic 0.

VCC - Tie the port to logic 1.

**Invert** -- Invert the polarity of this port. Inverting a port automatically instantiates an inverter into the generated HDL file:

- For a driver: Inverter added after pin or port.

- For a non-driver: Inverter added before pin or port.

Unused - Indicates the pin has been assigned the float attribute and is not included in the Connectivity Check.

#### <design name> Column

The <design name> column represents the top-level; the name of the column depends on the name of your design.

### **Instances Column(s)**

An instance column represents an instance that an instance-port of a row can be connected to.

#### **See Also**

Display panel

Making connections

Filtering views

Grid - Connection panel icons

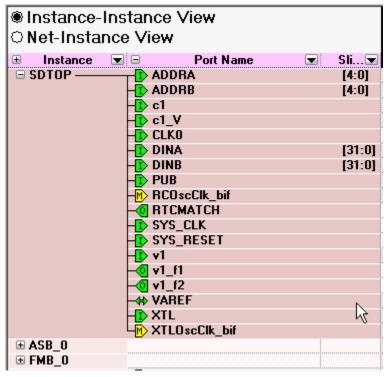

## **Instance-Instance View**

#### Instance-Instance View

The Instance-Instance view (see figure below) is divided into two panels: the <u>Display panel</u> and the <u>Connection panel</u>. By default, the Display panel shows Instance, Port Name, and Slice information.

By default, the Connection panel begins at the Attribute column, and lists instances in the design and their ports. You can show/hide any column in either panel; if you modify the view and wish to reset it, right-click the Instance-Instance View radio button in the Display panel and choose **Reset Instance View to Default**.

Figure 18 · Instance - Instance View

### Adding and Removing Fields

To add a field in the Display panel, right-click the field title (such as Direction in the image below) and from the right-click menu choose Field, and select the field you wish to add or remove. Added fields appear at the end of the list of fields.

You can add fields to view additional information about a port. Also, adding the field enables you to <u>Sort</u> your design based on fields.

Figure 19 · Add Field Menu in Display Panel

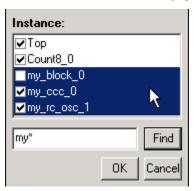

To add an instance in the Connection panel, click the drop-down arrow in Instances (as shown in the figure below), and choose **Custom Filter**. The <u>Custom Filter</u> dialog box appears. Select checkbox for the instance you wish to view, or use the Find box to search for a specific instance or range of instances.

Figure 20 · Add an Instance with Custom Filter in Connection Panel

### Sorting with Fields

The field columns inside the Grid can be used to sort the ports in your design.

The hierarchical order is defined by the order of the columns (left to right). The data within each field is sorted alphabetically. To change the hierarchical view, select a column and drag the column to the left or the right.

For example, this may be useful if you wish to see all of your INPUT ports together or if you want to see all of your 8-bit busses together. The image below shows the Display Panel sorted by Port Name.

Figure 21 · Display Panel Sorted by Port Name

### Making Connections Using the Grid

#### To make connections between ports on two instances:

- 1. Click in the intersection between the port (row) and the instance (column). SmartDesign displays a drop-down list of compatible ports from the instance on the column area.

- Select the desired port to make the connection. In the figure below, the port SYS\_RESET from the instance

Top is being connected to port Aclr in the instance Count8\_0. Note that the unconnected ports are shown in

white.

Figure 22 · Making Connections Between Two Ports on Two Instances

To disconnect an existing connection, click in the intersection between the port and the instance and choose **Disconnect**.

#### **See Also**

Connecting multiple ports (Connection panel)

Filtering views

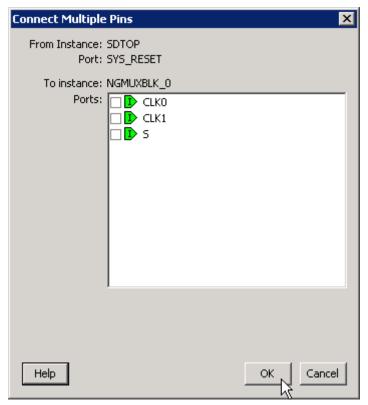

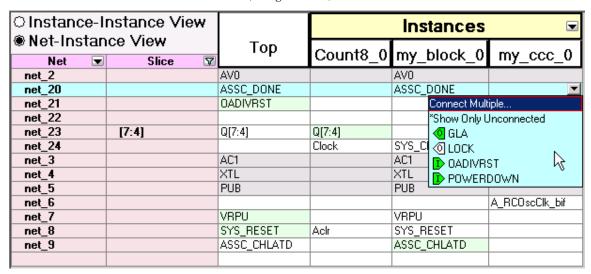

The Connect Multiple dialog box enables you to make multiple connections to a pin or net.

In the Instance to Instance view you can easily connect multiple non-driver pins from a single instance to a driver pin. To do so:

Click a cell intersection of a driver pin and you will see a drop down with Connect Multiple. Choose Connect

Multiple to open the dialog box below.

Figure 23 · Connect Multiple Pins Dialog Box - Instance to Instance

2. The dialog box lists all the compatible non-driver pins that can be connected to the selected driver pin. Click the checkbox to connect these pins to the driver pin.

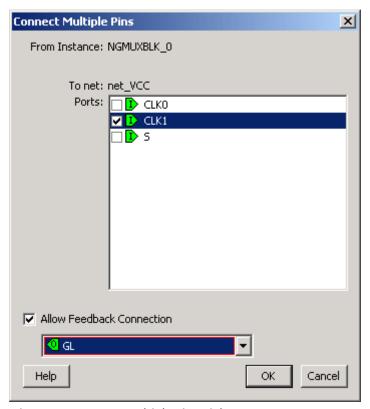

In the Net to Instance view you can easily connect multiple pins from a single instance to a net. To do so:

Click a cell intersection of an existing net and you will see a drop down with Connect Multiple. Choose

Connect Multiple to open the dialog box below. The dialog box lists all the compatible non-driver pins that can

be connected to this net.

#### Instance-Instance View

Figure 24 · Connect Multiple Pins Dialog Box - Net to Instance

- 2. Click the checkbox to connect these pins onto the net.

- 3. If the instance has driver pins available, you can click the checkbox for **Allow Feedback Connection** to select the driver pin for this net.

#### **See Also**

Filtering views

Connection panel

#### **Net-Instance View**

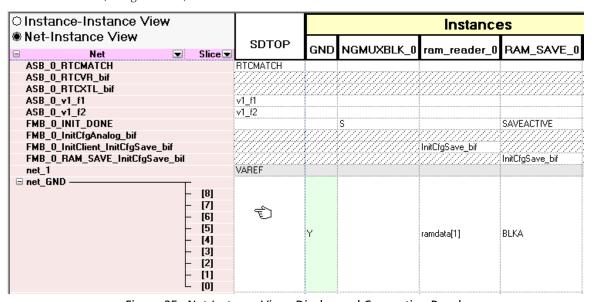

The Net-Instance view is a simplified version of the Instance-Instance view. Instead of an expandable list of every instance in your SmartDesign, the Display panel lists only the net names that are connected to an instance. This view is useful if you wish to see which nets are connected to an instance without changing your settings in the Instance-Instance view. The Display and Connection panels in the Net-Instance view behave the same in both views.

The default Display panel in Net-Instance view lists the nets in your design; the default Connection panel lists all instances (see figure below).

Figure 25  $\cdot$  Net-Instance View, Display and Connection Panels

To switch to Net-Instance view, click the Net-Instance radio button. To reset to the default view, from the Grid menu, choose Reset Net View to Default.

#### **See Also**

Connect to an existing net (Net-Instance view)

Connection panel

Display panel

Filtering views

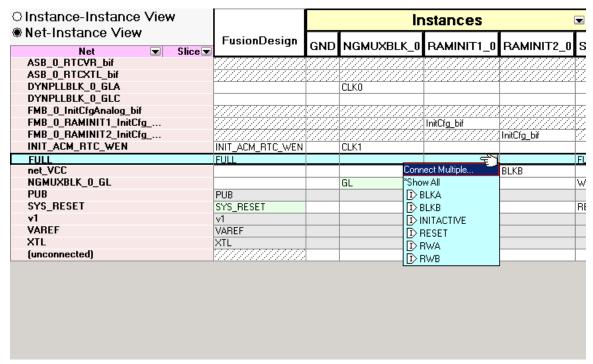

### Connect to an Existing Net (Net-Instance View)

To connect to an existing net, select the ports to be connected from the drop-down list by clicking in the cell at the intersection of the net and the instance (see figure below).

Figure 26 · Connecting to an Existing Net

Any net can have at most one driver. IN ports of the top-level or OUT ports from instances are considered drivers. If another driver is for an already driven net, the current driver will be disconnected and the new driver will be connected to the selected net.

#### **See Also**

Connection panel

Display panel

### Make New Connection (Net-Instance View)

To connect to a new net, select the ports to be connected from the drop-down list. Click the cell at the intersection of the (unconnected) net row and the instance. This creates a new net (see figure below).

Figure 27 · Making a New Connection

#### **See Also**

Connect to an existing net (Net-Instance view)

Connection panel

Display panel

### **Filtering Views**

To reduce the amount of data shown on the screen, you can display it selectively. The easiest way to hide an entry is to right-click the cell and choose **Hide Selection**. To show the entry again, you can right-click at the top and choose **Show All Rows**.

For more control over the data display, use the Custom Filter available from the button on the header row.

The Grid enables you to filter all instances within the design, as well as their direction, ports and slices. The example below filters by instance, but you can filter any column in the Display panel with the same procedure.

#### To filter the contents in the grid:

1. Use the filter button and choose **Custom Filter** to bring up the filter box (see figure below).

Figure 28 · Custom Filter Box in the Display Panel

- 2. From the filter box, you can find and select multiple values. In the image above, the Find field has highlighted all the instances that start with 'my', \* is a wildcard. You must click inside the checkbox to select, or de-select, highlighted values.

- 3. Click OK to commit your changes.

#### To hide data in the grid:

Select the rows you want to hide, right-click and choose Hide Selection.

#### To restore grid data:

From the SmartDesign menu, choose Connectivity View > Reset Instance View to Default.

#### **See Also**

Connection panel

Display panel

Making connections

# **Schematic View**

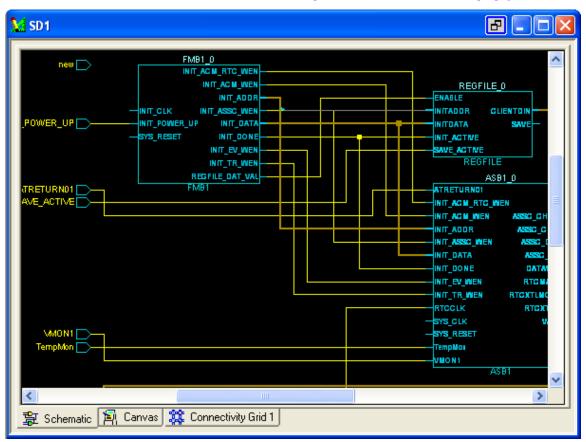

### **Schematic Overview**

The Schematic view (see figure below) displays a detailed connection diagram for all instances, ports, and pins in the current design with lines representing nets. This view is the closest representation to the exported HDL.

You can zoom the contents in the Schematic view or split the Schematic view into multiple pages.

Figure 29 · Schematic View

### **Page Splitting**

By default, the Schematic view displays large designs using multiple pages. Page splitting enables you to quickly compute and display the schematic. You can turn off page splitting to view your entire design on a single page. For larger designs, when this option is turned off, it may take SmartDesign longer to display the schematic.

To turn page splitting on or off, from the SmartDesign menu, choose Schematic View > Allow Page Splitting.

To navigate to the next page in a design, from the SmartDesign menu, choose Schematic View > Go to Next Page.

To navigate to the previous page, from the SmartDesign menu, choose Schematic View> Go to Previous Page.

To navigate to the first page, from the SmartDesign menu, choose Schematic View > Go to First Page.

To navigate to the last page, from the SmartDesign menu, choose Schematic View> Go to Last Page.

## **Zooming**

The zoom tool in the Schematic View enables you to zoom fit the contents of your design within the window.

To zoom fit the design, click and drag to the bottom left corner of the window.

Zoom in and out of your schematic using the zoom icons on your toolbar.

# **Creating a SmartDesign**

### Adding Components and Modules (Instantiating)

SmartDesign components, SmartGen cores, IP cores, and HDL modules are displayed in the <u>Hierarchy</u>, <u>Files</u>, and <u>Find output window</u>.

#### To add a component, do either of the following:

- Select the component and drag it to the <u>Canvas</u> or <u>Grid</u>.

- Select a component, right-click, and choose Instantiate in SmartDesign < name >.

The component is instantiated in the design.

SmartDesign creates a default instance name. To rename the instance, double-click the instance name in the canvas.

Note: HDL modules with syntax errors cannot be instantiated in SmartDesign. However, since SmartDesign requires only the port definitions, the logic causing syntax errors can be temporarily commented out to allow instantiation of the component.

# Adding a SmartDesign Component in a Higher-level Design (Instantiating)

SmartDesign components can be instantiated into another SmartDesign component.

Once a SmartDesign is generated, the exported netlist can be instantiated into HDL like any other HDL module.

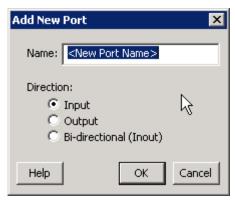

# Adding Top Level Ports / Renaming External Pads in a SmartDesign

You can add ports to, and/or rename ports in your SmartDesign.

#### To add ports:

From the SmartDesign menu, choose Logic > Add port. The Add Port dialog box appears (as shown below).

#### Creating a SmartDesign

Figure 30 · Add New Port Dialog Box

- 2. Specify the name of the port you wish to add. You can specify a bus port by indicating the bus width directly into the name using brackets [], such as mybus[3:0].

- 3. Select the direction of the port.

To remove a port from the top level, select the port in the Grid, right-click and choose Delete Top Level Port.

To rename a top-level port, right-click the top-level non-pad port and choose **Modify Top Level Port**. You can rename the port, change the bus width (if the port is a bus), and change the port direction.

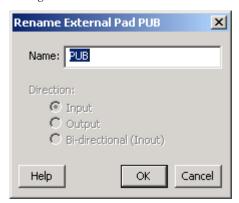

#### To rename an external pad:

1. Right-click a pad in the top-level port and select **Rename External Pad**. The Rename External Pad dialog box appears, as shown in the figure below.

Figure 31 · Rename External Pad Dialog Box

2. Enter the new name for the external pad and click OK.

#### **See Also**

Top level connections

# **Connecting Instances**

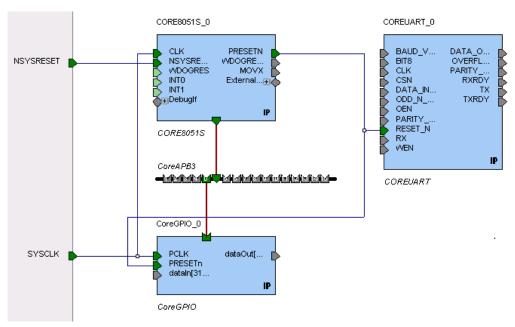

#### **Automatic Connections**

Using automatic connections (as shown in the figure below) enables the software to connect your design efficiently, reducing time required for manual connections and the possibility of introducing errors.

To auto connect the bus interfaces in your design, right-click the design Canvas and select Auto Connect, click the

Auto Connect button; or from the SmartDesign menu, choose Auto Connect.

You can select individual pins or groups on the Canvas to auto-connect. Select the pins, right-click and choose Auto Connect.

SmartDesign searches your design and connects all compatible bus interfaces.

SmartDesign will also form known connections for any SoC systems such as the processor CLK and RESET signals.

If there are multiple potential interfaces for a particular bus interface, Auto Connect will not attempt to make a connection; you must connect manually. You can use the <u>Canvas</u>, <u>Grid</u> or the <u>Find Compatible Bus Interface</u> dialog box to make the manual connection.

Figure 32 · Auto-Connected IP Cores

### **Manual Connections**

To make manual connections between to pins on the Canvas, select both pins (use CTRL + click), right-click either pin and choose **Connect**. If the pins cannot be legally connected the connection will fail.

### **Deleting Connections**

To delete a net connection on the Canvas, click to select the net and press the Delete key, or right-click and choose **Delete**.

To remove all connections from one or more instances on the Canvas, select the instances on the Canvas, right-click and choose **Clear all Connections**. This disconnects all connections that can be disconnected legally.

You can also select one or more rows in the Grid and choose **Remove Connections from Selected Ports** from the right-click menu to remove the connects for a group of Ports.

If you click in a cell displaying a connection, selecting Disconnect from the drop down removes just that connection.

Certain connections to ports with PAD properties cannot be disconnected. PAD ports must be connected to a design's top level port. PAD ports will eventually be assigned to a package pin. In SmartDesign, these ports are automatically promoted to the top level and cannot be modified or disconnected.

### **Top-Level Connections**

Connections between instances of your design normally require an OUTPUT (Driver Pin) on one instance to one or more INPUT(s) on other instances. This is the basic connection rule that is applied when connecting.

However, directions of ports at the top level are specified from an external viewpoint of that module. For example, an INPUT on the top level is actually sending ('driving') signals to instances of components in your design. An OUTPUT on the top level is receiving ('sinking') data from a Driver Pin on an internal component instance in your SmartDesign design.

The implied direction is essentially reversed at the top-level. Making connections from an OUTPUT of a component instance to an OUTPUT of top-level is legal.

This same concept applies for bus interfaces; with normal instance to instance connections, a MASTER drives a SLAVE interface. However, they go through a similar reversal on the top-level.

### **Bus Interfaces**

### **About Bus Interfaces**

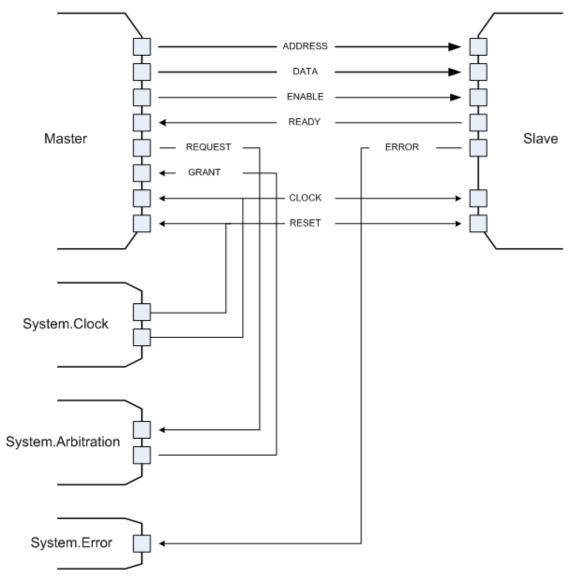

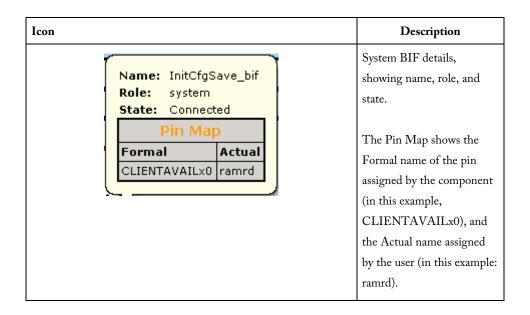

A bus interface is a standard mechanism for specifying the interconnect rules between components or instances in a design. A bus definition consists of the roles, signals, and rules that define that bus type. A bus interface is the instantiation of that bus definition onto a component or instance.

The available roles of a bus definition are master, slave, and system.

A master is the bus interface that initiates a transaction (such as read or write) on a bus.

A slave is the bus interface that terminates/consumes a transaction initiated by a master interface.

A system is the bus interface that does not have a simple input/output relationship on both master/slave. This could include signals that only drive the master interface, or only drive the slave interface, or drive both the master and slave interfaces. A bus definition can have zero or more system roles. Each system role is further defined by a group name. For example, you may have a system role for your arbitration logic, and another for your clock and reset signals.

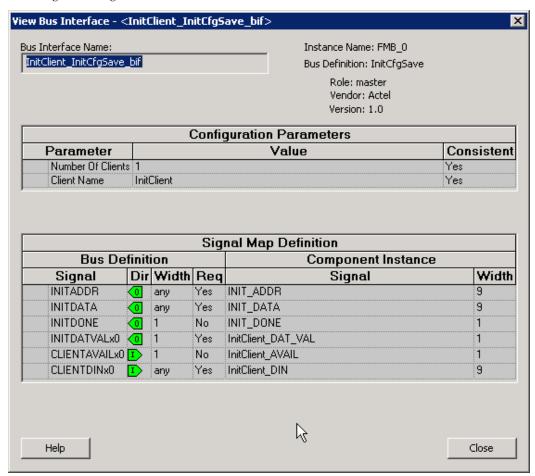

Mirror roles are for bus interfaces that are on a bus core, such as CoreAHB or CoreAPB. They are equivalent in signal definition to their respective non-mirror version except that the signal directions are reversed.