# PolarFire<sup>®</sup> FPGA and PolarFire SoC FPGA System Services

# Introduction

Microchip's PolarFire FPGAs are the fifth-generation family of non-volatile FPGA devices, built on state-of-the-art 28 nm non-volatile process technology. PolarFire FPGAs deliver the lowest power at mid-range densities. PolarFire FPGAs lower the cost of mid-range FPGAs by integrating the industry's lowest power FPGA fabric, lowest power 12.7 Gbps transceiver lane, built-in low power dual PCI Express Gen2 (EP/RP), and, on select data security (S) devices, an integrated low-power crypto co-processor.

Microchip's PolarFire SoC FPGAs are the fifth-generation family of non-volatile SoC FPGA devices, built on state-ofthe-art 28 nm non-volatile process technology. The PolarFire SoC family offers industry's first RISC-V based SoC FPGAs capable of running Linux. It combines a powerful 64-bit 5x core RISC-V Microprocessor Subsystem (MSS), based on SiFive's U54-MC family, with the PolarFire FPGA fabric in a single device.

Both PolarFire FPGA and PolarFire SoC FPGA devices include a System Controller, which accepts and responds to system service requests from the user. System services range from requesting the device and design specific information to requesting an IAP or auto-update. The following table lists the categories of system services available in PolarFire FPGA and PolarFire SoC FPGA.

| System Services                           | PolarFire FPGA (MPF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PolarFire SoC FPGA (MPFS) |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Device and Design Information<br>Services | <ul> <li>Image: A start of the start of</li></ul> | ✓                         |

| Design Programming Services               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                         |

| Data Security Services                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                         |

| Fabric Services                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                         |

| Debug Services                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                         |

| Passcode Services                         | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                         |

| SPI Flash Memory Read Service             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                         |

#### Table 1. System Services

### References

- For information about PolarFire FPGA CoreSysServices\_PF driver and example SoftConsole project, see *Firmware Catalog*. Firmware Catalog is available in the Libero SoC installation package.

- For information about PolarFire SoC FPGA mss\_system\_services driver and example SoftConsole project, see GitHub.

- For information about PolarFire FPGA system services SgCore and its configuration, see UG0848: PolarFire System Services User Guide.

- For information about PolarFire FPGA system services simulation , see PolarFire System Services Simulation User Guide.

- For information about device serial number, see PolarFire FPGA and PolarFire SoC FPGA Security User Guide.

- For information about eNVM parameters, see PolarFire SoC Advance Datasheet.

# **Table of Contents**

| Intro | oductio | n                                                          |     |

|-------|---------|------------------------------------------------------------|-----|

|       | 1.      | References                                                 | 1   |

| 1.    | Polar   | ire FPGA System Services                                   | 4   |

| 2.    | Polar   | Fire SoC FPGA System Services                              | . 5 |

| 3.    | Syste   | n Service Request                                          | 6   |

| 4.    | Devic   | e and Design Information Services                          | . 7 |

|       | 4.1.    | Serial Number Service                                      | . 7 |

|       | 4.2.    | USERCODE Service                                           | . 8 |

|       | 4.3.    | Design Information Service                                 | . 8 |

|       | 4.4.    | Device Certificate Service                                 |     |

|       | 4.5.    | Read Digests Service                                       |     |

|       | 4.6.    | Query Security Service                                     |     |

|       | 4.7.    | Read Debug Information Service                             |     |

|       | 4.8.    | Read eNVM Parameters Service (For PolarFire SoC FPGA Only) | 16  |

| 5.    | Desig   | n Programming Services                                     | 18  |

|       | 5.1.    | Bitstream Authentication Service                           | 18  |

|       | 5.2.    | IAP Image Authentication Service                           | 19  |

| 6.    | Data \$ | Security Services                                          | 20  |

|       | 6.1.    | Digital Signature Service                                  | 21  |

|       | 6.2.    | Secure NVM (sNVM) Services                                 | 21  |

|       | 6.3.    | PUF Emulation Service                                      | 24  |

|       | 6.4.    | Nonce Service                                              | 25  |

| 7.    | Fabric  | Services                                                   | 27  |

|       | 7.1.    | Digest Check Service                                       | 27  |

|       | 7.2.    | In-Application Programming (IAP) Service                   | 29  |

|       | 7.3.    | Auto Update Service                                        | 31  |

| 8.    | Debuę   | services (For PolarFire SoC FPGA only)                     | 32  |

|       | 8.1.    | Probe Read Debug Service                                   | 33  |

|       | 8.2.    | Probe Write Debug Service                                  | 34  |

|       | 8.3.    | Live Probe Debug Service                                   | 34  |

|       | 8.4.    | MEM Select Debug Service                                   | 35  |

|       | 8.5.    | MEM Read Debug Service                                     | 36  |

|       | 8.6.    | MEM Write Debug Service                                    | 37  |

|       | 8.7.    | APB Read Debug Service                                     |     |

|       | 8.8.    | APB Write Debug Service                                    |     |

|       | 8.9.    | Debug Snapshot Service                                     |     |

|       | 8.10.   | Terminate Debug Service                                    | 39  |

| 9.    | Passo   | ode Services (For PolarFire SoC FPGA Only)                 | 40  |

|       | 9.1.    | Generate OTP Service                                       | 40  |

|      | 9.2.<br>9.3.<br>9.4.                  | Match OTP Service.       2         Unlock Debug Passcode Service.       2         One Way Passcode Service.       2 | 11 |  |  |

|------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|----|--|--|

| 10.  |                                       | ash Memory Read Service (For PolarFire SoC FPGA Only)                                                               |    |  |  |

| 11.  | Using                                 | System Services in PolarFire FPGA                                                                                   | 15 |  |  |

| 12.  | Using                                 | System Services in PolarFire SoC FPGA                                                                               | 16 |  |  |

| 13.  | Revisi                                | on History                                                                                                          | 17 |  |  |

| The  | Microo                                | chip Website                                                                                                        | 18 |  |  |

| Pro  | Product Change Notification Service48 |                                                                                                                     |    |  |  |

| Cus  | Customer Support                      |                                                                                                                     |    |  |  |

| Mic  | rochip l                              | Devices Code Protection Feature                                                                                     | 18 |  |  |

| Leg  | al Notio                              | ce                                                                                                                  | 19 |  |  |

| Trac | Trademarks                            |                                                                                                                     |    |  |  |

| Qua  | Quality Management System             |                                                                                                                     |    |  |  |

| Woi  | Vorldwide Sales and Service           |                                                                                                                     |    |  |  |

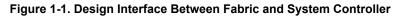

# 1. PolarFire FPGA System Services

In PolarFire FPGA, system services are system controller actions initiated by the fabric user logic through the system controller's system service interface (SSI). For initiating the system services, the fabric user logic requires the PF\_SYSTEM\_SERVICES SgCore IP available in the Libero catalog. The PF\_SYSTEM\_SERVICES SgCore IP provides an easy user interface to run the system services. The following figure shows the design interface between fabric and System Controller.

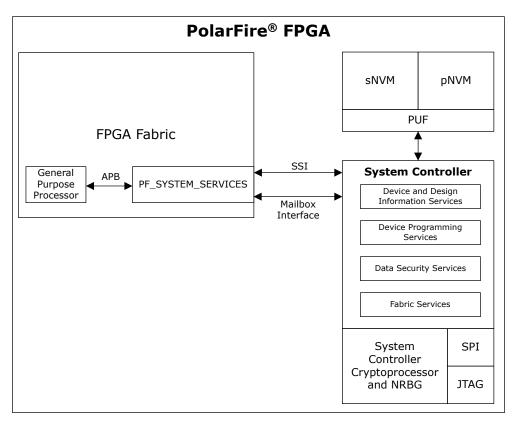

# 2. PolarFire SoC FPGA System Services

In PolarFire SoC FPGA, system services are System Controller actions initiated by PolarFire SoC MSS. MSS communicates with the System Controller over System Controller Bridge (SCB) bus. The following figure shows the design interface between MSS and System Controller.

# 3. System Service Request

In both PolarFire FPGA and PolarFire SoC FPGA, the system service request is initiated by passing a 16-bit system service descriptor to the System Controller. The lower seven bits of the descriptor specify the service to be performed and the upper nine bits specify mailbox address offset. There is a 2 Kbytes internal mailbox RAM memory space. This space is used for passing the input data and storing the service request output that is returned by the System controller. The mailbox address specifies the service-specific data structure that is used for any additional inputs to or outputs from the service. On completion of service, the System Controller writes a status code indicating the successful completion of the system service or an error code. The following table lists the system service request descriptor bits. For information about mailbox read/write communication from Fabric, see UG0848 PolarFire System Services User Guide.

| System Service Descriptor<br>Bit Field | Value          | Description                                                                                                                                      |

|----------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:7                                   | MBOXADDR[10:2] | Specifies the address offset in mailbox RAM to access minimum four bytes of memory. Mailbox addresses are specified using a word offset (0-511). |

| 6:0                                    | SERVICECMD     | Service command for System Controller to execute the request.                                                                                    |

# 4. Device and Design Information Services

These services provide return information about the device and current user design. The requested information is copied to a location whose address is included in the service descriptor. The size of the data returned is service dependent. The following table lists all the device and design information system services with their command values, description, and return status code.

| System Service<br>Name                                              | SERVICECMD in<br>Hexadecimal | Description                                                                                                                                              | Return Status Code                                                                                                                                 |

|---------------------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Number<br>Service                                            | 00                           | Fetches the 128-bit device serial number.                                                                                                                | 0: Success                                                                                                                                         |

| USERCODE Service                                                    | 01                           | Fetches the 32-bit USERCODE/<br>Silicon signature.                                                                                                       |                                                                                                                                                    |

| Design Information<br>Service                                       | 02                           | Returns design information<br>including 256-bit user defined<br>design ID, 16-bit design version,<br>and 16-bit design back-level<br>protection value.   |                                                                                                                                                    |

| Device Certificate<br>Service                                       | 03                           | Fetches the device's Supply Chain<br>Assurance Certificate from pNVM.                                                                                    | 0: Success     (Certificate is valid and     consistent with device.)                                                                              |

|                                                                     |                              |                                                                                                                                                          | <ul> <li>1: Device mismatch<br/>(Public key or factory serial<br/>number do not match<br/>device.)</li> </ul>                                      |

|                                                                     |                              |                                                                                                                                                          | <ul> <li>2: Certificate signature is<br/>invalid</li> <li>3: PUF or storage failure</li> </ul>                                                     |

| Read Digests Service                                                | 04                           | Returns the stored digests for the device.                                                                                                               | 0: Success                                                                                                                                         |

| Query Security<br>Service                                           | 05                           | Fetches non-volatile states of user security locks.                                                                                                      |                                                                                                                                                    |

| Read Debug<br>Information Service                                   | 06                           | Fetches debug information on<br>programming, user initialization,<br>device programming cycle count,<br>and In-application programming<br>(IAP) actions. |                                                                                                                                                    |

| Read eNVM<br>Parameters Service<br>(For PolarFire SoC<br>FPGA Only) | 07                           | Retrieves all parameters needed<br>for eNVM operation and<br>programming.                                                                                | <ul> <li>0: Success</li> <li>1: eNVM page mismatch<br/>error<br/>(Page digest mismatches.<br/>Parameter values are still<br/>returned.)</li> </ul> |

Table 4-1. Device and Design Information System Services

## 4.1 Serial Number Service

Fetches the 128-bit device serial number.

#### Table 4-2. Serial Number Service Request

| System Service<br>Descriptor Bit Field | Value          | Description                     |

|----------------------------------------|----------------|---------------------------------|

| 15:7                                   | MBOXADDR[10:2] | Mailbox address. See Table 4-3. |

| 6:0                                    | 00H            | Serial number service command   |

The following table lists the Serial Number Service mailbox format.

#### Table 4-3. Serial Number Service Mailbox Format

| Offset | Length (bytes) | Parameter | Direction | Description          |

|--------|----------------|-----------|-----------|----------------------|

| 0      | 16             | DSN       | Output    | Device Serial Number |

For more information about Device Serial Number, see PolarFire FPGA and PolarFire SoC FPGA Security User Guide.

## 4.2 USERCODE Service

Fetches the 32-bit USERCODE/Silicon signature.

#### Table 4-4. USERCODE Service Request

| System Service<br>Descriptor Bit Field | Value          | Description                     |

|----------------------------------------|----------------|---------------------------------|

| 15:7                                   | MBOXADDR[10:2] | Mailbox address. See Table 4-5. |

| 6:0                                    | 01H            | USERCODE service command        |

The following table lists the USERCODE Service mailbox format.

### Table 4-5. USERCODE Service Mailbox Format

| Offset | Length (bytes) | Parameter | Direction | Description     |

|--------|----------------|-----------|-----------|-----------------|

| 0      | 4              | USERCODE  | Output    | Device USERCODE |

### 4.3 Design Information Service

Returns design information including 256-bit user defined design ID, 16-bit design version, and 16-bit design back-level protection value.

#### Table 4-6. Design Information Service Request

| System Service<br>Descriptor Bit Field | Value          | Description                        |

|----------------------------------------|----------------|------------------------------------|

| 15:7                                   | MBOXADDR[10:2] | Mailbox address. See Table 4-7.    |

| 6:0                                    | 02H            | Design Information service command |

The following table lists the Design Information Service mailbox format.

| Offset | Length<br>(bytes) | Parameter | Direction | Description                    |

|--------|-------------------|-----------|-----------|--------------------------------|

| 0      | 32                | DESIGNID  | Output    | 256-bit user-defined design ID |

| 32     | 2                 | DESIGNVER | Output    | 16-bit design version          |

| 34     | 2                 | BACKLEVEL | Output    | 16-bit design back-level       |

Table 4-7. Design Information Service Mailbox Format

## 4.4 Device Certificate Service

Fetches the device's Supply Chain Assurance Certificate from pNVM. The certificate data is stored as a 1024-bit entity but the actual certificate size may be smaller. Any excess bytes should be discarded by the user.

The device validates the certificate by checking its signature using the Microchip public key, MCPK. In addition:

- The certificate DSN is checked against the device's serial number (DSN).

- The certificate public key is checked by recalculating the value using factory key and comparing against the certificate.

In the event of an error, the certificate content is still returned for inspection.

#### Table 4-8. Design Certificate Service Request

| System Service<br>Descriptor Bit Field | Value          | Description                         |

|----------------------------------------|----------------|-------------------------------------|

| 15:7                                   | MBOXADDR[10:2] | Mailbox address. See Table 4-9.     |

| 6:0                                    | 03H            | Design Certificate service command. |

The following table lists the Design Certificate Service mailbox format.

#### Table 4-9. Design Certificate Mailbox Format

| Offset | Length (bytes) | Parameter   | Direction | Description        |

|--------|----------------|-------------|-----------|--------------------|

| 0      | 1024           | CERTIFICATE | Output    | Device Certificate |

## 4.5 Read Digests Service

Returns the stored digests for the device. The following table lists the returned digests format.

#### Table 4-10. Read Digest Service Request

| System Service<br>Descriptor Bit Field | Value          | Description                      |

|----------------------------------------|----------------|----------------------------------|

| 15:7                                   | MBOXADDR[10:2] | Mailbox address. See Table 4-11. |

| 6:0                                    | 04H            | Read Digest service command.     |

The following table lists the Read Digest Service mailbox format.

#### Table 4-11. Read Digests Service Mailbox Format

| Offset | Length (bytes)                    | Parameter | Direction | Description  |

|--------|-----------------------------------|-----------|-----------|--------------|

| 0      | 416 (For PolarFire FPGA only)     | DIGESTS   | Output    | Digest Array |

|        | 576 (For PolarFire SoC FPGA only) | -         |           |              |

| Offset (byte) | Size (bytes) | Value      | Description                                                                            |

|---------------|--------------|------------|----------------------------------------------------------------------------------------|

| 0             | 32           | FD         | Fabric digest                                                                          |

| 32            | 32           | CCDIGEST   | Fabric configuration data digest                                                       |

| 64            | 32           | SNVMDIGEST | sNVM ROM pages digest                                                                  |

| 96            | 32           | ULDIGEST   | User security segment digest                                                           |

| 128           | 32           | UKDIGEST0  | Digest of user key segment containing SRAM-PUF data                                    |

| 160           | 32           | UKDIGEST1  | Digest of user key segment containing KUP (User EC key)                                |

| 192           | 32           | UKDIGEST2  | Digest of user key segment containing UPK1                                             |

| 224           | 32           | UKDIGEST3  | Digest of user key segment containing UEK1                                             |

| 256           | 32           | UKDIGEST4  | Digest of user key segment containing DPK                                              |

| 288           | 32           | UKDIGEST5  | Digest of user key segment containing UPK2                                             |

| 320           | 32           | UKDIGEST6  | Digest of user key segment containing UEK2                                             |

| 352           | 32           | UPDIGEST   | Digest of permanent lock security segments                                             |

| 384           | 32           | FDIGEST    | Digest of factory lock segment, factory key segment in pNVM, and System Controller ROM |

| 416           | 32           | UKDIGEST7  | User Key digest 7 (For PolarFire SoC FPGA only)                                        |

| 448           | 32           | ENVMDIGEST | ENVM Digest (For PolarFire SoC FPGA only)                                              |

| 480           | 32           | UKDIGEST8  | UKDIGEST8 for MSS Boot Information (For PolarFire SoC FPGA only)                       |

| 512           | 32           | UKDIGEST9  | SNVM_RW_ACCESS_MAP Digest (For PolarFire SoC FPGA only)                                |

| 544           | 32           | UKDIGEST10 | SBIC revocation digest (For PolarFire SoC FPGA only)                                   |

### Table 4-12. Returned Digests Format

# 4.6 Query Security Service

Fetches non-volatile states of user security locks. The following table lists the description of returned LOCKS array.

### Table 4-13. Query Security Service Request

| System Service<br>Descriptor Bit Field | Value          | Description                      |

|----------------------------------------|----------------|----------------------------------|

| 15:7                                   | MBOXADDR[10:2] | Mailbox address. See Table 4-14. |

| 6:0                                    | 05H            | Query Security service command   |

The following table lists the Query Security Service mailbox format.

### Table 4-14. Query Security Service Mailbox Format

| Offset | Length (bytes)                   | Parameter | Direction | Description |

|--------|----------------------------------|-----------|-----------|-------------|

| 0      | 9 (For PolarFire FPGA only)      | Locks     | Output    | Lock Array  |

|        | 33 (For PolarFire SoC FPGA only) |           |           |             |

| Byte | Bit | Lock               | Description                                   |

|------|-----|--------------------|-----------------------------------------------|

| 0    | 0   | UL DEBUG           | Debug instructions disable                    |

| 0    | 1   | UL_SNVM_DEBUG      | sNVM debug disable                            |

| 0    | 2   | UL LIVEPROBE       | Live probes disable                           |

| 0    | 3   | UL_UJTAG           | User JTAG interface disable                   |

| 0    | 4   | UL_JTAG_BS         | JTAG boundary scan disable                    |

| 0    | 5   | UL_TVS_MONITOR     | External access to System TVS monitor disable |

| 0    | 6   | UL_JTAG_MONITOR    | JTAG fabric monitor enable                    |

| 0    | 7   | UL JTAG            | JTAG TAP disable                              |

| 1    | 0   | UL_PLAINTEXT       | Plaintext passcode unlock disable             |

| 1    | 1   | UL_FAB_PROTECT     | Fabric erase/write disable                    |

| 1    | 2   | UL_EXT_DIGEST      | External digest check disable                 |

| 1    | 3   | UL VERSION         | Replay protection enable                      |

| 1    | 4   | UL FACT UNLOCK     | Factory test disable                          |

| 1    | 5   | UL IAP             | IAP disable                                   |

| 1    | 6   | UL_EXT_ZEROIZE     | External zeroization disable                  |

| 1    | 7   | UL_SPI_SLAVE       | SPI port disable                              |

| 2    | 0   | UL_USL             | UFS UL segment protect                        |

| 2    | 1   | UL_BS_AUTHENTICATE | External bitstream authentication disable     |

| 2    | 2   | UL_BS_PROGRAM      | External bitstream program mode disable       |

| 2    | 3   | UL_BS_VERIFY       | External bitstream verify mode disable        |

| 2    | 4   | UL_BITS_KEYMD[0]   | Bitstream key mode disable                    |

| 2    | 5   | UL_BITS_KEYMD[1]   | Bitstream key mode disable                    |

| 2    | 6   | UL_BITS_KEYMD[2]   | Bitstream key mode disable                    |

| 2    | 7   | UL_BITS_KEYMD[3]   | Bitstream key mode disable                    |

| 3    | 0   | UL_BITS_KEYMD[4]   | Bitstream key mode disable                    |

| 3    | 1   | UL_BITS_KEYMD[5]   | Bitstream key mode disable                    |

| 3    | 2   | UL_BITS_KEYMD[6]   | Bitstream key mode disable                    |

| 3    | 3   | UL_BITS_KEYMD[7]   | Bitstream key mode disable                    |

| 3    | 4   | UL_BITS_KEYMD[8]   | Bitstream key mode disable                    |

| 3    | 5   | UL_BITS_KEYMD[9]   | Bitstream key mode disable                    |

| 3    | 6   | UL_BITS_KEYMD[10]  | Bitstream key mode disable                    |

| 3    | 7   | UL_BITS_KEYMD[11]  | Bitstream key mode disable                    |

| 4    | 0   | UL_BITS_KEYMD[12]  | Bitstream key mode disable                    |

| 4    | 1   | UL_BITS_KEYMD[13]  | Bitstream key mode disable                    |

| 4    | 2   | UL_BITS_KEYMD[14]  | Bitstream key mode disable                    |

|      |     |                    |                                               |

## Table 4-15. Returned LOCKS Array

| con  | continued |                   |                                                                     |  |

|------|-----------|-------------------|---------------------------------------------------------------------|--|

| Byte | Bit       | Lock              | Description                                                         |  |

| 4    | 3         | UL_BITS_KEYMD[15] | Bitstream key mode disable                                          |  |

| 4    | 4         | UL_KEYMD[0]       | Global key mode disable                                             |  |

| 4    | 5         | UL_KEYMD[1]       | Global key mode disable                                             |  |

| 4    | 6         | UL_KEYMD[2]       | Global key mode disable                                             |  |

| 4    | 7         | UL_KEYMD[3]       | Global key mode disable                                             |  |

| 5    | 0         | UL_KEYMD[4]       | Global key mode disable                                             |  |

| 5    | 1         | UL_KEYMD[5]       | Global key mode disable                                             |  |

| 5    | 2         | UL_KEYMD[6]       | Global key mode disable                                             |  |

| 5    | 3         | UL_KEYMD[7]       | Global key mode disable                                             |  |

| 5    | 4         | UL_KEYMD[8]       | Global key mode disable                                             |  |

| 5    | 5         | UL_KEYMD[9]       | Global key mode disable                                             |  |

| 5    | 6         | UL_KEYMD[10]      | Global key mode disable                                             |  |

| 5    | 7         | UL_KEYMD[11]      | Global key mode disable                                             |  |

| 6    | 0         | UL_KEYMD[12]      | Global key mode disable                                             |  |

| 6    | 1         | UL_KEYMD[13]      | Global key mode disable                                             |  |

| 6    | 2         | UL_KEYMD[14]      | Global key mode disable                                             |  |

| 6    | 3         | UL_KEYMD[15]      | Global key mode disable                                             |  |

| 6    | 4         | UL_SNVM_PROTECT   | sNVM bitstream write protection enable                              |  |

| 6    | 5         | UL_EXT_CHALLENGE  | CHALLENGE instruction disable                                       |  |

| 6    | 6         | UL_UEK_PROTECT    | UEK overwrite protection                                            |  |

| 6    | 7         | UL_HWM            | High Water Mark Reset disable (For PolarFire SoC FPGA only)         |  |

| 7    | 0         | UL_ENVM_PROTECT   | Disable bitstream programming of eNVM (For PolarFire SoC FPGA only) |  |

| 7    | 1         | UL_USER_KEY       | User Key1 write protect                                             |  |

| 7    | 2         | UL_USER_KEY2      | User Key2 write protect                                             |  |

| 7    | 3         | UP_FACTORY        | Permanent factory test disable                                      |  |

| 7    | 4         | UP_DEBUG          | Permanent debug disable                                             |  |

| 7    | 5         | UP_FABRIC         | Permanent fabric write protect                                      |  |

| 7    | 6         | UP_UPK1           | Permanent disable of UPK1                                           |  |

| 7    | 7         | UP_UPK2           | Permanent disable of UPK2                                           |  |

| 8    | 0         | UP_DPK            | Permanent disable of DPK                                            |  |

| 8    | 1         | UP_PROTECT        | Write disable for UPERM segment                                     |  |

| 9:11 | _         | RESERVED          | Reserved                                                            |  |

| 12   | 0         | UATHENA_ENA       | User F5200 enable (For PolarFire SoC FPGA only)                     |  |

| 12   | 1:2       | UATHENA_MODE      | User F5200 mode (For PolarFire SoC FPGA only)                       |  |

| continue | continued |                  |                                                                                                                                                |  |

|----------|-----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Byte     | Bit       | Lock             | Description                                                                                                                                    |  |

| 12       | 3:5       | U_CLKMON_FREQ    | System Controller Clock Frequency monitor<br>configuration (For PolarFire SoC FPGA only)                                                       |  |

| 13       | —         | RESERVED         | Reserved                                                                                                                                       |  |

| 14-15    | —         | PORDIGEST[15:0]  | This field specifies a mask of device digests that<br>should be checked upon each power-up of the user<br>design (For PolarFire SoC FPGA only) |  |

| 16-31    |           | HWM              | High Water Mark value (For PolarFire SoC FPGA<br>only)<br>All 1s are returned if the HWM is invalid.                                           |  |

| 32       | _         | PORDIGEST[23:16] | This field specifies a mask of device digests that<br>should be checked upon each power-up of the user<br>design (For PolarFire SoC FPGA only) |  |

# 4.7 Read Debug Information Service

Fetches debug information on programming, user initialization, device programming cycle count, and In-application programming (IAP) actions. The device programming cycle count increases for device PROGRAM and ERASE actions. The following table lists the debug information reported by this service.

| System Service<br>Descriptor Bit Field | Value          | Description                      |

|----------------------------------------|----------------|----------------------------------|

| 15:7                                   | MBOXADDR[10:2] | Mailbox address. See Table 4-17. |

| 6:0                                    | 06H            | Read Debug service command.      |

### Table 4-17. Debug Information

| Size (Bytes) | Byte Offset | Parameter       | Description                                                                                                                                           |

|--------------|-------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32           | 0           | Reserved        | Reserved                                                                                                                                              |

| 4            | 32          | TOOL_INFO       | Reflects the tool specific data passed in during programming. IAP sets this field to 0.                                                               |

| 1            | 36          | TOOL_TYPE       | <ul><li>Tool type used to program device:</li><li>1: JTAG</li><li>2: IAP</li><li>3: SPI_SLAVE</li></ul>                                               |

| 4            | 37          | Reserved        | Reserved                                                                                                                                              |

| 1            | 41          | FRAME_ERRORCODE | An error has occurred during bitstream frame processing<br>and the error is identified by the FRAME_ERRORCODE<br>field. See Table 4-20.               |

| 6            | 42          | Reserved        | Reserved                                                                                                                                              |

| 1            | 48          | UIC_STATUS      | <ul><li>Device and design initialization Status.</li><li>0: Successful completion.</li><li>Others: Device and design initialization failed.</li></ul> |

| 11           | 49          | Reserved        | Reserved                                                                                                                                              |

| continu      | continued   |                |                                                                                                                                                                                                                                                                                                                                      |  |  |

|--------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Size (Bytes) | Byte Offset | Parameter      | Description                                                                                                                                                                                                                                                                                                                          |  |  |

| 4            | 60          | CYCLECOUNT     | Programming cycle count. CYCLECOUNT gets incremented for both Programming and Erase operations as ERASE is internally a Programming action.                                                                                                                                                                                          |  |  |

| 1            | 64          | IAP ERRORCODE  | IAP Error Information. Returns ERRORCODE 21-27, see Table 4-20.                                                                                                                                                                                                                                                                      |  |  |

| 7            | 65          | Reserved       | Reserved                                                                                                                                                                                                                                                                                                                             |  |  |

| 4            | 72          | IAP Location   | SPI address that was last run in IAP                                                                                                                                                                                                                                                                                                 |  |  |

| 4            | 76          | SYSCTRL_STATUS | System Controller status                                                                                                                                                                                                                                                                                                             |  |  |

| 4            | 80          | RESET_REASON   | When a reset occurs, a bit is set in the reset reason register<br>that allows the source of the reset to be determined post<br>reset. Multiple bits are set in the reset reason register when<br>a reset occurs. See Table 4-19 for bit position of the bits set<br>in the RESET_REASON register to find out the source of<br>reset. |  |  |

### Table 4-18. SYSCTRL\_STATUS

| Field Name          | Width (bits) | Field Offset |

|---------------------|--------------|--------------|

| SRAM_INIT_COMPLETE  | 1            | 0            |

| UIC_SCRIPT_COMPLETE | 1            | 8            |

| US_RAM_INIT_DONE    | 1            | 16           |

| RESET_REASON        | 5            | 24           |

### Table 4-19. Reset Reason

| Reset Reason    | Description                                                              | RESET_REASON[4:0] |

|-----------------|--------------------------------------------------------------------------|-------------------|

| POR             | Master POR asserted.                                                     | 0                 |

| POR1P05         | POR asserted due to the 1P05 supply is not at correct level.             | 1                 |

| POR1P8          | POR asserted due to the 1P8 supply is not at correct level.              | 2                 |

| POR2P5          | POR asserted due to the 2P5 supply is not at correct level.              | 3                 |

| Reserved        | Reserved.                                                                | 4                 |

| DEVRST          | Indicates that the device is reset by the DEVRSTN pin.                   | 5                 |

| AVIONICS        | Indicates that the device has exited system controller suspend mode.     | 6                 |

| WATCHDOG        | Indicates that the System Controller's watchdog had triggered the reset. | 7                 |

| SYSCON_SYSRESET | Indicates that the system controller requested the system reset.         | 8                 |

| MESH            | Indicates that the security mesh triggered the reset.                    | 9                 |

| continued       |                                                                                                |                   |  |  |

|-----------------|------------------------------------------------------------------------------------------------|-------------------|--|--|

| Reset Reason    | Description                                                                                    | RESET_REASON[4:0] |  |  |

| SECURITY_LOCKS  | Indicates that the security locks<br>system detected a security issue and<br>reset the system. | 10                |  |  |

| CLOCK_GLITCH    | Indicates that the clock glitch system detected an issue and reset the system.                 | 11                |  |  |

| VIRGIN          | Indicates that the virgin security system detected an issue and reset the system.              | 12                |  |  |

| TAMPER_RESPONSE | Indicates that the user asserted the system reset tamper response.                             | 13                |  |  |

### Table 4-20. ERRORCODE

| ERRORCODE | Description                                                              | Additional Notes                                                                                                                                                                                                                          |  |

|-----------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0         | No error                                                                 | —                                                                                                                                                                                                                                         |  |

| 1         | Bitstream authentication failed                                          | Invalid bitstream or wrong key used.                                                                                                                                                                                                      |  |

| 2         | Unexpected data received                                                 | Additional data is received after end of bitstream component.                                                                                                                                                                             |  |

| 3         | Invalid/corrupt encryption key                                           | The requested key mode is disabled or the key could not be read/reconstructed.                                                                                                                                                            |  |

| 4         | Invalid component header                                                 | Invalid bitstream                                                                                                                                                                                                                         |  |

| 5         | Back level not satisfied                                                 | Bitstream version is older than that of the current back level value set in the device.                                                                                                                                                   |  |

| 6         | Illegal bitstream key mode                                               | Bitstream key mode is not initialized or bitstream key mode is disabled by user security.                                                                                                                                                 |  |

| 7         | DSN binding mismatch                                                     | Bitstream is rejected because DSN in the bitstream<br>does not match with the DSN present in the device. A<br>bitstream can be bound to device's unique DSN such<br>that only a specific device can be programmed with<br>that bitstream. |  |

| 8         | Illegal component sequence                                               | Incorrect bitstream                                                                                                                                                                                                                       |  |

| 9         | Insufficient device capabilities                                         | Bitstream is rejected because the capabilities specified<br>in the bitstream do not match the target device's<br>capabilities.                                                                                                            |  |

| 10        | Incorrect DEVICEID                                                       | Bitstream is rejected because an attempt by the DEVICEID specified in the bitstream does not match the part identification field (for example, MPF300, MPF500 and so on) of the target device.                                            |  |

| 11        | Unsupported bitstream protocol version (bitstream regeneration required) | Bitstream is rejected because of an attempt made by<br>the old version of a device to decode a bitstream<br>created in new format or by the new version of a<br>device to decode a bitstream created in old format.                       |  |

| 12        | Verify not permitted on this bitstream                                   | Verify programming action is disabled in the bitstream.                                                                                                                                                                                   |  |

| 13        | Invalid Device Certificate                                               | Device certificate is invalid or not present.                                                                                                                                                                                             |  |

# **Device and Design Information Services**

| continued |                                                                                         |                                                                                                                                                |  |  |

|-----------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ERRORCODE | Description                                                                             | Additional Notes                                                                                                                               |  |  |

| 14        | Invalid DIB                                                                             | Device integrity bits (DIB) are invalid.                                                                                                       |  |  |

| 21        | Device not in SPI Master Mode                                                           | Error may occur only when bitstream is executed<br>through IAP mode. The System Controller SPI<br>controller is not configured in master mode. |  |  |

| 22        | No valid images found                                                                   | Error may occur when bitstream is executed through<br>Auto Update mode. Occurs when No valid image<br>pointers are found.                      |  |  |

| 23        | No valid images found                                                                   | Error may occur when bitstream is executed through IAP mode via Index Mode. Occurs when No valid image pointers are found.                     |  |  |

| 24        | Programmed design version is the same as the Auto Update image found                    | Error may occur when bitstream is executed through Auto Update mode.                                                                           |  |  |

| 25        | Reserved                                                                                | Reserved                                                                                                                                       |  |  |

| 26        | Selected image was invalid and no recovery was performed due to valid design in device. | Error may occur only when bitstream is executed<br>through Auto Update or IAP mode. Error could also<br>occur due to BACKLEVEL protection.     |  |  |

| 27        | Selected and Recovery image failed to program                                           | Error may occur only when bitstream is executed through Auto Update or IAP mode.                                                               |  |  |

| 127 Abort |                                                                                         | Non-bitstream instruction is executed during bitstream loading.                                                                                |  |  |

| 128       | NVMVERIFY                                                                               | Fabric or security segment verification failed.                                                                                                |  |  |

| 129       | PROTECTED                                                                               | Device security is prevented modification of non-volatile memory.                                                                              |  |  |

| 130       | NOTENA                                                                                  | Programming mode not enabled                                                                                                                   |  |  |

| 131       | PNVMVERIFY                                                                              | pNVM verify operation failed                                                                                                                   |  |  |

| 132       | SYSTEM                                                                                  | System hardware error (PUF or DRBG)                                                                                                            |  |  |

| 133       | BADCOMPONENT                                                                            | An internal error was detected in a bitstream component payload.                                                                               |  |  |

| 134       | HVPROGERR                                                                               | Failure in programming subsystem.                                                                                                              |  |  |

| 135       | HVSTATE                                                                                 | Error in the programming subsystem.                                                                                                            |  |  |

# 4.8 Read eNVM Parameters Service (For PolarFire SoC FPGA Only)

Retrieves all parameters needed for eNVM operation and programming.

| System Service<br>Descriptor Bit Field | Value          | Description                      |

|----------------------------------------|----------------|----------------------------------|

| 15:7                                   | MBOXADDR[10:2] | Mailbox address. See Table 4-22. |

| 6:0                                    | 07H            | Read eNVM service command        |

The following table lists the mailbox format.

| Offset | Length<br>(bytes) | Parameter | Direction | Description                                                                                  |

|--------|-------------------|-----------|-----------|----------------------------------------------------------------------------------------------|

| 0      | 256               | eNVM      | Output    | eNVM Parameters. For information about eNVM parameters, see PolarFire SoC Advance Datasheet. |

# 5. Design Programming Services

An IAP image contains the image descriptor, bitstream, and optional design initialization data. The design programming services are used to authenticate entire IAP image, bitstream portion, or program the device. The following table lists all the Design Programming system services with their command values, description, and return status code.

| System Service<br>Name                 | SERVICECMD in<br>Hexadecimal | Description                                                                                                                         | Return Status Code                                                    |

|----------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Bitstream<br>Authentication<br>Service | 23                           | Analyzes a bitstream image stored<br>in SPI Flash and checks for all<br>conditions, which may result in an<br>authentication error. | <ul> <li>0: Success</li> <li>1: ERRORCODE (see Table 4-20)</li> </ul> |

| IAP Image<br>Authentication<br>Service | 22                           | Allows the user to validate an IAP image stored in SPI flash.                                                                       |                                                                       |

Table 5-1. Design Programming System Services

## 5.1 Bitstream Authentication Service

Prior to using the IAP service, it may be required to first validate the new bitstream before committing the device to reprogramming, thus avoiding the need to invoke recovery procedures if the bitstream is invalid.

The bitstream authentication service analyzes a bitstream image stored in SPI Flash and checks for all conditions which may result in an authentication error. While the authentication is in progress, the user design continues to operate normally, but without access to SPI Flash and system services until the authentication process is complete.

If the authentication service is called while a new bitstream is being loaded through the JTAG interface, the system service takes precedence and the JTAG interface is stalled during the authentication and will ultimately fail.

#### Table 5-2. Bitstream Authentication Service Request

| System Service<br>Descriptor Bit Field | Value          | Description                               |

|----------------------------------------|----------------|-------------------------------------------|

| 15:7                                   | MBOXADDR[10:2] | Mailbox address. See Table 5-3.           |

| 6:0                                    | 23H            | Bitstream authentication service command. |

The following table lists the bitstream authentication service mailbox format.

#### Table 5-3. Bitstream Authentication Service Mailbox Format

| Offset | Length (bytes) | Parameter | Direction | Description                                                                                                                                    |

|--------|----------------|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 4              | SPIADDR   | Input     | Address of the bitstream in SPI Flash.<br>If the external SPI Flash device does not<br>support 32-bit addresses, SPIADDR[31:24] is<br>ignored. |

## 5.2 IAP Image Authentication Service

Allows the user to validate an IAP image stored in SPI Flash. The service authenticates the entire IAP image containing the image descriptor, the referenced bitstream, and optional initialization data. If the image is authenticated successfully, the image is guaranteed to be valid when used by an IAP programming service.

The SPI\_IDX parameter passed to this service identifies the index in the SPI directory to be used. To support recovery, SPI\_IDX = 1 must be an empty slot and the recovery image must be located in SPI\_IDX = 0. Since SPI\_IDX = 1 must be an empty slot, it should not be passed into the system service. The following table lists the fields contained in an IAP image authentication service request.

| System Service Descriptor<br>Bit Field | Value        | Description                                                               |

|----------------------------------------|--------------|---------------------------------------------------------------------------|

| 15                                     | <u> </u>     | Reserved.                                                                 |

| 14:7                                   | IMAGEID[7:0] | Identifies the image index in the SPI directory for image authentication. |

| 6:0                                    | 22H          | IAP Image Authenticate service command.                                   |

# 6. Data Security Services

The data security services are used to authenticate the device, generate unique random number, and store the encrypted data. The following table lists all the Data Security system services with their command values, description, and return status code.