# 120V, 5A, LCL/RLCL Programmable Current Limiting

**Power Switch For Space**

## Description

The LX7712 is a radiation-hardened-by-design power switch for integration into spacecraft power distribution systems as an electronic fuse for power line protection. DC supplies up to 120V with continuous current rating up to 5A can be easily turned on and off with slew rate programmability. The LX7712 includes a P-channel MOSFET power switch and catch diode for inductive loads.

The LX7712 is configurable as either a latchable current limiter or a fold-back current limiter, with optional thermal shutdown. Multiple LX7712 devices can be paralleled to increase the current rating. The current limit, on/off slew rate, and fault response fault timers are programmed with passive external components.

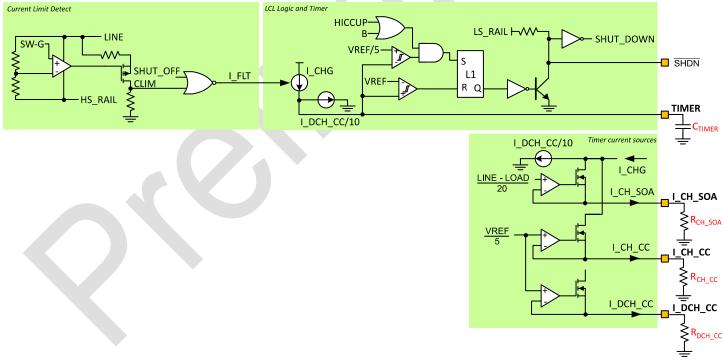

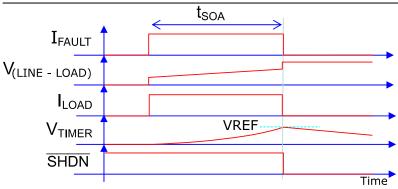

The latchable current limiter is configurable to either latch off (LCL) under fault conditions, or to attempt to restart in hiccup mode (RLCL). A fault time integrating function accumulates the thermal effects of short fault pulses. The fault timer is configurable for either a fixed duration or a duration that is a function of the voltage drop from line input to load output across the switch. A resistor programmable fault timer discharge function ensures that the LX7712 has dissipated excess energy to a safe level before restarting.

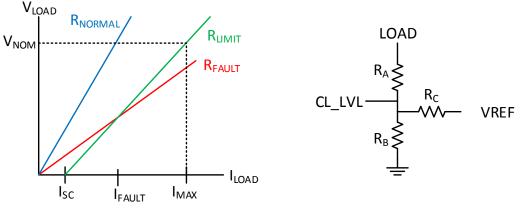

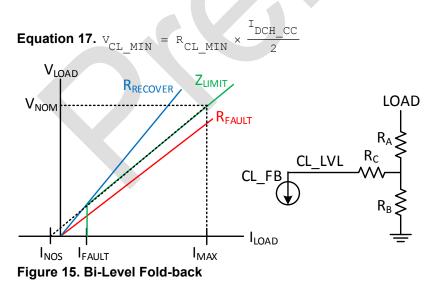

In fold-back current limit (FCL) mode, the profile of the fold-back load current versus load voltage curve is resistor programmable. Fold-back allows automatic fault recovery. An overload condition forces the current limit to a safe trickle level, and when the overload is removed the current limit returns to its normal level. This prevents soft-short fault situations which can cause the switch to over-dissipate.

A programmable current ramp function limits the slew rate of the current during turn on and turn off.

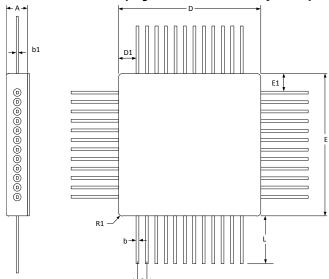

The LX7712MFM is packaged in a 48-pin hermetic hybrid tub flatpack (HTF) package. It operates over a -55°C to 125°C temperature range and is radiation tolerant to a minimum of 100krad(Si) TID and a minimum of 50krad(Si) ELDRS, as well as single event effects.

## Features

- Internal 120V, 5A rated power switch

- Internal catch diode for inductive loads

- Constant current or fold-back current limit

- Safe management of soft overload faults

- Optional hiccup automatic restart mode (RLCL)

- Programmable current levels

- Programmable fault timer

- Current monitor output

- Separate ON, OFF, and low power OFF control inputs

- Low power switch voltage drop

- Over temperature shutdown and optional restart

- Load current slew rate control

- Small hermetic 48 lead HTF package

- Radiation tolerant: 100krad(Si) TID, 50krad(Si) ELDRS, SEL immune up to 60 MeV.cm<sup>2</sup>/mg and 125°C (fluence of 10<sup>7</sup> particles/cm<sup>2</sup>)

## Applications

Spacecraft power control and distribution

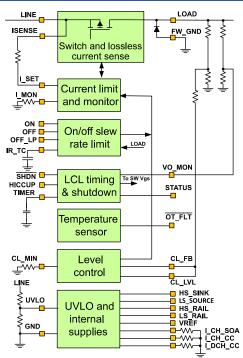

Typical Power Switch System

#### <u>Notes</u>

- 1. Pin 18 is directly connected to the metal package body and wire bonded to the die (see Figure 20 on page 26). Pin 18, the GND pin 19, and the four FW\_GND pins 41, 42, 43, and 44 must be connected to the same ground potential

- 2. The metal package top is electrically conductive to the metal package body, and so is at ground potential (GND)

- 3. The top or the base of the package can be used as the heat conducting surface. It is recommended to use the base of the package as the surface for conducting heat from the package. The metal package top is attached to the package body at the top of relatively thin cavity walls, and so has a much higher thermal resistance from the die than the base of the package. The leads can be formed to mount the part upside down if necessary. It is recommended to apply a thermal interface material between the package and its heat dissipater. The heat dissipater can be copper layers within a multilayer circuit board to spread heat laterally across the board, or a direct mounted dissipation element

### 2 Ordering Information

| Operating<br>Temperature | Package<br>Type   | Package  | Part Number            | SMD Number   | Flow                             | Shipping<br>Type      |  |

|--------------------------|-------------------|----------|------------------------|--------------|----------------------------------|-----------------------|--|

|                          | Hermetic<br>Metal | Hormotio |                        | LX7712MFM-EV | TBD                              | MIL-PRF-38535 Class V |  |

| -55°C to 125°C           |                   | HTF-48   | LX7712MFM-EQ           | TBD          | MIL-PRF-38535 Class Q            | Tray                  |  |

|                          | Metal             |          | LX7712-ES <sup>1</sup> | -            | Engineering Samples <sup>1</sup> |                       |  |

<sup>1</sup>Engineering samples are intended for design evaluation purposes only. They are only tested and trimmed at room temperature, and do not undergo any thermal, environmental, or hermeticity testing

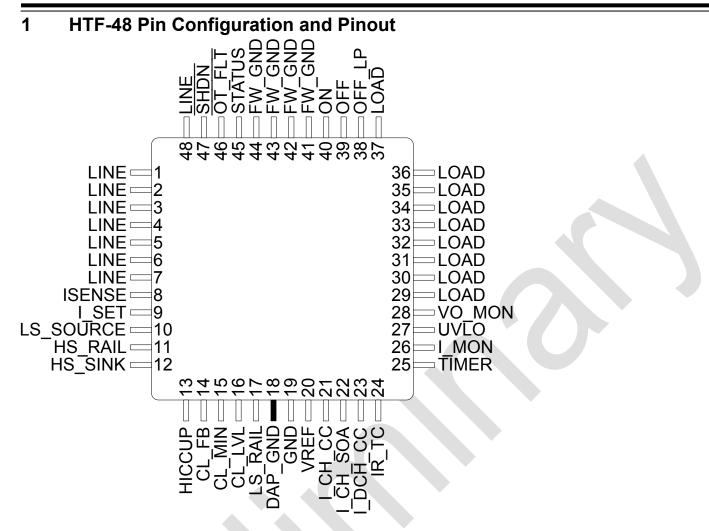

## 3 Pin Numbering and Pin Descriptions

| Di  | News      | Die Tee                          | Die Ermett                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-----------|----------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin | Name      | Pin Type                         | Pin Function                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1-7 | LINE      | Power                            | Power Switch<br>Input                                   | All LINE pins 1 to 7 and 48 must be used, connected to the power supply<br>to be switched. LINE is also the power input for the HS_RAIL regulator.<br>Bypass the group of LINE pins with a single 100nF capacitor to GND                                                                                                                                                                                                           |

| 8   | ISENSE    | Power Kelvin<br>Sense Input      | Current Monitor<br>Input                                | Connect a resistor $R_{LSET}$ = 10k $\Omega$ between ISENSE and I_SET to configure the power switch's current limit. ISENSE is internally bonded to                                                                                                                                                                                                                                                                                |

| 9   | I_SET     | Analog Input                     | Current Monitor<br>Reference                            | LINE and provides a Kelvin connection to LINE since it does not carry any of the LINE/LOAD current. The voltage across $R_{I\_SET}$ is 1V per amp of load current, so 5V maximum at 5A load current                                                                                                                                                                                                                                |

| 10  | LS_SOURCE | Power                            | Low-Side Rail<br>Power Source                           | Input to the LS_RAIL linear regulator. Connect directly to a voltage between 12V and 30V, or to a higher voltage via a series ballast resistor and/or pre-regulator. Bypass LS_SOURCE with a 100nF capacitor to GND. See the LS_SOURCE and LS_RAIL section 12.3 on page 13                                                                                                                                                         |

| 11  | HS_RAIL   | Power                            | High-Side Rail                                          | Output of an internal linear regulator delivering $10V \pm 1V$ below LINE.<br>Regulator input is HS_SINK pin 11. Bypass HS_RAIL with a 100nF capacitor to LINE. See the HS_SINK and HS_RAIL section 12.2 on page 12                                                                                                                                                                                                                |

| 12  | HS_SINK   | Power                            | High-Side Rail<br>Power Source                          | Input to the HS_RAIL linear regulator. Connect to a voltage at least 12V below VLINE, typically GND. See the HS_SINK and HS_RAIL section 12.2 on page 12                                                                                                                                                                                                                                                                           |

| 13  | HICCUP    | Logic Input (4M $\Omega$ to GND) | Hiccup Mode<br>Enable                                   | To enable hiccup mode, which resets a latched over-current fault under fault timer control, tie HICCUP to either VREF or to a 2.5V to 5V logic supply.<br>To disable hiccup mode, either leave HICCUP open or tie HICCUP to GND. See the Fault Timer section 16 on page 21                                                                                                                                                         |

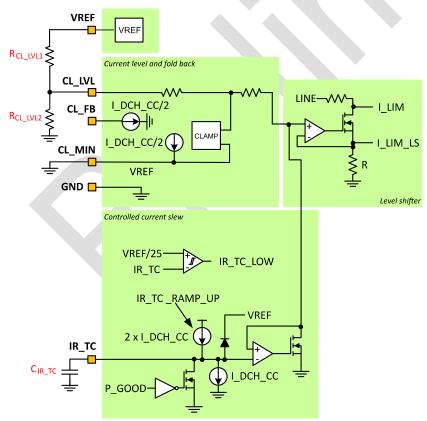

| 14  | CL_FB     | Analog Output                    | Current Limit<br>Fold Back                              | This pin is used to generate a negative current limit offset when fold back current limiting is used. This pin should be shorted to CL_LVL if the function is desired, otherwise, the pin can be left open. This pin is an open collector current sink with a value of $\frac{1}{2}$ of the discharge current                                                                                                                      |

| 15  | CL_MIN    | Analog Input                     | Current Limit<br>Minimum Level                          | The voltage on this pin sets the minimum level of current limit. This pin features a source current equal to ½ of the discharge current. In current-foldback mode, a resistor shall be used to connect this pin to ground and generate the desired voltage level to clip CL_LVL. In other modes, the voltage on this pin should be smaller than the level on CL_LVL to not interfere with the desired function (e.g. short to GND) |

| 16  | CL_LVL    | Analog Input                     | Current Limit<br>Level                                  | The voltage on this pin sets the current limit reference level. A specific resistor network shall be connecting this pin to LOAD and/or VREF, depending on the desired current limit mode                                                                                                                                                                                                                                          |

| 17  | LS_RAIL   | Power                            | Low-Side Rail                                           | Output of an internal linear regulator delivering $10V \pm 1V$ above GND.<br>Regulator input is LS_SOURCE pin 10. Bypass LS_RAIL with a 100nF capacitor to GND. See the LS_SOURCE and LS_RAIL section 12.3 on page 13                                                                                                                                                                                                              |

| 18  | DAP       | Power                            | Die Attach Pad                                          | This pin must be connected to GND                                                                                                                                                                                                                                                                                                                                                                                                  |

| 19  | GND       | Power                            | GND                                                     | This pin is the GND point for analog and logic signals                                                                                                                                                                                                                                                                                                                                                                             |

| 20  | VREF      | Analog Output                    | 5V Reference                                            | Output of an internal +5V ±4% reference voltage. VREF can source up to 2mA into external loads such as configuration resistor networks. Bypass VREF with a 100nF capacitor to GND                                                                                                                                                                                                                                                  |

| 21  | І_СН_СС   | Analog Input                     | Fault Timer<br>Static Charge<br>Current<br>Programming  | Connect resistor $R_{I\_CH\_CC}$ from I_CH_CC to GND to set a static reference current to charge the fault timer capacitor. Leave open if not used. See the Fault Timer section 16 on page 21                                                                                                                                                                                                                                      |

| 22  | I_CH_SOA  | Analog Input                     | Fault Timer<br>Dynamic<br>Charge Current<br>Programming | Connect resistor $R_{I\_SOA\_CC}$ from I_CH_SOA to GND to set a dynamic reference current to charge the fault timer capacitor. Leave open if not used. See the Fault Timer section 16 on page 21                                                                                                                                                                                                                                   |

| 23  | I_DCH_CC  | Analog Input                     | Fault Timer<br>Discharge<br>Current<br>Programming      | Connect resistor $R_{I\_DCH\_CC}$ from $I\_DCH\_CC$ to GND to set a static reference current to discharge the fault timer capacitor, and to set the slew rate during power switch turn on and turn off. See the Fault Timer section 16 on page 21                                                                                                                                                                                  |

| Pin       | Name   | Pin Type                                        | <b>Pin Function</b>                       | Description                                                                                                                                                                                                                                                                                                                                           |

|-----------|--------|-------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24        | IR_TC  | Analog Input                                    | Current<br>Ramping<br>Timing<br>Capacitor | Connect capacitor $C_{IR_TC}$ from IR_TC to GND to set the slew rate during power switch turn on and turn off or leave open. $R_{I_DCH_CC}$ on I_DCH_CC pin 23 is the other programming element. See the On and Off Controls section 13 on page 15                                                                                                    |

| 25        | TIMER  | Analog Input                                    | Latchable<br>Current Limit<br>Fault Timer | Connect capacitor $C_{\text{TIMER}}$ from TIMER to GND to set the programmable fault timer time constant together with resistors $R_{\text{L_CH}_{\text{CC}}}$ , $R_{\text{L}_{\text{DCH}_{\text{CC}}}}$ , and $R_{\text{L}_{\text{DCH}_{\text{CC}}}}$ . Grounding TIMER disables the fault timer function. See the Fault Timer section 16 on page 21 |

| 26        | I_MON  | Analog Output                                   | Load Current<br>Monitor                   | Connect resistor $R_{I_{MON}}$ from I_MON to GND to monitor the load current. The output current on this pin is 1/5000 x the load current                                                                                                                                                                                                             |

| 27        | UVLO   | Analog Input                                    | LINE Under-<br>Voltage Lock-<br>Out       | This input is used to monitor the LINE voltage. The under-voltage level is set with a LINE to GND external voltage divider. See the External Voltage Monitor Inputs section 13.2 on page 16                                                                                                                                                           |

| 28        | VO_MON | Analog Input                                    | LOAD Voltage<br>Monitor                   | This input is used to monitor the LOAD voltage. The under-voltage level is set with a LOAD to GND external voltage divider. See the External Voltage Monitor Inputs section 13.2 on page 16                                                                                                                                                           |

| 29-<br>37 | LOAD   | Power                                           | Power Switch<br>Output                    | All LOAD pins 29 to 37 must be used, connected to the external load. An internal reverse biased diode from LOAD to GND clamps inductive flyback voltages on turn-off                                                                                                                                                                                  |

| 38        | OFF_LP | Power<br>(2.4MΩ to GND)                         | OFF (Low<br>Power) Control                | A logic high level on OFF_LP will turn off the power switch and enter low<br>power mode by shutting down internal power supplies                                                                                                                                                                                                                      |

| 39        | OFF    | Logic Input<br>(4MΩ to GND)                     | OFF Control                               | A logic high pulse or level on this pin will turn off the power switch. The OFF input has priority over the ON pin if both are high                                                                                                                                                                                                                   |

| 40        | ON     | Logic Input<br>(4MΩ to GND)                     | ON Control                                | A logic high pulse or level on this pin will turn on the power switch                                                                                                                                                                                                                                                                                 |

| 41-<br>44 | FW_GND | Power GND                                       | Free-wheel<br>Diode Ground                | This pin provides a path for current to flow through the free-wheeling diode that provides a path of inductive load current if the power switch shuts off abruptly                                                                                                                                                                                    |

| 45        | STATUS | Open Collector<br>Logic Output                  | On/Off Status                             | A low level on this open collector output indicates that the switch is on,<br>and that the VO_MON is monitoring a LOAD voltage greater than the<br>under-voltage threshold                                                                                                                                                                            |

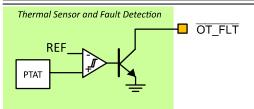

| 46        | OT_FLT | Open Collector<br>Logic I/O                     | Over<br>Temperature<br>Fault              | A low level on this open collector output indicates that an over-<br>temperature fault has occurred. The over-temperature sensor has<br>hysteresis and resets after cooling down. This pin can be connected to<br>SHDN. Multiple devices can have OT_FLT and SHDN connected                                                                           |

| 47        | SHDN   | Open Collector<br>Logic I/O<br>(1MΩ to LS_RAIL) | Shutdown Fault                            | A low logic output signal indicates that an LCL timeout has triggered the shutdown latch. This pin can also be used as an input from another device or from the temperature monitor output OT_FLT to conditionally shutdown the switch. Multiple devices can have SHDN connected                                                                      |

| 48        | LINE   | Power                                           | Power Switch<br>Input                     | All LINE pins 1 to 7 and 48 must be used, connected to the power supply<br>to be switched. LINE is also the power input for the HS_RAIL regulator.<br>Bypass the group of LINE pins with a single 100nF capacitor to GND                                                                                                                              |

### 4 Absolute Maximum Ratings

Stresses above those listed in ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

| Parameter                                                                                                      | Min                     | Мах                     | Units |

|----------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------|

| LINE input (V <sub>LINE</sub> ) to GND                                                                         | -3                      | 150                     | V     |

| V <sub>LOAD</sub>                                                                                              | -2                      | V <sub>LINE</sub> + 1.5 | V     |

| V <sub>HS_SINK</sub>                                                                                           | -0.3                    | V <sub>LINE</sub>       | V     |

| V <sub>LS_SOURCE</sub> , when directly connected to a supply                                                   | -0.3                    | 32                      | V     |

| $V_{LS_SOURCE}$ , when connected to a supply via a series current limiting resistor                            | -0.3                    | V <sub>LINE</sub>       | V     |

| P <sub>HS_SINK</sub> HS_SINK regulator dissipation                                                             |                         | 240                     | mW    |

| LS_SOURCE regulator dissipation, V <sub>LS_SOURCE</sub> < V <sub>LS_CLAMP</sub> (P <sub>LS_SOURCE</sub> )      |                         | 300                     | mW    |

| LS_SOURCE regulator + clamp dissipation, $V_{LS_{SOURCE}} \ge V_{LS_{CLAMP}}$ ( $P_{LS_{SOURCE}}$ )            |                         | 600                     | mW    |

| ILINE, ILOAD                                                                                                   | -7.5                    | 7.5                     | А     |

| I <sub>FW_GND</sub>                                                                                            |                         | 7.5                     | А     |

| V <sub>HS_RAIL</sub>                                                                                           | Self-regulated          | V <sub>LINE</sub>       | V     |

| V <sub>LSET</sub>                                                                                              | V <sub>LINE</sub> - 7.5 | V <sub>LINE</sub>       | V     |

| VLS_RAIL                                                                                                       | -0.3                    | 12                      | V     |

| V <sub>VREF</sub>                                                                                              | -0.3                    | Self-regulated          | V     |

| VIMON                                                                                                          | -0.3                    | 5.6                     | V     |

| V <sub>CL_LVL</sub> , V <sub>CL_MIN</sub> , V <sub>TIMER</sub>                                                 | -0.3                    | 9                       | V     |

| V <sub>UVLO</sub> , V <sub>VO_MON</sub>                                                                        | -0.3                    | 15                      | V     |

| V <sub>CL_FB</sub> , V <sub>I_CH_CC</sub> , V <sub>I_CH_SOA</sub> , V <sub>I_DCH_CC</sub> , V <sub>IR_TC</sub> | -0.3                    | 11                      | V     |

| VHICCUP, VOFF_LP, VOFF, VON, VSTATUS, VOT_FLT, VSHDN                                                           | -0.3                    | 12                      | V     |

| STATUS, SHDN. and OT_FLT sink current                                                                          |                         | 3                       | mA    |

| I_MON pin current                                                                                              | -1                      | 0                       | mA    |

## 5 Operating Ratings

Performance is generally guaranteed over this range as further detailed below under Electrical Characteristics.

| Parameter                                                                                                                | Min                   | Мах                                       | Units |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------|-------|

| V <sub>LINE</sub> , V <sub>LOAD</sub>                                                                                    | 12                    | 120                                       | V     |

| P <sub>HS_SINK</sub> HS_SINK regulator dissipation                                                                       |                       | 180                                       | mW    |

| P <sub>LS_SOURCE</sub> LS_SOURCE regulator dissipation, V <sub>LS_SOURCE</sub> < V <sub>LS_CLAMP</sub>                   |                       | 225                                       | mW    |

| P <sub>LS_SOURCE</sub> LS_SOURCE regulator + clamp dissipation, V <sub>LS_SOURCE</sub> ≥ V <sub>LS_CLAMP</sub>           |                       | 450                                       | mW    |

| V <sub>LS_SOURCE</sub> operating mode, V <sub>LS_SOURCE</sub> directly connected to a supply (OFF_LP = logic low)        | 12                    | 30                                        | V     |

| V <sub>LS_SOURCE</sub> operating mode, V <sub>LS_SOURCE</sub> connected via a series resistor (OFF_LP = logic low)       | 12                    | V <sub>LINE</sub>                         | V     |

| V <sub>LS_SOURCE</sub> low power mode (OFF_LP = logic high)                                                              | 12                    | VLINE                                     | V     |

| V <sub>LS_RAIL</sub>                                                                                                     | 9                     | 11                                        | V     |

| V <sub>HS_SINK</sub>                                                                                                     | 0                     | V <sub>LINE</sub> - 12                    | V     |

| V <sub>LSET</sub>                                                                                                        | V <sub>LINE</sub> - 6 | VLINE                                     | V     |

| V <sub>CL_LVL</sub>                                                                                                      | 0                     | 5.3                                       | V     |

| V <sub>UVLO</sub> , V <sub>VO_MON</sub>                                                                                  | 0                     | 13                                        | V     |

| Vcl_fb, Vcl_min, Vl_ch_cc, Vl_ch_soa, Vl_dch_cc, Vir_tc, Vtimer, Vhiccup, Voff_lp, Voff, Von,<br>Vstatus, Vot_flt, Vshdn | 0                     | 6                                         | V     |

| V <sub>IMON</sub>                                                                                                        | 0                     | (V <sub>I_SET</sub> - 5) up<br>to 5.5 max | V     |

| STATUS, SHDN, and OT_FLT sink current                                                                                    | 0                     | 2                                         | mA    |

| $I_{LINE}$ , $-I_{LOAD}$ (negative current when switch body diode or catch diode is forward biased)                      | -5                    | 5                                         | А     |

## 6 Electrostatic Discharge Ratings

JEDEC JEP155 states that 500V HBM allows safe manufacturing with a standard ESD controlled process. JEDEC JEP157 states that 250V CDM allows safe manufacturing with a standard ESD controlled process. ESD ratings apply to all pins.

| ESD Test                                              | Minimum Capability |

|-------------------------------------------------------|--------------------|

| HBM: Human Body Model, per MIL-STD-883 TM3015         | ±2kV               |

| CDM: Charged Device Model, per ANSI/ESDA/JEDEC JS-002 | ±TBDV              |

## 7 Electrical Characteristics

The following specifications apply over the operating ambient temperature of -55°C  $\leq T_A \leq 125$ °C except where otherwise noted with the following test conditions:  $V_{ON} = V_{HICCUP} = 6V$ ;  $V_{OFF} = V_{FB\_LVL} = GND$ ;  $V_{HS\_SINK} = GND$ ;  $V_{LS\_SOURCE} = 17V$ ; 22V  $< V_{LINE} < 120V$ . Typical parameters refer to  $T_J = 25$ °C. Positive currents flow into a pin

| Symbol                    | Parameter                                                                 | Test Conditions/Comments                                                                                              | Min  | Тур  | Max  | Units |

|---------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Operating                 |                                                                           |                                                                                                                       |      |      |      |       |

|                           | Internal IC current                                                       | Switch On or Off                                                                                                      |      | -3.5 | -8.0 | mA    |

| I <sub>GND</sub>          | consumption flowing to ground via the GND pin                             | Switch Off (low power); LS_SOURCE powered internally                                                                  |      | -0.6 | -2   | mA    |

| I <sub>HS_SINK</sub>      | Current for internal linear regulator HS_RAIL                             | OFF_LP = logic low                                                                                                    |      | -1   | -1.5 | mA    |

|                           | Current for internal linear regulator LS_RAIL (part of I <sub>GND</sub> ) | LS_SOURCE is supply for LS_RAIL regulator. OFF_LP = logic low                                                         | 3.5  | 6.5  | 10   | mA    |

| I <sub>LS_RAIL</sub>      | Current into LS_RAIL                                                      | LS_RAIL supplied with external 11V,<br>LS_SOURCE floating                                                             | TBD  | 7    | TBD  | mA    |

| Vls_clamp                 | Clamp voltage for<br>LS_SOURCE input                                      | Externally driven at 10mA                                                                                             | 32   | 34   | 36   | V     |

| V <sub>LINE_UVLO</sub>    | LINE UVLO                                                                 | LINE voltage rising, with both LS_RAIL and<br>VREF operating normally                                                 | 9    |      | 10   | V     |

| V <sub>LINE_HYST</sub>    | LINE UVLO hysteresis                                                      |                                                                                                                       |      | 0.7  |      | V     |

| VLS_RAIL_UVLO             | LS_RAIL UVLO                                                              | LS_RAIL voltage rising                                                                                                |      | 7.9  |      | V     |

| V <sub>HS_RAIL_UVLO</sub> | HS_RAIL UVLO                                                              | (V <sub>LINE</sub> - V <sub>HS_RAIL</sub> ) voltage rising                                                            |      | 7.9  |      | V     |

| V <sub>VREF_UVLO</sub>    | VREF UVLO                                                                 | LS_RAIL voltage rising                                                                                                |      | 4.25 |      | V     |

| V <sub>HS_RAIL</sub>      | Voltage below line                                                        | VLINE - VHS_RAIL                                                                                                      | 9    | 10   | 11   | V     |

| V <sub>LS_RAIL</sub>      | Voltage above ground                                                      | -5mA < I <sub>LS_RAIL</sub> < 0 drawn externally                                                                      | 9    | 10   | 11   | V     |

| I <sub>VREF</sub>         | Current limit                                                             | VREF shorted to ground                                                                                                | -2   | -12  |      | mA    |

| V <sub>VREF</sub>         | Output voltage                                                            | -2mA < I <sub>VREF</sub> < 0, T <sub>J</sub> = 25°C                                                                   | 4.8  | 5.0  | 5.2  | V     |

| $\Delta V_{VREF}$         | Output voltage variation                                                  | Across temperature range, $I_{VREF} = 100\mu A$ , guaranteed by design                                                | -50  |      | +50  | mV    |

| ON, OFF, HICCU            | JP, OFF_LP                                                                |                                                                                                                       |      |      |      |       |

|                           | Input logic high level                                                    |                                                                                                                       | 2.0  |      |      | V     |

| VINPUT                    | Input logic low level                                                     |                                                                                                                       |      |      | 0.8  | V     |

|                           | Leakage Current                                                           | $0V < V_{INPUT} < 5V$                                                                                                 | 0    |      | 10   | μA    |

| T <sub>LATCH</sub>        | Pulse Width to latch for<br>ON, OFF and HICCUP                            | Either ON or OFF                                                                                                      | 1    |      |      | μs    |

| I_CH_CC, I_CH_            | _SOA, I_DCH_CC                                                            |                                                                                                                       |      |      |      |       |

| V <sub>I_CH_CC</sub>      | Current program voltage                                                   | $R_{I CH CC} = 10 k\Omega$ to $100 k\Omega$                                                                           | 19.6 | 20   | 20.4 | %VREF |

| VI_DCH_CC                 | Current program voltage                                                   | $R_{I DCH CC} = 10 k\Omega$ to $100 k\Omega$                                                                          | 19.6 | 20   | 20.4 | %VREF |

|                           |                                                                           | $V_{\text{LINE}} - V_{\text{LOAD}} = 10V, R_{\text{L_CH}SOA} = 10k\Omega$ to 100kΩ                                    | 0.48 | 0.5  | 0.52 | V     |

| VI_CH_SOA                 | Current program voltage                                                   | $V_{\text{LINE}}$ - $V_{\text{LOAD}}$ = 100V, $R_{\text{I}_{\text{CH}_{\text{SOA}}}}$ = 10k $\Omega$ to 100k $\Omega$ | 4.8  | 5.0  | 5.2  | V     |

| Symbol                                                                                                     | Parameter                                                                                                              | Test Conditions/Comments                                                                                               | Min  | Тур   | Max  | Units         |

|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|-------|------|---------------|

| -                                                                                                          | 3 under current limiting co                                                                                            |                                                                                                                        |      | 71    | -    |               |

| I <sub>CL_FB</sub>                                                                                         | CL FB sink current                                                                                                     | R <sub>I DCH CC</sub> = 50kΩ, 0.5V < V <sub>CL FB</sub> < 5V                                                           | 9    | 10    | 11   | μA            |

| V <sub>satCL_FB</sub>                                                                                      | CL_FB saturation voltage                                                                                               | $R_{I DCH CC} = 50 k\Omega$ , $I_{CL FB} = 5 \mu A$                                                                    |      |       | TBD  | mV            |

| $\Delta I_{LOAD_{TRIP}} / \Delta V_{CL_{MIN}}$                                                             | CL_MIN input voltage to<br>LOAD current gain<br>(transconductance)                                                     | $R_{I\_SET} = 10k\Omega$ , $R_{DIS} = 50k\Omega$ , for CL_LVL = 0V,<br>CL_FB floating, CL_MIN = 0.2V to 2V             | TBD  |       | TBD  | $\Omega^{-1}$ |

| V <sub>CL_MIN offset</sub>                                                                                 | CL_MIN input voltage to<br>LOAD current<br>extrapolated offset                                                         | $R_{I\_SET}$ = 10k $\Omega$ , $R_{DIS}$ = 50k $\Omega$ , for CL_LVL = 0V,<br>CL_FB floating, CL_MIN = 0.2V to 2V       | -TBD |       | TBD  | mV            |

| I <sub>CL_MIN</sub>                                                                                        | CL_MIN pin current                                                                                                     | $R_{DIS} = 50 k\Omega$ , $0V < V_{CL_{MIN}} < 4V$                                                                      | -11  | -10.5 | -9.5 | μA            |

| Switch Characteris                                                                                         | tics                                                                                                                   |                                                                                                                        |      |       |      |               |

| $\begin{array}{l} \Delta I_{\text{LOAD}_{\text{TRIP}}} \\ / \Delta V_{\text{CL}_{\text{LVL}}} \end{array}$ | CL_LVL input voltage to<br>LOAD current gain<br>(transconductance)                                                     | $R_{I\_SET}$ = 10k $\Omega$ , for CL_LVL = 1V to 5V                                                                    | TBD  |       | TBD  | $\Omega^{-1}$ |

| ILOAD_TRIP_2V                                                                                              | Load current trip value at 2V                                                                                          | $R_{I\_SET}$ = 10k $\Omega$ , for CL_LVL = 2V                                                                          | TBD  |       | TBD  | А             |

| ILOAD_TRIP_offset                                                                                          | Load current trip value extrapolated at 0V                                                                             | $R_{I\_SET} = 10k\Omega$ , $CL\_LVL = 1V$ , $CL\_LVL = 2V$                                                             | TBD  |       | TBD  | А             |

| $\Delta I_{LOAD_{TRIP}}$ / 4A                                                                              | Error from ideal line with<br>respect to 4A scale                                                                      | $R_{I\_SET} = 10k\Omega$ , for CL_LVL = 1V to 5V                                                                       | -10  | ±5    | 10   | %             |

| I <sub>LOAD</sub> / I <sub>LSET</sub>                                                                      | ILSET to ILOAD current gain                                                                                            | Test at $I_{LOAD}$ = 1A and $V_{LINE} - V_{LOAD}$ = 5V                                                                 |      | 10000 |      | A/A           |

| I <sub>I_MON_0A</sub>                                                                                      | I <sub>L_MON</sub> current at I <sub>LOAD</sub> = 0A                                                                   | Test at $I_{LOAD}$ = 0A, CL_LVL = 5.25V, $R_{I_MON}$ = 5k $\Omega$ , $R_{I_SET}$ = 10k $\Omega$                        | 0    |       | TBD  | μA            |

| I <sub>I_MON_1A</sub>                                                                                      | I <sub>L_MON</sub> current at I <sub>LOAD</sub> = 1A                                                                   | Test at I <sub>LOAD</sub> = 1A, CL_LVL = 5.25V<br>R <sub>I_MON</sub> = 5kΩ, R <sub>I_SET</sub> = 10kΩ                  | TBD  |       | TBD  | μA            |

| I <sub>I_MON_2A</sub>                                                                                      | I <sub>L_MON</sub> current at I <sub>LOAD</sub> = 2A                                                                   | Test at $I_{LOAD}$ = 1A, CL_LVL = 5.25V, $R_{I_MON}$ = 5K $\Omega$ , $R_{I_SET}$ = 10k $\Omega$                        | TBD  |       | TBD  | μA            |

| I <sub>I_MON_4A</sub>                                                                                      | I <sub>L_MON</sub> current at I <sub>LOAD</sub> = 4A                                                                   | Test at I <sub>LOAD</sub> = 4A, CL_LVL = 5.25V<br>R <sub>I_MON</sub> = 5kΩ, R <sub>I_SET</sub> = 10kΩ                  | TBD  |       | TBD  | μA            |

| $\Delta I_{I\_MON}$ / $I_{I\_MON\_4A}$                                                                     | Error from ideal line with respect to 4A scale for I <sub>I MON</sub>                                                  | $R_{I\_SET}$ = 10kΩ, for CL_LVL = 5.2V, $I_{LOAD}$ = 1A to 4A                                                          | 4    | ±1    | 4    | %             |

|                                                                                                            | Maximum error of load<br>current limit from load trip<br>current (I <sub>LOAD_CLIM</sub> -<br>I <sub>LOAD_TRIP</sub> ) | $R_{I\_SET}$ = 10k $\Omega$ , for CL_LVL = 1V to 5V, CL<br>condition V <sub>LINE</sub> - V <sub>LOAD</sub> = 5V        | -0.1 | 0.0   | 1.0  | A             |

| V <sub>LINE-LOAD</sub>                                                                                     | Switch Voltage drop                                                                                                    | Test at I <sub>LOAD</sub> = 1A                                                                                         |      | 100   | 200  | mV            |

| ILINE-LOAD                                                                                                 | Switch off leakage                                                                                                     | In short circuit                                                                                                       |      |       | 55   | μA            |

| t <sub>PWR_ON</sub>                                                                                        | Switch turn on time                                                                                                    | From ON to LOAD; IR_TC = open                                                                                          |      |       | 150  | μs            |

| t <sub>LP_ON</sub>                                                                                         | Switch turn on time from low power mode                                                                                | From OFF_LP de-assertion (50%) to LOAD<br>(10%); ON = asserted; IR_TC = open; 100nF<br>capacitor from LS_SOURCE to GND |      |       | 1.5  | ms            |

| t <sub>C_LIM</sub>                                                                                         | Current limit reaction time                                                                                            | 5A current limit, LOAD step from $10k\Omega$ to $1m\Omega$ , I <sub>LOAD</sub> falls below 5A                          |      |       | 100  | μs            |

| V <sub>Reverse</sub>                                                                                       | On voltage for switch back diode                                                                                       | I <sub>reverse</sub> = 5A                                                                                              |      | 1     | 1.5  | V             |

| I <sub>Reverse_sw</sub>                                                                                    | Maximum reverse current                                                                                                | DC                                                                                                                     |      |       | 5    | Α             |

| Catch Diode Chara                                                                                          |                                                                                                                        |                                                                                                                        |      |       |      |               |

| V <sub>FWD</sub>                                                                                           | Forward voltage from<br>FW_GND to LOAD                                                                                 | I <sub>FW_GND</sub> = 2A pulsed                                                                                        |      | 1     | TBD  | V             |

| I <sub>FWDcatchD</sub>                                                                                     | Forward maximum current                                                                                                | DC                                                                                                                     |      |       | 0.5  | А             |

| P <sub>FWD</sub>                                                                                           | Average power during<br>pulsed regime                                                                                  | Example 5A x 10ms                                                                                                      |      |       | 0.5  | W             |

| Q <sub>FWD</sub>                                                                                           | Maximum pulse charge                                                                                                   | Example 5A x 10ms                                                                                                      |      |       | 50   | mC            |

| I <sub>FW_GND</sub>                                                                                        | Leakage current                                                                                                        | V <sub>LOAD</sub> = 100V                                                                                               |      | 25    | 50   | μA            |

| Symbol                                | Parameter                                               | Test Conditions/Comments                                                                          | Min                    | Тур       | Max                  | Units |

|---------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------|-----------|----------------------|-------|

| Fault Timer                           |                                                         |                                                                                                   |                        |           |                      |       |

| I <sub>TIMER</sub>                    | Fault timer charge<br>current,<br>Under fault condition | $R_{I\_CH\_CC}$ = 100k $\Omega$ , $R_{I\_CH\_SOA}$ = open, $V_{TIMER}$ = 2.5V                     | -12.0                  | -10.0     | -8.0                 | μA    |

| TIMER                                 | Fault timer charge<br>current, Under fault<br>condition | $      R_{I\_CH\_CC} = open; R_{I\_CH\_SOA} = 100k, V_{LINE} - V_{LOAD} = 20V, V_{TIMER} = 2.5V $ | -12.0                  | -10.0     | -8.0                 | μ, τ  |

| I <sub>TIMER</sub>                    | Fault timer discharge current                           | $R_{I_{DCH_{CC}}} = 10k\Omega$ , $V_{TIMER} = 2.5V$ , non-fault condition                         | 8                      | 10        | 12                   | μA    |

| T <sub>RT_SHDN</sub>                  | SHDN reaction time                                      | Trip detected at SHDN to LOAD disconnect,<br>IR_TC = open, 50% to 90%                             |                        | 35        | 50                   | μs    |

| V <sub>TIMER</sub>                    | Fault timer threshold voltage                           | Rising; detecting a fault<br>Falling; detecting end of rest state                                 | 98<br>19               | 100<br>20 | 102<br>21            | %VREF |

| V <sub>TIMER</sub>                    | Fault timer discharge voltage                           | At full discharge state                                                                           |                        |           | 100                  | mV    |

| T <sub>TIMER_PD</sub>                 | Fault timer trip to SHDN                                | Rising or falling fault timer. TIMER driven with external 0V to 5V square wave                    |                        |           | 5                    | μs    |

| IR_TC                                 |                                                         |                                                                                                   |                        |           |                      |       |

| V <sub>I_SET</sub>                    | IR_TC accuracy                                          | $0.2V < V_{IR_{TC}} < VREF, V_{LINE} - (V_{I_{SET}} + V_{IR_{TC}})$                               | -100                   | 0         | 100                  | mV    |

|                                       | IR_TC current sink                                      | $0.2V < V_{I RC} < VREF, R_{I DCH CC} = 10k\Omega$                                                | 96                     | 100       | 104                  | μA    |

|                                       | IR_TC current source                                    | $0V < V_{I RC} < VREF, R_{I DCH CC} = 10k\Omega$                                                  | -104                   | -100      | -96                  | μA    |

| V <sub>IR_TC</sub>                    | VIR_TC Off Voltage                                      | $R_{I DCH CC} = 10k\Omega$                                                                        |                        | 20        | 100                  | mV    |

| Logic Input SHDN                      |                                                         |                                                                                                   |                        |           |                      |       |

| 0                                     | Input logic high level                                  |                                                                                                   | 2.0                    |           |                      |       |

| V <sub>SHDN</sub>                     | Input logic low level                                   | SHDN as input                                                                                     |                        |           | 0.8                  | V     |

|                                       | Leakage Current                                         | SHDN as input; 0V < V <sub>SHDN</sub> < V <sub>LS_RAIL</sub>                                      | -50                    |           | 50                   | μA    |

| Logic Outputs STA                     | ATUS, OT_FLT, SHDN                                      |                                                                                                   |                        |           |                      |       |

|                                       |                                                         | High output voltage: 10kO pull up to LC DAIL                                                      | V <sub>LS_RAIL</sub> - |           | V                    | V     |

| $V_{STATUS}, V_{\overline{OT}\_FLT},$ | Logic levels                                            | High output voltage; 10kΩ pull-up to LS_RAIL                                                      | 0.5V                   |           | V <sub>LS_RAIL</sub> | v     |

| V <sub>SHDN</sub>                     | SHDN as output                                          | Low output voltage; I <sub>SINK</sub> = 1mA                                                       | 0                      |           | 0.5                  | V     |

|                                       |                                                         | I <sub>SINK</sub> internal current limit                                                          | 2                      |           | 10                   | mA    |

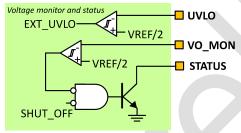

|                                       | Itage Lockout (UVLO)                                    |                                                                                                   |                        |           |                      |       |

| V <sub>UVLO</sub>                     | Voltage threshold                                       | Voltage rising                                                                                    | 49                     | 50        | 51                   | %VREF |

| V <sub>UVLO</sub>                     | Hysteresis                                              |                                                                                                   | 1                      | 3         | 4                    | %VREF |

| I <sub>UVLO</sub>                     | UVLO monitor leakage                                    | 0V < V <sub>UVLO</sub> < V <sub>LS_RAIL</sub>                                                     | -10                    |           | 10                   | μA    |

| T <sub>D UVLO</sub>                   | UVLO to STATUS delay time                               | UVLO 5V to 0V step, $R_{STATUS}$ = 10k $\Omega$ , $C_{STATUS}$ = 100pF, 50% to 50%                | 0.5                    |           | 1.5                  | ms    |

| VO_MON                                |                                                         |                                                                                                   |                        |           |                      |       |

| V <sub>VO_MON</sub>                   | VO_MON threshold                                        | Voltage rising                                                                                    | 49                     | 50        | 51                   | %VREF |

| Vvo_mon                               | VO_MON hysteresis                                       | Hysteresis                                                                                        | 1                      | 3         | 4                    | %VREF |

| Ivo_mon                               | VO_MON leakage                                          | 0 < V <sub>VO_MON</sub> < V <sub>LS_RAIL</sub>                                                    | -10                    |           | 10                   | μA    |

| T <sub>D VO_MON</sub>                 | VO_MON to STATUS delay time                             | VO_MON 5V to 0V step, $R_{STATUS}$ = 10k $\Omega$ , $C_{STATUS}$ = 100pF, 50% to 50%              |                        | TBD       |                      | μs    |

| <b>Over Temperature</b>               | Detect                                                  |                                                                                                   |                        |           |                      |       |

| TEMPot                                | Over temperature threshold                              | Shutdown (die temperature rising)                                                                 | 150                    |           | 175                  | °C    |

|                                       | Over temperature<br>hysteresis                          | Reset (die temperature falling)                                                                   | 25                     | 50        | 60                   | °C    |

| t <sub>TEMP</sub>                     | Reaction time                                           | Delay from die temp threshold event to OT fault detection                                         |                        | 1         | 2                    | ms    |

### 8 Thermal Properties

Thermal resistance,  $\theta_{JB}$ , is provided from die to the back surface of the package. Junction temperature  $T_J$  is calculated using  $T_J = T_B + (PD \times \theta_{JB})$ , where  $T_B$  is the temperature maintained on the back surface of the package.

| Package | Thermal Resistance | Тур | Units |

|---------|--------------------|-----|-------|

| HTF-48  | $\theta_{JB}$      | 1.2 | °C/W  |

### 9 Heatsink Recommendations

The LX7712 dissipates up to 1W (200mV x 5A) at full normal load, and so thermal considerations are usually necessary even in applications where additional energy absorption under fault conditions is small. The base of the metal package should be used as the heat conducting surface for all but light duty applications. The metal package top is attached to the package body at the top of relatively thin cavity walls, and so has a much higher thermal resistance from the die than the base of the package. It is recommended to apply a thermal interface material between the base of the package and the heat dissipater. The heat dissipater can be copper layers within a multilayer circuit board to spread heat laterally across the board, or a direct mounted dissipation element.

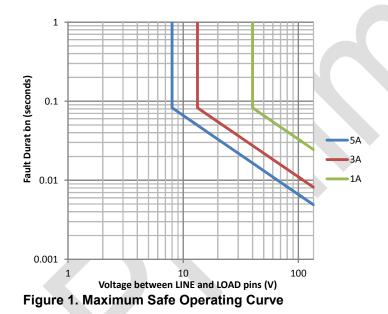

### 10 Safe Operating Area

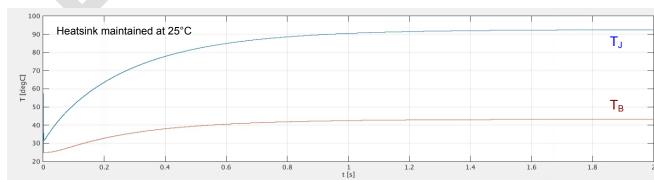

The safe operating area curve in Figure 1 shows the maximum operating time allowed versus voltage drop between LINE input and LOAD output for a given current limit setting with a 25°C heat sink. The device can dissipate 40W indefinitely if connected to a 25°C heat sink, and that the maximum safe limit energy dissipated during a current limit pulse is 3.2J. Peak die temperature increase due to a short pulse of 3.2J is 32°C as the energy is mostly absorbed in the die initially. Junction temperature stabilizes at nominally  $92^{\circ}C - 25^{\circ} = 67^{\circ}$  above heatsink temperature under 40W dissipation (Figure 2), with the package base rising to  $92^{\circ}C - (40W \times 1.2^{\circ}C/W) = 44^{\circ}C$ .

Figure 2. Die and Package Base Temperature Rise Over Time with 40W Dissipation

© 2021 Microchip Technology Inc.

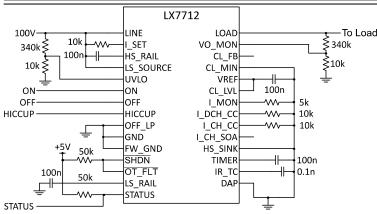

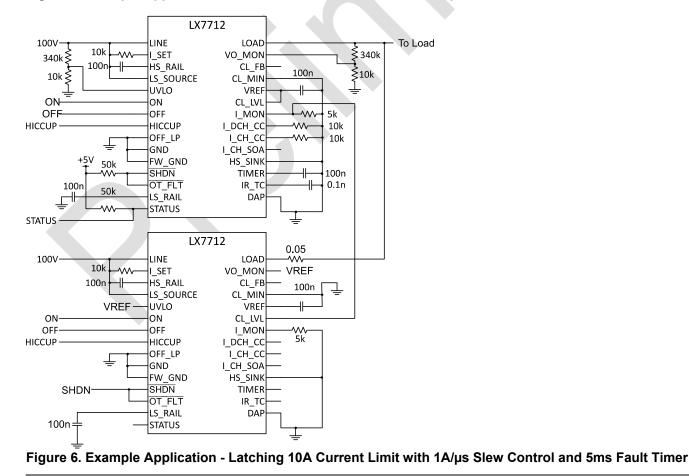

Figure 4. Example Application - Latching 5A Current Limit with 1A/µs Slew Control and 5ms Fault Timer

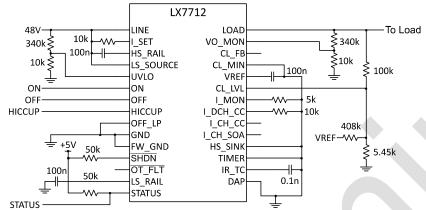

Figure 5. Example Application - Foldback 5A Current Limit with 1A/µs Slew Control

© 2021 Microchip Technology Inc.

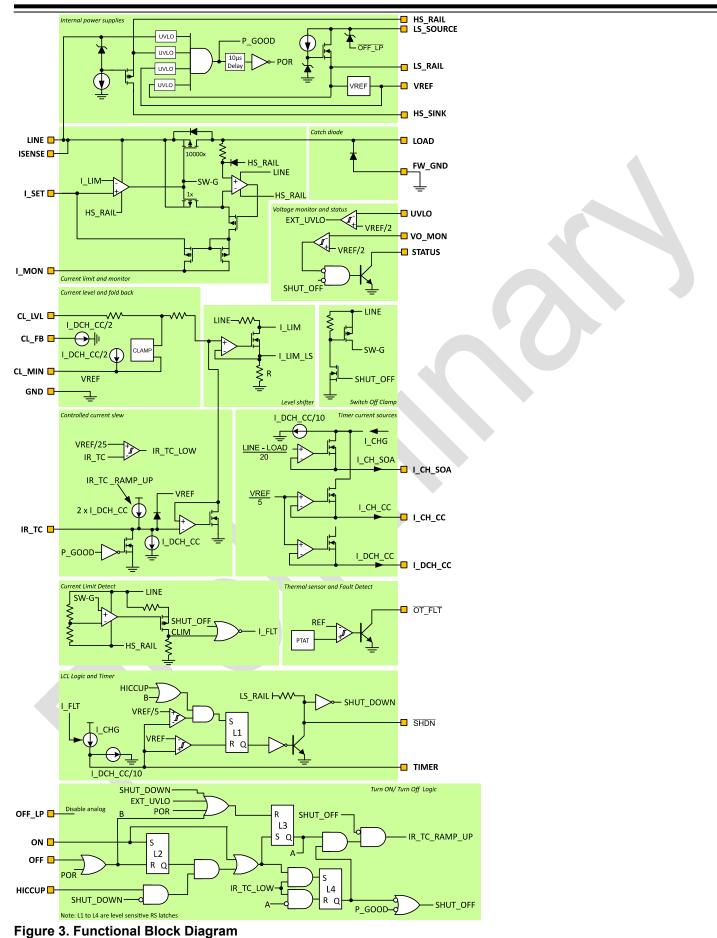

### 11 LX7712 System Outline

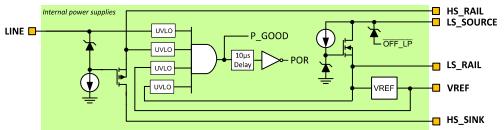

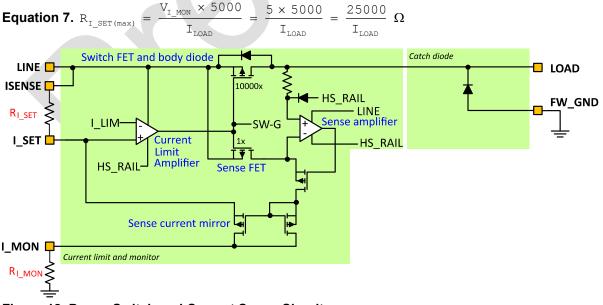

The LX7712 is a versatile, configurable, resettable e-fuse with integrated PMOS power switch rated at 5A continuous current. The current sensing is performed using a SenseFET which contains a tiny current sense FET buried in the main switch FET body. A closed-loop amplifier matches the operating conditions of the current sense device to the power switch, which ensures that the sense current represents a consistent fraction of the power switch current.

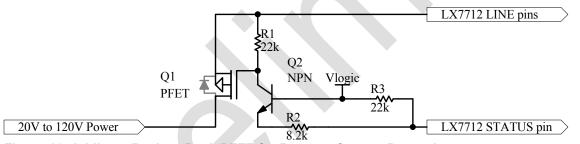

The LX7712's power switch has a reverse body diode, as shown in the Functional Block Diagram on page 10, which provides a path from the LOAD output to the LINE input when the power switch is turned off. See section 17 on page 25 for details how to add an external reverse PFET to block the reverse path automatically when the LX7712 is off.

The LX7712 functional blocks are:

- Internal power supplies and voltage reference (section 12 on page 12)

- ON, OFF, and OFF\_LP control inputs (section 13 on page 15)

- Internal under-voltage lockouts and LINE and LOAD voltage monitoring and (sections 13.1 and 13.2 on page 16)

- STATUS output and SHDN I/O (sections 13.3 and 13.4 on page 16)

- Over-temperature detection (section 13.5 on page 16)

- Current monitoring system (section 14 on page 17)

- Current limiting with current ramp control, and a hard or foldback current limit options (section 15 on page 18)

- Overload fault energy integration fault timer and hiccup fault recovery fault timer (section 16 on page 21)

### 12 Power Supplies, Voltage Reference, and Decoupling

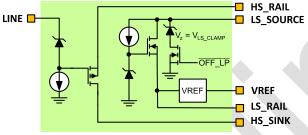

The LX7712 generates two internal rails to operate the internal control circuits, HS\_RAIL and LS\_RAIL, and an internal 5V reference, VREF (Figure 7). LINE, HS\_RAIL, LS\_RAIL, and VREF have independent under-voltage detectors which will cause the LX7712 to shut off the power switch if any rail falls too low (section 13.1 on page 16).

Figure 7. HS\_RAIL, LS\_RAIL, and VREF

#### 12.1 Reference Output VREF

The reference is available to bias the external resistor configuration networks and is accurate to  $\pm 4\%$  over LINE voltage variations with external loading up to 2mA, plus another  $\pm 1\%$  tolerance over the -55°C to +125°C temperature range. Bypass VREF with a 100nF capacitor to GND, even if no external loading is applied.

#### 12.2 HS\_SINK and HS\_RAIL

HS\_RAIL is the output of an internal linear regulator which floats at 10V ±1V below LINE. Bypass HS\_RAIL with a 100nF capacitor to LINE. HS\_RAIL only sinks current (acts as a return).

The HS\_RAIL regulator's input is the HS\_SINK pin, to be connected to a voltage at least 12V below VLINE, typically GND. This regulator dissipates typically { $V_{LINE}$  - 10} mW. For higher LINE voltages, such as above 60V, it is helpful to connect HS\_SINK to GND via a series resistor to move some dissipation off-chip. A suitable resistance would be:

Equation 1:  $R_{HS_SINK} = 600 \times (V_{LINE(min)} - 12) \Omega \pm 0$

where  $V_{\text{LINE(min)}}$  is the lowest LINE input voltage expected.

So, for an example application where V<sub>LINE</sub> varies from 80V to 120V:  $R_{HS SINK} = 600 \times (80 - 12) = 40.8 \text{k}\Omega \pm 10\%$

Since the maximum draw from HS\_RAIL is 1.5mA, maximum  $R_{\text{HS}\_SINK}$  dissipation will be 1.5mA<sup>2</sup> × 40.8k $\Omega$  = 91.8mW at the nominal resistor value.

#### 12.3 LS\_SOURCE and LS\_RAIL

LS\_RAIL is the output of an internal linear regulator which delivers  $10V \pm 1V$  above GND. Bypass LS\_RAIL with a 100nF to  $2.2\mu$ F capacitor to GND. LS\_RAIL can source up to 5mA to external loads in addition the 10mA max it provides to the internal circuits.

The LS\_RAIL regulator's input is the LS\_SOURCE pin, which has an internal 33V nominal (32V to 36V) Zener clamp to GND. The clamp is enabled in normal operation and disabled in low power shutdown when OFF\_LP is high (Figure 7 on page 12). The purpose of the 33V Zener clamp is to assist in managing dissipation in the LS\_RAIL regulator pass element, which is rated at 225mW. The Zener is rated at an additional 225mW.

When the LX7712 is put into sleep mode via OFF\_LP pin, the Zener clamp is disconnected. Since no current is shunted by the Zener, current consumption is just the LX7712's sleep mode current.

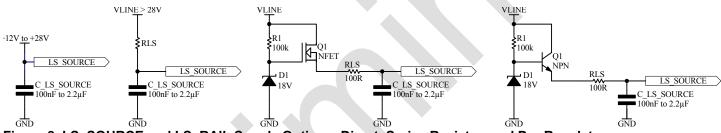

Table 1 and Figure 8 below show the options for powering LS\_SOURCE and LS\_RAIL.

| LINE Voltage                 | LS_SOURCE and LS_RAIL Connection                                                                                |

|------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Any                          | Connect LS_SOURCE and LS_RAIL together to an external 10V ±1V supply                                            |

| Any                          | Connect LS_SOURCE to an existing 12V to 28V supply, which can be LINE if within this range                      |

| $V_{\text{LINE(MAX)}} > 28V$ | Connect LS_SOURCE to LINE via a series resistor.<br>Note: VLINE(MIN) > 12V, and (VLINE(MAX) - VLINE(MIN)) ≤ 20V |

|                              | Connect LS_SOURCE to LINE via a 12V to 28V NMOS or NPN pre-regulator (Figure 8)                                 |

Table 1. LS\_SOURCE and LS\_RAIL Supply Options

Figure 8. LS\_SOURCE and LS\_RAIL Supply Options: Direct, Series Resistor, and Pre-Regulator

If LS\_SOURCE is to be supplied from the LINE supply greater than 28V, a single series can be used if the range of LINE variation is 20V or less. The equations below and examples show that the limitation is the dissipation of the internal Zener diode. For wide ranging LINE input, a simple pre-regulator is recommended. This is a source/emitter follower using an NMOS or NPS pass transistor. The 100 $\Omega$  resistor limits the peak charging current into the output capacitor on power-up.

The equations to calculate the resistor between LINE and LS\_SOURCE pin use:

V<sub>LINE(MAX)</sub> is the maximum line input voltage

V<sub>LINE(MIN)</sub> is the minimum line input voltage

$V_{Z(MIN)}$  is the minimum Zener voltage (32V)

Iz is the current passing through the Zener

V<sub>LS\_SOURCE(MIN)</sub> is the minimum allowed LS\_SOURCE voltage (12V)

ILS\_SOURCE(MAX) is the maximum LS\_SOURCE current draw (10mA)

I<sub>LS\_SOURCE(MIN)</sub> is the minimum LS\_SOURCE current draw (3.5mA)

R<sub>LS</sub> is the resistor between LINE and LS\_SOURCE pin

The maximum allowed series resistance is set by the minimum LINE voltage and maximum current:

Equation 2:  $R_{LS (MAX)} = \frac{V_{LINE (MIN)} - V_{LS_{SOURCE (MIN)}}}{I_{LS SOURCE (MAX)}} = \frac{V_{LINE (MIN)} - 12}{10 \text{mA}} \Omega$

This allows  $R_{LS}$  to be chosen, with tolerance range from  $R_{LS(MAX) to} R_{LS(MIN)}$ .

At  $V_{\text{LINE}(MAX)}$  the maximum current that can pass through the Zener can be calculated. There are two possible maximum currents, using tolerance limits:

Equation 3:

$$I_{Z (MAX)} = \frac{V_{\text{LINE (MAX)}} - V_{Z (MIN)}}{R_{\text{LSMIN}}} - I_{\text{LS}_{\text{SOURCEMIN}}} = \left[\frac{V_{\text{LINE (MAX)}} - 32}{R_{\text{LSMIN}}} - 3.5 \text{mA}\right] \text{A}$$

Equation 4:  $I_{Z (MAX)} = \frac{V_{\text{LINE (MAX)}} - V_{Z (MAX)}}{R_{\text{LSMIN}}} - I_{\text{LS}_{\text{SOURCEMIN}}} = \left[\frac{V_{\text{LINE (MAX)}} - 36}{R_{\text{LSMIN}}} - 3.5 \text{mA}\right] \text{A}$

**Example specification 1**: V<sub>LINE</sub> = 22V to 38V From Equation 2:

$R_{\rm LS(MAX)} = \frac{22 - 12}{10 \text{mA}} = 1000 \Omega$

Choosing  $R_{LS}$  to be 950 $\Omega$  ±50 $\Omega$ ,  $R_{LS(MIN)}$  = 900 $\Omega$

From Equation 3:

$I_{Z(MAX)} = \left[\frac{38 - 32}{900} - 3.5 \text{mA}\right] = 3.17 \text{mA}$

Zener dissipation is 32V x 3.17mA = 101mW, under the 225mW limit

**Example specification 2**: V<sub>LINE</sub> = 20V to 40V From Equation 2:

$R_{\rm LS\,(MAX)} = \frac{20 - 12}{10 \text{mA}} = 800\Omega$

Choosing R<sub>LS</sub> to be 787 $\Omega$  ±1%, R<sub>LS(MIN)</sub> = 779.1 $\Omega$

#### From Equation 3:

$I_{Z(MAX)} = \left[\frac{40 - 32}{779.1} - 3.5 \text{mA}\right] = 6.77 \text{mA}$

Zener dissipation is 32V x 6.77mA = 217mW, under the 225mW limit

#### **Example specification 3**: V<sub>LINE</sub> = 100V to 120V From Equation 2:

$R_{LS(MAX)} = \frac{100 - 12}{10mA} = 8800\Omega$

Choosing  $R_{LS}$  to be 8.66k $\Omega$  ±1%,  $R_{LS(MIN)}$  = 8.57k $\Omega$

From Equation 3:  $I_{Z (MAX)} = \left[\frac{120 - 32}{8.57k} - 3.5mA\right] = 6.76mA$

Zener dissipation is 32V x 6.76mA = 216mW, under the 225mW limit

From Equation 4:

$I_{Z(MAX)} = \left[\frac{120 - 36}{8.57k} - 3.5mA\right] = 6.30mA$

Zener dissipation is 36V x 6.30mA = 227mW, just over the 225mW limit.  $R_{LS}$  needs to be 8.66k $\Omega$  ±0.5% to pass.

### 13 On and Off Controls

The basis of the power switch's on/off mechanism is an internal RS latch operated by the ON and OFF logic inputs, which initiate a programmable slew rate control which limits the rate of the load current increase during turn-on, and decrease during turn-off (see the Current Limiting and Slew Rate Limiting section on page 18).

There is negligible difference in LX7712 power consumption whether the power switch is on or off. The optional OFF\_LP input reduces power consumption for long standby periods by powering down much of the internal circuitry. The OFF\_LP input is not latched, unlike the ON and OFF inputs, and must be maintained logic high to assert low power mode. Taking OFF\_LP high overrides the ON and OFF inputs. The OFF and OFF\_LP inputs can be tied together, and a 1µs to 10µs pulse high used to set the internal RS latch OFF without the LX7712 entering low power mode ( $C_{LS_SOURCE} \ge 100$ nF).

The power switch is turned on by a logic-high level (or a high pulse  $\geq 1\mu$ s) on the ON input. The ON control is overridden, and the power switch turned off, by either a logic input (OFF, OFF\_LP, or SHDN), by the UVLO comparator input, by a latched current limit fault, or by under-voltage on a supply rail.

| atorica current infint laun, or by under-volta                                                                                                                                                                                   | ge on a supply to          |                                                                                                        |                    |                                                                                                                  |                                     |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|

| Control Mode                                                                                                                                                                                                                     | UVLO Input<br>pin 27       | SHDN I/O<br>pin 47                                                                                     | ON Input<br>pin 40 | OFF Input<br>pin 39                                                                                              | OFF_LP Input<br>pin 38              |  |

| Normal On/Off Operation in either LCL Mode                                                                                                                                                                                       | e (HICCUP = low c          | or hi-z) or RLCL Mode (H                                                                               | IICCUP = hig       | gh)                                                                                                              |                                     |  |

| Switch on via ON input with slew control in LCL Mode (HICCUP = low or hi-z))                                                                                                                                                     |                            | High                                                                                                   | or f               | Low                                                                                                              | Low                                 |  |