# Synopsys FPGA Synthesis Synplify Pro for Microsemi Edition

**Command Reference**

May 2015

# **Copyright Notice and Proprietary Information**

Copyright © 2015 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

# **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only.

Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

"This document is duplicated with the permission of Synopsys, Inc., for the exclusive use of \_\_\_\_\_\_ and its employees. This is copy number \_\_\_\_\_\_."

## **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

## Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

# **Registered Trademarks (®)**

Synopsys, AEON, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, CHIPit, CoMET, CODE V, Design Compiler, DesignWare, EMBED-IT!, Formality, Galaxy Custom Designer, Global Synthesis, HAPS, HapsTrak, HDL Analyst, HSIM, HSPICE, Identify, Leda, LightTools, MAST, METeor, ModelTools, NanoSim, NOVeA, OpenVera, ORA, PathMill, Physical Compiler, PrimeTime, SCOPE, Simply Better Results, SiVL, SNUG, SolvNet, Sonic Focus, STAR Memory System, Syndicated, Synplicity, the Synplicity logo, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, UMRBus, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

## Trademarks (™)

AFGen, Apollo, ARC, ASAP, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Cosmos, CosmosLE, CosmosScope, CRITIC, CustomExplorer, CustomSim, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, DesignerHDL, DesignPower, DFTMAX, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, HANEX, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping System, HSIMplus, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Intelli, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Macro-PLUS, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, ORAengineering, Physical Analyst, Planet, Planet-PL, Polaris, Power Compiler, Raphael, RippledMixer, Saturn, Scirocco, Scirocco-i, SiWare, Star-RCXT, Star-SimXT, StarRC, System Compiler, System Designer, Taurus, Total-Recall, TSUPREM-4, VCSi, VHDL Compiler, VMC, and Worksheet Buffer are trademarks of Synopsys, Inc.

# Service Marks (sm)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license.

ARM and AMBA are registered trademarks of ARM Limited.

Saber is a registered trademark of SabreMark Limited Partnership and is used under license.

All other product or company names may be trademarks of their respective owners.

Printed in the U.S.A May 2015

# Contents

## **Chapter 1: Introduction**

| About Tcl Commands     | 8  |

|------------------------|----|

| About the GUI Commands | 10 |

| Document Set           | 2  |

## **Chapter 2: Tcl Commands**

| Alphabetical List of Commands14 |

|---------------------------------|

| add_file                        |

| add_folder                      |

| check_fdc_query                 |

| command_history                 |

| constraint_file                 |

| create_fdc_template             |

| encryptIP                       |

| encryptP1735                    |

| get_env                         |

| get_option                      |

| hdl_define                      |

| hdl_param                       |

| impl                            |

| job                             |

| log_filter                      |

| log_report                      |

| message_override                |

| open_design                     |

| open_file                       |

| partdata                        |

|       | program_terminate  |

|-------|--------------------|

|       | program_version    |

|       |                    |

|       | project_data       |

|       | project_file       |

|       | project_folder     |

|       | recording          |

|       | report_clocks      |

|       | run tcl            |

|       | sdc2fdc            |

|       | set_option         |

|       |                    |

|       | status_report      |

|       | synplify_pro       |

| Tcl ( | Command Categories |

## Chapter 3: Tcl Find, Expand, and Collection Commands

| find                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| find -filter                                                                                                                                                                                                                                                                                                                                          |

| expand                                                                                                                                                                                                                                                                                                                                                |

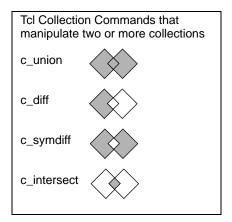

| Collection Commands       110         c_diff       111         c_info       112         c_intersect       112         c_list       113         c_print       114         c_symdiff       114         c_union       115         define_collection       116         define_scope_collection       117         get_prop       117         set       117 |

| Query Commands         119           all_clocks         122           all_fanin         122                                                                                                                                                                                                                                                           |

| all_fanout                                                                                                                                                                                                                                                                                                                                            |

| all_registers                                                                                                                                                                                                                                                                                                                                         |

| get_cells       126         get_clocks       130         get_clock_source       132         get_nets       132         get_pins       134         get_ports       136         object_list       138         report_timing       138 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synopsys Standard Collection Commands142                                                                                                                                                                                            |

| add_to_collection                                                                                                                                                                                                                   |

| append_to_collection                                                                                                                                                                                                                |

| copy_collection                                                                                                                                                                                                                     |

| foreach_in_collection                                                                                                                                                                                                               |

| get_object_name                                                                                                                                                                                                                     |

| index_collection                                                                                                                                                                                                                    |

| remove_from_collection                                                                                                                                                                                                              |

| sizeof_collection                                                                                                                                                                                                                   |

## **Chapter 4: User Interface Commands**

| File Menu       New Command         New Command       Create Image Command         Build Project Command       Open Project Command                     | . 155<br>. 156<br>. 158                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Edit Menu<br>Find Command (Text)<br>Find Command (In Project)<br>Find Command (HDL Analyst)<br>Find in Files Command<br>Replace Command<br>Goto Command | . 161<br>. 162<br>. 164<br>. 168<br>. 170 |

| View Menu<br>Toolbar Command<br>View Sheets Command<br>View Log File Command                                                                            | . 175<br>. 176                            |

| Project Menu<br>Add Source File Command<br>Change File Command<br>Set VHDL Library Command<br>Add Implementation Command                                | . 181<br>. 183<br>. 184                   |

| Convert Vendor Constraints Command184Archive Project Command185Un-Archive Project Command186Copy Project Command189Hierarchical Project Options Command192                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Implementation Options Command193Device Panel194Options Panel196Constraints Panel198Implementation Results Panel200Timing Report Panel201High Reliability Panel203VHDL Panel204Verilog Panel207Compiler Directives and Design Parameters210Place and Route Panel218                                                                                                                                       |

| Import Menu                                                                                                                                                                                                                                                                                                                                                                                               |

| Run Menu220Run Tcl Script Command223Run Implementations Setup Command224Job Status Command226Launch Identify Instrumentor Command226Launch Identify Debugger Command228Launch SYNCore Command228SYNCore FIFO Wizard230SYNCore RAM Wizard240SYNCore Byte-Enable RAM Wizard247SYNCore ROM Wizard247SYNCore Adder/Subtractor Wizard251SYNCore Counter Wizard255Configure and Launch VCS Simulator Command257 |

| Analysis Menu                                                                                                                                                                                                                                                                                                                                                                                             |

| HDL Analyst Menu279HDL Analyst Menu: RTL and Technology View Submenus279HDL Analyst Menu: Hierarchical and Current Level Submenus280HDL Analyst Menu: Filtering and Flattening Commands282HDL Analyst Menu: Timing Commands286HDL Analyst Menu: Analysis Commands286                                                                                                                                      |

| HDL Analyst Menu: Selection Commands       290         HDL Analyst Menu: FSM Commands       290                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Options Menu       29         Configure Compile Point Process Command       292         Project View Options Command       298         Editor Options Command       300         Place and Route Environment Options Command       300         Project Status Page Location       303         HDL Analyst Options Command       305         Configure External Programs Command       315 |

| Web Menu       314         Check Resource Center Messages Command       315         Configure Resource Center Command       317                                                                                                                                                                                                                                                          |

| Help Menu       318         Preferred License Selection Command       319         Tip of the Day Command       320                                                                                                                                                                                                                                                                       |

## **Chapter 5: GUI Popup Menu Commands**

| Popup Menus                                       | 322 |

|---------------------------------------------------|-----|

| Watch Window Popup Menu                           |     |

| Tcl Window Popup Menu                             |     |

| Text Editor Popup Menu                            | 323 |

| Log File Popup Menu                               | 323 |

| FSM Viewer Popup Menu                             | 326 |

| Project View Popup Menus                          | 329 |

| Project Management View Popup Folder Commands     |     |

| File Options Popup Menu Command                   |     |

| Copy File Popup Menu Command                      |     |

| Change Implementation Popup Menu Commands         |     |

| Show Compile Points Popup Menu Command            | 338 |

| Project Options Popup Menu Command                | 338 |

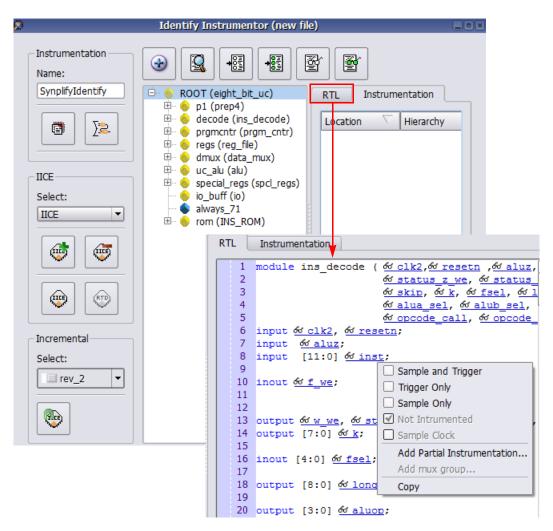

| Identify Instrumentor Popup Menu Command          | 339 |

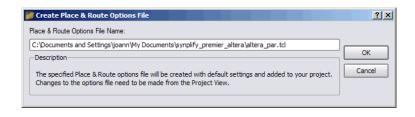

| Add P&R Implementation Popup Menu Command         | 343 |

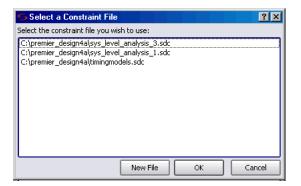

| Options for Place & Route Jobs Popup Menu Command | 345 |

| RTL and Technology Views Popup Menus              | 347 |

# CHAPTER 1 Introduction

This document is part of a set that includes reference and procedural information for the Synopsys<sup>®</sup> Synplify Pro<sup>®</sup> FPGA synthesis tool.

This document describes the commands available in the synthesis tools.

This chapter includes the following introductory information:

- About Tcl Commands, on page 8

- About the GUI Commands, on page 10

- Document Set, on page 12

# About Tcl Commands

Tcl (Tool Command Language) is a popular scripting language for controlling software applications. Synopsys has extended the Tcl command set with additional commands that you can use to run the Synopsys FPGA programs. These commands are not intended for use in controlling interactive debugging, but you can use them to run synthesis multiple times with alternate options to try different technologies, timing goals, or constraints on a design.

Tcl scripts are text files that have a tcl file extension and contain a set of Tcl commands designed to complete a task or set of tasks. You can also run Tcl scripts through the Tcl window (see Tcl Script Window, on page 54).

The Synopsys FPGA Tcl commands are described here. For information on the standard Tcl commands, syntax, language, and conventions, refer to the Tcl online help (Help->TCL Help).

## **Tcl Conventions**

Here is a list of conventions to respect when entering Tcl commands and/or creating Tcl scripts.

- Tcl is case sensitive.

- Comments begin with a hash mark or pound sign (#).

- Enclose all path names and filenames in double quotes (").

- Use a forward slash (/) as the separator between directory and path names (even on the Microsoft<sup>®</sup> Windows<sup>®</sup> operating system). For example:

```

designs/big_design/test.v

```

## **Tcl Scripts and Batch Mode**

For procedures for creating Tcl scripts and using batch mode, see Working with Tcl Scripts and Commands, on page 474 in the *User Guide*:

- Running Batch Mode on a Project File, on page 468

- Running Batch Mode with a Tcl Script, on page 469

- Generating a Job Script, on page 475

- Creating a Tcl Synthesis Script, on page 476

- Using Tcl Variables to Try Different Clock Frequencies, on page 478

- Running Bottom-up Synthesis with a Script, on page 480

# About the GUI Commands

The FPGA synthesis tools include a graphical user interface (GUI) as well as a command line capability. Most commands have GUI and command line versions, so you can use either method to specify commands.

The commands that are available vary with the capabilities of synthesis tools. The following sections give you an overview of the commands in various tools:

- Graphic User Interface Commands, on page 10

- Tcl Commands, on page 12

## **Graphic User Interface Commands**

The GUI commands are accessed from the software graphical interface. Most commands open dialog boxes where you can specify parameters for the command.

The GUI provides a few ways to access commands:

- Menus, on page 10

- Context-sensitive Popup Menus, on page 11

- Toolbars, on page 11

- Keyboard Shortcuts, on page 11

- Buttons and Options, on page 12

- Tcl Commands, on page 12

#### Menus

The set of commands on the pull-down menus in the menu bar varies depending on the view, design status, task to perform, and selected object(s). For example, the File menu commands in the Project view differ slightly from those in the RTL view. Menu commands that are not available for the current context are greyed out. The menu bar in the Project view is shown below:

Eile Edit View Project Import Run Analysis HDL-Analyst Options Window Tech-Support Web Help

The individual menus, their commands, and the associated dialog boxes are described in the following sections:

- File Menu, on page 154

- Edit Menu, on page 159

- View Menu, on page 172

- Project Menu, on page 180

- Import Menu, on page 219

- Run Menu, on page 220

- Analysis Menu, on page 267

- HDL Analyst Menu, on page 279

- Options Menu, on page 291

- Web Menu, on page 314

- Help Menu, on page 318

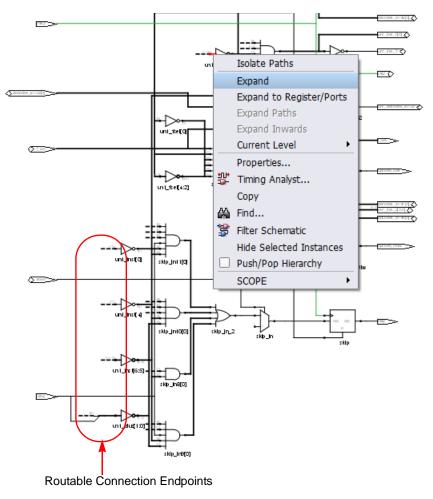

### **Context-sensitive Popup Menus**

Popup menus, available by right-clicking, offer access to commonly used commands that are specific to the current context. See Popup Menus, on page 322, Project View Popup Menus, on page 329, and RTL and Technology Views Popup Menus, on page 347 for information on individual popup menus.

## Toolbars

Toolbars contain icons associated with commonly used commands. For more information about toolbars, see Toolbars, on page 82.

## **Keyboard Shortcuts**

Keyboard shortcuts are available for commonly used commands. The shortcut appears next to the command in the menu. See Keyboard Shortcuts, on page 90 for details.

### **Buttons and Options**

The Project view has buttons for quick access to commonly used commands and options. See Buttons and Options, on page 98 for details.

## **Tcl Commands**

You can enter the Tcl (Tool Command Language) commands directly in the Tcl window, or include them in Tcl scripts that you can run in batch mode. For more information about Tcl commands, see Tcl Commands, on page 13.

the online help sidebar has three tabs (Contents, Index, and Bookmarks) with the Contents tab active.

# **Document Set**

This document is part of a series of books included with the Synopsys FPGA synthesis software tools. The set consists of the following books that are packaged with the tool:

- FPGA Synthesis User Guide

- FPGA Synthesis Reference Manual

- FPGA Command Reference Manual

- FPGA Attributes and Directives Manual

## CHAPTER 2

# **Tcl Commands**

This chapter describes supported Tcl commands. The Tcl commands appear in alphabetical order.

- Alphabetical List of Commands, on page 14

- Tcl Command Categories, on page 88

# Alphabetical List of Commands

The commands are listed in alphabetical order. The find, expand, and collection commands appear in the table, but are described in Tcl Find, Expand, and Collection Commands, on page 89.

| add_file              | add_folder              |

|-----------------------|-------------------------|

| add_to_collection     | all_clocks              |

| all_fanin             | all_fanout              |

| all_inputs            | all_outputs             |

| all_registers         | append_to_collection    |

| c_diff                | c_info                  |

| c_intersect           | c_list                  |

| c_print               | c_symdiff               |

| c_union               | check_fdc_query         |

| command_history       | constraint_file         |

| copy_collection       | create_fdc_template     |

| define_collection     | define_scope_collection |

| encryptIP             | encryptP1735            |

| expand                | find (Tcl find)         |

| foreach_in_collection | get_cells               |

| get_clocks            | get_clock_source        |

| get_env               | get_nets                |

| get_object_name       | get_option              |

| get_pins              | get_ports               |

| get_prop              | hdl_define              |

| hdl_param             | impl                    |

| index_collection      | job                     |

| log_filter            | log_report              |

| message_override       | object_list       |

|------------------------|-------------------|

| open_design            | open_file         |

| partdata               | program_terminate |

| program_version        | project           |

| project_data           | project_file      |

| project_folder         | recording         |

| remove_from_collection | report_clocks     |

| report_timing          | run_tcl           |

| sdc2fdc                | set               |

| set_option             | sizeof_collection |

| status_report          | synplify_pro      |

## add\_file

The add\_file command adds one or more files to a project.

## Syntax

| <pre>add_file [-filetype] fileName [ fileName [] ] add_file -verilog fileName [ fileName [] ] [-folder folderName] add_file -vhdl [-lib libName[ libName] fileName [ fileName [] ] [-folder folderName] add_file -include fileName [ fileName [] ] add_file [-filetype] -job_owner par   simulation [ fileName [] ] add_file -structver [fileName [] ] add_file -vlog_std standard fileName [ fileName [] ]</pre> |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -filetype                                                                                                                                                                                                                                                                                                                                                                                                         | Specifies the type of file being added to the project (files are<br>placed in folders according to their file types; including<br>this argument overrides automatic filename-extension<br>placement). See Filename Extensions, on page 18 for a<br>list of the recognized file types.                                                                                                                                |  |

| fileName                                                                                                                                                                                                                                                                                                                                                                                                          | Specifies the name of the file being added to the project.<br>Files are added to the individual project folders according<br>to their filename extensions (View Project Files in Folders must<br>be set in the Project View Options dialog box). You can add<br>multiple files by separating individual filenames with a<br>space, and you can specify different file types (extensions)<br>within the same command. |  |

| -verilog or -vhdl                                                                                                                                                                                                                                                                                                                                                                                                 | Adds HDL files with non-standard extensions to the Verilog<br>or VHDL directory, so that they can be compiled with the<br>project. For example, the following command adds the file<br>alu.v.new to the project's verilog directory:                                                                                                                                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                   | <pre>% add_file -verilog /designs/megachip/alu.v.new</pre>                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                   | If you do not specify -verilog, the file is added to the Other<br>directory (new is not a recognized Verilog extension), and<br>the file would not be compiled with the files in the Verilog<br>directory.                                                                                                                                                                                                           |  |

| [-lib <i>libName</i> ] | Specifies the library associated with VHDL files. The default library is work. The -lib option sets the VHDL library to <i>libName</i> .                                                                                                                                                                                                                                                                                                                              |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                        | Note: You can also specify multiple libraries for VHDL files.<br>For example:                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                        | add_file -vhdl -lib {mylib,work} "ff.vhd"                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                        | Both the logical and physical libraries must be specified in<br>the Project file (if you only specify the logical library<br>associated with the VHDL files, the compiler treats the<br>module as a black box).                                                                                                                                                                                                                                                       |  |

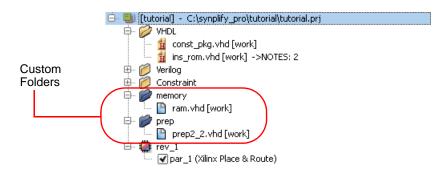

| [-folder folderName]   | Creates logical folders with custom files in various<br>hierarchy groupings within your Project view. For example:                                                                                                                                                                                                                                                                                                                                                    |  |

|                        | add_file -verilog -folder memory "ram_1.v"                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                        | add_file -verilog -folder memory<br>"C:/examples/verilog/common_rtl/memory/ram_1.v"                                                                                                                                                                                                                                                                                                                                                                                   |  |

| -include               | Indicates that the specified file is to be added to the project<br>as an include file (include files are added to the Include<br>directory regardless of their extension). Include files are<br>not passed to the compiler, but are assumed to be<br>referenced from within the HDL source code. Adding an<br>include file to a project, although not required, allows it to<br>be accessed in the user interface where it can be viewed,<br>edited, or cross-probed. |  |

| -job_owner                | Allows you to determine how files are used; you can<br>specify these options from the File Options dialog box. For<br>example, you can automatically decide to pass files to the<br>backend place-and-route tool (Use for Place and Route) or<br>use them for test benches containing HDL constructs for<br>simulation (Use for Simulation only).                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -structver fileName       | Adds structural Verilog files as input for your design<br>project. The software performs fast compilation of the<br>structural Verilog files, providing runtime improvements<br>for the design. For example:<br>add_file -structver <i>fileName.vm</i><br>For more information, see Using the Structural Verilog<br>Flow, on page 50.                                                                                                                                                                                                                                                                                                                                                                                                         |

| -vlog_std <i>standard</i> | Overrides the global Verilog standard for an individual file.<br>The accepted values for <i>standard</i> are v95 (Verilog 95),<br>v2001 (Verilog 2001), and sysv (SystemVerilog). The file<br>( <i>fileName</i> ) is added to the Verilog folder in the project; the<br>specified standard is listed after the filename in the project<br>view and is enclosed in angle brackets (for example,<br>commchip.v <sysv>). Note that when you add a<br/>SystemVerilog file (a file with an sv extension) to a project,<br/>the add_file entry in the project file includes the -vlog_std<br/><i>standard</i> string.<br/>The default standard for new projects is SystemVerilog.<br/>For Verilog 2005 extensions, use sysv (SystemVerilog).</sysv> |

#### **Filename Extensions**

Files with the following extensions are automatically added to their corresponding project directories; files with any other extension are added to the Other directory. The *-filetype* argument overrides automatic filename extension placement.

| -Filetype                    | Project Folder                                                               |

|------------------------------|------------------------------------------------------------------------------|

| -analysis_constraint         | Analysis Design Constraint                                                   |

| -edif                        | EDIF                                                                         |

| -fpga_constraint/-constraint | Logic Constraints (FDC)                                                      |

| -constraint                  | Logic Constraints (SDC)                                                      |

| -verilog                     | Verilog                                                                      |

|                              | -analysis_constraint<br>-edif<br>-fpga_constraint/-constraint<br>-constraint |

| Extension   | -Filetype  | Project Folder          |

|-------------|------------|-------------------------|

| .tcl        | -tcl       | Tcl Script              |

| .v          | -verilog   | Verilog                 |

| .vhd, .vhdl | -vhdl      | VHDL                    |

| .vm         | -structver | Structural Verilog File |

| any         | -include   | Include                 |

1. Use the sv format for SystemVerilog keyword support. Both Verilog and SystemVerilog formats are added to the Verilog folder.

### **Example: Add Files**

Add a series of VHDL files to the VHDL directory and add an include file to the project:

% add\_file /designs/sequencer/top.vhd % add\_file /designs/sequencer/alu.vhdl % add\_file -vhdl /designs/sequencer/reg.vhd.fast % add file -include /designs/std/decode.vhd

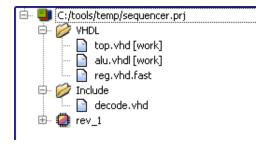

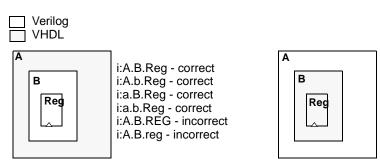

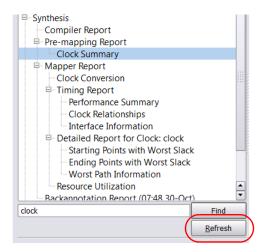

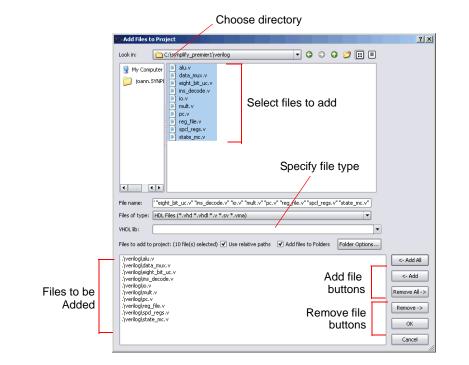

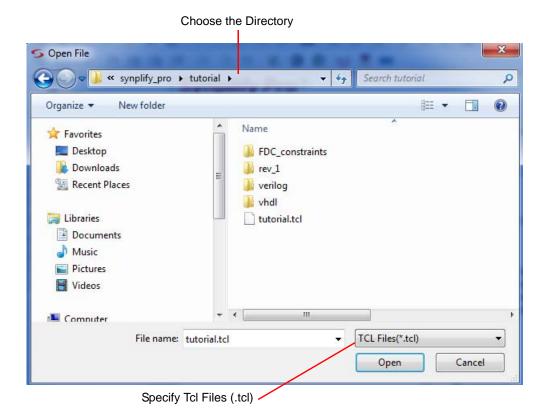

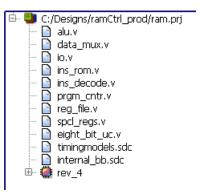

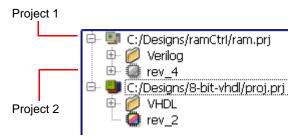

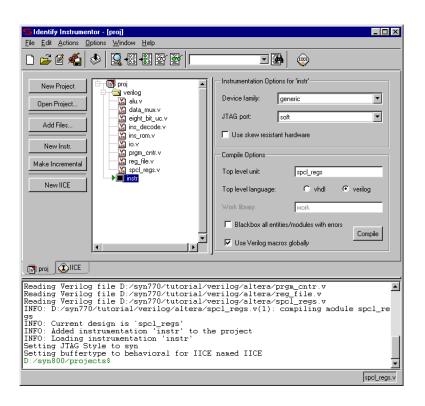

The corresponding directory structure in the Project view is shown in the following figure:

## **Example: File Options Designation**

Designate some IP core wrappers as well as their associated instantiated component files that must be passed on to the place-and-route tool, since they are not written to the final netlist:

```

add_file -verilog -job_owner par "my_ip_core.v"

add file -verilog -job owner par "my ip core enc.v"

```

## add\_folder

The add\_folder command adds a custom folder to a project.

## Syntax

add\_folder folderName

Creates logical folders with files in various custom hierarchy groupings within your Project view. These custom folders can be specified with any name or hierarchy level.

add\_folder verilog

add\_folder verilog/common\_rtl

add\_folder verilog/common\_rtl/prep

For more information about custom folders, see Managing Project File Hierarchy, on page 66 in the *User Guide*.

## check\_fdc\_query

Runs the constraint checker for constraints using the get\_\* and/or all\_\* query commands specified in the timing constraint file for the project.

#### Syntax

check\_fdc\_query [-full\_check]

### **Arguments and Options**

#### -full\_check

Runs the full constraint checker before checking the query commands. The default is to run the check\_fdc\_query command without this option.

When the -full\_check option is *not* specified, the command only runs the constraint syntax checker, which reduces runtime significantly, since most objects being searched are found in pre-mapping and do not require full mapping to be run. However, this option does not find bit-blasted registers and objects using the advanced -filter @property =~ commands, where the property is created or applied during mapping because it requires optimizations such as register replication.

For example, if a 4-bit RAM output is targeted with the get\_cell command, the differences in the results are shown below:

| Command                       | Run Stage   | Results                                                  |

|-------------------------------|-------------|----------------------------------------------------------|

| Default (without -full_check) | Pre-mapping | ram_out [3:0]                                            |

| With -full_check              | Mapping     | ram_out [3]<br>ram_out [2]<br>ram_out [1]<br>ram_out [0] |

### Description

The check\_fdc\_query command reads the fdc constraint file of the current project file. It runs the constraint checker for the following object query commands that are used with FDC constraints:

| all_* Commands | get_* Commands |

|----------------|----------------|

| all_clocks     | get_cells      |

| all_fanin      | get_clocks     |

| all_fanout     | get_nets       |

| all_inputs     | get_pins       |

| all_outputs    | get_ports      |

| all_registers  |                |

|                |                |

The report provides feedback on how these query commands are applied and ensures that the commands are used properly with constraints in the constraint file.

Collections created with define\_scope\_collection, find, and expand are not covered by this Tcl command. You can check these SCOPE collections in the HDL Analyst and the SCOPE interface. The report does not cover the define\_io\_standard constraint either.

## Example

Invoke check\_fdc\_query from the Tcl command line for the project. You can also invoke it from a shell window.

The command writes out the results of the object query commands to the *projectName\_cck\_fdc.rpt* file that opens in the GUI. You may need to run the constraint checker (Run->Constraint Check) to find additional issues with constraints.

The following example shows the results of running the constraint checker in the *projectName\_cck\_fdc.rpt* file.

```

FDC query commands results

****

# 1019 : set multicycle path 2 -from [get cells -hier {*[4]}]

# line 175 in :

C:/check fdc query/all clocks/test1 basic/top translated.fdc

Results of query command: get cells -hier {*[4]}

(none)

# 1027 : set multicycle path 3 -to [all clocks]

# line 196 in :

C:/check fdc query/all clocks/test1 basic/top translated.fdc

Results of query command: all clocks

clka

clkb

dcm CLK0 BUF clock CLKIN1

dcm clk0 i clock CLKIN1

dcm CLK0 BUF 1 clock CLKIN1

```

The syntax checker reports the object query commands and any issues it found and writes them to the *projectName\_scck.rpt* file.

```

# Synospys Constraint Checker (syntax only), version map610dev,

Build 1085R

# Copyright (C) 1994-2013, Synopsys, Inc.

# Written on Tue Apr 30 15:39:07 2013

##### DESIGN INFO

Top View:

"top"

Constraint File(s):

"C:\check fdc query\all clocks\test1 basic\top translated.fdc"

"C:\builds\syn201309 063R\lib\fdc query.fdc"

# Run constraint checker to find more issues with constraints.

#######

No issues found in constraint syntax.

Clock Summary

*****

Start

Requested

Requested

Clock

Clock

```

© 2015 Synopsys, Inc.

```

Clock Frequency Period Type Group

clka 100.0 MHz10.000 declareddefault_clkgroup

clkb 50.0 MHz 20.000 declareddefault_clkgroup

dcm|CLK0_BUF_clock_CLKIN1

200.0 MHz5.000 derived (from clka) default_clkgroup

dcm|CLK0_BUF_1_clock_CLKIN1

50.0 MHz 20.000 derived (from clka) default_clkgroup

```

#### See Also

- Constraint Checking, on page 154

- Constraint Checking Report, on page 275

## command\_history

Displays a list of the Tcl commands executed during the current session.

#### Syntax

command\_history [-save filename]

#### **Arguments and Options**

-save

Writes the list of Tcl commands to the specified filename.

#### Description

The command\_history command displays a list of the Tcl commands executed during the current session. Including the -save option, saves the commands to the specified file to create Tcl scripts.

#### **Examples**

command\_history -save C:/DesignsII/tut/proto/myTclScript.tcl

#### See Also

• recording, on page 55

## constraint\_file

The constraint\_file command manipulates the constraint files used by the active implementation.

## Syntax

constraint\_file -enable constraintFileName -disable constraintFileName -list -all -clear

The following table describes the command arguments.

| Option   | Description                                                                          |

|----------|--------------------------------------------------------------------------------------|

| -enable  | Selects the specified constraint file to use for the active implementation.          |

| -disable | Excludes the specified constraint file from being used for the active implementation |

| -list    | Lists the constraint files used by the active implementation                         |

| -all     | Selects (includes) all the project constraint files for the active implementation.   |

| -clear   | Clears (excludes) all the constraint files for the active implementation             |

#### **Examples**

List all constraint files added to a project, then disable one of these files for the next synthesis run.

```

% constraint_file -list

attributes.fdc clocks1.fdc clocks2.fdc eight_bit_uc.fdc

% constraint_file -disable eight_bit_uc.fdc

```

Disable all constraint files previously enabled for the project, then enable only one of them for the next synthesis run.

```

% constraint_file -clear

% constraint_file -enable clocks2.fdc

```

## create\_fdc\_template

Lets you create an initial constraint file (fdc) for your specific design.

#### **Syntax**

#### create\_fdc\_template [-period float] [-in\_delay float] [-out\_delay float]

The following table describes the create\_fdc\_template command options.

| Option           | Description                                              |

|------------------|----------------------------------------------------------|

| -period float    | Specifies the default values for port clocks.            |

| -in_delay float  | Specifies the default values for the input delay ports.  |

| -out_delay float | Specifies the default values for the output delay ports. |

#### **Examples**

Each port clock includes a set\_clock\_groups header with details shown below, which can help you determine whether clocks have been optimized away or if there are any derived clocks.

```

### Individual "set clock groups" commands for all "clka" derived clocks

### appear at the end of this file. Enabling a given command will make the

### given clock asynchronous to all other clocks. If a given clock (below)

### does not appear in the final Performance Summary (in the *.srr

### file after synthesis), the clock may have been optimized away due to

### Gated/Generated Clock Conversion.

### See the "CLOCK OPTIMIZATION REPORT" in the *.srr file.

### Below is a list of any clocks derived from "clka":

### clka DERIVED CLOCKS:

###

dcm | CLK0_BUF_1_derived_clock_CLKIN_Clock_Object: {t:dcm_inst.CLK_BUF1.0}

###

dcm|CLK0_BUF_derived_clock_CLKIN1 Clock Object: {t:dcm_inst.CLK_BUF0.0}

set clock groups -disable -asynchronous -name {clka group}

-group {clka} -comment {Source clock clka group}

set clock groups -disable -asynchronous

-name {dcm|CLK0 BUF 1 derived clock CLKIN1 group}

-group [get_clocks

-of_objects [get_pins {t:dcm_inst.CLK_BUF1.0}]]

-comment {Derived clock dcm CLK0 BUF 1 derived clock CLKIN1

from source clock clka}

set clock groups -disable -asynchronous

-name {dcm CLK0_BUF_derived_clock_CLKIN1_group}

-group [get clocks

-of objects [get pins {t:dcm inst.CLK BUF0.0}]]

-comment {Derived clock dcm CLK0_BUF_derived_clock_CLKIN1

from source clock clka}

set clock groups -disable -asynchronous -name {clkb group}

-group {clkb} -comment {Source clock clkb group}

```

## encryptIP

Runs a Perl script that lets IP vendors provide encrypted evaluation IP to synthesis users. The IP is encrypted using the OpenIp scheme. You can download the encryptIP Perl script from SolvNet. See the article published at https://solvnet.synopsys.com/retrieve/032343.html.

For additional information about the script, see The encryptIP Script, on page 688 in the *Reference* manual.

## Syntax

#### encryptIP

-in | input inputFile

-out | output outputFileName

-c | cipher "{des-cbc | 3des-cbc |aes128-cbc}"

-k | key symmetricEncryptionKeyInTextFormat

-kx | keyx symmetricEncryptionKeyInHexadecimalFormat

-bd | build\_date ddmmmyyyy

-om | outputmethod "{plaintext | blackbox | persistent\_key}"

-incv | includevendor vendorKeyBlock

-dkn | datakeyname sessionKeyName

-dko | datakeyowner sessionKeyOwner

-a | author dataAuthor

-v | verbose

You must specify all required parameters.

| -in   input   | Names the input RTL file to be encrypted.                                                                                                                                                                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -out   output | Names the output file generated after encryption.                                                                                                                                                                                                                                                                    |

| -c   cipher   | Specifies the symmetric encryption cipher. The keylength must match the algorithm being used, with each character using 8 bits.                                                                                                                                                                                      |

|               | <ul> <li>des-cbc specifies the Data Encryption Standard (DES); uses a<br/>64-bit key.</li> </ul>                                                                                                                                                                                                                     |

|               | <ul> <li>3des-cbc specifies the Triple Data Encryption Standard (Triple DES); uses a 192-bit key.</li> </ul>                                                                                                                                                                                                         |

|               | <ul> <li>aes128-cbc specifies the Advanced Encryption Standard (AES<br/>Rijndael); uses a 128-bit key.</li> </ul>                                                                                                                                                                                                    |

|               | See Encryption and Decryption Methodologies, on page 683 in<br>the <i>Command Reference</i> for an overview. For information about<br>how symmetric encryption fits into the encryption flow, see<br>Encryption and Decryption, on page 441 in the <i>User Guide</i> .                                               |

| -k   key      | Specifies the symmetric data decryption key used to encode your<br>RTL data block. The key is in text format, and can be any string<br>(e.g. ABCDEFG).The exact length of the key depends on the data<br>method you use. In a future release, this key will be automatically<br>generated if you do not specify one. |

| -kx   keyx*   | Optional parameter. Specifies the symmetric encryption key in hexadecimal format.                                                                                                                                                                                                                                    |

|               |                                                                                                                                                                                                                                                                                                                      |

| -bd   build_date         | Specifies a date (ddmmmyyyy). The IP only works in Synplicity<br>software released after the specified date. It is recommended that<br>you use a date in January 2008 or later. For example:16FEB2008.<br>This option lets you force users to use newer Synopsys FPGA<br>releases that contain more security features. Contact Synopsys if<br>you need help in deciding what build date to use. |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -om                      | Determines how the IP is treated in the output after synthesis:                                                                                                                                                                                                                                                                                                                                 |

| outputmethod             | <ul> <li>plaintext specifies that the IP is unencrypted in the synthesis netlist.</li> </ul>                                                                                                                                                                                                                                                                                                    |

|                          | • blackbox specifies that the IP is treated as a black box, and only interface information is in the output.                                                                                                                                                                                                                                                                                    |

|                          | <ul> <li>persistent_key is the default setting.</li> </ul>                                                                                                                                                                                                                                                                                                                                      |

|                          | See Output Methods for encryptIP, on page 29 for more information.                                                                                                                                                                                                                                                                                                                              |

| -incv  <br>includevendor | Optional parameter that specifies a key block for an EDA vendor, so that IP can be read by the vendor tools. C                                                                                                                                                                                                                                                                                  |

| -dkn  <br>datakeyname    | Specifies a string that denotes your session key, that was used to encrypt your IP.                                                                                                                                                                                                                                                                                                             |

| -dko  <br>datakeyowner   | Optional parameter that names the owner of the session key. The value can be any string.                                                                                                                                                                                                                                                                                                        |

| -a  author               | Optional parameter that names the author of the session key. The value can be any string.                                                                                                                                                                                                                                                                                                       |

| -v  verbose              | Specifies that the script run in verbose mode.                                                                                                                                                                                                                                                                                                                                                  |

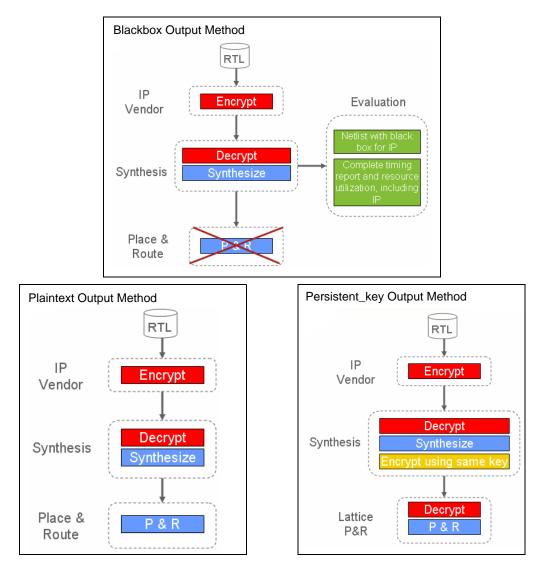

#### **Output Methods for encryptIP**

You can control the level of IP protection in the synthesis output netlist by specifying an output method when you encrypt your IP by running the encryptIP script. For example, -om blackbox. The output method is included in the encrypted key block of your encrypted RTL. The table below shows the values for -om. See Specifying the Script Output Method, on page 453 in the User Guide for guidelines on how to use these methods effectively.

| Output Method | Description                                                                                                                                                                                                                                                                                           |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| blackbox      | With this method, you cannot run gate-level simulation on the<br>output netlist or place and route the IP. This is because the<br>output netlist contains the IP interface only and no IP contents.<br>It only includes ports and connections; there are no nets or<br>instances shown inside the IP. |

| Output Method  | Description                                                                                                                                                                                                                      |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| plaintext      | With this method, you can synthesize, run gate-level simulation,<br>place, route, and implement an FPGA on the board that includes<br>your IP. The output netlist contains your unencrypted IP, which<br>is completely readable. |

| persistent_key | By default, the output is encrypted using the same session key<br>and cipher you used to encrypt your IP for the synthesis tools.                                                                                                |

The following figure shows how the synthesis tools work with each of the three encryptIP output methods:

## Effect of Output Method on Viewing IP

In the synthesis tools, the contents of the IP are always shown as black boxes, and you cannot view the contents. In the Technology view, you cannot view the initialization values for the LUT.

### Effect of Output Method on Output Constraints

After synthesis, the output constraints generated for the IP are not encrypted, regardless of the output method. They are always readable.

### Effect of Output Method on Output Netlist

The following table summarizes how different output methods affect the output:

| Method (-om)   | Output Netlist After Synthesis                                                                                                                                                                                                                                                                                                              |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| blackbox       | The output netlist contains the IP interface only and no IP content, and only includes IP ports and connections. The IPs are treated as black boxes, and there are no nets or instances shown inside the IP. This content applies to all netlist formats generated for different vendors, whether it is HDL (vm or vhm), EDIF (edf or edn). |

| plaintext      | The output netlist contains your unencrypted IP, which is completely readable (nothing is encrypted).                                                                                                                                                                                                                                       |

| persistent_key | The output netlist includes encrypted versions of the IP.<br>Specifics differ, based on the target.                                                                                                                                                                                                                                         |

## encryptP1735

Runs a script that allows IP vendors to encrypt modules or components that can then be downloaded for evaluation or used by a Synopsys FPGA user.

The encryptP1735 script supports three different use models for encrypting RTL files. See The encryptP1735 Script, on page 684 in the *Reference* manual for more information on the use models and the files they use.

#### **Syntax**

encryptP1735 -I | list listofFiles [-pk | public\_keys keyFileName] [-sk | showkey] [-verbose] [-verilog] [-vhdl] [-log logFileName] [-h | -help]

The following table describes the command-line arguments.

| -l   list         | Specifies a list of the files to be encrypted; <i>listofFiles</i> is a list of the non-encrypted HDL input files with each filename entry on a separate line.                                                                                                                                                                                                                                                               |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -pk   public_keys | Specifies the public keys repository file. This file contains<br>public keys for various tools. If the encryption envelope<br>contains a key block with a particular keyowner and keyname,<br>the public keys file is searched by the script to find a public key<br>to use during key-block generation. See Public Keys<br>Repository File, on page 685 in the <i>Reference</i> manual for<br>information about this file. |

| -sk   showkey     | When used, the encryption script displays the session key in<br>use (useful when random keys are used and the user wants to<br>make a note of the key being used).                                                                                                                                                                                                                                                          |

| -verbose          | Prints more detailed messages to the screen or log file.                                                                                                                                                                                                                                                                                                                                                                    |

| -verilog          | Specifies Verilog HDL file format when filename does not include a .v or .sv extension.                                                                                                                                                                                                                                                                                                                                     |

| -vhdl             | Specifies VHDL HDL file format when filename does not include a .vhd or .vhdl extension.                                                                                                                                                                                                                                                                                                                                    |

| -log              | Prints messages to the specified log file.                                                                                                                                                                                                                                                                                                                                                                                  |

#### Examples

The example below encrypts the files in mylist and uses the default keys.txt file as the public keys file. Resulting messages are written to the encrypt.log file.

perl encryptP1735.pl -l mylist -log encrypt.log

The following example illustrates a similar command using an explicit publickeys file:

perl encryptP1735.pl -l mylist -pk public\_keys.txt

-log encrypt.log

#### get\_env

The get\_env command reports the value of a predefined system variable.

#### **Syntax**

get\_env systemVariable

Use this command to view system variable values. The following example shows you how to use the get\_env command to see the value of the previously created MY\_PROJECT environment variable. The MY\_PROJECT variable contains the path to an HDL file directory, so get\_env reports this path.

get\_env MY\_PROJECT

d:\project\hdl\_files

In the project file or a Tcl script, you can define a Tcl variable that contains the environment variable. In this example, my\_project\_dir contains the MY\_PROJECT variable, which points to an HDL file directory.

set my\_project\_dir [get\_env MY\_PROJECT]

Then, use the *\$systemVariable* syntax to access the variable value. This is useful for specifying paths in your scripts, as in the following example which adds the file myfile1.v to the project.

add\_file \$my\_project\_dir/myfile1.v

## get\_option

The get\_option command reports the settings of predefined project and device options. The options are the same as those for set\_option. See set\_option, on page 58 for details.

#### Syntax

get\_option -optionName

# hdl\_define

For Verilog designs, this command specifies values for Verilog text macros. You can specify text macro values that you would normally enter using the Verilog `define statement in a Verilog file included at the top of the synthesis project. The parameter value is valid for the current implementation only.

This command is equivalent to the set\_option -hdl\_define command.

## **Syntax**

hdl\_define -set "directive=value [directive=value ...]" -clear -list

## Examples

hdl define -set "SIZE=32"

This statement specifies the value 32 for the SIZE directive; the following statement is written to the project file:

set\_option -hdl\_define -set "SIZE=32"

To define multiple directive values using hdl\_define, enclose the directives in quotes and use a space delimiter. For example:

hdl define -set "SIZE=32 WIDTH=8"

The software writes the following statement to the prj file:

set\_option -hdl\_define -set "size=32 width=8"

## See Also

Compiler Directives and Design Parameters, on page 210 for information on specifying compiler directives in the GUI.

## hdl\_param

The hdl\_param command shows or sets HDL parameter overrides. For the GUI equivalent of this command, select Project->Implementation Options->Verilog/VHDL.

#### **Syntax**

hdl\_param -add {paramName} -list | -set paramName {paramValue} -clear -overrides

The following table describes the command arguments.

| Option     | Description                                                                                                                            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|

| -add       | Adds a parameter override to the project.                                                                                              |

| -list      | Shows parameters for the top-level module only and lists values for parameters if there is a parameter override.                       |

| -set       | Sets a parameter override and its value for the active<br>implementation. Only the parameter value is enclosed within<br>curly braces. |

| -clear     | Clears all parameter overrides of the active implementation.                                                                           |

| -overrides | Lists all the parameter override values used in this project.                                                                          |

#### Examples

In batch mode, to set generic values using the set\_option command in a project file, specify the hdl\_param generic with quotes and enclose it within {}. For example:

set\_option -hdl\_param -set ram\_file {"init.mem"}

set\_option -hdl\_param -set simulation {"false"}

Suppose the following parameter is set for the top-level module.

set\_option -hdl\_param -set {"width=8"}

Add a parameter override and its value, then list the parameter override.

```

hdl_param -add {"size=32"}

hdl param -list "size=32"

```

## impl

The impl command adds, removes, or modifies an implementation.

#### Syntax

# impl -add [implName] [model] -name implName -remove implName -active [implName] -list -type implType -result\_file -dir

The following table describes the command arguments.

| Option  | Description                                                                                                                        |

|---------|------------------------------------------------------------------------------------------------------------------------------------|

| -add    | Adds a new device implementation. If:                                                                                              |

|         | • <i>implName</i> is not specified, creates a unique implementation name by incrementing the name of the active implementation.    |

|         | • you want to add a new implementation copied from implementation <i>model</i> .                                                   |

| -name   | Changes the name of the active implementation.                                                                                     |

| -remove | Removes the specified implementation.                                                                                              |

| -active | Reports the active implementation. If you specify an implementation name, changes the specified name to the active implementation. |

| -list   | Lists all the implementations used in this project.                                                                                |

| Option       | Description                                                                                                                                                                                                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -type        | <ul><li>Specifies the type of implementation to add. For example, the:</li><li>-type fpga option creates an FPGA implementation.</li><li>-type identify option creates an Identify implementation.</li></ul> |

| -result_file | Displays the implementation results file.                                                                                                                                                                    |

| -dir         | Displays the implementation directory.                                                                                                                                                                       |

#### **Examples**

The following command sequence lists all implementations, reports the active implementation, and then activates a different implementation.

```

% impl -list

design_worst design_typical design_best

% impl -active

design_best

% impl -active design_typical

% impl -active

design_typical

% impl -add rev 1 identify mixed -type identify

```

## job

The job command, for place and route job support, creates, removes, identifies, runs, cancels, and sets/gets options for named P&R jobs.

#### Syntax

```