# Timberwolf Digital Signal Processor family, powered by *AcuEdge*<sup>™</sup> Technology

Designed for IP and Security Cameras

ZL38050

Product Brief

## Description

The ZL38050 is part of Microsemi's new Timberwolf audio processor family of products that feature the company's innovative *AcuEdge* acoustic technology, which is a set of highly-complex and integrated algorithms. These algorithms are incorporated into a powerful DSP platform that allow the user to extract intelligible information from the audio environment.

The Microsemi *AcuEdge* Technology ZL38050 device is ideal for IP and security camera applications. Its license-free, royalty-free intelligent audio Firmware (ZLS38050) provides Acoustic Echo Cancellation (AEC), Noise Reduction (NR) and a variety of other voice enhancements to improve both the intelligibility and subjective quality of voice in harsh acoustic environments.

Microsemi offers additional tools to speed up the product development cycle. The *MiTuner™* ZLS38508 or ZLS38508LITE GUI software packages allow a user to interactively configure the ZL38050 device. The optional *MiTuner* ZLE38470BADA Automatic Tuning Kit provides automatic tuning and easy control for manual fine tuning adjustments.

#### **Applications**

- IP Cameras

- Security Cameras

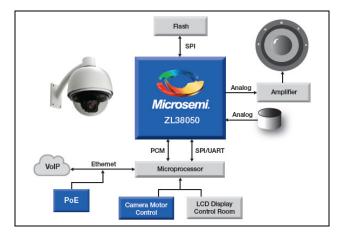

**Typical IP Security Camera Application**

Document ID# 148964

Version 8

October 2015

#### **Ordering Information**

| Device OPN  | Package                 | Packing     |

|-------------|-------------------------|-------------|

| ZL38050LDF1 | 64-pin QFN (9x9)        | Tape & Reel |

| ZL38050LDG1 | 64-pin QFN (9x9)        | Trày        |

| ZL38050UGB2 | 56-ball WLCSP (3.1x3.1) | •           |

These packages meet RoHS 2 Directive 2011/65/EU of the European Council to minimize the environmental impact of electrical equipment.

## Microsemi *AcuEdge* Technology ZLS38050 Firmware

- Wideband and Narrowband Acoustic Echo Cancellation

- Full or Half duplex operation

- Supports long tail AEC (up to 256 ms) in both Narrowband and Wideband operation

- · Howling detection/cancellation

- · Prevents oscillation in AEC audio path

- Non-linear echo cancellation provides higher tolerance for speaker distortions

- Advanced NR reduces background noise from the near-end speech signal using Psychoacoustic techniques

- Provisions for stereo audio mixing and stereo music record and playback (sample rate of 48 kHz) with 16 kHz voice processing

- Multi-tone generation

- · Various encoding/decoding options:

- 16-bit 2's complement (linear)

- G.711 A/μ law

- G.722

- Send and receive path equalizers

- 16-band for Narrowband mode

- 22-band for Wideband mode

- · Comfort noise generation

- 48 kHz bypass mode

- Configurable Cross-Point Switch

#### **Tools**

- ZLK38000 Evaluation Kit

- MiTuner™ ZLS38508 and ZLS38508LITE GUI

- MiTuner™ ZLE38470BADA Automatic Tuning Kit

# Timberwolf Digital Signal Processor family, powered by *AcuEdge*<sup>™</sup> Technology

Designed for IP and Security Cameras

ZL38050

Product Brief

#### **ZL38050 Hardware Features**

- · DSP with Voice Hardware Accelerators

- Dual  $\Delta\Sigma$  16-bit digital-to-analog converters (DAC)

- Sampling up to 48 kHz and internal output drivers

- Headphone amps capable of 4 single-ended or 2 differential outputs

- 32 mW output drive power into 16 ohms

- Impulse pop/click protection

- A single Digital Microphone input supporting up to 2 Microphones

- TDM port shared between PCM and Inter-IC Sound (I<sup>2</sup>S)

- · Performs sample rate conversions

- SPI Slave port for host processor interface

- · Master SPI port for serial Flash interface

- 14 General Purpose Input/Output (GPIO) pins

- · General purpose UART port

- Boots from SPI, UART, or Flash allowing easy firmware updates

- Can run unattended (controllerless), selfbooting into a configured operational state

- Crystal-less operation (with a valid TDM clock)

- · 2 low power modes controlled by reset

- Available in miniature Wafer Level Chip Scale Package

#### **Performance**

AEC Tail Length: 256 ms

AEC sampling rate: 8 and 16 kHz

Single-Talk Weighted Terminal Coupling Loss (TCLw): > 60 dB

Double-Talk TCLw: > 40 dB

Double-Talk Attenuation: < 3 dB</li>

Noise reduction up to 30 dB

## The *MiTuner*<sup>™</sup> Automatic Tuning Kit and ZLS38508 MiTuner GUI

Microsemi's Automatic Tuning Kit provides Audio Interface Box hardware, Auto Tuning and Subjective Tuning software, and GUI support for tuning of Microsemi's *AcuEdge* Technology Audio Processors.

#### ZLS38508 software features:

- Allows tuning of key parameters of the system design

- Provides visual representations of the audio paths with drop-down menus to program parameters, allowing:

- Control of the audio routing configuration

- Programming of key building blocks in the transmit (Tx) and receive (Rx) audio paths

- · Setting analog and digital gains

- Configuration parameters allow users to "fine tune" the overall performance

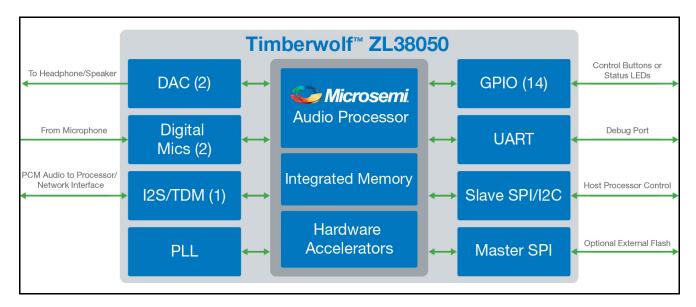

### **Device Block Diagram**

The Microsemi ZL38050 Audio Processor powered by ZLS38050  $AcuEdge^{\tau M}$  Technology Firmware is ideal for providing high definition audio to IP cameras.

**ZL38050 Audio Processor for IP and Security Cameras**

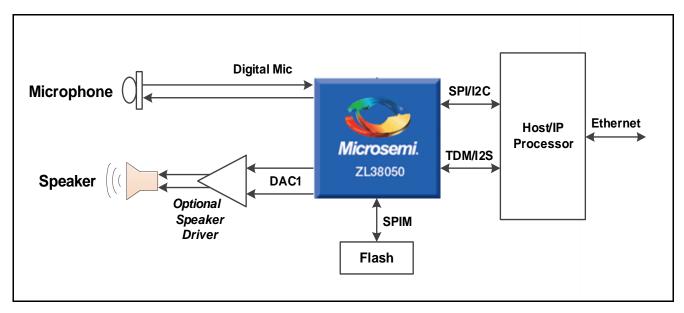

## **Typical Application Block Diagram**

IP Camera HD Voice 2-way Audio Application

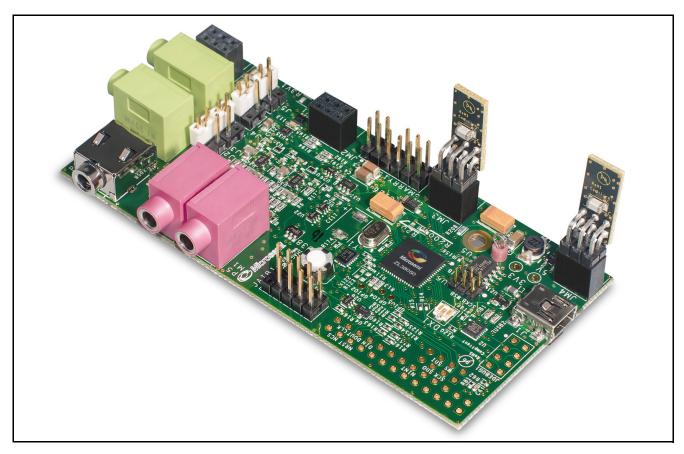

#### **ZLK38000 Evaluation Kit**

The ZLK38000 Evaluation Kit includes all the hardware necessary to operate the ZLE38000 Evaluation Board. The Evaluation Board provides a flexible platform to evaluate a ZL38050 Timberwolf Audio Processor device with *AcuEdge™* Technology Firmware.

The ZLE38000 Evaluation Board provides a simple analog interface that can be connected to microphones and speakers to allow for subjective testing. The miniature size allows for easy mounting in an existing plastic enclosure.

**ZLE38000 Evaluation Board**

Firmware Code for the ZL38050 can be downloaded into the Evaluation Board using the ZLS38000 Firmware Loader software. The ZLE38000 Evaluation Board can then be controlled using the *MiTuner*<sup>™</sup> GUI Lite Software (ZLS38508LITE) or the full *MiTuner* GUI Software package (ZLS38508). Microsemi has developed automatic tuning capability into the full *MiTuner* GUI Software to further facilitate and shorten the design process. The ZLS38508 Software package consists of the *MiTuner* GUI Software and the Audio Interface Box (AIB) Evaluation Kit (ZLE38470BADA) hardware, together performing automatic tuning of the Timberwolf Audio Processor on the Evaluation Board or in a system design.

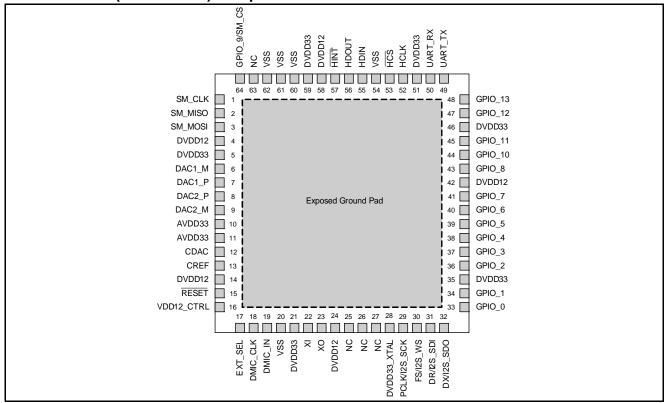

### Device Pinout (64-Pin QFN) - Top View

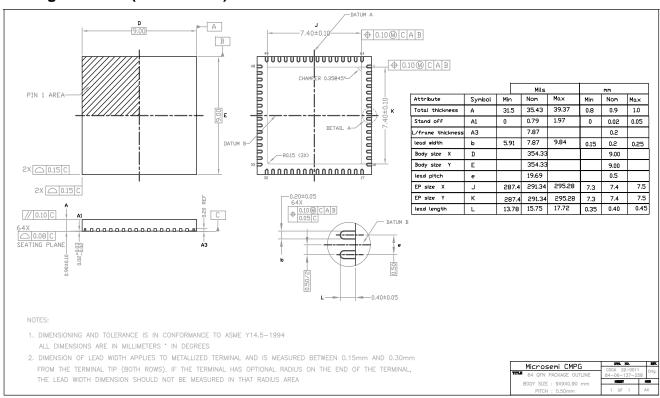

## Package Outline (64-Pin QFN)

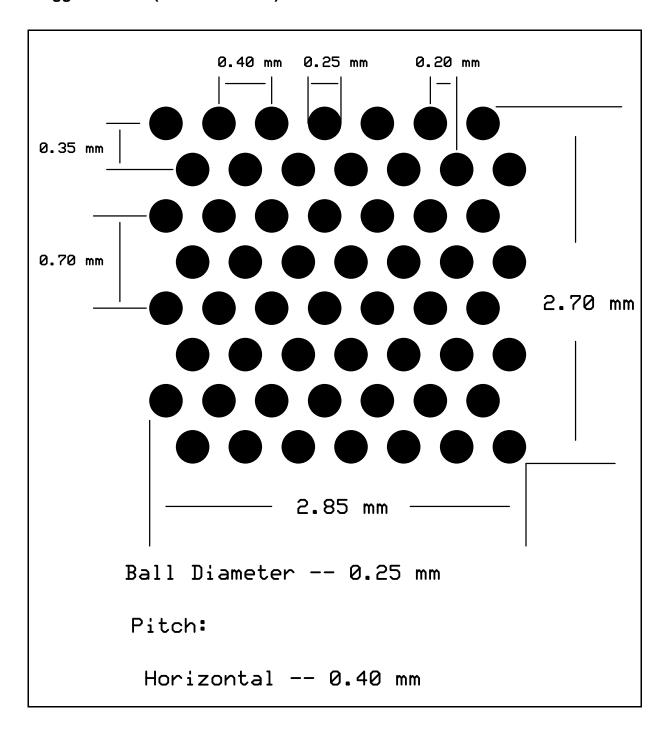

## Device Pinout (56-Ball WLCSP) - Top View

| /           | CLK<br>A1)  | HDIN<br>(A2) | HDOUT<br>(A3) | GPI       | O_9/SM<br>(A4) | _cs         | SM_CLK    | S         | M_MISO<br>(A6) | SM_MOS     | SI       |

|-------------|-------------|--------------|---------------|-----------|----------------|-------------|-----------|-----------|----------------|------------|----------|

| HCS<br>(B1) | UART_F      | RX DVDD      | 33            | VSS<br>B4 | I              | DVDD1<br>B5 | 2         | VSS<br>B6 | ים             | VDD33      |          |

| /           | INT (C1)    | JART_TX      | GPIO_11       |           | VSS<br>C4      |             | VSS<br>C5 |           | NC<br>(C6)     | DAC1_F     | <b>D</b> |

| DVDD12      | VSS<br>D2   | GPIO D3      | _8<br>)       | VSS<br>D4 |                | VSS<br>D5   | i         | RESET D6  | D              | AC2_P      |          |

|             | VI2S_SCK    | GPIO_7       | GPIO_10       | (         | GPIO_1         |             | GPIO_6    |           | VSS<br>E6      | AVDD33     | 3        |

| FS/I2S_WS   | GPIO_<br>F2 | 3 GPIO       | _2 (          | GPIO_0    | 1              | XO<br>F5    |           | GPIO_5    | (              | CDAC<br>F7 |          |

| /           | 2S_SDI      | VSS<br>G2    | DVDD33        |           | NC<br>G4       |             | DVDD12    | 2 [       | OVDD12         | CREF<br>G7 |          |

| DX/I2S_SDO  | VSS<br>H2   | DMIC_        | _IN<br>)      | NC<br>H4  |                | NC<br>(H5)  | D         | MIC_CL    | K              | XI<br>H7   |          |

## Staggered Balls (56-Ball WLCSP) - Bottom View

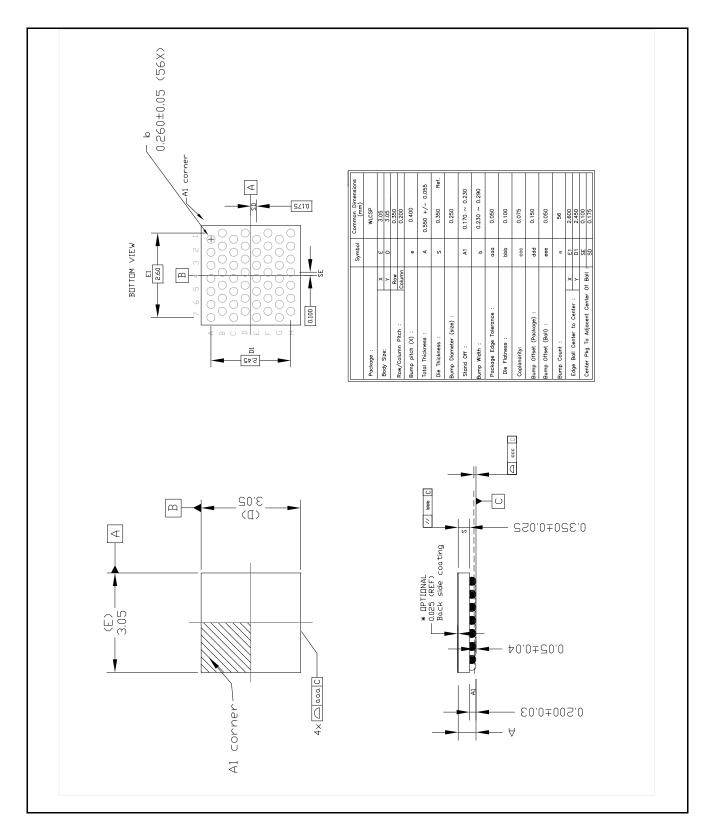

## Package Outline (56-Ball WLCSP)

## **Device Pinout**

| QFN<br>Pin # | WLCSP<br>Ball | Name  | Туре | Description                                                                                                                                                                                                                                                                          |

|--------------|---------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15           | D6            | RESET | ·    | <b>Reset.</b> When low the device is in its reset state and all tristate outputs will be in a high impedance state. This input must be high for normal device operation. A 10 K $\Omega$ pull-up resistor is required on this node to DVDD33 if this pin is not continuously driven. |

**Table 1 - Reset Pin Description**

| QFN<br>Pin # | WLCSP<br>Ball | Name   | Туре   | Description                                                                                                                             |

|--------------|---------------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 6            | -             | DAC1_M | Output | DAC 1 Minus Output. This is the negative output signal of the differential amplifier of the DAC 1.  Not available on the WLCSP package. |

| 7            | C7            | DAC1_P | Output | DAC 1 Plus Output. This is the positive output signal of the differential amplifier of the DAC 1.                                       |

| 9            | -             | DAC2_M | Output | DAC 2 Minus Output. This is the negative output signal of the differential amplifier of the DAC 2.  Not available on the WLCSP package. |

| 8            | D7            | DAC2_P | Output | DAC 2 Plus Output. This is the positive output signal of the differential amplifier of DAC 2.                                           |

| 12           | F7            | CDAC   | Output | DAC Reference. This node requires capacitive decoupling.                                                                                |

| 13           | G7            | CREF   | Output | Common Mode Reference. This node requires capacitive decoupling.                                                                        |

**Table 2 - DAC Pin Descriptions**

| QFN<br>Pin # | WLCSP<br>Ball | Name     | Туре   | Description                                                                                                                         |

|--------------|---------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| 18           | H6            | DMIC_CLK | Output | <b>Digital Microphone Clock Output.</b> Clock output for digital microphones and digital electret microphone pre-amplifier devices. |

| 19           | НЗ            | DMIC_IN  | Input  | <b>Digital Microphone Input.</b> Stereo or mono digital microphone input. <i>Tie to VSS if unused.</i>                              |

**Table 3 - Microphone Pin Descriptions**

The ZL38050 device has one TDM interface. The TDM block is capable of being a master or a slave. The port can be configured for Pulse-Code Modulation (PCM) or Inter-IC Sound ( $I^2S$ ) operation. The port conforms to PCM, GCI, and  $I^2S$  timing protocols.

| QFN<br>Pin # | WLCSP<br>Ball | Name             | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|---------------|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29           | E1            | PCLK/<br>I2S_SCK | Input/<br>Output | PCM Port Clock (Input/Tristate Output). PCLK is equal to the bit rate of signals DR/DX. In TDM master mode this clock is an output and in TDM slave mode this clock is an input.  I²S Port Serial Clock (Input/Tristate Output). This is the I²S port bit clock. In I²S master mode this clock is an output and drives the bit clock input of the external slave device's peripheral converters. In I²S slave mode this clock is an input and is driven from a converter operating in master mode.  After power-up, this signal defaults to be an input in I²S slave mode.  A 100 KΩ pull-down resistor is required on this pin to VSS. If this pin is unused, tie the pin to VSS.  When driving PCLK/I2S_SCK from a host, one of the following conditions must be satisfied:  1. Host drives PCLK low during reset (the 100 KΩ resistor will keep PCLK low), or  3. Host drives PCLK at its normal frequency |

| 30           | F1            | FS/<br>I2S_WS    | Input/<br>Output | PCM Port Frame Pulse (Input/Tristate Output). This is the TDM frame alignment reference. This signal is an input for applications where the PCM bus is frame aligned to an external frame signal (slave mode). In master mode this signal is a frame pulse output.  I <sup>2</sup> S Port Word Select (Left/Right) (Input/Tristate Output). This is the I <sup>2</sup> S port left or right word select. In I <sup>2</sup> S master mode word select is an output which drives the left/right input of the external slave device's peripheral converters. In I <sup>2</sup> S slave mode this pin is an input which is driven from a converter operating in master mode.  After power-up, this signal defaults to be an input in I <sup>2</sup> S slave mode.  Tie this pin to VSS if unused.                                                                                                                 |

| 31           | G1            | DR/<br>I2S_SDI   | Input            | PCM Port Serial Data Stream Input. This serial data stream operates at PCLK data rates.  I <sup>2</sup> S Port Serial Data Input. This is the I <sup>2</sup> S port serial data input.  Tie this pin to VSS if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 32           | H1            | DX/<br>I2S_SDO   | Output           | PCM Port Serial Data Stream Output. This serial data stream operates at PCLK data rates.  12S Port Serial Data Output. This is the I2S port serial data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              |               |                  |                  | I <sup>2</sup> S Port Serial Data Output. This is the I <sup>2</sup> S port serial data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Table 4 - TDM and I<sup>2</sup>S Ports Pin Description

The HBI port functions as a peripheral interface for an external controller, and supports access to the internal registers and memory of the device.

| QFN<br>Pin # | WLCSP<br>Ball | Name  | Туре             | Description                                                                                                                                                                                  |

|--------------|---------------|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52           | A1            | HCLK  | Input            | HBI SPI Slave Port Clock Input. Clock input for the SPI Slave port. Maximum frequency = 25 MHz.                                                                                              |

|              |               |       |                  | This input should be tied to VSS in I <sup>2</sup> C mode.<br>Tie this pin to VSS if unused.                                                                                                 |

| 53           | B1            | HCS   | Input            | <b>HBI SPI Slave Chip Select Input.</b> This active low chip select signal activates the SPI Slave port.                                                                                     |

|              |               |       |                  | HBI I <sup>2</sup> C Serial Clock Input. This pin functions as the I2C_SCLK input in I <sup>2</sup> C mode. A pull-up resistor is required on this node for I <sup>2</sup> C operation.      |

|              |               |       |                  | Tie this pin to VSS if unused.                                                                                                                                                               |

| 55           | A2            | HDIN  | Input            | HBI SPI Slave Port Data Input. Data input signal for the SPI Slave port.                                                                                                                     |

|              |               |       |                  | This input selects the slave address in I <sup>2</sup> C mode.<br>Tie this pin to VSS if unused.                                                                                             |

| 56           | А3            | HDOUT | Input/<br>Output | HBI SPI Slave Port Data Output (Tristate Output). Data output signal for the SPI Slave port.                                                                                                 |

|              |               |       |                  | HBI I <sup>2</sup> C Serial Data (Input/Output). This pin functions as the I2C_SDA I/O in I <sup>2</sup> C mode. A pull-up resistor is required on this node for I <sup>2</sup> C operation. |

| 57           | C1            | HINT  | Output           | <b>HBI Interrupt Output.</b> This output can be configured as either CMOS or open drain by the host.                                                                                         |

Table 5 - HBI - SPI Slave Port Pin Descriptions

The Master SPI port functions as the interface to an external Flash device used to optionally Auto Boot and load the device's firmware and configuration record from external Flash memory.

| QFN<br>Pin # | WLCSP<br>Ball | Name             | Туре             | Description                                                                                                                            |

|--------------|---------------|------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1            | A5            | SM_CLK           | Output           | Master SPI Port Clock (Tristate Output). Clock output for the Master SPI port. Maximum frequency = 8 MHz.                              |

| 2            | A6            | SM_MISO          | Input            | Master SPI Port Data Input. Data input signal for the Master SPI port.                                                                 |

| 3            | A7            | SM_MOSI          | Output           | Master SPI Port Data Output (Tristate Output). Data output signal for the Master SPI port.                                             |

| 64           | A4            | GPIO_9/<br>SM_CS | Input/<br>Output | Master SPI Port Chip Select (Input Internal Pull-Up/Tristate Output). Chip select output for the Master SPI port.  Shared with GPIO_9. |

Table 6 - Master SPI Port Pin Descriptions

The ZL38050 device incorporates a two-wire UART (Universal Asynchronous Receiver Transmitter) interface with a fixed 115.2K baud transfer rate, 8 data bits, 1 stop and no parity. The UART port can be used as a debug tool and is used for tuning purposes.

| QFN<br>Pin # | WLCSP<br>Ball | Name    | Туре | Description                                                                                                                                                                                               |

|--------------|---------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50           | B2            | UART_RX |      | <b>UART (Input).</b> Receive serial data in. This port functions as a peripheral interface for an external controller and supports access to the internal registers and memory of the device.             |

| 49           | C2            | UART_TX |      | <b>UART (Tristate Output).</b> Transmit serial data out. This port functions as a peripheral interface for an external controller and supports access to the internal registers and memory of the device. |

**Table 7 - UART Pin Description**

GPIO ports can be used for interrupt and event reporting, fixed function control, bootstrap options, as well as being used for general purpose I/O for communication and controlling external devices.

| QFN<br>Pin #                 | WLCSP<br>Ball               | Name             | Туре             | Description                                                                                                                                                                                                                    |

|------------------------------|-----------------------------|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33, 34,<br>36                | F4, E4,<br>F3               | GPIO_[0:2]       | Input/<br>Output | General Purpose I/O (Input Internal Pull-Down/Tristate Output). These pins can be configured as an input or output and are intended for low-frequency signalling.                                                              |

| 37, 38,<br>39, 40,<br>41, 43 | F2, -,<br>F6, E5,<br>E2, D3 | GPIO_[3:8]       | Input/<br>Output | General Purpose I/O (Input Internal Pull-Down/Tristate Output). These pins can be configured as an input or output and are intended for low-frequency signalling.  GPIO_4 is not available on the WLCSP package.               |

| 64                           | A4                          | GPIO_9/<br>SM_CS | Input/<br>Output | General Purpose I/O (Input Internal Pull-Down/Tristate Output). This pin can be configured as an input or output and is intended for low-frequency signalling.  Alternate functionality with SM_CS.                            |

| 44, 45,<br>47, 48            | E3, C3,<br>-, -             | GPIO_<br>[10:13] | Input/<br>Output | General Purpose I/O (Input Internal Pull-Down/Tristate Output). These pins can be configured as an input or output and are intended for low-frequency signalling.  GPIO_12 and GPIO_13 are not available on the WLCSP package. |

**Table 8 - GPIO Pin Descriptions**

The oscillator pins are connected to a 12.000 MHz crystal or clock oscillator which drives the device's internal PLL. Alternatively, PCLK can be used as the internal clock source.

| QFN<br>Pin # | WLCSP<br>Ball | Name | Туре   | Description                |

|--------------|---------------|------|--------|----------------------------|

| 22           | H7            | ΧI   | Input  | Crystal Oscillator Input.  |

| 23           | F5            | XO   | Output | Crystal Oscillator Output. |

**Table 9 - Oscillator Pin Description**

| QFN<br>Pin #                 | WLCSP<br>Ball                                      | Name                  | Туре   | Description                                                                                                                                                                                                                                                                                                          |

|------------------------------|----------------------------------------------------|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                           | -                                                  | EXT_SEL               | Input  | VDD +1.2 V Select. Select external +1.2 V supply. Tie to DVDD33 if the +1.2 V supply is to be provided externally. Tie to VSS (0 V) if the +1.2 V supply is to be generated internally.  Not available on the WLCSP package.                                                                                         |

| 16                           | _                                                  | VDD12_CTRL            | Output | VDD +1.2 V Control. Analog control line for the voltage regulator external FET when EXT_SEL is tied to VSS. When EXT_SEL is tied to DVDD33, the VDD12_CTRL pin becomes a CMOS output which can drive the shutdown input of an external LDO.  Not available on the WLCSP package.                                     |

| 4,14,<br>24,42,<br>58        | B5, D1,<br>G5, G6                                  | DVDD12                | Power  | Core Supply. Connect to a +1.2 V ±5% supply. Place a 100 nF, 20%, 10 V, ceramic capacitor on each pin decoupled to the VSS plane.                                                                                                                                                                                    |

| 5,<br>21,35,<br>46,51,<br>59 | B3, B7,<br>G3                                      | DVDD33                | Power  | <b>Digital Supply.</b> Connect to a +3.3 V $\pm$ 5% supply. Place a 100 nF, 20%, 10 V, ceramic capacitor on each pin decoupled to the VSS plane.                                                                                                                                                                     |

| 28                           | -                                                  | DVDD33_<br>XTAL       | Power  | Crystal Digital Supply. For designs using a crystal or external oscillator, this pin must be connected to a +3.3 V supply source capable of delivering 10 mA.  For designs that do not use a crystal or external oscillator this pin can be tied to VSS in order to save power.  Not available on the WLCSP package. |

| 10,11                        | E7                                                 | AVDD33                | Power  | <b>Analog Supply.</b> Connect to a +3.3 V ±5% supply. Place a 100 nF, 20%, 10 V, ceramic capacitor on each pin decoupled to the VSS plane.                                                                                                                                                                           |

| 20, 54,<br>60, 61,<br>62     | B4, B6,<br>C4, C5,<br>D2, D4,<br>D5, E6,<br>G2, H2 | VSS                   | Ground | Ground. Connect to digital ground plane.                                                                                                                                                                                                                                                                             |

|                              | _                                                  | Exposed<br>Ground Pad | Ground | <b>Exposed Pad Substrate Connection.</b> Connect to VSS. This pad is at ground potential and must be soldered to the printed circuit board and connected via multiple vias to a heatsink area on the bottom of the board and to the internal ground plane.  Not available on the WLCSP package.                      |

Table 10 - Supply and Ground Pin Description

| QFN<br>Pin #      | WLCSP<br>Ball     | Name | Type | Description                                                                             |

|-------------------|-------------------|------|------|-----------------------------------------------------------------------------------------|

| 25, 26,<br>27, 63 | C6, G4,<br>H4, H5 | NC   |      | <b>No Connection.</b> These pins are to be left unconnected, do not use as a tie point. |

**Table 11 - No Connect Pin Description**

Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively "Microsemi") is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.

This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi's conditions of sale which are available on request.

For more information about all Microsemi products visit our website at www.microsemi.com

TECHNICAL DOCUMENTATION - NOT FOR RESALE

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include mixed-signal ICs, SoCs, and ASICs; programmable logic solutions; power management products; timing and voice processing devices; RF solutions; discrete components; and systems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at www.microsemi.com.

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.