### LG0623 Lab Guide RTG4 FPGA Fabric

а **Міскоснір** company

#### Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revisi            | on History                                           | 1    |

|---|-------------------|------------------------------------------------------|------|

|   | 1.1               | Revision 8.0                                         | 1    |

|   | 1.2               | Revision 7.0                                         | 1    |

|   | 1.3               | Revision 6.0                                         | 1    |

|   | 1.4               | Revision 5.0                                         | 1    |

|   | 1.5               | Revision 4.0                                         | 1    |

|   | 1.6               | Revision 3.0                                         | 1    |

|   | 1.7               | Revision 2.0                                         | 1    |

|   | 1.8               | Revision 1.0                                         | 1    |

| 2 | RTG4              | FPGA Fabric                                          | 2    |

|   | 2.1               | RTG4 Device Components                               |      |

|   | 2.2               | Design Requirements                                  | 2    |

|   | 2.3               | Prerequisites                                        | 3    |

|   | 2.4               | Demo Design                                          | 3    |

|   | 2.5               | Extracting the Source Files                          |      |

|   | 2.6               | Step 1: Creating the Design                          |      |

|   |                   | 2.6.1 Launching Libero SoC Software                  | 4    |

|   | 2.7               | Step 2: Simulating the Design                        |      |

|   | 2.8               | Step 3: Synthesize the Design                        | 18   |

|   | 2.9               | Step 4: Pin Assignments                              |      |

|   | 2.10              | Step 5: Entering Timing Constraints                  |      |

|   | 2.11              | Step 6: Layout and Timing Verification               |      |

|   |                   | 2.11.1 Layout Verification                           |      |

|   | 2.12              | 2.11.2 Timing Verification                           |      |

|   | 2.12              | Step 8: Programming the Device                       |      |

|   | 2.13              | Step 9: Running the Application                      |      |

|   | Z. 1 <del>4</del> | Step 9. Rullilling the Application                   | 20   |

| 3 | Appen             | dix 1: Programming the Device Using FlashPro Express | . 29 |

| 4 | Appen             | idix 2: Running the TCL Script                       | . 32 |

# **Figures**

| Figure 1                | Demo Design Files Top-Level Structure                     |     |

|-------------------------|-----------------------------------------------------------|-----|

| Figure 2                | Libero SoC Project Manager                                |     |

| Figure 3                | Project Details                                           |     |

| Figure 4                | Device Selection Settings                                 |     |

| Figure 5                | Device I/O Settings                                       |     |

| Figure 6                | Imported HDL Source Files                                 | . 6 |

| Figure 7                | Use Enhanced Constraint Flow                              |     |

| Figure 8                | Design Hierarchy Tab with Imported Files (VHDL shown)     | . 7 |

| Figure 9                | Opening the SmartDesign Canvas                            |     |

| Figure 10               | Entering SmartDesign Name                                 |     |

| Figure 11               | Clock & Management Category of the Libero SoC IP Catalog  |     |

| Figure 12               | Configuring the RTG4 Fabric CCC                           |     |

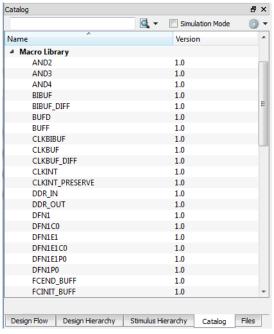

| Figure 13               | Macro Library Category of the Libero SoC IP Catalog       |     |

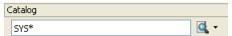

| Figure 14               | IP Catalog Search Field                                   |     |

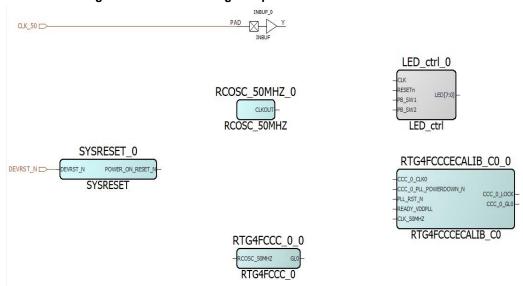

| Figure 15               | SmartDesign Canvas After Adding Components                |     |

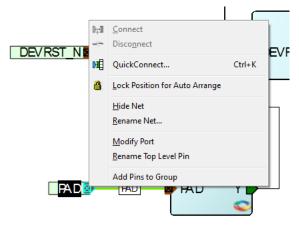

| Figure 16               | Renaming the Top-Level Port PAD                           |     |

| Figure 17               | Modifying Top Level Port Names                            |     |

| Figure 18               | SmartDesign Canvas After Connecting the Ports             |     |

| Figure 19               | Setting Fabric_Top as the Root Level                      |     |

| Figure 20               | Importing the Testbench                                   |     |

| Figure 21               | Importing the Testbench                                   |     |

| Figure 22               | Testbenches in the RTG4_Fabric Project (VHDL shown)       |     |

| Figure 23               | Selecting user_testbench for Simulation                   | 15  |

| Figure 24               | Importing the Simulation Files                            |     |

| Figure 25               | Testbench and Simulation Files (VHDL shown)               |     |

| Figure 26               | Location of the Libero SoC Project                        |     |

| Figure 27               | Libero SoC Project Settings Dialog Box                    |     |

| Figure 28               | Simulation Options                                        |     |

| Figure 29               | Launching Pre-Synthesis Simulation                        |     |

| Figure 30               | ModelSim Waveform Window (VHDL results shown)             |     |

| Figure 31               | Design Flow - Synthesize                                  |     |

| Figure 32               | Opening the I/O Editor                                    |     |

| Figure 33               | Constraint Manager Window                                 |     |

| Figure 34               | I/O Editor                                                |     |

| Figure 35               | I/O Editor with Pin Assignments                           |     |

| Figure 36               | Edit Timing Constraint                                    |     |

| Figure 37               | Constraint Editor                                         |     |

| Figure 38               | Create Clock Constraint Dialog Box                        |     |

| Figure 39               | Clock Constraint Window                                   |     |

| Figure 40               | Entering the Clock Constraint                             |     |

| Figure 41               | Constraints Editor with Clock Constraint                  |     |

| Figure 42               | Running Layout and Verifying Timing                       | 24  |

| Figure 43               | Design Flow Tab after Layout and Timing Report Generation |     |

| Figure 44               | Timing Reports                                            |     |

| Figure 45               |                                                           |     |

| Figure 46               | FlashPro Express Job Project                              |     |

| Figure 47<br>Figure 48  | New Job Project from FlashPro Express Job                 |     |

| Figure 46               | Programming the Device                                    |     |

| i igui <del>C 4</del> 9 | I IASHI TO EAPIGSS-TOIN FASSED                            | JΙ  |

## **Tables**

| Table 1 | State of SW7, SW2, and SW1 Switches | . 2 |

|---------|-------------------------------------|-----|

| Table 2 | Design Requirements                 |     |

| Table 3 | SmartDesign Port Connections        |     |

| Table 4 | Pin Assignments                     |     |

|         | Jumper Settings                     |     |

### 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the current publication.

#### 1.1 **Revision 8.0**

The following is a summary of the changes made in this revision.

- Updated the document for Libero SoC v2021.2.

- Updated section Demo Design, page 3 and Extracting the Source Files, page 3.

- Replaced Figure 11, page 8, Figure 12, page 9, Figure 15, page 10, Figure 18, page 12, Figure 39, page 23, and Figure 41, page 24.

- Updated Table 3, page 11.

### 1.2 **Revision 7.0**

The following is a summary of the changes made in this revision.

- · Added Step 8: Programming the Device, page 28.

- Added Appendix 1: Programming the Device Using FlashPro Express, page 29.

- Added Appendix 2: Running the TCL Script, page 32.

- Removed the references to Libero version numbers.

### **1.3** Revision 6.0

Updated the document for Libero v11.9 SP1 software release.

#### 1.4 Revision 5.0

Updated the document for Libero v11.8 SP2 software release.

### 1.5 Revision 4.0

Updated the document for Libero v11.8 software release.

### **1.6** Revision 3.0

Revision 3.0 was updated for Libero SoC 11.7 SP1 software release change in the document (SAR 82451).

### **1.7** Revision 2.0

Revision 2.0 was updated for Libero SoC 11.7 software release change in the document.

### 1.8 **Revision 1.0**

Revision 1.0 was the first release of this document.

### 2 RTG4 FPGA Fabric

This lab guide demonstrates how to implement a basic RTG4™ Field Programmable Gate Array (FPGA) fabric design using SmartDesign. The design drives LEDs on the RTG4 Development Kit board with different patterns based on the state of SW7, SW2, and SW1 switches (refer to the following table).

Table 1 • State of SW7, SW2, and SW1 Switches

| Reset Switch (SW7) | User Switch (SW2) | User Switch (SW1) | LED [8:1] Behavior                                     |

|--------------------|-------------------|-------------------|--------------------------------------------------------|

| Pressed            | Do not care       | Do not care       | Off                                                    |

| Released           | Released          | Released          | Toggle LED [6:5] and LED [4:3]<br>Red and Green LEDs   |

| Released           | Released          | Pressed           | Shift left                                             |

| Released           | Pressed           | Released          | Shift right                                            |

| Released           | Pressed           | Pressed           | Toggle LED[8:7] and LED[2:1]<br>Orange and Yellow LEDs |

After completing this lab guide, you will be familiar with the following:

- Creating a Libero<sup>®</sup> System-on-Chip (SoC) project

- Implementing an RTG4 fabric design with SmartDesign

- · Simulating the design

- Making pin assignments, running layout, and programming the RTG4 silicon

### 2.1 RTG4 Device Components

This lab guide uses the RTG4 FPGA fabric and fabric clock conditioning circuit (CCC).

### 2.2 Design Requirements

The following table lists the hardware and software design requirements to run the design.

Table 2 • Design Requirements

| Requirement                                                                    | Version                                                          |  |  |

|--------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| Hardware                                                                       |                                                                  |  |  |

| RTG4 FPGA Development Kit:  USB 2.0 cable  12 V, 5A AC power adapter and cords | RT4G150-CB1657PROTO FPGA                                         |  |  |

| Host PC or laptop                                                              | 64-bit Windows 7 and 10                                          |  |  |

| Software                                                                       |                                                                  |  |  |

| Libero SoC                                                                     | Note: Refer to the readme.txt file provided in the design        |  |  |

| FlashPro Express                                                               | files for the software versions used with this reference design. |  |  |

**Note:** Libero SmartDesign and configuration screen shots shown in this guide are for illustration purpose only. Open the Libero design to see the latest updates.

### 2.3 Prerequisites

Download and install Libero SoC (as indicated in the website for this design) on the host PC from the following location: https://www.microsemi.com/product-directory/design-resources/1750-libero-soc

### 2.4 Demo Design

The demo design files are available for download at:

http://soc.microsemi.com/download/rsc/?f=rtg4\_lg0623\_df

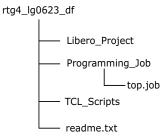

The demo design files include:

- · Source files

- Libero\_Project

- Programming\_Job

- TCL\_Scripts

- readme.txt

The following figure shows the top-level structure of the design files. For more information, refer to the readme.txt file.

Figure 1 • Demo Design Files Top-Level Structure

### 2.5 Extracting the Source Files

- Download the design files from http://soc.microsemi.com/download/rsc/?f=rtg4\_lg0623\_df

- 2. Extract rtg4\_lg0623\_df.zip to extract the required lab files to the <C:, D:, or E:>\Microsemipri folder on the HDD of the PC.

- 3. Ensure that the rtg4 lg0623 df folder contains a Source files sub-folder, which is extracted.

### 2.6 Step 1: Creating the Design

The following steps describe how to create the fabric design using SmartDesign by using the source files provided in the Programming\_Job folder.

### 2.6.1 Launching Libero SoC Software

Follow the instructions to launch the Libero SoC software:

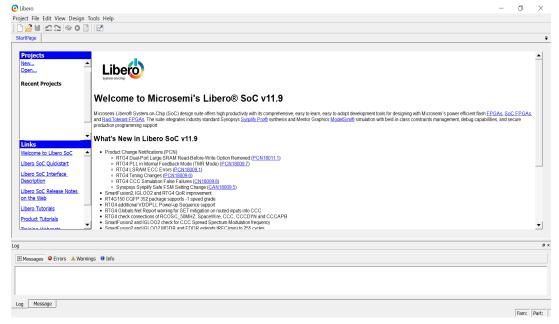

- Go to Start > Programs > Microsemi > Libero SoC v(xx.x) or double-click the shortcut on the desktop to open the Libero SoC Project Manager.

- Create a new project using one of the following options:

- Click New on the Start Page tab, as shown in the following figure.

- Go to Project > New Project from the Libero SoC menu.

Figure 2 • Libero SoC Project Manager

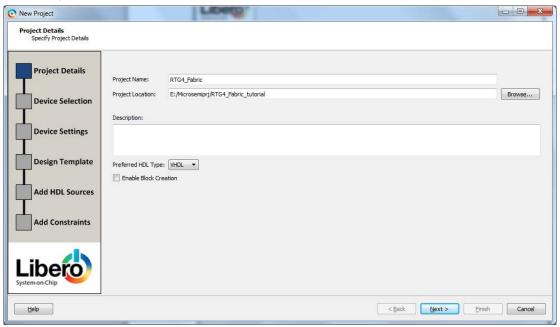

- 3. Enter the following information in the **Project Details** page of the **New Project** dialog box as shown in the following figure:

- Project Name: RTG4\_Fabric

- **Project Location**: <*C*:, *D*:, or *E*:>\Microsemiprj\RTG4\_Fabric\_tutorial (depending on where you extracted the source files)

- Preferred HDL Type: Verilog or VHDL

- Enable Block Creation: Leave Unchecked (default)

#### 4. Click Next.

Figure 3 • Project Details

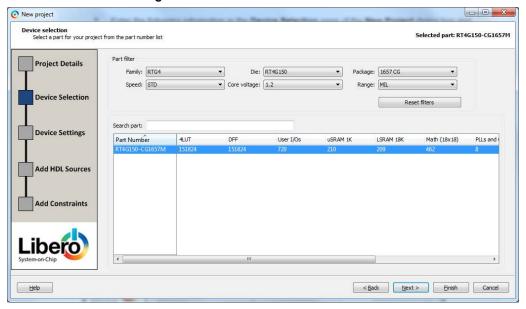

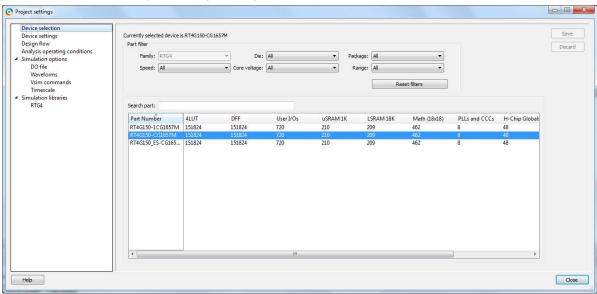

Enter the following information in the **Device Selection** page of the **New Project** dialog box and click **Next**:

Family: RTG4

Die: RT4G150

Package: 1657 CG

Speed: STD

Core Voltage: 1.2

Range: MIL

Figure 4 • Device Selection Settings

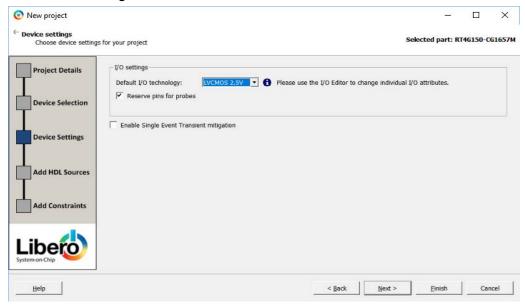

- Enter the following information in the **Device Settings** page of the **New Project** dialog box and click **Next**:

- Default I/O Technology: LVCMOS 2.5 V (default)

- Reserve Pins for Probes: Check (default)

- Reserve Pins for SPI: Leave Unchecked (default)

Figure 5 • Device I/O Settings

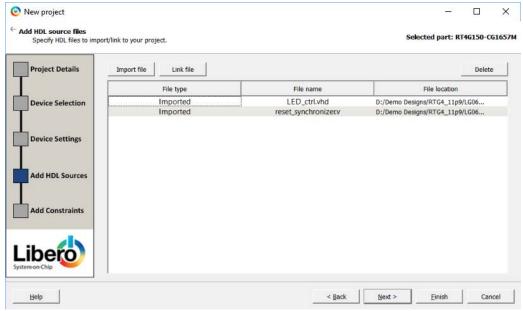

The following figure shows the Add HDL Source Files page.

Figure 6 • Imported HDL Source Files

- Click Import File to import the provided VHDL and Verilog source file into the project.

- 8. Enter the following information in the Import Files dialog box and click Open:

- Files Type: HDL Source Files (\*.vhd \*.v \*.h)

- File Name: LED ctrl.vhd (for VHDL projects) or LED ctrl.v (for Verilog projects)

- File Location: <C:, D:, or E>\Microsemiprj\rtg4 lg0623 df\Source files

- Click Finish.

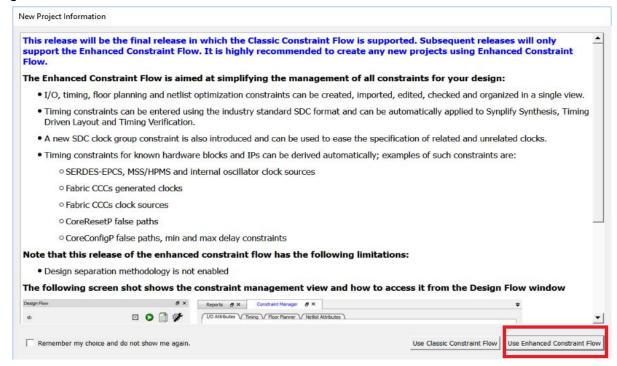

10. Click Use Enhanced Constraint Flow as shown in the following figure.

Figure 7 • Use Enhanced Constraint Flow

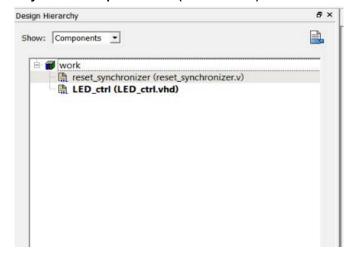

The LED\_ctrl (LED\_ctrl.vhd) file is displayed on the Libero Design Hierarchy tab as shown in the following figure.

Figure 8 • Design Hierarchy Tab with Imported Files (VHDL shown)

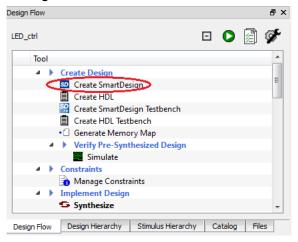

11. Open the SmartDesign canvas by selecting **File > New > SmartDesign** or by double-clicking **Create SmartDesign** under Create Design in the Design Flow tab.

Figure 9 • Opening the SmartDesign Canvas

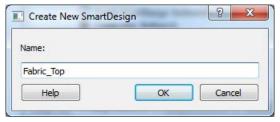

12. Enter **Fabric\_Top** in the **Create New SmartDesign** dialog box then click **OK**. For Verilog designs, the name is case sensitive.

Figure 10 • Entering SmartDesign Name

- 13. Drag-and-drop the LED\_ctrl component from the Design Hierarchy tab in the SmartDesign canvas. This design uses a Fabric CCC to generate the 500 kHz internal clock. The CCC reference clock is the 50 MHz crystal oscillator on the RTG4 Development Kit. In the following steps, configure the CCC to output a 500 kHz clock.

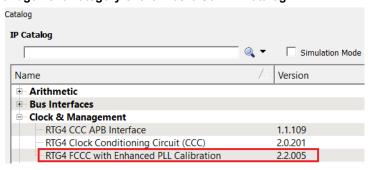

- 14. Expand Clock & Management in the IP catalog.

Figure 11 • Clock & Management Category of the Libero SoC IP Catalog

- 15. Drag-and-drop an instance of the RTG4FCCCECALIB component in the SmartDesign canvas.

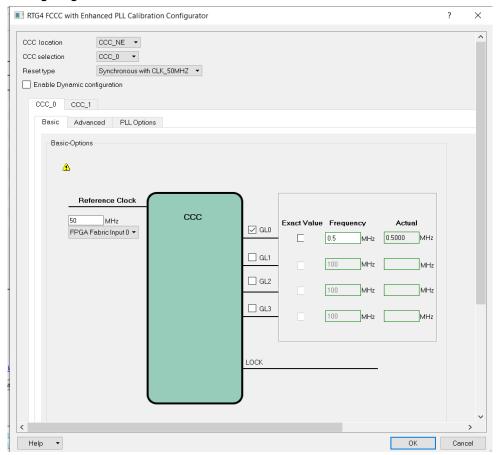

- 16. Double-click the **RTGFCCCECALIB\_C0** component in the SmartDesign canvas to open the RTG4FCCCECALIB Configurator.

- 17. Select the **Basic** tab in the FAB CCC configurator. Enter the following:

- Enter Reference Clock as 50 MHz

- Select FPGA Fabric Input 0 from the drop-down menu

- Select the **GL0** check box

- Enter **Frequency** as 0.5 MHz

Figure 12 • Configuring the RTG4 Fabric CCC

- 18. Click **OK** to save the changes.

- 19. Expand Macro Library in the Libero SoC IP catalog.

Figure 13 • Macro Library Category of the Libero SoC IP Catalog

20. Drag-and-drop an instance of INBUF, and SYSRESET in the SmartDesign Canvas.

**Note:** Type part of the macro name followed by \* in the IP Catalog search field to find macros from the list. When finished, change the field to \* to display the entire catalog.

Figure 14 • IP Catalog Search Field

21. After adding the components, the SmartDesign is displayed, as shown in the following figure. Drag the components to improve the appearance of the canvas, if required.

Note: Expand the canvas area by selecting View > Maximize Work Area or click icon on the tool bar.

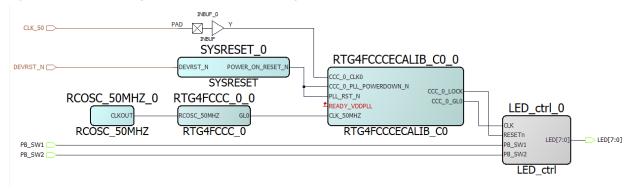

Figure 15 • SmartDesign Canvas After Adding Components

#### 2.6.1.1 Making Connections in the Canvas

Connect the components in the SmartDesign canvas to complete the design. SmartDesign in the Libero SoC software has a connection mode that supports click, drag, and release to make connections.

- Connect the GL0 port of RTG4FCCCECALIB\_C0 component to the CLK port of the LED\_ctrl\_0 as follows:

- Click and drag-and-drop the GL0 port of the RTG4FCCCECALIB\_C0 component in the CLK port of the LED\_ctrl\_0 component.

- 3. Repeat step 2 to connect the ports as shown in the following table.

Table 3 • SmartDesign Port Connections

| From              |                  | То                    |                                     |

|-------------------|------------------|-----------------------|-------------------------------------|

| Component         | Port             | Component             | Port                                |

| RTG4FCCCECALIB_C0 | LOCK             | LED_ctrl_0            | RESETn                              |

| SYSRESET_0        | POWER_ON_RESET_N | RTG4FCCCECALIB_C<br>0 | PLL_RST_N and CCC_0_PLL_POWERDOWN_N |

|                   |                  |                       |                                     |

|                   |                  |                       |                                     |

| INBUF-0           | Υ                | RTGFCCCECALIB_C0      | CCC_0_CLK0                          |

| RTG4FCCC_0        | GL0              | RTGFCCCECALIB_C0      | CLK_50MHz                           |

- 4. Select SmartDesign > Connection Mode from the Libero SoC menu to exit the connection mode.

- Promote the following ports to the top-level. Right-click on the port and select **Promote to Top** Level:

- LED\_ctrl\_0: PB\_SW1

- LED\_ctrl\_0: PB\_SW2

- LED\_ctrl: LED[7:0]

- Rename the top-level PAD CLK\_50 port by right-clicking the port and selecting Rename Top Level Pin.

- 7. Enter CLK\_50 as name in the Rename Top Level Port dialog box as shown in the following figure.

Figure 16 • Renaming the Top-Level Port PAD

Figure 17 • Modifying Top Level Port Names

- 8. Click **OK** to save the top level port name.

- 9. After making the connections, the SmartDesign canvas is displayed as shown in the following figure. You can drag-and-drop the components or use the **SmartDesign Auto Arrange** feature to improve the appearance of the canvas.

Figure 18 • SmartDesign Canvas After Connecting the Ports

- 10. Save the design (File > Save Fabric\_Top).

- 11. Generate the design by clicking **SmartDesign > Generate Component** or by clicking the **Generate Component** on the SmartDesign toolbar.

- 12. Restore the work area from View > Restore Work Area if you have expanded the work area earlier.

- 13. Ensure that **'Fabric\_Top' was generated successfully**. The message appears in the Libero Message window.

- 14. Close the design from **File > Close Fabric\_Top**.

### 2.7 Step 2: Simulating the Design

A testbench, ModelSim macro, and wave format files are provided as part of the source files. The LED\_ctrl module/entity contains a 19-bit counter. To accelerate the simulation of the design, some of the counter bits are forced high in the ModelSim macro file.

Note: Simulation takes a long time with the slow clock rate such as 500 kHz.

Follow the instructions to simulate the design:

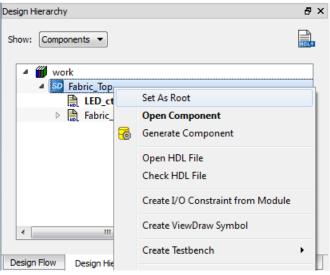

Ensure that Fabric\_Top is in bold font in the Libero Design Hierarchy window. If it does not, select Fabric\_Top, right-click and select Set As Root.

Figure 19 • Setting Fabric\_Top as the Root Level

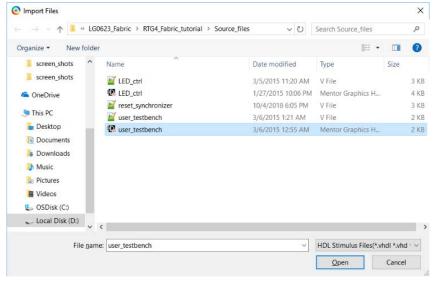

2. Expand **Verify Pre-Synthesized Design** in the Design Flow window. Right-click **Simulate** and select **Import Files**...

Figure 20 · Importing the Testbench

- 3. Enter the following in the **Import Files** dialog box and click **Open**:

- Look in: <C:, D:, or E:>\Microsemiprj\rtg4\_lg0623\_df\Source\_files

- Files of type: HDL Stimulus Files (\*.vhd \*.v)

- File name: user\_testbench.vhd (for VHDL projects) or user\_testbench.v (for Verilog projects)

Figure 21 · Importing the Testbench

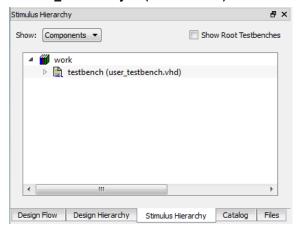

4. Select the **Stimulus Hierarchy** tab. The testbench .hdl file is displayed.

**Note:** If user\_testbench.v or user\_testbench.vhd is not visible in the Stimulus Hierarchy tab, the file is not imported as an HDL stimulus file. Re-import the file as described in step 3 and step 4.

Figure 22 · Testbenches in the RTG4\_Fabric Project (VHDL shown)

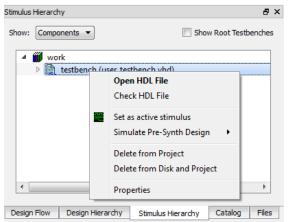

5. Right-click user\_testbench.vor user\_testbench.vhd and select **Set as active stimulus** to use the testbench you imported for simulation. A waveform symbol will be displayed next to the testbench name to indicate it is the active stimulus.

Figure 23 • Selecting user\_testbench for Simulation

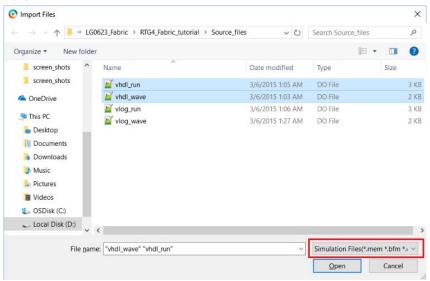

- 6. Import the ModelSim macro and Wave format files by right-clicking **Simulate** under Verify Pre-Synthesized Design in the Design Flow window and selecting **Import Files**.

- 7. Enter the following in the **Import Files** dialog box and click **Open**:

- Look in: <C: or D: or E:>\Microsemiprj\rtg4\_lg0623\_df\Source\_files

- Files of type: Simulation Files (\*.mem \*.bfm \*.dat \*.txt \*.do)

- File name: Hold the shift key and select <code>vhdl\_run.do</code> and <code>vhdl\_wave.do</code> (VHDL projects) or <code>vlog run.do</code> and <code>vlog wave.do</code> (Verilog projects)

Figure 24 • Importing the Simulation Files

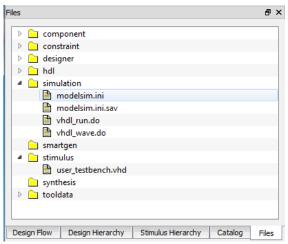

The testbench and simulation files are visible on the **Libero SoC** Files tab under Stimulus and Simulation, respectively.

Figure 25 • Testbench and Simulation Files (VHDL shown)

- 8. Open the ModelSim macro file (vhdl\_run.do or vlog\_run.do) in the Libero SoC editor by double-clicking the filename on the Files tab.

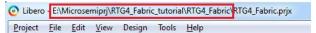

- Locate the variable PROJECT\_DIR at line 11 of vhdl\_run.do or vlog\_run.do and confirm that it

matches the location of the Libero SoC fabric tutorial. The location is displayed at the top of the

Libero SoC GUI (do not include RTG4\_Fabric.prjx). Edit the path if required.

Figure 26 · Location of the Libero SoC Project

- Locate the variable INSTALL\_DIR at line 12 of vhdl\_run.do or vlog\_run.do and confirm that it

matches the location of the Libero SoC RTG4\_Launch installation. Edit the path if required.

- 11. Save the file after making the changes (File > Save vhdl\_run.do or File > Save vlog\_run.do).

- 12. The <code>vhdl\_run.do/vlog\_run.do</code> file contains the force-freeze command to force the counter bits in LED ctrl to high, This command helps to speed up the simulation.

- 13. Close the editor from File > Close vhdl\_run.do or File > Close vlog\_run.do.

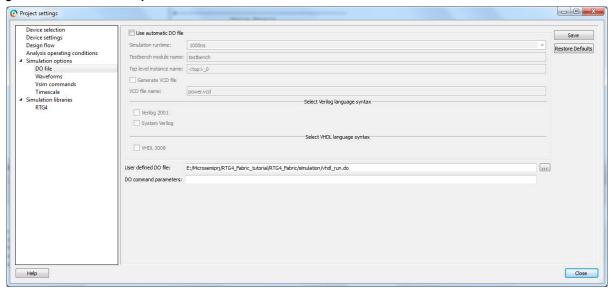

- 14. Open the Libero SoC project settings from **Project > Project Settings**.

Figure 27 • Libero SoC Project Settings Dialog Box

15. Select Do File under Simulation Options in the Project Settings Dialog box.

- 16. Uncheck Use automatic DO file check box.

- 17. Click browse next to User defined DO file, enter the following information and click Open:

- Look in: <C: or D: or E:>\Microsemiprj\rtg4\_lg0623\_df/Libero\_Project/Simulation

- Files of type:\*.do

- File name: whdl run.do (VHDL projects) or wlog run.do (Verilog projects)

The ModelSim macro file (vhdl\_run.do or vlog\_run.do) calls the Wave format file (vhdl\_wave.do or vlog wave.do), and hence do not require any separate settings for the Wave Format file.

Figure 28 • Simulation Options

- 18. Click Save and Close to close the Project Settings dialog box by saving the project settings.

- Expand Verify Pre-Synthesized Design in the Design Flow window. Right-click Simulate and select Open Interactively to launch ModelSim in GUI mode.

Figure 29 · Launching Pre-Synthesis Simulation

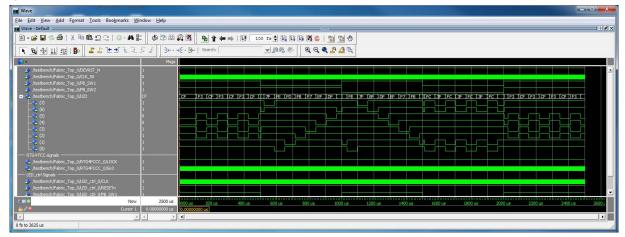

20. The simulation runs for 2.5 ms. When finished, the waveform window is displayed, as shown in the following figure.

Figure 30 • ModelSim Waveform Window (VHDL results shown)

- 21. Scroll in the window. The LED port represents the LED driver (1 = LED off; 0 = LED on). The PB\_SW1 and PB\_SW2 ports represent the switch inputs (0 = switch pressed; 1 = switch released). The DEVRST N input represents the Reset (SW7 input).

- 22. Ensure that the LED output (LED) matches the description in Table 1, page 2.

- 23. Close the ModelSim simulator by File > Quit. Click Yes when asked if you want to quit.

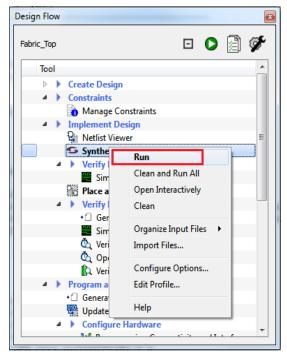

### 2.8 Step 3: Synthesize the Design

In the **Design Flow** window, expand the **Implement Design** and right-click **Synthesize** and select **Run**, as shown in the following figure.

Figure 31 • Design Flow - Synthesize

### 2.9 Step 4: Pin Assignments

Follow the instructions to assign the pins in the software:

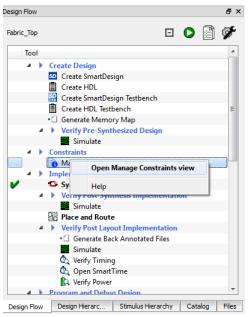

In the Design Flow window, expand Constraints. Right-click Manage Constraints and select Open Manage Constraints View.

Figure 32 · Opening the I/O Editor

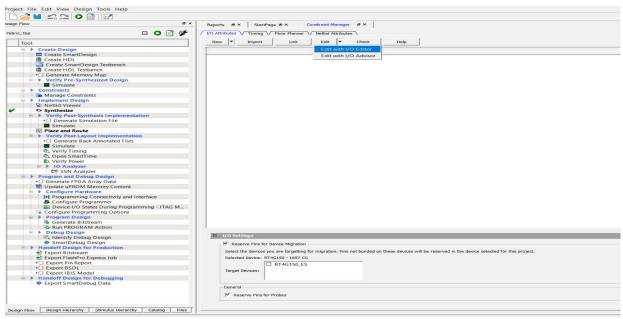

In the Constraint Manager window, select the I/O Attributes tab and click Edit with I/O Editor as shown in the following figure.

Figure 33 • Constraint Manager Window

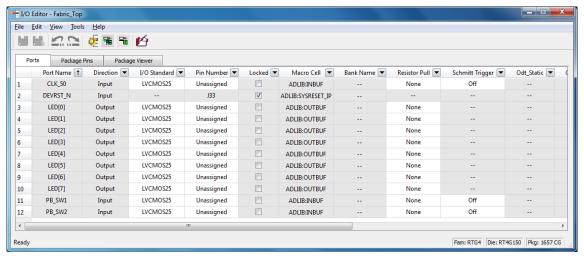

The following figure shows the I/O Editor page.

Figure 34 • I/O Editor

Make the pin assignments as listed in the following table. In I/O Editor, go to the Pin Number

column and click Unassigned in the Pin Number column to see the available I/O pins. Accept the

default settings for all other options.

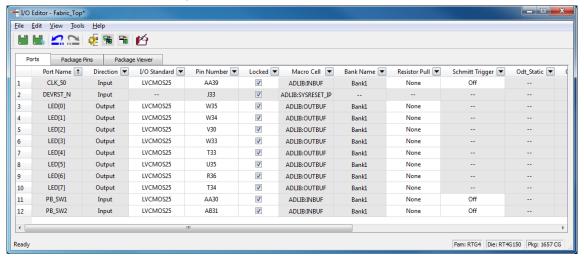

Table 4 • Pin Assignments

| Port Name | I/O Standard | Pin No | Pin Name           |

|-----------|--------------|--------|--------------------|

| CLK_50    | LVCMOS25     | AA39   | MSIOD73PB1/GB12_23 |

| LED[0]    | LVCMOS25     | W35    | MSIOD62PB1         |

| LED[1]    | LVCMOS25     | W34    | MSIOD46PB1         |

| LED[2]    | LVCMOS25     | V30    | MSIOD47PB1         |

| LED[3]    | LVCMOS25     | W33    | MSIOD46NB1         |

| LED[4]    | LVCMOS25     | T33    | MSIOD38PB1         |

| LED[5]    | LVCMOS25     | U35    | MSIOD41NB1         |

| LED[6]    | LVCMOS25     | R36    | MSIOD37PB1         |

| LED[7]    | LVCMOS25     | T34    | MSIOD38NB1         |

| PB_SW1    | LVCMOS25     | AA30   | MSIOD68NB1         |

| PB_SW2    | LVCMOS25     | AB31   | MSIOD65PB1         |

The following table shows the I/O Attribute Editor after assigning the pins.

Figure 35 • I/O Editor with Pin Assignments

- Select File > Commit and Check from the I/O Attribute Editor menu. Ensure that the I/O Editor Log window has no errors.

- 5. Close the I/O Attribute Editor using File > Exit.

### 2.10 Step 5: Entering Timing Constraints

Follow the instructions to set timing constraints in the Libero SoC software:

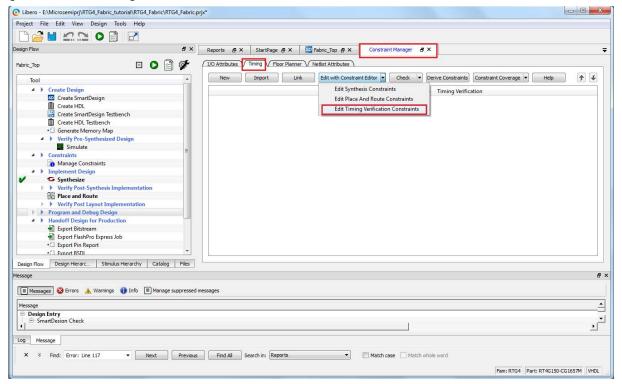

In the Constraint Manager window, select the Timing tab, click Edit with Constraint Editor > Edit Timing Verification Constraints, as shown in the following figure.

Figure 36 • Edit Timing Constraint

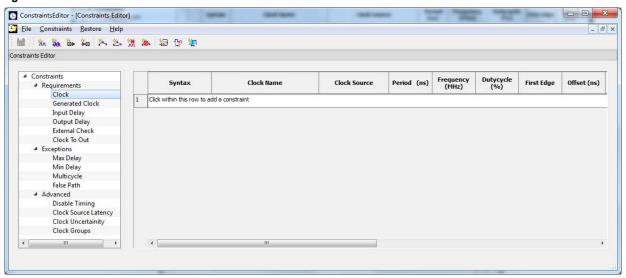

The following figure shows the **Constraint Editor** window.

Figure 37 • Constraint Editor

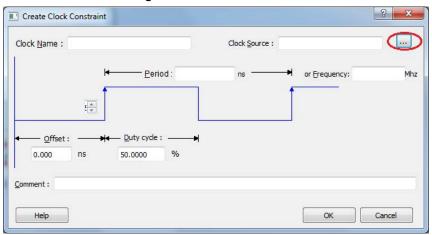

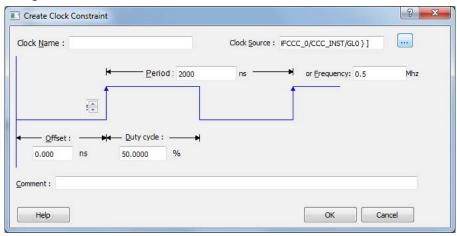

2. Click **Constraints > Clock** to add a Clock constraint. The Create Clock Constraint dialog box is displayed as shown in the following figure and click **Browse**.

Figure 38 · Create Clock Constraint Dialog Box

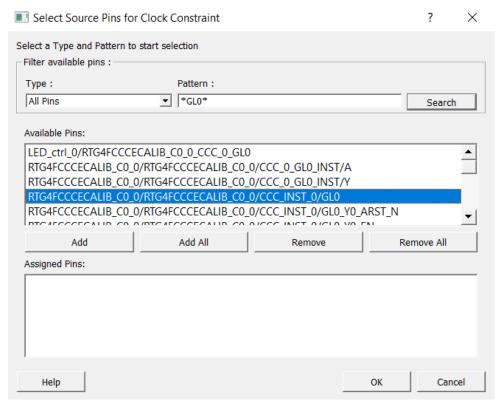

It opens the Select Source Pins for Clock Constraint window. Select the RTG4FCCCECALIB\_C0/RTGFCCCECALIB\_C0\_0/CCC\_INST\_0/GL0 pin, click Add and click OK as shown in the following figure.

Figure 39 · Clock Constraint Window

- 4. Enter the following information in the Create Clock Constraint dialog box and click OK:

- Frequency: 0.5 MHz

Figure 40 • Entering the Clock Constraint

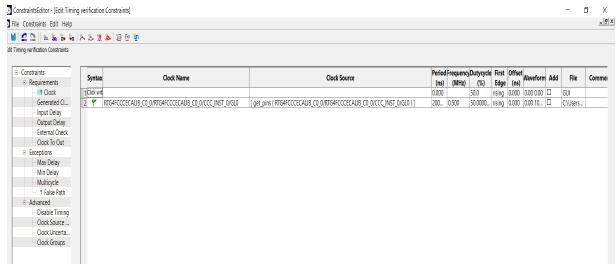

The following figure shows the clock constraint in the Constraints Editor.

Figure 41 • Constraints Editor with Clock Constraint

5. Close the Constraints Editor (File > Exit). Click Yes when prompted to save the changes.

### 2.11 Step 6: Layout and Timing Verification

### 2.11.1 Layout Verification

Expand **Verify Post Layout Implementation** on the Design Flow tab. Right-click **Verify Timing** and select **Run**. Place-and-Route tool is executed and a timing report is generated.

Figure 42 • Running Layout and Verifying Timing

A green checkmark is displayed in the Design Flow window next to Place and Route and Verify Timing indicating that the layout is completed without any errors and a timing report is generated.

Figure 43 • Design Flow Tab after Layout and Timing Report Generation

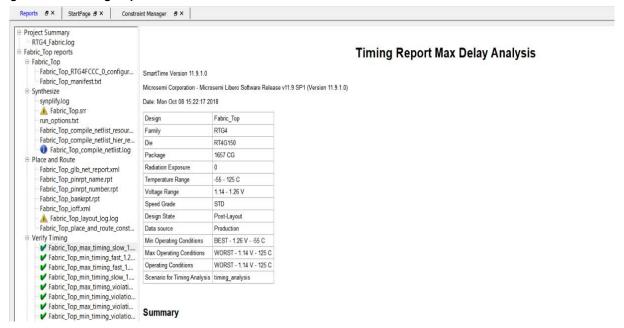

### 2.11.2 Timing Verification

- The timing reports are in the Reports tab.

- Maximum Delay Analysis is contained in the Fabric\_Top\_max\_timing\_slow\_1.14V\_125C.xml report.

Minimum Delay Analysis is contained in the Fabric\_Top\_min\_timing\_fast\_1.26V\_-55C.xml report.

Both the reports are available in the Reports window.

Figure 44 • Timing Reports

Timing violations can quickly be identified by looking at the timing violations reports such as Fabric\_Top\_max\_timing\_violations\_slow\_1.14V\_125C.xml or Fabric\_Top\_min\_timing\_violations\_fast\_1.26V\_-55C.xml.

### 2.12 Step 7: Setting Up the Demo Design

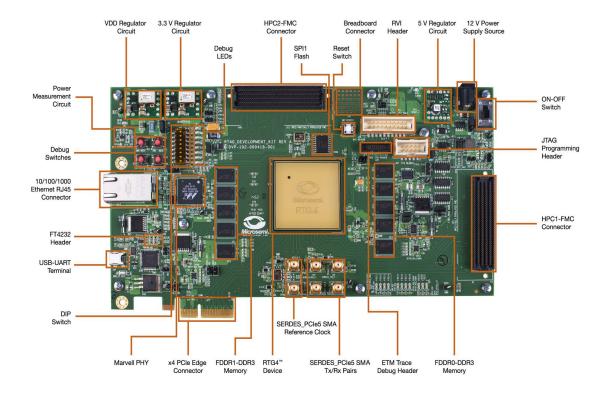

The RTG4 Development Kit board is shown in the following figure.

Figure 45 • RTG4 Development Kit Board

The following steps describe how to set up the RTG4 Development Kit to run the demo design:

- Ensure that the board is powered OFF using SW6 switch. Also ensure that AC input connector is not connected to JP before connecting the cable or changing the jumper connections.

- 2. Plug the AC adapter to the J9 connector and plug into a 120 V AC outlet.

3. Before programming (and powering up) the RTG4 Development Kit board, ensure that the jumpers are positioned as show in the following table.

Table 5 • Jumper Settings

| Jumper | Location                                   | Purpose                                                              | Settings                       |

|--------|--------------------------------------------|----------------------------------------------------------------------|--------------------------------|

| J16    | Above SW3                                  | Select VDD core voltage                                              | 2-3 installed                  |

| J17    | Below J9 AC connector                      | Select either SW6 input or signal<br>ENABLE_FT4232 from FT4232H chip | 1-2 installed                  |

| J19    | Below J9 AC connector                      |                                                                      | 1-2 installed                  |

| J21    | To the right of the dip switch bank        | Bank 7 supply voltage                                                | 1-2 installed                  |

| J23    | To the right of the FP4 programming header |                                                                      | 1-2 installed                  |

| J26    | Below ETM Trace header                     | Bank 2 supply voltage                                                | 1-2 installed                  |

| J28    | Below the dip switch bank                  |                                                                      | 1-2 installed                  |

| J32    | To the left of the FMC connector (HPC1)    | Enable FlashPro5 for programming                                     | 1-2 installed                  |

| J33    | Below FP4 programming header               |                                                                      | 1-2 installed<br>3-4 installed |

- 4. Connect USB cable (mini USB to Type A USB cable) to J47 of the RTG4 Development Kit board and another end of the cable to the USB port of the Host PC.

- 5. Switch ON the power supply switch, **SW6**.

### 2.13 Step 8: Programming the Device

To program the RTG4 Development Kit with the job file provided as part of the design files using FlashPro Express software, refer to Appendix 1: Programming the Device Using FlashPro Express, page 29.

### 2.14 Step 9: Running the Application

Follow the instructions to run the application:

- 1. Reset the board by holding the **SW7** reset switch. The LEDs must be in the OFF position.

- 2. Release SW7 and observe the pattern of the LEDs. LEDs [6:5] and LEDs [4:3] (the Red and Green LEDs) must be toggled.

- 3. Press and hold the SW1 switch and observe the pattern of the LEDs. Release the SW1 switch and press the SW2 switch and observe the pattern of the LEDs. Press and hold SW1 and SW2 switches together. The LED pattern must match the description in Table 1, page 2.

- 4. When finished, change the SW6 switch to the OFF position and power OFF the board.

# 3 Appendix 1: Programming the Device Using FlashPro Express

This section describes how to program the RTG4 device with the programming job file using FlashPro Express.

To program the device, perform the following steps:

- 1. Ensure that the jumper settings on the board are the same as those listed in *Table 3 of UG0617:* RTG4 Development Kit User Guide.

- Optionally, jumper J32 can be set to connect pins 2-3 when using an external FlashPro4, FlashPro5, or FlashPro6 programmer instead of the default jumper setting to use the embedded FlashPro5.

Note: The power supply switch, SW6 must be switched OFF while making the jumper connections.

- 3. Connect the power supply cable to the **J9** connector on the board.

- 4. Power **ON** the power supply switch **SW6**.

- If using the embedded FlashPro5, connect the USB cable to connector J47 and the host PC.

Alternatively, if using an external programmer, connect the ribbon cable to the JTAG header J22 and connect the programmer to the host PC.

- 6. On the host PC, launch the FlashPro Express software.

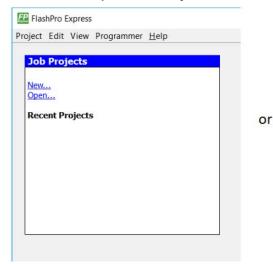

- 7. Click **New** or select **New Job Project from FlashPro Express Job** from **Project** menu to create a new job project, as shown in the following figure.

Figure 46 • FlashPro Express Job Project

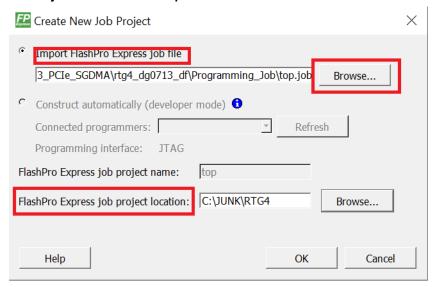

- 8. Enter the following in the New Job Project from FlashPro Express Job dialog box:

- **Programming job file:** Click **Browse**, and navigate to the location where the .job file is located and select the file. The default location is:

- <download folder>\rtg4 lg0623 df\Programming Job

- FlashPro Express job project location: Click Browse and navigate to the desired FlashPro Express project location.

Figure 47 • New Job Project from FlashPro Express Job

- 9. Click **OK**. The required programming file is selected and ready to be programmed in the device.

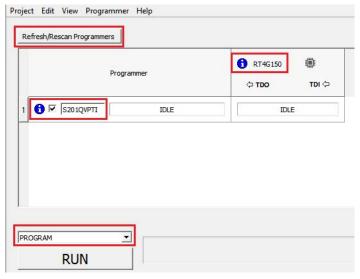

- 10. The FlashPro Express window appears as shown in the following figure. Confirm that a programmer number appears in the Programmer field. If it does not, confirm the board connections and click Refresh/Rescan Programmers.

Figure 48 • Programming the Device

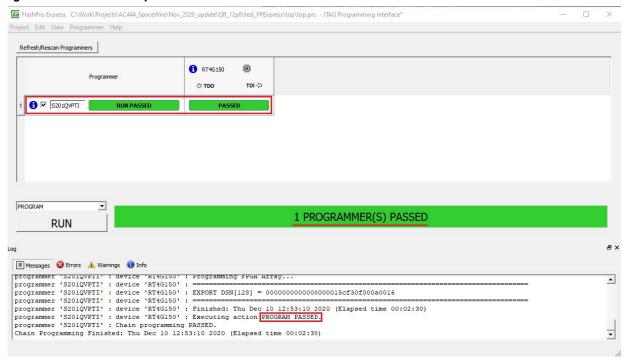

11. Click **RUN**. When the device is programmed successfully, a **RUN PASSED** status is displayed as shown in the following figure.

Figure 49 • FlashPro Express—RUN PASSED

12. Close FlashPro Express or click Exit in the Project tab.

### 4 Appendix 2: Running the TCL Script

TCL scripts are provided in the design files folder under directory TCL\_Scripts. If required, the design flow can be reproduced from Design Implementation till generation of job file.

To run the TCL, follow the steps below:

- 1. Launch the Libero software

- 2. Select Project > Execute Script....

- 3. Click Browse and select script.tcl from the downloaded TCL\_Scripts directory.

- 1 Click Run

After successful execution of TCL script, Libero project is created within TCL\_Scripts directory.

For more information about TCL scripts, refer to rtg4\_lg0623\_df/TCL\_Scripts/readme.txt.

Refer to *Libero*® *SoC TCL Command Reference Guide* for more details on TCL commands. Contact Technical Support for any queries encountered when running the TCL script.