# DG0611 Demo Guide Implementing JESD204B Interface Using SmartFusion2

a MICROCHIP company

#### Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revis | ion History                                         | 1  |

|---|-------|-----------------------------------------------------|----|

|   | 1.1   | Revision 5.0                                        |    |

|   | 1.2   | Revision 4.0                                        |    |

|   | 1.3   | Revision 3.0                                        |    |

|   | 1.4   | Revision 2.0                                        |    |

|   | 1.5   | Revision 1.0                                        |    |

|   |       |                                                     |    |

| 2 | Imple | menting JESD204B Interface Using SmartFusion2       | 2  |

|   | 2.1   | Design Requirements                                 | 3  |

|   | 2.2   | Prerequisites                                       | 3  |

|   | 2.3   | Demo Design                                         | 4  |

|   |       | 2.3.1 Features                                      | 5  |

|   |       | 2.3.2 Description                                   | 6  |

|   | 2.4   | Simulating the Design                               | 10 |

|   | 2.5   | Setting Up the Demo Design                          | 13 |

|   | 2.6   | Programming the Device                              | 14 |

|   | 2.7   | Installing the GUI                                  | 14 |

|   | 2.8   | Running the Demo Design                             | 15 |

| 3 | Appe  | ndix: Programming the Device Using FlashPro Express | 23 |

# **Figures**

| Figure 1  | Top-Level Directory Structure             | . 4 |

|-----------|-------------------------------------------|-----|

| Figure 2  | Hardware Implementation Block Diagram     |     |

| Figure 3  | Core JESD204B Tx Configuration            |     |

| Figure 4  | Core JESD204B Rx Configuration            |     |

| Figure 5  | SERDESIF2 Configuration                   |     |

| Figure 6  | Simulating the Design                     |     |

| Figure 7  | Transcript Window                         | 11  |

| Figure 8  | Simulation Waveform Window                |     |

| Figure 9  | Hardware Setup                            | 13  |

| Figure 10 | GUI Set Up Window                         | 14  |

| Figure 11 | GUI Set Up Progress Bar                   |     |

| Figure 12 | SmartFusion2 JESD204B Demo GUI Window     | 16  |

| Figure 13 | Serial Port Configuration                 | 17  |

| Figure 14 | PRBS Pattern Selection                    | 18  |

| Figure 15 | Data Error Generation                     | 19  |

| Figure 16 | Data Error Generation                     | 20  |

| Figure 17 | Waveform Pattern Selection                | 2   |

| Figure 18 | Waveform Tab                              | 22  |

| Figure 19 | FlashPro Express Job Project              | 23  |

| Figure 20 | New Job Project from FlashPro Express Job | 24  |

| Figure 21 | Programming the Device                    | 24  |

| Figure 22 | FlashPro Express—RUN PASSED               | 25  |

# **Tables**

| Table 1 | Design Requirements                                  | . 3 |

|---------|------------------------------------------------------|-----|

| Table 2 | SmartFusion2 Security Evaluation Kit Jumper Settings | 13  |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

#### 1.1 **Revision 5.0**

The following is a summary of the changes made in this revision.

- Updated the document for Libero SoC v12.6.

- Removed the references to Libero version numbers.

#### 1.2 **Revision 4.0**

Updated the demo guide for Libero v11.8 software release changes.

#### 1.3 **Revision 3.0**

Updated the demo guide for Libero v11.7 software release changes.

#### 1.4 **Revision 2.0**

The following is a summary of the changes in revision 2.0 of this document.

- Updated the demo guide for Libero v11.6 software release changes.

- Updated the labview runtime installer instruction in the Installing the GUI, page 14.

#### 1.5 **Revision 1.0**

Revision 1.0 was the first publication of this document.

# 2 Implementing JESD204B Interface Using SmartFusion2

The demo describes the use of SmartFusion<sup>®</sup>2 System-on-Chip (SoC) Field Programmable Gate Array (FPGA) serializer/de-serializer (SerDes) and JESD204B Tx/Rx IP cores for JESD204B data converter interface. This demo uses the CoreJESD204BTx and CoreJESD204BRx IP cores in a loop-back configuration and operates as a standalone demo for the JESD204B data converter interface that can be used with the SmartFusion2 Security Evaluation Kit board. A testbench is also provided to simulate the CoreJESD204BTx/Rx cores. Instructions are provided on how to use the corresponding demo as a reference design for JESD204B applications.

This document is intended for FPGA designers, embedded designers, and system-level designers.

The SmartFusion2 SoC and IGLOO®2 FPGA family device has embedded high-speed SerDes blocks that can handle data rates from 1 Gbps to 5 Gbps. The SerDes module integrates several functional blocks to support multiple high-speed serial protocols within the FPGA. JESD204B is a high-speed serial interface standard for data converters from the JEDEC committee. It reduces the number of data inputs and outputs between the high-speed data converters and receivers. Microsemi has both JESD204B Rx/Tx IP cores compliant with the JESD204B standards. These cores are easy to integrate with JESD204B based data converters for developing high bandwidth applications such as wireless infrastructure transceivers, software defined radios, medical imaging systems, and radar and secure communications.

The SmartFusion2 and IGLOO2 JESD204B Rx/Tx IP core supports link widths of x1, x2, and x4 up to 3.2 Gbps per lane using subclass 0, 1, and 2. This demo guide describes how to use the SmartFusion2 SerDes blocks, JESD204B Rx/Tx IP cores for interfacing subclass0 JES204B based data converters with data rates up to 2 Gbps. This demo does not use any Analog-to-Digital Converter (ADC) or Digital-to-Analog Converter (DAC) devices, but operates in a loop-back to provide an example of these IP cores in a working design. This demo design works only on SmartFusion2 devices, not on IGLOO2 devices.

- For more information about the JESD204B interface, refer to the JESD204B standard from JEDEC.

- For more information about SerDes blocks, refer to the UG0447: IGLOO2 and SmartFusion2 High Speed Serial Interfaces User Guide.

# 2.1 Design Requirements

The following table lists the hardware, software, and IP requirements for this demo design.

Table 1 • Design Requirements

| Requirement                                                                                                                                                                                                                   | Version                                                              |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|

| Operating System                                                                                                                                                                                                              | 64 bit Windows 7 and 10                                              |  |

| Hardware                                                                                                                                                                                                                      |                                                                      |  |

| <ul> <li>SmartFusion2 Security Evaluation Kit</li> <li>12 V - 2 A wall mounted power supply</li> <li>FlashPro4 JTAG Programmer</li> <li>USB 2.0 A-male to mini-B for UART</li> <li>2 SMA to SMA cables<sup>1</sup></li> </ul> | Rev D or later                                                       |  |

| Software                                                                                                                                                                                                                      |                                                                      |  |

| Libero <sup>®</sup> System-on-Chip (SoC)                                                                                                                                                                                      | Refer to the readme.txt file provided in the design files for the    |  |

| SoftConsole                                                                                                                                                                                                                   | ─software versions used with this reference SoftConsole design.<br>— |  |

| FlashPro Express                                                                                                                                                                                                              |                                                                      |  |

| Host PC Drivers                                                                                                                                                                                                               | USB to UART drivers                                                  |  |

<sup>1.</sup> SmartFusion2 Security Evaluation Kit does not include the 2 SMA cables. The user needs to obtain the cables to run this demo.

**Note:** Libero SmartDesign and configuration screen shots shown in this guide are for illustration purpose only. Open the Libero design to see the latest updates.

# 2.2 Prerequisites

Before you begin:

Download and install Libero SoC (as indicated in the website for this design) on the host PC from the following location.

https://www.microsemi.com/product-directory/design-resources/1750-libero-soc

# 2.3 Demo Design

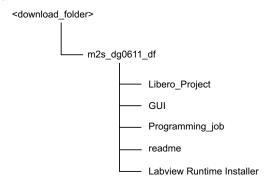

The demo design files are available for download from the following path in the Microsemi website: http://soc.microsemi.com/download/rsc/?f=m2s\_dg0611\_df

The demo design files include:

- Libero project

- Programming job

- Graphical User Interface (GUI)

- Labview Runtime Installer

For more information, refer to the readme.txt file.

The following figure shows the top-level structure of the design files.

Figure 1 • Top-Level Directory Structure

#### 2.3.1 Features

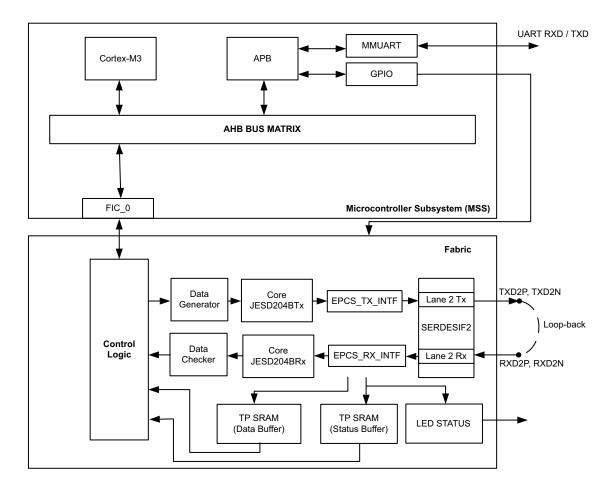

The SmartFusion2 JESD204B demo is a standalone reference design developed for interfacing JESD204B compliant data converters with the SmartFusion2 devices. In this demo design, the SerDes lanes are looped back and the data generator pattern is checked by the data checker after traversing through both the JESD204B Tx/Rx IP cores. A user friendly GUI is provided to control and monitor the status signals. The following figure shows the JESD204B demo design block diagram implemented in the SmartFusion2 device.

This reference design describes the following:

- Hardware demonstration by externally looping back the SerDes Tx/Rx lanes externally on SmartFusion2 Security Evaluation Kit

- Simulation by looping back the SerDes Tx/Rx lane internally on a test bench to verify the mode of operation

Figure 2 • Hardware Implementation Block Diagram

#### 2.3.2 Description

#### 2.3.2.1 Hardware Design

The hardware design for the JESD204B demo implementation includes the following:

- Data Generator

- JESD204BTx IP core

- JESD204BRx IP core

- Data Checker

- SERDESIF

- Control Logic

- MMUART for console communications

- Fabric Interface Controller

Figure 2, page 5 shows the block diagram for the design implementation. For more information, refer to the Block Descriptions, page 6.

#### 2.3.2.2 Block Descriptions

#### 2.3.2.2.1 Data Generator

The data generator has a PRBS generator and a waveform generator. The PRBS generator can generate PRBS9, PRBS15, PRBS23, and PRBS31 patterns. An error insertion mode is also implemented in the PRBS generator, which inserts an error into the PRBS sequence for checking. The waveform generator generates a sine wave, saw tooth wave, triangle wave, and square wave. The data generator feeds the

16-bit test pattern to CoreJESD204BTx core for transmitting data for SEREDESIF.

#### 2.3.2.2.2 Data Checker

The data checker receives 16-bit data output from the CoreJESD204BRx IP core and checks for the correctness of the received data. It generates both an error count and status signal, which is sent to the GUI for status indication. It only checks the PRBS sequences of the data generator.

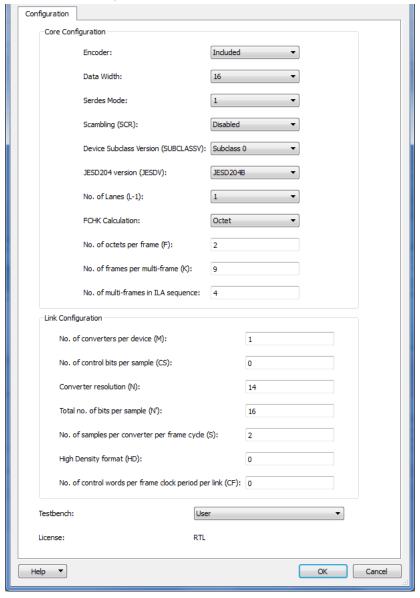

#### 2.3.2.2.3 Core JESD204B Tx

The CoreJESD204BTx is compatible with the JEDEC JESD204B standard. For this demo design, the IP core is configured, as shown in the following figure.

Figure 3 • Core JESD204B Tx Configuration

For more information about settings, refer to the IP Core Configuration Guide.

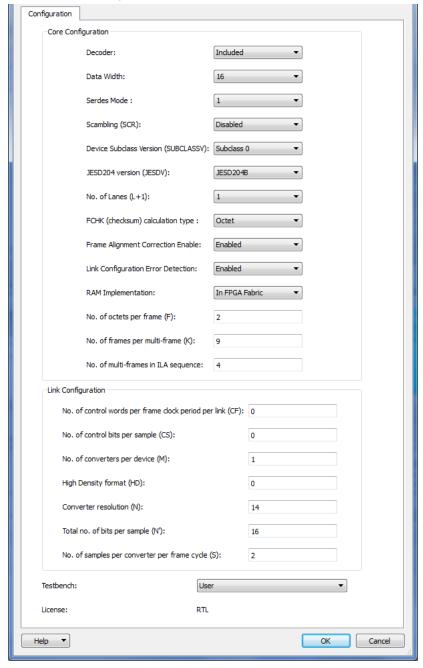

#### 2.3.2.2.4 Core JESD204B Rx

The Core JESD204B Rx is compatible with the JEDEC JESD204B standard. The IP core is configured, as shown in the following figure.

Figure 4 • Core JESD204B Rx Configuration

For more information about settings, refer to the IP Core Configuration Guide.

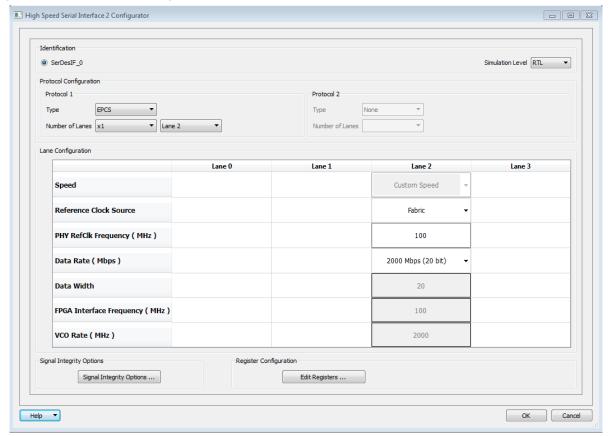

#### 2.3.2.2.5 **SERDESIF**

The SmartFusion2 SoC FPGA high-speed SerDes is a hard IP block on chip that supports the high-speed data rates up to 5 Gbps. The SERDESIF EPCS mode is used for JESD204B providing a data path directly to the PMA.

For more information about the SerDes block, refer to UG0447: IGLOO2 and SmartFusion2 High Speed Serial Interfaces User Guide.

In this demo, the SERDESIF2 block is configured in EPCS mode on lane 2 to interface JESD204B IP cores, with a reference clock of 100 MHz from fabric to support a 2 Gbps data rate. The following figure shows the SerDes block configuration details.

Figure 5 • SERDESIF2 Configuration

**Note:** The M2S090/M2GL090 and M2S060/M2GL060 devices use the SERDESIF2 module. All the other SmartFusion2 device use the SERDESIF module.

#### 2.3.2.2.6 MSS Block

The Microcontroller Subsystem (MSS) block sends and receives the data between the host PC (GUI interface) and fabric logic. The MMUART interface is used to communicate with the host PC. The FIC\_0 interface (APB master) is used to communicate with the fabric user logic.

#### 2.3.2.2.7 TPSRAM IP

TPSRAM IP is an LSRAM module and is used for loading status and data signal, and is configured as follows:

- Status data Buffer (Depth: 1024, Width: 32)

- Output data Buffer (Depth: 1024, Width: 32)

#### 2.3.2.2.8 Control Logic

The control logic implemented in the fabric consists of an APB slave FSM to communicate with an MSS APB master and also controls operations such as reading and writing status and output data buffers.

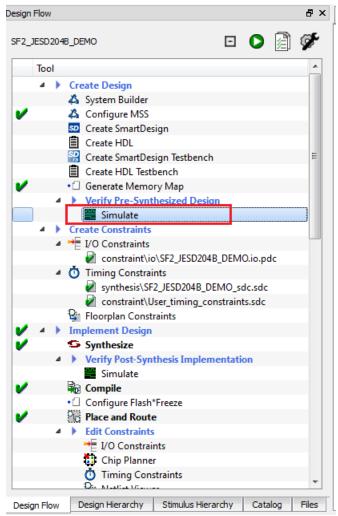

#### 2.4 Simulating the Design

The design is simulated using the provided testbench. The testbench simulates the JESD204B demo design for PRBS pattern and waveform selection.

To run the simulation,

- Double-click **Simulate** under **Verify Pre-Synthesized Design** in the **Design Flow** tab of the Libero project, as shown in the following figure.

- Or right-click and select Simulate to invoke the simulator.

#### Figure 6 • Simulating the Design

The testbench generates the test selection for the PRBS input (PRBS7, PRBS15, PRBS23, and PRBS31) and sine wave for waveform input. It also monitors the JESD204B output status signals (SYNC\_N, ALIGNED, and CGS\_ERR) for the verification of JESD204B phases and PRBS checker output status signals for the correctness of the Input PRBS pattern (PRBS7, PRBS15, PRBS23, and PRB31).

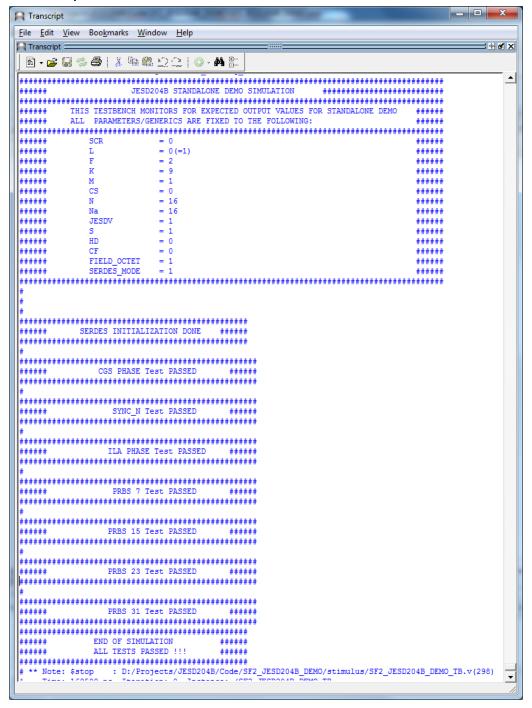

The simulation ends after executing all the test cases. The status of the test cases is shown in the **Modelsim Transcript** window, as shown in the following figure.

Figure 7 • Transcript Window

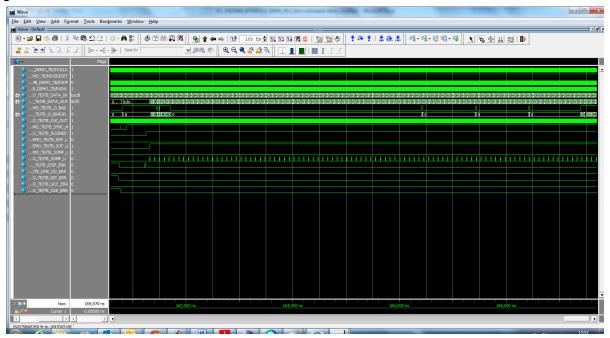

After simulation, the Simulation Waveform window is displayed, as shown in the following figure.

Figure 8 • Simulation Waveform Window

## 2.5 Setting Up the Demo Design

The following steps describe how to set up the demo design:

- 1. Connect the FlashPro4 programmer to the FlashPro header on the SmartFusion2 Security Evaluation Kit, as shown in the following figure.

- Connect the jumpers to the SmartFusion2 Security Evaluation Kit board as listed in the following table.

Table 2 • SmartFusion2 Security Evaluation Kit Jumper Settings

| Jumper | Pin From | Pin To | Comments |

|--------|----------|--------|----------|

| J3     | 1        | 2      | Default  |

| J8     | 1        | 2      | Default  |

**CAUTION:** Ensure that the power supply switch SW7 is switched OFF while connecting the jumpers to the SmartFusion2 FPGA Security Evaluation Kit.

- 3. Connect the J18 connector and host PC using the mini-B cable.

- 4. Ensure that the USB to UART bridge drivers are automatically detected (can be verified in the Device Manager).

- 5. Loop-back the SerDes Lane 2 (TxD2P <-> RxD2P, TxD2N <-> RxD2N) using two SMA-SMA cables, as shown in the following figure.

- 6. Connect the 12 V power adapter that shipped with the FPGA development board to the power jack J6, and switch on the power supply.

Figure 9 • Hardware Setup

**Note:** SerDes Lane 1 is looped back from transmit to receive data on the board. If the SMA cables are not available, the user can reconfigure the SERDESIF2 to Lane 1.

#### 2.6 Programming the Device

Program the SmartFusion2 Security Evaluation Kit board with the job file provided as part of the design files using FlashPro Express software, refer to Appendix: Programming the Device Using FlashPro Express, page 23.

### 2.7 Installing the GUI

The JESD204B demo is provided with a user friendly GUI that runs on the host PC to communicate using a UART with the SmartFusion2 Security Evaluation Kit.

The following steps describe how to run the installer if the GUI is used for the first time:

- Download the design files from http://soc.microsemi.com/download/rsc/?f=m2s\_dg0611\_df

- Open and run Labview Runtime Installer > setup.exe before installing JESD204B GUI. Restart the host PC if necessary.

- 3. Open GUI\_Installer > Volume > setup.exe.

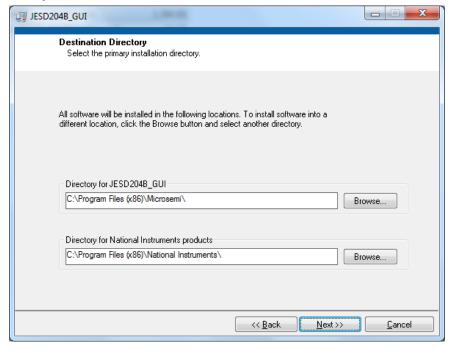

- 4. Click **Yes** for any message from **User Account Control**. The Destination Directory window is displayed with the default locations, as shown in the following figure.

- 5. Click Next.

Figure 10 • GUI Set Up Window

6. Follow the instructions in the GUI to start the installation.

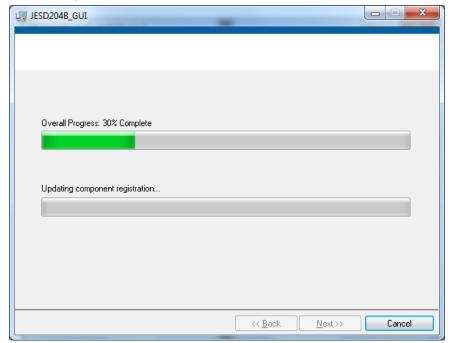

A progress bar appears, which shows the progress of installation as shown in the following figure.

Figure 11 • GUI Set Up Progress Bar

- 7. Wait for the installation to complete. After successful installation, the Installation Complete message is displayed.

- 8. Click Finish.

- 9. Restart the host PC before using the installed GUI.

# 2.8 Running the Demo Design

This section describes how to use the GUI for selecting the test patterns and monitoring the loop-back data for the demo design. It provides an interactive GUI for the selection of different PRBS test patterns as a demo input and observes the JESD204B status signals and PRBS status collected from the board. It also shows the output waveform samples collected from the board during waveform selection on the waveform tab.

The following steps describe how to run the demo design:

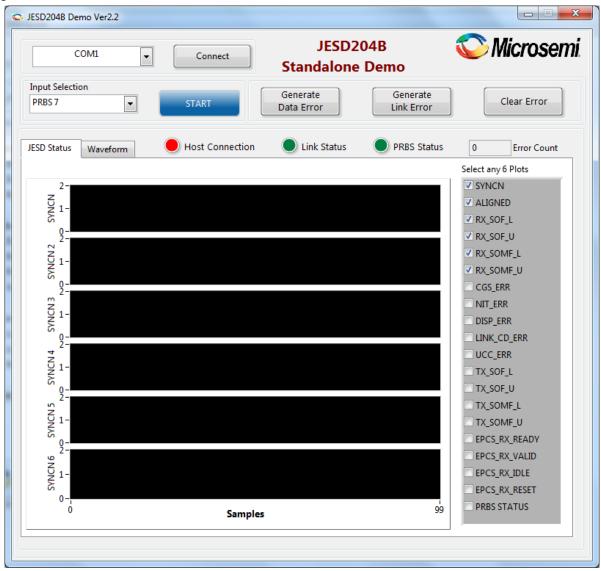

Open Programs > SF2\_JESD204B Demo.

The following figure shows the GUI window.

Figure 12 • SmartFusion2 JESD204B Demo GUI Window

The drop-down list for ports has the list of serial ports available on the host PC. The working ports are enabled and the unavailable ports are grayed out.

Note: The default settings for the design are 115200 baud, no flow control, one stop, and no parity.

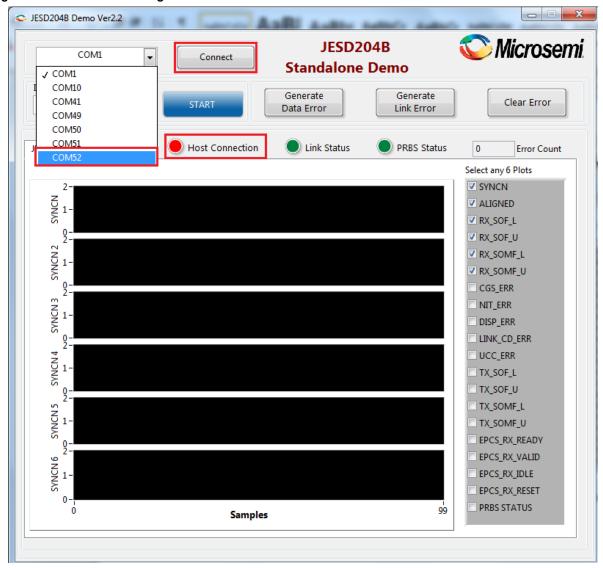

2. Select the COM port number that is detected to configure the serial port.

3. Click **Connect** to connect the host PC to the hardware through the selected port, as shown in the following figure.

Note: Port numbers may vary. Select the correct port number from the list.

Figure 13 • Serial Port Configuration

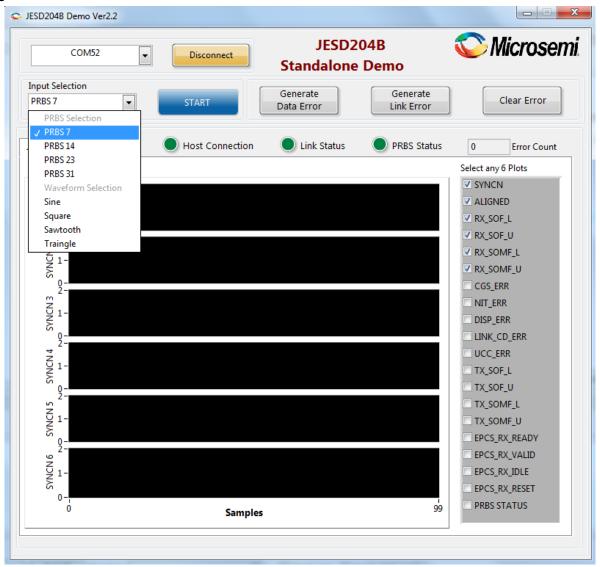

4. Select the pattern to be transmitted using the **Input selection**. Select one of the patterns in PRBS selection, Select **PRBS 7** as shown in the following figure.

Figure 14 • PRBS Pattern Selection

Click START to start the JESD204B demo. The selected pattern is sent over a serial transmit link.

The looped back data is received by the receiver and checked for any errors. The status can be

monitored using the status signals in the GUI at any time.

**Note:** Select any six signal check boxes on the right side panel to view the status of the signals. If the count is more than six, de-select the selected signals before selecting any new signals.

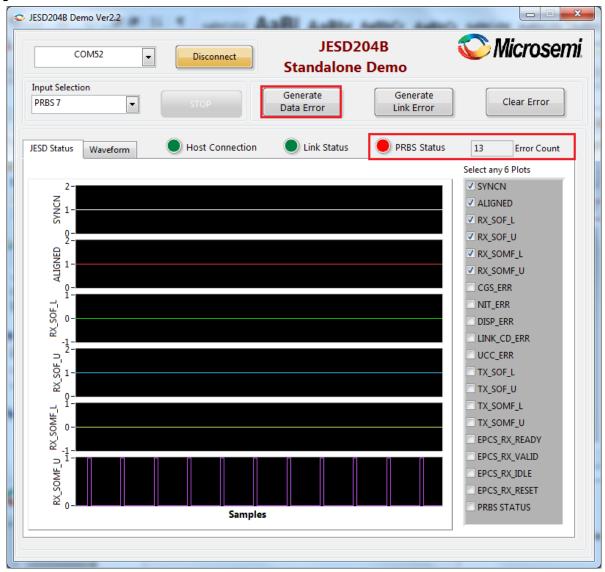

6. Click **Generate Data Error** and observe error status using GUI. The following figure shows the Host Connection, Link Status, PRBS Status, and Error Count.

Figure 15 • Data Error Generation

Click Clear Error to stop generating the error data PRBS Status turns green, and Error Count is displayed as 0.

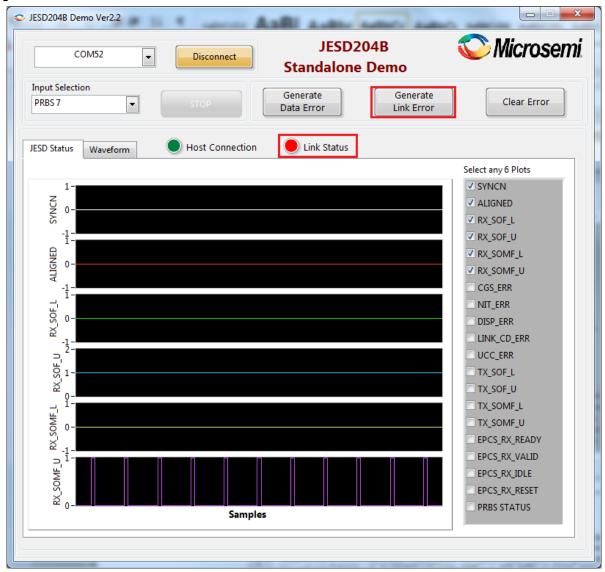

8. Click **Generate Link Error** to generate error in 20 bits SerDes lane. The following figure shows the **Link Status** changed to RED on link error.

Figure 16 • Data Error Generation

**Note:** Select any six signal checkboxes on the right side panel to view the status of the signals. De-select the selected signals before selecting any new signals if the count is more than six. The SYNCN, ALIGNED, CGS\_ERR, NIT\_ERR, DISP\_ERR, and EPCS\_RX\_VALID signals are enabled during Link Status failure.

9. Click Clear Error to stop generating the error data and observe the Link Status turn to green.

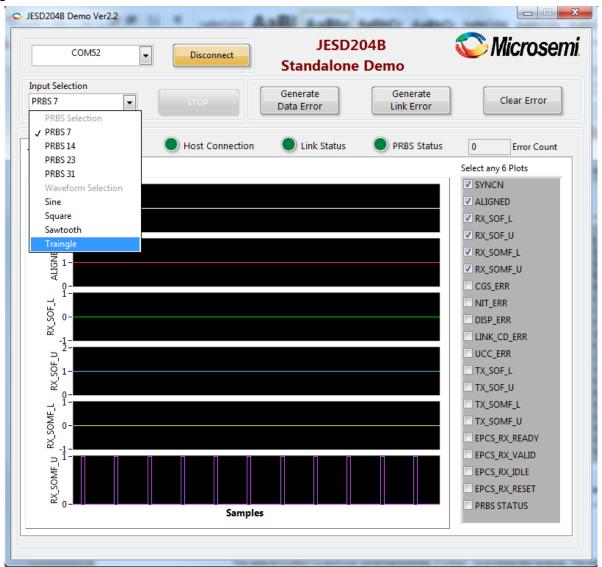

Select **Triangle** as Input selection to change the pattern and view the status link, as shown in the following figure.

Figure 17 • Waveform Pattern Selection

The selected pattern is sent over the serial transmit link. It is then received by the receiver. The status can be monitored using **Status Signals** in the GUI.

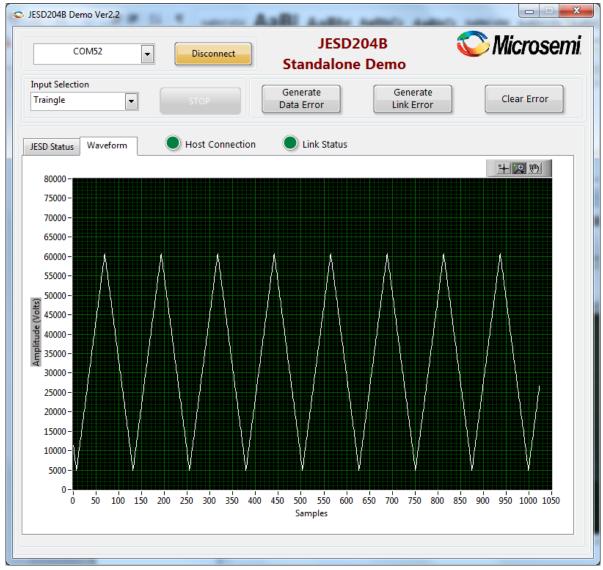

11. Click **Waveform** tab to view the **Triangle** waveform received from the JESD204BRx IP core, as shown in the following figure.

Figure 18 • Waveform Tab

12. Click Stop.

# 3 Appendix: Programming the Device Using FlashPro Express

This section describes how to program the SmartFusion2 device with the programming job file using FlashPro Express.

To program the device, perform the following steps:

1. Ensure that the jumper settings on the board are the same as those listed in Table 2, page 13.

Note: The power supply switch must be switched off while making the jumper connections.

- 2. Connect the power supply cable to the J6 connector on the board.

- 3. Power **ON** the power supply switch **SW7**.

- 4. On the host PC, launch the FlashPro Express software.

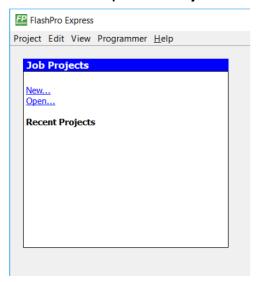

- Click New or select New Job Project from FlashPro Express Job from Project menu to create a new job project, as shown in the following figure.

Figure 19 • FlashPro Express Job Project

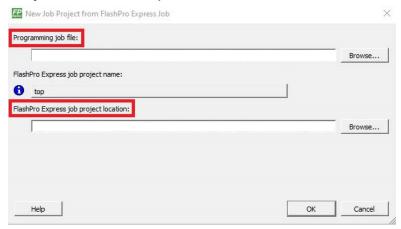

6. Enter the following in the New Job Project from FlashPro Express Job dialog box:

or

- **Programming job file:** Click **Browse**, and navigate to the location where the .job file is located and select the file. The default location is:

- <download folder>\m2s dq0611 df\Programming Job

- FlashPro Express job project name: Click Browse and navigate to the location where you want to save the project.

Figure 20 • New Job Project from FlashPro Express Job

- 7. Click **OK**. The required programming file is selected and ready to be programmed in the device.

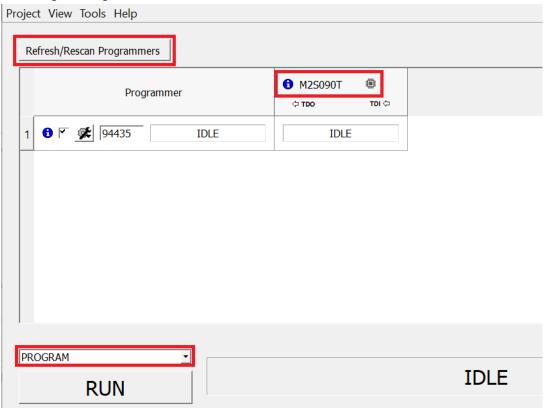

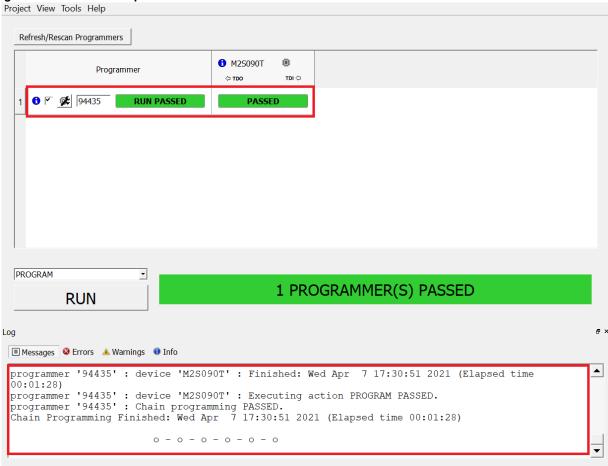

- 8. The FlashPro Express window appears as shown in the following figure. Confirm that a programmer number appears in the Programmer field. If it does not, confirm the board connections and click **Refresh/Rescan** Programmers.

Figure 21 • Programming the Device

9. Click **RUN**. When the device is programmed successfully, a **RUN PASSED** status is displayed as shown in the following figure.

Figure 22 • FlashPro Express—RUN PASSED

10. Close FlashPro Express or in the Project tab, click Exit.