# SmartFusion 2 and IGLOO 2 FPGA High-Speed DDR Interfaces User Guide

## Introduction (Ask a Question)

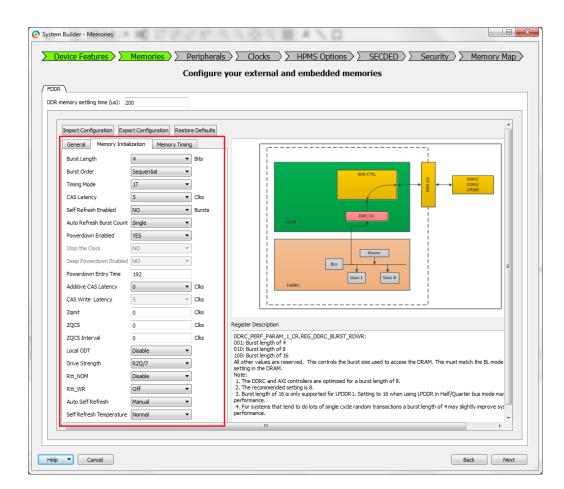

This user guide describes the high-speed memory interfaces in SmartFusion<sup>®</sup> 2 System-on-Chip (SoC) Field Programmable Gate Array (FPGA) and IGLOO<sup>®</sup> 2 FPGA devices. The high-speed interfaces Microcontroller/ Memory Subsystem Double-Data Rate (MDDR) subsystem and fabric DDR (FDDR) subsystem provide access to DDR memories for high-speed data transfers. The DDR subsystem's functionality, configurations, and their use models are discussed in this user guide.

This user guide contains the following chapters:

- 1. MDDR Subsystem

- 2. Fabric DDR Subsystem

- 3. DDR Bridge

- 4. Soft Memory Controller Fabric Interface Controller

## Additional Documentation (Ask a Question)

The following table describes additional documentation available for the SmartFusion 2 and IGLOO 2 devices. For more information, see the SmartFusion 2 Documentation Page and IGLOO 2 Documentation Page online.

| Document                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SmartFusion 2 System-on-Chip FPGAs Product Brief and IGLOO 2<br>FPGA Product Brief |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IGLOO 2 and SmartFusion 2 Datasheet                                                | This datasheet contains SmartFusion 2 and IGLOO 2 DC and switching characteristics.                                                                                                                                                                                                                                                                                                                                                               |

| IGLOO 2 Pin Descriptions Datasheet                                                 | This document contains IGLOO 2 pin descriptions, package outline drawings, and links to pin tables in Excel format.                                                                                                                                                                                                                                                                                                                               |

| SmartFusion 2 Pin Descriptions Datasheet                                           | This document contains SmartFusion 2 pin descriptions, package outline drawings, and links to pin tables in Excel format.                                                                                                                                                                                                                                                                                                                         |

| IGLOO 2 FPGA and SmartFusion 2 SoC FPGA Fabric User Guide                          | SmartFusion 2 and IGLOO 2 FPGAs integrate fourth generation flash-based FPGA fabric. The FPGA fabric is comprised of Logic Elements which consist of a 4 input Look Up Table (LUT), includes embedded memories and Mathblocks for DSP processing capabilities. This document describes the SmartFusion 2 and IGLOO 2SmartFusion 2 and IGLOO 2 FPGA fabric architecture, embedded memories, Mathblocks, fabric routing, and I/Os.                  |

| SmartFusion 2 Microcontroller Subsystem                                            | SmartFusion 2 devices integrate a hard microcontroller subsystem (MSS).<br>The MSS consists of a Arm <sup>®</sup> Cortex <sup>®</sup> -M3 processor with Embedded Trace<br>Macrocell (ETM), instruction cache, embedded memories, DMA engines,<br>communication peripherals, timers, Real-Time Counter (RTC), general<br>purpose I/Os, and FPGA fabric interfaces. This document describes the<br>SmartFusion 2 MSS and its internal peripherals. |

| IGLOO 2 High Performance Memory Subsystem User Guide                               | IGLOO 2 devices integrate a hard High Performance Memory Subsystem<br>(HPMS) consists of embedded memories, DMA engines, and FPGA fabric<br>interfaces. This document describes the IGLOO 2 HPMS and its internal<br>peripherals.                                                                                                                                                                                                                 |

#### Table 1. Additional Documents

| continued                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Document                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| IGLOO 2 and SmartFusion 2 High Speed Serial Interfaces User<br>Guide  | SmartFusion 2 and IGLOO 2 devices integrate hard high-speed serial interfaces (PCIe <sup>®</sup> , XAUI/XGXS, SerDes). This document describes the SmartFusion 2 and IGLOO 2 high-speed serial interfaces.                                                                                                                                                                                                                                                                                                                                                                                                     |

| SmartFusion 2 and IGLOO 2 Clocking Resources User Guide               | SmartFusion 2 and IGLOO 2 clocking resources include on-chip oscillators,<br>FPGA fabric global network, and Clock Conditioning Circuitry (CCCs) with<br>dedicated Phase-Locked Loops (PLLs). These clocking resources provide<br>flexible clocking schemes to the on-chip hard IP blocks—HPMS, fabric<br>DDR (FDDR) subsystem, and high-speed serial interfaces (PCIe, XAUI/XGXS,<br>SerDes)—and logic implemented in the FPGA fabric.                                                                                                                                                                        |

| SmartFusion 2 and IGLOO 2 Low Power Design User Guide                 | In addition to low static power consumption during normal operation, the<br>SmartFusion 2 and IGLOO 2 devices support an ultra-low-power Static mode<br>(Flash*Freeze mode) with power consumption less than 1 mW. Flash*Freeze<br>mode retains all the SRAM and register data which enables fast recovery<br>to Active mode. This document describes the SmartFusion 2 and IGLOO 2<br>Flash*Freeze mode entry and exit mechanisms.                                                                                                                                                                            |

| SmartFusion 2 and IGLOO 2 FPGA Security and Reliability User<br>Guide | The SmartFusion 2 and IGLOO 2 devices incorporate essentially all the security features that made third generation Microchip SoC devices the gold standard for security in the PLD industry. Also included are unique design and data security features and use models new to the PLD industry. SmartFusion 2 and IGLOO 2 Flash-based FPGA fabric has zero FIT configuration rate due to its Single Event Upset (SEU) immunity, which is critical in reliability applications. This document describes the SmartFusion 2 and IGLOO 2 security features and Error Detection and Correction (EDAC) capabilities. |

| SmartFusion 2 SoC and IGLOO 2 FPGA System Controller User<br>Guide    | The system controller manages programming of the SmartFusion 2 and IGLOO 2 devices and handles system service requests. The subsystems, interfaces, and system services in the system controller are discussed in this user guide.                                                                                                                                                                                                                                                                                                                                                                             |

| SmartFusion 2 SoC and IGLOO 2 FPGA System Controller User<br>Guide    | Describes different programming modes supported in the SmartFusion 2<br>and IGLOO 2 devices. High level schematics of these programming methods<br>are also provided as a reference. Important board-level considerations are<br>discussed.                                                                                                                                                                                                                                                                                                                                                                    |

| Libero <sup>®</sup> System-on-Chip (SoC) User Guide                   | Libero <sup>®</sup> SoC is the most comprehensive and powerful FPGA design<br>and development software available, providing start-to-finish design flow<br>guidance and support for novice and experienced users alike. Libero SoC<br>combines Microchip SoC Products Group tools with such EDA powerhouses<br>as Synplify and ModelSim <sup>®</sup> . This user guide discusses the usage of the<br>software and design flow.                                                                                                                                                                                 |

## **Table of Contents**

| Inti | roducti                | on                                                       | 1    |  |  |

|------|------------------------|----------------------------------------------------------|------|--|--|

|      | Addit                  | ional Documentation                                      | 1    |  |  |

| 1.   | мор                    | R Subsystem                                              | 5    |  |  |

|      | 1.1.                   | Features                                                 |      |  |  |

|      | 1.1.                   | Memory Configurations                                    |      |  |  |

|      | 1.3.                   | Performance                                              |      |  |  |

|      | 1.4.                   | I/O Utilization                                          |      |  |  |

|      | 1.5.                   | Functional Description                                   |      |  |  |

|      | 1.6.                   | How to Use MDDR in IGLOO 2 Device                        |      |  |  |

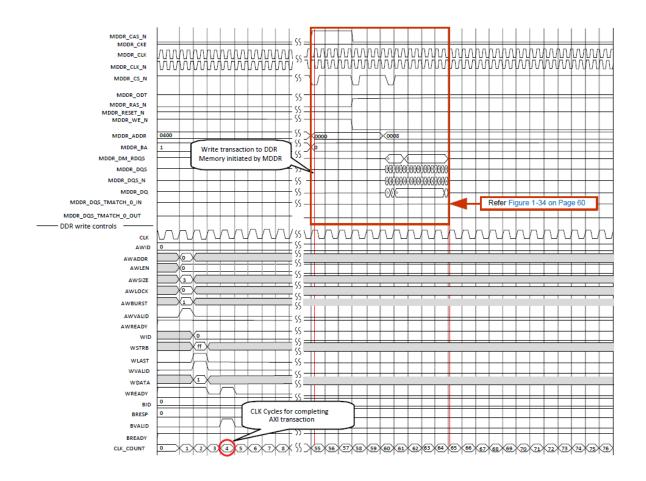

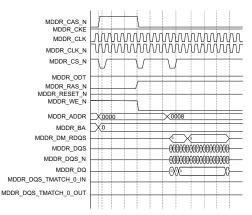

|      | 1.7.                   | Timing Diagrams                                          |      |  |  |

|      | 1.8.                   | Timing Optimization Technique for AXI                    | 55   |  |  |

|      | 1.9.                   | DDR Memory Device Examples                               | 57   |  |  |

|      | 1.10.                  | Board Design Considerations                              | 60   |  |  |

|      | 1.11.                  | MDDR Configuration Registers                             | 60   |  |  |

|      | 1.12.                  | How to Use the MDDR in SmartFusion 2                     | 136  |  |  |

| 2.   | Fabri                  | DDR Subsystem                                            | 159  |  |  |

|      | 2.1.                   | Features                                                 |      |  |  |

|      | 2.2.                   | Memory Configurations                                    |      |  |  |

|      | 2.3.                   | Performance                                              |      |  |  |

|      | 2.4.                   | I/O Utilization                                          |      |  |  |

|      | 2.5.                   | Functional Description                                   |      |  |  |

|      | 2.6.                   | Initialization                                           | 169  |  |  |

|      | 2.7.                   | How to Use FDDR in IGLOO 2 Devices                       | 183  |  |  |

|      | 2.8.                   | DDR Memory Device Examples                               | .200 |  |  |

|      | 2.9.                   | FDDR Configuration Registers                             | .202 |  |  |

|      | 2.10.                  | Appendix A: How to Use the FDDR in SmartFusion 2 Devices | 210  |  |  |

|      | 2.11.                  | Appendix B: Register Lock Bits Configuration             | 232  |  |  |

| 3.   | DDR                    | Bridge                                                   | .236 |  |  |

|      | 3.1.                   | Functional Description                                   | 237  |  |  |

|      | 3.2.                   | How to Use DDR Bridge in IGLOO 2 Device                  | .241 |  |  |

|      | 3.3.                   | SYSREG Control Registers                                 | 245  |  |  |

|      | 3.4.                   | DDR Bridge Control Registers in MDDR and FDDR            | .246 |  |  |

|      | 3.5.                   | How to Use DDR Bridge in SmartFusion 2 Device            | 246  |  |  |

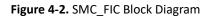

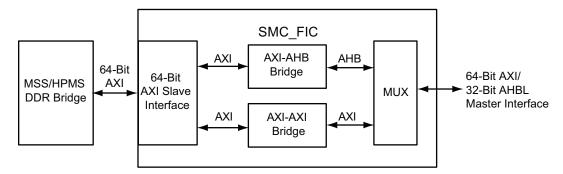

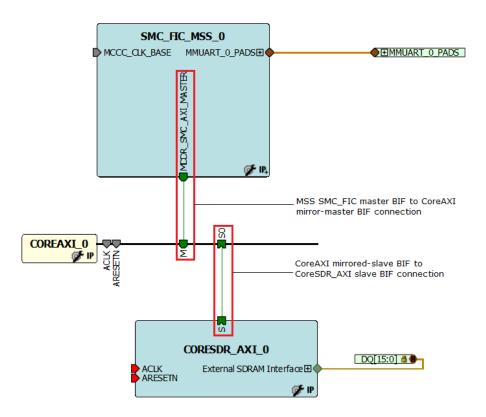

| 4.   | Soft N                 | Aemory Controller Fabric Interface Controller            | 250  |  |  |

|      | 4.1.                   | Functional Description                                   | 250  |  |  |

|      | 4.2.                   | How to Use SMC_FIC in IGLOO2 Device                      |      |  |  |

|      | 4.3.                   | SYSREG Control Register for SMC_FIC                      |      |  |  |

|      | 4.4.                   | How to Use SMC_FIC in SmartFusion 2 Devices              |      |  |  |

| 5.   | Revis                  | on History                                               | .262 |  |  |

| Mic  | Microchip FPGA Support |                                                          |      |  |  |

|      |                        |                                                          |      |  |  |

| Mic  | rochip                 | Information                                              | 264  |  |  |

| The Microchip Website                     | 264 |

|-------------------------------------------|-----|

| Product Change Notification Service       | 264 |

| Customer Support                          | 264 |

| Microchip Devices Code Protection Feature | 264 |

| Legal Notice                              | 265 |

| Trademarks                                | 265 |

| Quality Management System                 | 266 |

| Worldwide Sales and Service               | 267 |

## 1. MDDR Subsystem (Ask a Question)

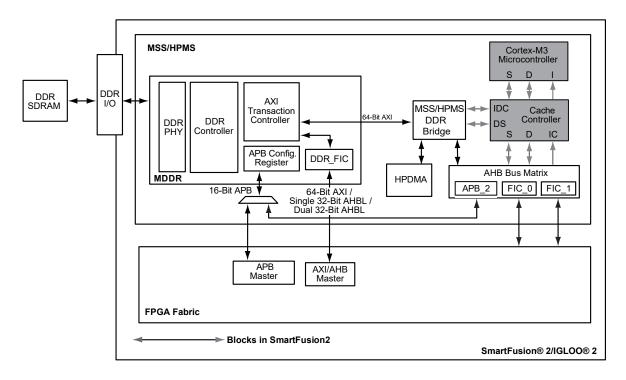

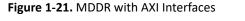

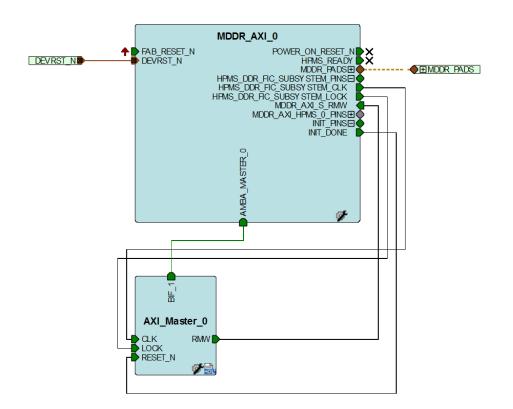

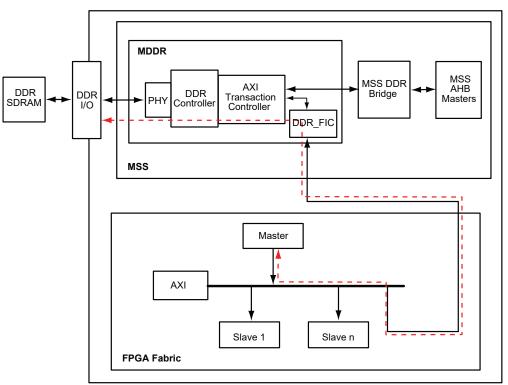

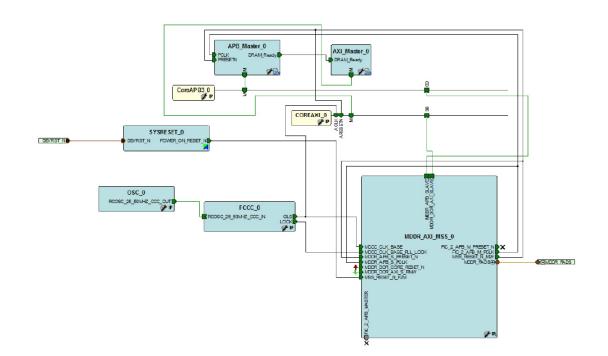

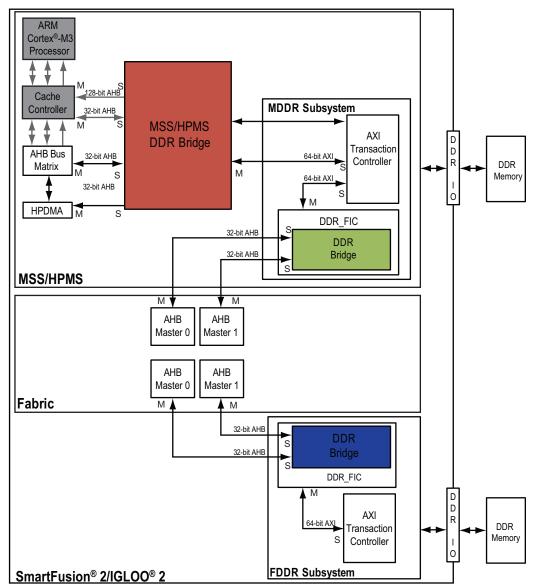

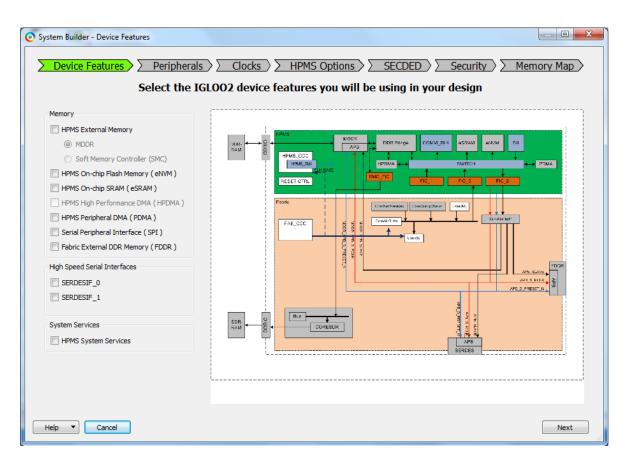

The MDDR is a hardened ASIC block for interfacing the DDR2, DDR3, and LPDDR1 memories. The MDDR subsystem is used to access DDR memories for high-speed data transfers and code execution, and includes a DDR memory controller, DDR PHY, and arbitration logic to support multiple masters. DDR memory connected to the MDDR subsystem can be accessed by the MSS/ HPMS masters and master logic implemented in the FPGA fabric (FPGA fabric master).

The MSS/HPMS masters communicate with the MDDR subsystem through an MSS/HPMS DDR bridge that provides an efficient access path. FPGA fabric masters communicate with the MDDR subsystem through AXI or AHB interfaces.

### 1.1 Features (Ask a Question)

The features of the MDDR subsystem are:

- Integrated on-chip DDR memory controller and PHY

- Capable of supporting LPDDR1, DDR2, and DDR3 memory devices

- Up to 667 Mbps (333.33 MHz DDR) performance

- Supports memory densities upto 2 GB

- Supports 8/16/32-bit DDR Standard Dynamic Random Access Memory (SDRAM) data bus width modes

- Supports a maximum of 8 memory banks

- Supports single rank memory

- Single Error Correction and Double Error Detection (SECDED) enable/disable feature

- Supports DRAM burst lengths of 4, 8, or 16, depending on the bus-width mode and DDR type configuration

- Support for sequential and interleaved burst ordering

- Programs internal control for ZQ short calibration cycles for DDR3 configurations

- Supports dynamic scheduling to optimize bandwidth and latency

- Supports self refresh entry and exit on command

- Supports deep power-down entry and exit on command

- Flexible address mapper logic to allow application specific mapping of row, column, bank, and rank bits

- Configurable support for 1T or 2T timing on the DDR SDRAM control signals

- Supports autonomous DRAM power-down entry and exit caused by lack of transaction arrival for programmable time

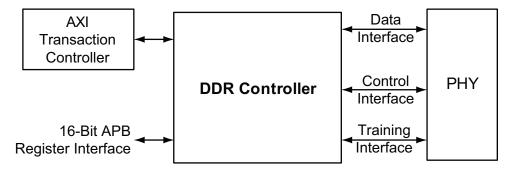

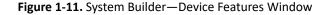

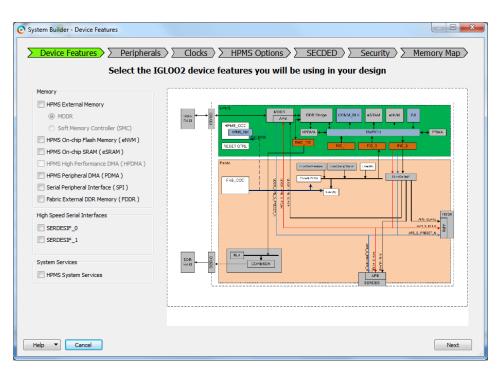

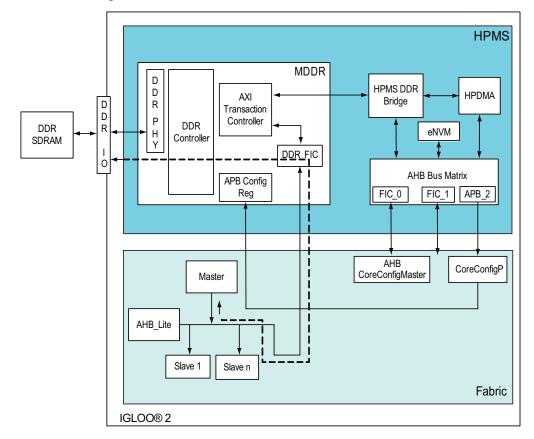

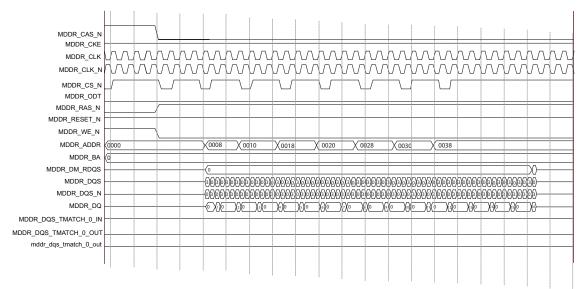

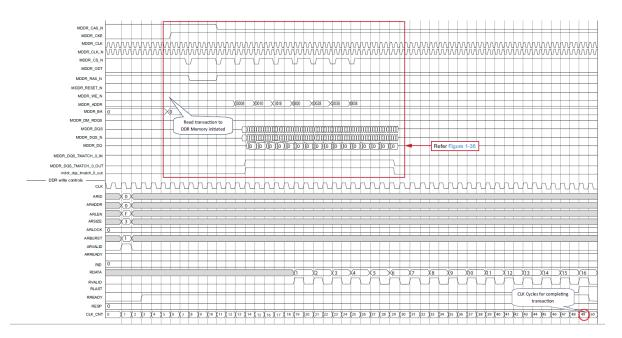

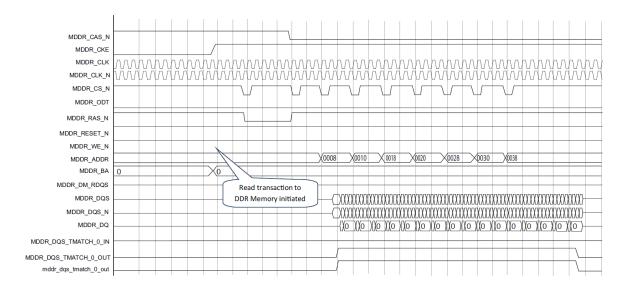

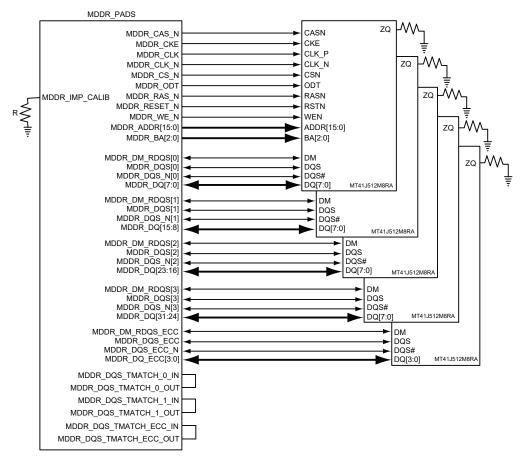

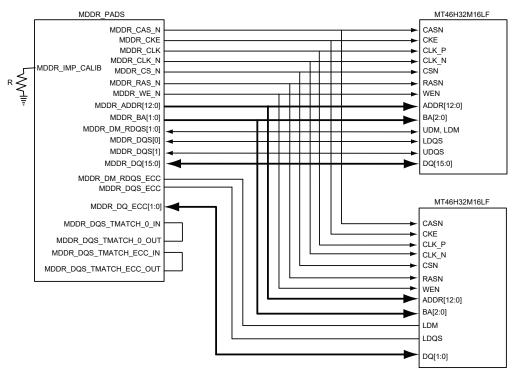

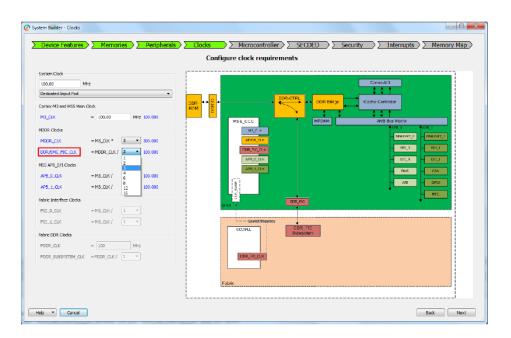

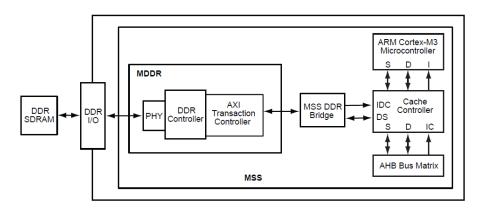

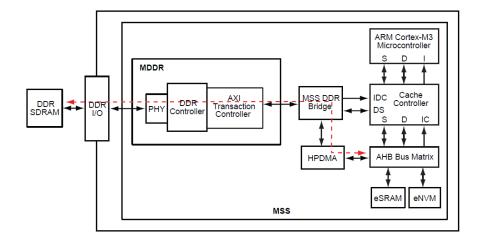

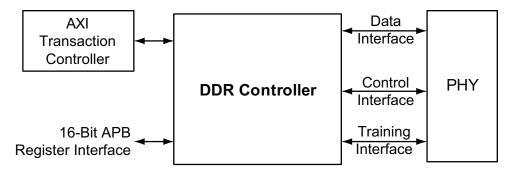

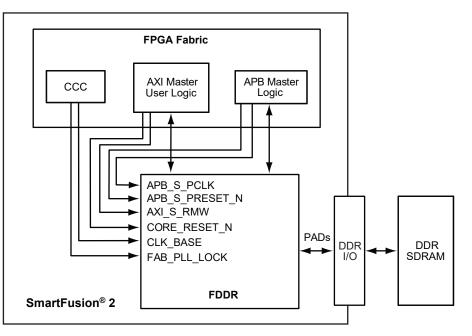

The following illustration shows the system level block diagram of the MDDR subsystem.

Figure 1-1. System Level MDDR Block Diagram

The MDDR subsystem accepts data transfer requests from AXI or AHB interfaces. Any read/write transactions to the DDR memories can occur from the following four paths:

- High performance DMA (HPDMA) controller can access DDR memories through the MSS/HPMS DDR bridge for high speed data transactions.

- Other MSS/HPMS masters (for example, FIC\_0, FIC\_1, and PDMA) can access DDR memories through the MSS/HPMS DDR bridge.

- AXI or AHBL masters in the FPGA fabric can access DDR memories through DDR\_FIC interface.

#### Important:

- The Cortex<sup>®</sup>-M3 processor can access DDR memories through the MSS DDR bridge for data and code execution in SmartFusion 2.

- The maximum DDR3 data rate supported by MDDR is 333 MHz/667 Mbps. Therefore, Write Leveling is not mandatory and the interface works if the board layout includes length matching and follows

AN4153: Board and Layout Design Guidelines for SmartFusion2 SoC and IGLOO2

FPGAs. For Read Leveling, Libero SOC auto-generates predefined static delay ratios for MDDR initialization. These delay values are sufficient if the board layout follows the SmartFusion 2/IGLOO 2 board-level guidelines.

## 1.2 Memory Configurations (Ask a Question)

The SmartFusion 2 and IGLOO 2 FPGA MDDR subsystem supports a wide range of common memory types, configurations, and densities, as shown in the following table. If SECDED mode is enabled in the MDDR controller, the external memory module must be connected to the following:

- Data lines MDDR\_DQ\_ECC[3:0] when data width is x32

- Data lines MDDR\_DQ\_ECC[1:0] when data width is x16

• Data line MDDR\_DQ\_ECC[0] when data width is x8

| Memory<br>Depth | Width | Width<br>(in SECDED<br>Mode) | SmartFusion <sup>®</sup> 2 and IGLOO <sup>®</sup> 2 Devices |                                           |                         |                       |  |  |

|-----------------|-------|------------------------------|-------------------------------------------------------------|-------------------------------------------|-------------------------|-----------------------|--|--|

|                 |       |                              | M2S/M2GL<br>005/010/025/060/090<br>M2S/M2GL150-FCV484       | M2S/M2GL 050<br>(FCS325, VF400,<br>FG484) | M2S/M2GL 050<br>(FG896) | M2S/M2GL150 (FC1152)  |  |  |

| 128M or         | ×32   | ×36                          | —                                                           | —                                         | v                       | <ul> <li>✓</li> </ul> |  |  |

| Less            | ×16   | ×18                          | <b>v</b>                                                    | ~                                         | <b>v</b>                | <b>v</b>              |  |  |

|                 | ×8    | ×9                           | <b>v</b>                                                    | —                                         | —                       | <b>v</b>              |  |  |

| 256M            | ×32   | ×36                          | _                                                           | —                                         | ~                       | <b>v</b>              |  |  |

|                 | ×16   | ×18                          | <b>v</b>                                                    | ~                                         | ~                       | V                     |  |  |

|                 | ×8    | ×9                           | ✓                                                           | _                                         | —                       | V                     |  |  |

| 512M            | ×32   | ×36                          | —                                                           | —                                         | ~                       | <b>v</b>              |  |  |

|                 | ×16   | ×18                          | ✓                                                           | ~                                         | <ul> <li>✓</li> </ul>   | <b>v</b>              |  |  |

|                 | ×8    | ×9                           | <ul> <li>✓</li> </ul>                                       | —                                         | —                       | V                     |  |  |

| 1G              | ×32   | ×36                          | _                                                           | -                                         | ~                       | <b>v</b>              |  |  |

|                 | ×16   | ×18                          | <b>v</b>                                                    | v                                         | v                       | V                     |  |  |

|                 | x8    | ×9                           | ✓                                                           | —                                         | -                       | <b>v</b>              |  |  |

Table 1-1. Supported Memory (DDR2, DDR3, and LPDDR1) Configurations

#### 1.3 Performance (Ask a Question)

The following table shows the maximum data rates supported by MDDR subsystem for supported memory types.

For more Information, refer to the "DDR Memory Interface Characteristics" section in IGLOO2 FPGA and SmartFusion2 SoC FPGA Datasheet.

#### Table 1-2. DDR Speeds

| Memory Type | Maximum Data Rate (Mbps) |

|-------------|--------------------------|

| LPDDR1      | 400 Mbps (200 MHz)       |

| DDR2        | 667 Mbps (333.33 MHz)    |

| DDR3        | 667 Mbps (333.33 MHz)    |

## 1.4 I/O Utilization (Ask a Question)

The following table lists the I/O utilization for the SmartFusion 2 and IGLOO 2 devices corresponding to supported bus widths. The remaining I/Os in Bank 0 are used for general purposes.

| MDDR Bus<br>Width | M2S/<br>M2GL005/010/025/060/090<br>M2S/M2GL150-FCV484 | M2S/M2GL 050<br>(FCS325, VF400,<br>FG484) | M2S/M2GL 050<br>(FG896) | M2S/M2GL 150<br>(FC1152) |

|-------------------|-------------------------------------------------------|-------------------------------------------|-------------------------|--------------------------|

| 36-bit            | —                                                     | —                                         | Bank0 (85 pins)         | Bank2 (85 pins)          |

| 32-bit            | —                                                     | -                                         | Bank0 (76 pins)         | Bank2 (76 pins)          |

| 18-bit            | Bank0 (59 pins)                                       | Bank0 (59 pins)                           | Bank0 (59 pins)         | Bank2 (59 pins)          |

| 16-bit            | Bank0 (53 pins)                                       | Bank0 (53 pins)                           | Bank0 (53 pins)         | Bank2 (53 pins)          |

| 9-bit             | Bank0 (47 pins)                                       | —                                         | —                       | Bank2 (47 pins)          |

| 8-bit             | Bank0 (41 pins)                                       | —                                         | -                       | Bank2 (41 pins)          |

Table 1-3. I/O Utilization for SmartFusion<sup>®</sup> 2 and IGLOO<sup>®</sup> 2 Devices

**Important:** If MDDR is configured for LPDDR, one more I/O also available for every 8-bit as the LPDDR does not have DQS\_N.

For general purpose use of the unused I/Os in the MDDR bank, select one of the I/O standards with the same voltage level as the DDR I/Os.

Self refresh must be disabled if the MDDR banks contain a mix of I/Os used for DDR and for general purpose fabric I/Os. For more information, see 1.5.4.3.5. Power Saving Modes.

#### 1.5 Functional Description (Ask a Question)

This section provides the functional description of the MDDR subsystem.

#### 1.5.1 Architecture Overview (Ask a Question)

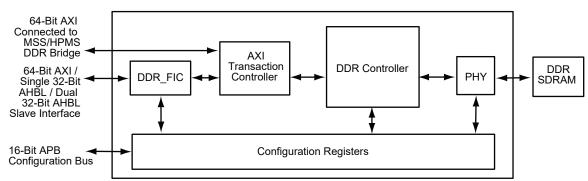

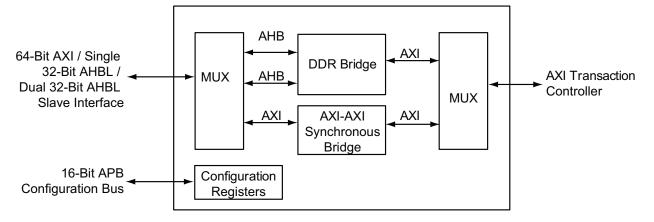

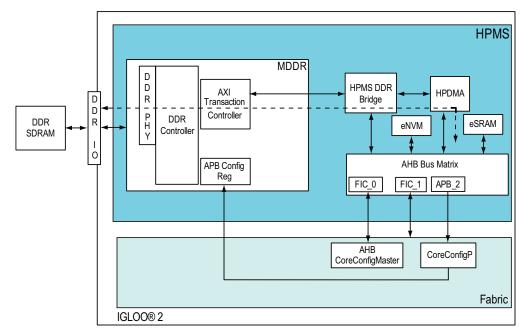

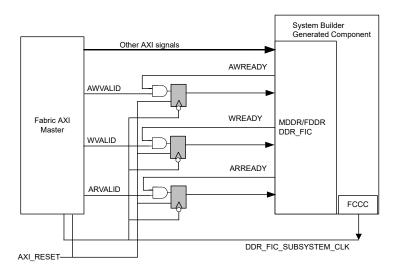

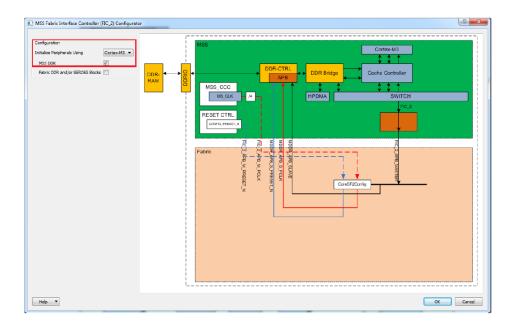

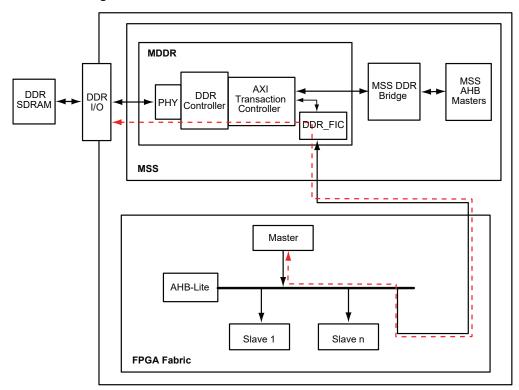

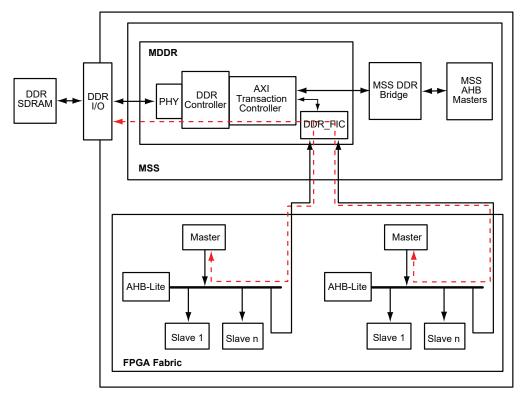

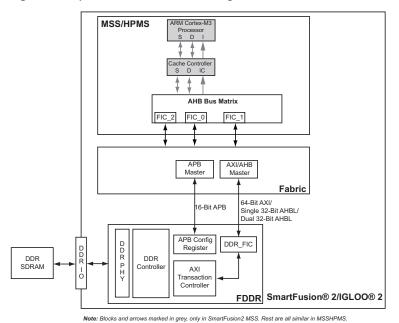

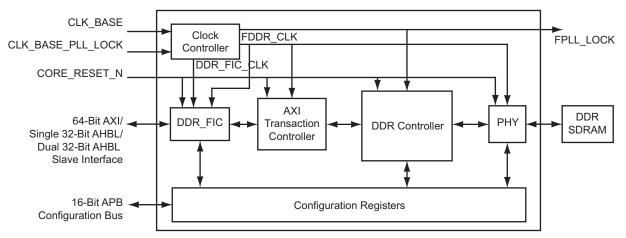

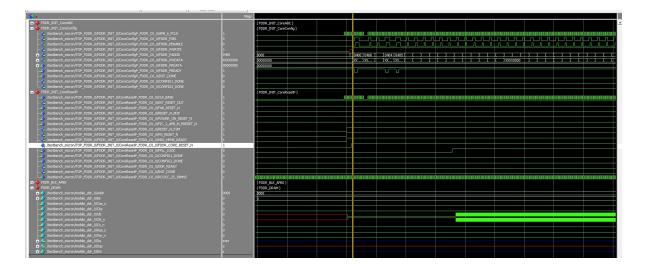

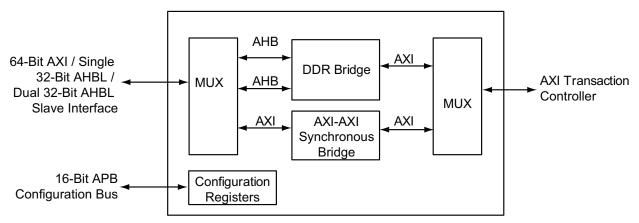

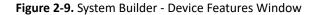

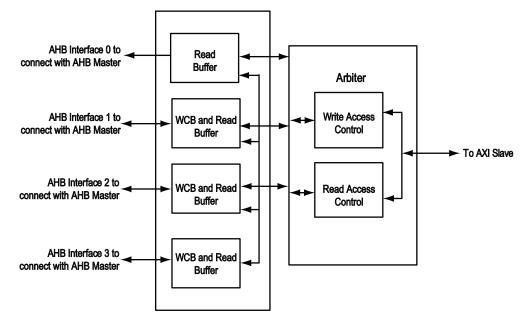

The following illustration shows a functional block diagram of the MDDR subsystem. The main components include the DDR fabric interface controller (DDR\_FIC), AXI transaction handler, DDR memory controller, and DDR PHY.

Figure 1-2. MDDR Subsystem Functional Block Diagram

The DDR\_FIC facilitates communication between the FPGA fabric masters and AXI transaction controller. The DDR\_FIC is configured to provide either one 64-bit AXI slave interface or two independent 32-bit AHB-Lite (AHBL) slave interfaces to the FPGA fabric masters.

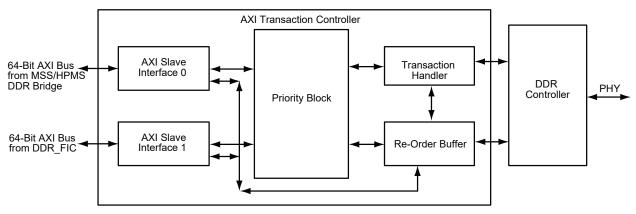

The AXI transaction controller receives read and write requests from AXI masters (MSS/HPMS DDR bridge and DDR\_FIC) and schedules for the DDR controller by translating them into DDR controller commands.

The DDR controller receives the commands from the AXI transaction controller. These commands are queued internally and scheduled for access to the DDR SDRAM while satisfying DDR SDRAM constraints, transaction priorities, and dependencies between the transactions. The DDR controller in turn issues commands to the PHY module, which launches and captures data to and from the DDR SDRAM.

DDR PHY receives commands from the DDR controller and generates DDR memory signals required to access the external DDR memory.

The 16-bit APB configuration bus provides an interface to configure the MDDR subsystem registers. The MDDR subsystem operates on MDDR\_CLK. MSS/HPMS CCC generates the MDDR\_CLK using MPLL. For more details on MSS/HPMS CCC refer UG0449: SmartFusion2 and IGLOO2 Clocking Resources User Guide.

#### 1.5.2 Port List (Ask a Question)

The following table describes the MDDR subsystem interface signals.

#### Table 1-4. MDDR Subsystem Interface Signals

| Signal Name                                                      | Туре   | Polarity | Description                                                                                                                                                                                                                          |

|------------------------------------------------------------------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APB_S_PCLK                                                       | In     | —        | APB clock. This clock drives all the registers of the APB interface.                                                                                                                                                                 |

| APB_S_PRESET_N                                                   | In     | Low      | APB reset signal. This is an active-low signal. This drives<br>the APB interface and is used to generate the soft reset<br>for the DDR controller as well.                                                                           |

| MDDR_DDR_CORE_RESET_N                                            | In     | Low      | Global reset. This resets the DDR_FIC/DDRC/PHY/DDRAXI logic.                                                                                                                                                                         |

| MDDR_DDR_AXI_S_RMW                                               | In     | High     | AXI mode only indicates whether all bytes of a 64-bit lane are valid for all beats of an AXI transfer.                                                                                                                               |

|                                                                  |        |          | • 0: Indicates that all bytes in all beats are valid in the burst and the controller should default to write commands                                                                                                                |

|                                                                  |        |          | <ul> <li>1: Indicates that some bytes are invalid and the<br/>controller should default to RMW commands.<br/>This is classed as an AXI write address channel<br/>sideband signal and is valid with the AWVALID<br/>signal</li> </ul> |

| HPMS_DDR_FIC_SUBSYSTEM_CLK<br>or,<br>MSS_DDR_FIC_SUBSYSTEM_CLK   | Out    | -        | This output clock is derived from the MDDR_CLK and<br>is based on the DDR_FIC divider ratio. This is the clock<br>that should be used for the AXI or AHB slave interfaces<br>to move data in and out of the MDDR.                    |

| HPMS_DDR_FIC_SUBSYSTEM_LOCK<br>or,<br>MSS_DDR_FIC_SUBSYSTEM_LOCK | Out    | —        | This indicates the lock from FCCC which generates<br>HPMS_DDR_FIC_SUBSYSTEM_CLK for IGLOO2 and<br>MSS_DDR_FIC_SUBSYSTEM_LOCK in SmartFusion 2.                                                                                       |

| Bus Interfaces                                                   |        |          |                                                                                                                                                                                                                                      |

| AXI_SLAVE <sup>1</sup>                                           | Bus    | _        | AXI slave interface 1.0 bus                                                                                                                                                                                                          |

| AHB0_SLAVE <sup>2</sup>                                          | Bus    | -        | AHB0 slave interface 3.0 bus                                                                                                                                                                                                         |

| AHB1_SLAVE <sup>3</sup>                                          | Bus    | -        | AHB1 slave interface 3.0 bus                                                                                                                                                                                                         |

| APB_SLAVE                                                        | Bus    | -        | APB slave interface 3.0 bus                                                                                                                                                                                                          |

| DRAM Interface                                                   |        |          |                                                                                                                                                                                                                                      |

| MDDR_CAS_N                                                       | Out    | Low      | DRAM CASN                                                                                                                                                                                                                            |

| MDDR_CKE                                                         | Out    | High     | DRAM CKE                                                                                                                                                                                                                             |

| MDDR_CLK                                                         | Out    | —        | DRAM single-ended clock – for differential pads                                                                                                                                                                                      |

| MDDR_CLK_N                                                       | Out    | —        | DRAM single-ended clock – for differential pads                                                                                                                                                                                      |

| MDDR_CS_N                                                        | Out    | Low      | DRAM CSN                                                                                                                                                                                                                             |

| MDDR_ODT                                                         | Out    | High     | DRAM ODT.                                                                                                                                                                                                                            |

|                                                                  |        |          | 0: Termination OFF                                                                                                                                                                                                                   |

|                                                                  |        |          | 1: Termination ON                                                                                                                                                                                                                    |

| MDDR_RAS_N                                                       | Out    | Low      | DRAM RASN                                                                                                                                                                                                                            |

| MDDR_ RESET_N                                                    | Out    | Low      | DRAM reset for DDR3                                                                                                                                                                                                                  |

| MDDR_WE_N                                                        | Out    | Low      | DRAM WEN                                                                                                                                                                                                                             |

| MDDR_ADDR[15:0]                                                  | Out    | —        | Dram address bits                                                                                                                                                                                                                    |

| MDDR_BA[2:0]                                                     | Out    | —        | Dram bank address                                                                                                                                                                                                                    |

| MDDR_DM_RDQS[3:0]                                                | In/out | —        | DRAM data mask – from bidirectional pads                                                                                                                                                                                             |

| MDDR_DQS[3:0]                                                    | In/out | _        | DRAM single-ended data strobe output – for bidirectional pads                                                                                                                                                                        |

| MDDR_DQS_N[3:0]                                                  | In/out | —        | DRAM single-ended data strobe output – for<br>bidirectional pads                                                                                                                                                                     |

| MDDR_DQ[31:0]                                                    | In/out | —        | DRAM data input/output – for bidirectional pads                                                                                                                                                                                      |

|                                                                  |        |          |                                                                                                                                                                                                                                      |

| continued               |        |          |                                                                                                                         |  |  |  |

|-------------------------|--------|----------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Signal Name             | Туре   | Polarity | Description                                                                                                             |  |  |  |

| MDDR_DQ_ECC[3:0]        | In/out | —        | DRAM data input/output for SECDED                                                                                       |  |  |  |

| MDDR_DM_RDQS_ECC        | In/out | High     | DRAM single-ended data strobe output – for<br>bidirectional pads                                                        |  |  |  |

| MDDR_DQS_ECC            | In/out | High     | DRAM single-ended data strobe output – for<br>bidirectional pads                                                        |  |  |  |

| MDDR_DQS_ECC_N          | In/out | Low      | DRAM data input/output – for bidirectional pads                                                                         |  |  |  |

| MDDR_DQS_TMATCH_0_IN    | In     | High     | DQS enables input for timing match between DQS and system clock. For simulations, tie to MDDR_DQS_TMATCH_0_OUT.         |  |  |  |

| MDDR_DQS_TMATCH_1_IN    | In     | High     | DQS enables input for timing match between DQS and system clock. For simulations, tie to MDDR_DQS_TMATCH_1_OUT.         |  |  |  |

| MDDR_DQS_TMATCH_0_OUT   | Out    | High     | DQS enables output for timing match between DQS and system clock. For simulations, tie to MDDR_DQS_TMATCH_0_IN.         |  |  |  |

| MDDR_DQS_TMATCH_1_OUT   | Out    | High     | DQS enables output for timing match between DQS and system clock. For simulations, tie to MDDR_DQS_TMATCH_1_IN.         |  |  |  |

| MDDR_DQS_TMATCH_ECC_IN  | In     | High     | DQS enables input for timing match between DQS and system clock. For simulations, tie to MDDR_DQS_TMATCH_ECC_OUT.       |  |  |  |

| MDDR_DQS_TMATCH_ECC_OUT | Out    | High     | DQS enables output for timing match between DQS<br>and system clock.<br>For simulations, tie to MDDR_DQS_TMATCH_ECC_IN. |  |  |  |

#### Notes:

- 1. AXI or AHB interface, depending on configuration.

- 2. MDDR\_DQS\_N[3:0] signals are not available for LPDDR.

- 3. TMATCH\_IN and TMATCH\_OUT pins are required to be connected together outside the device. They are used for gate training as part of the read data capture operation. The two pins create an internal DQS Enable signal that is used to calibrate the flight path. DQS needs to be gated to prevent false triggering of the FIFO write clock. This DQS Enable signal is derived from the system clock and physically matches the clock output buffer and DQS input buffer to compensate for I/O buffer uncertainty due to Process-Voltage-Temperature (PVT) changes. Without this connection, the circuit is not operable.

#### 1.5.2.1 AXI Slave Interface (Ask a Question)

The following table describes the MDDR AXI slave interface signals. These signals will be available only if the MDDR interface is configured for AXI mode. For more AXI protocol details, see the AMBA AXI v1.0 protocol specification.

| Signal Name            | Direction | Polarity | Description                                                                                                                                                                      |

|------------------------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDDR_DDR_AXI_S_ARREADY | Output    | High     | <ul> <li>Indicates whether or not the slave<br/>is ready to accept an address and<br/>associated control signals.</li> <li>1: Slave ready</li> <li>0: Slave not ready</li> </ul> |

| MDDR_DDR_AXI_S_AWREADY | Output    | High     | <ul><li>Indicates that the slave is ready to accept<br/>an address and associated control signals.</li><li>1: Slave ready</li><li>0: Slave not ready</li></ul>                   |

#### Table 1-5. AXI Slave Interface Signals

| continued                            |           |          |                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|--------------------------------------|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Signal Name                          | Direction | Polarity | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| MDDR_DDR_AXI_S_BID[3:0]              | Output    | —        | Indicates response ID. The identification tag of the write response.                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| MDDR_DDR_AXI_S_BRESP[1:0]            | Output    | -        | <ul> <li>Indicates write response. This signal indicates the status of the write transaction.</li> <li>00: Normal access okay</li> <li>01: Exclusive access okay</li> <li>10: Slave error</li> <li>11: Decode error</li> </ul>                                                                                                                                                                                                            |  |  |

| MDDR_DDR_AXI_S_BVALID                | Output    | High     | <ul><li>Indicates whether a valid write response<br/>is available.</li><li>1: Write response available</li><li>0: Write response not available</li></ul>                                                                                                                                                                                                                                                                                  |  |  |

| MDDR_DDR_AXI_S_RDATA[63:0]           | Output    | _        | Indicates read data.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| MDDR_DDR_AXI_S_RID[3:0]              | Output    | _        | Read ID tag. This signal is the ID tag of the read data group of signals.                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| MDDR_DDR_AXI_S_RLAST                 | Output    | High     | Indicates the last transfer in a read burst.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| MDDR_DDR_AXI_S_RRESP[1:0]            | Output    | _        | <ul> <li>Indicates read response. This signal<br/>indicates the status of the read transfer.</li> <li>00: Normal access</li> <li>01: Exclusive access</li> <li>10: Slave error</li> <li>11: Decode error</li> </ul>                                                                                                                                                                                                                       |  |  |

| MDDR_DDR_AXI_S_RVALID                | Output    | -        | <ul> <li>Indicates whether the required read data is available and the read transfer can complete.</li> <li>1: Read data available</li> <li>0: Read data not available</li> </ul>                                                                                                                                                                                                                                                         |  |  |

| MDDR_DDR_AXI_S_WREADY                | Output    | High     | <ul><li>Indicates whether the slave can accept<br/>the write data.</li><li>1: Slave ready</li><li>0: Slave not ready</li></ul>                                                                                                                                                                                                                                                                                                            |  |  |

| MDDR_DDR_MDDR_DDR_AXI_S_ARADDR[31:0] | Input     | _        | Indicates initial address of a read burst transaction.<br><b>Note:</b> DDR_FIC AXI interface supports only 64-bit aligned addresses.                                                                                                                                                                                                                                                                                                      |  |  |

| MDDR_DDR_AXI_S_ARBURST[1:0]          | Input     |          | <ul> <li>Indicates burst type. The burst type, coupled with the size information, details how the address for each transfer within the burst is calculated.</li> <li>00: FIXED - Fixed-address burst FIFO type (Not Supported)</li> <li>01: INCR - Incrementing-address burst normal sequential memory</li> <li>10: WRAP - Incrementing-address burst that wraps to a lower address at the wrap boundary</li> <li>11: Reserved</li> </ul> |  |  |

| continued                   |           |          |                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-----------------------------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Signal Name                 | Direction | Polarity | Description                                                                                                                                                                                                                                                                                                           |  |  |  |

| MDDR_DDR_AXI_S_ARID[3:0]    | Input     | -        | Indicates identification tag for the read address group of signals.                                                                                                                                                                                                                                                   |  |  |  |

| MDDR_DDR_AXI_S_ARLEN[3:0]   | Input     |          | Indicates burst length. The burst length<br>gives the exact number of transfers in a<br>burst.<br>• 0000: 1<br>• 0001: 2<br>• 0010: 3<br>• 0011: 4<br>• 0100: 5<br>• 0101: 6<br>• 0110: 7<br>• 0111: 8<br>• 1000: 9<br>• 1001: 10<br>• 1010: 11<br>• 1010: 11<br>• 1010: 13<br>• 1101: 14<br>• 1110: 15<br>• 1111: 16 |  |  |  |

| MDDR_DDR_AXI_S_ARLOCK[1:0]  | Input     | -        | <ul> <li>Indicates lock type. This signal provides<br/>additional information about the atomic<br/>characteristics of the read transfer.</li> <li>00: Normal access</li> <li>01: Exclusive access</li> <li>10: Locked access</li> <li>11: Reserved</li> </ul>                                                         |  |  |  |

| MDDR_DDR_AXI_S_ARSIZE[1:0]  | Input     | _        | <ul> <li>Indicates the maximum number of data bytes to transfer in each data transfer, within a burst.</li> <li>00: 10 : Not Supported</li> <li>11: 8</li> </ul>                                                                                                                                                      |  |  |  |

| MDDR_DDR_AXI_S_ARVALID      | Input     | High     | <ul> <li>Indicates the validity of read address and control information.</li> <li>1: Address and control information valid</li> <li>0: Address and control information not valid</li> </ul>                                                                                                                           |  |  |  |

| MDDR_DDR_AXI_S_AWADDR[31:0] | Input     |          | Indicates write address. The write address<br>bus gives the address of the first transfer<br>in a write burst transaction.<br><b>Note:</b> DDR_FIC AXI interface supports<br>only 64-bit aligned addresses.                                                                                                           |  |  |  |

| continued                   |           |          |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name                 | Direction | Polarity | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MDDR_DDR_AXI_S_AWBURST[1:0] | Input     | _        | <ul> <li>Indicates burst type. The burst type, coupled with the size information, details how the address for each transfer within the burst is calculated.</li> <li>00: FIXED - Fixed-address burst FIFO-type (Not Supported)</li> <li>01: INCR - Incrementing-address burst normal sequential memory</li> <li>10: WRAP - Incrementing-address burst that wraps to a lower address at the wrap boundary</li> <li>11: Reserved</li> </ul> |

| MDDR_DDR_AXI_S_AWID[3:0]    | Input     | —        | Indicates identification tag for the write address group of signals.                                                                                                                                                                                                                                                                                                                                                                      |

| MDDR_DDR_AXI_S_AWLEN[3:0]   | Input     |          | Indicates burst length. The burst length<br>gives the exact number of transfers in<br>a burst. This information determines the<br>number of data transfers associated with<br>the address.<br>• 0000: 1<br>• 0001: 2<br>• 0010: 3<br>• 0011: 4<br>• 0100: 5<br>• 0101: 6<br>• 0110: 7<br>• 0111: 8<br>• 1000: 9<br>• 1001: 10<br>• 1010: 11<br>• 1011: 12<br>• 1100: 13<br>• 1101: 14<br>• 1110: 15<br>• 1111: 16                         |

| MDDR_DDR_AXI_S_AWLOCK[1:0]  | Input     | _        | <ul> <li>Indicates lock type. This signal provides<br/>additional information about the atomic<br/>characteristics of the write transfer.</li> <li>00: Normal access</li> <li>01: Exclusive access</li> <li>10: Locked access</li> <li>11: Reserved</li> </ul>                                                                                                                                                                            |

| MDDR_DDR_AXI_S_AWSIZE[1:0]  | Input     | -        | <ul> <li>Indicates the maximum number of data bytes to transfer in each data transfer, within a burst.</li> <li>00 to 10 : Not Supported</li> <li>11: 8</li> </ul>                                                                                                                                                                                                                                                                        |

| continued                  |           |          |                                                                                                                                                                                                                                         |  |  |  |  |

|----------------------------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Signal Name                | Direction | Polarity | Description                                                                                                                                                                                                                             |  |  |  |  |

| MDDR_DDR_AXI_S_AWVALID     | Input     | High     | <ul> <li>Indicates whether or not valid write<br/>address and control information are<br/>available.</li> <li>1: Address and control information<br/>available</li> <li>0: Address and control information<br/>not available</li> </ul> |  |  |  |  |

| MDDR_DDR_AXI_S_BREADY      | Input     | High     | <ul><li>Indicates whether or not the master can accept the response information.</li><li>1: Master ready</li><li>0: Master not ready</li></ul>                                                                                          |  |  |  |  |

| MDDR_DDR_AXI_S_RREADY      | Input     | High     | <ul> <li>Indicates whether or not the master can accept the read data and response information.</li> <li>1: Master ready</li> <li>0: Master not ready</li> </ul>                                                                        |  |  |  |  |

| MDDR_DDR_AXI_S_WDATA[63:0] | Input     | -        | Indicates write data.                                                                                                                                                                                                                   |  |  |  |  |

| MDDR_DDR_AXI_S_WID[3:0]    | Input     | —        | Indicates response ID. The identification tag of the write response.                                                                                                                                                                    |  |  |  |  |

| MDDR_DDR_AXI_S_WLAST       | Input     | High     | Indicates the last transfer in a write burst.                                                                                                                                                                                           |  |  |  |  |

| MDDR_DDR_AXI_S_WSTRB[7:0]  | Input     | —        | Indicates which byte lanes to update in memory.                                                                                                                                                                                         |  |  |  |  |

| MDDR_DDR_AXI_S_WVALID      | Input     | High     | <ul> <li>Indicates whether or not valid write data<br/>and strobes are available.</li> <li>1: Write data and strobes available</li> <li>0: Write data and strobes not available</li> </ul>                                              |  |  |  |  |

#### 1.5.2.2 AHB Slave Interface (Ask a Question)

The following table describes the MDDR AHB slave interface signals. These signals are available only if MDDR interface is configured for single or dual AHB mode. For more AHB protocol details, see the AMBA AHB v3.0 protocol specification.

| Signal Name                  | Direction | Polarity | Description                                                                                                                       |

|------------------------------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------|

| MDDR_DDR_AHBx_S_HREADYOUT    | Output    | High     | Indicates that a transfer has finished on the bus.<br>The signal is asserted Low to extend a transfer.<br>Input to Fabric master. |

| MDDR_DDR_AHBx_S_HRESP        | Output    | High     | Indicates AHB transfer response to Fabric master.                                                                                 |

| MDDR_DDR_AHBx_S_HRDATA[31:0] | Output    | —        | Indicates AHB read data to Fabric master.                                                                                         |

| MDDR_DDR_AHBx_S_HSEL         | Input     | High     | Indicates AHB slave select signal from Fabric master.                                                                             |

| MDDR_DDR_AHBx_S_HADDR[31:0]  | Input     | _        | Indicates AHB address initiated by Fabric master.                                                                                 |

#### Table 1-6. AHB Slave Interface Signals

| continued                    |           |          |                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|------------------------------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Signal Name                  | Direction | Polarity | Description                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| MDDR_DDR_AHBx_S_HBURST[2:0]  | Input     | _        | <ul> <li>Indicates AHB burst type from Fabric master.</li> <li>000: Single burst</li> <li>001: Incrementing burst of undefined length</li> <li>010: 4-beat wrapping burst</li> <li>011: 4-beat incrementing burst</li> <li>100: 8-beat wrapping burst</li> <li>101: 8-beat incrementing burst</li> <li>110: 16-beat wrapping burst</li> <li>111: 16-beat incrementing burst</li> </ul> |  |  |  |  |

| MDDR_DDR_AHBx_S_HSIZE[1:0]   | Input     | _        | <ul> <li>Indicates AHB transfer size from Fabric master.</li> <li>00: 8 Byte</li> <li>01: 16 Halfword</li> <li>10: 32 Word</li> </ul>                                                                                                                                                                                                                                                  |  |  |  |  |

| MDDR_DDR_AHBx_S_HTRANS[1:0]  | Input     | -        | <ul> <li>Indicates AHB transfer type from Fabric master.</li> <li>00: IDLE</li> <li>01: BUSY</li> <li>10: NONSEQUENTIAL</li> <li>11: SEQUENTIAL</li> </ul>                                                                                                                                                                                                                             |  |  |  |  |

| MDDR_DDR_AHBx_S_HMASTLOCK    | Input     | High     | Indicates AHB master lock signal from Fabric master.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| MDDR_DDR_AHBx_S_HWRITE       | Input     | High     | Indicates AHB write control signal from Fabric master.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| MDDR_DDR_AHBx_S_HREADY       | Input     | High     | Indicates that a transfer has finished on the bus.<br>Fabric master can drive this signal Low to extend<br>a transfer.                                                                                                                                                                                                                                                                 |  |  |  |  |

| MDDR_DDR_AHBx_S_HWDATA[31:0] | Input     | -        | Indicates AHB write data from Fabric master.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

**Important:** AHBx indicates AHB0 or AHB1.

## 1.5.2.3 APB Slave Interface (Ask a Question)

The following table describes the MDDR APB slave interface signals. For more information about APB protocol, see the AMBA APB v3.0 protocol specification.

| Table 1-7 | . MDDR | <b>APB Slave</b> | Interface Signals |

|-----------|--------|------------------|-------------------|

|-----------|--------|------------------|-------------------|

| Signal Name             | Direction | Polarity | Description                                                                                                         |  |  |  |

|-------------------------|-----------|----------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| MDDR_APB_S_PREADY       | Output    | High     | Indicates APB Ready signal to Fabric master.                                                                        |  |  |  |

| MDDR_APB_S_PSLVERR      | Output    | High     | Indicates error condition on an APB transfer to Fabric master.                                                      |  |  |  |

| MDDR_APB_S_PRDATA[15:0] | Output    | —        | Indicates APB read data to Fabric master.                                                                           |  |  |  |

| MDDR_APB_S_PENABLE      | Input     | High     | Indicates APB enable from Fabric master. The enable signal is used to indicate the second cycle of an APB transfer. |  |  |  |

| MDDR_APB_S_PSEL         | Input     | High     | Indicates APB slave select signal from Fabric master                                                                |  |  |  |

| MDDR_APB_S_PWRITE       | Input     | High     | Indicates APB write control signal form Fabric master                                                               |  |  |  |

| MDDR_APB_S_PADDR[10:2]  | Input     | —        | Indicates APB address initiated by Fabric master.                                                                   |  |  |  |

| continued               |           |          |                                              |

|-------------------------|-----------|----------|----------------------------------------------|

| Signal Name             | Direction | Polarity | Description                                  |

| MDDR_APB_S_PWDATA[15:0] | Input     | _        | Indicates APB write data from Fabric master. |

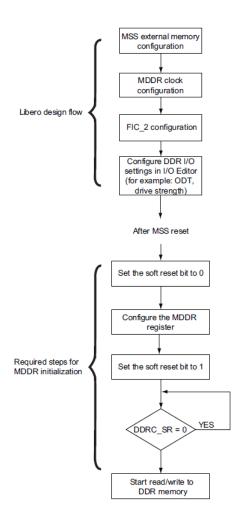

#### 1.5.3 Initialization (Ask a Question)

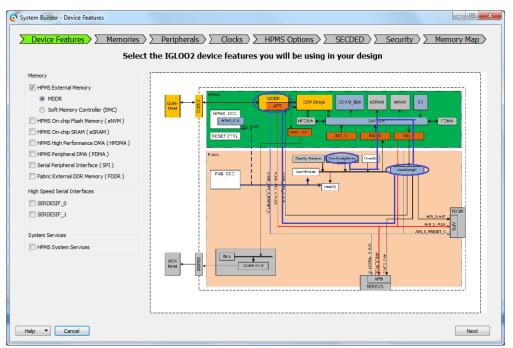

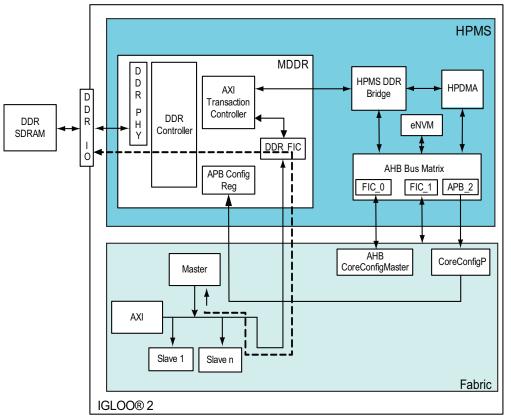

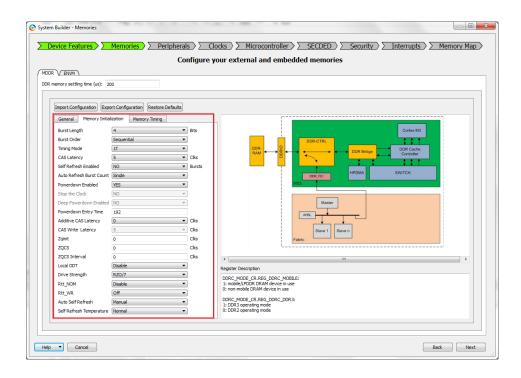

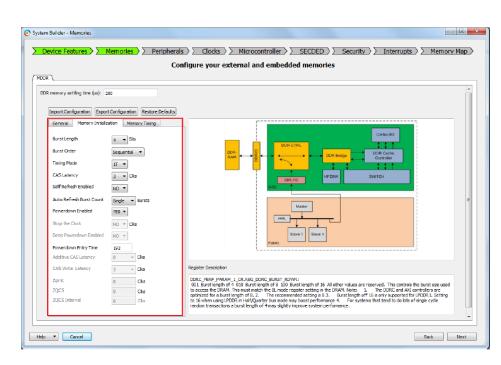

After power-up, the MDDR needs to have all of the configuration registers written to establish the operating modes of the blocks. When using the System Builder design flow through Libero SoC, this is all handled for the user through the use of the System Builder module. All of the configuration register values are selected by the user and stored in a special portion of the embedded Non-Volatile memory (eNVM). Before the MDDR subsystem is active, it goes through an initialization phase and this process starts with a reset sequence. For DDR3 memories, the initialization phase also includes ZQ calibration and DRAM training.

#### 1.5.3.1 Reset Sequence (Ask a Question)

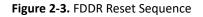

The following illustration shows the reset sequence for the MDDR subsystem from the Poweron Reset stage. The MDDR subsystem comes out of reset after MPLL Lock is asserted by the MSS/HPMS\_CCC. De-assertion of MDDR\_AXI\_RESET\_N signifies the end of the reset sequence. The MDDR reset is generated by asserting the MDDR\_CTLR\_SOFTRESET bit in SOFT\_RESET\_CR to 1. For more information about SOFT\_RESET\_CR, see UG0448: IGLOO2 FPGA High Performance Memory Subsystem. The DDR controller performs external DRAM memory reset and initialization as per the JEDEC specification, including reset, refresh, and mode registers.

#### 1.5.3.2 DDRIO Calibration (Ask a Question)

Each DDRIO has an ODT feature, which is calibrated depending on the DDR I/O standard. DDR I/O calibration occurs after the DDR I/Os are enabled. If the impedance feature is enabled, impedance can be programmed to the desired value in three ways:

- Calibrate the ODT/driver impedance with a calibration block (recommended)

- Calibrate the ODT/driver impedance with fixed calibration codes

- Configure the ODT/driver impedance to the desired value directly

The system register, MDDR\_IO\_CALIB\_CR, can be configured for changing the ODT value to the desired value.

The I/O calibration is always enabled when the DDR subsystem is configured for DDR2 and DDR3 memories.

The I/O calibration is disabled or enabled using the DDR configurator when the DDR subsystem is configured for LPDDR memories.

**Important:** If I/O calibration is enabled, all I/Os in the DDR bank are calibrated even though the DDR controller is not using all I/Os in the bank.

For more information on DDR I/O calibration, see the Configurable ODT and Driver Impedance section of the I/Os chapter in the UG0445: IGLOO2 FPGA and SmartFusion2 SoC FPGA Fabric User Guide.

#### Figure 1-3. Reset Sequence

| PO_RESET_N                                                          |  |

|---------------------------------------------------------------------|--|

| 50 MHz Clock<br>Enable                                              |  |

| Enable I/Os                                                         |  |

| DDRIO<br>Calibration                                                |  |

| SC_HPMS_RESET_N (for IGL002)<br>, SC_MSS_RESET_N (for SmarfFusion2) |  |

| MPLL Lock                                                           |  |

| MDDR AXI RESET N                                                    |  |

#### 1.5.3.3 ZQ Calibration (Ask a Question)

This is applicable for DDR3 only. The ZQ calibration command is used to calibrate DRAM output drivers ( $R_{ON}$ ) and On-Die Termination (ODT) values. The DDR3 SDRAM needs a longer time to calibrate  $R_{ON}$  and ODT at initialization and a relatively smaller time to perform periodic calibrations.

The DDR controller performs ZQ calibration by issuing a ZQ Calibration Long (ZQCL) command and ZQ Calibration Short (ZQCS) command.

ZQCL is used to perform initial calibration during the power-up initialization sequence. This command is allowed for a period of  $t_{ZQinit}$ , as specified by memory vendor. The value of  $t_{ZQinit}$  can be modified through register bits of REG\_DDRC\_T\_ZQ\_LONG\_NOP in Table 1-59.

The ZQCS command is used to perform periodic calibration to account for voltage and temperature variations. A shorter timing window is provided to perform calibration and transfer of values as defined by timing parameter tZQCS. The tZQCS parameter can be modified through register bits of REG\_DDRC\_T\_ZQ\_SHORT\_NOP in Table 1-60.

Other activities are not performed by the controller for the duration of  $t_{ZQinit}$  and tZQCS. All DRAM banks are precharged and tRP is met before ZQCL or ZQCS commands are issued by the DDR controller.

#### 1.5.3.4 DRAM Training (Ask a Question)

High-Speed DDR3 memories typically require the DDR controller to implement Write-Leveling, Read DQS Gate Training, and Read Data Eye Training. However, MDDR only supports a maximum data rate of 333 MHz/667 Mbps, which means the clock period and data window are relatively large compared to high-speed DDR3 memory interfaces. Therefore dynamic write-leveling and read training are not performed. The following sections describe how write-leveling and read training are addressed by the MDDR.

#### 1.5.3.4.1 Write Leveling (Ask a Question)

Dynamic write-leveling is not required for the MDDR controller. The board-layout needs to follow AN4153 SmartFusion2 and IGLOO2 Board Design Guidelines Application Note to keep the skew between DQS and CK within the JEDEC DDR3 tDQSS limit of ±750 ps at each memory device.

333 MHz/667 Mbps is the maximum DDR3 rate MDDR supports. Leveling is not mandatory and the interface will work if the board layout guidelines are followed and length matching is done.

#### 1.5.3.4.2 Read Leveling (Ask a Question)

MDDR does not perform dynamic Read DQS Gate Training and Data Eye Training. Instead, these functions are achieved by using built-in static delay values automatically generated by Libero SoC for the MDDR automatic register initialization.

#### 1.5.3.4.3 Read Gate (Ask a Question)

The DQS gate is aligned by the Libero SoC auto-generated MDDR initialization code containing fixed delay ratios to account for board round-trip time between FPGA and the DDR3 memory. The TMATCH\_OUT and TMATCH\_IN signals are shorted close to the FPGA balls to remove the FPGA output and input delays from the round trip delay time. Therefore, the fixed delay ratios represent only the board delay.

The fixed delay ratios work in combination with board layouts which follow the SmartFusion2/ IGLOO2 Board Design Guidelines (refer AN4153 SmartFusion2 and IGLOO2 Board Design Guidelines Application Note).

#### 1.5.3.4.4 DQS Alignment within Data Eye (Ask a Question)

The incoming read DQS is internally centered within the read DQ data window using a static delay ratio. This static delay is applied by the Libero SoC auto-generated MDDR initialization code. The fixed delay ratios work in combination with board layouts which follow the SmartFusion 2/IGLOO 2 Board Design Guidelines (refer AN4153 SmartFusion2 and IGLOO2 Board Design Guidelines Application Note).

**Important:** The Libero SoC auto-generated delay ratio for read DQS data eye centering is written to the required register.

#### 1.5.3.5 DDR Memory Initialization Time (Ask a Question)

The time to initialize the DDR memory depends on the following factors:

- Power-up and register initialization by system controller. It depends on the Power-on Reset delay configuration in the Libero project (Project > Project Settings > Device settings).

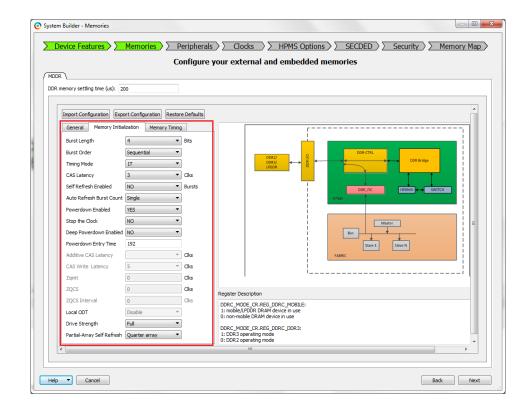

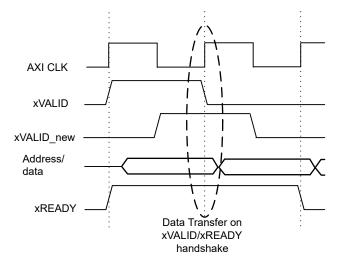

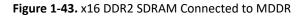

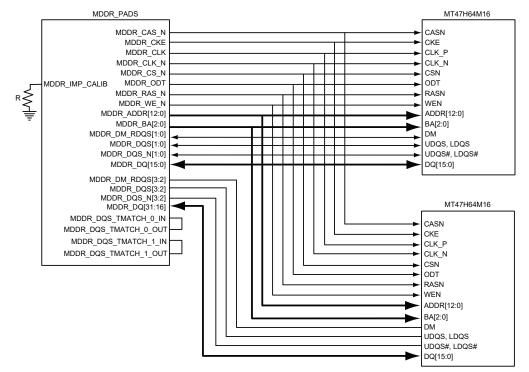

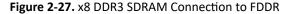

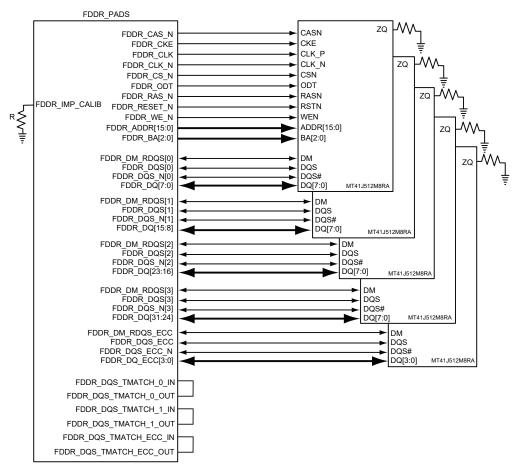

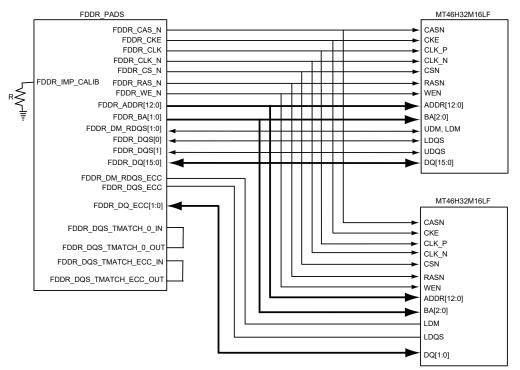

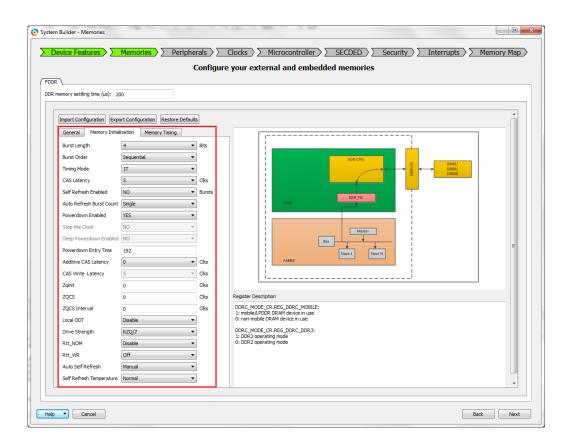

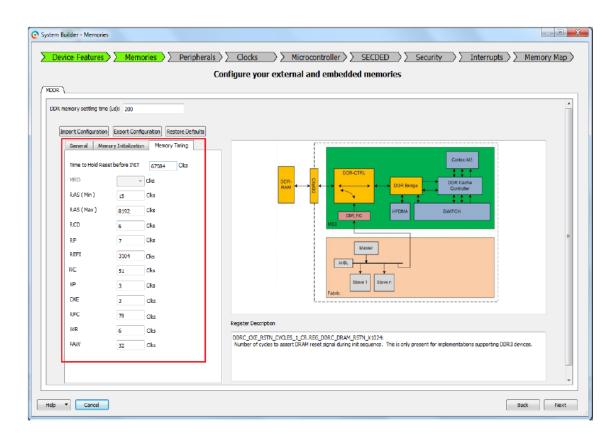

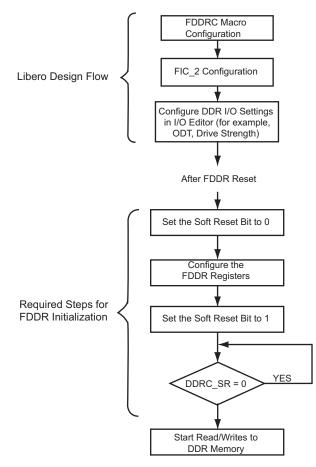

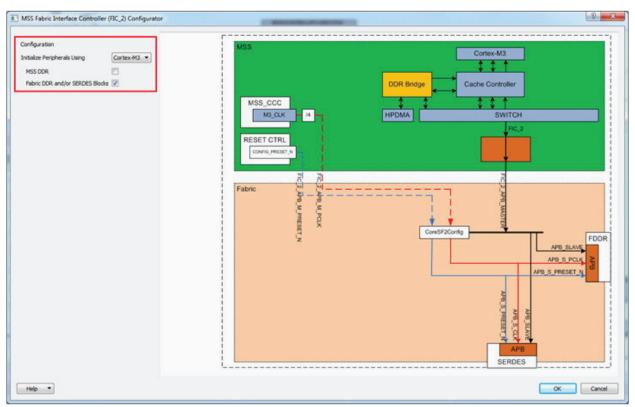

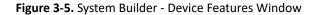

- DDR controller and PHY configuration registers initialization. In SmartFusion 2 devices, the Cortex-M3 initializes these registers. In IGLOO 2 devices, the ConfigMaster in the FPGA fabric initializes these registers.