# UG0443 User Guide SmartFusion2 and IGLOO2 FPGA Security and Best Practices

а 🔨 Міскоснір company

Microsemi Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136

Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2022 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# Contents

| 1 | Revisi | on History                                                                                             |     |

|---|--------|--------------------------------------------------------------------------------------------------------|-----|

|   | 1.2    | Revision 10.0                                                                                          | . 1 |

|   | 1.3    | Revision 9.0                                                                                           | . 1 |

|   | 1.4    | Revision 8.0                                                                                           | . 1 |

|   | 1.5    | Revision 7.0                                                                                           | . 2 |

|   | 1.6    | Revision 6.0                                                                                           | . 2 |

|   | 1.7    | IGLOO2 Document List of Changes (Outdated)                                                             | . 2 |

|   | 1.8    | SmartFusion2 Document List of Changes (Outdated)                                                       | . 2 |

| 2 | Secur  | ity Concerns in FPGAs                                                                                  | 3   |

|   | 2.1    | Design Security                                                                                        |     |

|   | 2.2    | Data Security                                                                                          |     |

|   | 2.3    | Design Security Concerns                                                                               |     |

|   |        | 2.3.1 Cloning                                                                                          |     |

|   |        | 2.3.2 Overbuilding                                                                                     |     |

|   |        | 2.3.3 Reverse Engineering                                                                              |     |

|   | 0.4    | 2.3.4 Counterfeiting                                                                                   |     |

|   | 2.4    | Data Security Concerns                                                                                 |     |

|   | 2.5    | Design Security Impact on Data Security                                                                | . 0 |

| 3 | Secur  | ty Features Overview                                                                                   |     |

|   | 3.1    | Security Architecture                                                                                  |     |

|   | 3.2    | SmartFusion2 Security Architecture                                                                     |     |

|   | 3.3    | IGLOO2 Security Architecture                                                                           |     |

|   | 3.4    | System Controller for Programming and Various Services                                                 |     |

|   | 3.5    | Hardware Cryptographic Accelerators                                                                    |     |

|   | 3.6    | AES-128/256 Hardware Accelerator                                                                       |     |

|   | 3.7    | SHA-256 Hardware Accelerator                                                                           |     |

|   | 3.8    | Non-Deterministic Random Bit Generator (NRBG)                                                          |     |

|   | 3.9    | Elliptic Curve Cryptography Hardware Accelerator (P-384 Curve)                                         |     |

|   | 3.10   | SRAM-PUF Secure Key Storage and Random Seed Generation Engine                                          |     |

|   | 3.11   | Design Security Features                                                                               |     |

|   | 3.12   | Cryptographic Design Security                                                                          |     |

|   |        | 3.12.1       Bitstream Protection and Key Management         3.12.2       FPGA Hardware Access Control |     |

|   |        | 3.12.3 Supply Chain Assurance                                                                          |     |

|   | 3.13   | Anti-Tamper Protection                                                                                 |     |

|   | 3.14   | Data Security Features                                                                                 |     |

|   | 3.15   | Cryptography Research Incorporated (CRI) DPA Patent Portfolio License                                  |     |

|   | 3.16   | Summary of SmartFusion2 and IGLOO2 FPGA Security Features                                              |     |

| 4 | Crypto | ographic Security Features                                                                             | 19  |

|   | 4.1    | SmartFusion2 and IGLOO2 FPGAs Programming Model                                                        |     |

|   | т. 1   | 4.1.1 Security Segment                                                                                 |     |

|   |        | 4.1.2 User Security Segment                                                                            |     |

|   |        | 4.1.3 Fabric Configuration Segment                                                                     | 24  |

|   |        | 4.1.4 FPGA Fabric                                                                                      | 24  |

|   |      | •                         |                                                                    |    |

|---|------|---------------------------|--------------------------------------------------------------------|----|

|   | 4.2  |                           |                                                                    |    |

|   |      |                           | yption Overview                                                    |    |

|   |      |                           | tent                                                               |    |

|   | 4.0  | 0 0                       | Modes                                                              |    |

|   | 4.3  |                           | 22 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                             |    |

|   |      |                           |                                                                    |    |

|   |      |                           | ode & Associated Symmetric Key Databases                           |    |

|   |      |                           | Public Key Modes                                                   |    |

|   |      |                           | ic Key Modes                                                       |    |

|   |      |                           | Modes (KUP and KUPE)                                               |    |

|   | 4.4  | Authorization Code Cor    | nponent and Key Mode                                               | 30 |

|   |      | 4.4.1 Use of the Aut      | norization Code to Prevent Overbuilding                            | 30 |

|   |      |                           | Code Key Mode                                                      |    |

|   |      |                           | Code with ECC Key Modes                                            |    |

|   | 4.5  | Support for Configuration | n Variations                                                       | 32 |

|   | 4.6  | Versioning (Bitstream F   | e-Play Protection)                                                 | 33 |

|   | 4.7  | Key Confirmation/Verifi   | cation Protocols                                                   | 33 |

|   | 4.8  | Passcode Matching Pro     | tocols                                                             | 33 |

|   |      |                           | code Matching Protocol                                             |    |

|   |      | 4.8.2 One-Time-Use        | Encrypted Passcode Matching Protocol                               | 34 |

|   | 4.9  | FlashLock                 |                                                                    | 34 |

|   | 4.10 | Permanent FlashLock (     | OTP Mode)                                                          | 34 |

| 5 | FPGA | Hardware Access           | Controls                                                           | 5  |

|   | 5.1  | FlashLock Passcode Se     | ecurity (256-bit)                                                  | 35 |

|   | 5.2  | FPGA Lock-bits            |                                                                    | 35 |

|   |      | 5.2.1 Security Segm       | ent Lock-bits (Erase/Write/Verify)                                 | 36 |

|   |      |                           | ks (Permanent Locks)                                               |    |

|   |      | -                         | nming Erase Verify Read Lock-bits                                  |    |

|   |      | 5                         | k-bits                                                             | 38 |

|   |      | (Prohibit Plain           | uire One-Time-Use Encrypted Passcodes<br>ext Passcode Matching) 39 |    |

|   |      |                           | Port Lock-bits                                                     |    |

|   |      |                           | activate Debugging Features                                        |    |

|   |      |                           | Services Lock-bits                                                 |    |

|   |      |                           | wall Lock-bits                                                     |    |

|   | 5.3  | •                         | ls                                                                 |    |

|   | 5.4  |                           |                                                                    |    |

|   |      |                           | // User Page-Write Locks                                           |    |

|   |      | 5.4.3 Hardware eNV        | M Factory Page-Write Locks                                         | 12 |

|   | 5.5  |                           |                                                                    |    |

| _ |      | •                         |                                                                    |    |

| 6 |      |                           |                                                                    |    |

|   | 6.1  |                           | nce (C-of-C)                                                       |    |

|   | 6.2  | -                         | on (Versioning)                                                    |    |

|   | 6.3  | 1 0                       | ation or Configuration Data                                        |    |

|   | 6.4  |                           |                                                                    |    |

|   | 0.4  |                           | sign Information System Service                                    |    |

|   |      |                           | Service                                                            |    |

|   |      |                           | Service                                                            |    |

|   |      |                           | ersion Service                                                     |    |

|    |            |                                                                                                     | а 🐼 <b>Місвоснір</b> company |

|----|------------|-----------------------------------------------------------------------------------------------------|------------------------------|

|    |            | 6.4.5 Security Settings                                                                             |                              |

|    |            | 6.4.6 Exporting User SRAM-PUF Activation Codes                                                      |                              |

|    |            | 6.4.7Configuration Read Back in User Mode6.4.8Configuration Read Back in Factory Test Mode          |                              |

|    |            |                                                                                                     |                              |

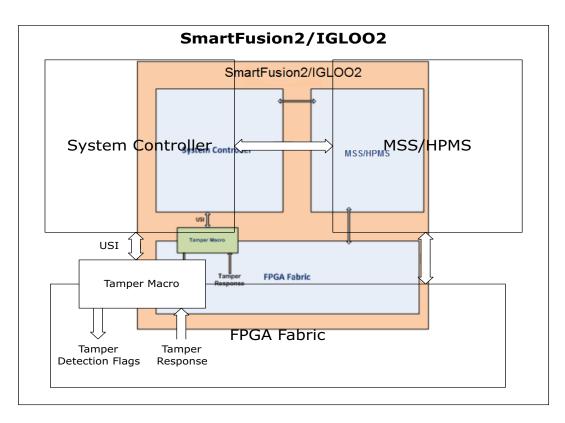

| 7  | Devic      | e Level Anti-Tamper Features                                                                        |                              |

|    | 7.1        | SmartFusion2 and IGLOO2 FPGA Tamper Detection and Tamper Response                                   | se                           |

|    |            | 7.1.1 Tamper Detection Flags                                                                        |                              |

|    |            | 7.1.2 Tamper Response                                                                               |                              |

|    |            | 7.1.3 LOCKDOWN_ALL_N                                                                                |                              |

|    |            | 7.1.4 DISABLEIO_ALL_IOS_N                                                                           |                              |

|    |            | 7.1.5 RESET_N                                                                                       |                              |

|    | 7.2        | Differential Power or Side-Channel Analysis Resistance                                              |                              |

|    | 7.3        | CRI Pass-Through DPA Patent License                                                                 |                              |

|    | 7.3<br>7.4 | Fabric Configuration and eNVM Integrity Tests                                                       |                              |

|    | 7.4        | 7.4.1 Legacy Verification Method – Resubmitting Bitstream                                           | 68                           |

|    |            | 7.4.2 Digest-Based Verification Method                                                              |                              |

|    |            | 7.4.3 Automatic Integrity Check (Power-up Digest Check)                                             |                              |

|    |            | 7.4.4 Exporting Digests (Externally)                                                                |                              |

|    |            | 7.4.5 On-Demand Integrity Check                                                                     |                              |

| 8  | Data       | Socurity Through System Services                                                                    | 70                           |

| 0  |            | Security Through System Services                                                                    |                              |

|    | 8.1        | SmartFusion2 and IGLOO2 System Services                                                             |                              |

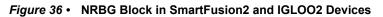

|    | 8.2        | Non-Deterministic Random Bit Generator Service                                                      |                              |

|    |            | 8.2.1         SmartFusion2 and IGLOO2 NRBG Implementation           8.2.2         Self Test Service |                              |

|    |            | 8.2.3 Instantiate Service                                                                           |                              |

|    |            | 8.2.4 Generate Service                                                                              |                              |

|    |            | 8.2.5 Reseed Service                                                                                |                              |

|    |            | 8.2.6 Uninstantiate Service                                                                         |                              |

|    |            | 8.2.7 DRBG Reset Service                                                                            |                              |

|    | 8.3        | AES-128/256 Service (ECB, OFB, CTR, CBC modes)                                                      |                              |

|    | 8.4        | SHA-256 Service                                                                                     |                              |

|    | 8.5        | HMAC-SHA-256 Service                                                                                |                              |

|    | 8.6        | Key Tree System Service                                                                             |                              |

|    | 8.7        | PUF Emulation (Pseudo-PUF) Service                                                                  |                              |

|    | 8.8        | SRAM-PUF Services                                                                                   |                              |

|    |            | 8.8.1 Create User AC or Delete User AC Service                                                      |                              |

|    |            | 8.8.2       Create Delete Export Import User Key Code         8.8.3       Fetch a User PUF Key      |                              |

|    |            | 8.8.4 Fetch a PUF ECC Public Key                                                                    |                              |

|    |            | 8.8.5 Get a PUF Seed                                                                                |                              |

|    | 8.9        | Elliptic Curve Cryptography (ECC) Services                                                          |                              |

|    |            | 8.9.1 ECC Point Multiplication Service                                                              |                              |

|    | 8.10       | Elliptic Curve Cryptography (ECC) Point-Addition Service                                            |                              |

|    | 8.11       | Summary of Expected DPA-Resistance of Cryptographic Services                                        |                              |

| 9  | Using      | System Services Driver                                                                              |                              |

| 10 | Rever      | se Engineering Protection                                                                           | 105                          |

| 10 |            |                                                                                                     |                              |

|    | 10.1       | Configuration Port Security                                                                         |                              |

|    | 10.2       | User JTAG (UJTAG) Security Considerations                                                           |                              |

|    | 10.3       | Programming Port Monitor                                                                            |                              |

|    | 10.4       | Intrusion Detection and Protection                                                                  |                              |

Dicrosemi.

|    | 10.5    | Side Char | nnel Analysis (SCA), Passive & Active, Non- and Semi-Invasive | 128 |

|----|---------|-----------|---------------------------------------------------------------|-----|

| 11 | Interna | al Secur  | ity Features                                                  | 30  |

|    | 11.1    | Single Ev | ent Upset Robustness                                          | 130 |

|    |         | 11.1.1 F  | FPGA Fabric Configuration Memory                              | 130 |

|    |         | 11.1.2 \$ | Security Non-Volatile Memory (NVM)                            | 131 |

|    |         |           | Embedded NVM Array                                            |     |

|    |         |           | MSS embedded SRAM (eSRAM)                                     |     |

|    |         |           | Niscellaneous SRAM Blocks Throughout the MSS                  |     |

|    |         |           | DDR Memory Controllers                                        |     |

|    |         |           | FPGA Fabric SRAM Blocks                                       |     |

|    |         |           | System Controller SRAM Buffers                                |     |

|    |         |           | -<br>PGA Fabric User Flip-Flops                               |     |

|    | 11.2    |           | ental Monitoring                                              |     |

|    | 11.3    |           | configuration Security                                        |     |

|    |         |           |                                                               |     |

|    | 11.4    |           | and Debug Modes                                               |     |

|    |         |           | FPGA Fabric Real-Time Probes and Probe Read/Write Features    |     |

|    |         |           | System IP Interface (SII) Bus Test Modes                      |     |

|    |         |           | Cortex - M3 Debugging Modes                                   |     |

|    |         |           | MSS Debug Features                                            |     |

|    |         |           | Activating and Deactivating Debugging Features                |     |

|    | 11.5    |           | eze Service                                                   |     |

|    | 11.6    | System C  | ontroller Suspend Mode                                        | 136 |

| 12 | Securi  | ty Gloss  | sary                                                          | 37  |

| 12 |         |           |                                                               |     |

|    | 12.1    |           | · · · · · · · · · · · · · · · · · · ·                         |     |

|    |         |           | Advanced Encryption Standard (AES)                            |     |

|    |         |           | AES                                                           |     |

|    |         |           | ANSI                                                          |     |

|    |         |           |                                                               |     |

|    |         |           | Authorization                                                 |     |

|    | 12.2    |           | · · · · · · · · · · · · · · · · · · ·                         |     |

|    |         |           | Block Cipher                                                  |     |

|    | 12.3    | С         | <i>.</i>                                                      | 138 |

|    |         | 12.3.1 (  | CERT                                                          | 138 |

|    |         | 12.3.2    | Checksum                                                      | 138 |

|    |         | 12.3.3 (  | Cipher                                                        | 138 |

|    |         | 12.3.4 (  | Code                                                          | 139 |

|    |         |           | Cloning                                                       |     |

|    |         |           | Configuration                                                 |     |

|    |         |           | Corrupt Data                                                  |     |

|    |         |           | CPLD                                                          |     |

|    |         | 12.3.9 (  | CRC                                                           | 139 |

|    |         |           | Cryptography                                                  |     |

|    |         | 12.3.11 ( | Cyclic Redundancy Check (CRC)                                 | 140 |

|    | 12.4    | D         | · · · · · · · · · · · · · · · · · · ·                         | 140 |

|    |         |           |                                                               | 140 |

|    |         | 12.4.2    | Data Encryption Standard (DES)                                | 140 |

|    |         |           |                                                               |     |

|    |         | 12.4.4    | Denial of Service                                             | 141 |

|    |         |           | DES                                                           |     |

|    |         |           | Differential Power Analysis (DPA)                             |     |

|    |         | 12.4.7 E  | Diffie-Hellman Key Exchange                                   | 141 |

|    |         |           | Digital Signatures                                            |     |

|    |         | 12.4.9 E  | Disable                                                       | 142 |

|    | 12.5    | Ε         | · · · · · · · · · · · · · · · · · · ·                         | 143 |

|    |         |           |                                                               |     |

|       | 12.5.2 Elliptic Curve Cryptography (EC | C)                                      | 143 |

|-------|----------------------------------------|-----------------------------------------|-----|

|       | 12.5.4 Entropy                         | ••••••••••••••••••••••••••••••••••••••• | 143 |

| 12.6  |                                        |                                         |     |

|       |                                        | ••••••••••••••••••••••••••••••••••••••• |     |

|       |                                        | ••••••••••••••••••••••••••••••••••••••• |     |

| 12.7  |                                        |                                         |     |

|       |                                        | ۰                                       |     |

|       | 12.7.3 In-System Programming (ISP) .   | ,<br>                                   | 144 |

|       |                                        |                                         |     |

|       | -                                      | ••••••••••••••••••••••••••••••••••••••• |     |

| 12.8  |                                        | ••••••••••••••••••••••••••••••••••••••• |     |

|       |                                        |                                         |     |

|       |                                        | • • • • • • • • • • • • • • • • • • • • |     |

|       | •                                      | ••••••••••••••••••••••••••••••••••••••• |     |

| 12.9  |                                        | nd Technology (NIST)                    |     |

|       |                                        |                                         |     |

|       |                                        |                                         |     |

| 12.10 |                                        | · · · · · · · · · · · · · · · · · · ·   |     |

| 12.10 |                                        | • • • • • • • • • • • • • • • • • • • • |     |

| 12.11 |                                        | ••••••••••••••••••••••••••••••••••••••• |     |

|       | •                                      |                                         |     |

| 12.12 |                                        | ••••••••••••••••••••••••••••••••••••••• |     |

|       | 12.12.1 Random Numbers                 |                                         | 147 |

| 10.10 | <b>c c</b>                             | ••••••••••••••••••••••••••••••••••••••• |     |

| 12.13 |                                        |                                         |     |

|       | 12.13.2 Semi-Invasive Attack           |                                         | 148 |

|       |                                        |                                         |     |

|       |                                        | • • • • • • • • • • • • • • • • • • • • |     |

| 12.14 |                                        | ••••••••••••••••••••••••••••••••••••••• |     |

|       | •                                      |                                         |     |

| 12.15 |                                        |                                         |     |

|       | 12.15.1 Volatile                       |                                         | 149 |

| 12.16 |                                        |                                         |     |

|       | 12.16.1 Zeroization                    | ••••••••••••••••••••••••••••••••••••••• | 149 |

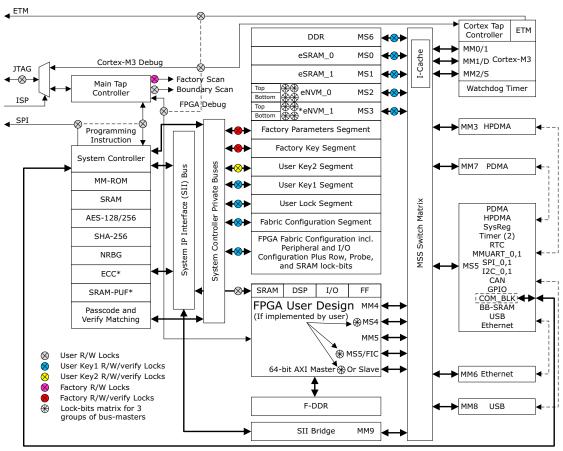

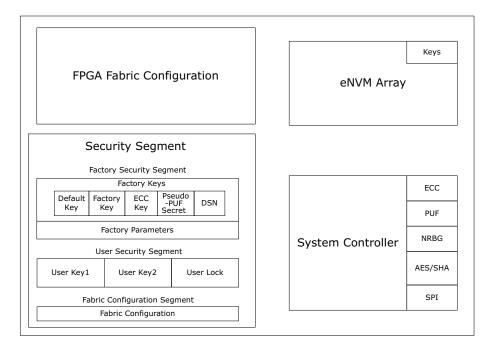

| Figure 1  | SmartFusion2 Device Security Architecture                                           | 8    |

|-----------|-------------------------------------------------------------------------------------|------|

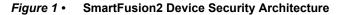

| Figure 2  | IGLOO2 Device Security Architecture                                                 |      |

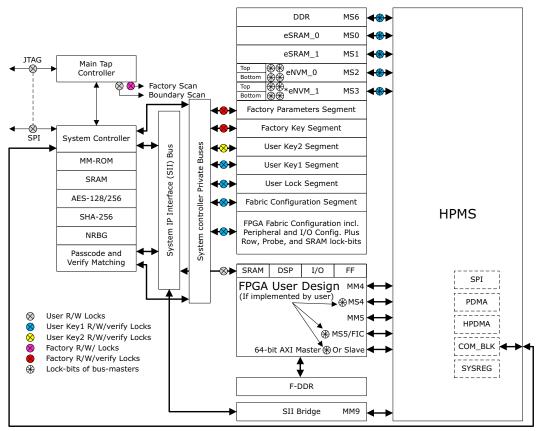

| Figure 3  | Non-Deterministic Random Bit Generator (NRBG) Block Diagram                         |      |

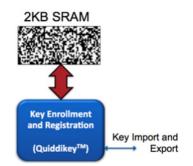

| Figure 4  | Quiddikey SRAM-PUF in SmartFusion2 and IGLOO2 devices                               |      |

| Figure 5  | Trademark Logo of Cryptography Research, Inc., used under license                   |      |

| Figure 6  | SmartFusion2 and IGLOO2 FPGA Programming Model                                      |      |

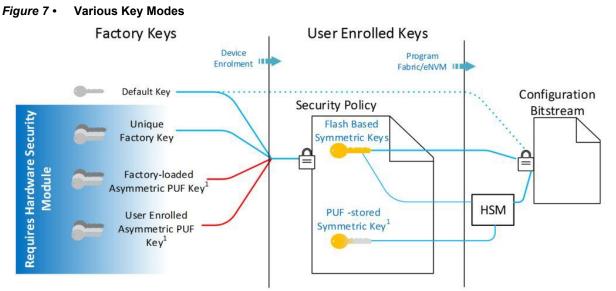

| Figure 7  | Various Key Modes                                                                   |      |

| Figure 8  | Permanently Lock Settings via SPM in the Libero SoC                                 | . 36 |

| Figure 9  | Permanently Protect Factory Test Mode Settings via SPM in the Libero SoC            | . 37 |

| Figure 10 | Fabric Update Protection via SPM in the Libero SoC                                  | . 38 |

| Figure 11 | UEK1 and UEK2 Programming Key Mode Lock via SPM in the Libero SoC                   |      |

| Figure 12 | Programming Interfaces Lock via SPM in the Libero SoC                               |      |

| Figure 13 | Disabling JTAG Boundary Scan                                                        |      |

| Figure 14 | Setting Debug Locks via SPM in the Libero SoC                                       |      |

| Figure 15 | Cortex -M3 Configurator                                                             |      |

| Figure 16 | MSS Security Policies Configurator-eSRAM0, eSRAM1, eNVM0, eNVM1 and DDR Bridge Lock |      |

| Figure 17 | M2S090TS/M2GL090TS MSS Security Configurator showing eNVM Special Sectors           |      |

| Figure 18 | MSS Security Policies Configurator - Fabric master to MSS                           |      |

| Figure 19 | Back Level Protection Settings in the Security Policy Manager                       |      |

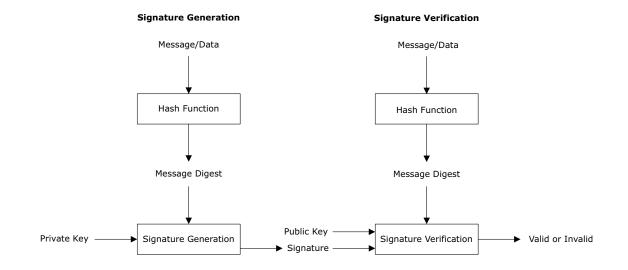

| Figure 20 | Digital Signature Processes                                                         |      |

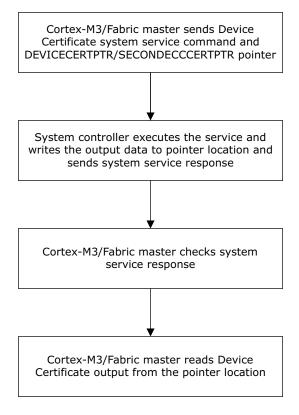

| Figure 21 | Device Certificate System Service Flow                                              |      |

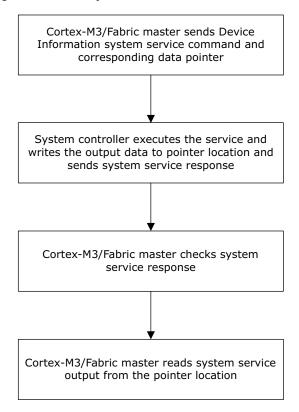

| Figure 22 | Device and Design Information System Service Flow                                   |      |

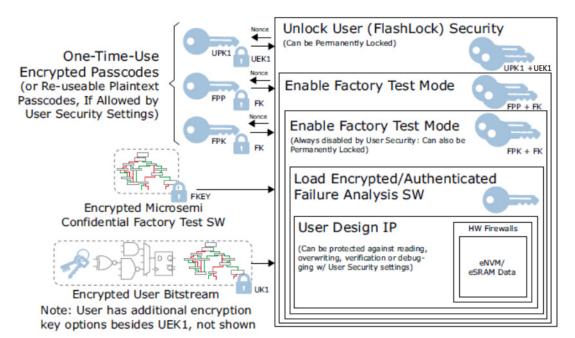

| Figure 23 | Layered Security Preventing Read-back of Design IP or User Data                     |      |

| Figure 24 | Built-in Tamper Detection Flags and Tamper Response Inputs                          |      |

| Figure 25 | Tamper Flags Waveform                                                               |      |

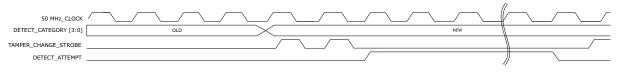

| Figure 26 | DETECT_CATEGORY Flags Waveform                                                      |      |

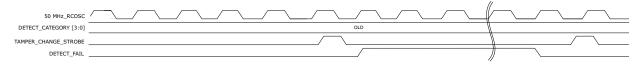

| Figure 27 | DETECT_FAIL Flags Waveform                                                          |      |

| Figure 28 | DPA Logo                                                                            |      |

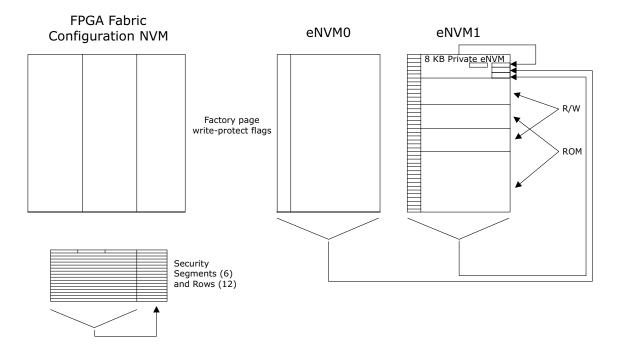

| Figure 29 | Message Digests Used for Integrity Checking of NVM                                  |      |

| Figure 30 | Power up Digest Check Selection in Tamper Macro                                     |      |

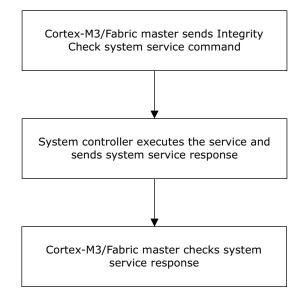

| Figure 31 | Integrity Check System Service Flow                                                 |      |

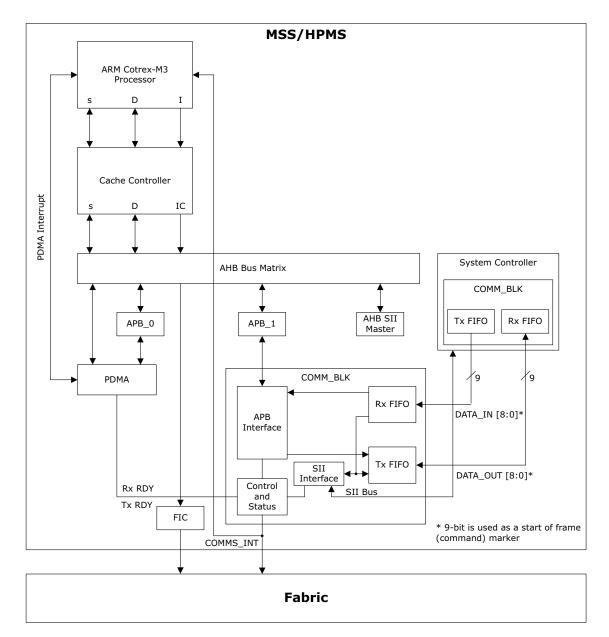

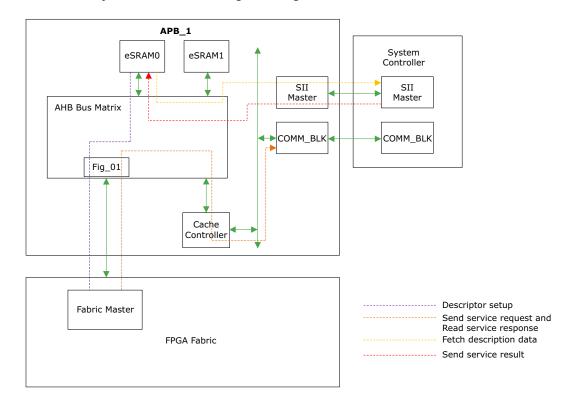

| Figure 32 | Interfacing of COMM_BLK with System Controller                                      |      |

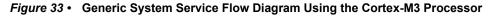

| Figure 33 | Generic System Service Flow Diagram Using the Cortex-M3 Processor                   | . 76 |

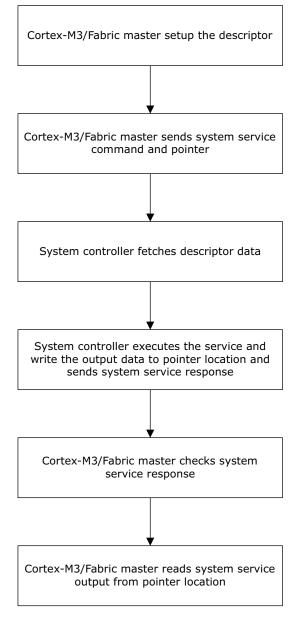

| Figure 34 | Generic System Service Flow Diagram using an FPGA Fabric Master                     |      |

| Figure 35 | Generic System Service Flow Diagram                                                 | 78   |

| Figure 36 | NRBG Block in SmartFusion2 and IGLOO2 Devices                                       | . 79 |

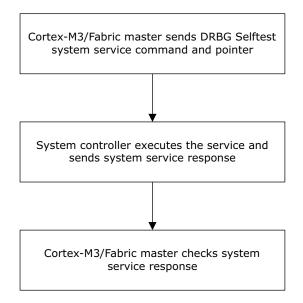

| Figure 37 | DRBG Self Test Check System Service Flow                                            | 81   |

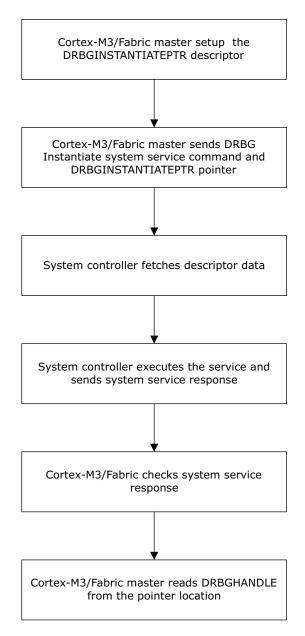

| Figure 38 | DRBG Instantiate Check System Service Flow                                          | 83   |

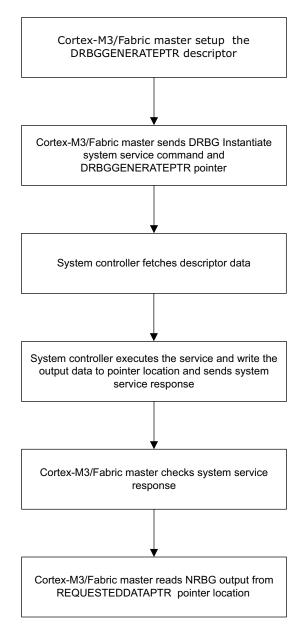

| Figure 39 | DRBG Generate System Service Flow                                                   |      |

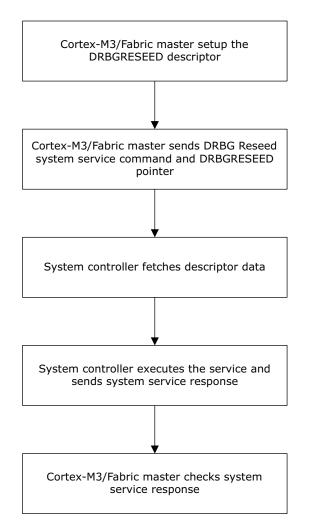

| Figure 40 | DRBG Reseed System Service Flow                                                     | 87   |

| Figure 41 | DRBG Uninstantiate System Service Flow                                              | 88   |

| Figure 42 | DRBG Reset System Service Flow                                                      | 89   |

| Figure 43 | Cryptographic Services Block in SmartFusion2                                        | 90   |

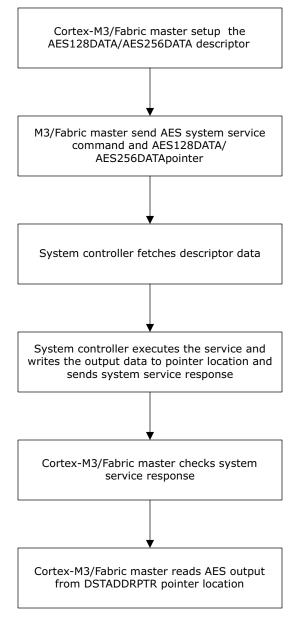

| Figure 44 | AES System Service Flow                                                             |      |

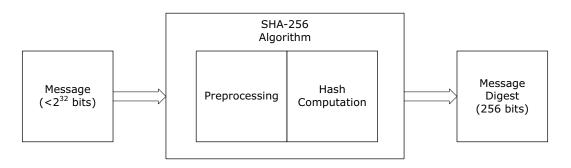

| Figure 45 | SmartFusion2 and IGLOO2 SHA-256 Operation                                           | . 93 |

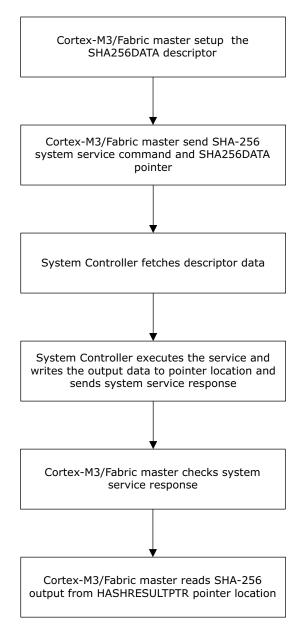

| Figure 46 | SHA-256 System Service Flow                                                         | 94   |

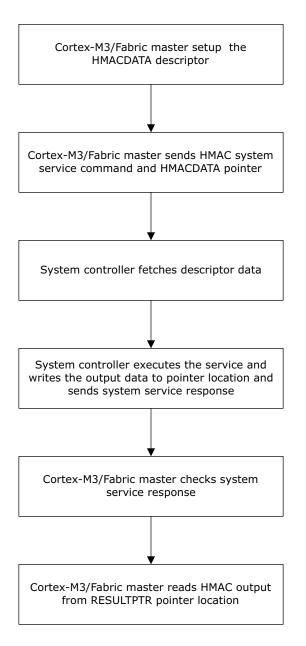

| Figure 47 | HMAC-256 System Service Flow                                                        |      |

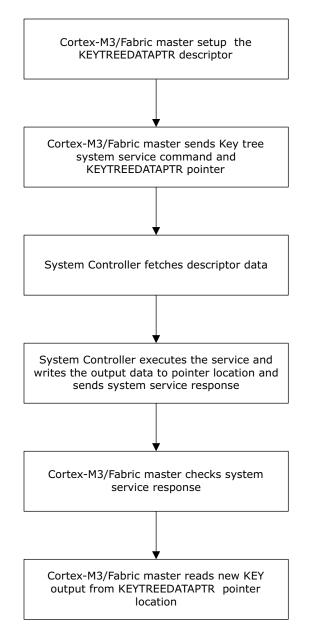

| Figure 48 | Key Tree System Service Flow                                                        |      |

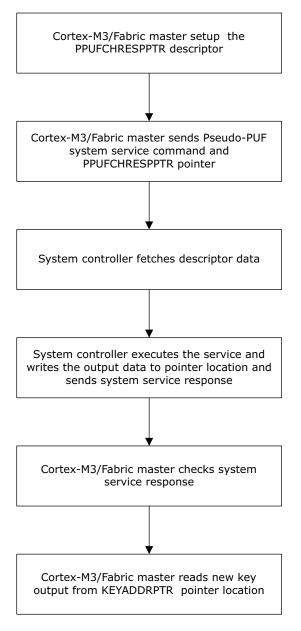

| Figure 49 | Pseudo-PUF System Service Flow                                                      | 101  |

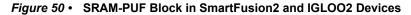

| Figure 50 | SRAM-PUF Block in SmartFusion2 and IGLOO2 Devices                                   |      |

| Figure 51 | SRAM-PUF User AC System Service Flow                                                |      |

| Figure 52 | SRAM-PUF Key Codes                                                                  |      |

| Figure 53 | Create Delete Export Import User Key Code System Service Flow                       |      |

| Figure 54 | Fetching a User PUF Key System Service Flow                                         | 111  |

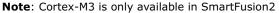

| Figure 55 | Fetching a PUF ECC Public Key System Service Flow                | 113 |

|-----------|------------------------------------------------------------------|-----|

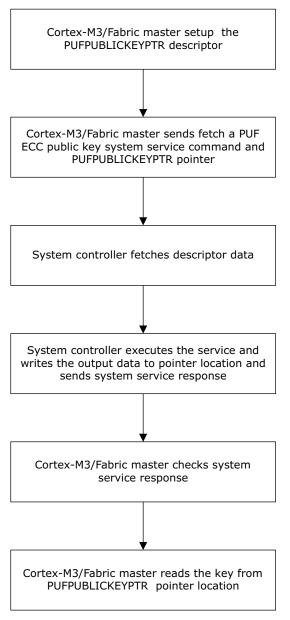

| Figure 56 | Get a PUF Seed System Service Flow                               | 115 |

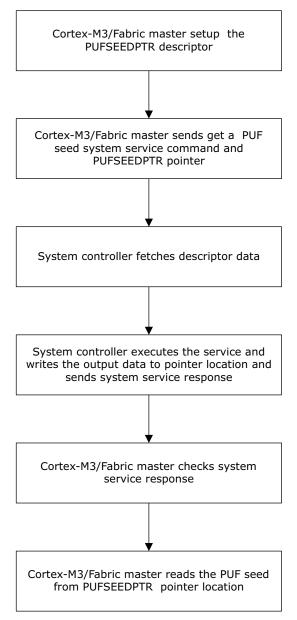

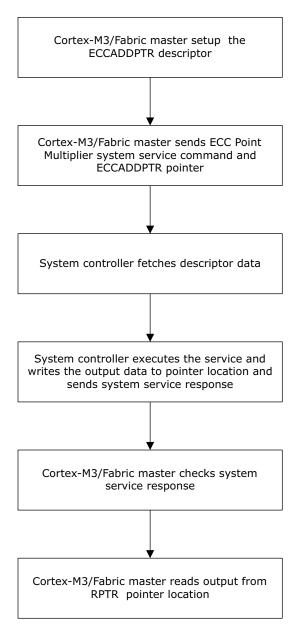

| Figure 57 | ECC Point Multiplication System Service Flow                     | 118 |

| Figure 58 | ECC Point Addition System Service Flow                           | 120 |

| Figure 59 | System Service Firmware Driver Generation                        | 124 |

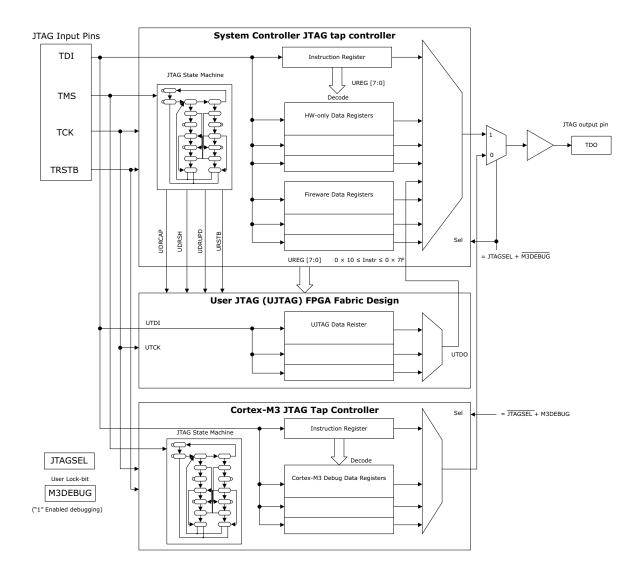

| Figure 60 | JTAG Controllers CBlock Diagram (Including UJTAG Data Registers) | 127 |

| Figure 61 | DPA Logo                                                         | 128 |

# **Tables**

| Table 1<br>Table 2   | SmartFusion2 and IGLOO2 Design Security Features through System Service |    |

|----------------------|-------------------------------------------------------------------------|----|

|                      |                                                                         |    |

| Table 3              | eNVM Special Sector Address Ranges                                      |    |

| Table 4              | Device Certificate System Service Request                               |    |

| Table 5              | Device Certificate System Service Response                              |    |

| Table 6              | Service Status                                                          |    |

| Table 7              | Public Information Accessible                                           |    |

| Table 8              | Information System Services                                             |    |

| Table 9              | Serial Number Service Request                                           |    |

| Table 10             | Serial Number Service Response                                          |    |

| Table 11             | Service Status                                                          |    |

| Table 12             | USERCODE Service Request                                                |    |

| Table 13             | USERCODE Service Response                                               |    |

| Table 14             | Design Version Service Request                                          |    |

| Table 15             | Design Version Service Response                                         |    |

| Table 16             |                                                                         |    |

| Table 17             | DETECT_CATEGORY Flag Description                                        |    |

| Table 18             | Built-in Tamper Response Options                                        |    |

| Table 19             | Zeroization Options                                                     |    |

| Table 20             | FPGA Components during the Zeroization                                  |    |

| Table 21             | Security Segments during the Zeroization                                |    |

| Table 22             | Integrity Check Service Request                                         |    |

| Table 23             | Integrity Check Service Response                                        |    |

| Table 24             | Integrity Check Function                                                |    |

| Table 25             | SmartFusion2 and IGLOO2 Data Security Features through System Service   |    |

| Table 26             | DRBG Self Test Check System Service Request                             | 82 |

| Table 27             | DRBG Self Test Check System Service Response                            |    |

| Table 28             | DRBG Service Response Status Codes                                      |    |

| Table 29             | DRBG Instantiate Check System Service Request                           |    |

| Table 30             | DRBG Instantiate Check System Service Response                          |    |

| Table 31             | DRBGINSTANTIATE Data Descriptor Structure                               |    |

| Table 32             | DRBG Generate System Service Request                                    |    |

| Table 33             | DRBG Generate System Service Response                                   |    |

| Table 34<br>Table 35 | DRBGGENERATE Data Descriptor Structure                                  |    |

| Table 35             | DRBG Reseed System Service Request                                      |    |

| Table 30             | DRBGRESEED Data Descriptor Structure                                    |    |

| Table 37             | DRBG Uninstantiate System Service Request                               |    |

| Table 30             | DRBG Reset System Service Request                                       |    |

| Table 39             | DRBG Reset System Service Response                                      |    |

| Table 40             | DRBG Uninstantiate System Service Response                              |    |

| Table 42             | AES System Service Request                                              |    |

| Table 42             | AES System Service Response                                             |    |

| Table 43             | AES128 Data Descriptor                                                  |    |

| Table 45             | AES256 Data Descriptor                                                  |    |

| Table 46             | SHA-256 System Service Request                                          |    |

| Table 40             | SHA-256 System Service Response                                         |    |

| Table 47             | SHA256DATA Structure                                                    |    |

| Table 40             | HMAC System Service Request                                             |    |

| Table 50             | HMAC System Service Response                                            |    |

| Table 50             | HMAC System Service Response                                            |    |

| Table 51             | KeyTree System Service Request                                          |    |

| Table 52             | KeyTree System Service Response                                         |    |

| Table 54             | KEYTREEDATA Structure                                                   |    |

|                      |                                                                         |    |

а 🐼 Міскоснір company

| Table 55 | Pseudo-PUF System Service Request                                 | 101 |

|----------|-------------------------------------------------------------------|-----|

| Table 56 | Pseudo-PUF System Service Response                                | 102 |

| Table 57 | PPUFCHRESP Structure                                              | 102 |

| Table 58 | User Activation Code Create or Delete Service Request             | 104 |

| Table 59 | User Activation Code Create or Delete Service Response            | 105 |

| Table 60 | User SRAM-PUF Activation Code (PUFUSERAC) structure               | 105 |

| Table 61 | Create Delete Export Import User Key Code System Service Request  | 107 |

| Table 62 | Create Delete Export Import User Key Code System Service Response | 108 |

| Table 63 | SRAM-PUF User Key Code (PUFUSERKC) Structure                      |     |

| Table 64 | PUFUSERACKCEXPORT Memory View                                     |     |

| Table 65 | PUFUSERACKCIMPORT Memory View                                     | 110 |

| Table 66 | Fetch a User PUF Key System Service Request                       |     |

| Table 67 | Fetch a User PUF Key System Service Response                      | 112 |

| Table 68 | Fetch a User PUF Key Response Status                              |     |

| Table 69 | Fetch a User PUF Key (PUFUSERKEY) Structure                       | 112 |

| Table 70 | Fetch a PUF ECC Public Key System Service Request                 |     |

| Table 71 | Fetch a PUF ECC Public key Descriptor Structure                   | 114 |

| Table 72 | Fetch a PUF ECC Public Key System Service Response                |     |

| Table 73 | Fetch a PUF ECC Public key Status                                 | 114 |

| Table 74 | Get a PUF Seed System Service Request                             |     |

| Table 75 | Get a PUF Seed System Service Response                            | 116 |

| Table 76 | Get a PUF Seed Response Status Codes                              | 116 |

| Table 77 | PUFSEEDPTR Structure                                              | 116 |

| Table 78 | ECC Point Multiplication System Service Request                   | 118 |

| Table 79 | ECC Point Multiplication System Service Response                  | 119 |

| Table 80 | ECCPMULT Structure                                                |     |

| Table 81 | ECC Point Addition System Service Request                         | 120 |

| Table 82 | ECC Point Addition System Service Response                        |     |

| Table 83 | ECCPADDRPTR Structure                                             | 121 |

| Table 84 | DPA Protection on System Services                                 | 121 |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

### 1.1 Revision 11.0

- Added a new section Debug Pass Key, page 23.

- · Replaced the base activation code to activation code throughout the document.

- Updated Figure 1, page 8 to indicate the JTAG disable between JTAG interface and the Main Tap Controller.

- The following points summarize the updates made in section Tamper Detection Flags, page 59:

- Changed the description of JTAG\_ACTIVE flag, see Table 16, page 59.

- Added the description of DETECT\_CATEGORY, DETECT\_ATTEMPT, and DETECT\_FAIL flags, see Table 16, page 59.

- Added a column to specify the source that generates the tamper flags, see Table 16, page 59.

Undeted the Figure 26, page 61 and Figure 27, page 61.

- Updated the Figure 26, page 61 and Figure 27, page 61.

- Updated the note that describe the DETECT\_CATEGORY flag after Figure 26, page 61.

- Added a note to specify the clear condition of tamper flags after Table 16, page 59.

- Renamed section 4.3.6 User ECC Public Key Modes to User ECC Key Modes (KUP and KUPE), page 30. And, added the section KUP Key Mode, page 30 and KUPE Key Mode, page 30.

## 1.2 Revision 10.0

The following is a summary of changes made in this revision.

- Updated the document for Libero SoC v12.0.

- Updated the sections Passcode Locks (Permanent Locks), page 36 and Fabric Programming Erase Verify Read Lock-bits, page 37.

- Added a note under Table 25, page 73 to include a programming workaround when cryptographic system services are enabled in the design.

- Updated the section Using Zeroization to Decommission Devices, page 66.

- Added a footnote for Table 1, page 16.

- Added descriptions for DETECT\_CATEGORY flag, see Table 17, page 60.

- Added information about how to disable JTAG boundary scan using Libero SoC, seeProgramming Port Lock-bits, page 39.

- Updated Table 19, page 62 to clearly specify which information segment is retained and which segment is destroyed when the Recoverable option is selected.

### 1.3 Revision 9.0

The following changes were made in this revision.

- Information about eNVM array was updated to include SRAM-PUF/ECC key storage information.

For more information, see eNVM Array, page 24.

- Throughout the document, figures were updated to show Libero SoC v11.8.

- Information about key mode lock bits was updated to include UEK3. For more information, see Key-Mode Lock-bits, page 38.

- Throughout the document, KUS was replaced by UEK3.

### 1.4 Revision 8.0

The following changes were made in this revision.

- Security Concerns in FPGAs, page 3, Reverse Engineering Protection, page 125, and Internal Security Features, page 130 were added.

- "Error Detection and Correction Controllers" section was deleted.

- Security Features Overview, page 7, Cryptographic Security Features, page 19, FPGA Hardware Access Controls, page 35, Supply Chain Assurance, page 47, Data Security Through System Services, page 73, and Using System Services Driver, page 124 were updated.

- DISABLEIO\_ALL\_IOS\_N, page 62 was updated (SAR 80923).

### 1.5 **Revision 7.0**

In revision 7.0 of this document, a note was updated in Programming Port Lock-bits, page 39 (SAR 78163).

### 1.6 Revision 6.0

The following changes were made in revision 6.0 of this document.

- IGLOO2 Security and Reliability User Guide and SmartFusion2 Security and Reliability User Guide were merged into this user guide.

- This revision number continues for further updates. Refer to SmartFusion2 and IGLOO2 list of changes tables provided below for earlier updates.

- Zeroization Procedure, page 62 was updated (SAR 56959).

- Fabric Configuration and eNVM Integrity Tests, page 67 was updated (SAR 67636).

## 1.7 IGLOO2 Document List of Changes (Outdated)

| Revision                       | Changes                                                                                                                                                                                        |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision 4<br>(July 2015)      | This user guide was restructured and rewritten (SAR 57510 and 68479).                                                                                                                          |

| Revision 3<br>(January 2015)   | Removed all instances of and references to M2S100 device from Table 1, Table 2, Table 4, Table 16 and Table 25 (SAR 62858).<br>Replaced all instances of "S" version with "S" or "TS" version. |

| Revision 2<br>(June 2014)      | User guide was restructured and rewritten (SAR 57510).                                                                                                                                         |

| Revision 1<br>(September 2013) | Added "How to Use EDAC" section in Error Detection and Correction Controllers chapter (SAR 50571)                                                                                              |

| Revision 0<br>(June 2013)      | Initial release.                                                                                                                                                                               |

## **1.8 SmartFusion2 Document List of Changes (Outdated)**

| Revision                       | Changes                                                                                                                                                                                        |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision 5<br>(January 2015)   | Removed all instances of and references to M2S100 device from Table 1, Table 2, Table 4, Table 16 and Table 25 (SAR 62858).<br>Replaced all instances of "S" version with "S" or "TS" version. |

| Revision 4<br>(May 2014)       | This user guide was restructured and rewritten (SAR 57510).                                                                                                                                    |

| Revision 3<br>(September 2013) | Updated the "SmartFusion2 Security Features Overview" chapter (SAR 42854).                                                                                                                     |

| Revision 2<br>(April 2013)     | Restructured the Error Detection and Correction Controllers chapter (SAR 46164).                                                                                                               |

| Revision 1<br>(November 2012)  | Added the "SmartFusion2 Security Features Overview" Chapter.                                                                                                                                   |

| Revision 0<br>(October 2012)   | Initial release.                                                                                                                                                                               |

# 2 Security Concerns in FPGAs

As FPGA sizes have grown to exceed the million-gate mark, they are used for more complex and valuable designs. These days FPGAs include millions of gates of logic, megabytes of memory, high-speed transceivers, analog interfaces, and robust processors. Hence, applications such as communications infrastructure, sensitive database access, critical industrial control, and high-performance signal processing that run in the FPGAs, have more value and handle more data. This brings a greater need to protect these applications and data. This chapter briefly describes the various common security concerns in FPGAs designs.

Throughout this document, the FPGA security functions are referenced as "design security" features and "data security" features. The following section describes the design security and data security features.

### 2.1 Design Security

Design security feature protects the design IP and other sensitive information such as cryptographic keys that are used in the FPGA initial configuration. Design IP includes designer's logic design, firmware code, and security settings loaded in the design. Designer's logic design is typically a register-transfer-level (RTL) source code in a design language such as Verilog or VHDL. This source code is compiled ultimately to a binary form that is used to configure the FPGA Fabric look-up tables (LUTs), routing switches and other programmable elements that give the FPGA Fabric and I/Os their desired functionality. Another aspect of design IP is firmware code (C language or assembly source code) that can be complied to binary code and is normally loaded and stored in eNVM within the device for execution by the Cortex-M3 -based microprocessor sub-system (MSS). Microsemi SoC FPGAs such as SmartFusion<sup>®</sup>2 also contain a hard ARM<sup>®</sup> Cortex<sup>™</sup>-M3 processor. The larger programs may require external non-volatile memory as well, to hold them, but the security of this code must be managed by the application that the user writes, not the built-in features of the device.

Static end-application data values, considered as part of the design IP, may also be stored in the on-chip eNVM.

A third broad category of IP includes all the cryptographic keys and security settings loaded into a device that configures the security properties, for example, whether upgrades are allowed, and what action to take if tampering is detected, etc. In SmartFusion2 most of the security keys and settings are stored in a specially designed flash-based security segment described later in the guide.

Common security goals of the design owner are to keep the design IP confidential, to control the number of devices (and systems containing such devices) that are produced, and to prevent tampering with the design either when initially programmed, or thereafter. If field updates are allowed, they should only originate with the design owner, and must be installed only with the exact configuration the owner intends. The systems configured should perform reliability as intended, without unwanted extra functionality. This implies that the design owner wants to use only trusted devices with the expected performance, environmental capabilities, and reliability characteristics.

### 2.2 Data Security

Data security feature protects the data that is processed by the end application. The asset being protected is the data generated/computed, stored, or communicated by the run-time application. This data is often dynamic and usually owned by the user. Very often, cryptographic techniques are used to protect these assets. Data security is closely related to the terms— information assurance (IA) and information security. For example, if the configured design is implementing the key management and encryption portion of a secure military radio, data security can entail encrypting and authenticating the radio traffic, and protect the associated application-level cryptographic keys.

All Smartfusion2 and IGLOO<sup>®</sup>2 devices incorporate enhanced design security which make them the most secure programmable logic devices. SmartFusion2 and IGLOO2 devices also include an advanced set of on-chip data security features that make designing secure information assurance applications easier and better than before. Several of the largest family members have additional design and data

security features not present in the smaller devices. The design and data security features are described later in the document.

## 2.3 Design Security Concerns

In this section, few specific design security concerns are described:

### 2.3.1 Cloning

Cloning (with respect to FPGAs) refers to producing additional devices that are programmed identical to legitimately produced ones. The concern arises as FPGAs are generally openly available on the market, and anyone with valid binary configuration data (often referred to as a "bitstream" file) can obtain devices and, without proper FPGA security, might be able to produce as many fully configured copies as they wish. An understanding of how the design works is not necessarily a requirement to produce clones; possessing the configuration data and blank devices may be all that is required.

### 2.3.2 Overbuilding

Overbuilding is a special case of cloning of whole systems where the legitimate design owner hires a contract manufacturer (CM) to build a certain number of systems, but a dishonest CM (or perhaps his rogue employees) produce more systems than that were authorized so they can sell the overage themselves. Because of the CM's privileged and trusted insider position and possessing all the data required to produce legitimate systems including, for example, the FPGA configuration files and perhaps even the associated cryptographic keys, overbuilding by dishonest CMs or insiders is generally a bigger threat than cloning from other types of adversaries that don't have access to all the same data.

SmartFusion2 and IGLOO2 contain security features, described later, that allow the design owner to control the number of FPGAs that are programmed with a given design, almost completely eliminating the risk of cloned FPGAs, and thus also preventing overbuilding of systems containing FPGAs.

### 2.3.3 Reverse Engineering

Modern FPGAs can be configured with large and very complex functionality. Reverse engineering (RE) by observing only the FPGA inputs and outputs is quite difficult. This can be a significant hurdle to those attempting to steal the design IP. However, if an adversary can gain access to the binary FPGA Fabric or CPU firmware configuration data in plaintext form, reverse engineering of the system is much easier, since it becomes more of a "white-box" class of problem where some or all of the internal elements of the design are visible.

The detailed knowledge and understanding of how the FPGA logic or CPU firmware in a design works, can be very valuable IP, a high-value asset in its own right. For example, the IP could be an industrial or national security secret. The adversary may wish to understand how the design works to find security vulnerabilities that can be exploited in systems of the same or similar design. In some cases, just publishing full or partial design secrets can be a major concern.

The cost of reverse engineering can be lower than the cost of designing a competitive system from publicly available knowledge, giving the IP thief an unfair economic advantage versus the legitimate IP owner. Such IP, once revealed, may be cloned, ported to other implementations, or even sometimes enhanced. The useful lifetime of systems with known exploits may be reduced, which requires expensive development of replacement systems.

Furthermore, if the workings of a design are known, it may also be possible for an adversary to insert undesired functionality into it, such as a Trojan Horse that provides a back-door for extracting sensitive run-time data, and then re-introduce the modified design, undetected into the otherwise legitimate original system.

The main approach to prevent reverse engineering is to keep the design confidential. This confidentiality can be lost if the FPGA configuration data (e.g., for the FPGA fabric, or the firmware for the MCU) is captured in plaintext form or can be read-back from a device; or if an encrypted version of the configuration data is known and the encryption keys are stolen or extracted from a device. SmartFusion2 and IGLOO2 have strong countermeasures to maintain the confidentiality of the design configuration and associated secret keys. See Reverse Engineering Protection, page 125 to know more.

### 2.3.4 Counterfeiting

Counterfeiting can refer to several types of fraud at either the component or system level. While there is a remote possibility of an FPGA being copied and produced by an unauthorized manufacturer, the more realistic threats are from devices originally produced by the FPGA's original component manufacturer (OCM) that are somehow obtained by, and then misrepresented and sold by the counterfeiter.

These devices can be used devices that are removed from old systems, refurbished, and resold as new; or devices binned as lower-speed grade or requiring a more restricted operating temperature that are remarked and misrepresented as faster or having guaranteed performance over a wider temperature range. Similarly, devices could be misrepresented as having been screened for higher reliability levels, which actually are not screened, or which have failed screening tests. In many of the above cases the devices may work at first, or in benign environments, but fail under conditions where the properly binned or screened devices would have worked correctly. As these are "real" devices that work correctly (at least initially) they can be very difficult to segregate from legitimate devices by performing an inspection or an electrical test. It is a challenge for the legitimate suppliers of ICs to provide better marking and inspection methods while the counterfeiters create higher fidelity fakes that are harder to detect.

Rogue insiders could possibly obtain devices that have failed some functional test, and fraudulently introduce them into the supply chain as fully functional devices. In some cases, the devices in question may be obtained by "buying low and selling high," (after being re-marked with added features that aren't actually present) or they may be stolen from fabrication, test or assembly facilities, delivery trucks, warehouses, or in stages further down the supply chain.

Microsemi has instituted a number of very strong measures during the manufacturing process and in the shipped devices which help in stopping counterfeiting and related fraud. These features, supported in the Libero<sup>®</sup> design automation tool suite, detect counterfeit devices before being shipped in end-user systems, no matter where they are introduced in the supply chain.

Counterfeiting at the system level usually means a clone, or a system that is designed to work similar to the real system, but produced by a counterfeiter who fraudulently misrepresents it as coming from the legitimate source. Counterfeit systems are often made using inferior components and processes in order to produce them at the lowest possible cost. Any brand damage due to bad design, shoddy construction, or poor reliability will unfortunately be directed to the legitimate brand owner while the counterfeiter can stay safe with the illegal profits earned. In extreme cases, the legitimate manufacturer may find counterfeit systems returned under warranty, or even worse, to the subject of liability or litigation.

Many of the other security concerns mentioned so far may also lead to counterfeiting at the system level. For example, a counterfeit system may include a Trojan Horse. It could be a standard-grade offering misrepresented as a premium grade, or modified to provide optional premium services with the premium price going to the counterfeiter rather than the legitimate producer.

If good FPGA security makes cloning and reverse engineering difficult, it can be a useful deterrent to several types of system-level fraud. Therefore, good FPGA security can be part of the solution to system-level counterfeiting.

### 2.4 Data Security Concerns

Data security is potentially as broad a subject as there are possible end uses of an FPGA, since in the broadest sense an FPGA is always used to process data, a concise but all-encompassing definition is difficult. In order to concise the definition, the data considered is usually restricted to data that are sensitive.

Data security very often uses cryptographic techniques, implementing various security services. Often the services provided are amongst the five familiar information security services:

- · Confidentiality Keeping the data secret

- Integrity Insuring the data hasn't been altered

- Availability Both available when needed, and denied to unauthorized uses (including unauthorized privilege escalation)

- Authenticity Data is genuine and from the correct source

- Non-repudiation A completed transaction cannot be denied

Listed below are some of the attacks that may be used to break the security services.

- Monitoring or snooping on communication traffic or stored data in motion, or data at rest)

- Tampering with or changing data (for example, a "replay attack")

- Impersonating one of the legitimate actors (for example, man-in-the-middle attack)

- Exploiting weak protocols

- Freshness, oracle, type, binding, repudiation, or other flaws

- Exploiting other design security weaknesses

- Weakness discovered with reverse engineering

- Inserting a Trojan Horse into user's system

- Re-introducing a weakness user had fixed with an update

### 2.5 Design Security Impact on Data Security

Without design/device security, it is virtually impossible to provide good data security. Most design security threats, such as reverse engineering, insertion of a Trojan Horse, unauthorized field upgrades, etc. can lead to serious data security vulnerabilities. Data Security, including features provided by Microsemi intended for use in data security applications, are discussed later in the document.

# **3 Security Features Overview**

Microsemi's SmartFusion2 and IGLOO2 devices have built-in features that provide enhanced security during all stages of the device life-cycle from user key injection and bitstream programming, to field updates, and finally to device decommissioning, when necessary. This chapter gives an overview of these security features.

## 3.1 Security Architecture

The following sections describe SmartFusion2 and IGLOO2 security model architecture

### 3.2 SmartFusion2 Security Architecture

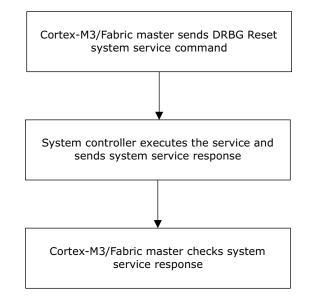

The following figure shows SmartFusion2 device architecture from a security model point of view. The left column shows the system controller and its major hardware cryptographic accelerators. The system controller manages all programming, verification, design security key-management, and related operations. Also, it manages the system services through various hardware cryptographic accelerators. The right column shows the Microcontroller Subsystem (MSS) that has configurable access control policies to prevent over-writing any elements of a design. The middle column shows the eNVM blocks (two on -090 and -150 devices and one on other SmartFusion2 devices) identified in blue. The eNVM pages can be designated as write-protected to make it easy to control sensitive data. Additionally, a novel NVM integrity check mechanism can be used to check the reliability and security in a device automatically upon power-up, or upon demand. The middle column also shows the six security segments to store keys and user settings (identified in green) and shows the FPGA fabric configuration block (shown in light blue). Microsemi flash-based FPGA configuration memory cells are located within the FPGA fabric and directly control the routing switches and look-up tables that are used to implement the user's design. This means the bitstream is not exposed on every power up for SmartFusion2 devices as is done by SRAM-based FPGAs.

\* Only on target devices

The small circles with X's in them (shown in the preceding figure) indicate some of the functions that can be disabled through the setting of various security options—often referred to as Lock-bits. This user guide is divided into various sections to cover each element of the diagram, and cover the various capabilities of the SmartFusion2 device in a way that is easy to understand.

### 3.3 IGLOO2 Security Architecture

The following figure shows IGLOO2 device architecture from a security model point of view. The left column shows the system controller and its major hardware cryptographic accelerators. The system controller manages all programming, verification, design security key-management, and related operations. It also manages the system services through various hardware cryptographic accelerators. It is similar to SmartFusion2 except that the MSS is replaced by high performance memory Subsystem (HPMS) block. The right column shows the HPMS that has configurable access control policies to prevent over-writing any elements of a design. The middle column shows the eNVM blocks (two on larger devices and one on smaller devices) identified in blue. The eNVM pages can be designated as write-protected to make it easy to control sensitive data. Additionally, a novel NVM integrity check mechanism can be used to check the reliability and security in a device automatically upon power-up, or upon demand. The middle column also shows the SPGA fabric configuration block, shown in light blue. Microsemi flash-based FPGA configuration memory cells are located within the FPGA fabric and directly control the routing switches and look-up tables used to implement the users design. This means the bitstream is not exposed on every power up for IGLOO2 devices as is done by SRAM-based FPGAs

\* Only on target devices

The small circles with X's in them (shown in the preceding figure) indicate some of the functions that can be disabled through the setting of various security options, often referred to as Lock-Bits.

### 3.4 System Controller for Programming and Various Services

The system controller in SmartFusion2 and IGLOO2 devices manages all programming, verification, design security key-management, and related operations. The system controller is a dedicated fixed-function hardened processor reserved for these functions, and is not reconfigurable. Its programming and runtime operations are determined by a dedicated immutable metal-mask ROM. During programming, the system controller authenticates and decrypts incoming bitstreams, erases and writes the target flash memory segments, and responds to other external programming-related protocols, such as key verification. The system controller includes several cryptographic hardware accelerators for data security applications. Refer to Data Security Through System Services, page 73.

The system controller also provides both internal and external information-related services, such as reporting the Factory Serial Number, the JTAG USERCODE value, or exporting the Device Certificate. Refer to Supply Chain Assurance, page 47. The availability of many of the services can be controlled by user security lock-bit settings. The system controller can optionally be suspended after booting, refer to System Controller Suspend Mode, page 136.

During factory test mode the system controller is used, along with other built-in hardware test features such as scan chains and memory built-in self-test (BIST) to verify the correct manufacturing of each device and to program factory-related data such as the factory keys and device calibration data (used to account for normal manufacturing process variations). If user and factory security settings allow, it is possible for the user and factory to collaborate, to supply the correct passcodes and keys required to re-

enter factory test mode in order to perform failure analysis of a failed device. There are strong, layered, protections in place to prevent an adversary (or just the user or factory) from being able to enter factory test mode. In user-configured devices there are default mechanisms that lock-out the factory, including several optional layered mechanisms whereby the user can permanently prevent the device from entering the factory test mode. Of course, if any of these permanent lock options are used, failure analysis becomes impossible. Depending on the exact mechanisms deployed, field updates or design verification may also be permanently blocked.

# 3.5 Hardware Cryptographic Accelerators

The system controller and associated security hardware includes hardware-based security countermeasures to protect it against a broad range of threats, and manages the hardware-based security countermeasures throughout the rest of the device. This section describes the hardware cryptographic accelerators. The cryptographic system services are only available in premium devices denoted with an "S" (or "TS") suffix in the model number immediately following the device capacity code.

The hardware accelerator includes the following:

- Cryptographic Services block:

- AES-128/256 Hardware Accelerator

- SHA-256 Hardware Accelerator

- Non-Deterministic Random Bit Generator (NRBG)

- Elliptic Curve Cryptography Hardware Accelerator (P-384 Curve)

- SRAM-PUF Secure Key Storage and Random Seed Generation Engine

These hardware accelerators have been certified in NIST's cryptographic algorithm validation program (CAVP). Refer to the following sections for links to the appropriate certificates in the NIST algorithm validation lists on the NIST website.

The use of the hardware accelerators in the SmartFusion2 and IGLOO2 design security protocols have been assessed by an accredited independent third-party security laboratory for resistance to side channel analysis and have been certified as defined by the Rambus Cryptography Research *Differential Power Analysis (DPA) Countermeasure Validation Program (CVP) scheme*. The following design security protocols and services were assessed and certified:

- Bitstream Loading Protocol, BSP

- Bitstream Authentication Service, BAS

- Key Verification Protocol, KVP

- Plaintext Passcode Matching & Privilege Escalation, PTP

- One-Time Passcode, OTP

- Device Certificate Service DCS

- Pseudo-PUF Challenge/Response Service, PPS

The underlying cryptographic primitives (AES, ECC, SHA), used in the context of these protocols are included. These protocols and services are described later in this document.

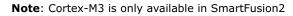

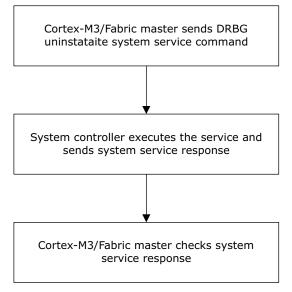

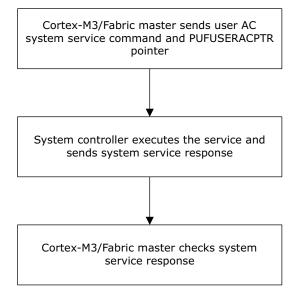

### 3.6 AES-128/256 Hardware Accelerator