# UG0445 User Guide SmartFusion2 SoC FPGA and IGLOO2 FPGA Fabric

a **Microchip** company

#### Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email:FPGA\_marketing@microchip.co

www.microchip.com

©2022 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revisi          | on History                                                                       | 1   |

|---|-----------------|----------------------------------------------------------------------------------|-----|

|   | 1.1             | Revision 9.0                                                                     | . 1 |

|   | 1.2             | Revision 8.0                                                                     | . 1 |

|   | 1.3             | Revision 7.0                                                                     | . 1 |

|   | 1.4             | Revision 6.0                                                                     | . 1 |

|   | 1.5             | Revision 5.0                                                                     | . 1 |

|   | 1.6             | Revision 4.0                                                                     | 2   |

|   | 1.7             | Revision 3.0                                                                     | . 2 |

|   | 1.8             | Revision 2.0                                                                     | . 2 |

|   | 1.9             | Revision 1.0                                                                     | 2   |

|   | 1.10            | Revision 0.0                                                                     | . 3 |

| 2 | Cabria          | Analitaatuma                                                                     | 1   |

| 2 |                 | Architecture                                                                     |     |

|   | 2.1             | Introduction                                                                     |     |

|   | 2.2             | Fabric Resources                                                                 |     |

|   | 2.3             | Architecture Overview                                                            |     |

|   |                 | 2.3.1 Logic Element                                                              |     |

|   |                 | 2.3.2       Interface Logic Element         2.3.3       I/O Module               |     |

|   |                 | 2.3.4 FPGA Routing Architecture                                                  |     |

|   | 2.4             | Fabric Array Coordinate System                                                   |     |

|   |                 |                                                                                  |     |

| 3 | LSRA            |                                                                                  |     |

|   | 3.1             | Introduction                                                                     |     |

|   |                 | 3.1.1 Features                                                                   |     |

|   | 3.2             | LSRAM Resources                                                                  |     |

|   | 3.3             | Functional Description                                                           |     |

|   |                 | 3.3.1 Port List                                                                  |     |

|   | 3.4             | Memory Modes                                                                     |     |

|   | J. <del>4</del> | 3.4.1 Dual-Port Mode                                                             |     |

|   |                 | 3.4.2 Two-Port Mode                                                              |     |

|   | 3.5             | Operating Modes                                                                  | 24  |

|   |                 | 3.5.1 Read Operation                                                             | 24  |

|   |                 | 3.5.2 Write Operation                                                            |     |

|   |                 | 3.5.3 Reset Operation                                                            |     |

|   |                 | 3.5.4       Block Select Operation       2         3.5.5       Collision       3 |     |

|   | 3.6             | How to Use LSRAM                                                                 |     |

|   | 3.0             | 3.6.1 Design Flow                                                                |     |

|   |                 | 3.6.2 LSRAM Use Model                                                            |     |

| 4 | Micro           | SRAM (µSRAM)                                                                     | l8  |

| т | 4.1             | Introduction                                                                     |     |

|   | 4.1             | 4.1.1 Features                                                                   |     |

|   | 4.2             | μSRAM Resource Table                                                             |     |

|   | 4.3             | Functional Description                                                           |     |

|   | 1.0             | 4.3.1 Architecture Overview                                                      |     |

|   |                 |                                                                                  | 40  |

|   |   |    |     |       | _ | _  | _   |    | _  |

|---|---|----|-----|-------|---|----|-----|----|----|

| а | M | Mı | -00 | יכאוו |   | on | าทะ | an | \/ |

|   |            | 4.3.3             | Port Description                                         | . 41 |

|---|------------|-------------------|----------------------------------------------------------|------|

|   | 4.4        | •                 | ng Modes                                                 |      |

|   |            | 4.4.1<br>4.4.2    | Read Operation                                           |      |

|   | 4.5        |                   | peration                                                 |      |

|   | 4.5        | 4.5.1             | Collision                                                |      |

|   | 4.6        |                   | Jse µSRAM                                                |      |

|   | 4.0        | 4.6.1             | Design Flow                                              |      |

|   |            |                   | ·                                                        |      |

| 5 | Math I     | Blocks            |                                                          | 57   |

|   | 5.1        | Introduc          | tion                                                     |      |

|   |            | 5.1.1             | Features                                                 |      |

|   | 5.2        |                   | ock Resource Table                                       |      |

|   | 5.3        |                   | nal Description                                          |      |

|   | <b>5</b> 4 | 5.3.1             | Architecture Overview                                    |      |

|   | 5.4        | 5.4.1             | Jse Math Blocks Design Flow                              |      |

|   |            | 5.4.2             | Math Block Use Models                                    |      |

|   |            | 5.4.3             | Coding Style Examples                                    |      |

| _ |            |                   |                                                          |      |

| 6 |            |                   |                                                          |      |

|   | 6.1        |                   | tion                                                     |      |

|   | 6.2        |                   | nal Description                                          |      |

|   |            | 6.2.1<br>6.2.2    | Transmit Buffer                                          |      |

|   |            | 6.2.3             | Low-Power Exit                                           |      |

|   |            | 6.2.4             | On-Die Termination                                       |      |

|   | 6.3        | I/O Bank          | (S                                                       | . 82 |

|   | 6.4        | Simultar          | neous Switching Noise                                    | . 82 |

|   |            | 6.4.1             | GND Bounce and V <sub>DDI</sub> Bounce                   |      |

|   | 6.5        |                   | ed I/O Standards                                         |      |

|   |            | 6.5.1<br>6.5.2    | Single-Ended Standards                                   |      |

|   |            | 6.5.2<br>6.5.3    | Differential Standards                                   |      |

|   | 6.6        |                   | rammable Features                                        |      |

|   | 0.0        | 6.6.1             | Programmable Slew-Rate Control                           |      |

|   |            | 6.6.2             | Programmable Input Delay                                 | . 92 |

|   |            | 6.6.3             | Programmable Weak Pull-Up and Pull-Down                  |      |

|   |            | 6.6.4<br>6.6.5    | Programmable Schmitt Trigger Receiver                    |      |

|   |            | 6.6.6             | Programmable Pre-emphasis                                |      |

|   | 6.7        |                   | r ODT Configuration                                      |      |

|   | 0.1        | 6.7.1             | Receiver ODT Configuration for MSIO and MSIOD Banks      |      |

|   |            | 6.7.2             | Receiver ODT Configuration for DDRIO Banks               | . 98 |

|   | 6.8        | Driver In         | npedance Configuration                                   |      |

|   |            | 6.8.1             | Driver Impedance Configuration for MSIO/MSIODs           |      |

|   | 0.0        | 6.8.2             | Driver Impedance Configuration for DDRIOs                |      |

|   | 6.9        |                   | er Structure                                             |      |

|   | 6.10       |                   | Clamp Diode                                              |      |

|   | 6.11       | Low-Pov<br>6.11.1 | wer Signature Mode and Activity Mode                     |      |

|   |            | 6.11.1            | Activity Mode                                            |      |

|   | 6.12       |                   | out Tolerance in 2.5 V MSIOD/DDRIO Banks                 |      |

|   | 6.13       | -                 | t Tolerance and Output Driving Compatibility (only MSIO) |      |

|   | -          | 6.13.1            | 5 V Input Tolerance                                      |      |

|   |            |                   |                                                          |      |

|   |       |         | _                                                            |     |

|---|-------|---------|--------------------------------------------------------------|-----|

|   |       | 6.13.2  | 5 V Output Driving Compatibility                             | 108 |

|   | 6.14  | I/Os in | Conjunction with Fabric, MDDR/FDDR, and MSS/HPMS Peripherals | 108 |

|   |       | 6.14.1  | DDRIOs with MDDR/FDDR                                        |     |

|   |       | 6.14.2  | DDRIOs with Fabric                                           | 108 |

|   |       | 6.14.3  | MSIOs/MSIODs with MSS or HPMS Peripherals                    | 109 |

|   |       | 6.14.4  | MSIOs/MSIODs with Fabric                                     | 109 |

|   | 6.15  | JTAG I  | /O                                                           | 109 |

|   | 6.16  | Dedicat | ted I/O                                                      | 111 |

|   |       | 6.16.1  | Device Reset I/O                                             | 111 |

|   |       | 6.16.2  |                                                              |     |

|   |       | 6.16.3  | SerDes I/O                                                   | 112 |

| 7 | Gloss | ary     |                                                              | 113 |

|   | 7.1   | Acrony  | ms                                                           | 113 |

|   | 7.2   | Termino | ology                                                        | 115 |

|   |       |         |                                                              |     |

# **Figures**

| Figure 1               | SmartFusion2/IGLOO2 Fabric Architecture for M2S050/M2GL050                                 | 5    |

|------------------------|--------------------------------------------------------------------------------------------|------|

| Figure 2               | Functional Block Diagram of Logic Element                                                  | . 6  |

| Figure 3               | Functional Block Diagram of MSIO                                                           | 8    |

| Figure 4               | Logic Cluster Top-Level Layout                                                             | 9    |

| Figure 5               | Interface Cluster                                                                          | 9    |

| Figure 6               | Fabric Routing Structure                                                                   | . 10 |

| Figure 7               | M2S050/M2GL050 and M2S060/M2GL060 Fabric Logical Coordinates                               |      |

| Figure 8               | M2S025/M2GL025 Fabric Logical Coordinates                                                  |      |

| Figure 9               | M2S010/M2GL010 Fabric Logical Coordinates                                                  |      |

| Figure 10              | Simplified Functional Block Diagram for LSRAM                                              |      |

| Figure 11              | Data Path for Dual-Port Mode                                                               |      |

| Figure 12              | Data Path for Two-Port Mode                                                                |      |

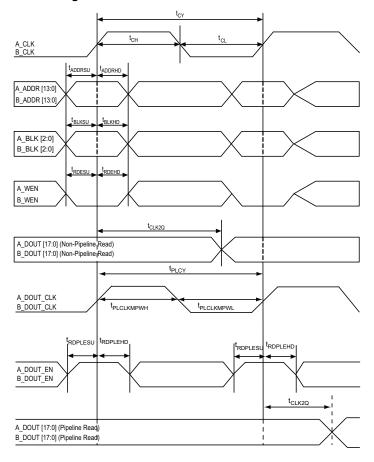

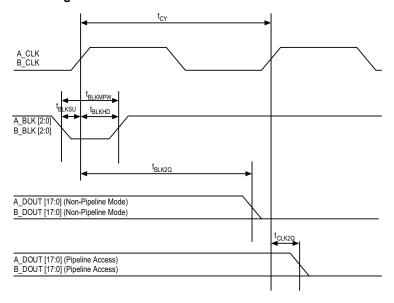

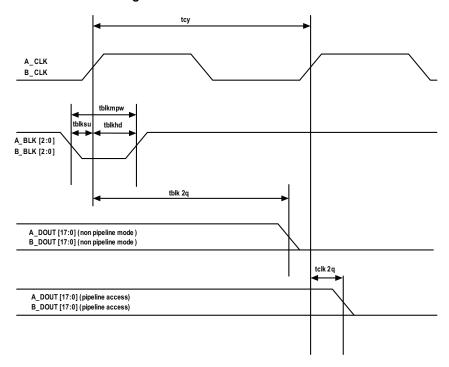

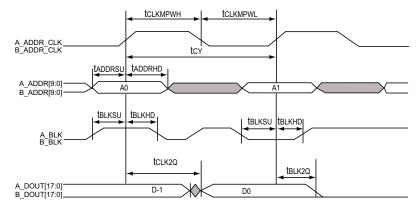

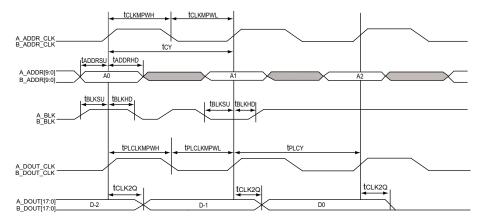

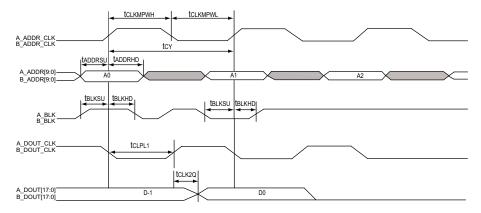

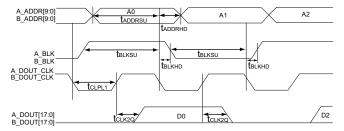

| Figure 13              | Read Operation Timing Waveforms                                                            |      |

| Figure 14              | RADDR Synchronizer                                                                         |      |

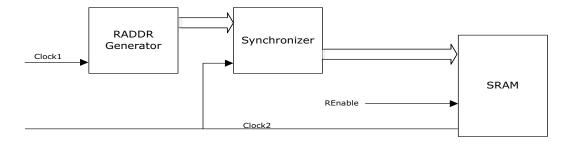

| Figure 15              | Write Operation Timing Waveforms                                                           |      |

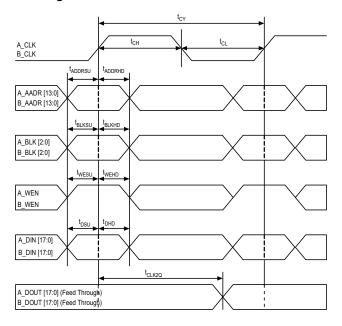

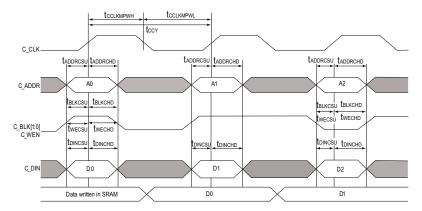

| Figure 16              | Asynchronous Reset Operation                                                               |      |

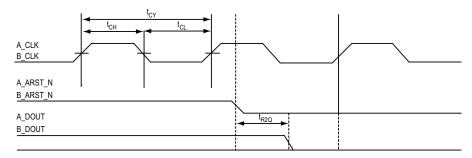

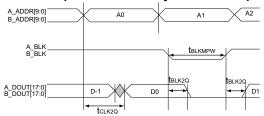

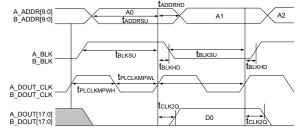

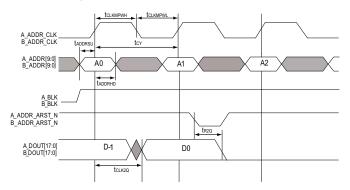

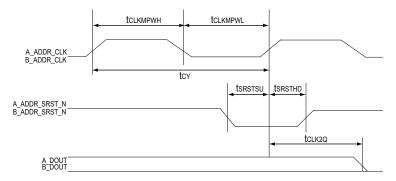

| Figure 17              | Block Select Timings                                                                       |      |

| Figure 18              | Ports of the LSRAM Configured as Dual-Port SRAM - DPSRAM Macro in Libero SoC               |      |

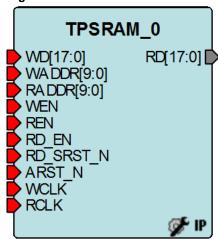

| Figure 19              | Ports of the LSRAM Configured as Two-Port SRAM - TPSRAM Macro in Libero SoC                |      |

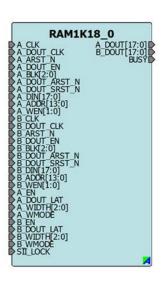

| Figure 20              | RAM1Kx18 Macro                                                                             |      |

| Figure 21              | CoreAHBLSRAM IP in Libero SoC                                                              |      |

| Figure 22              | CoreAPBLSRAM IP in Libero SoC                                                              |      |

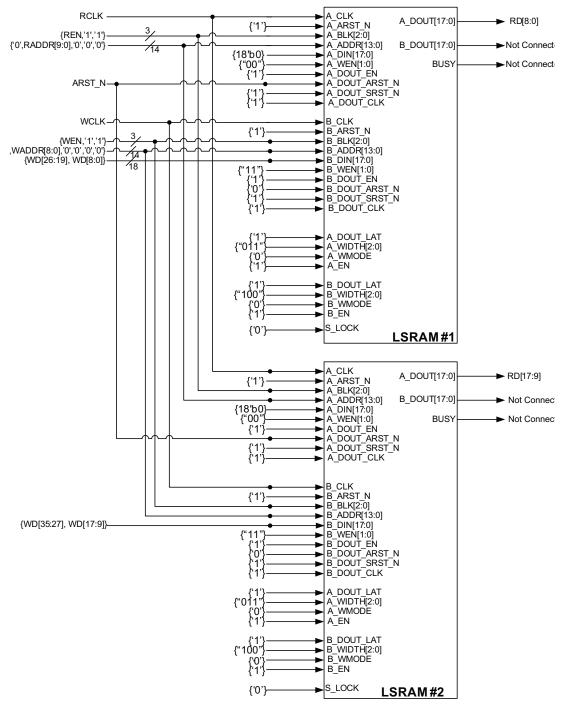

| Figure 23              | Two-Port SRAM With W36 and R18                                                             |      |

| Figure 24              | Simplified Functional Block Diagram of µSRAM                                               |      |

| Figure 25              | Timing Waveforms for Synchronous-Asynchronous Read Operation                               |      |

| Figure 26              | Timing Waveforms for Synchronous-Synchronous Read Operation                                |      |

| Figure 27              | Timing Waveforms for Synchronous Latched Read Operation                                    |      |

| Figure 28              | Timing Waveforms for Read Operations with Asynchronous Inputs Without Pipeline Registers . |      |

| Figure 29              | Timing Waveforms for Read Operations with Asynchronous Inputs with Pipeline Registers      |      |

| Figure 30              | Timing Waveforms for Read Operations with Asynchronous Inputs with Latched Outputs         |      |

| Figure 31              | Timing Waveforms for the Write Operation                                                   |      |

| Figure 32              | Timing Waveforms for Asynchronous Reset                                                    |      |

| Figure 33              | Timing Waveforms for Synchronous Reset                                                     |      |

| Figure 34              | μSRAM IP Macro in Libero SoC                                                               |      |

| Figure 35              | RAM64x18 Macro                                                                             |      |

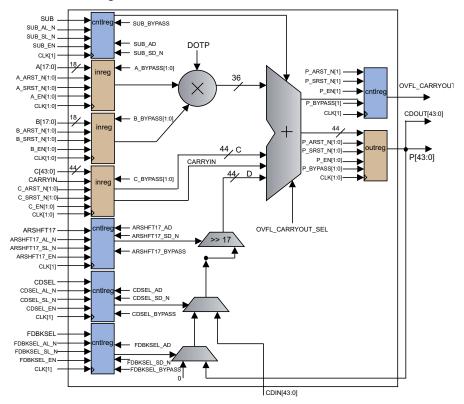

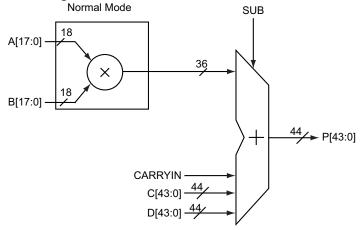

| Figure 36              | Functional Block Diagram of the Math Block                                                 |      |

| -                      | Functional Block Diagram of the Math Block in Normal Mode                                  |      |

| Figure 37<br>Figure 38 | Functional Block Diagram of the Math Block in DOTP Mode                                    |      |

| Figure 39              | Math Block Macro                                                                           |      |

| Figure 40              | Non-Pipelined 35 x 35 Multiplier                                                           |      |

| Figure 41              | Pipeline 35 x 35 Multiplier                                                                |      |

| Figure 41              | 9-Bit Complex Multiplication Using DOTP Mode                                               | 70   |

| Figure 43              | Rounding Using C-Input and CARRYIN                                                         |      |

| Figure 44              | Rounding and Trimming of the Final Sum                                                     |      |

| •                      | Rounding and Trimming of the Final Sum                                                     |      |

| Figure 45              | · ·                                                                                        |      |

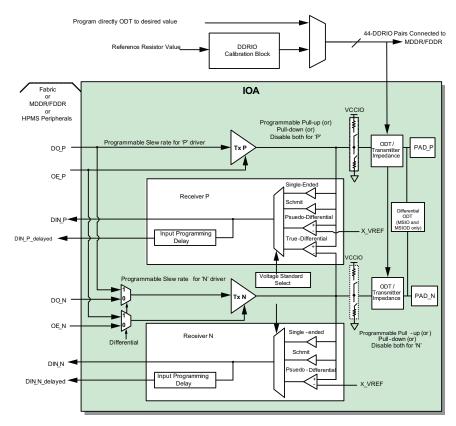

| Figure 46              | I/O Interconnection IOA Architecture                                                       |      |

| Figure 47              |                                                                                            |      |

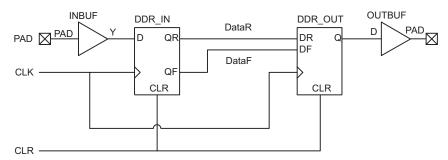

| Figure 48              | DDR Support in Low Power Flash Devices                                                     |      |

| Figure 49              | A Sample Switching Output Buffer Showing Parasitic Inductance                              |      |

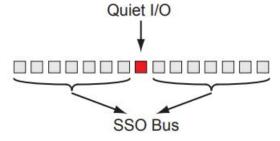

| Figure 50              | Basic Block Diagram of Quiet I/O Surrounded by SSO Bus                                     |      |

| Figure 51              | Programmable Slew-Rate                                                                     |      |

| Figure 52              | Programmable Input Delay                                                                   |      |

| Figure 53              | Programmable Weak Pull-Up and Pull-Down                                                    |      |

| Figure 54              | Programmable Schmitt Trigger Receiver                                                      | . 94 |

#### Figure 55 Programmable Pre-emphasis .......94 Figure 56 Figure 57 Figure 58 Figure 59 Figure 60 Figure 61 Figure 62 Figure 63 Figure 64

# **Tables**

| Table 1  | Fabric Resources for SmartFusion2 Devices                                  | . 5 |

|----------|----------------------------------------------------------------------------|-----|

| Table 2  | Fabric Resources for IGLOO2 Devices                                        | . 6 |

| Table 3  | Fabric Array Coordinate Systems                                            | 13  |

| Table 4  | SmartFusion2 and IGLOO2 LSRAM (18Kb Blocks) Resource Table                 | 14  |

| Table 5  | Port List for LSRAM Macro (RAM1KX18)                                       | 16  |

| Table 6  | Depth/Width Mode Selection                                                 |     |

| Table 7  | Read/Write Operation Selection                                             | 17  |

| Table 8  | Address Bus Used and Unused Bits                                           | 18  |

| Table 9  | Data Input Buses Used and Unused Bits                                      | 18  |

| Table 10 | Data Output Buses Used and Unused Bits                                     | 19  |

| Table 11 | Port Select Control Signals                                                |     |

| Table 12 | Data Width Configurations for LSRAM in Dual-Port Mode                      | 22  |

| Table 13 | Data Width Configurations for LSRAM in Two-Port Mode                       | 23  |

| Table 14 | Read Operation Timing Parameters                                           | 25  |

| Table 15 | Write Operation Timing Parameters                                          |     |

| Table 16 | Asynchronous Reset Timing Parameters                                       | 28  |

| Table 17 | Block Selection Timing Parameters                                          | 29  |

| Table 18 | Collision Operation Description                                            | 30  |

| Table 19 | Port Description for the DPSRAM Macro                                      | 31  |

| Table 20 | Port Description for the TPSRAM Macro                                      | 32  |

| Table 21 | Port Description for the CoreAPBLSRAM IP                                   | 34  |

| Table 22 | Port Description for the CoreAHBLSRAM IP                                   |     |

| Table 23 | Two-Port Configurations Requiring Two LSRAM Blocks                         | 37  |

| Table 24 | SmartFusion2 and IGLOO2 µSRAM (1Kb Blocks) Resource Table                  | 38  |

| Table 25 | Port List for µSRAM                                                        |     |

| Table 26 | Width/Depth Mode Selection                                                 |     |

| Table 27 | Address Bus Used and Unused Bits                                           |     |

| Table 28 | Data Input Buses Used and Unused Bits                                      |     |

| Table 29 | Data Output Buses Used and Unused Bits                                     | 42  |

| Table 30 | Port Select Control Signals                                                |     |

| Table 31 | Timing Parameters for Synchronous-Asynchronous Read Operation              |     |

| Table 32 | Timing Parameters for Synchronous-Synchronous Read Operation               |     |

| Table 33 | Timing Parameters for Synchronous Latched Read Operation                   |     |

| Table 34 | Timing Parameters of the Asynchronous Read Mode Without Pipeline Registers |     |

| Table 35 | Timing Parameters of the Asynchronous Read Mode with Pipeline Registers    |     |

| Table 36 | Timing Parameters of the Asynchronous Read Mode with Latched Outputs       |     |

| Table 37 | Timing Parameters of the Write Operation                                   |     |

| Table 38 | Timing Parameters of the Asynchronous Reset                                |     |

| Table 39 | Timing Parameters of the Synchronous Reset                                 |     |

| Table 40 | Collision Scenarios                                                        |     |

| Table 41 | Port Description for the µSRAM-IP Macro                                    |     |

| Table 42 | SmartFusion2 and IGLOO2 Math Blocks Resource                               |     |

| Table 43 | Truth Table for Propagating Operand D of the Adder or Accumulator          |     |

| Table 44 | Math Block Pin Descriptions                                                |     |

| Table 45 | Rounding Examples                                                          |     |

| Table 46 | MSIO SSO Guidelines for M2S010 - FG484 Device                              |     |

| Table 47 | MSIOD SSO Guidelines for M2S010 - FG484 Device                             |     |

| Table 48 | DDRIO SSO Guidelines for M2S010 - FG484 Device                             |     |

| Table 49 | MSIO, MSIOD, and DDRIO SSO Guidelines for M2S025 - FG484 Device            |     |

| Table 50 | MSIO SSO Guidelines for M2S050 - FG896 Device                              |     |

| Table 51 | MSIOD SSO Guidelines for M2S050 - FG896 Device                             |     |

| Table 52 | DDRIO SSO Guidelines for M2S050 - FG896 Device                             |     |

| Table 53 | MSIO, MSIOD, and DDRIO SSO Guidelines for M2S060 - FG676 Device            |     |

| Table 54 | MSIO, MSIOD, and DDRIO SSO Guidelines for M2S090 - FG676 Device            | 86  |

| Table 55 | MSIO, MSIOD, and DDRIO SSO Guidelines for M2S090 - FCS325 Device              | 87  |

|----------|-------------------------------------------------------------------------------|-----|

| Table 56 | MSIO, MSIOD, and DDRIO SSO Guidelines for M2S150 - FC1152 Device              | 87  |

| Table 57 | Supported I/O Standards                                                       |     |

| Table 58 | IOA Pair Design Rules                                                         | 90  |

| Table 59 | Status of the V <sub>RFF</sub> Pin Assigned Rule for IOA                      | 90  |

| Table 60 | SmartFusion2 and IGLOO2 I/O Features                                          | 9   |

| Table 61 | Programmable Slew Rate Control                                                | 92  |

| Table 62 | Programmable Weak Pull-up and Pull-down                                       | 93  |

| Table 63 | I/O Programmable Features and Standards                                       | 95  |

| Table 64 | ODT Impedance Values                                                          | 98  |

| Table 65 | ODT Configuration Options for MSIO, MSIOD, and DDRIOs                         | 99  |

| Table 66 | DDRIO ODT Configuration- for I/O Connected to Fabric                          | 100 |

| Table 67 | DDRIO ODT Configuration- for I/O Connected to DDR Controller                  |     |

| Table 68 | Driver Impedance Configurations                                               |     |

| Table 69 | Driver Impedance Configurations for MSIO/MSIODs                               |     |

| Table 70 | Driver Impedance Configurations for DDRIOs                                    | 102 |

| Table 71 | Driver Impedance Configurations for DDRIOs without DDR Controller             | 103 |

| Table 72 | F <sub>MAX</sub> , I <sub>RMS</sub> , and Max DC Voltage and Current of MSIOD | 105 |

| Table 73 | F <sub>MAX</sub> , I <sub>RMS</sub> , and Max DC Voltage and Current of DDRIO | 106 |

| Table 74 | Slew Rate Control                                                             |     |

| Table 75 | JTAG Pin Description                                                          |     |

| Table 76 | Recommended Tie-Off Values for the TCK and TRST Pins                          |     |

| Table 77 | Device Reset I/O Pin                                                          | 11′ |

| Table 78 | Crystal Oscillator I/O Pins                                                   | 111 |

## 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

## 1.1 Revision 10.0

Updated Low Voltage CMOS (LVCMOS), page 89.

## 1.2 **Revision 9.0**

The following is a summary of the changes in this revision.

- Removed Sub-LVDS related information.

- Updated to highlight that Mini-LVDS is only supported for MSIOD 2.5V, see Table 57, page 88.

- Added a note on how to set the ODT value when multiple ODT values are supported for an I/O standard, see Receiver ODT Configuration, page 96.

## 1.3 **Revision 8.0**

The following is a summary of the changes in revision 8.0 of this document.

Updated information in the note read failure violation of the Block SRAM timing. For more information see, Table 14, page 25.

## 1.4 Revision 7.0

The following is a summary of the changes in revision 7.0 of this document.

- Updated information about RADDR Synchronizer circuit. For more information see, Figure 14, page 26 and Operating Modes, page 24.

- Updated Table 64, page 98. For more information see, Receiver ODT Configuration, page 96.

- Updated recommendation for A\_BLK[1:0],B\_BLK [1:0],and C\_BLK signals. For more information see, A\_BLK[1:0], B\_BLK [1:0], and C\_BLK [1:0], page 43.

- Updated Synchronous Read Mode, page 45. For more information, see Operating Modes, page 45.

## 1.5 **Revision 6.0**

The following is a summary of the changes in revision 6.0 of this document.

- Updated SSO Guidelines to Simultaneous Switching Noise. For more information, see Simultaneous Switching Noise, page 82.

- Added a table to provide the status of the V<sub>REF</sub> pin when assigned to P-side of the pair. For more information, see Table 59, page 90.

## 1.6 **Revision 5.0**

The following is a summary of the changes in revision 5.0 of this document.

- Added 060 device information.

- Updated Figure 2, page 6. For more information, see Fabric Architecture, page 4.

- · Updated Logic Element, page 6. For more information, see Fabric Architecture, page 4.

- Added note to Two-Port Mode, page 22. For more information, see LSRAM, page 14.

- Updated A\_DOUT[17:0] and B\_DOUT[17:0], page 19 with the unconnected information. For more information, see LSRAM, page 14.

- · Updated Table 7, page 17. For more information, see LSRAM, page 14.

- Updated Table 44, page 63. For more information, see Math Blocks, page 57.

- Added Input Reference Voltage, page 89. For more information, see I/Os, page 78.

- Added 3.3 V Input Tolerance in 2.5 V MSIOD/DDRIO Banks, page 105. For more information, see I/Os, page 78.

- Added Simultaneous Switching Noise, page 82. For more information, see I/Os, page 78.

- Updated table note Table 64, page 98. For more information, see I/Os, page 78.

## 1.7 Revision 4.0

The following is a summary of the changes in revision 4.0 of this document.

- Updated Supported I/O Standards, page 88. For more information, see I/Os, page 78.

- Updated I/O Programmable Features, page 91 with ODT, Driver impedance, and other features. For more information, see I/Os, page 78.

- Updated Figure 47, page 81 for DDRIO. For more information, see I/Os, page 78.

- Added Internal Clamp Diode, page 103. For more information, see I/Os, page 78.

## 1.8 **Revision 3.0**

The following is a summary of the changes in revision 3.0 of this document.

- Merged the SmartFusion2 SoC and IGLOO2 FPGA Fabric user guide.

- Removed all instances of and references to M2GL100 device from Table 1, page 5 and Table 3, page 13. For more information, see Fabric Architecture, page 4.

- Removed all instances of and references to M2GL100 device from Table 4, page 14 and Table 3, page 13. For more information, see LSRAM, page 14.

- Removed all instances of and references to M2GL100 device from Table 24, page 38. For more information, see Micro SRAM (µSRAM), page 38.

- Removed all instances of and references to M2GL100 device from Table 42, page 57. For more information, see Math Blocks, page 57.

- Updated Table 18, page 30. For more information, see LSRAM, page 14.

- Updated Micro SRAM (µSRAM), page 38.

- Updated Math Blocks, page 57.

- Updated Introduction, page 78 and Functional Description, page 78. For more information, see I/Os, page 78.

- Updated Figure 46, page 79. For more information, see I/Os, page 78.

- Updated Table 57, page 88 and Table 60, page 91. For more information, see I/Os, page 78.

- Updated Programmable Slew-Rate Control, page 92 and Table 63, page 95. For more information, see I/Os, page 78.

- Updated Receiver ODT Configuration, page 96. For more information, see I/Os, page 78.

- Updated 5 V Input Tolerance and Output Driving Compatibility (only MSIO), page 106. For more information, see I/Os, page 78.

- Updated I/O Banks, page 82. For more information, see I/Os, page 78.

- Updated the Receive Buffer, page 80 for DDR support in low power devices. For more information, see I/Os, page 78.

- Added the Sub-LVDS information.

- Added Solution 3, page 107 for 5 V input tolerance section. For more information, see I/Os, page 78.

## 1.9 **Revision 2.0**

The following is a summary of the changes in revision 2.0 of this document.

- Updated Introduction, page 4, Architecture Overview, page 6, and Table 3, page 13. For more information, see Fabric Architecture, page 4.

- Updated Figure 36, page 58 and Coding Style Examples, page 73. For more information, see Math Blocks, page 57.

- Updated Introduction, page 78, I/O Banks, page 82, Low-Power Signature Mode and Activity Mode, page 104, Table 60, page 91, and Table 75, page 109. For more information, see I/Os, page 78.

## 1.10 Revision 1.0

The following is a summary of the changes in revision 1.0 of this document.

- Updated Figure 46, page 79, Figure 51, page 92, Figure 52, page 93. For more information, see I/Os, page 78.

- Updated B-LVDS/M-LVDS, page 91. For more information, see I/Os, page 78.

- Updated 5 V Input Tolerance and Output Driving Compatibility (only MSIO), page 106. For more information, see I/Os, page 78.

- Updated SerDes I/O Pins, page 112. For more information, see I/Os, page 78.

## 1.11 **Revision 0.0**

Revision 0.0 was the first publication of this document.

## 2 Fabric Architecture

## 2.1 Introduction

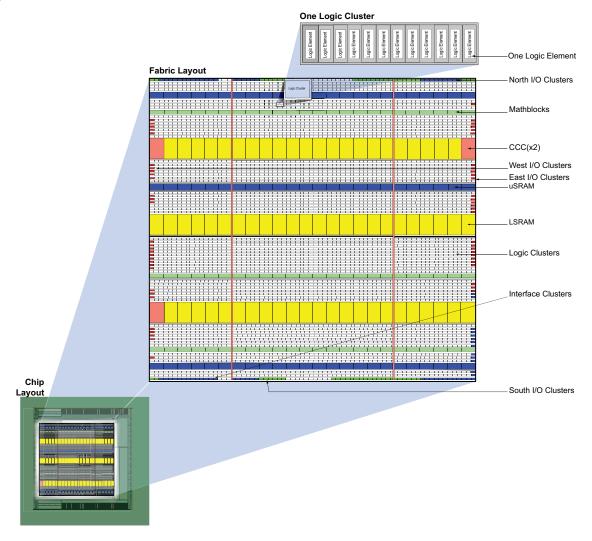

SmartFusion<sup>®</sup>2 SoC FPGA and IGLOO2 FPGA fabric comprises an array of logic blocks and embedded hard blocks such as large static random access memory (LSRAM), micro SRAM (µSRAM), and math blocks for digital signal processing (DSP) capability. These elements are arranged as several rows inside the fabric, interconnected by the clustered routing architecture of the SmartFusion2 and IGLOO2 device. Each element in the fabric has a distinct logical coordinate value assigned to it. Figure 1, page 5 shows the simple layout of the SmartFusion2 and IGLOO2 fabric architecture.

Three types of resources constitute the major part of the fabric logic blocks:

- Logic elements

- · Interface logic elements

- I/O modules

The logic element is the basic element used for implementing the combinatorial circuits, arithmetic functions, and sequential circuits inside the fabric. Each logic module consists of a 4-input LUT, a D-flip-flop, and a dedicated carry chain.

The interface logic is the logic element that interfaces the embedded hard blocks to the fabric routing. The interface logic enables the accessibility of the embedded hard block through the fabric routing. The interface logic is structurally similar to the logic element except that it does not contain the dedicated carry chain. The interface logic can also be used to implement the combinatorial and sequential circuits, if the associated embedded hard block is not being used by the design.

The I/O module forms the digital part of the fabric user I/Os, also called as multi-standard inputs/outputs (MSIOs). The I/O module enables the user I/Os to be connected to the fabric routing.

The SmartFusion2 and IGLOO2 fabric use a clustered routing architecture to interconnect the various elements of the fabric. In clustered architecture, various logic elements are grouped together to form the clusters. The SmartFusion2 and IGLOO2 fabric has three types of clusters:

- · Logic clusters

- · Interface clusters

- I/O clusters

The logic cluster is composed of 12 logic elements; the interface cluster is composed of 12 interface logic elements. I/O clusters are composed of 3 to 4 I/O modules, which are distributed on four sides of the device, as shown in the following figurer (north, south, east, and west I/O clusters).

Figure 1 • SmartFusion2/IGLOO2 Fabric Architecture for M2S050/M2GL050

## 2.2 Fabric Resources

The following tables list the fabric resources available on SmartFusion2 and IGLOO2 devices.

Table 1 • Fabric Resources for SmartFusion2 Devices

| Fabric Resource                             | M2S005 | M2S010 | M2S025 | M2S050 | M2S060 | M2S090 | M2S150  |

|---------------------------------------------|--------|--------|--------|--------|--------|--------|---------|

| Logic elements<br>(4-input LUT + Flip-Flop) | 6,060  | 12,084 | 27,696 | 56,340 | 56,520 | 86,316 | 146,124 |

| LSRAM 18K blocks                            | 10     | 21     | 31     | 69     | 69     | 109    | 236     |

| μSRAM 1K blocks                             | 11     | 22     | 34     | 72     | 72     | 112    | 240     |

| Math blocks                                 | 11     | 22     | 34     | 72     | 72     | 84     | 240     |

| PLLs and CCCs                               | 2      | 2      | 6      | 6      | 6      | 6      | 8       |

Table 2 • Fabric Resources for IGLOO2 Devices

| Fabric Resource                                 | M2GL005 | M2GL010 | M2GL025 | M2GL050 | M2GL060 | M2GL090 | M2GL150 |

|-------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|

| Logic elements<br>(4-input LUT + Flip-<br>Flop) | 6,060   | 12,084  | 27,696  | 56,340  | 56,520  | 86,316  | 146,124 |

| LSRAM 18K blocks                                | 10      | 21      | 31      | 69      | 69      | 109     | 236     |

| µSRAM 1K blocks                                 | 11      | 22      | 34      | 72      | 72      | 112     | 240     |

| Math blocks                                     | 11      | 22      | 34      | 72      | 72      | 84      | 240     |

| PLLs and CCCs                                   | 2       | 2       | 6       | 6       | 6       | 6       | 8       |

## 2.3 Architecture Overview

The following sections of this chapter describe the SmartFusion2 and IGLOO2 fabric architecture in detail.

- · Logic Element

- · Interface Logic Element

- I/O Module

- · FPGA Routing Architecture

## 2.3.1 Logic Element

The logic elements can be used as a combinational logic element (CLE), and/or sequential logic element (SLE) in the design. Each logic element consists of:

- A 4-input LUT

- A dedicated carry chain based on the carry look-ahead technique

- · A separate flip-flop which can be used independently from the LUT

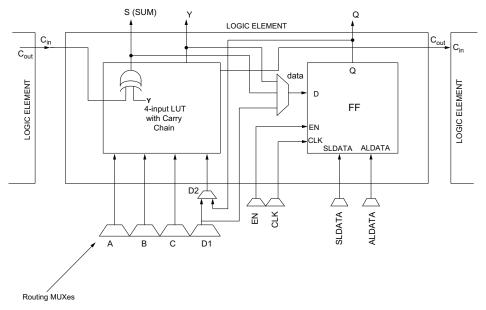

The following illustration shows the functional block diagram of the logic element with carry chain.

Figure 2 • Functional Block Diagram of Logic Element

The 4-input LUT can be configured to implement any 4-input combinatorial function or to implement an arithmetic function, where the LUT output is XORed with carry input (Cin) to generate the sum (S) output. The sum output, S, is typically used as an output for arithmetic functions but can also be used as an output for logical functions along with the other output, Y, when the LUT is used to implement combinatorial functions.

Each logic element has a dedicated 3-bit look-ahead carry implementation, which is used to implement a dedicated carry chain between the logic elements when the LUT is used to implement arithmetic operations.

The carry chain has hardwired routing nets running between the logic elements, which reduces the carry propagation delay through the carry chain, thus giving better performance. The logic element also contains a dedicated flip-flop, which can be used in conjunction with or independently from the LUT. The flip-flop can be configured as a register or latch. It has asynchronous and synchronous load and clock enable inputs. Asynchronous load signal (ALDATA) can be used as asynchronous set or reset signal of each fabric D flip-flops. It sets or resets the register depending on configuration. Synchronous load signal (SLDATA) can be used as synchronous set or reset signal of each fabric D flip-flop. It sets or resets the register depending on configuration. The data input of the flip-flop can be fed from the direct input (D1) or from the outputs of the 4-input LUT inside the logic element.

## 2.3.2 Interface Logic Element

Embedded hard blocks (LSRAM blocks, µSRAM blocks, and math blocks) contain a dedicated interface logic. The embedded hard blocks are connected to the fabric routing structure through LUTs and flip-flops on their inputs and outputs, and these together form the interface logic element.

Each embedded hard block is associated with 36 interface logic elements. This interface logic element is structurally equivalent to a logic element but does not have a dedicated carry chain. When a given embedded hard block is used by the target design, the interface logic is used to connect the embedded hard block's I/Os to the fabric routing. If an embedded hard block is not used by the design, the interface logic element is available for use as a normal logic elements for implementing combinatorial and sequential circuits. These are in addition to the logic elements available in the fabric.

#### **2.3.3 I/O Module**

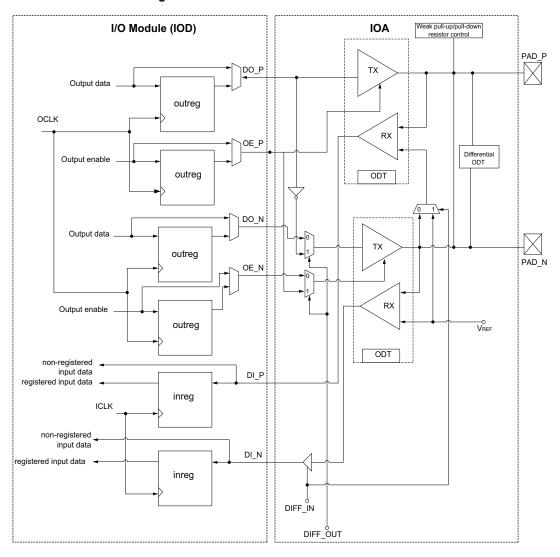

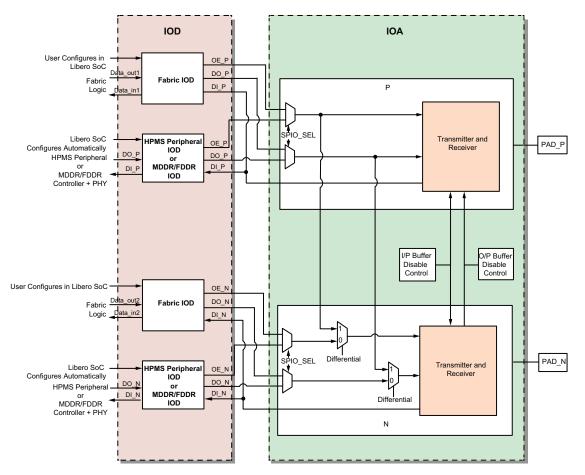

The I/O module includes the I/O digital (IOD) circuitry and the associated routing interface. Each user I/O pad is connected to its own dedicated I/O module. The I/O module interfaces the user I/Os with the fabric routing and enables the routing of external signals coming in through the I/Os to reach all the logic elements. The I/O modules also enable the internal signals to reach the I/Os.

The following illustration shows the functional diagram of the complete MSIO with the IOD and I/O analog (IOA) sections. The IOD consists of the input registers, output registers, output enable registers, and routing multiplexers (MUXes). The output register provides the registered version of the output signals to the I/Os. In the same way, the input registers are used to register the inputs received from the I/Os. The output enable acts as a control signal for the output, if the I/O is configured as a tristated or bidirectional I/O. These registers in the I/O modules are similar to the D-flip-flops available in the logic element. The usage of the output registers in the I/O modules for registering the output signals at I/Os enables better design performance. Also, in the case of a signal bus, these registers ensure that all the bits of the signal bus are synchronized to the clock signal when being sent out through the I/Os. At the input side, the input registers allow capturing the input signals and synchronizing them to the design clock.

Figure 3 • Functional Block Diagram of MSIO

## 2.3.4 FPGA Routing Architecture

The SmartFusion2 and IGLOO2 fabric has a clustered routing architecture. Clustering is a hierarchical grouping of fabric resources that allows a more area-efficient implementation of designs while maintaining optimal performance. It also helps in reducing the run-time of the place-and-route software.

The SmartFusion2 and IGLOO2 fabric routing architecture is composed of three types of clusters:

- Logic Cluster

- Interface Cluster

- I/O Cluster

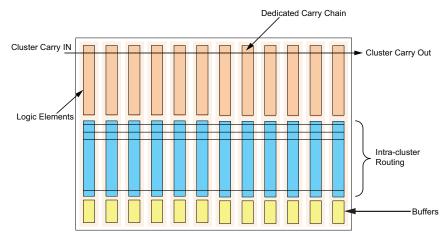

## 2.3.4.1 Logic Cluster

The logic cluster is a combination of 12 logic elements with a dedicated hardwired carry chain implemented for all 12 logic elements. The logic clusters contain routing MUXes. Each routed signal is driven by a unique logic element output or routing MUX. All the logic elements are interconnected with feedback from outputs to inputs. The intra-routing inside the logic clusters has a very low propagation delay as compared to the routing outside the logic clusters.

Each LUT, D-flip-flop, and the carry-circuit in the logic cluster have an individual X-Y logical coordinate assigned, and this makes them independently addressable. The following illustration shows the top-level logic cluster layout diagram.

Figure 4 • Logic Cluster Top-Level Layout

#### 2.3.4.2 Interface Cluster

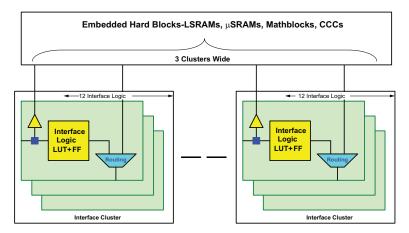

The interface cluster is similar to the logic cluster except that it is a combination of 12 interface logic elements. These clusters are used to interface the inputs and outputs of the embedded hard blocks (LSRAM, µSRAM, math blocks, and CCCs) to fabric routing. Each embedded hard block is spanned by 3 interface clusters, as shown in the following figure. The interface logic can be used as a logic elements (without carry chain) when the associated embedded hard block is not used by the design.

Figure 5 • Interface Cluster

#### 2.3.4.3 I/O Cluster

I/O clusters are combinations of I/O modules and the associated routing interfaces. The north and south I/O clusters each contain four I/O modules. The east and west I/O clusters, each contain three I/O modules. Each I/O pad is associated with its own dedicated I/O module.

#### 2.3.4.4 Routing Structure

The routing of any design is completed automatically by the software, thus, the utilization of the routing resources is completely transparent to the user. The selection among various routing resources by the placement-and-routing software is impacted by the design constraints provided. For more details on how to use the constraints using Libero SoC software, see *SmartTime User Guide*, *I/O Editor User Guide*, and *ChipPlanner User Guide* on the *Libero SoC Documentation* page.

Knowledge of the routing architecture and functional modules can be useful in providing effective design constraints to the software, so that it can be guided to do an optimal design implementation on the SmartFusion2 and IGLOO2 fabric.

In the SmartFusion2 and IGLOO2 device, the fabric routing is segregated into two parts:

- Inter-cluster routing

- Intra-cluster routing

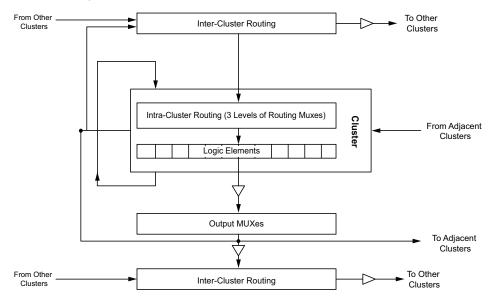

The following illustration shows the fabric routing structure for the SmartFusion2 and IGLOO2 device.

Figure 6 • Fabric Routing Structure

Inter-cluster routing spans the clusters and connects them together. The inter-cluster routing resource is common to all the clusters inside the fabric and is universal across the clusters.

Intra-cluster routing spans the modules that constitute a cluster. Intra-cluster routing is not unique and varies from cluster to cluster, depending upon the functionality of the cluster. For example, the intra-cluster routing for an interface cluster is different from that of a logic cluster. There are differences in the routing of the various interface clusters, depending upon the embedded hard block to which they interface.

Inter-cluster routing and intra-cluster routing are completely separate. Inter-cluster routing never drives the inputs of the functional modules (logic elements, interface logic elements, or I/O modules) directly and the outputs of the functional modules do not drive the inter-cluster routing directly. Inter-cluster routing has to pass through the intra-cluster routing to reach the functional modules. That makes SmartFusion2 and IGLOO2 routing a fully clustered routing architecture.

The global network can also drive intra-cluster routing through special routing MUXes. These global routing MUXes bring in flip-flop control signals such as clock, enable, and sets/resets.

There are a few short routing lines between the adjacent clusters and between the inter-cluster and intracluster routing MUXes. These short paths are provided to provide better performance to the signals routed through these lines.

## 2.4 Fabric Array Coordinate System

Every element in the SmartFusion2 and IGLOO2 fabric has individual logical X-Y coordinates associated with the fabric array coordinate system. These logical coordinates are used by the place-and-route software while implementing the design using the fabric elements. The place-and-route software can be constrained to occupy the design components in specific locations inside the fabric using this coordinate system. Regions can be created inside the fabric and a particular part of the design can be assigned to that region using the Libero SoC floor-planner software.

The boundaries of these regions can be specified using the array coordinates. Similarly, the embedded hard block is also addressable through the fabric coordinate system.

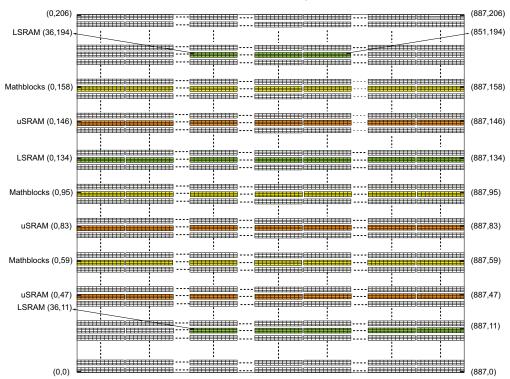

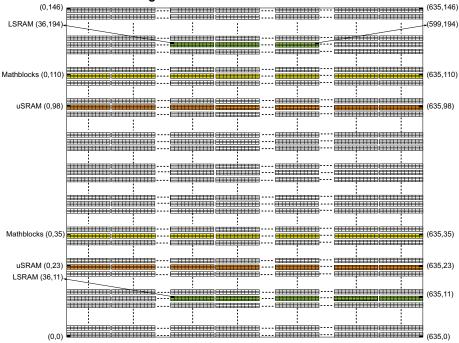

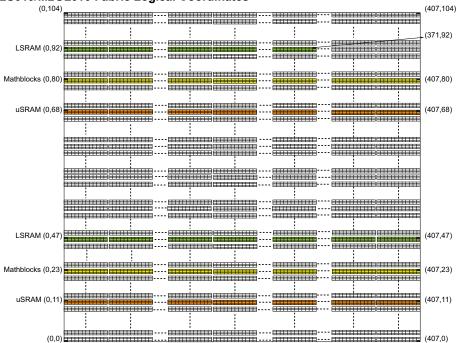

The array coordinates are measured from the bottom-left corner to the top-right corner of the FPGA fabric. Table 3, page 13 provides the array coordinates of logical modules and embedded hard blocks of SmartFusion2 and IGLOO2 devices. Figure 7, page 11, Figure 8, page 12, and Figure 9, page 12 show the array coordinates of an M2S050/M2GL050, M2S060/M2GL060, M2S025/M2GL025, and M2S010/M2GL010 devices. For more information on how to use array coordinates for region/placement constraints, see *Libero SoC Design Flow User Guide* or online help (available in the software) for SmartFusion2 and IGLOO2 Libero SoC tools.

Figure 7 • M2S050/M2GL050 and M2S060/M2GL060 Fabric Logical Coordinates

Figure 8 • M2S025/M2GL025 Fabric Logical Coordinates

Figure 9 • M2S010/M2GL010 Fabric Logical Coordinates

Table 3 • Fabric Array Coordinate Systems

|                   | Logi | c Ele | ments |     | μSRAM              | •                    |                      | LSRAM               |                      | •                        | Math Bl            | ocks                 |                      |

|-------------------|------|-------|-------|-----|--------------------|----------------------|----------------------|---------------------|----------------------|--------------------------|--------------------|----------------------|----------------------|

|                   | Min  |       | Max   |     | Bottom             | Middle               | Тор                  | Bottom              | Middle               | Тор                      | Bottom             | Middle               | Тор                  |

| Device            | X    | Υ     | X     | Υ   | (X,Y)              | (X,Y)                | (X,Y)                | (X,Y)               | (X,Y)                | (X,Y)                    | (X,Y)              | (X,Y)                | (X,Y)                |

| M2S005<br>M2GL005 | 0    | 0     | 407   | 56  | NA                 | NA                   | (0,11)               | NA                  | NA                   | (0,44)                   | NA                 | NA                   | (0,23)               |

| M2S010<br>M2GL010 | 0    | 0     | 407   | 104 | (0,11)             | NA                   | (0,68)               | (0,47)              | NA                   | (0,92)                   | (0,23)             | NA                   | (0,80)               |

| M2S025<br>M2GL025 | 0    | 0     | 635   | 146 | (0,23)             | NA                   | (0,98)               | (36,11)             | NA                   | (36,134                  | (0,35)             | NA                   | (0,110)              |

| M2S050<br>M2GL050 | 0    | 0     | 887   | 206 | (0,47)             | (0,83)               | (0,146)              | (36,11)             | (0,134)              | (36,194                  | (0,59)             | (0,95)               | (0,158)              |

| M2S060<br>M2GL060 | 0    | 0     | 887   | 206 | (0,47)             | (0,83)               | (0,146)              | (36,11)             | (0,134)              | (36,194                  | (0,59)             | (0,95)               | (0,158)              |

| M2S090<br>M2GL090 | 0    | 0     | 1031  | 266 | (0, 23)            | (0, 59)<br>(0, 194)  | (0, 242)             | (36, 11)            | (0, 119)<br>(0, 170) | (36,<br>254)             | (0, 35)            | (0, 71)              | (0, 206)             |

| M2S150<br>M2GL150 | 0    | 0     | 1463  | 314 | (0, 35)<br>(0, 59) | (0, 107)<br>(0, 182) | (0, 230)<br>(0, 278) | (36, 11)<br>(0, 95) | (0, 143)<br>(0, 218) | (0, 266)<br>(36,<br>302) | (0, 47)<br>(0, 71) | (0, 119)<br>(0, 194) | (0, 242)<br>(0, 290) |

## 3 LSRAM

## 3.1 Introduction

The SmartFusion2 and IGLOO2 fabric has embedded 18 Kbit SRAM blocks used for storing data. These large SRAM blocks (LSRAMs) are arranged in multiple rows within the FPGA fabric and can be accessed through the fabric routing architecture. The number of LSRAM blocks available depends upon the specific SmartFusion2 and IGLOO2 device, as shown in the following table. For example, in the M2S050 or M2GL050 device, there are 69 LSRAM blocks available, which are spread across three rows inside the fabric.

## 3.1.1 Features

The SmartFusion2 and IGLOO2 LSRAM blocks have the following features:

- Each LSRAM block can store up to 18,432 bits of data and can be configured in any of the following depth x width combinations: 512 x 36, 512 x 32, 1k x 18, 1k x 16, 2k x 9, 2k x 8, 4k x 4, 8k x 2, or 16k x 1.

- Each LSRAM block contains two independent data ports—Port A and Port B.

- The LSRAM is synchronous for both read and write operations. These operations are triggered on the rising edge of the clock.

- Supports maximum frequency up to 400 MHz.

- · An optional pipeline register is available at the read data port to improve the clock-to-out delay.

- LSRAM supports two types of read operations:

- Flow-through read (or non-pipelined)

- Pipelined read

- LSRAM supports two types of write operations:

- Simple write

- Feed-through write (write-bypass write)

- LSRAM can be operated in two memory modes:

- Dual-port mode

- Two-port mode

- A write operation requires one clock cycle.

- A read operation requires one clock cycle in Non-pipelined mode. In Pipelined mode, the output data appears in the next cycle.

- Read from both ports at the same location is allowed.

- Read and write on the same location at the same time is not allowed. There is no built in collision prevention or detection circuit in LSRAM.

## 3.2 LSRAM Resources

The following table lists LSRAM rows and 18K blocks available in SmartFusion2 and IGLOO2 devices.

Table 4 • SmartFusion2 and IGLOO2 LSRAM (18Kb Blocks) Resource Table

| Device            | M2S005/<br>M2GL005 | M2S010/<br>M2GL010 | M2S025/<br>M2GL025 | M2S050/<br>M2GL050 | M2S060/<br>M2GL060 | M2S090/<br>M2GL090 | M2S150/<br>M2GL150 |

|-------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| Rows              | 1                  | 2                  | 2                  | 3                  | 3                  | 4                  | 6                  |

| LSRAM 18 K Blocks | 10                 | 21                 | 31                 | 69                 | 69                 | 109                | 236                |

Note: All numbers given above are per device.

## 3.3 Functional Description

This section provides the detailed description of the following:

- Architecture Overview

- Port List

- · Port Descriptions

**Architecture Overview**

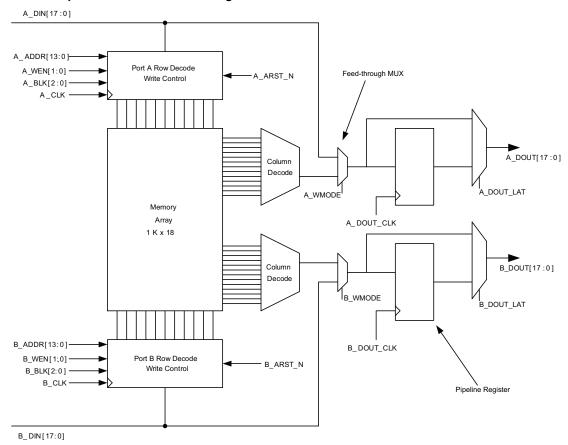

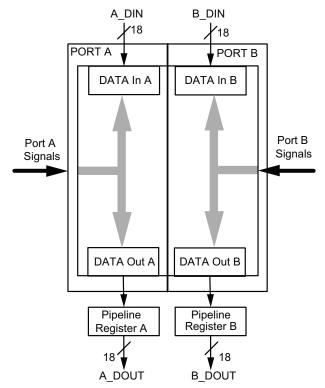

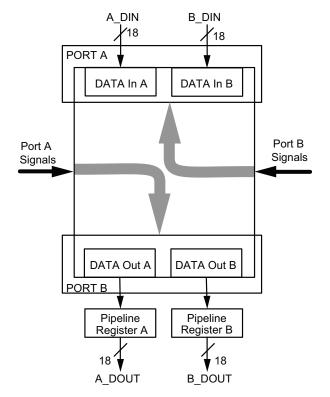

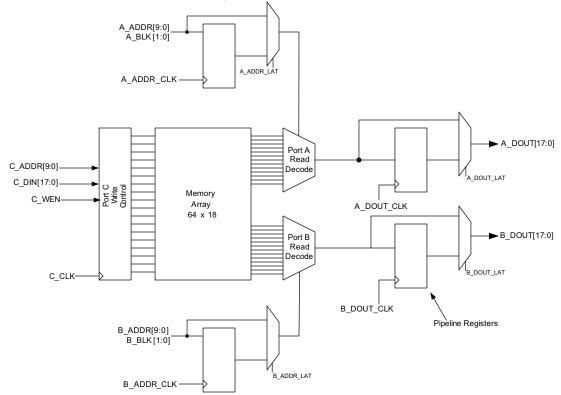

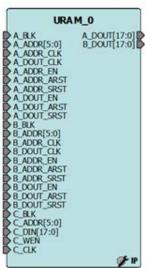

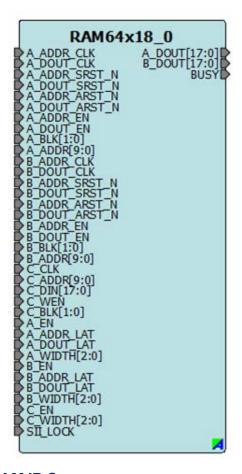

SmartFusion2 and IGLOO2 LSRAM embedded memory includes the RAM1Kx18 macro. The following illustration shows a simplified block diagram of the LSRAM memory block and Table 5, page 16 provides the port descriptions. The following illustration shows two independent data ports, the pipeline registers for read data delay, and the feed-through multiplexers to enable immediate access to the write data.

Figure 10 • Simplified Functional Block Diagram for LSRAM

## 3.3.1 Port List

Table 5 • Port List for LSRAM Macro (RAM1KX18)

| Port Name               | Direction | Type <sup>1</sup> | Polarity | Description                                 |

|-------------------------|-----------|-------------------|----------|---------------------------------------------|

| PORT A                  |           |                   |          |                                             |

| A_WIDTH[2:0]            | Input     | Static            |          | Port A Width/depth mode select              |

| A_WEN[1:0]2             | Input     | Dynamic           | High     | Port A Write enable                         |

| A_ADDR[13:0]            | Input     | Dynamic           |          | Port A Address input                        |

| A_DIN[17:0]             | Input     | Dynamic           |          | Port A Data input                           |

| A_DOUT[17:0]            | Output    | Dynamic           |          | Port A Data output                          |

| A_BLK[2:0]              | Input     | Dynamic           | High     | Port A Block select                         |

| A_WMODE                 | Input     | Static            | High     | Port A Feed-through write select            |

| A_CLK                   | Input     | Dynamic           | Rising   | Port A Clock                                |

| A_ARST_N                | Input     | Dynamic           | Low      | Port A Asynchronous reset                   |

| A_DOUT_CLK              | Input     | Dynamic           | Rising   | Port A Pipeline register clock              |

| A_DOUT_LAT              | Input     | Static            | Low      | Port A Pipeline register Select             |

| A_DOUT_ARST_N           | Input     | Dynamic           | Low      | Port A Pipeline register asynchronous reset |

| A_DOUT_EN               | Input     | Dynamic           | High     | Port A Pipeline register enable             |

| A_DOUT_SRST_N           | Input     | Dynamic           | Low      | Port A Pipeline register synchronous reset  |

| PORT B                  |           |                   |          |                                             |

| B_WIDTH[2:0]            | Input     | Static            |          | Port B Width/depth mode select              |

| B_WEN[1:0] <sup>2</sup> | Input     | Dynamic           | High     | Port B Write enable                         |

| B_ADDR[13:0]            | Input     | Dynamic           |          | Port B Address input                        |

| B_DIN[17:0]             | Input     | Dynamic           |          | Port B Data input                           |

| B_DOUT[17:0]            | Output    | Dynamic           |          | Port B Data output                          |

| B_BLK[2:0]              | Input     | Dynamic           | High     | Port B Block select                         |

| B_WMODE                 | Input     | Static            | High     | Port B Feed-through write select            |

| B_CLK                   | Input     | Dynamic           | Rising   | Port B Clock                                |

| B_ARST_N                | Input     | Dynamic           | Low      | Port B Asynchronous reset                   |

| B_DOUT_CLK              | Input     | Dynamic           | Rising   | Port B Pipeline register clock              |

| B_DOUT_LAT              | Input     | Static            | Low      | Port B Pipeline register select             |

| B_DOUT_ARST_N           | Input     | Dynamic           | Low      | Port B Pipeline register asynchronous reset |

| B_DOUT_EN               | Input     | Dynamic           | High     | Port B Pipeline register enable             |

| B_DOUT_SRST_N           | Input     | Dynamic           | Low      | Port B Pipeline register synchronous reset  |

| Common Signals          |           |                   |          |                                             |

| A_EN                    | Input     | Static            | Low      | Port A power-down                           |

| B_EN                    | Input     | Static            | Low      | Port B power-down                           |

| SII_LOCK                | Input     | Static            | High     | Lock access to SII                          |

| BUSY                    | Output    | Dynamic           | High     | Busy signal from SII                        |

<sup>1.</sup> Static inputs are defined at design time and can be or are controlled by flash configuration bits.

2. If LSRAM is configured in two-port mode with a write data width of x36/x32 and read data width of x36/x32, both the bits of A\_WEN and B\_WEN must be tied to logic 1 and should not be dynamically changed.

## 3.3.2 Port Descriptions

## 3.3.2.1 A\_WIDTH[2:0] and B\_WIDTH[2:0]

These signals represent the depth x width mode selections for each port. The following table shows the depth x width based on ports width selection.

Table 6 • Depth/Width Mode Selection

| A_WIDTH/B_WIDTH                 | Depth/Width          |

|---------------------------------|----------------------|

| 000                             | 16K x 1              |

| 001                             | 8K x 2               |

| 010                             | 4k x 4               |

| 011                             | 2K x 9<br>2K x 8     |

| 100                             | 1K x 18<br>1K x 16   |

| 101<br>110<br>111<br>(Two-port) | 512 x 36<br>512 x 32 |

## 3.3.2.2 A\_WEN[1:0] and B\_WEN[1:0]

These signals represent the write enables for each port to select read/write operations. The following table shows the depth x width operations based on port write enable selection.

Table 7 • Read/Write Operation Selection<sup>1, 2</sup>

| Depth x Width           | A_WEN/B_WEN       | Operation    |

|-------------------------|-------------------|--------------|

| 16K x 1                 | 00                | Read         |

| 8K x 2                  |                   | operation    |

| 4K x 4                  |                   |              |

| 2K x 8                  |                   |              |

| 2K x 9                  |                   |              |

| 1K x 16                 |                   |              |

| 1K x 18                 |                   |              |

| 16K x 1                 | 1                 | Write        |

| 8K x 2                  |                   | operation    |

| 4K x 4                  |                   |              |

| 2K x 8                  |                   |              |

| 2K x 9                  |                   |              |

| 1K x 16                 |                   |              |

| 1K x 18                 |                   |              |

| 512 x 32                | A_WEN[1:0] = "11" | Write [31:0] |

| (Two-port write-Port B) | B_WEN[1:0] = "11" |              |

| 512 x 36                | B_WEN[1:0] = "11" | Write [35:0] |

| (Two-port write-Port B) | A_WEN[1:0] = "11" |              |

In dual-port mode, every port reads when the corresponding write enable (A\_WEN/B\_WEN) is "00" and corresponding port select (A BLK/B BLK) is active.

In two-port mode, the read port (Port A) reads in every clock cycle if A BLK is active.

## 3.3.2.3 A\_ADDR[13:0] and B\_ADDR[13:0]

These signals represent the address buses for the two ports. In x1 mode 14 bits are used to address the 16,384 independent locations. In wider modes (x2, x4, etc.) fewer address bits are used. The used address bits are the most significant bits (MSB). The unused bits are the least significant bits (LSBs) and they must be grounded. The following table shows the address bus used and unused bits for depth x width selections.

Table 8 • Address Bus Used and Unused Bits

|                    | A_ADDR/B_ADDR |                              |

|--------------------|---------------|------------------------------|

| Depth x Width      | Used Bits     | Unused bits (to be grounded) |

| 16K x 1            | [13:0]        | None                         |

| 8K x 2             | [13:1]        | [0]                          |

| 4K x 4             | [13:2]        | [1:0]                        |

| 2K x 9<br>2K x 8   | [13:3]        | [2:0]                        |

| 1K x 18<br>1K x 16 | [13:4]        | [3:0]                        |

| 512 x 36           | [13:5]        | [4:0]                        |

## 3.3.2.4 A\_DIN[17:0] and B\_DIN[17:0]

These signals represent the data input buses for the two ports. In dual-port mode, the data width can range from 1 bit to 18 bits. In two-port mode, Port B becomes the write-only port. Giving a write data width of 36 bits, A\_DIN[17:0] becomes write data[35:18] and B\_DIN[17:0] becomes write data[17:0]. The used bits for any mode are LSB justified in the data bus and the unused MSB bits must be grounded. The following table shows the data input buses used and unused bits for depth x width selections.

Table 9 • Data Input Buses Used and Unused Bits

| Depth x Width | A_DIN/B_DIN                                                                                     |                                                |

|---------------|-------------------------------------------------------------------------------------------------|------------------------------------------------|

|               | Used Bits                                                                                       | Unused bits (to be grounded)                   |

| 16K x 1       | [0]                                                                                             | [17:1]                                         |

| 8K x 2        | [1:0]                                                                                           | [17:2]                                         |

| 4K x 4        | [3:0]                                                                                           | [17:4]                                         |

| 2K x 8        | [7:0]                                                                                           | [17:8]                                         |

| 2K x 9        | [8:0]                                                                                           | [17:9]                                         |

| 1K x 16       | [16:9] is [15:8]<br>[7:0] is [7:0]                                                              | [17]<br>[8]                                    |

| 1K x 18       | [17:0]                                                                                          | None                                           |

| 512 x 32      | A_DIN[16:9] is [31:24]<br>A_DIN[7:0] is [23:16]<br>B_DIN[16:9] is [15:8]<br>B_DIN[7:0] is [7:0] | A_DIN[17]<br>A_DIN[8]<br>B_DIN[17]<br>B_DIN[8] |

| 512 x 36      | A_DIN[17:0] is [35:18]<br>B_DIN[17:0] is [17:0]                                                 | None                                           |

## 3.3.2.5 A\_DOUT[17:0] and B\_DOUT[17:0]

These signals represent the data output buses for the two ports. In dual-port mode, the data width can range from 1 bit to 18 bits. In two-port mode, Port A becomes the read-only port. Giving a read data width of 36 bits, A\_DOUT[17:0] becomes read data[35:18] and B\_DOUT[17:0] becomes read data[17:0]. The used bits for any mode are LSB justified in the data bus and the unused MSB bits must be unconnected. The following table shows the data output buses used and unused bits for depth x width selections.

Table 10 · Data Output Buses Used and Unused Bits

|               | A_DOUT/B_DOUT                                                                                       |                                                    |  |

|---------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------|--|

| Depth x Width | Used Bits                                                                                           | Unused bits (unconnected)                          |  |

| 16K x 1       | [0]                                                                                                 | [17:1]                                             |  |

| 8K x 2        | [1:0]                                                                                               | [17:2]                                             |  |

| 4K x 4        | [3:0]                                                                                               | [17:4]                                             |  |

| 2K x 8        | [7:0]                                                                                               | [17:8]                                             |  |

| 2K x 9        | [8:0]                                                                                               | [17:9]                                             |  |

| 1K x 16       | [16:9] is [15:8]<br>[7:0] is [7:0]                                                                  | [17]<br>[8]                                        |  |

| 1K x 18       | [17:0]                                                                                              | None                                               |  |

| 512 x 32      | A_DOUT[16:9] is [31:24]<br>A_DOUT[7:0] is [23:16]<br>B_DOUT[16:9] is [15:8]<br>B_DOUT[7:0] is [7:0] | A_DOUT[17]<br>A_DOUT[8]<br>B_DOUT[17]<br>B_DOUT[8] |  |

| 512 x 36      | A_DOUT[17:0] is [35:18]<br>B_DOUT[17:0] is [17:0]                                                   | None                                               |  |

|               | ·                                                                                                   | ·                                                  |  |

## 3.3.2.6 A\_BLK[2:0] and B\_BLK[2:0]

These signals represent the port select control signals for each port. The following table shows operations (Read, Write, and No operation) based on selection of port select control signals.

Table 11 • Port Select Control Signals

| Port Select Signal | Value | Result                                                                  |

|--------------------|-------|-------------------------------------------------------------------------|

| A_BLK[2:0]         | 111   | Perform read or write operation on Port A.                              |

| A_BLK[2:0]         | 000   | No operation in memory from Port A. Port A output is forced to logic 0. |

|                    | 001   |                                                                         |

|                    | 010   |                                                                         |

|                    | 011   |                                                                         |

|                    | 100   |                                                                         |

|                    | 101   |                                                                         |

|                    | 110   |                                                                         |

| B_BLK[2:0]         | 111   | Perform read or write operation on Port B.                              |

| B BLK[2:0]         | 000   | No operation in memory from Port B. Port B output is forced to logic 0. |

|                    | 001   |                                                                         |

|                    | 010   |                                                                         |

|                    | 011   |                                                                         |

|                    | 100   |                                                                         |

|                    | 101   |                                                                         |

|                    | 110   |                                                                         |

## 3.3.2.7 A WMODE and B WMODE

These signals represent the Write mode control signals for Port A and Port B.

- Logic 0: Output data port holds the previous value.

- Logic 1: Feed-through; write data appears on the corresponding output data port. In two-port mode, feed-through write is not supported.

#### 3.3.2.8 A CLK and B CLK

These signals represent the clock inputs for Port A and Port B. All inputs must be set up before the rising edge of the clock. The read or write operation begins with the rising edge.

#### 3.3.2.9 A\_ARST\_N and B\_ARST\_N

These signals represent Active Low, asynchronous reset inputs for Port A and Port B. Assertion of these resets during read operation forces the data output lines to logic 0. Assertion of these resets during write operation results in garbage values written into the memory.

## 3.3.2.10 A DOUT ARST N and B DOUT ARST N

These signals represent Active Low, asynchronous reset inputs for the output pipeline registers for Port A and Port B. Assertion of these reset signals forces the data output to logic 0. In Non-pipelined mode, these inputs should be tied to logic 1.

## 3.3.2.11 A\_DOUT\_LAT and B\_DOUT\_LAT

These signals represent Latch mode inputs for the output pipeline registers for Port A and Port B.

- Logic 0: Register operation

- · Logic 1: Latch operation

#### 3.3.2.12 A\_DOUT\_EN and B\_DOUT\_EN

These signals represent Active High; enable inputs for the output pipeline registers for Port A and Port B.

- Logic 1: Normal register operation

- · Logic 0: Register holds previous data

#### 3.3.2.13 A DOUT SRST N and B DOUT SRST N

These signals represent Active Low, synchronous reset inputs for the output pipeline registers for Port A and Port B. Assertion of these reset signals forces the data output to logic 0. In Non-pipelined mode, these inputs should be tied to logic 1.

#### 3.3.2.14 A EN and B EN

These are Active Low, power-down configuration bits for each port.

#### 3.3.2.15 SII LOCK

This control signal, when asserted to logic 1, locks the entire LSRAM memory for being accessed by the system controller interface bus (SII). The system controller can access the LSRAM for the following purposes:

- Testing the memory

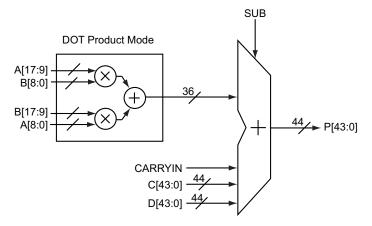

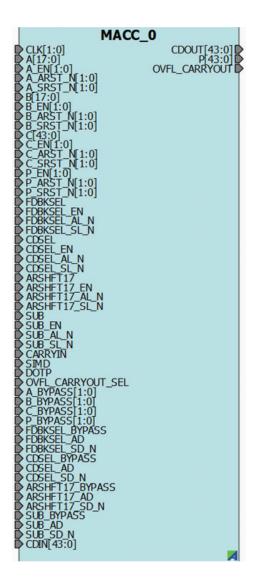

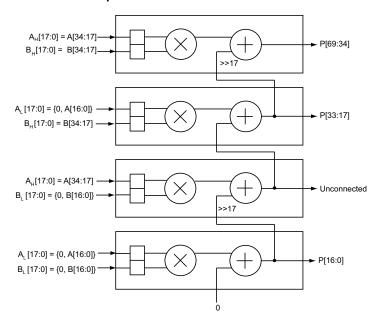

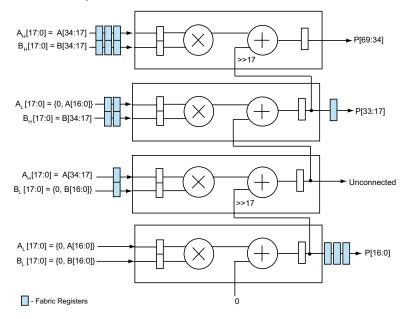

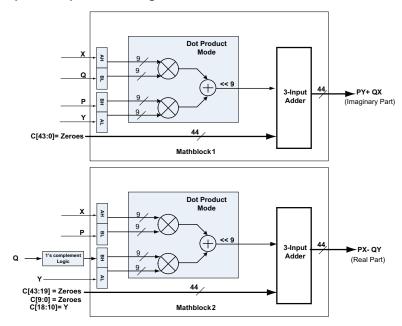

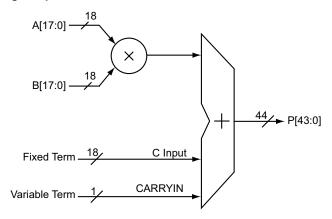

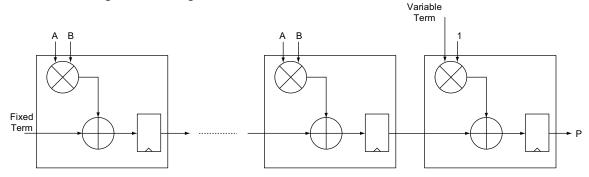

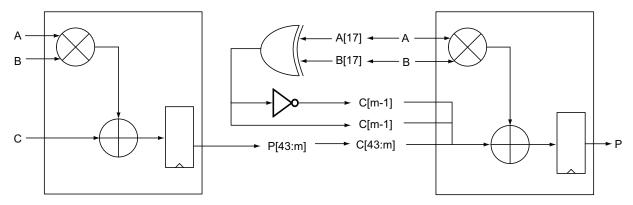

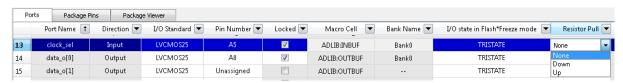

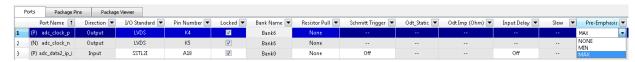

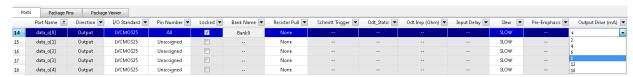

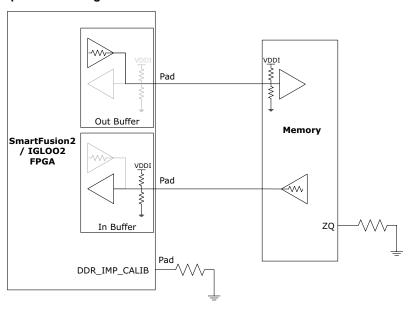

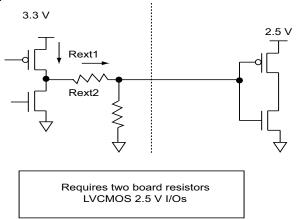

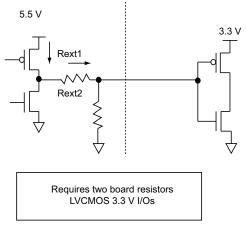

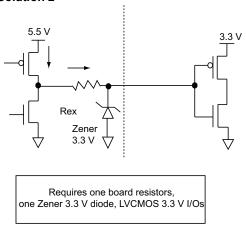

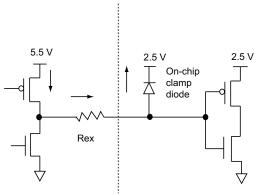

- Moving data between LSRAM and embedded nonvolatile memory (eNVM) or external memories