# Title: Radiation Results of the SER Test of Actel, Xilinx and Altera FPGA instances

Project Name: SER Test of Actel, Xilinx and Altera FPGA instances in Dec'03

| T | Н | E | C | $\vdash$ | П | P | P | R |  | TI | Ε | C. | Т |  | R |  |

|---|---|---|---|----------|---|---|---|---|--|----|---|----|---|--|---|--|

|---|---|---|---|----------|---|---|---|---|--|----|---|----|---|--|---|--|

Department: Engineering

Document type: Test Report

Version: 0.08

Date: 25-Oct-04

Confidentiality Level: 2

Distribution list:

Eric Dupont iRoC

Olivier Lauzeral iRoC

Rémi Gaillard iRoC

Marcos Olmos iRoC

Code Reference:

GRE\_2\_ACTEL\_SERTEST\_DEC\_03\_ENG\_TR\_008

#### DOCUMENT CONTROL # 281

| Released To (Company):     | ACTEL                                            |  |

|----------------------------|--------------------------------------------------|--|

|                            |                                                  |  |

| NDA Reference:             | 0-20-0002 Rev1                                   |  |

|                            |                                                  |  |

| Released to (Person):      | Jonathan Alexander, Yankin Tanurhan, Ken O'Neill |  |

|                            |                                                  |  |

| Source document reference: | CDE 2 ACTEL CENTERT DEC 02 ENG TD 000            |  |

|                            | GRE_2_ACTEL_SERTEST_DEC_03_ENG_TR_008            |  |

|                            |                                                  |  |

| Requested By               |                                                  |  |

| (iRoC Contact):            | O. Lauzeral                                      |  |

|                            | Signature                                        |  |

| Approved By:               |                                                  |  |

|                            | Olivier Lauzeral                                 |  |

|                            | Rémi Gaillard                                    |  |

|                            | Marcos Olmos                                     |  |

|                            |                                                  |  |

## THIS DOCUMENT IS THE PROPERTY OF iRoC Technologies Before using it for any purpose, please contact iRoC Technologies.

The iRoC logo, Product Names (e.g. Roban, Rockit, Smartestbed) are registered trademarks of iRoC Technologies. All other trademarks are property of their respective owners

#### iRoC Technologies, SA

World Trade Center, PO Box 1510 38025 Grenoble

**FRANCE**

+ 33 438 120 763

Fax + 33 438 129 615

E mail info@iroctech.com

Web www.iroctech.com

## **Revision History**

| Version | Author       | Date      | Description of change                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.01    | Marcos Olmos | 15-Jan-04 | First release                                                                                                                                                                                                                                                                                                                                                                         |

| 0.02    | Marcos Olmos | 22-Jan-04 | <ul> <li>Added test strategy copied from the Test Plan [3]</li> <li>Added error definitions copied from the Test Plan [3]</li> <li>Added Analysis of critical vs non critical SEU in 4.4.2</li> <li>Added Bitmaps of errors in 4.4.4</li> <li>Added Chip to chip variation in 4.4.5</li> <li>Added consistency check in 4.4.6</li> <li>Added Special observations in 4.4.7</li> </ul> |

| 0.03    | Marcos Olmos | 2-Mar-04  | - Added cosmic ray results of the LANSCE campaign in Feb 04.                                                                                                                                                                                                                                                                                                                          |

| 0.04    | Marcos Olmos | 8-Mar-04  | <ul><li>Completed cosmic ray results of the LANSCE campaign in Feb 04.</li><li>Added FIT at 5,000 ft</li></ul>                                                                                                                                                                                                                                                                        |

| 0.05    | Marcos Olmos | 18-Mar-04 | - Linked excel files copied in appendix A                                                                                                                                                                                                                                                                                                                                             |

| 0.06    | Marcos Olmos | 25-Mar-04 | - Added executive summary                                                                                                                                                                                                                                                                                                                                                             |

| 0.06A   | Marcos Olmos | 31 Mar-04 | - Minor typographical errors corrected                                                                                                                                                                                                                                                                                                                                                |

| 0.07    | Marcos Olmos | 16-Apr-04 | - Added alpha results for AX1000 and XC3S1000                                                                                                                                                                                                                                                                                                                                         |

| 0.08    | Marcos Olmos | 25-Oct-04 | <ul><li>Added alpha results for APA1000</li><li>Added alpha results for XC2V3000</li><li>Added alpha results for EP1C20</li></ul>                                                                                                                                                                                                                                                     |

|         |              |           |                                                                                                                                                                                                                                                                                                                                                                                       |

|         |              |           |                                                                                                                                                                                                                                                                                                                                                                                       |

|         |              |           |                                                                                                                                                                                                                                                                                                                                                                                       |

|         |              |           |                                                                                                                                                                                                                                                                                                                                                                                       |

|         |              |           |                                                                                                                                                                                                                                                                                                                                                                                       |

|         |              |           |                                                                                                                                                                                                                                                                                                                                                                                       |

|         |              |           |                                                                                                                                                                                                                                                                                                                                                                                       |

|         |              |           |                                                                                                                                                                                                                                                                                                                                                                                       |

|         |              |           |                                                                                                                                                                                                                                                                                                                                                                                       |

### **Applicable Documents**

[1] Title: ASER test for FPGAs Commercial Proposal

Doc. ACTEL 081903 v2

Number:

Version:

Date: Sep 03 Source: iRoC

[2] Title: JEDEC Standard - Measurement and Reporting of Alpha Particles and Terrestrial Cosmic-

ray-Induced Soft Errors in Semiconductor Devices

Doc. JESD89

Number:

Version:

Date: August 2001 Source: JEDEC

[3] Title: Test Plan for the SER Test of Actel, Xilinx and Altera FPGA instances

Doc. GRE 2 ACTEL SERTEST DEC 03 ENG TP 005

Number:

Version: 0.05

Date: 24-Nov-03

Source: iRoC

[4] Title: A. Taber and E. Normand, "Single Event Upset in Avionics", IEEE Trans. Nucl. Sci.,

NS-40, 120, 1993

Doc.

Number: Version:

Date: Source:

#### Table of contents

| OBJECT                                                                   | ••••••••••• |

|--------------------------------------------------------------------------|-------------|

| TEST STRATEGY                                                            |             |

| ERROR DEFINITION                                                         | ••••••      |

| 14 MEV TESTS                                                             |             |

| TESTED CONDITIONS AND SCHEDULE                                           |             |

| DEVICES TESTED                                                           |             |

| STABILITY WITHOUT NEUTRON BEAM                                           | •••••••     |

| 14 MEV RESULTS                                                           |             |

| CROSS-SECTION AND FIT CALCULATION                                        |             |

| OVERALL FIT RESULTS                                                      |             |

| ACCURACY OF RESULTS                                                      |             |

| ERROR COUNT STATISTICS                                                   |             |

| FLUENCE MEASUREMENT ACCURACY                                             |             |

| DETAILED ANALYSIS                                                        |             |

| VOLTAGE INFLUENCE ON FIT                                                 |             |

| ANALYSIS OF CRITICAL VS NON CRITICAL SEUANALYSIS OF SINGLE EVENT LATCHUP |             |

| BITMAPS OF ERRORS                                                        |             |

| CHIP TO CHIP VARIATION                                                   |             |

| CONSISTENCY CHECK                                                        |             |

| SPECIAL OBSERVATIONS                                                     |             |

| 14 MEV CONCLUSIONS                                                       |             |

|                                                                          |             |

| LANSCE TESTS                                                             | •••••       |

| LANSCE RESULTS                           | 39        |

|------------------------------------------|-----------|

| CROSS-SECTION AND FIT CALCULATION        | 20        |

| OVERALL FIT RESULTS                      |           |

| ACCURACY OF RESULTS                      |           |

| ERROR COUNT STATISTICS                   |           |

| FLUENCE MEASUREMENT ACCURACY             |           |

| DETAILED ANALYSIS                        |           |

| VOLTAGE INFLUENCE ON FIT                 |           |

| ANALYSIS OF CRITICAL VS NON CRITICAL SEU |           |

| ANALYSIS OF SINGLE EVENT LATCHUP         |           |

| BITMAPS OF ERRORS                        |           |

| CHIP TO CHIP VARIATION                   |           |

| CONSISTENCY CHECK                        |           |

| SPECIAL OBSERVATIONS                     |           |

| OI DOLLE ODDER (TITIOTO                  | 03        |

| LANSCE CONCLUSIONS                       | 68        |

| LANGCE CONCLUSIONS                       | <u>00</u> |

|                                          |           |

| A L DULA TREGIEG                         | (0        |

| ALPHA TESTS                              | 69        |

|                                          |           |

| CHARACTERISTICS OF THE ALPHA SOURCES     |           |

| TESTED CONDITIONS AND SCHEDULE           | 70        |

| DEVICES TESTED                           | 72        |

| STABILITY WITHOUT ALPHA SOURCE           | 72        |

| ALPHA RESULTS                            | 73        |

|                                          | _         |

| CROSS-SECTION AND FIT CALCULATION        |           |

| OVERALL FIT RESULTS                      |           |

| ACCURACY OF RESULTS                      |           |

| ERROR COUNT STATISTICS                   |           |

| FLUENCE MEASUREMENT ACCURACY             |           |

| DETAILED ANALYSIS                        |           |

| VOLTAGE INFLUENCE ON FIT                 |           |

| ANALYSIS OF CRITICAL VS NON CRITICAL SEU |           |

| ANALYSIS OF SINGLE EVENT LATCHUP         |           |

| BITMAPS OF ERRORS                        |           |

| CHIP TO CHIP VARIATION                   |           |

| CONSISTENCY CHECK.                       |           |

| SPECIAL OBSERVATIONS                     | 93        |

|                                          |           |

| ALPHA CONCLUSIONS                        | 94        |

| <u>A</u> ]              | DETAILS OF CROSS-SECTIONS AND FIT                    | 95  |

|-------------------------|------------------------------------------------------|-----|

| <b>A.1</b>              | 14 MEV NEUTRONS                                      | 95  |

|                         | LANSCE                                               |     |

|                         | ALPHA                                                |     |

| <u>B</u> 9              | 95% CONFIDENCE INTERVALS                             | 106 |

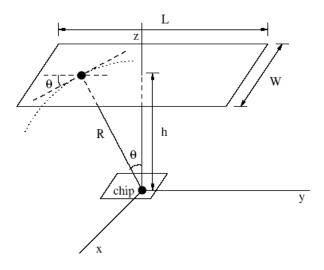

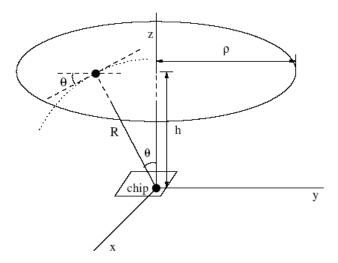

| <u>C</u> <u></u>        | GEOMETRY FACTOR CALCULATION FOR ALPHA TESTS          | 107 |

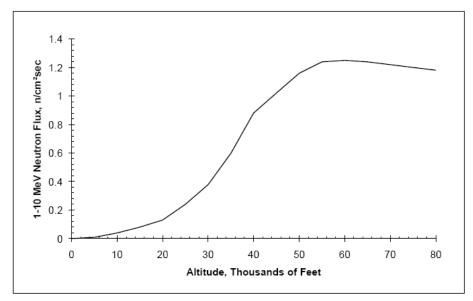

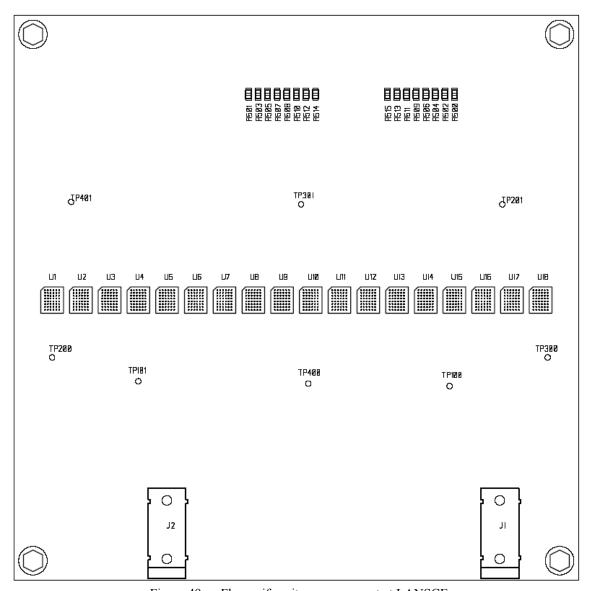

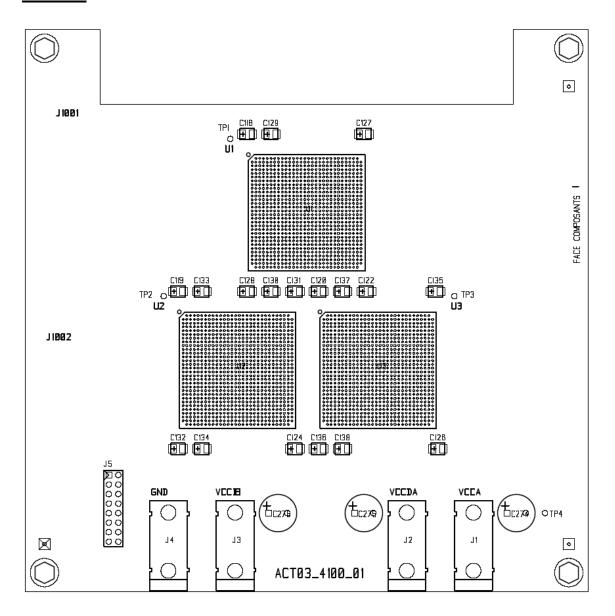

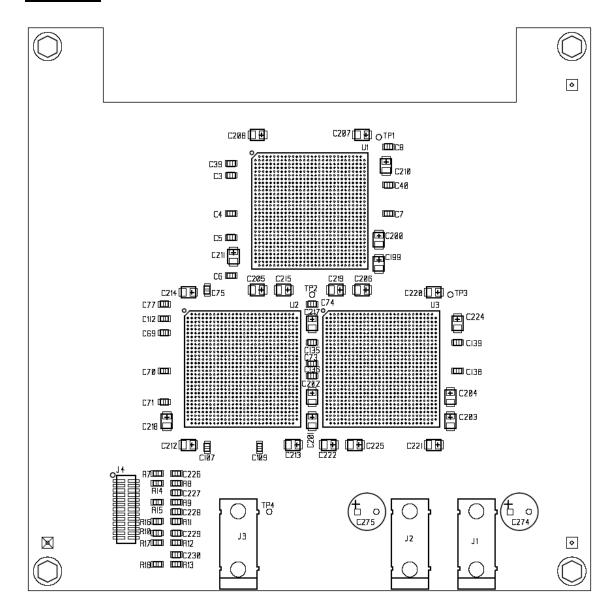

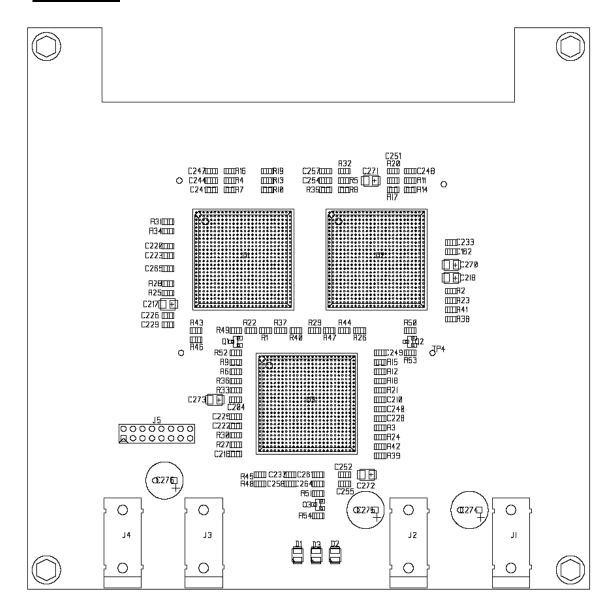

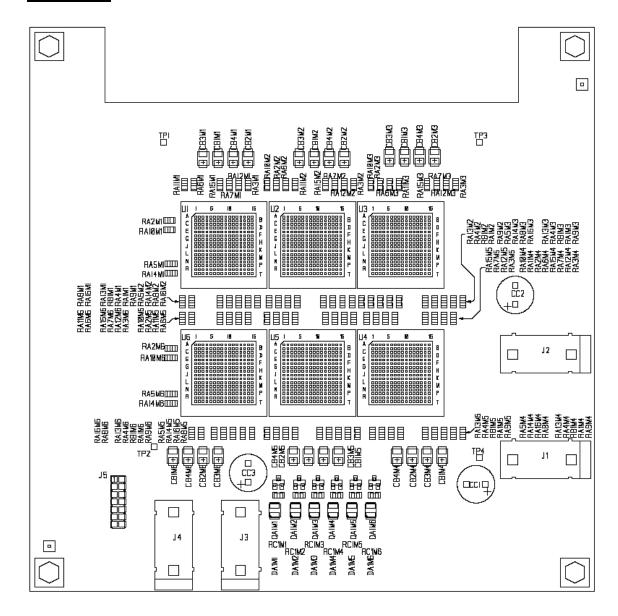

| <u>D</u> <u>'</u>       | TEST BOARD LAYOUT                                    | 110 |

| <b>D.1</b>              | AX1000                                               | 110 |

| <b>D.2</b>              | APA1000                                              | 111 |

| D.3                     | XC2V3000                                             | 112 |

|                         | XC3S1000                                             |     |

|                         | EP1C20                                               |     |

| List of Figu            |                                                      |     |

| FIGURE 1.               | TEST CIRCUIT BLOCK DIAGRAM                           |     |

| FIGURE 2.               | COSMIC-RAY NEUTRON FLUX AT GROUND LEVEL              |     |

| FIGURE 3.               | NEUTRON FLUX VS ALTITUDE                             |     |

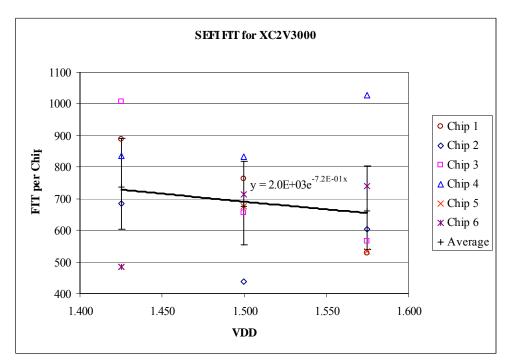

| FIGURE 4.               | SEFI FIT OF XC2V3000 VS VDD                          |     |

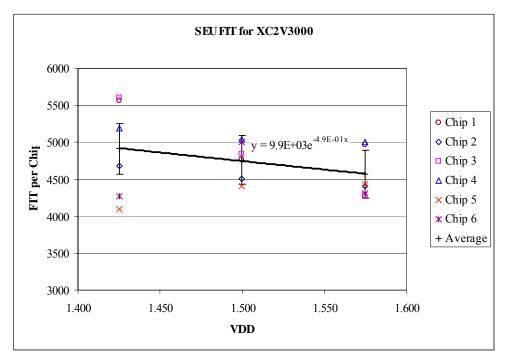

| FIGURE 5.               | SEU FIT OF XC2V3000 VS VDD                           |     |

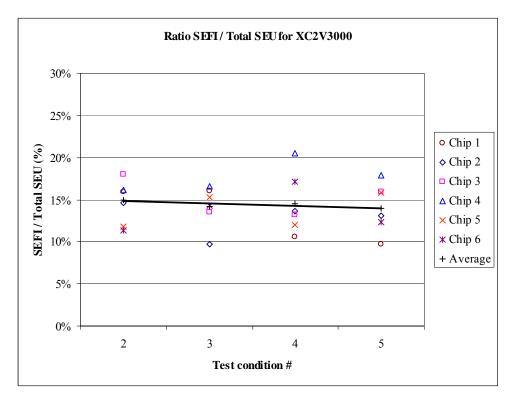

| FIGURE 6. FIGURE 7.     | SEFI VS TOTAL SEU XC2V3000                           |     |

| FIGURE 7.<br>FIGURE 8.  | AX1000 VCCA AND VCCIB WAVEFORMSAX1000 VCCDA WAVEFORM |     |

| FIGURE 8.               | APA1000 VCCDA WAVEFORM                               |     |

| FIGURE 9.<br>FIGURE 10. |                                                      |     |

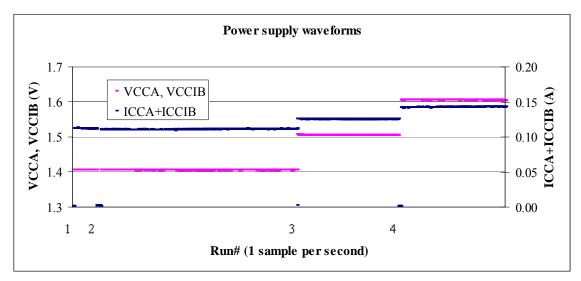

| FIGURE 10.              | XC2V3000 VCCINT WAVEFORM                             |     |

| FIGURE 12.              | . 1102 / 5000 / 6 611 / 1 / 1 / 61 614 / 1           |     |

| FIGURE 13.              |                                                      |     |

| FIGURE 14.              |                                                      |     |

| FIGURE 15.              |                                                      |     |

| FIGURE 16.              |                                                      |     |

| FIGURE 17.              |                                                      |     |

| FIGURE 18.              |                                                      |     |

| FIGURE 19.              |                                                      |     |

| FIGURE 20.              | . SEFI FIT OF XC2V3000 VS VDD                        | 45  |

| FIGURE 21.              |                                                      |     |

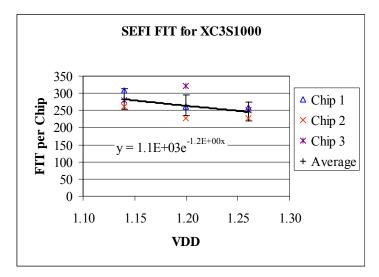

| FIGURE 22.              | . SEFI FIT OF XC3S1000 VS VDD                        | 47  |

| FIGURE 23. | SEU FIT OF XC3S1000 VS VDD              | 47 |

|------------|-----------------------------------------|----|

| FIGURE 24. | SEFI FIT OF EP1C20 VS VDD               |    |

| FIGURE 25. | SEFI VS TOTAL SEU XC2V3000              |    |

| FIGURE 26. | SEFI VS TOTAL SEU XC3S1000              |    |

| FIGURE 27. | AX1000 VCCA AND VCCIB WAVEFORMS         | 51 |

| FIGURE 28. | AX1000 VCCDA WAVEFORM                   | 51 |

| FIGURE 29. | APA1000 VDD WAVEFORM                    |    |

| FIGURE 30. | APA1000 VDDP WAVEFORM                   | 52 |

| FIGURE 31. | XC2V3000 VCCINT WAVEFORM                | 53 |

| FIGURE 32. | XC2V3000 VCCO WAVEFORM                  |    |

| FIGURE 33. | BITMAP FOR RUN#2 OF XC2V3000            |    |

| FIGURE 34. | BITMAP FOR RUN#3 OF XC2V3000            | 56 |

| FIGURE 35. | BITMAP FOR RUN#4 OF XC2V3000            | 56 |

| FIGURE 36. | BITMAP FOR RUN#5 OF XC2V3000            | 57 |

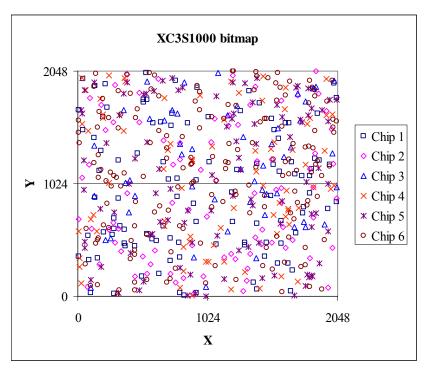

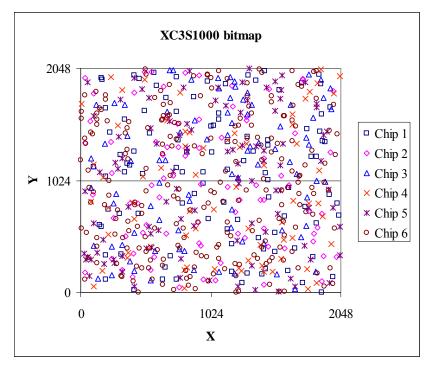

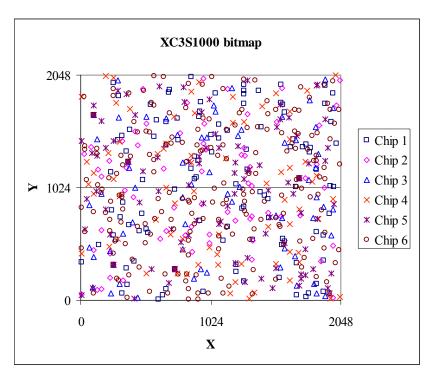

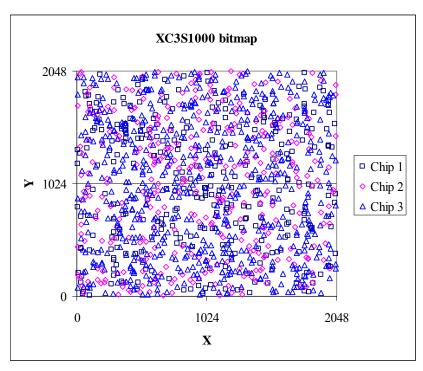

| FIGURE 37. | BITMAP FOR RUN#2 OF XC3S1000            | 58 |

| FIGURE 38. | BITMAP FOR RUN#3 OF XC3S1000            |    |

| FIGURE 39. | BITMAP FOR RUN#4 OF XC3S1000            |    |

| FIGURE 40. | BITMAP FOR RUN#5 OF XC3S1000            | 59 |

| FIGURE 41. | CHIP TO CHIP FIT VARIATION FOR XC2V3000 | 60 |

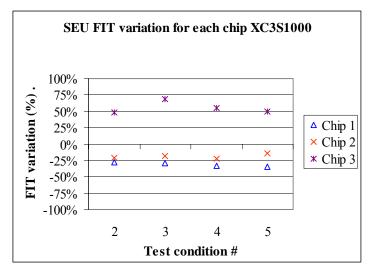

| FIGURE 42. | CHIP TO CHIP FIT VARIATION FOR XC3S1000 |    |

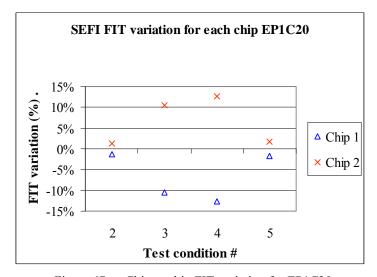

| FIGURE 43. | CHIP TO CHIP FIT VARIATION FOR EP1C20   |    |

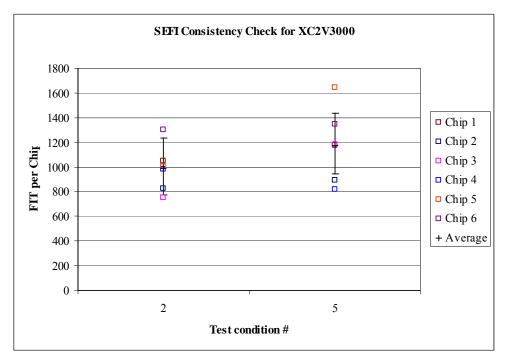

| FIGURE 44. | SEFI CONSISTENCY CHECK FOR XC2V3000     |    |

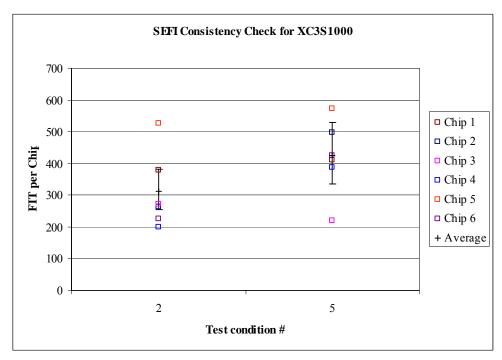

| FIGURE 45. | SEFI CONSISTENCY CHECK FOR XC3S1000     |    |

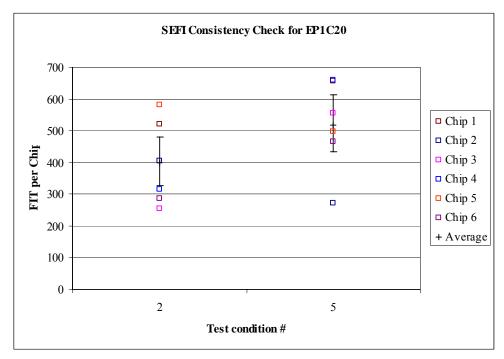

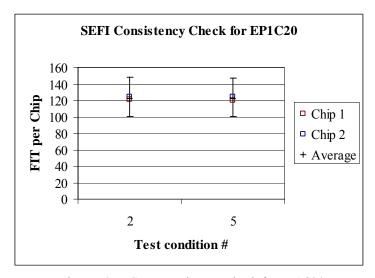

| FIGURE 46. | SEFI CONSISTENCY CHECK FOR EP1C20       |    |

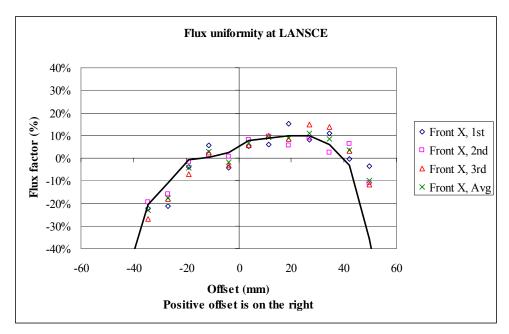

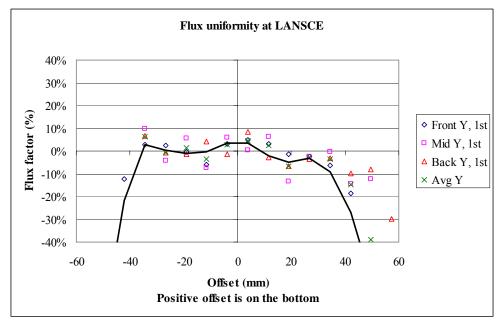

| FIGURE 47. | FLUX UNIFORMITY AT LANSCE (X-AXIS)      |    |

| FIGURE 48. | FLUX UNIFORMITY AT LANSCE (Y-AXIS)      |    |

| FIGURE 49. | FLUX UNIFORMITY MEASUREMENT AT LANSCE   |    |

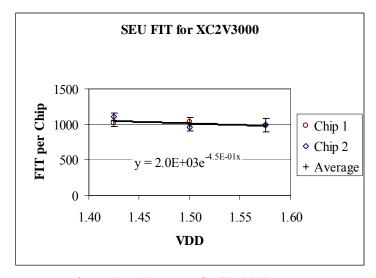

| FIGURE 50. | SEU FIT OF XC2V3000 VS VDD              |    |

| FIGURE 51. | SEFI FIT OF XC3S1000 VS VDD             |    |

| FIGURE 52. | SEU FIT OF XC3S1000 VS VDD              |    |

| FIGURE 53. | SEFI FIT OF EP1C20 VS VDD               | 79 |

| FIGURE 54. | SEFI VS TOTAL SEU XC3S1000              |    |

| FIGURE 55. | AX1000 VCCA AND VCCIB WAVEFORMS         |    |

| FIGURE 56. | AX1000 VCCDA WAVEFORM                   |    |

| FIGURE 57. | BITMAP FOR RUN#2 OF XC2V3000            |    |

| FIGURE 58. | BITMAP FOR RUN#3 OF XC2V3000            |    |

| FIGURE 59. | BITMAP FOR RUN#4 OF XC2V3000            |    |

| FIGURE 60. | BITMAP FOR RUN#5 OF XC2V3000            |    |

| FIGURE 61. | BITMAP FOR RUN#2 OF XC3S1000            |    |

| FIGURE 62. | BITMAP FOR RUN#3 OF XC3S1000            |    |

| FIGURE 63. | BITMAP FOR RUN#4 OF XC3S1000            |    |

| FIGURE 64. | BITMAP FOR RUN#5 OF XC3S1000            | 88 |

| FIGURE 65. | CHIP TO CHIP FIT VARIATION FOR XC2V3000 |    |

| FIGURE 66. | CHIP TO CHIP FIT VARIATION FOR XC3S1000 |    |

| FIGURE 67. | CHIP TO CHIP FIT VARIATION FOR EP1C20   |    |

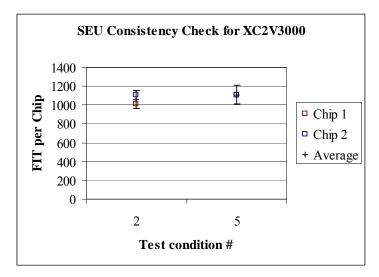

| FIGURE 68. | SEU CONSISTENCY CHECK FOR XC2V3000      |    |

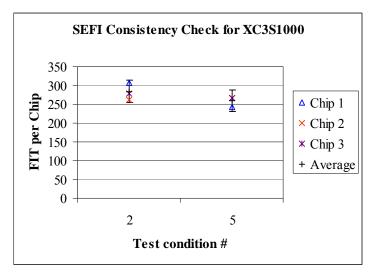

| FIGURE 69. | SEFI CONSISTENCY CHECK FOR XC3S1000     |    |

| FIGURE 70  | SEFI CONSISTENCY CHECK FOR EP1C20       | 92 |

List of Tables

| TABLE 1.  | SUMMARY OF TEST CAMPAIGNS                                     | 12 |

|-----------|---------------------------------------------------------------|----|

| TABLE 2.  | ERROR DEFINITIONS                                             | 14 |

| TABLE 3.  | CONDITIONS TESTED FOR AX1000                                  |    |

| TABLE 4.  | CONDITIONS TESTED FOR APA1000                                 |    |

| TABLE 5.  | CONDITIONS TESTED FOR XC2V3000                                |    |

| TABLE 6.  | LOT CODES OF THE AX1000 CHIPS TESTED                          | 16 |

| TABLE 7.  | LOT CODES OF THE APA1000 CHIPS TESTED                         | 16 |

| TABLE 8.  | LOT CODES OF THE XC2V3000 CHIPS TESTED                        | 16 |

| TABLE 9.  | OVERALL COSMIC-RAY FIT AT SEA LEVEL IN NYC                    |    |

| TABLE 10. | OVERALL COSMIC-RAY FIT AT DIFFERENT ALTITUDES                 |    |

| TABLE 11. | 95% CONFIDENCE LIMITS FOR SMALL NUMBER OF EVENTS              | 20 |

| TABLE 12. | 95% CONFIDENCE INTERVALS FOR ALL DEVICES                      | 20 |

| TABLE 13. | DETAILED ANALYSIS FOR 14 MEV TESTS                            |    |

| TABLE 14. | XC2V3000 NUMBER OF SEFI FOR EACH CHIP                         |    |

| TABLE 15. | OVERALL COSMIC-RAY FIT AT SEA LEVEL IN NYC                    | 35 |

| TABLE 16. | OVERALL COSMIC-RAY FIT AT DIFFERENT ALTITUDES                 | 35 |

| TABLE 17. | CONDITIONS TESTED FOR AX1000                                  | 36 |

| TABLE 18. | CONDITIONS TESTED FOR APA1000                                 | 36 |

| TABLE 19. | CONDITIONS TESTED FOR XC2V3000                                | 37 |

| TABLE 20. | CONDITIONS TESTED FOR XC3S1000                                |    |

| TABLE 21. | CONDITIONS TESTED FOR EP1C20                                  | 37 |

| TABLE 22. | LOT CODES OF THE AX1000 CHIPS TESTED                          |    |

| TABLE 23. | LOT CODES OF THE APA1000 CHIPS TESTED                         |    |

| TABLE 24. | LOT CODES OF THE XC2V3000 CHIPS TESTED                        |    |

| TABLE 25. | LOT CODES OF THE XC3S1000 CHIPS TESTED                        |    |

| TABLE 26. | LOT CODES OF THE EP1C20 CHIPS TESTED                          |    |

| TABLE 27. | OVERALL COSMIC-RAY FIT AT SEA LEVEL IN NYC                    |    |

| TABLE 28. | OVERALL COSMIC-RAY FIT AT DIFFERENT ALTITUDES                 |    |

| TABLE 29. | 95% CONFIDENCE INTERVALS FOR ALL DEVICES                      |    |

| TABLE 30. | DETAILED ANALYSIS FOR LANSCE TESTS                            |    |

| TABLE 31. | XC2V3000 NUMBER OF SEFI FOR EACH CHIP                         |    |

| TABLE 32. | XC3S1000 NUMBER OF SEFI FOR EACH CHIP                         |    |

| TABLE 33. | EP1C20 NUMBER OF SEFI FOR EACH CHIP                           | 54 |

| TABLE 34. | OVERALL COSMIC-RAY FIT AT SEA LEVEL IN NYC                    | 68 |

| TABLE 35. | OVERALL COSMIC-RAY FIT AT DIFFERENT ALTITUDES                 |    |

| TABLE 36. | CHARACTERISTICS OF THE ALPHA SOURCES                          |    |

| TABLE 37. | ALPHA SOURCE UTILIZATION AND GEOMETRY FACTORS FOR EACH DEVICE |    |

| TABLE 38. | CONDITIONS TESTED FOR AX1000                                  |    |

| TABLE 39. | CONDITIONS TESTED FOR APA1000                                 |    |

| TABLE 40. | CONDITIONS TESTED FOR XC2V3000                                |    |

| TABLE 41. | CONDITIONS TESTED FOR XC3S1000                                |    |

| TABLE 42. | CONDITIONS TESTED FOR EP1C20                                  |    |

| TABLE 43. | LOT CODES OF THE AX1000 CHIPS TESTED                          |    |

| TABLE 44. | LOT CODES OF THE APA1000 CHIPS TESTED                         |    |

| TABLE 45. | LOT CODES OF THE XC2V3000 CHIPS TESTED                        |    |

| TABLE 46. | LOT CODES OF THE XC3S1000 CHIPS TESTED                        |    |

| TABLE 47. | LOT CODES OF THE EP1C20 CHIPS TESTED                          |    |

| TABLE 48. | OVERALL ALPHA PARTICLE FIT FOR 0.001 A/CM²/HOUR               |    |

| TABLE 49. | 95% CONFIDENCE INTERVALS FOR ALL DEVICES                      |    |

| TARLE 50  | ΔΙΡΗΔ ΝΟΙΙΚΟΉ ΙΙΙΙΙΙΙΖΑΙΙΟΝΙΑΝΙΙ ΔΟΟΙΙΚΑΟΎ ΕΟΚ ΕΔΟΉ ΝΕΥΙΟΈ    | 76 |

## GRE\_2\_ACTEL\_SERTEST\_DEC\_03\_ENG\_TR\_008 Radiation Results of the SER Test of Actel, Xilinx and Altera FPGA instances

| TABLE 51. | DETAILED ANALYSIS FOR ALPHA TESTS                            | 77 |

|-----------|--------------------------------------------------------------|----|

| TABLE 52. | XC2V3000 NUMBER OF SEU FOR EACH CHIP                         | 82 |

| TABLE 53. | XC3S1000 NUMBER OF SEFI FOR EACH CHIP                        | 83 |

| TABLE 54. | EP1C20 NUMBER OF SEFI FOR EACH CHIP                          | 83 |

| TABLE 55. | OVERALL ALPHA PARTICLE FIT FOR 0.001 A/CM <sup>2</sup> /HOUR | 94 |

## 1 Executive summary

- Cosmic-ray and alpha-particle soft error rates were measured for five different architectures of FPGAs, from three different vendors, using three different programming technologies.

- Test methodology was compliant with JESD-89.

- SRAM-based FPGAs are liable to configuration SEU and SEFI when exposed to high-energy neutrons and alpha particles.

- Antifuse-based and Flash-based FPGAs did not exhibit any configuration SEU or SEFI when exposed to high-energy neutrons and alpha particles.

- Test results allowed the calculation of the ratio of SEFIs to SEUs.

## 2 Object

This test report provides the cosmic-ray SER of AX1000, APA1000, XC2V3000, XC3S1000 and EP1C20 devices. The cosmic-ray SER was measured at the LANSCE WNR facility at Los Alamos in February 2004.

The LANSCE results are compared with the preliminary SER of AX1000, APA1000 and XC2V3000 devices. The preliminary SER was measured using 14 MeV neutrons at the Interfaculty Reactor Institute (IRI) at Delft in The Netherlands in December 2003.

This test report also provides the alpha particle SER of AX1000, APA1000, XC2V3000, XC3S1000 and EP1C20 devices. The alpha particle SER was measured at iRoC premises using calibrated Am241 foil sources in April and October 2004.

The tests were conducted following the Test Plan [3]. Table 1 summarizes the tests performed for each device.

| Mfg    | Family            | Device   | 14 MeV       | Full spectrum | Alpha        |

|--------|-------------------|----------|--------------|---------------|--------------|

|        |                   |          | neutrons     | neutrons      | particles    |

| Actel  | Axcelerator       | AX1000   | $\checkmark$ | $\sqrt{}$     | $\checkmark$ |

| Actel  | ProASICPLUS Flash | APA1000  | $\sqrt{}$    | $\sqrt{}$     | $\checkmark$ |

| Xilinx | Virtex-II         | XC2V3000 | $\sqrt{}$    | $\sqrt{}$     | $\sqrt{}$    |

| Xilinx | Spartan-3         | XC3S1000 |              | $\sqrt{}$     | $\checkmark$ |

| Altera | Cyclone           | EP1C20   |              | $\sqrt{}$     | $\sqrt{}$    |

Table 1. Summary of test campaigns

This test report includes the description of the different tests performed during the experiments, and provides the detailed analysis and explanation of the FIT results.

#### 2.1 Test strategy

This section recalls the test strategy. The test strategy is described in the Test Plan [3].

The test approach has special emphasis for the faults affecting the configuration memory.

The test strategy is based in the continuous monitoring of the outputs of a combinatorial circuit implemented in the FPGA under test. As soon as a permanent mismatch of the output values is observed, the test is stopped and the configuration memory read back and stored in a file. Additionally, the FPGA configuration memory is periodically read back, even if the output values are correct. The test strategy enables to identify the non critical and the critical SEU in the configuration memory, that is, those SEU in the configuration memory that do not create an error in the output, and those that create an error in the output.

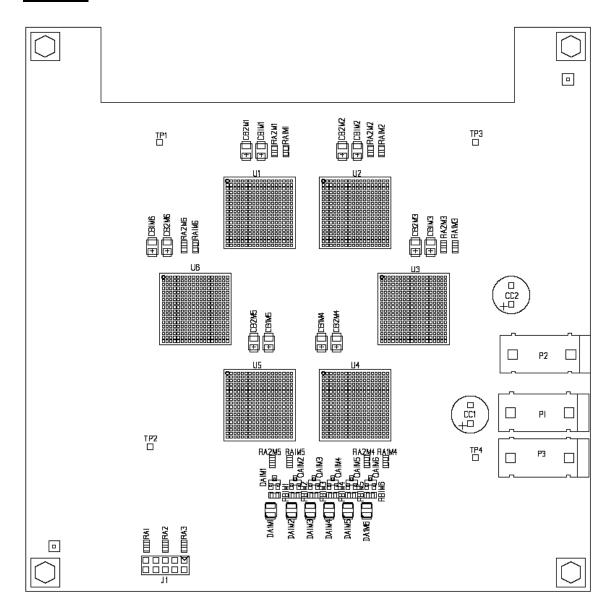

The target circuit implemented in the DUT is composed of an array of 16x16-bit binary multipliers. Inputs of the multipliers are connected in parallel, and the outputs are connected to a multiplexer. The tester checks the output of each multiplier sequentially by means of the multiplexer. The main feature of this circuit is that

it is purely combinatorial and uses a large part of the Look-Up Table (LUT) resources. The absence of Flip-Flops ensures that fails occur only when the configuration memory is modified.

The test of the IO blocks (IOB) is accomplished by connecting a chain of IOB between the outputs of the multiplexer and the tester. In this way all the available IOB of the FPGA can be tested.

Figure 1 presents the block diagram of the target circuit.

Figure 1. Test circuit block diagram

#### 2.2 Error definition

This section recalls the error definitions. Error definitions are included in the Test Plan [3].

| Type of error                   | Description                                                                                                                                                                                                                                              |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEU in the configuration memory | A bit flip in the configuration memory caused by a single particle strike, neutron or alpha.                                                                                                                                                             |

| SEFI in the target circuit      | A permanent mismatch of the output of the target circuit. It is created by a SEU in the configuration memory that alters the Look-Up Tables (LUT) or the routing of signals in the target circuit.                                                       |

| Configuration circuitry failure | A failure in the controlling circuitry of the FPGA. Configuration and read back operations fail.                                                                                                                                                         |

| Latchup                         | The activation of a parasitic structure in the silicon by a single neutron strike. The latchup effects are an increase of the current consumption and failures in the target circuit, the configuration memory or the controlling circuitry of the FPGA. |

| Hard error                      | A permanent failure in the FPGA that cannot be recovered after switching the beam off, switching the power off/on, and reconfiguration.                                                                                                                  |

Table 2. Error definitions

## 3 14 MeV tests

#### 3.1 Tested conditions and schedule

The following tables provide the sequence of conditions that were tested. Additionally to the test conditions, stability and consistency checks have been performed at the beginning and the end of each test sequence. A stability test (beam off) has been carried out before irradiation (cf. section 3.3). A consistency test (repetition of the first condition) has been carried out at the end of the test sequence. The order of the test conditions follows the Test Plan [3].

The tables are extracted from the campaign logbook files in appendix A.1.

| Run #  | Device | Energy | St     | art      | Stop     | C     | ondition |      |

|--------|--------|--------|--------|----------|----------|-------|----------|------|

| Kuii # | Device | (MeV)  | Date   | Time     | Time     | Cycle | VDD      | Temp |

| 1      | AX1000 | 14     | Dec-16 | 14:29:13 | 14:44:16 | 200ns | 1.4      | 25°C |

| 2      | AX1000 | 14     | Dec-16 | 14:47:15 | 16:59:27 | 200ns | 1.4      | 25°C |

| 3      | AX1000 | 14     | Dec-17 | 8:00:00  | 9:08:22  | 200ns | 1.5      | 25°C |

| 4      | AX1000 | 14     | Dec-17 | 9:10:42  | 10:21:37 | 200ns | 1.6      | 25°C |

| 5      | AX1000 | 14     | Note 1 | Note 1   | Note 1   | 200ns | 1.4      | 25°C |

Table 3. Conditions tested for AX1000

| Run #  | Device  | Energy | Start  |          | Stop     | C     | onditio | n    |

|--------|---------|--------|--------|----------|----------|-------|---------|------|

| Kuii # | Device  | (MeV)  | Date   | Time     | Time     | Cycle | VDD     | Temp |

| 1      | APA1000 | 14     | Dec-16 | 14:30:26 | 14:44:14 | 200ns | 2.3     | 25°C |

| 2      | APA1000 | 14     | Dec-16 | 14:47:31 | 16:59:35 | 200ns | 2.3     | 25°C |

| 3      | APA1000 | 14     | Dec-17 | 8:00:00  | 9:08:20  | 200ns | 2.5     | 25°C |

| 4      | APA1000 | 14     | Dec-17 | 9:10:45  | 10:21:34 | 200ns | 2.7     | 25°C |

| 5      | APA1000 | 14     | Note 1 | Note 1   | Note 1   | 200ns | 2.3     | 25°C |

Table 4. Conditions tested for APA1000

| Run #  | Device   | Energy | St     | Start Stop |          | t Stop Condit |       | tion |  |

|--------|----------|--------|--------|------------|----------|---------------|-------|------|--|

| Kuii # | Device   | (MeV)  | Date   | Time       | Time     | Cycle         | VDD   | Temp |  |

| 1      | XC2V3000 | 14     | Dec-17 | 13:31:49   | 13:36:11 | 200ns         | 1.425 | 25°C |  |

| 2      | XC2V3000 | 14     | Dec-17 | 13:36:31   | 14:29:04 | 200ns         | 1.425 | 25°C |  |

| 3      | XC2V3000 | 14     | Dec-17 | 14:31:12   | 15:08:02 | 200ns         | 1.500 | 25°C |  |

| 4      | XC2V3000 | 14     | Dec-17 | 15:08:40   | 15:46:06 | 200ns         | 1.575 | 25°C |  |

| 5      | XC2V3000 | 14     | Dec-17 | 15:52:07   | 16:34:41 | 200ns         | 1.425 | 25°C |  |

Table 5. Conditions tested for XC2V3000

Note 1: The consistency check, run #5, was not done for the AX1000 and APA1000 because no errors were observed for any of the conditions tested.

#### 3.2 Devices tested

The following tables show the lot codes of the chips that were actually tested:

| Chip 1          | Chip 2         | Chip 3         |

|-----------------|----------------|----------------|

| DOAAJ1<br>0320  | DOJC21<br>0345 | DOJC21<br>0345 |

| Chip 4          | Chip 5         |                |

| DOH5S21<br>0331 | DOJC21<br>0345 |                |

Table 6. Lot codes of the AX1000 chips tested

| Chip 1 | Chip 2 | Chip 3 |

|--------|--------|--------|

| MF7G7  | MF7G7  | MF7G7  |

| 0247   | 0247   | 0247   |

| Chip 4 | Chip 5 | Chip 6 |

| MF7G7  | MF7G7  | MF7G7  |

| 0247   | 0247   | 0247   |

Table 7. Lot codes of the APA1000 chips tested

| Chip 1    | Chip 2    | Chip 3    |  |

|-----------|-----------|-----------|--|

| AGT0337   | AGT0337   | AGT0337   |  |

| F2149925A | F2149925A | F2149925A |  |

| Chip 4    | Chip 5    | Chip 6    |  |

| AGT0337   | AGT0337   | AGT0337   |  |

| F2149925A | F2149925A | F2149925A |  |

Table 8. Lot codes of the XC2V3000 chips tested

#### 3.3 Stability without neutron beam

An error rate measurement is performed with the beam off and with the components placed in the target. The components are in the real environment with the real electromagnetic parasitic. This aims at verifying the robustness of both the tester and the DUT boards against the real noisy environment.

This experiment was done during 10 minutes for each DUT board and no error occurred (cf run #1 in Table 3 to Table 5).

## 4 14 MeV results

#### 4.1 Cross-section and FIT calculation

The cross-section defines the sensitivity of a device. The cross-section per chip, as a function of neutron energy E, is defined as  $\sigma(E)=N/(F^*C)$  where N is the total number of errors, F is the fluence and C is the number of chips tested. In this document, the cross-section is given in cm<sup>2</sup>/chip.

The cross-section measured with 14 MeV neutrons is directly used to estimate the terrestrial failure rate. We approximate the full energy spectrum cross-section by the cross-section at 14 MeV. The approximation results in a lower estimate of the full spectrum cross-section because of the regular increase of cross-section at high energy. The full spectrum cross-section could be up to 50% higher than the 14 MeV cross-section.

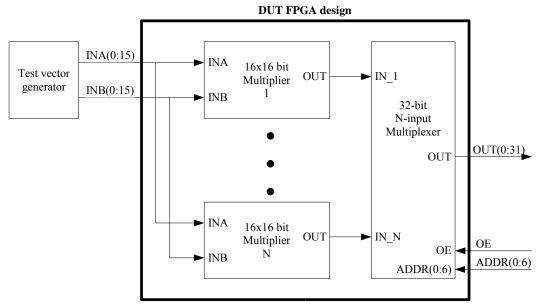

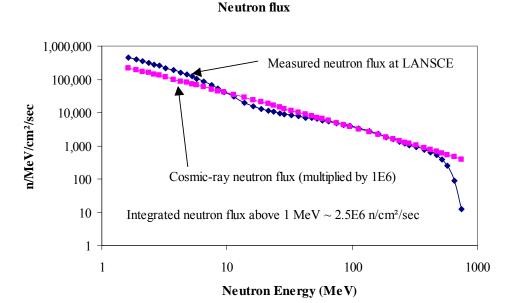

#### Neutron flux

Figure 2. Cosmic-ray neutron flux at ground level

According to the JESD89 specification [2], the FIT rate is calculated using the value of neutron flux for the New-York City,  $f_{\rm NYC}$  =14 n/cm<sup>2</sup>/hour for neutrons with energy above 10 MeV. Thus, the FIT is given by the following formula:

$$FIT = \sigma * f_{NYC} * 10^9 (errors/10^9 hour)$$

Where  $\sigma$  is the cross-section given in cm<sup>2</sup>/chip, and  $f_{NYC}$  is the flux given in n/cm<sup>2</sup>/hour.

The FIT is calculated using the neutron flux for the New-York City at sea level. The neutron flux depends on the altitude and location. Appendix E of the JESD89 specification [2] shows how to adjust the error rates calculated for the NYC for other locations.

#### 4.2 Overall FIT results

Table 9 presents the overall cosmic-ray FIT for each device at sea level in NYC. The overall FIT is calculated as the average of all chips and test conditions for the XC2V3000. Appendix A details the cross-section and FIT for each chip and test condition.

| Device   | Overall<br>FIT (SEFI)<br>per Device | Overall<br>FIT (SEU)<br>per Device |

|----------|-------------------------------------|------------------------------------|

| AX1000   | < 0.017                             | < 0.017                            |

| APA1000  | < 0.026                             | < 0.026                            |

| XC2V3000 | 680                                 | 4700                               |

Table 9. Overall cosmic-ray FIT at sea level in NYC

In Table 9, it is important to understand that no errors were observed for the AX1000 and APA1000, for anyof the test conditions. The given figure of FIT is an upper bound calculated considering one error for all chips and test conditions. The AX1000 and APA1000, based in Antifuse and Flash processes respectively, are considered insensitive to 14 MeV neutrons, therefore extending the test for longer periods would still produce no errors, and result in lower bounds of FIT.

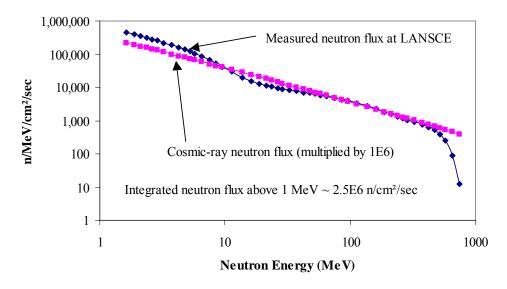

The neutron flux increases with altitude, and has a maximum at approximately 60,000 ft. The FIT at sea level, 5,000 ft, 30,000 ft and 60,000 ft is provided in Table 10:

| Device   | FIT (SEFI) at sea level | FIT (SEFI) at 5,000 ft | FIT (SEFI) at 30,000 ft | FIT (SEFI) at 60,000 ft |

|----------|-------------------------|------------------------|-------------------------|-------------------------|

| AX1000   | < 0.017                 | < 0.058                | <2.5                    | <8.1                    |

| APA1000  | < 0.026                 | < 0.089                | <3.8                    | <12                     |

| XC2V3000 | 680                     | 2,300                  | 99,000                  | 320,000                 |

Table 10. Overall cosmic-ray FIT at different altitudes

The altitude effect at 5,000 ft and 30,000 ft is evaluated using the formula provided in appendix E of JESD89 [2]:

Neutron flux

$$(n/cm^2/hour) = 15E3 * e^{-(A/148)}$$

Where the altitude, a, in feet above sea level, is expressed as the areal density of the air column, A, in units of g/cm<sup>2</sup>. The altitude, a, can be converted to the areal density, A using the following equation:

$$A = 1033 \times \exp[-.03813 \times (a/1000) -.00014 \times (a/1000)^{2} + 6.4E - 7 \times (a/1000)^{3}]$$

The altitude effect at 60,000 ft is evaluated using Figure 3 from reference [4].

Figure 3. Neutron flux vs altitude

#### 4.3 Accuracy of results

The accuracy of the cross-section results is assessed in this section. The accuracy of the cross-section is the sum of the error count and fluence measurement accuracies.

#### 4.3.1 Error count statistics

The error count is generally described by a Poisson distribution, cf appendix C.1 in [2]. If N errors occur, the mean error count is approximated by N. The standard deviation is given by  $\sqrt{N}$ .

The error count can be bounded using the upper and lower limits in Table 11, extracted from appendix C.2 of [2]. In using this table, the first column is the actual number of events observed in the experiment. The upper and lower limits define the 95% confidence interval for the true mean of the distribution. The upper and lower limits for any number of events can be calculated using the formulas given in appendix B.

|        | 95% confidence limit |             |  |  |

|--------|----------------------|-------------|--|--|

| Events | Lower limit          | Upper limit |  |  |

| 0      | 0.0                  | 3.7         |  |  |

| 1      | 0.0                  | 5.6         |  |  |

| 2      | 0.2                  | 7.2         |  |  |

| 3      | 0.6                  | 8.8         |  |  |

| 4      | 1.1                  | 10.2        |  |  |

| 5      | 1.6                  | 11.7        |  |  |

| 6      | 2.2                  | 13.1        |  |  |

| 7      | 2.8                  | 14.4        |  |  |

| 8      | 3.5                  | 15.8        |  |  |

| 9      | 4.1                  | 17.1        |  |  |

| 10     | 4.8                  | 18.4        |  |  |

| 20     | 12.2                 | 30.9        |  |  |

| 50     | 37.1                 | 65.9        |  |  |

| 100    | 81.4                 | 121.6       |  |  |

Table 11. 95% confidence limits for small number of events

The accuracy of the error count is defined in this report using 95% confidence intervals. The 95% confidence limits depend on the number of errors observed. The number of errors is detailed in appendix A for each chip and test condition.

The following table summarizes the 95% confidence intervals for each device. For example, the overall number of SEFI per chip and test condition is 18 for the XC2V3000. By using the formulas given in appendix B, we find that the lower and upper limits are 10.7 and 28.4 respectively. The limits in Table 12 are calculated as (Lower limit/Mean error count -1)\*100 = -41%, and (Upper limit/Mean error count -1)\*100 = +58%.

| Device   | Error type            | Mean error count | Lower limit        | Upper limit | Comment                                  |

|----------|-----------------------|------------------|--------------------|-------------|------------------------------------------|

| AX1000   | AX1000 SEFI 0 n/a n/a |                  | No errors observed |             |                                          |

| APA1000  | SEFI                  | 0                | n/a                | n/a         | No errors observed                       |

|          |                       | 18               | -41%               | +58%        | Errors per chip and test condition       |

|          | SEFI                  | 105              | -18%               | +21%        | Errors for all chips per test condition  |

| XC2V3000 |                       | 420              | -9%                | +10%        | Errors for all chips and test conditions |

|          | SEU                   | 122              | -17%               | +19%        | Errors per chip and test condition       |

|          | SEU                   | 730              | -7%                | +8%         | Errors for all chips per test condition  |

Table 12. 95% confidence intervals for all devices

#### 4.3.2 Fluence measurement accuracy

The accuracy of the fluence measurement is better than 10% for the IRI facility.

#### 4.4 Detailed analysis

Detailed analysis of the results is presented hereafter. The following table summarizes the analyses presented for each device:

| Analysis                                 | AX1000 | APA1000 | XC2V3000 |

|------------------------------------------|--------|---------|----------|

| Voltage influence on FIT                 |        |         |          |

| Analysis of critical vs non critical SEU |        |         |          |

| Analysis of single event latchup         | √      | √       | V        |

| Bitmaps of errors                        |        |         | V        |

| Chip to chip variations                  |        |         | <b>√</b> |

| Special observations                     | V      | √       | √        |

Table 13. Detailed analysis for 14 MeV tests

Many of the detailed analysis cannot be performed for the AX1000 and APA1000 because no errors were observed for these devices.

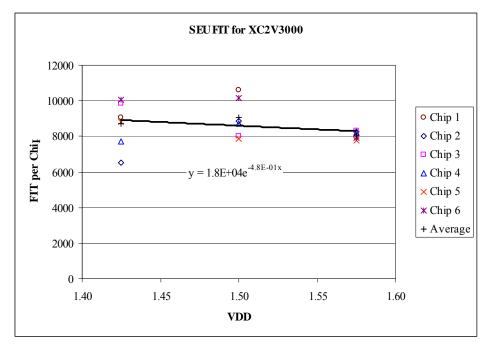

#### 4.4.1 Voltage influence on FIT

The SEFI and SEU FIT dependence vs VDD is presented in this section. The FIT is plotted separately for each chip. The FIT average of all chips is also plotted, and the average FIT is used to fit an exponential curve. Figure 4 and Figure 5 show a regular decrease of FIT at the higher VDD, as expected.

The FIT dispersion between chips is consistent with the accuracy assessments given in section 4.3.

Figure 4. SEFI FIT of XC2V3000 vs VDD

Figure 5. SEU FIT of XC2V3000 vs VDD

#### 4.4.2 Analysis of critical vs non critical SEU

The test strategy enables to identify the critical and the non critical SEU in the configuration memory, that is, those SEU in the configuration memory that create an SEFI, and those that do not create an SEFI.

Figure 6 presents the ratio SEFI / Total SEU for each chip and test condition. The overall ratio is 15% independent of the test condition.

Figure 6. SEFI vs Total SEU XC2V3000

#### 4.4.3 Analysis of single event latchup

Single event latchup (SEL) consists in the neutron induced activation of parasitic thyristor structures in the CMOS process. In case a process is sensitive to latchup, the latchup rate is higher at the higher voltage, temperature and particle energy.

Latchups result in increased current consumption, partial or total configuration memory wipe out, or complete loss of operation. Because the current is limited for protection, latchups lead to voltage shutdown to the DUT. The way the tester detects latchups is by monitoring the DUT supply voltages. In case a latchup is detected, the tester logs the event and switches the power off/on for recovering.

A particular case of latchup is the microlatchup. The microlatchup consists in the activation of a parasitic thyristor structure with weak on-resistance and a low increase of current consumption. In case of microlatchup, the voltage and current can find a stability point that cannot be detected by the tester. In this case, one or more chips are partially or totally wiped out, or experience complete loss of operation during the duration of a test condition.

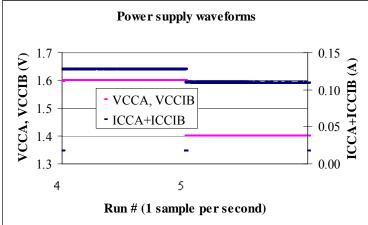

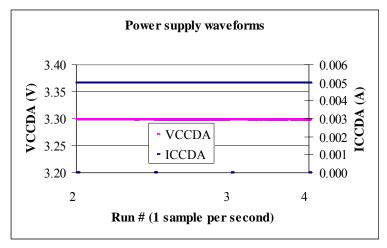

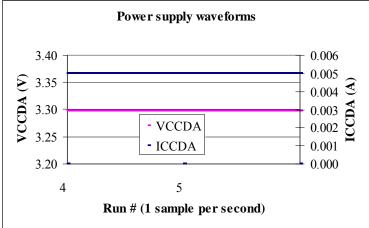

No latchups were detected for any of the devices and conditions tested. In the following subsections, the voltage and current waveforms, acquired during the experiments, will be presented for each device and test condition. The sensitivity to microlatchup will be analyzed by inspection of the voltage and current waveforms and correlation with the observed number of errors in each chip.

#### 4.4.3.1 AX1000

We observe regular voltage and current waveforms in Figure 7 and Figure 8. No errors were observed for any of the chips and conditions tested. Therefore, there is no indication of latchup.

Figure 7. AX1000 VCCA and VCCIB waveforms

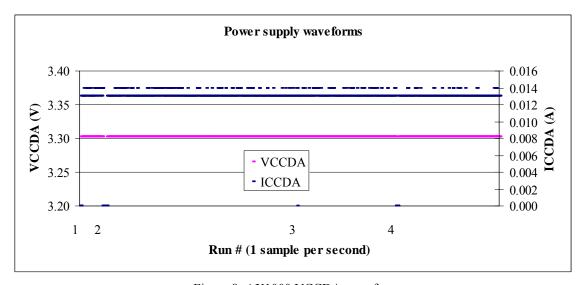

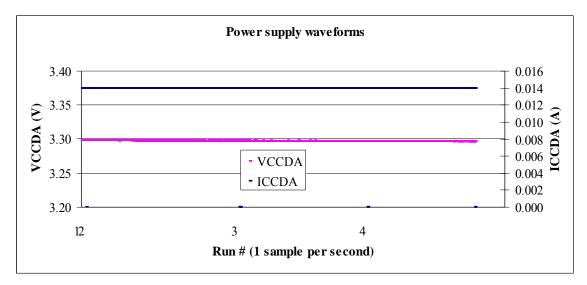

Figure 8. AX1000 VCCDA waveform

#### 4.4.3.2 APA1000

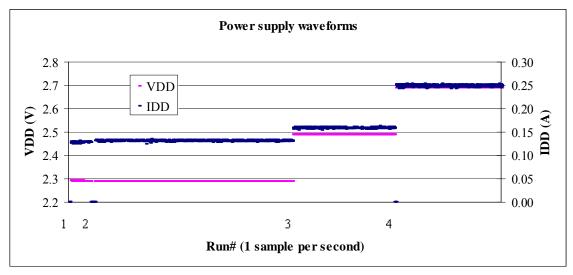

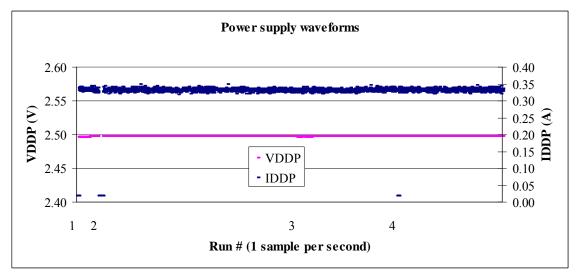

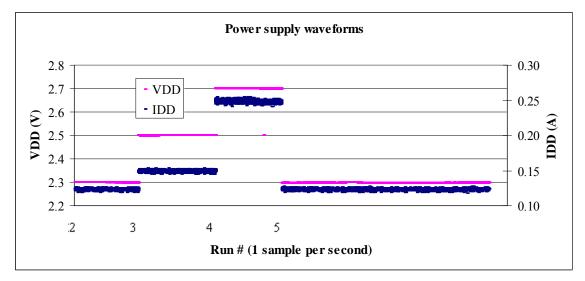

We observe regular voltage and current waveforms in Figure 9 and Figure 10. No errors were observed for any of the chips and conditions tested. Therefore, there is no indication of latchup.

Figure 9. APA1000 VDD waveform

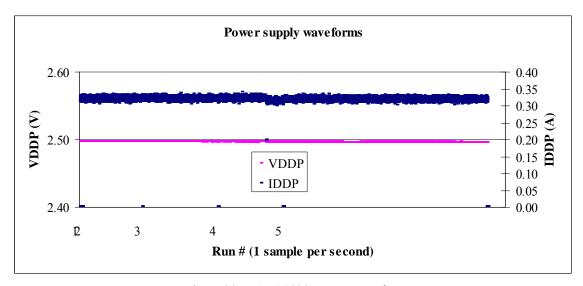

Figure 10. APA1000 VDDP waveform

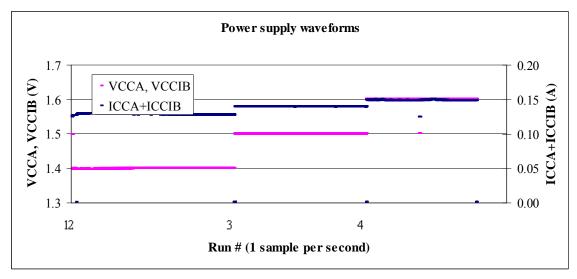

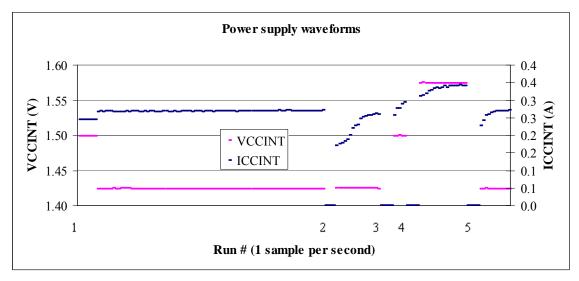

#### 4.4.3.3 XC2V3000

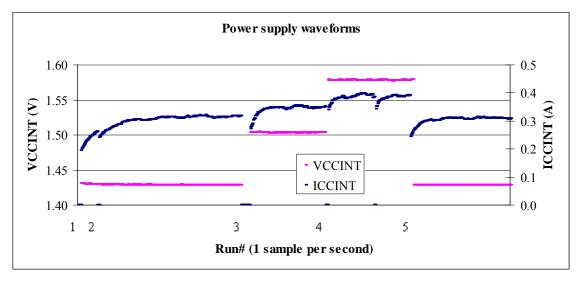

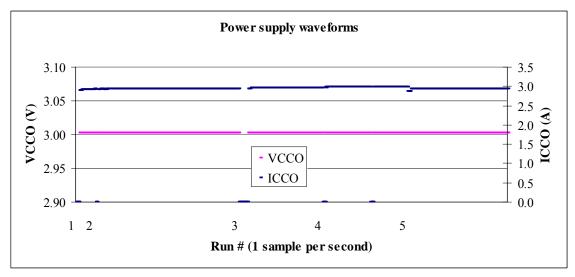

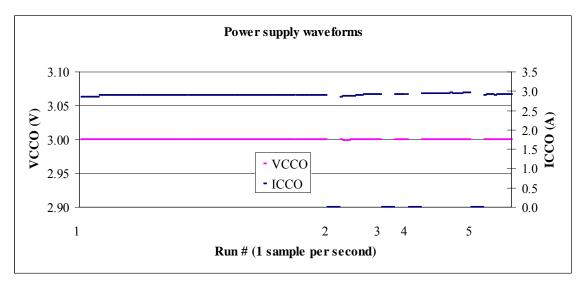

We observe regular voltage and current waveforms in Figure 11 and Figure 12. The number of errors, presented in the following table is regular across the six chips tested. Therefore, there is no indication of latchup.

Figure 11. XC2V3000 VCCINT waveform

Figure 12. XC2V3000 VCCO waveform

| Run #  | Condition | Number of SEFI |        |        |        |        |        |

|--------|-----------|----------------|--------|--------|--------|--------|--------|

| Kuii # | VDD       | Chip 1         | Chip 2 | Chip 3 | Chip 4 | Chip 5 | Chip 6 |

| 1      | 1.425     | 0              | 0      | 0      | 0      | 0      | 0      |

| 2      | 1.425     | 22             | 17     | 25     | 19     | 11     | 11     |

| 3      | 1.500     | 21             | 12     | 18     | 21     | 17     | 18     |

| 4      | 1.575     | 14             | 16     | 15     | 25     | 13     | 18     |

| 5      | 1.425     | 14             | 18     | 23     | 20     | 16     | 16     |

Table 14. XC2V3000 number of SEFI for each chip

Note: run #1 was a test run with the beam switched off, to test that the tester electronics was working correctly (cf section 3.3).

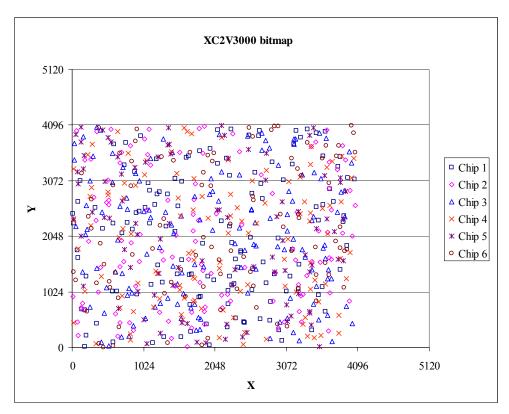

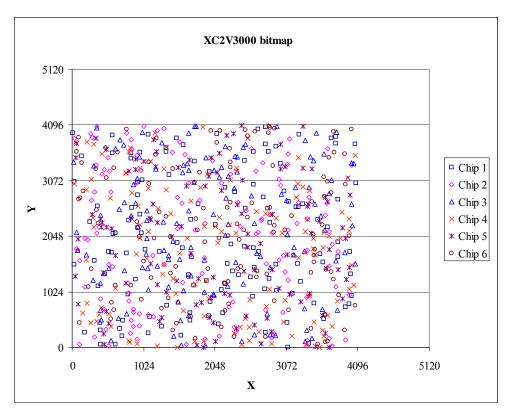

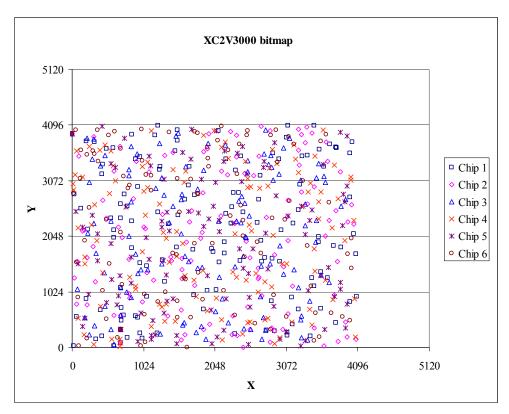

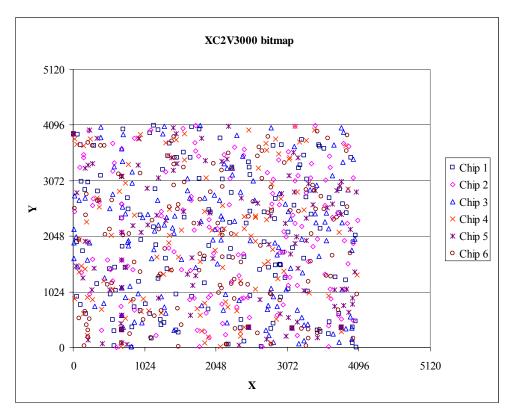

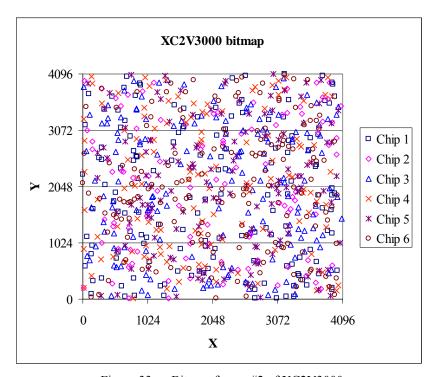

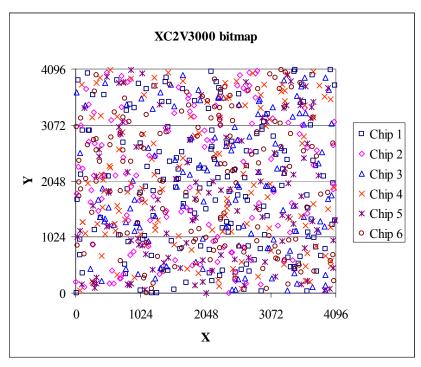

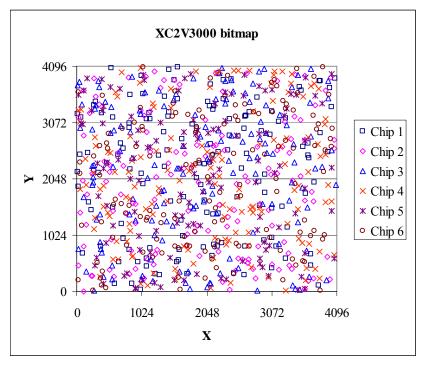

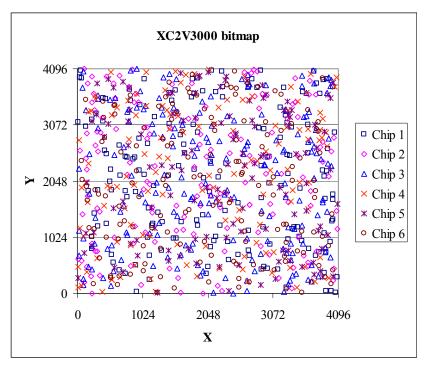

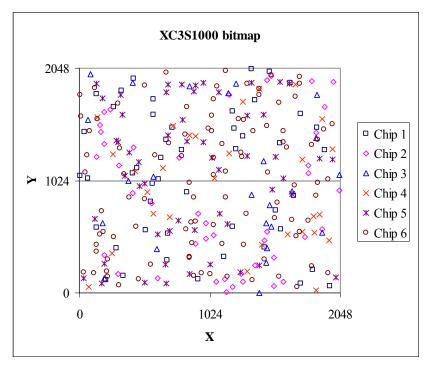

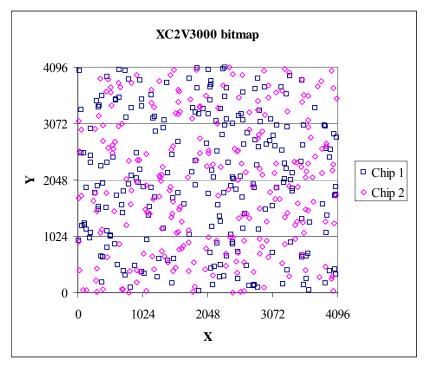

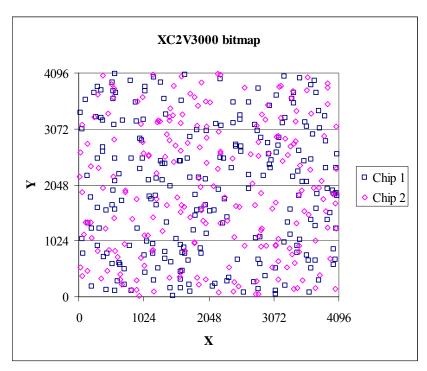

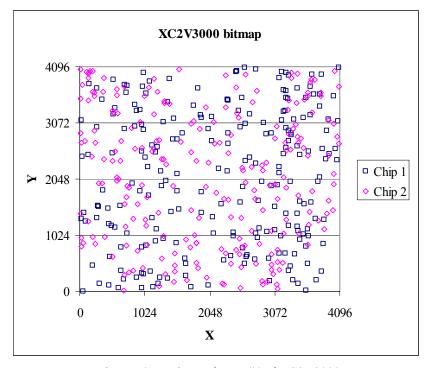

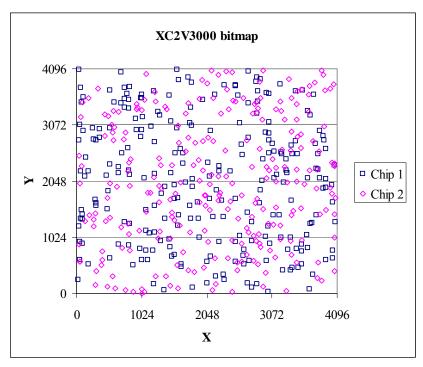

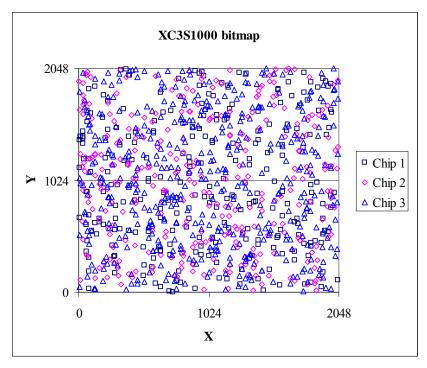

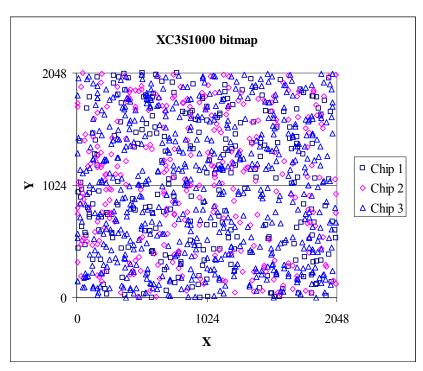

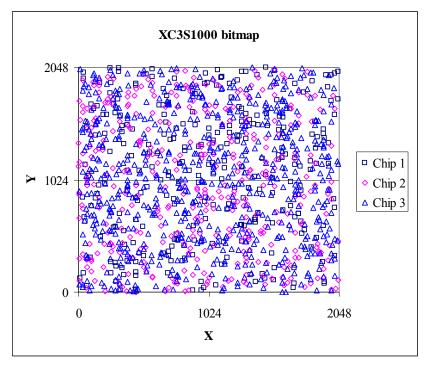

#### 4.4.4 Bitmaps of errors

Bitmaps allow to check the expected random distribution of errors in the configuration memory arrays.

Each point in the bitmap represents a failing address. The bitmaps are logical bitmaps, not physical bitmaps, because the layout of the configuration memory is not available. In the logical bitmaps, the address LSB are mapped in the x-axis and the address MSB are mapped in the y-axis.

The address refers to the location where the verification bitstream is stored in the tester memory. Valid addresses for the XC2V3000 are in the range 0x400069 to 0x5D4329. Each address holds 5 bits. Therefore, the verification bitstream length is 9,588,165 bits.

The bitmaps show the expected random distribution of errors.

Figure 13. Bitmap for run#2 of XC2V3000

Figure 14. Bitmap for run#3 of XC2V3000

Figure 15. Bitmap for run#4 of XC2V3000

Figure 16. Bitmap for run#5 of XC2V3000

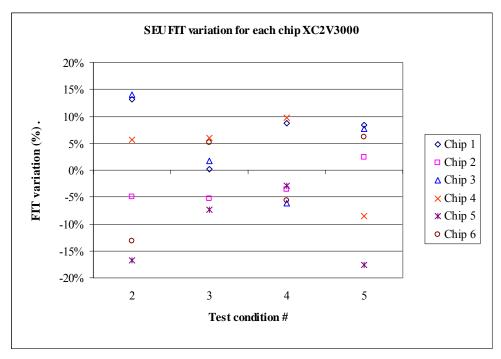

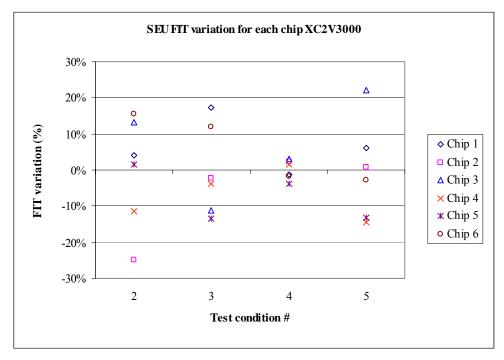

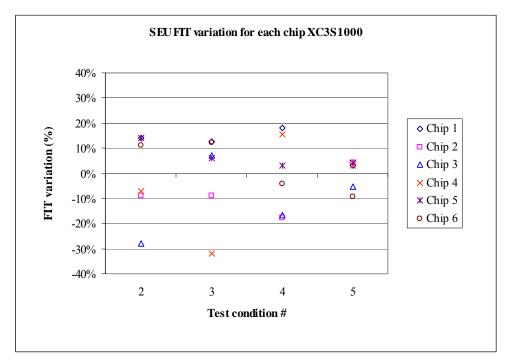

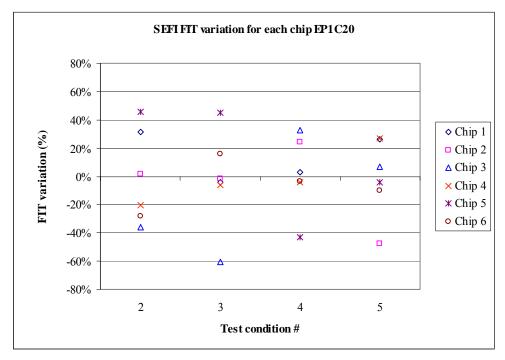

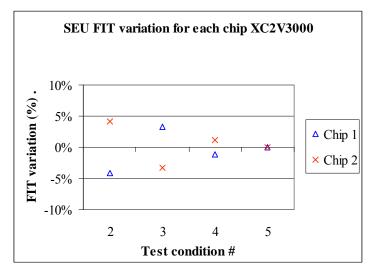

#### 4.4.5 Chip to chip variation

This section presents the chip to chip FIT variations observed. The objective of this section is to check the neutron flux uniformity.

The FIT variations shown in Figure 17 are defined as the variation relative to the average of the 6 chips tested.

FIT variation for chip(i) (%) =

$$\left(\frac{\text{FIT Chip(i)}}{\text{Average FIT Chips(1 to 6)}} - 1\right) \times 100$$

The FIT variations observed are within the expected statistical uncertainty: -17% to +19%, see Table 12. Therefore, we verify that the neutron flux is uniform.

Figure 17. Chip to chip FIT variation

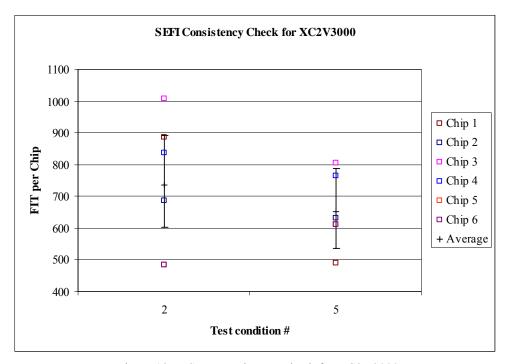

#### 4.4.6 Consistency check

A consistency test (repetition of the first condition) has been carried out at the end of the test sequence. The consistency test verifies the stability of the beam, DUT and tester.

Figure 18 verifies that the results of runs #2 and #5 are consistent, taking into account the statistical uncertainty shown by the error bars.

Figure 18. SEFI consistency check for XC2V3000

#### 4.4.7 Special observations

A verify operation using the Flash Pro programmer was performed for the APA1000 chips, at the end of the radiation tests performed. The verify operation was successful for all the APA1000 chips.

## 5 14 MeV conclusions

The preliminary cosmic-ray SER of AX1000, APA1000 and XC2V3000 devices was measured using 14 MeV neutrons at the Interfaculty Reactor Institute (IRI) at Delft in The Netherlands in December 2003.

Table 15 presents the overall cosmic-ray FIT for each device at sea level in NYC. The overall FIT is calculated as the average of all chips and test conditions for the XC2V3000.

| Device   | Overall<br>FIT (SEFI)<br>per Device | Overall<br>FIT (SEU)<br>per Device |

|----------|-------------------------------------|------------------------------------|

| AX1000   | < 0.017                             | < 0.017                            |

| APA1000  | < 0.026                             | < 0.026                            |

| XC2V3000 | 680                                 | 4700                               |

Table 15. Overall cosmic-ray FIT at sea level in NYC

In Table 15, it is important to understand that no errors were observed for the AX1000 and APA1000, for any of the test conditions. The given figure of FIT is an upper bound calculated considering one error for all chips and test conditions. The AX1000 and APA1000, based in Antifuse and Flash processes respectively, are considered insensitive to 14 MeV neutrons, therefore extending the test for longer periods would still produce no errors, and result in lower bounds of FIT.

The neutron flux increases with altitude, and has a maximum at approximately 60,000 ft. The FIT at sea level, 5,000 ft, 30,000 ft and 60,000 ft is provided in Table 16.

| Device   | FIT (SEFI) at sea level | FIT (SEFI) at 5,000 ft | FIT (SEFI) at 30,000 ft | FIT (SEFI) at 60,000 ft |  |  |

|----------|-------------------------|------------------------|-------------------------|-------------------------|--|--|

| AX1000   | < 0.017                 | < 0.058                | <2.5                    | <8.1                    |  |  |

| APA1000  | < 0.026                 | < 0.089                | <3.8                    | <12                     |  |  |

| XC2V3000 | 680                     | 2,300                  | 99,000                  | 320,000                 |  |  |

Table 16. Overall cosmic-ray FIT at different altitudes

No occurrences of latchup have been observed for any of the devices.

No errors in the configuration circuitry of the XC2V3000 were observed.

No hard errors were observed for any of the devices.

It is important to understand that we approximate the full energy spectrum cross-section by the cross-section at 14 MeV. The approximation results in a lower estimate of the full spectrum cross-section, that could be up to 50% higher than the 14 MeV cross-section. Additionally, devices that are not sensitive to latchup for 14 MeV neutrons, can be sensitive for neutrons of higher energy. Therefore, full spectrum tests at LANSCE will be performed to consolidate these preliminary results.

## **6 LANSCE tests**

#### 6.1 Tested conditions and schedule

The following tables provide the sequence of conditions that were tested. Additionally to the test conditions, stability and consistency checks have been performed at the beginning and the end of each test sequence. A stability test (beam off) has been carried out before irradiation (cf. section 6.3). A consistency test (repetition of the first condition) has been carried out at the end of the test sequence. The order of the test conditions follows the Test Plan [3].

The tables are extracted from the campaign logbook files in appendix A.2.

| Run # | Device | Energy (MeV) | Start  |          | Stop   |          | Condition |     |      |

|-------|--------|--------------|--------|----------|--------|----------|-----------|-----|------|

|       |        |              | Date   | Time     | Date   | Time     | Cycle     | VDD | Temp |

| 1     | AX1000 | LANSCE       | 17-Feb | 14:27:15 | 17-Feb | 14:38:02 | 200ns     | 1.4 | 25°C |

| 2     | AX1000 | LANSCE       | 17-Feb | 15:46:19 | 17-Feb | 22:40:35 | 200ns     | 1.4 | 25°C |

| 3     | AX1000 | LANSCE       | 17-Feb | 22:41:50 | 18-Feb | 4:27:11  | 200ns     | 1.5 | 25°C |

| 4     | AX1000 | LANSCE       | 18-Feb | 4:28:29  | 18-Feb | 9:46:52  | 200ns     | 1.6 | 25°C |

| 5     | AX1000 | LANSCE       | Note 1 | Note 1   | Note 1 | Note 1   | 200ns     | 1.4 | 25°C |

Table 17. Conditions tested for AX1000

Note 1: The consistency check, run #5, was not done for the AX1000 because no errors were observed for any of the conditions tested.

| Run # | Device  | Energy (MeV) | Start  |          | Stop   |          | Condition |     |      |

|-------|---------|--------------|--------|----------|--------|----------|-----------|-----|------|

|       |         |              | Date   | Time     | Date   | Time     | Cycle     | VDD | Temp |

| 1     | APA1000 | LANSCE       | 18-Feb | 10:36:44 | 18-Feb | 10:46:44 | 200ns     | 2.3 | 25°C |

| 2     | APA1000 | LANSCE       | 18-Feb | 10:47:46 | 18-Feb | 15:21:14 | 200ns     | 2.3 | 25°C |

| 3     | APA1000 | LANSCE       | 18-Feb | 15:22:12 | 18-Feb | 21:07:56 | 200ns     | 2.5 | 25°C |

| 4     | APA1000 | LANSCE       | 18-Feb | 21:09:08 | 19-Feb | 5:55:00  | 200ns     | 2.7 | 25°C |

| 5     | APA1000 | LANSCE       | 19-Feb | 5:56:33  | 19-Feb | 21:26:26 | 200ns     | 2.3 | 25°C |

Table 18. Conditions tested for APA1000

No errors were observed for any of the conditions tested for the APA1000. The consistency check, run #5, was done because beam time was available, to increase the fluence and thus the accuracy of the FIT bound.

| Run # | Device   | Energy | S      | tart     | S      | Stop     | C     | Condition |      |

|-------|----------|--------|--------|----------|--------|----------|-------|-----------|------|

|       | Device   | (MeV)  | Date   | Time     | Date   | Time     | Cycle | VDD       | Temp |

| 1     | XC2V3000 | LANSCE | 17-Feb | 14:28:11 | 17-Feb | 14:38:56 | 200ns | 1.425     | 25°C |

| 2     | XC2V3000 | LANSCE | 17-Feb | 15:46:53 | 17-Feb | 15:57:28 | 200ns | 1.425     | 25°C |

| 3     | XC2V3000 | LANSCE | 17-Feb | 15:59:04 | 17-Feb | 16:09:44 | 200ns | 1.500     | 25°C |

| 4     | XC2V3000 | LANSCE | 17-Feb | 16:10:38 | 17-Feb | 16:22:29 | 200ns | 1.575     | 25°C |

| 5     | XC2V3000 | LANSCE | 17-Feb | 16:23:38 | 17-Feb | 16:35:45 | 200ns | 1.425     | 25°C |

Table 19. Conditions tested for XC2V3000

| Run # | Device   | Energy | Start  |          | Stop   |          | Condition |       |      |

|-------|----------|--------|--------|----------|--------|----------|-----------|-------|------|

|       |          | (MeV)  | Date   | Time     | Date   | Time     | Cycle     | VDD   | Temp |

| 1     | XC3S1000 | LANSCE | 17-Feb | 17:16:20 | 17-Feb | 17:25:22 | 200ns     | 1.140 | 25°C |

| 2     | XC3S1000 | LANSCE | 17-Feb | 17:25:56 | 17-Feb | 17:51:15 | 200ns     | 1.140 | 25°C |

| 3     | XC3S1000 | LANSCE | 17-Feb | 17:52:36 | 17-Feb | 19:40:45 | 200ns     | 1.200 | 25°C |

| 4     | XC3S1000 | LANSCE | 17-Feb | 19:41:23 | 17-Feb | 20:07:31 | 200ns     | 1.260 | 25°C |

| 5     | XC3S1000 | LANSCE | 17-Feb | 20:08:11 | 17-Feb | 20:23:55 | 200ns     | 1.140 | 25°C |

Table 20. Conditions tested for XC3S1000

| Run # | Davias | Energy | S      | Start    | S      | Stop     | Conditio |       | n    |

|-------|--------|--------|--------|----------|--------|----------|----------|-------|------|

|       | Device | (MeV)  | Date   | Time     | Date   | Time     | Cycle    | VDD   | Temp |

| 1     | EP1C20 | LANSCE | 17-Feb | 20:58:26 | 17-Feb | 21:08:40 | 200ns    | 1.425 | 25°C |

| 2     | EP1C20 | LANSCE | 17-Feb | 21:09:30 | 17-Feb | 21:27:50 | 200ns    | 1.425 | 25°C |

| 3     | EP1C20 | LANSCE | 17-Feb | 21:49:43 | 17-Feb | 22:03:20 | 200ns    | 1.500 | 25°C |

| 4     | EP1C20 | LANSCE | 17-Feb | 22:04:36 | 17-Feb | 22:21:21 | 200ns    | 1.575 | 25°C |

| 5     | EP1C20 | LANSCE | 17-Feb | 22:22:38 | 17-Feb | 22:39:26 | 200ns    | 1.425 | 25°C |

Table 21. Conditions tested for EP1C20

## **6.2** Devices tested

The following tables show the lot codes of the chips that were actually tested:

| Chip 1          | Chip 2         | Chip 3         |

|-----------------|----------------|----------------|

| DOAAJ1<br>0320  | DOJC21<br>0345 | DOJC21<br>0345 |

| Chip 4          | Chip 5         |                |

| DOH5S21<br>0331 | DOJC21<br>0345 |                |

Table 22. Lot codes of the AX1000 chips tested

| Chip 1        | Chip 2        | Chip 3        |

|---------------|---------------|---------------|

| MF7G7<br>0247 | MF7G7<br>0247 | MF7G7<br>0247 |

| Chip 4        | Chip 5        |               |

| MF7G7<br>0247 | MF7G7<br>0247 |               |

Table 23. Lot codes of the APA1000 chips tested

| Chip 1    | Chip 2    | Chip 3    |  |  |

|-----------|-----------|-----------|--|--|

| AGT0337   | AGT0337   | AGT0337   |  |  |

| F2149925A | F2149925A | F2149925A |  |  |

| Chip 4    | Chip 5    | Chip 6    |  |  |

| AGT0337   | AGT0337   | AGT0337   |  |  |

| F2149925A | F2149925A | F2149925A |  |  |

Table 24. Lot codes of the XC2V3000 chips tested

| Chip 1       | Chip 2       | Chip 3       |  |  |

|--------------|--------------|--------------|--|--|

| FT256AFQ0341 | FT256AFQ0341 | FT256AFQ0341 |  |  |

| D13989A      | D13989A      | D13990A      |  |  |

| Chip 4       | Chip 5       | Chip 6       |  |  |

| FT256AFQ0341 | FT256AFQ0341 | FT256AFQ0341 |  |  |

| D13989A      | D13989A      | D13989A      |  |  |

Table 25. Lot codes of the XC3S1000 chips tested

| Chip 1       | Chip 2       | Chip 3       |  |  |

|--------------|--------------|--------------|--|--|

| EP1C20F324C8 | EP1C20F324C8 | EP1C20F324C8 |  |  |

| AAD900313A   | AAD900313A   | AAD900313A   |  |  |

| Chip 4       | Chip 5       | Chip 6       |  |  |

| EP1C20F324C8 | EP1C20F324C8 | EP1C20F324C8 |  |  |

| AAD900313A   | AAD900313A   | AAD900313A   |  |  |

Table 26. Lot codes of the EP1C20 chips tested

## 6.3 Stability without neutron beam

An error rate measurement is performed with the beam off and with the components placed in the target. The components are in the real environment with the real electromagnetic parasitic. This aims at verifying the robustness of both the tester and the DUT boards against the real noisy environment.

This experiment was done during 10 minutes for each DUT board and no error occurred (cf run #1 in Table 17 to Table 21).

# **7 LANSCE results**

## 7.1 Cross-section and FIT calculation

The cross-section defines the sensitivity of a device. The cross-section per chip, as a function of neutron energy E, is defined as  $\sigma(E)=N/(F^*C)$  where N is the total number of errors, F is the fluence and C is the number of chips tested. In this document, the cross-section is given in cm<sup>2</sup>/chip.

Since the WNR neutron beam has a neutron energy spectrum very similar to the terrestrial neutron energy spectrum, the cross-section per bit obtained at WNR can be used directly to estimate the terrestrial failure rate.

Figure 19. Cosmic-ray neutron flux at ground level

According to the JESD89 specification [2], the FIT rate is calculated using the value of neutron flux for New-York City,  $f_{\rm NYC}$  =14 n/cm<sup>2</sup>/hour for neutrons with energy above 10 MeV. The FIT is calculated in this report for one device. Thus, the FIT is given by the following formula:

$$FIT = \sigma * f_{NYC} * 10^9 (errors/10^9 hour)$$

Where  $\sigma$  is the cross-section given in cm<sup>2</sup>/chip, and  $f_{NYC}$  is the flux given in n/cm<sup>2</sup>/hour.

The FIT is calculated using the neutron flux for the New-York City at sea level. The neutron flux depends on the altitude and location. Appendix E of the JESD89 specification [2] shows how to adjust the error rates calculated for the NYC for other locations.

## 7.2 Overall FIT results

Table 27 presents the overall cosmic-ray FIT for each device at sea level in NYC. The overall FIT is calculated as the average of all chips and test conditions for the XC2V3000, XC3S1000 and EP1C20 devices. Appendix A details the cross-section and FIT for each chip and test condition.

| Device   | Overall<br>FIT (SEFI)<br>per Device | Overall<br>FIT (SEU)<br>per Device |

|----------|-------------------------------------|------------------------------------|

| AX1000   | < 0.082                             | < 0.082                            |

| APA1000  | < 0.038                             | < 0.038                            |

| XC2V3000 | 1,150                               | 8,680                              |

| XC3S1000 | 320                                 | 1,240                              |

| EP1C20   | 460                                 | n/a                                |

Table 27. Overall cosmic-ray FIT at sea level in NYC

In Table 27, it is important to understand that no errors were observed for the AX1000 and APA1000, for any of the test conditions. The given figure of FIT is an upper bound calculated considering one error for all chips and test conditions. The AX1000 and APA1000, based in Antifuse and Flash processes respectively, are considered insensitive to terrestrial spectrum of neutrons, therefore extending the test for longer periods would still produce no errors, and result in lower bounds of FIT.

The readback of the configuration memory is not available for the EP1C20. Therefore, the SEU FIT could not be measured for the EP1C20.

The neutron flux increases with altitude, and has a maximum at approximately 60,000 ft. The FIT at sea level, 5,000 ft, 30,000 ft and 60,000 ft is provided in Table 28.

| Device   | FIT (SEFI) at sea level | FIT (SEFI) at 5,000 ft | FIT (SEFI) at 30,000 ft | FIT (SEFI) at 60,000 ft |

|----------|-------------------------|------------------------|-------------------------|-------------------------|

| AX1000   | < 0.082                 | < 0.28                 | <12                     | <39                     |

| APA1000  | < 0.038                 | < 0.13                 | < 5.6                   | <18                     |

| XC2V3000 | 1,150                   | 3,900                  | 170,000                 | 540,000                 |

| XC3S1000 | 320                     | 1,100                  | 47,000                  | 150,000                 |

| EP1C20   | 460                     | 1,600                  | 67,000                  | 220,000                 |

Table 28. Overall cosmic-ray FIT at different altitudes

The altitude effect at 5,000 ft and 30,000 ft is evaluated using the formula provided in appendix E of JESD89 [2]:

Neutron flux  $(n/cm^2/hour) = 15E3 * e^{-(A/148)}$

Where the altitude, a, in feet above sea level, is expressed as the areal density of the air column, A, in units of g/cm<sup>2</sup>. The altitude, a, can be converted to the areal density, A using the following equation:

$$A = 1033 \times \exp[-.03813 \times (a/1000) -.00014 \times (a/1000)^2 +6.4E-7 \times (a/1000)^3]$$

The altitude effect at 60,000 ft is evaluated using Figure 3 from reference [4].

### 7.3 Accuracy of results

The accuracy of the cross-section results is assessed in this section. The accuracy of the cross-section is the sum of the error count and fluence measurement accuracies.

#### 7.3.1 Error count statistics

The error count is generally described by a Poisson distribution, cf appendix C.1 in [2]. If N errors occur, the mean error count is approximated by N. The standard deviation is given by  $\sqrt{N}$ .

The error count can be bounded using the upper and lower limits in Table 11, extracted from appendix C.2 of [2]. In using this table, the first column is the actual number of events observed in the experiment. The upper and lower limits define the 95% confidence interval for the true mean of the distribution. The upper and lower limits for any number of events can be calculated using the formulas given in appendix B.

The accuracy of the error count is defined in this report using 95% confidence intervals. The 95% confidence limits depend on the number of errors observed. The number of errors is detailed in appendix A for each chip and test condition.

The following table summarizes the 95% confidence intervals for each device. For example, the overall number of SEFI per chip and test condition is 15 for the XC2V3000. By using the formulas given in appendix B, we find that the lower and upper limits are 8.4 and 24.7 respectively. The limits in Table 29 are calculated as (Lower limit/Mean error count -1)\*100 = -44%, and (Upper limit/Mean error count -1)\*100 = +65%.

| Device   | Error type | Errors | Lower limit | Upper limit | Comment                                  |

|----------|------------|--------|-------------|-------------|------------------------------------------|

| AX1000   | SEFI       | 0      | n/a         | n/a         | No errors observed                       |

| APA1000  | SEFI       | 0      | n/a         | n/a         | No errors observed                       |

|          |            | 15     | -44%        | 65%         | Errors per chip and test condition       |

|          | SEFI       | 87     | -20%        | 23%         | Errors for all chips per test condition  |

| XC2V3000 |            | 349    | -10%        | 11%         | Errors for all chips and test conditions |

|          | SEU        | 144    | -16%        | 18%         | Errors per chip and test condition       |

|          |            | 865    | -7%         | 7%          | Errors for all chips per test condition  |

|          | SEFI       | 17     | -42%        | 60%         | Errors per chip and test condition       |

|          |            | 101    | -19%        | 22%         | Errors for all chips per test condition  |

| XC3S1000 |            | 405    | -10%        | 10%         | Errors for all chips and test conditions |

|          | SEU        | 81     | -21%        | 24%         | Errors per chip and test condition       |

|          | SEU        | 484    | -9%         | 9%          | Errors for all chips per test condition  |

|          |            | 19     | -40%        | 56%         | Errors per chip and test condition       |

| EP1C20   | SEFI       | 113    | -18%        | 20%         | Errors for all chips per test condition  |

|          |            | 453    | -9%         | 10%         | Errors for all chips and test conditions |

Table 29. 95% confidence intervals for all devices

## 7.3.2 Fluence measurement accuracy

The accuracy of the fluence measurement is better than 5% for the LANSCE facility.

## 7.4 <u>Detailed analysis</u>

Detailed analysis of the results is presented hereafter. The following table summarizes the analyses presented for each device:

| Analysis                                 | AX1000 | APA1000 | XC2V3000  | XC3S1000  | EP1C20       |

|------------------------------------------|--------|---------|-----------|-----------|--------------|

| Voltage influence on FIT                 |        |         | $\sqrt{}$ | $\sqrt{}$ | $\checkmark$ |

| Analysis of critical vs non critical SEU |        |         | V         |           |              |

| Analysis of single event latchup         | √      | √       | √         | √         |              |

| Bitmaps of errors                        |        |         | V         |           |              |

| Chip to chip variations                  |        |         | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$    |

| Special observations                     | V      | V       | V         | V         | V            |

Table 30. Detailed analysis for LANSCE tests

Many of the detailed analysis cannot be performed for the AX1000 and APA1000 because no errors were observed for these devices.

#### 7.4.1 Voltage influence on FIT

The SEFI and SEU FIT dependence vs VDD is presented in this section. The FIT is plotted separately for each chip. The FIT average of all chips is also plotted, and the average FIT is used to fit an exponential curve.

#### 7.4.1.1 XC2V3000

Figure 20 does not show a regular decrease of SEFI FIT at the higher VDD, as measured with 14 MeV neutrons. This is partially explained because of the statistical uncertainty of SEFI events, ±20% as shown in Table 29. Figure 21 shows a regular decrease of SEU FIT at the higher VDD, as expected.

The FIT dispersion between chips is consistent with the accuracy assessments given in section 7.3.

Figure 20. SEFI FIT of XC2V3000 vs VDD

Figure 21. SEU FIT of XC2V3000 vs VDD

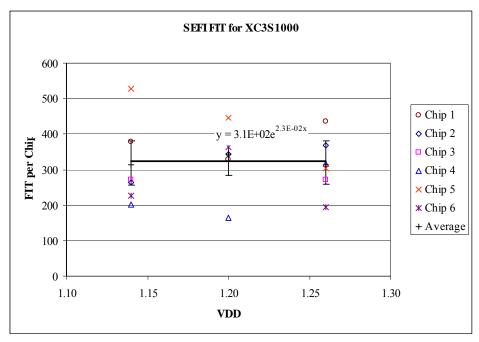

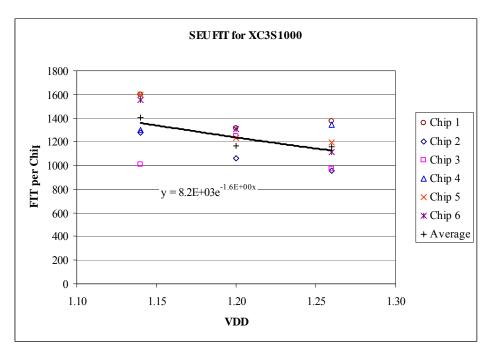

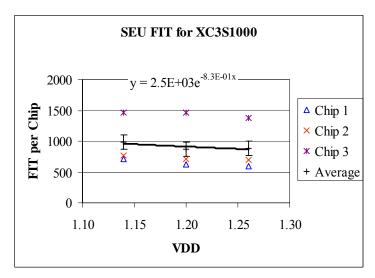

#### 7.4.1.2 XC3S1000

Figure 22 does not show a regular decrease of SEFI FIT at the higher VDD, as expected. This is partially explained because of the statistical uncertainty of SEFI events,  $\pm 20\%$  as shown in Table 29. Figure 23 shows a regular decrease of SEU FIT at the higher VDD, as expected.

The FIT dispersion between chips is consistent with the accuracy assessments given in section 7.3.

Figure 22. SEFI FIT of XC3S1000 vs VDD

Figure 23. SEU FIT of XC3S1000 vs VDD

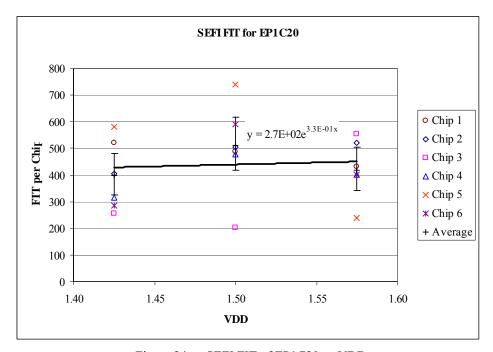

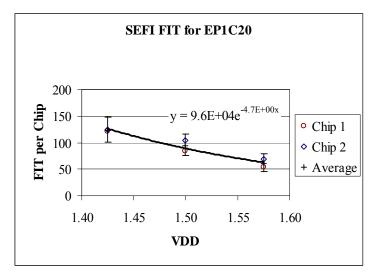

#### 7.4.1.3 EP1C20

Figure 24 does not show a regular decrease of SEFI FIT at the higher VDD, as expected. This is partially explained because of the statistical uncertainty of SEFI events,  $\pm 20\%$  as shown in Table 29.

The FIT dispersion between chips is consistent with the accuracy assessments given in section 7.3.

Figure 24. SEFI FIT of EP1C20 vs VDD

#### 7.4.2 Analysis of critical vs non critical SEU

The test strategy enables to identify the critical and the non critical SEU in the configuration memory, that is, those SEU in the configuration memory that create an SEFI, and those that do not create an SEFI.

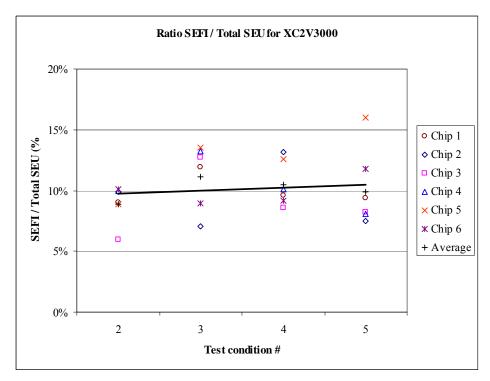

#### 7.4.2.1 XC2V3000

Figure 25 presents the ratio SEFI / Total SEU for each chip and test condition. The overall ratio is 10% independent of the test condition.

Figure 25. SEFI vs Total SEU XC2V3000

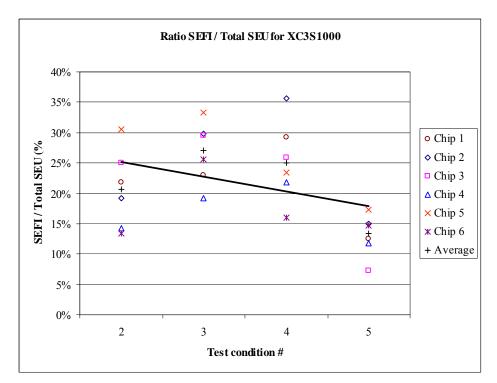

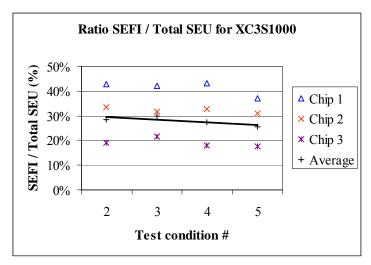

#### 7.4.2.2 XC3S1000

Figure 26 presents the ratio SEFI  $\!\!\!/$  Total SEU for each chip and test condition. The overall ratio is 22% independent of the test condition.

Figure 26. SEFI vs Total SEU XC3S1000

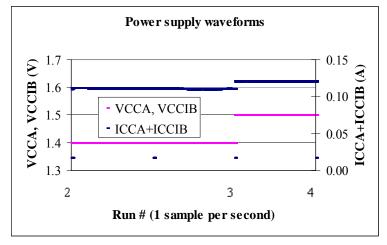

#### 7.4.3 Analysis of single event latchup

Single event latchup (SEL) consists in the neutron induced activation of parasitic thyristor structures in the CMOS process. In case a process is sensitive to latchup, the latchup rate is higher at the higher voltage, temperature and particle energy.