# Identify® Actel Edition Tutorial

September 2010

http://solvnet.synopsys.com

#### **Disclaimer of Warranty**

Synopsys, Inc. makes no representations or warranties, either expressed or implied, by or with respect to anything in this manual, and shall not be liable for any implied warranties of merchantability or fitness for a particular purpose of for any indirect, special or consequential damages.

### **Copyright Notice**

Copyright © 2010 Synopsys, Inc. All Rights Reserved.

Synopsys software products contain certain confidential information of Synopsys, Inc. Use of this copyright notice is precautionary and does not imply publication or disclosure. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form by any means without the prior written permission of Synopsys, Inc. While every precaution has been taken in the preparation of this book, Synopsys, Inc. assumes no responsibility for errors or omissions. This publication and the features described herein are subject to change without notice.

### Trademarks

#### **Registered Trademarks (®)**

Synopsys, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, CHIPit, CoMET, Design Compiler, DesignWare, Formality, Galaxy Custom Designer, HAPS, HapsTrak, HDL Analyst, HSIM, HSPICE, Identify, Leda, MAST, METeor, ModelTools, NanoSim, OpenVera, PathMill, Physical Compiler, PrimeTime, SCOPE, Simply Better Results, SiVL, SNUG, SolvNet, Syndicated, Synplicity, the Synplicity logo, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, UMRBus, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

#### Trademarks (™)

AFGen, Apollo, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Confirma, Cosmos, CosmosLE, CosmosScope, CRITIC, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, Design-erHDL, DesignPower, Direct Silicon Access, Discovery, Eclypse, Encore,

EPIC, Galaxy, HANEX, HAPS, HapsTrak, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping System, HSIM, HSIM<sup>plus</sup>, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, Physical Analyst, Planet, Planet-PL, Polaris, Power Compiler, Raphael, Saturn, Scirocco, Scirocco-i, Star-RCXT, Star-SimXT, System Compiler, System Designer, Taurus, TotalRecall, TSUPREM-4, VCS Express, VCSi, VHDL Compiler, VirSim, and VMC are trademarks of Synopsys, Inc.

#### Service Marks (SM)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license. ARM and AMBA are registered trademarks of ARM Limited. Saber is a registered trademark of SabreMark Limited Partnership and is used under license. All other product or company names may be trademarks of their respective owners.

### **Restricted Rights Legend**

Government Users: Use, reproduction, release, modification, or disclosure of this commercial computer software, or of any related documentation of any kind, is restricted in accordance with FAR 12.212 and DFARS 227.7202, and further restricted by the Synopsys Software License and Maintenance Agreement. Synopsys, Inc., Synplicity Business Group, 700 East Middlefield Road, Mountain View, CA 94043, U. S. A.

Printed in the U.S.A September 2010

# Contents

#### **Chapter 1: Getting Started**

| The Debugging System       8         Identify Instrumentor       9         Identify Debugger       9 | 9 |

|------------------------------------------------------------------------------------------------------|---|

| Design Flow                                                                                          | С |

| Tutorial Requirements       1 <sup>-</sup> Hardware/Software Environments       1 <sup>-</sup>       |   |

#### **Chapter 2: The Tutorial Design**

| Design Schematic        | 14 |

|-------------------------|----|

| Verilog Tutorial Design | 15 |

| VHDL Tutorial Design    | 18 |

#### **Chapter 3: Instrumenting Your Design**

| Launching the Identify Instrumentor2                                                                                                  | 22 |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Setting up the IICE       2         Setting the Common IICE Parameters       2         Setting the Individual IICE Parameters       2 | 26 |

| Selecting the Instrumentation       3         VHDL Design Instrumentation       3         Verilog Design Instrumentation       3      | 30 |

| Writing the Instrumented Design                                                                                                       | 36 |

#### Chapter 4: Implementing the Design

| Synthesis          | 40 |

|--------------------|----|

| Place and Route    | 41 |

| Program the Device | 41 |

### Chapter 5: Debugging Your Design

| Starting the Identify Debugger                                                                                                                               | 43             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Specifying the JTAG Cable                                                                                                                                    | 45             |

| Setting the JTAG Chain                                                                                                                                       | 46             |

| Setting Up Triggers and Capturing Data<br>Triggering on a Breakpoint<br>Deactivating a Breakpoint<br>Triggering on a Watchpoint<br>Using the Complex Counter | 48<br>51<br>51 |

| Generating Waveforms                                                                                                                                         | 55             |

# Getting Started

The Identify<sup>®</sup> Actel Edition tool set is an innovative set of programmable hardware tools that lets you debug your HDL design:

- In the target system,

- At the target speed,

- At the VHDL/Verilog RTL Source level.

The Identify Actel Edition tool set enables the debugging of FPGA designs, FPGA-based prototypes, and system-on-a-chip designs. For the first time, you can debug live hardware using intuitive, HDL-based debugging techniques that provide visibility into the internal operation of your system.

The Identify Actel Edition tool set easily integrates into your existing design flow so that minimal effort is required to begin the debugging of your HDL designs. To better understand how the tool set works and how it works with your HDL design flow, this guide provides comprehensive information about navigating through the Identify tools and integrating with your other design flow tools.

This remainder of this chapter describes:

- The Debugging System

- Design Flow

- Tutorial Requirements

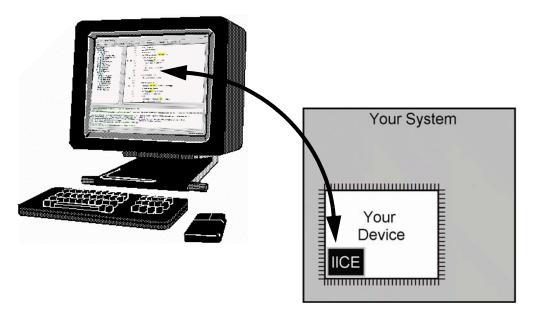

# The Debugging System

The Identify Actel Edition tool set is based on the principle of in-system debugging. Using thes Identify tool set allows you to debug your device in the target system, at target speed while still debugging at the HDL level.

The Identify instrumentor captures your device's internal states by inserting probe hardware (called an IICE<sup>™</sup> – Intelligent In-Circuit-Emulator) into your design. The IICE captures internal design states based on user-specified trigger conditions. Data captured at the target device is transferred back to the host computer where it is transformed and displayed by the Identify debugger.

The Identify tool set is a dual-component software system consisting of:

- The Identify instrumentor which inserts and configures the IICE

- The Identify debugger which controls the IICE and displays data from the IICE.

The following sections briefly describe these two software components.

### **Identify Instrumentor**

The Identify instrumentor reads and analyzes the HDL description of a design and provides you with detailed information about the signals that can be sampled and the locations in the source code where breakpoints can be set. This information is collectively referred to as the *instrumentation*.

The Identify instrumentor uses the HDL design files and your selected instrumentation information to create a custom IICE block. The Identify instrumentor then connects one or more IICE blocks to the appropriate locations in the design.

Finally, the Identify instrumentor re-writes your HDL design with the modifications necessary to implement and connect the IICE blocks. The modified HDL design is written to a different location so that it does not overwrite your original design.

### **Identify Debugger**

The Identify debugger lets you interact with your real hardware at the HDL level. In the Identify debugger, you set trigger conditions to determine when to capture data, and then view the captured data as either annotated source code or as waveforms.

# **Design Flow**

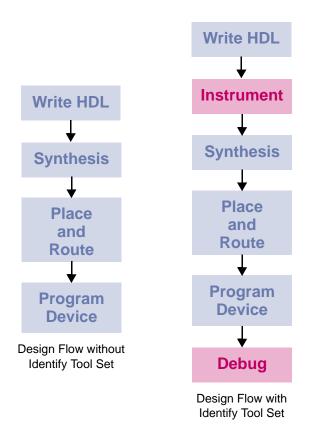

Design flows for HDL design and debugging vary according to the type of hardware and device you use. Displayed below is the typical HDL design flow without the Identify tool set on the left and a typical HDL design flow with the Identify tool set on the right.

In the design flow without the Identify tool set, the first step is to create the HDL source files for the design. Next, the design is synthesized to the target device. Once synthesized, the design is placed and routed before it is finally implemented in the target device.

The design flow with the Identify tool set adds two steps to the standard flow – one step at the beginning and one step at the end. After the HDL source is created, the Identify instrumentor is used to create a debuggable design. This design is then run through the rest of the standard design flow. After the instrumented design has been implemented, the Identify debugger is then used to debug the design in the target system.

# **Tutorial Requirements**

This tutorial guides you through the process of debugging a small HDL design in a real hardware environment. The tutorial teaches you how to generate an instrumented design for debugging and then how to debug that instrumented design.

The tutorial explains how the Identify tools are used in concert with your synthesis and place-and-route flow. However, the tutorial does not provide details and procedures for synthesizing and using place-and-route tools with your instrumented hardware design. For the purposes of this tutorial, it is assumed that you have a working implementation flow. To find out more about these processes, consult your synthesis and place-and-route tool vendor documentation for more information.

### Hardware/Software Environments

This tutorial is intended to be performed with Actel hardware. The tutorial was developed using the following software:

- FPGA synthesis software: Synplify Pro E-2010.09A-1 or newer

- Actel Libero 9.0 or newer

- Identify software: Identify E-2010.09A or newer

# CHAPTER 2 The Tutorial Design

The Identify Actel Edition tool set can debug a variety of HDL designs. To better understand the debugging process, this guide provides a small HDL design example. The example design is a simple 4-bit counter. It only requires a clock and a reset signal connection to run in the hardware. Two versions of the counter are provided: one in VHDL and one in Verilog.

- For the Verilog tutorial, see Verilog Tutorial Design

- For the VHDL tutorial, see VHDL Tutorial Design

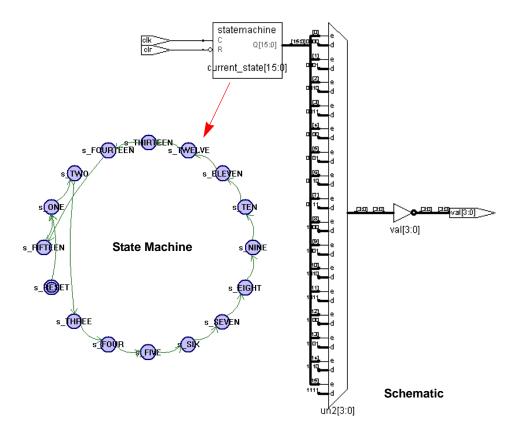

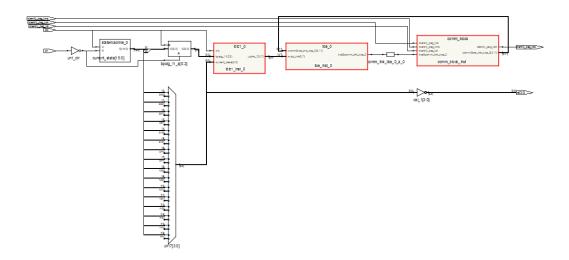

# **Design Schematic**

The following figure is a schematic representation of the simple state machine that is used for the tutorial design. The state machine is configured as a 4-bit counter; the state machine representation is shown to the left of the schematic.

Figure 2-1: Tutorial design schematic

# Verilog Tutorial Design

The tutorial design is implemented in Verilog as a single module with two always block statements. The first always block implements a state machine that controls the state of the system; the second always block computes the output values based on the current state. Parameter definitions make the module easier to read.

The tutorial design has two external inputs and one external output. The inputs are:

- CLK the system clock for the design

- CLR resets the state machine to a known state

The single output is val.

The board-mounted programmable device interconnects with the Identify software through a communications cable. For this tutorial:

- physically connect the CLK input to a clock generator on your target Actel FPGA system.

- connect the CLR input to a switch on your board that connects the signal to a zero value when pressed.

Direct the Actel place-and-route tool to make these connections.

When CLR is zero, the state machine enters state s\_RESET. When CLR is no longer zero, the state machine transitions to state s\_ONE, then s\_TWO, and so on, on each clock cycle.

Based on the current state value, the val output is set to the values listed in the second always block. These output values represent a binary encoding of the output state. However, this binary encoding is inverted so that it can be used to drive active-low LED displays on your board (if they exist). For example, if the state machine is in state s\_ONE, the val output is set to 1110, and when the state machine is state s\_ELEVEN, the output val is set to 0100.

The Verilog source code file for the tutorial design is displayed below:

```

module counter_self(clr, val, clk);

output [3:0] val;

input

clk;

input

clr;

reg [3:0] val;

reg [3:0] current_state;

parameter [3:0]

s_RESET

= 0,

= 1,

s ONE

s_TWO

= 2,

s THREE

= 3,

s FOUR

= 4,

= 5,

s_FIVE

s SIX

= б,

s SEVEN

= 7,

= 8,

s_EIGHT

s NINE

= 9,

s TEN

= 10,

s_ELEVEN

= 11,

= 12.

s TWELVE

s THIRTEEN = 13,

s_FOURTEEN = 14,

s_FIFTEEN = 15;

always @(posedge clk or negedge clr)

begin

if (clr == 1'b0)

current state = s RESET; /* 4'b0000 */

else begin

case (current_state)

s RESET:

current_state = s_ONE;

s ONE:

current state = s TWO;

s TWO:

current_state = s_THREE;

s_THREE:

current_state = s_FOUR;

s FOUR:

current state = s FIVE;

current_state = s_SIX;

s FIVE:

s_SIX:

current_state = s_SEVEN;

s SEVEN:

current state = s EIGHT;

s EIGHT:

current_state = s_NINE;

current_state = s_TEN;

s NINE:

s TEN:

current_state = s_ELEVEN;

current_state = s_TWELVE;

s_ELEVEN:

s TWELVE:

current state = s THIRTEEN;

```

```

s_THIRTEEN: current_state = s_FOURTEEN;

s_FOURTEEN: current_state = s_FIFTEEN;

s_FIFTEEN: current_state = s_ONE;

default:

current state = s RESET;

endcase /* case(current state) */

end /* else: !if(clr == 1'b0) */

end /* always @ (posedge clk or negedge clr) */

always @(current_state)

begin

case (current state)

val = 4'b1111;

s RESET:

s ONE:

val = 4'b1110;

val = 4'b1101;

s TWO:

s THREE:

val = 4'b1100;

s FOUR:

val = 4'b1011;

s FIVE:

val = 4'b1010;

s_SIX:

val = 4'b1001;

s SEVEN:

val = 4'b1000;

s EIGHT:

val = 4'b0111;

val = 4'b0110;

s NINE:

val = 4'b0101;

s TEN:

s ELEVEN:

val = 4'b0100;

s TWELVE:

val = 4'b0011;

s_THIRTEEN: val = 4'b0010;

s FOURTEEN: val = 4'b0001;

s_FIFTEEN: val = 4'b0000;

default:

val = 4'b0000;

endcase /* case(current state) */

always @ (current state) */

end /*

endmodule /* counter self */

/* EOF */

```

# VHDL Tutorial Design

The tutorial design is implemented in VHDL as a single entity with two processes. The first process implements a state machine that controls the state of the system, and the second process computes the output values based on the state. This design has a user-defined type named **state**, which is used to make the design more readable.

The design has two inputs and one output. The inputs are:

- CLK the system clock for the design

- CLR resets the state machine to a known state

The single output is val.

The board-mounted programmable device interconnects with the Identify software through a communications cable. For this tutorial:

- physically connect the CLK input to a clock generator on your target Actel FPGA system.

- connect the CLR input to a switch on your board that connects the signal to a zero value when pressed.

Direct the Actel place-and-route tool to make these connections.

When CLR is zero, the state machine enters state  $s\_RESET$ . When CLR is no longer zero, the state machine transitions to state  $s\_ONE$ , then  $s\_TWO$ , and so on, on each clock cycle.

Based on the current state value, the val output is set to the values listed in the second process. These output values represent a binary encoding of the output state. However, this binary encoding is inverted so that it can be used to drive active-low LED displays on your board (if they exist). For example, when the state machine is in state s\_ONE, the val output is set to 1110, and when the state machine is state s\_ELEVEN, the output val is set to 0100.

The VHDL source code file for tutorial design is displayed below:

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity counter_self is

port(

val : out unsigned ( 3 downto 0 );

clr : in std_logic;

clk : in std logic

);

end counter self;

architecture rtl of counter self is

type state is (

s_RESET,

s_ONE,

s TWO,

s_THREE,

s FOUR,

s FIVE,

s_SIX,

s SEVEN,

s EIGHT,

s_NINE,

s TEN,

s ELEVEN,

s_TWELVE,

s_THIRTEEN,

s FOURTEEN,

s FIFTEEN );

signal current_state: state;

begin

process(clk, clr)

begin

if clr = '0' then

current state <= s RESET;

elsif clk'event and clk = '1' then

case current state is

when s_RESET => current_state <= s_ONE;

when s_ONE

=> current_state <= s_TWO;

when s TWO

=> current state <= s THREE;

when s THREE

=> current state <= s FOUR;

when s_FOUR

=> current_state <= s_FIVE;

when s FIVE

=> current state <= s SIX;

when s SIX

=> current state <= s SEVEN;

when s_SEVEN => current_state <= s_EIGHT;

```

```

when s EIGHT

=> current_state <= s_NINE;

when s NINE

=> current_state <= s_TEN;

when s_TEN => current_state <= s_ELEVEN;

when s ELEVEN => current state <= s TWELVE;

when s TWELVE => current state <= s THIRTEEN;

when s_THIRTEEN => current_state <= s_FOURTEEN;

when s FOURTEEN => current state <= s FIFTEEN;

when s FIFTEEN => current state <= s ONE;

end case;

end if;

end process;

process( current_state )

begin

case current state is

when s_RESET

=> val <= "1111";

=> val <= "1110";

when s ONE

when s TWO

=> val <= "1101";

when s THREE => val <= "1100";

when s FOUR

=> val <= "1011";

when s FIVE

=> val <= "1010";

when s_SIX

=> val <= "1001";

when s_SEVEN => val <= "1000";

when s EIGHT

=> val <= "0111";

when s NINE

=> val <= "0110";

when s_TEN

=> val <= "0101";

when s ELEVEN => val <= "0100";

when s TWELVE => val <= "0011";

when s_THIRTEEN => val <= "0010";

when s_FOURTEEN => val <= "0001";

when s FIFTEEN => val <= "0000";

end case;

end process;

end rtl;

-- EOF

```

# CHAPTER 3 Instrumenting Your Design

The Identify instrumentor selects the design visibility (breakpoints and watchpoints) and special hardware configurations including complex event counters, and sampling and triggering modes for your design. The goal of the instrumentation process is to define an IICE and insert it into your HDL design. The instrumentation flow is:

- Launching the Identify Instrumentor

- Setting up the IICE

- Selecting the Instrumentation

- Writing the Instrumented Design

The HDL design and project files are included in a "tutorial" subdirectory under the Identify installation directory. This subdirectory includes the following files:

- counter\_self.v (Verilog design file)

- counter\_verilog\_actel.prj (Verilog project file)

- counter\_self.vhd (VHDL design file)

- counter\_vhdl\_actel.prj (VHDL project file)

Before you begin the tutorial, copy the files to a local directory and make sure that you have read and write permission for both the directory and files.

**Note:** While performing the tutorial, the active project (.prj) file will be updated; copying the files to a local directory preserves the original files installed in the tutorial directory.

# Launching the Identify Instrumentor

The Identify instrumentor is launched from the Synopsys Synplify Pro synthesis tool and is run prior to synthesis. Before starting the tutorial, copy the files from the tutorial directory to a local directory.

To launch the Identify instrumentor:

- 1. Start the Synopsys Synplify Pro synthesis tool.

- 2. In the project view, click the Open Project button to display the Open Project dialog box and click the Existing Project button.

- 3. Navigate to the tutorial directory where the Identify tool set is installed. This directory includes the HDL design files and a set of Actel-specific project files for both Verilog and VHDL implementations.

- 4. Select (open) the desired, Actel-specific project file.

5. Right click on the Identify implementation and select Launch Identify Instrumentor from the popup menu.

| C:/Designs5_identify/tutorial/counter_verilog_actel.prj |                                                |       |                                          |

|---------------------------------------------------------|------------------------------------------------|-------|------------------------------------------|

| Run     Synplify      Pro                               |                                                |       |                                          |

| -Rull                                                   | Ready                                          |       |                                          |

| 没 Open Project                                          | Actel 500K : A500K050                          |       | Implementation Directory                 |

| 没 Close Project                                         | i ⊡ Icounter_verilog_actel] -<br>i ∅ Ø Verilog | C:\D€ | C:\Designs5_identify\tutorial\rev_1_iden |

| Add File                                                | e @ rev_1                                      |       | Name 🛆 Size                              |

| hange File                                              | 🖗 rev_1_identify_1                             |       |                                          |

| Add Implementation                                      |                                                |       | lementation Options                      |

| Implementation Options                                  |                                                |       | inge Implementation Name                 |

| Add P&R Implementation                                  | Show Compile Points                            |       |                                          |

| View Log                                                |                                                |       | v Design Plan                            |

| Frequency(MHz):                                         |                                                |       | y Implementation                         |

|                                                         |                                                |       | nove Implementation DEL                  |

| Auto Constrain                                          |                                                |       | v Identify Implementation                |

| FSM Compil_                                             |                                                |       | nch Identify Instrumentor                |

| FSM Explor_                                             |                                                |       | nch Identify Debugger                    |

| Resource S_                                             |                                                |       | View                                     |

|                                                         |                                                |       | hnology View                             |

|                                                         |                                                |       | Place & Route Job                        |

|                                                         |                                                | Run   | ·                                        |

|                                                         |                                                | Proj  | ect View Options                         |

6. If prompted, enter the location of the Identify installation in the Configure Identify Launch dialog box, click the Locate Identify Installation radio button, and click OK to launch the Identify instrumentor..

| SConfigure Identify Launch                           |

|------------------------------------------------------|

| CLocate Identify                                     |

| O Use Current Identify Installation                  |

| C:\tools\Identify_ae_C200906ASP2                     |

| Locate Identify Installation (identify_instrumentor) |

| C:\tools\ident200906asp4_01                          |

| _ Identify License Option                            |

| O Use current synthesis license                      |

| Use separate Identify license                        |

| OK Cancel                                            |

7. If prompted for a license, select a license from the list of available licenses displayed and click Select.

| Select available license or E     To continue, please select a license type     Note: Server name not used in preferred I                                                                                                                                                                                 | for use in the current session.                                                                                                        |                                                                                                                                                              | X    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| License Type                                                                                                                                                                                                                                                                                              | Features                                                                                                                               | Server                                                                                                                                                       | Avai |

| <pre>&amp; identinstrumentor<br/>&amp; identinstrumentor cert<br/>&amp; identinstrumentor cert<br/>&amp; identinstrumentor prr<br/>&amp; identinstrumentor prdp<br/>&amp; identproinstrumentor<br/>&amp; identproinstrumentor<br/>&amp; identinstrumentor altera<br/>&amp; identinstrumentor rilinx</pre> | fpga<br>fpga<br>fpga,co=certify<br>fpga,co=certify<br>fpga,co=synplifypremier<br>fpga,co=synplifypremierdp<br>fpga<br>altera<br>xilinx | 1708@nsparky<br>1708@nsparky<br>1708@nsparky<br>1708@nsparky<br>1708@nsparky<br>1708@nsparky<br>1708@nsparky<br>1708@nsparky<br>1708@nsparky<br>1708@nsparky |      |

|                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |                                                                                                                                                              |      |

| & Indicates the current license preference                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                                                                                              |      |

| Save as default license type                                                                                                                                                                                                                                                                              |                                                                                                                                        |                                                                                                                                                              |      |

|                                                                                                                                                                                                                                                                                                           | Select Exit Refresh                                                                                                                    |                                                                                                                                                              |      |

**Note:** To avoid being prompted for a license each time you startup the Identify instrumentor, check the Save as default license type box before selecting your license.

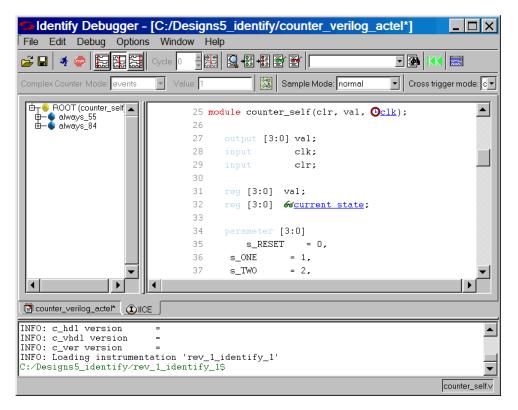

The figure on the following shows the initial Identify instrumentor window as launched from the Synplify Pro tool on the Verilog version of the tutorial. The window shows the design hierarchy on the left and the HDL file content with all the potential instrumentation marked and available for selection on the right.

| Identify Instrumentor - [C:/De                                          | signs5_identify/tutorial/counter_verilog 💶 🗙          |

|-------------------------------------------------------------------------|-------------------------------------------------------|

| File Edit Actions Options Window                                        | Help                                                  |

| D 🚔 🐔 🗇 🖳 🕄 🕄 🖉 🖉 🚺                                                     |                                                       |

| · · · · · · · · · · · · · · · · · · ·                                   |                                                       |

| Er ♦ ROOT (counter_self<br>Er ♦ always_55 25                            | module counter_self(&dclr, &dval, &dclk);             |

| <b>⊡</b> — <b>♦</b> always_84 26                                        |                                                       |

| 27                                                                      | output [3:0] val;                                     |

| 28                                                                      | input clk;                                            |

| 29                                                                      | input clr;                                            |

| 30                                                                      |                                                       |

| 31                                                                      | reg [3:0] val;                                        |

| 32                                                                      | reg [3:0] &d <u>current state</u> ;                   |

| 33                                                                      |                                                       |

| 34                                                                      | E 1                                                   |

| 35                                                                      | s_RESET = 0,                                          |

| ▼ 36                                                                    | s_ONE = 1,                                            |

|                                                                         |                                                       |

|                                                                         |                                                       |

| Counter_verilog_actel                                                   |                                                       |

| INFO: c_ver version = comp40<br>ild@BLDWIN2003A                         | Orc, Build 290R R on Apr 29 2010 18:05:09 by sbg_bu 🔺 |

| INFO: Current design is `counter_s                                      |                                                       |

| INFO: Loading instrumentation 'rev<br>C:/Designs5 identifv/tutorial/rev |                                                       |

| <pre>c:/besigns5_identify/tutorial/rev_</pre>                           |                                                       |

|                                                                         | counter_self.v                                        |

# Setting up the IICE

After you have launched the Identify instrumentor for the tutorial project, you need to configure your IICE. The IICE settings common to all IICE units for an instrumentation are set in the project window, and the individual IICE settings unique to each IICE in a multi-IICE configuration are set on the IICE Configuration dialog box. Although the tutorial uses a single IICE, you must set both the common IICE parameters in the project window and the individual IICE parameters in the IICE Configuration dialog box.

### **Setting the Common IICE Parameters**

The common IICE parameters are set in the project window. To redisplay the project window, click the project window tab along the bottom of the instrumentation window.

After a project is loaded, the common IICE parameters appear in the Implementation Options block on the right side of the project window above the compile options as shown in the following figure. These parameters:

- show the device family

- select the JTAG port for the communication between the hardware and the Identify debugger

| ち Identify Instr                           | umentor - [C:/Designs5                                                                           | _identify/tutorial/counter_verilog_actel]                                                        | _ 🗆 X |

|--------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------|

| File Edit Actions                          | Options Window Help                                                                              |                                                                                                  |       |

| 🗅 🗳 🐔 🛇                                    | +ख़ •ख़ ॡ∕ ॡ∕                                                                                    |                                                                                                  |       |

| New Project<br>Open Project<br>Add Files   | Counter_verilog_actel<br>Counter_self.v [work]<br>Counter_self.v [work]<br>Counter_self.v [work] | Instrumentation Options for 'rev_1_identify_1'     Device family: proASIC     JTAG port: builtin |       |

| New Instr.<br>Make Incremental<br>New IICE |                                                                                                  | Compile Options Top level unit Counter_self Compile                                              |       |

For the tutorial design:

- The device family (proASIC) is specified in the selected project file and reported in the first field.

- Select which connection to use for the communication between the Identify debugger and your hardware from the drop-down list in the JTAG port field. For the tutorial, you can select either the builtin or soft connection.

### **Setting the Individual IICE Parameters**

The individual IICE parameters are set by tabs on the IICE Configuration dialog box. Click on the Edit IICE settings icon in the toolbar or select Actions->Configure IICE from the menu to bring up the IICE Sampler tab shown in the following figure.

#### **IICE Sampler Tab**

The IICE Sampler tab defines the buffer type and sample depth of the data sampling hardware, controls the two optional sampling modes, and defines the sample clock and clock edge.

| IICE Sampler                  |                       |  |  |

|-------------------------------|-----------------------|--|--|

| Current IICE: IICE            |                       |  |  |

| Buffer type:                  | behavioral 💌          |  |  |

| Sample depth:                 | 128                   |  |  |

| Allow qualified sampling      |                       |  |  |

| Allow always-armed triggering |                       |  |  |

| -Sample Clock                 |                       |  |  |

| Sample clock:                 | /clk                  |  |  |

| Clock edge:                   | © Positive © Negative |  |  |

For the tutorial design:

- Leave Buffer type set to behavioral (only supported type)

- Select 128 for the sample buffer depth.

- Leave the Allow qualified sampling check box unchecked

- Leave the Allow always-armed sampling check box unchecked

- Enter /clk for the sample clock and select the positive polarity for the clock edge.

After you have set and/or verified the above IICE Sampler tab settings, click the IICE Controller tab.

#### **IICE Controller Tab**

The IICE Controller tab selects the type of triggering.

| IICE Controller                                |          |  |  |

|------------------------------------------------|----------|--|--|

| Current IICE: IICE                             |          |  |  |

| C Simple triggering                            |          |  |  |

| <ul> <li>Complex counter triggering</li> </ul> |          |  |  |

| Width:                                         | 16       |  |  |

| State Machine triggering                       |          |  |  |

| Trigger states:                                | 4        |  |  |

| Trigger conditions:                            | 4        |  |  |

| Counter width:                                 | 16       |  |  |

| -IICE Options                                  |          |  |  |

| Import external trigger signals: 0             | <b>_</b> |  |  |

| Export IICE trigger signal                     |          |  |  |

| Allow cross-triggering in IICE                 |          |  |  |

For the tutorial design:

- Make sure that the Complex counter triggering radio button is selected and that the Width is set to 16.

- Leave the Import external trigger signals value at 0.

- Leave the Export IICE trigger signal check box unchecked.

- Leave the Allow cross-triggering in IICE check box unchecked.

When all of the IICE configuration settings have been made or verified, click the OK button at the bottom of the dialog box.

# Selecting the Instrumentation

The steps for instrumenting a design file differ slightly from VHDL to Verilog.

- For VHDL designs, see VHDL Design Instrumentation, below

- For Verilog designs, see Verilog Design Instrumentation

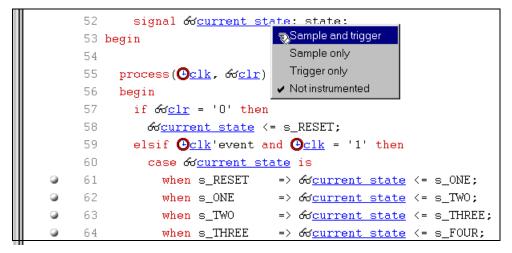

## **VHDL Design Instrumentation**

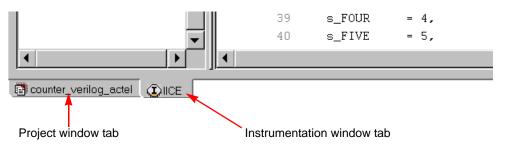

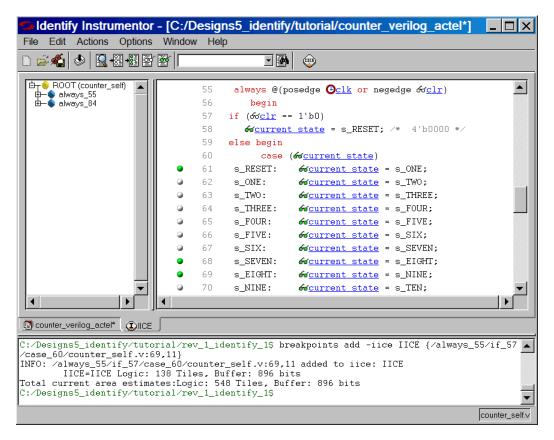

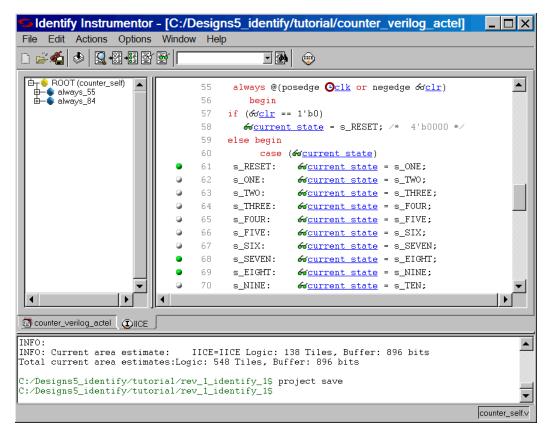

When your VHDL design compiles successfully, the instrumentation window displays the top-level entity VHDL code on the right and the hierarchy browser on the left (if the instrumentation window is not displayed, click on the "IICE" tab at the bottom of the project window). Use the hierarchy browser to navigate through your design. Clicking on a hierarchical node displays the corresponding VHDL source code in the source code display on the right.

| Identify Instrumentor                                                                       | - [C:/Designs5_identify/tutorial/counter_verilog 💶 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Edit Actions Options                                                                   | Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 🗋 🗳 🎑 📲 🗑                                                                                   | 2 De la companya de l |

| □<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 🖶 🖶 🖕 always_55                                                                             | 25 module counter_self(& <u>clr</u> , & <u>val</u> , <mark>⊙</mark> clk);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ⊡—♦ always_84                                                                               | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                             | 27 output [3:0] val;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                             | 28 input clk;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                             | 29 input clr;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                             | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                             | 31 reg [3:0] val;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                             | 32 reg [3:0] &c <u>current state</u> ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                             | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                             | 34 parameter [3:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                             | 35 s_RESET = 0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                             | 36 s_ONE = 1,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |