# DirectC Frequently Asked Questions

# 1. What is DirectC programming?

DirectC is an Embedded In-System Programming (ISP) solution for Actel Flash FPGA devices

# 2. What is required to enable DirectC Programming?

To perform In-System Programming (ISP) for the FPGA, the system must contain the following

- Control logic (a microprocessor or a soft-core microprocessor implemented in another FPGA with at least 256 bytes of RAM)

- JTAG interface to the target device

- Access to the data file containing the programming data

- Memory to store and run DirectC code

# 3. What does the DirectC package contain?

DirectC package contains ANSI C compliant C code to support in-system programming along with sample project and documentation

# 4. Do I have to make any changes to DirectC Code to work on my Setup?

Yes.

Some minor modifications to the source code need to be done to address three major components of DirectC application. These components are JTAG interface functions, memory interface functions for the data file, and the delay function (dp\_delay) defined in dpuser.c and dpcom.c. Once done, compile the source code to create a binary executable. This binary executable is downloaded into the system along with the programming data for execution

### 5. What functions do I need to change in DirectC code?

You must modify the *dpuser.h* and *dpuser.c* files when using the DirectC source code. Please refer to the "Required Source Code Modifications" section in the <u>DirectC</u> User's Guide for specific details

### 6. I am using a processor for DirectC. What type of I/O can I use to connect to JTAG signals?

DirectC supports discrete JTAG toggling. You can use a General Purpose I/O to connect to JTAG signals (TDI, TMS, TCK, TRSTN, TDO). JTAG port on Actel devices is LVTTL.

# 7. What Microprocessors/Microcontrollers are supported?

Any Microprocessor/Microcontroller that comes with ANSI C-Compliant compiler is supported.

# 8. Does DirectC code work on the 8051 Processor?

Yes

#### 9. Does DirectC run on a DSP processor?

Yes

# 10. What the memory requirements for DirectC?

The following applies to DirectC Version 2.0 and higher.

Microprocessor with a minimum of 256 Bytes RAM is required to run DirectC. There are two components of memory required

- Memory to store compiled DirectC code, the application code. While this varies based on the compiler switches selected, it does not vary much based on the device selected

- Memory to hold the programming data (\*.dat). This depends on the device being programmed, plain text or encrypted programming

Refer to the latest DirectC User's Guide for updated information

ProASICPLUS uses STAPL files that require large amount of memory, so if you are using ProASICPLUS your memory requirements also depend on the size of the device.

# 11. What devices/families are supported by DirectC?

DirectC Version 1.3 solution supports the ProASICPLUS FPGA family of devices.

DirectC V2.0 and higher support Fusion, IGLOO and ProASIC3 Mixed-Signal FPGA devices and their derivatives.

Neither version of DirectC supports ProASIC devices.

# 12. Does the DirectC for ProASICPLUS support all flash devices?

No. Refer to question 11 for the list of supported families.

# 13. How long does it take to program with DirectC?

The time taken to program depends on the speed of the microprocessor, speed of the I/O driving the JTAG signals, device size and data access speed.

### 14. What is DatGen?

Datgen is a standalone program that is used to generate the "\*.dat" file, which contains programming data extracted from the STAPL file. This was required before Libero IDE v8.5. With Libero IDE v8.5, the \*.dat file can be generated from Designer similar to a STAPL or PDB file

### 15. What is a \*.dat file?

The \*.dat file contains programming data for the device to be programmed with DirectC. This is to reduce the run time memory and data storage requirement.

# 16. How do I generate a \*.dat file?

This is not required for Libero IDE v8.5 or later. However if the design is created with an earlier version of Libero IDE and STAPL is available, the DATGEN executable which is available in DirectC package versions prior to Version 2.4 can be used to generate the \*.dat file.

To generate the DAT file:

- Copy datgen.exe to a local directory

- Copy the STAPL files to the same directory as datgen.exe

- o From the DOS prompt, type the following command:

- DatGen <STAPL file>

- The output is a binary data file (\*.dat) with same name as input file

# 17. Does ProASICPLUS require a \*.dat file?

ProASICPLUS uses a different version of DirectC compared with other flash devices. This version of DirectC (As of Q4-2008, the latest is v1.3), uses a STAPL file. It does not use a DAT file

# 18. Libero IDE version compatibility with DirectC?

While there is no direct link between these two, the way STAPL file and DAT files are generated evolved over time. The following table summarizes the evolution. This applies to flash families except ProASICPLUS.

| DirectC     | Libero IDE |                     |                                           |

|-------------|------------|---------------------|-------------------------------------------|

| Version     | Version    | DAT File Generation | Comment                                   |

|             | Libero IDE |                     |                                           |

|             | v8.4 and   |                     | Datgen must be used to generate the       |

| Version 2.2 | earlier    | DATGEN (STAPL file) | DAT file from the STAPL file              |

|             |            |                     | DAT file could be generated from          |

|             |            |                     | Designer or from Datgen utility. Both     |

|             | Libero IDE |                     | files are identical. DAT file from Libero |

| Version 2.3 | v8.5       | Designer            | IDE v8.4 can be used                      |

|             |            |                     | Datgen is no longer supported with        |

|             |            |                     | this version of the software. Designer    |

|             | Libero IDE |                     | software must be used to generate the     |

| Version 2.4 | v8.6       | Designer            | DAT file.                                 |

# 19. Is there a limit on the JTAG Clock (TCK) Frequency?

Not applicable. DirectC uses discrete JTAG Signal Toggling. So there is no frequency associated to TCK. However, Fusion, IGLOO and ProASIC3 devices have a limit of 20MHz.

#### 20. What are the power supply requirements?

The VCC, VPUMP and VJTAG power supplies are required. Please refer to the datasheet for the FPGA family for power specifications.

# 21. Are there any bypass capacitor requirements for DirectC?

Yes. For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible. The bypass capacitor must be placed within 2.5 cm of the device pins

# 22. How do I enable Chain Programming with DirectC?

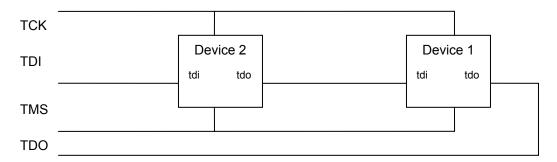

Please refer to the "Chain Programming Section" of the <u>DirectC</u> User's Guide. In a setup which has two Actel Flash Devices in a chain, AGL600 for example

### 1. Chain setup:

To program Device 1, we need to set up the pre and post IR/DR to:

```

// START Actel Chain Configuration

```

```

#define PREIR_DATA_SIZE

// Byte

#define PREDR_DATA_SIZE

// Byte

1

#define POSTIR_DATA_SIZE

1

// Byte - dummy

#define POSTDR_DATA_SIZE

// Byte - dummy

1

#define PREIR_LENGTH_VALUE 0

// bits

#define PREDR_LENGTH_VALUE 0

// bits

#define POSTIR_LENGTH_VALUE 8

// bits

#define POSTDR_LENGTH_VALUE 1

// bits

// END Actel Chain Configuration

```

To program Device 2, we need to set up the pre and post IR/DR to:

```

// START Actel Chain Configuration

```

```

#define PREIR_DATA_SIZE 1 // Byte - dummy

#define PREDR_DATA_SIZE 1 // Byte - dummy

#define POSTIR_DATA_SIZE 1 // Byte

#define POSTDR_DATA_SIZE 1 // Byte

```

```

#define PREIR_LENGTH_VALUE 8  // bits

#define PREDR_LENGTH_VALUE 1  // bits

#define POSTIR_LENGTH_VALUE 0  // bits

#define POSTDR_LENGTH_VALUE 0  // bits

// END Actel Chain Configuration

```

# 23. How do I read Device ID using DirectC?

There is a standalone action called "read\_idcode". Assign the Action\_code variable to DP\_READ\_IDCODE\_ACTION\_CODE prior to calling dp\_top.

# 24. Can I select I/O-State during DirectC Programming?

You can specify individual I/Os to drive high, low, or tri-state during generating the DAT file from Designer.

Maintaining the last known state of the I/Os is possible. See question 25 for more details on how to do it. However, this setting must be applied to all I/Os.

#### 25. How do I maintain the last known state of the I/Os?

To maintain the last known state of all I/Os, uncomment #define **BSR\_SAMPLE** in dpuser.h. By doing this, DirectC ignores the BSR setting in the DAT file.

#### 26. Can I use DirectC to program incremental UID to Flash ROM?

No. This feature is not supported

### 27. What action codes are supported in DirectC?

The following Action codes are supported as of DirectC v2.4

```

#define DP DEVICE INFO ACTION CODE 1

#define DP READ IDCODE ACTION CODE 2

#define DP ERASE ACTION CODE 3

#define DP_ERASE_ALL_ACTION_CODE 4

#define DP PROGRAM ACTION CODE 5

#define DP_VERIFY_ACTION_CODE 6

#define DP_ENC_DATA_AUTHENTICATION_ACTION_CODE 7

#define DP ERASE ARRAY ACTION CODE 8

#define DP PROGRAM ARRAY ACTION CODE 9

#define DP_VERIFY_ARRAY_ACTION_CODE 10

#define DP ERASE FROM ACTION CODE 11

#define DP_PROGRAM_FROM_ACTION CODE 12

#define DP_VERIFY_FROM_ACTION_CODE 13

#define DP ERASE SECURITY ACTION CODE 14

#define DP_PROGRAM_SECURITY_ACTION_CODE 15

#define DP_PROGRAM_NVM_ACTION_CODE 16

#define DP_VERIFY_NVM_ACTION_CODE 17

#define DP VERIFY DEVICE INFO CODE 18

```

#define DP\_READ\_USERCODE\_ACTION\_CODE 19

#define DP\_PROGRAM\_NVM\_ACTIVE\_ARRAY\_CODE 20

#define DP\_VERIFY\_NVM\_ACTIVE\_ARRAY\_CODE 21

Actel is the leader in low-power and mixed-signal FPGAs and offers the most comprehensive portfolio of system and power management solutions. Power Matters. Learn more at http://www.actel.com.

# **Actel Corporation**

2061 Stierlin Court Mountain View, CA 94043-4655 USA **Phone** 650.318.4200 **Fax** 650.318.4600

# Actel Europe Ltd.

River Court, Meadows Business Park Station Approach, Blackwater Camberley Surrey GU17 9AB United Kingdom Phone +44 (0) 1276 609 300

**Phone** +44 (0) 1276 609 300 **Fax** +44 (0) 1276 607 540

# Actel Japan

EXOS Ebisu Building 4F 1-24-14 Ebisu Shibuya-ku Tokyo 150, Japan Phone +81.03.3445.7671 Fax +81.03.3445.7668 http://jp.actel.com

# **Actel Hong Kong**

Room 2107, China Resources Building 26 Harbour Road Wanchai, Hong Kong Phone +852 2185 6460 Fax +852 2185 6488 www.actel.com.cn

© 2009 Actel Corporation. All rights reserved. Actel and the Actel logo are trademarks of Actel Corporation. All other brand or product names are the property of their respective owners.