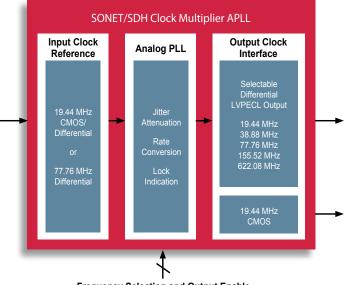

# **ZL30415 Simplified Block Diagram**

Frequency Selection and Output Enable

The ZL<sup>™</sup>30415 is an analog phase locked loop (APLL) that performs jitter attenuation and rate conversion for SONET (synchronous optical network) and SDH (synchronous digital hierarchy) equipment. The APLL is specifically designed to meet the feature, performance and price requirements of high-volume OC-3/STM-1 and OC-12/STM-4 line card applications.

The ZL30415 accepts a single input reference at 19.44 MHz or 77.76 MHz and generates a frequency selectable LVPECL output clock, as well as a 19.44 MHz CMOS output clock. Zarlink's ZL30415 seamlessly interfaces with framers, mappers and SERDES devices, eliminating external circuitry to save cost, board space and design resource requirements. With ultra-low jitter, the ZL30415 provides designers with confidence in meeting Telcordia and ITU-T specifications.

#### **Ultra-Low Jitter Output Clocks**

- → Ultra-low jitter generation of 3.5ps<sub>RMS</sub> (35ps<sub>pk-pk</sub>) maximum surpasses worldwide system requirements

- Surpasses Telcordia GR-253-CORE jitter requirements for OC-3 and OC-12 rates

- Surpasses ITU-T G.813 jitter requirements for STM-1 and STM-4 rates

- Easily accommodates the most stringent jitter requirements imposed by SONET/SDH interfacing devices

### **Design Flexibility**

- → Accepts a single-ended CMOS reference at 19.44 MHz or a differential LVDS, LVPECL, or CML reference at 19.44 MHz or 77.76 MHz

- Differential LVPECL output clock is frequency selectable to 19.44 MHz, 38.88 MHz, 77.76 MHz, 155.52 MHz, or 622.08 MHz

- → Single-ended CMOS output clock at 19.44 MHz

## **Simplifies Design**

- Seamlessly interfaces to framers, mappers and SERDES

- LVPECL output clock eliminates need for external translation circuitry, saving board space, cost and design effort

- Input/output frequencies are selectable through the control pins

- → Does not require external crystal oscillator

## Packaging and Availibility

- → Package: 64-ball CABGA (8 mm x 8 mm)

- → Available now in production quantities

#### **Applications**

- SONET/SDH line cards

- SONET/SDH timing cards

## **Complementary Products**

- → MT9046 T1/E1 system synchronizer DPLL

- → ZL30407 SONET/SDH network element DPLL

- → ZL30410 multi-service line card PLL

### **Customer Support**

The ZL30415 is supported by a customer evaluation board (ZLE30415) and Zarlink's network of field application and design engineers.

# Ultra-Low Jitter, Frequency Selectable APLL Reduces Cost, Simplifies Design

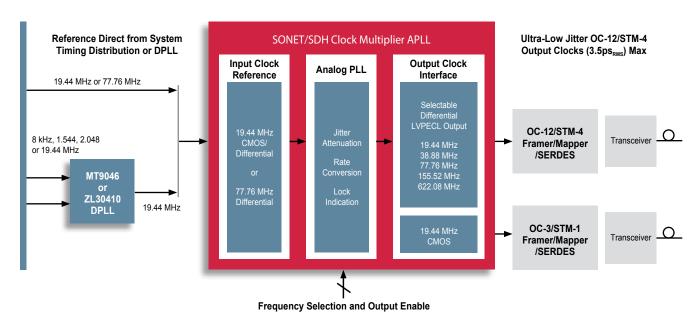

The diagram below demonstrates how the outputs of the ZL30415 can be used to drive framers, mappers and SERDES devices in OC-3/STM-1 and OC-12/STM-4 line card applications.

In this application the ZL30415 accepts a single input reference (19.44 MHz or 77.76 MHz) directly from the timing card represented by the system timing distribution bus. When reference switching or advanced timing functionality are required on the line card, a digital PLL such as Zarlink's MT9046 or ZL30410 is used to provide the reference. The ZL30415 performs jitter attenuation and provides one LVPECL output clock that is frequency selectable to 19.44 MHz, 38.88 MHz, 77.76 MHz, 155.52 MHz or 622.08 MHz, and one CMOS output clock at 19.44 MHz.

The ability to support multiple output clock frequencies allows the device to be used in any OC-3/STM-1 or OC-12/STM-4 system. Frequencies are selected using the control pins, allowing designers to use the ZL30415 in multiple line cards without changing the layout.

Since the ZL30415 is able to support LVPECL output clocks up to 622.08 MHz, no external circuitry is required to interface to framers, mappers, SERDES, or other surrounding devices. Eliminating external translation circuitry reduces bill of materials cost, board space and design effort.

With ultra-low jitter of  $3.5ps_{\tiny RMS}$  ( $35ps_{\tiny pk-pk}$ ) maximum, the ZL30415 offers significant margin compared to the maximum jitter generation of  $16ps_{\tiny RMS}$  ( $161ps_{\tiny pk-pk}$ ) specified by the OC-12/STM-4 standard requirements. This provides designers with flexibility in choosing SONET/SDH devices with the right set of features and cost for any given application.

### **ZL30415 SONET/SDH Line Card Application**

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively Zarlink) is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee expressed or implied is made regarding the capability, performance or suitability of any product or service.

ZARLINK, ZL, and the Zarlink logo are trademarks of Zarlink Semiconductor Inc. Copyright 2003, Zarlink Semiconductor Inc. All Rights Reserved.

Publication Number PP5862