# PolarFire<sup>®</sup> FPGA and PolarFire SoC FPGA Transceiver

# Introduction

Microchip's PolarFire FPGAs are the fifth-generation family of non-volatile FPGA devices, built on state-of-the-art 28 nm non-volatile process technology. PolarFire FPGAs deliver the lowest power at mid-range densities. PolarFire FPGAs lower the cost of mid-range FPGAs by integrating the industry's lowest power FPGA fabric, lowest power 12.7 Gbps transceiver lane, built-in low power dual PCI Express Gen2 (EP/RP), and, on select data security (S) devices, an integrated low-power crypto co-processor.

Microchip's PolarFire SoC FPGAs are the fifth-generation family of non-volatile SoC FPGA devices, built on state-ofthe-art 28 nm non-volatile process technology. The PolarFire SoC family offers industry's first RISC-V based SoC FPGAs capable of running Linux. It combines a powerful 64-bit 5x core RISC-V Microprocessor Sub-System (MSS), based on SiFive's U54-MC family, with the PolarFire FPGA fabric in a single device.

The PolarFire FPGA and PolarFire SoC FPGA family includes multiple embedded low-power, performance-optimized transceivers. Each transceiver has both the physical medium attachment (PMA), protocol physical coding sub-layer (PCS) logic, and interfaces to the FPGA fabric. The transceiver has a multi-lane architecture with each lane natively supporting serial data transmission rates from 500 Mbps (250 Mbps with interpolation) to 12.7 Gbps.

The following table summarizes the transceiver components available in PolarFire FPGA and PolarFire SoC FPGA families.

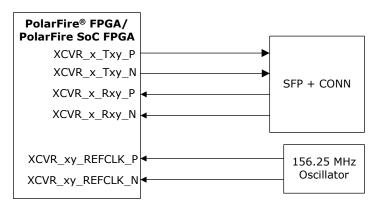

#### **Table 1. Transceiver Components**

| Components | PolarFire FPGA (MPF) | PolarFire SoC FPGA (MPFS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMA/PCS    | ✓                    | <ul> <li>Image: A start of the start of</li></ul> |

| TXPLL      | ✓                    | <ul> <li>Image: A start of the start of</li></ul> |

| REF_CLK    | <i>✓</i>             | <ul> <li>Image: A start of the start of</li></ul> |

The transceiver includes all required analog functions for high-speed data transmission between devices over printed circuit boards (PCB) and high-quality cables. The transceiver is suitable for a variety of device-to-device communication protocols, as listed in the following table.

| Table 2. Supported Serial | Protocols |

|---------------------------|-----------|

|---------------------------|-----------|

| Protocol                | Standard/Version        | Protocol          | Standard/Version                                                                            |

|-------------------------|-------------------------|-------------------|---------------------------------------------------------------------------------------------|

| PCle                    | Gen1                    | CPRI <sup>1</sup> | CPRI-1, 2, 3, 4, 5, 6, 7, 7A, 8, 9                                                          |

| PCle                    | Gen2                    | SATA <sup>2</sup> | 1.0a                                                                                        |

| XAUI                    | IEEE <sup>®</sup> 802.3 | SATA <sup>2</sup> | 2.0                                                                                         |

| Interlaken <sup>3</sup> | 10.3125                 | SATA <sup>2</sup> | 3.0                                                                                         |

| Interlaken <sup>3</sup> | 6.375                   | SDI-SD            | SMPTE 259M                                                                                  |

| 10GBASE-R               | IEEE 802.3              | SDI-HD            | SMPTE 292M                                                                                  |

| 10GBASE-KR <sup>4</sup> | IEEE 802.3              | SDI-3G            | SMPTE 424M                                                                                  |

| Fibre Channel           | 1GFC                    | SGMII             | -                                                                                           |

| Fibre Channel           | 2GFC                    | 1000BASE-X        | IEEE 802.3                                                                                  |

| Fibre Channel           | 4GFC                    | LiteFast          | Proprietary Lightweight Serial Protocol<br>Interface (up to 12.7 Gbps, 8b10b<br>mode only.) |

| Fibre Channel           | 8GFC                    | RXAUI             | N/A                                                                                         |

| JESD204B                | LV-OIF-SxI5             | QSGMII            | -                                                                                           |

| JESD204B                | LV-OIF-6G-SR            | SLVS-EC           | —                                                                                           |

| JESD204B                | LV-OIF-11G-SR           | DisplayPort       | -                                                                                           |

| USXGMII                 | —                       | CoaXPress         | -                                                                                           |

(1) Common Public Radio Interface (CPRI) Specification V7.0 (2015-10-09).

$^{(2)}$  SATA is supported using PMA only mode.

(3) Interlaken Protocol Specification, v1.2.

(4) PMA supports 10GBASE-KR operation.

**Note:** Transmit/receive fabric interfaces are specified in the associated PCS pin lists, that is, 8b10b, 64b6xb, PIPE, and PMA Only. For more information on PCIESS, see PolarFire FPGA and PolarFire SoC FPGA PCI Express User Guide.

# Features

Transceiver enables users to quickly build high-speed links that support many standard protocols with the features listed:

- Supports data rates from 500 Mbps (250 Mbps with interpolation) up to 12.7 Gbps.

- Serialization/deserialization width at FPGA fabric interface—8, 10, 16, 20, 32, 40, 64, and 80 bits.

- Differential output termination from 85  $\Omega,$  100  $\Omega,$  and 150  $\Omega.$

- Low-power modes.

- Receivers are compatible with CML and LVDS I/O Standards.

- Transmitters are compatible with CML, LVDS, and LVPECL I/O Standards.

- Configurable transmit pre- and post-tap de-emphasis controls.

- Configurable amplitude control from 250 mV to 1 V differential.

- Receivers detect circuitry for use with PCIe.

- Out-of-band (OOB), electrical idle signaling capability for

- Serial-attached SCSI: small computer system interface (SAS).

- Serial advanced technology attachment (SATA).

- Peripheral component interconnect express (PCIe).

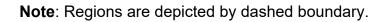

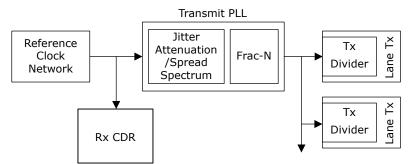

- Spread-spectrum generation built into the transmit phase-locked loop (PLL).

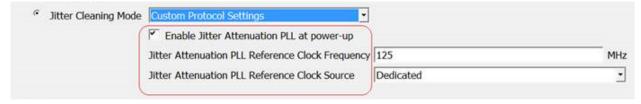

- 1 Gb and 10 Gb SyncE compatible Jitter attenuation available in the transmit PLL for loop timing applications.

- Continuous time linear equalizer (CTLE) with optional auto-calibration to improve received signal integrity.

- 5-tap decision feedback equalizer (DFE) with auto-calibration to compensate for high-frequency losses.

- · Receive data eye monitor for link analysis.

- Configurable peak detector/signal detect.

- Polarity inversion (receiver).

- Diagnostic loopback modes.

- Embedded pseudo-random binary sequence (PRBS) test pattern generators/checkers—available PRBS polynomials (2<sup>n</sup>), where n = 7, 9, 15, 23, and 31.

- AC JTAG (IEEE 1149.6) and DC JTAG (IEEE 1149.1) transmitter and receiver.

- IBIS-AMI support of transceiver inputs and outputs.

- Supports AC and DC coupling modes with configurable transmit common-mode voltage.

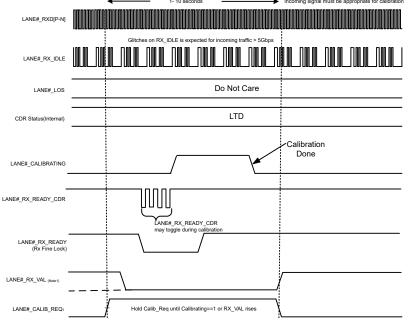

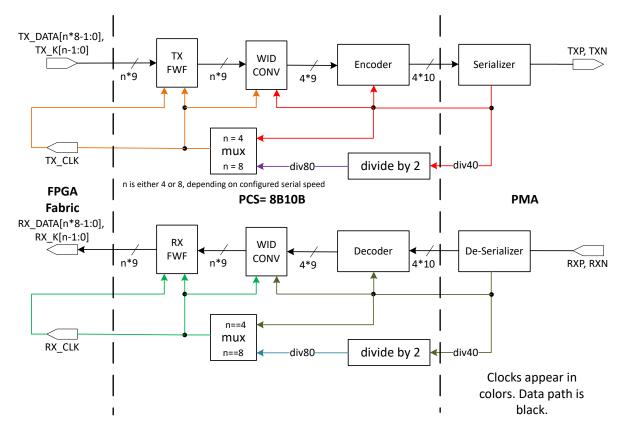

- Embedded PCS:

- 8b10b—encoding/decoding is provided.

- 64b6xb—64b/66b or 64/67b encoding/decoding with gearbox logic is provided.

- PIPE—PHY interface for the PCI Express Rev 3.0 supporting PCIe Gen1/2.

- PMA only-direct access to the PMA without any encoding.

- PCIe—fully embedded PCIe Gen1/Gen2 root-port or endpoint subsystem (PCIESS) with AXI4 user interface with built-in DMA. The embedded PCIe controller subsystem is available only within Quad0. See PolarFire FPGA and PolarFire SoC FPGA PCI Express User Guide for more information on the embedded PCIE capabilities and its usage.

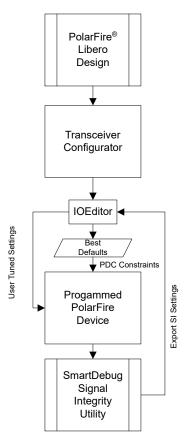

The Microchip Libero<sup>®</sup> SoC software supports configuration for the various modes of transceiver operations. Table 2 shows which of these configurations support industry-standard protocols and user-defined custom protocols. The Libero SoC software design tools allow designers to set the configuration needed for a specific operational mode for each transceiver lane. The software correctly provisions and generates all the required programming and configuration data used to initialize and bring the transceiver into operation. The transceiver configuration registers are set automatically by the Libero SoC transceiver configurator. These registers must be left at their default values set by the configurator, except for use cases that explicitly request different values.

## References

- For information about PCIESS, see PolarFire FPGA and PolarFire SoC FPGA PCI Express User Guide.

- For information about regional clock resources and connectivity of the transceivers to the global clock network, see PolarFire FPGA and PolarFire SoC FPGA Clocking Resources User Guide.

- For information about available I/O standards, see PolarFire FPGA and PolarFire SoC FPGA User I/O User Guide.

- For information about Optimized DFE feature, see UG0773: PolarFire FPGA SmartDebug User Guide.

- For information about implementing transceiver designs on printed circuit boards, see respective UG0726: PolarFire FPGA Board Design User Guide or PolarFire SoC FPGA Board Design Guidelines User Guide.

# **Table of Contents**

| Intro | oductio | n                                                        | 1 |

|-------|---------|----------------------------------------------------------|---|

|       | 1.      | Features                                                 | 4 |

|       | 2.      | References                                               | 5 |

| 1.    | Funct   | onal Description                                         | 8 |

|       | 1.1.    | PMA                                                      |   |

|       | 1.2.    | Enhanced Receiver Management                             |   |

|       | 1.3.    | Transceiver PCS Interface Modes                          |   |

|       | 1.4.    | PCS/FPGA Fabric Interface                                |   |

|       | 1.5.    | Transceiver Clocking                                     |   |

|       | 1.6.    | PMA and PCS Resets                                       |   |

|       | 1.7.    | PCS Rate Switch Between 8b10b and 64b66b Mode for CPRI75 |   |

| 2.    | Implei  | nentation8                                               | 1 |

| ۷.    | 2.1.    | Libero Configurators                                     |   |

|       | 2.1.    | Transceiver Modes                                        |   |

|       | 2.2.    | Libero Generated Files                                   |   |

|       | 2.3.    | Design Constraints                                       |   |

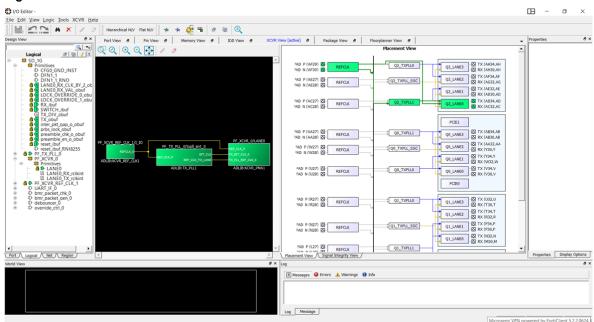

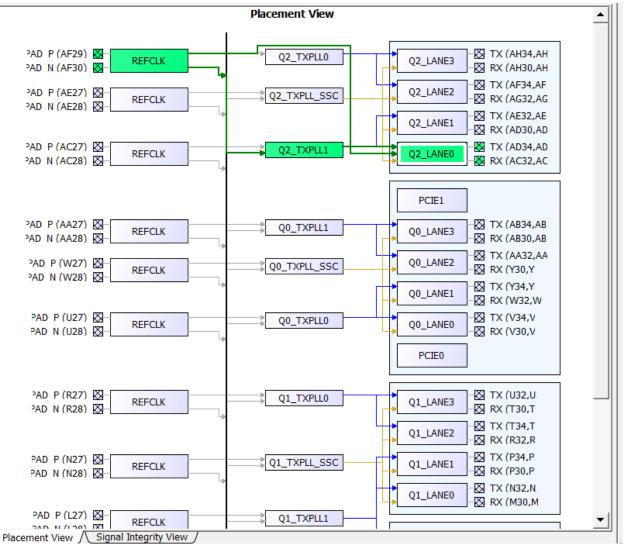

|       | 2.4.    | Adding Physical Constraints Using Libero                 |   |

|       | 2.5.    | Transceiver Initialization                               |   |

|       |         |                                                          |   |

| 3.    | Signa   | I Integrity Conditioning110                              | C |

|       | 3.1.    | Transmitter                                              | 1 |

|       | 3.2.    | Receiver                                                 |   |

|       | 3.3.    | IO Editor for Signal Integrity                           |   |

|       | 3.4.    | SmartDebug Signal Integrity110                           | 6 |

| 4.    | Simul   | ation                                                    | 2 |

|       | 4.1.    | RTL Simulation Mode122                                   | 2 |

| 5.    | Debu    | g and Testing                                            | 4 |

|       | 5.1.    | PRBS Generator/Checker                                   | 4 |

|       | 5.2.    | Loopback                                                 | 4 |

|       | 5.3.    | Dynamic Reconfiguration Interface                        | 6 |

| 6.    | Board   | Design Recommendations                                   | 7 |

| 0.    | 6.1.    | Transceiver Top-Level Pin Out                            |   |

|       | 6.2.    | Design for Protocols                                     |   |

|       | 6.3.    | 10G Interface                                            |   |

|       | 6.4.    | Transceivers Insertion Loss                              |   |

| _     |         |                                                          |   |

| 7.    | Revis   | ion History                                              | 2 |

| The   | Micro   | chip Website                                             | 3 |

| Pro   | duct C  | nange Notification Service13                             | 3 |

| Cus   | stomer  | Support13                                                | 3 |

| Microchip Devices Code Protection Feature | . 133 |

|-------------------------------------------|-------|

| Legal Notice                              | . 134 |

| Trademarks                                | . 134 |

| Quality Management System                 | . 135 |

| Worldwide Sales and Service               | 136   |

# 1. Functional Description

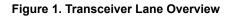

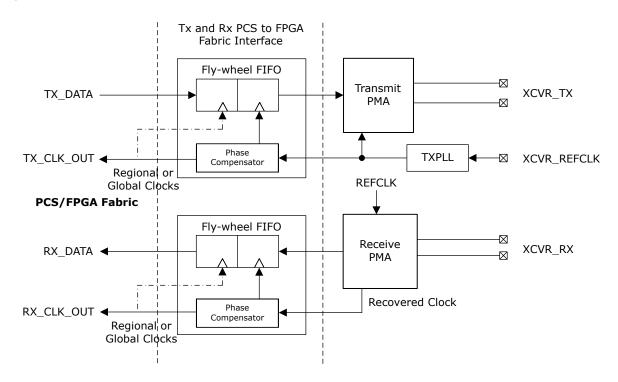

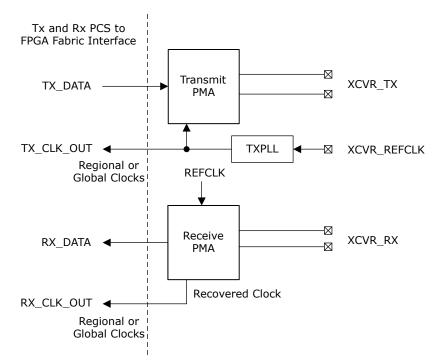

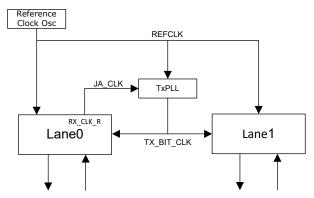

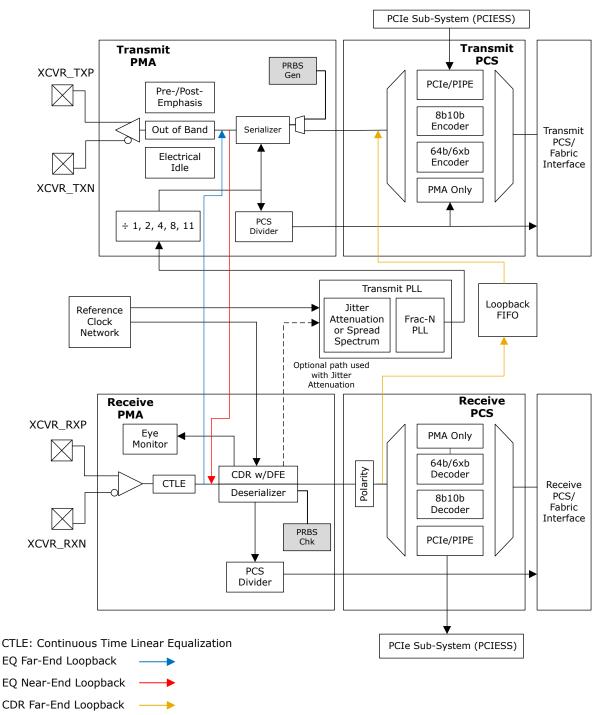

The transceiver (Figure 1) is divided into four distinct transmit (Tx) and receive (Rx) blocks:

- PMA

- · PCS interface block, including a dedicated PCIe PCS

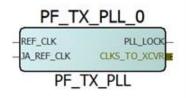

- Transmit PLL (Tx PLL)

- Reference clock inputs

The high-speed PMA blocks connect to the FPGA fabric through the PCS block. The PMA generates the required clocks and converts the transmit data from parallel to serial, and receive data from serial to parallel. Each PMA block includes a connection to a PCS block and associated interface to the FPGA fabric making up a transceiver lane. The PCS interface block provides several industry-standard interfaces for use in protocol-specific designs.

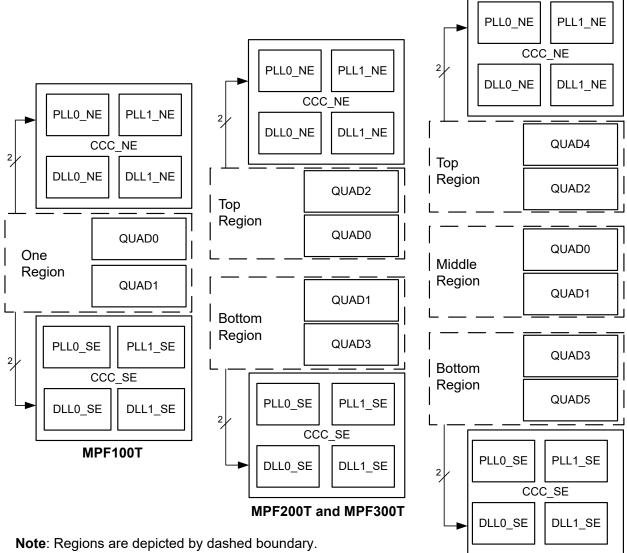

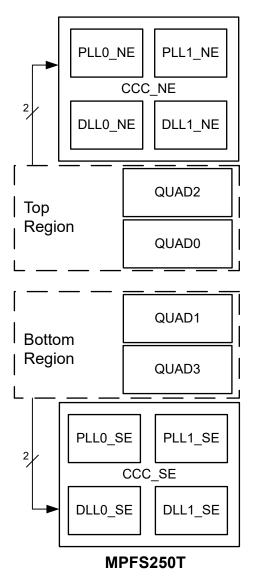

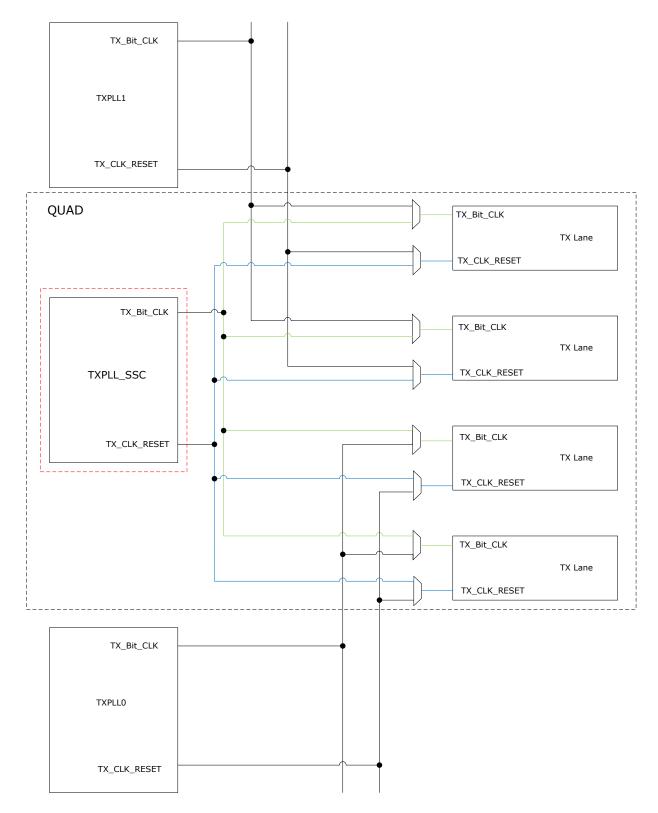

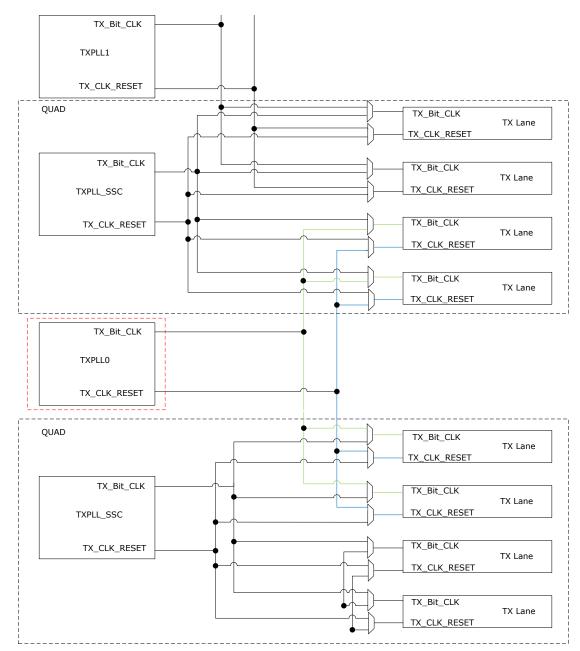

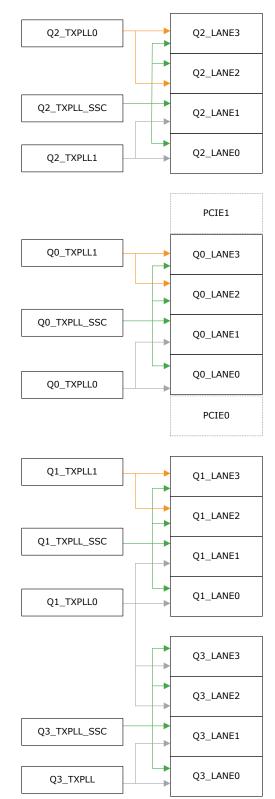

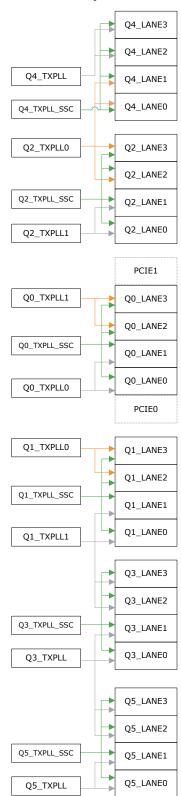

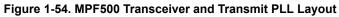

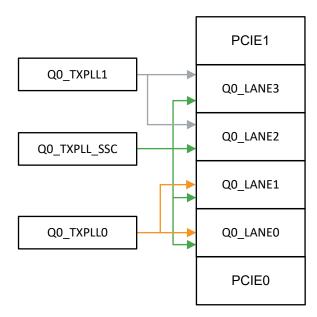

A group of four transceiver lanes is called a quad. Each quad has a local transmit PLL used exclusively within the four transceiver lanes. Additional transmit PLLs are shared between quads.

In addition to the 8b10b, 64b6xb, PIPE, and PMA only blocks, two PCIe PCS logic blocks are included in each device. These blocks include hard embedded logic that provides full-featured PCIe endpoint/root port sub-system. These PCIe sub-systems (PCIESS) have hard connections to multiple transceiver lanes, providing flexibility for ×1, ×2, and ×4 width links. See PolarFire FPGA and PolarFire SoC FPGA PCI Express User Guide for additional information pertaining to PCIe.

### 1.1 PMA

The transceiver lanes include PMA receiver and transmitter sub-modules. These PMA sub-modules include the input and output buffers, signal conditioning circuits, CDRs, and transceiver. The PMA architecture allows the receive and transmit portions of each lane to operate independently. The PMA features are initialized at power-up and can also be altered during device operation using an APB dynamic reconfiguration interface (DRI).

The SmartDebug tool set provides access to dynamic changes of PMA features, including transmit and receive tuning, and receive eye monitoring capabilities.

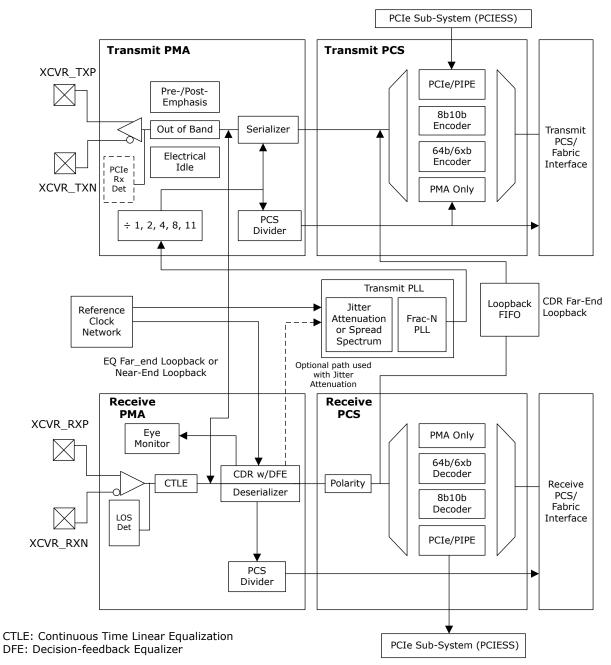

#### 1.1.1 Receiver

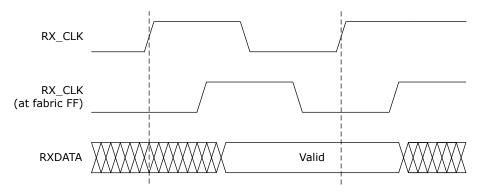

The receiver deserializes high-speed serial data received through the input buffer by creating a parallel data stream for the FPGA fabric and recovering the clock information from the received data. The receiver portion of the PMA includes the receiver buffer, the clock and data recovery (CDR) unit, and the deserializer. The deserializer within the receive PMA passes deserialized data to the PCS block across a data bus up to 40-bits wide of the PMA-PCS interface, which provides the data path to the gearing logic before the data is passed to the FPGA fabric.

#### Figure 1-1. Transceiver Receiver

#### 1.1.1.1 Receive Input Buffer

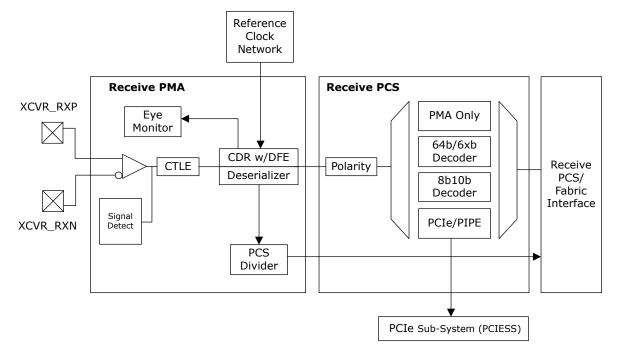

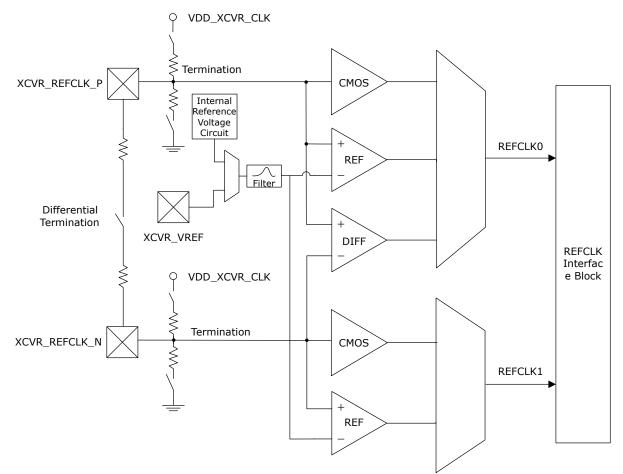

The receiver provides an external input interface through differential pins, XCVR\_RXP/N, as shown in the following figure. The receiver includes a current mode logic (CML) input buffer with programmable DC restoration that is used in either AC- or DC-coupled applications.

The receive buffer provides an on-die differential termination scheme which can be programmed to 85  $\Omega$ , 100  $\Omega$ , or 150  $\Omega$ . The receiver buffer also includes a high-impedance (high-Z) mode for hot-swap capability when the device is powered OFF. Additionally, the receiver input supports logical swapping of the polarity of the P and N pins for added flexibility.

#### Figure 1-2. Receiver Input Buffer

**Note:** VICM is connected to VDDA when AC-coupled link is configured. DC-coupled configurations effectively disconnects VICM source. See 3.2.4 AC/DC Coupled Connection.

Each receiver lane includes optional signal threshold detection circuitry that users can select according to protocol or application requirements. This feature identifies whether the signal level present at the receiver input buffer is above the signal detect threshold voltage needed to trip or activate the receiver input, which prevents false activity on the receiver path. The signal detection has both a high and low signal detector. The Libero SoC software configurator provides the correct setting based on protocol or customization.

Note: The user can also use a JTAG-based interface from SmartDebug to experiment with receiver settings.

#### 1.1.1.2 Loss of Signal Detect (LOS)

Loss of signal (LOS) detection is included within the receiver path. The LOS circuitry detects the initial incoming signal determining a valid input (electrical RX\_IDLE=0) for clock-data recovery operations. The LOS peak detection captures the most positive and negative points of the input signal and compares the amplitude to a limit set by the user. See 3.2.5 Loss-of-Signal Detector. The performance of the physical peak detector is limited by the bandwidth of the input signal. The LOS detection works for rates 5 Gbps and less and may not be suitable for all protocols or data patterns. For conditions outside the range of the LOS operation, see 1.2 Enhanced Receiver Management.

#### 1.1.1.3 Continuous-Time Linear Equalizers (CTLE)

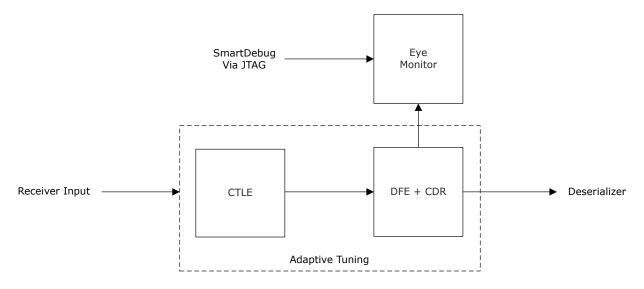

The CTLEs equalize a lane's low-pass response to compensate for high-frequency losses in that lane, thereby improving the quality of the received signal. This circuit can be adjusted to compensate for any physical lane mismatches.

There are two transparent stages of CTLE and a separate pair of stages for the decision feedback equalizer (DFE)/eye monitor receive path. The input signal path (Figure 1-3) is conditioned by tuning the incoming signal allowing the user to observe the effects of the tuning. The DC gain and peak bandwidth of each stage is selected with Libero. CTLE settings can be selected based on DC gain, peaking frequency, and AC gain or with an auto adaptive setting through the Libero transceiver interface configurator. The automatic or adaptive mode uses internally generated settings to the physical channels for lane optimization.

#### Figure 1-3. Input Signal Path

#### 1.1.1.4 Decision Feedback Equalizer

In the receiver front end, an optionally enabled 5-tap decision feedback equalizer (DFE) is available to equalize the lane response in conjunction with the CTLE. The DFE allows better compensation of transmission channel losses than a linear equalizer of CTLE, by providing a closer adjustment of filter parameters. The tap values of the DFE are the coefficients of this filter that are set by the adaptive algorithm.

The DFE mitigates lane noise or inter-symbol interference (ISI) caused by reflections or cross-talk without amplifying the high-frequency noise within the data. The DFE-based operation uses current bit information to cancel ISI for the following bit through a feedback mechanism, allowing the following bits to be correctly sampled. Using taps to delay and multiply the symbols, the DFE effectively cancels out interference on the analog signal. Similar to the CTLE operation, the DFE has an automatic mode. When the DFE is used in automatic mode, the CTLE can be in automatic mode as-well.

The operation is nonlinear, allowing it to overcome the notch response that the CTLE cannot perform. The DFE also includes an automatic calibration that finds the best possible tuning to match the transceiver lane to the system channel.

#### 1.1.1.5 Eye Monitor

The eye monitor is on-device circuitry to visualize the post-equalization signal quality in the receive path while the data path is still active in the system. The non-destructive eye monitor runs a separate sampler in parallel with the CDR and DFE data sampler. This permits the system to remain operational while the eye monitor is functioning.

The eye monitor systematically adjusts the offsets across the complete eye, calculates the bit-error rate (BER) for each offset setting, then correlates the BER and offset to statistically rebuild the eye diagram. Eye diagram statistics can be read and reconstructed using the Libero SmartDebug tools, which permits access through a JTAG interface for transceiver debugging and test access.

Swing and de-emphasis can be configured in hundreds of combinations. However, it is very cumbersome for the user to tune these when optimizing the transceiver input. The eye monitor feature eases the manual steps to find the adjustments. It is used as part of the CTLE/DFE auto-calibration. The eye monitor feedback mechanism optimizes the correct DFE settings by using a duplicate DFE circuit to monitor and adjust the incoming data stream.

#### 1.1.1.6 Receive Clock and Data Recovery

The receive CDR circuit follows the CTLE and works in tandem with the DFE. The receive CDR PLL can lock onto the input reference clock or the incoming data stream to be able to re-time the incoming data. The deserializer is closely coupled with the CDR, and translates the data from a serial to a parallel stream.

#### 1.1.1.6.1 CDR Options

The PMA of each lane includes a PLL used for the receiver CDR. The CDR PLL supports lock-to-reference and lock-to-data modes, which allows customization of the CDR options best suited for the application. It also includes a Burst-mode receiver option, which can switch between both options that are selectable through the Libero transceiver configurator.

**Lock-to-Reference**: The phase frequency detector (PFD) in the CDR tracks the receiver input reference clock. The PFD controls the charge pump that tunes the VCO in the CDR. The LOCK status signal is asserted high to indicate that the CDR has locked to the phase and frequency of the receiver input reference clock regardless of the data phase detector (PD). Lock-to-reference is used to lock the transceiver CDR to the reference clock rather than the incoming data when the receiver is used as a simple over-sampler, or when the CDR must be locked to a local oscillator.

**Lock-to-Data**: The CDR must use the lock-to-data mode to recover the clock and data from the incoming serial data. In this mode, the data phase detector of the CDR tracks the incoming serial data at the receiver input. Depending on the phase difference between the incoming data and the CDR output clock, the PD controls the CDR charge pump that adjusts the VCO. The LOCK status signal is asserted when the CDR finds valid data. The actual lock time depends on the incoming data stream's transition density.

**Burst Mode Receiver**: The transceiver CDR circuit has enhanced capabilities to support burst mode receivers (BMR). BMR is used in NGPON2 and 10GEPON passive optical network applications for fast and bounded lock times. The BMR option is used to implement the fast clock-data recovery when the conventional bang-bang phase detector PLLs cannot meet the stringent lock times required by the passive optical network (PON) applications.

Note: DFE auto-calibration is not available when the transceiver is configured for burst mode (BMR).

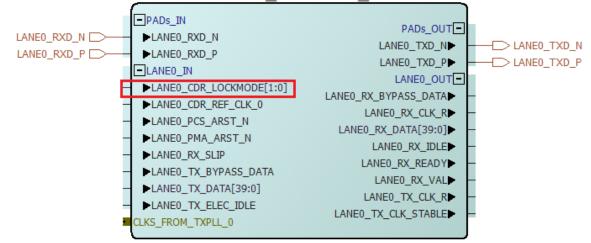

When BMR mode is selected, LANE\_X\_CDR\_LOCKMODE[1:0] are exposed for CDR mode control. The following table lists the value and the description of the CDR lock mode control bits.

| LANE_X_CDR_LOCKMODE[1:0]<br>Values | Mode                     |

|------------------------------------|--------------------------|

| 2'b00                              | Not used                 |

| 2'b01                              | High gain <sup>1</sup>   |

| 2'b10                              | Lock to reference        |

| 2'b11                              | Normal Mode <sup>2</sup> |

#### Table 1-1. CDR Lock Mode Values

<sup>(1)</sup> High Gain mode is used during Preamble/delimiter detection phase to fast phase lock to the incoming RX data. This mode may generate additional clock jitter on the recovered clock. Once the preamble/de-limiter is detected, it is recommended to switch to normal CDR mode to minimize jitter.

<sup>(2)</sup> This is used when payload is received form burst mode receiver.

For detailed CDR specifications, see respective PolarFire FPGA Datasheet and PolarFire SoC Advance Datasheet. For application example and implementation details, see DG0841: PolarFire Burst Mode Receiver Demo Guide.

Lock to Data with 2X Gain: This transceiver option is used to implement the fast clock-data recovery when incoming data streams such as stressful SDI patterns require high gain to quickly phase lock to the incoming pattern. This mode produces faster lock times than that of normal lock-to-data mode.

The following figure shows the CDR lock mode options.

#### Figure 1-4. CDR Lock Mode Options

| CDR lock mode                                             | Lock to data 💌                                                                        |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------|

| CDR reference dock source<br>CDR reference dock frequency | Lock to data<br>Lock to reference<br>Burst Mode Receiver<br>Lock to data with 2x gain |

#### 1.1.1.7 Bit Slip

The deserializer has a bit-slip feature for word alignment. In this mode, the CDR slips to the next bit from the deserializer. This feature helps with building word-alignment logic in the fabric. It is not used with the built-in 8b10b PCS core but is available for PMA only applications using fabric-based alignment. This feature adjusts the alignment of the deserialized word by 1-bit in either direction when the bit-slip feature is active, reducing the uncertainty by ensuring deterministic latency. This feature is supported by the transceiver configurator. The configurator enables this RX\_SLIP input port. This port requests the transceiver CDR lane slip the parallel boundary by 1-bit.

In PMA mode applications, the RX\_BIT\_SLIP port is exposed on the block for the fabric to access. The RX\_BIT\_SLIP rising edge requests Rx data path slip relative to the RX\_CLK by 1-bit (UI) using handshaking between RX\_BIT\_SLIP and RX\_VAL. The handshake works as follows:

- 1. Fabric must wait for RX\_VAL = 1. Then RX\_BIT\_SLIP may be asserted to initiate slip.

- 2. XCVR responds by lowering RX VAL to 0.

- 3. Fabric then lowers RX\_BIT\_SLIP.

- 4. XCVR completes the slip and the RX\_VAL is assigned to 1 synchronously with respect to RX\_CLK rising edge.

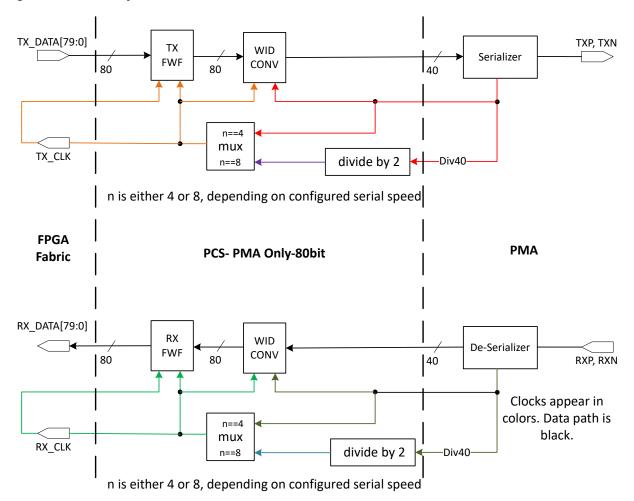

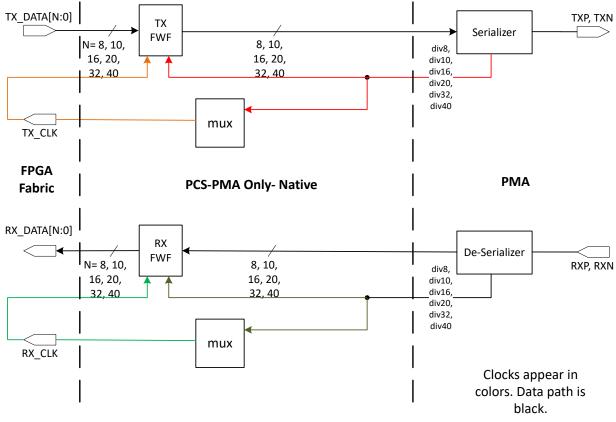

#### 1.1.1.8 Receive PCS Divider

The PCS divider divides the bit-rate clock from the CDR PLL to a lower rate for use in the receive PCS. The PMA sends parallel data from the de-serializer up to 40-bits wide. This divider also sets the width of the parallel data provided to the PCS to 8, 10, 16, 20, 32, 40, 64, or 80 bits. The Libero transceiver configurator sets the divider based on the data rate and ultimate fabric interface width.

#### 1.1.1.9 Receiver Calibration

The XCVR receivers include both analog and digital blocks that require calibration to compensate for process, voltage, and temperature (PVT) variations in conjunction with signal integrity. The embedded calibration block of transceiver performs calibration operations that optimize the performance of the transceiver interconnection. It includes an adaptive deserializer calibration algorithm to correct for lossy channels.

Libero selects CTLE only and CTLE/DFE modes based on the system data rate and channel loss needs. The pre-determined settings provide the starting point for the design. These settings are configured to the appropriate calibration requirements based on the targeted requirements. Three types of calibrations are carried out within the Rx:

CTLE DC-offset

- CTLE Frequency Response

- DFE

#### 1.1.1.9.1 CTLE DC-Offset Calibration

Process, voltage, and temperature (PVT) variations result in a DC-offset of the receiver front-end amplifiers, that is, the output is different from zero when the input is zero. This limits the sensitivity of the receiver and therefore the signal-to-noise ratio (SNR). It also limits the performance of the other calibration mechanisms.

The CTLE DC-offset calibration circuitry calibrates the DC-offset by zeroing the input and adding an offset. This offset is dynamically determined by a binary search in response to the logic output of the amplifier.

#### 1.1.1.9.2 CTLE Frequency Response Calibration

The CTLE frequency response can be set to a few discrete values, therefore calibration depends on searching for the settings that result in the largest eye area.

CTLE DC\_offset and CTLE Frequency Response calibration together make up the CTLE solution. For the most lossy and disruptive channels, many or all CTLE settings combinations can result in a zero eye-opening area. In these scenarios, DFE can sometimes allow for a non-zero area, which would otherwise be impossible with CTLE alone.

#### 1.1.1.9.3 DFE Calibration

DFE calibration is carried out by an embedded sequence function, which is optimized to avoid local minima, achieve predictable results, allow for low area, and operate at high clock speeds. It adjusts the feedback coefficients in response to the eye-area. The sequence of the function is used to determine the width, height, and center of the eye opening. DFE Calibration is carried out by a algorithm that adjusts the feedback coefficients (from H1 to H5) by trial-and-error in response to the eye-area of the eye\_monitor. The algorithm operates on one dimension (a single coefficient) at a time. It takes a step of size 1 in the positive direction and then the negative direction that is H1+1 and H1-1. If the area improves on either step, it continues to take another step in the same direction. If both directions yield a lower area, it continues to the next coefficient with the same step size. After failing to improve the area on all coefficients, it increases the step size and continue. If the area is improved, the step size immediately reduces to 1. See the AC468: PolarFire FPGA Transceiver Decision Feedback Equalization Application Note for more information.

Dependent on the specific design targets chosen through Libero, the design can be configured in one of two modes that require calibration of the receiver.

In CTLE only mode, CTLE solution is executed to optimize gain/frequency settings using CTLE Frequency Response and DC Offset calibration.

In CTLE/DFE mode, CTLE calibration is first run to optimize gain/frequency settings using CTLE Frequency Response and DC Offset calibration. DFE calibration is then run for centering and coefficients.

DFE is optionally programmed to be used in several operations. Full DFE calibration autonomously calibrates to the best found DFE coefficients for optimized data eye centering. These are controlled by Libero specified options.

DFE can also be set in static mode where the user can specify the exact DFE coefficients required by the design. DFE Coefficients are set through PDC commands (see 2.4.2.1 DFE Coefficients) can be used from the register rather than from calibration. This mode does not expose the CALIB\_REQ pin or any of the pins to trigger auto-calibration or incremental calibration.

Incremental DFE is another option of calibration to incrementally improve the performance of the DFE path. A specific PF\_XCVR\_ERM core is generated by Libero which, exposes the required pins to trigger the incremental calibration.

Two algorithms are available for re-calibration:

- Data Eye clock centering Re-calibration

- DFE Coefficient Re-calibration.

Both algorithms do eye-centering, however, they are independent operations. Full calibration and Static calibration are mutually exclusive and Incremental calibration of any of the two algorithms can only be applied after at least one 'Full calibration'.

Users can enable one or both choices in PF\_XCVR\_ERM configurator depending on the mode of operation and the receiver calibration options selected.

The calibration blocks are used at power-up calibration and user demanded recalibration. These are Libero configured. The following table lists the summary of mode of operations.

#### Table 1-2. Mode of Operations

| CDR Mode<br>(Data Rate ≤ 10312.5 Mbps) | Incrementally Re-calibrate Data Eye | Incrementally Re-calibrate DFE Co-efficients |

|----------------------------------------|-------------------------------------|----------------------------------------------|

| None_CDR                               | Not supported                       | Not supported                                |

| On Demand                              | Supported                           | Not supported                                |

| On Demand and First Lock               | Supported                           | Not supported                                |

| None_DFE                               | Not supported                       | Not supported                                |

Examples of the specific types of calibration are:

#### ON\_DEMAND

The receiver does not calibrate automatically. The user must initiate an on-demand calibration using either the wires on the XCVR interface or over the DRI. If the specific design performs dynamic reconfiguration using DRI, then the user routine must perform a recalibration each time the XCVR locks to a new data rate and/or data pattern.

In CDR modes where data rate  $\leq$  10312.5 Mbps, the device performs DC offset calibration of the CDR and the CTLE calibration when the user toggles the CALIB\_REQ port. When calibration is completed, the best DC offset and RX CTLE settings are applied to the receiver.

In DFE modes where data rate > 10312.5 Mbps, the device performs the same optimization as in CDR mode with the addition on performing full DFE calibration of the DFE coefficients. When calibration is completed the best DC offset, RX CTLE, and DFE coefficient settings are applied to the receiver.

To successfully complete the RX (CTLE) calibration process, the reference clocks must be stable and free running at device power-up and valid data must be present at the transceiver Rx input buffers. The data should be approximately the actual data that is received but does not need to be any particular data pattern. However, for DFE, calibration can be dependent on the data pattern used at DFE calibration. For example, JESD204B startups with a continuous K28.5 stream, then later shifts to actual 8b10b data. This is a change in data pattern and may impact calibrated DFE coefficients.

The transceiver component is generated by the Libero software to include enhanced receiver management logic to control the proper calibration of the receiver, see 1.2 Enhanced Receiver Management. The ERM manages calibration providing the user design a streamlined procedure to initiate and monitor calibration from the fabric interface. These calibration modes have higher power than using the NONE selection as the EYE MONITOR circuitry is active during these modes.

#### Incrementally Recalibrate Data Eye

This is a method to improve the performance of the DFE path after an initial calibration is performed. This recalibration is intended to improve the data eye for most gradients that typically occur due to temperature or voltage changes within the system.

The recalibration is performed by using the DC offset values for the DFE path that were determined by the prior offset calibration as the initial values and then perform the clock phase centering function. The calibration is marked as complete, when the area compute function is completed in the silicon/FPGA. This is indicated by driving the output signal LANE#\_DATA\_EYE\_CALIBRATION\_DONE to high.

#### Incrementally Recalibrate DFE Co-efficients

In this recalibration, the DFE co-efficients are recomputed in an incremental manner when an initial calibration is performed (on-demand or on initial power up).

The recalibration is performed by using the DC-offset values for the DFE path that were determined during a prior offset calibration as the initial value. The prior computed DFE coefficient values (H1-H5) are used as the starting coefficients for the DFE calibration. This reduces the DFE computation time. The calibration is marked as complete when the DFE calibration is completed in the silicon/FPGA. The output signal LANE#\_DFE\_COEFF\_RECALIBRATION\_DONE is driven high when the calibration is completed.

#### ON\_DEMAND\_AND\_FIRST\_LOCK

It is same as On\_Demand with the addition of auto calibration. Auto calibration occurs automatically the first time the CDR locks to data. The user can also on-demand initiate a calibration event using wires on the XCVR interface or over the DRI.

#### 1.1.2 Transmitter

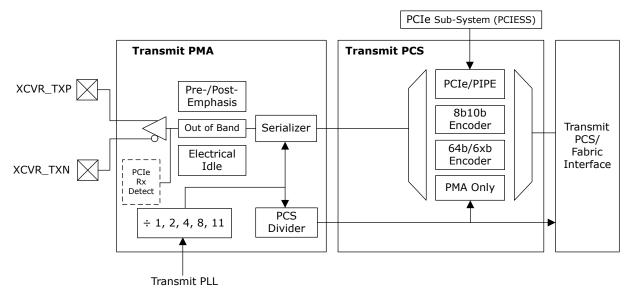

The transmitter takes parallel data from the FPGA fabric through the PCS-fabric interface block and gearing logic. The data passes through the PMA-PCS interface to the serializer to create a high-speed serial data stream using the serial clock provided from the transmit PLL. The transmitter portion of the PMA includes the transmitter serializer and the transmitter buffer as shown in the following figure.

#### Figure 1-5. Transceiver Transmitter

#### 1.1.2.1 Serializer

The serializer provides the link between the high-speed interface and the transmit PCS by performing a parallel-toserial conversion. Each lane has up to 40-bit data bus to the transmit PCS block and a separate post-divider for a divide by 1, 2, 4, 8, or 11. The post dividers are provided to divide the high-speed clock from the TxPLL to exactly what the serializer requires for the data rate. This allows sharing of a high-speed TxPLL by adjusting the local data rate within the transceiver lane. The glitch-free post-divider also allows for dynamic switching between dividers and data rates using the APB DRI.

#### 1.1.2.2 Transmit PCS Divider

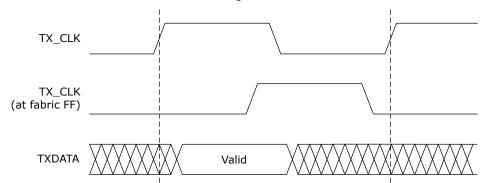

The PCS divider divides the bit-rate clock from the transmit PLL to a lower rate TX\_CLK clock for use in the fabric. The PMA receives parallel data in the serializer up to 40 bits wide. This divider also sets the width of the parallel data received from the PCS to 8, 10, 16, 20, 32, 40, 64, and 80 bits. The specific ratio is a function of the parallel-to-serial or serial-to-parallel conversion in the PMA.

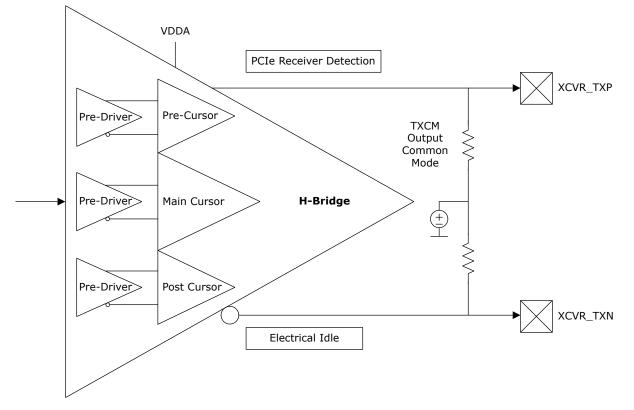

#### 1.1.2.3 Transmit Output Buffer

The following figure shows the transmit output buffer of the transceiver lane, which connects to the PCB via the XCVR\_TXP/N output pins. The low-power H-bridge differential output buffer includes a configurable driver for amplitude on the 100  $\Omega$  differential load up to a maximum swing of 1 V peak to peak. In addition, selectable levels of transmit common-mode voltage (Tx VCM) are available besides the swing amplitude control for the output driver segments to control the amount of emphasis. The transmit output buffer settings are accessible in real-time for adjustment through the JTAG interface using SmartDebug. It includes a receiver detection to recognize the presence of a physical link. The output buffer also has electrical idle capabilities used to orderly quiet the link transmitters.

#### Figure 1-6. Transmit Output Driver

Transmit common-mode voltage levels for the drivers are selected by the user during the configuration of the PMA when using the transceiver configurator in the Libero software. Reducing the transmit output amplitude lowers the overall transceiver power consumption.

**Note:** The user can also use a JTAG-based interface from SmartDebug to experiment with transmit settings.

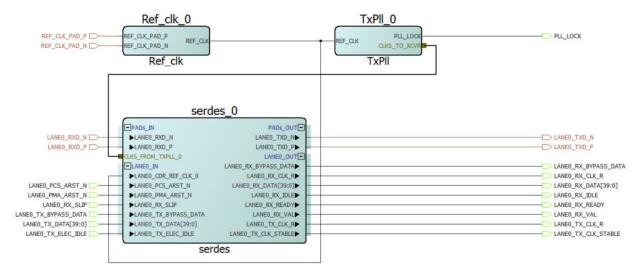

## 1.2 Enhanced Receiver Management

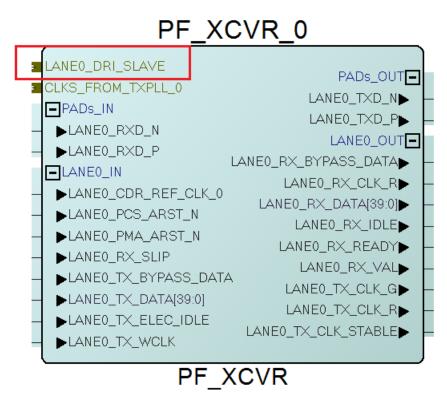

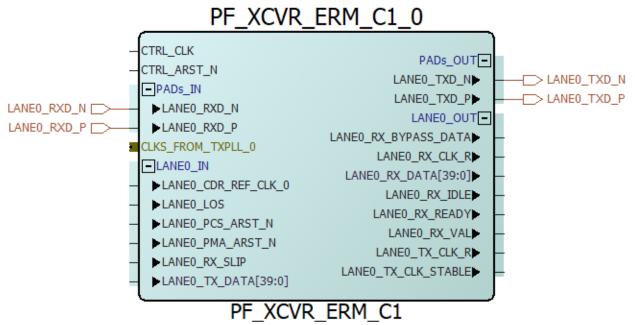

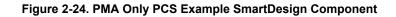

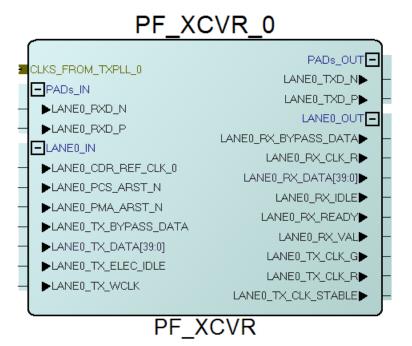

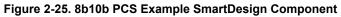

Enhanced receiver management (ERM) is implemented in FPGA logic inside the XCVR component. The ERM adds DFE/CDR calibration management, and lock-to-data lock detection capabilities of the PF\_XCVR. The RTL is autonomously generated by Libero software. The generated blocks manage the start-up/on-demand CDR/DFE calibration and fine-grain lock detector with a PMA, 8b10b, and 64b6xb modes of the PF\_XCVR. The ERM allows the Rx Lock detection logic to handle advanced capabilities of Delayed Traffic and Cable Pull during operation without further interaction from other user logic.

The enhanced receiver management feature provides the following functions.

- Manages receiver lock-to-reference versus lock-to-data operation modes of PF\_XCVR.

- Manages receiver calibration, see 1.1.1.9 Receiver Calibration.

- Provides optional automatic calibration upon determining first valid receiver bit-lock.

- Provides optional support for on-demand requested calibration.

- Provides optional support for Data Eye clock centering recalibration.

- Provides optional support for DFE Coefficient recalibration.

- Provides indicator when receiver completes calibration.

- Provides LANEx\_LOS input, which may be asserted as a means of holding lock management in lock-toreference. This is useful when interfacing to an optical interface, which provides a loss-of-signal indicator such as SFP.

Enhanced receiver management is recommended to optionally improve the link management for data rates above 5 Gbps but can be used to improve link reliability with lower data rates while using the automatic calibration features of ERM. Enhanced receiver management is not included for PCI Express, PIPE, or Burst Mode Receiver solutions of PF\_XCVR when generated by Libero software. Generally, the advanced features from ERM are already managed by these protocol layers.

ERM is utilized to augment the Rx\_IDLE peak detector logic, which is only valid for a limited minimum density of transitions on the Rx data or high bit rates. Other lower density patterns such as SDI at 270 Mb/s or 10G-KR Auto-negotiation data are good examples of data patterns that cannot use the peak detector and thus other system-dependent methods to keep the Rx PLL in lock-to-reference mode in the absence of incoming data are required.

For example, some protocols such as 10GBASE-KR and PCI-Express, exchange specific training patterns to establish and tune the respective links. These protocols does not use the ERM as it can interfere with these kinds of negotiation operations. Other applications such as CPRI goes through a sophisticated process by stepping through multiple data rates during its startup. The ERM must not be used in this type of application. ERM must also not be used with Rx-only modes such as DisplayPort where the RxPLL is locked to a lower rate data stream.

ERM can be used with JESD204b, Interlaken, and fixed rate CPRI applications.

The ERM functionality extends capabilities for transceiver applications for both the family devices excluding the MPF300XT device. The ERM uses minimal logic resources, but does extend the lock time of the CDR by approximately three times versus when the ERM is not included.

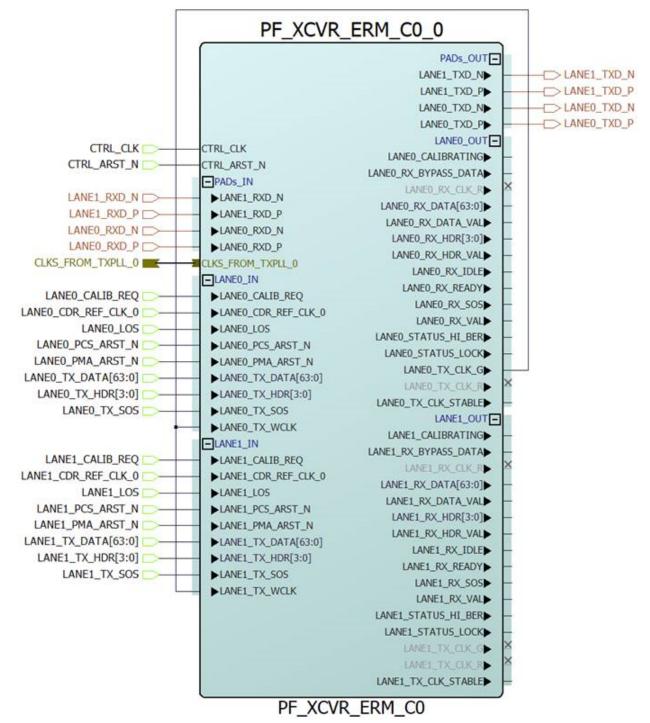

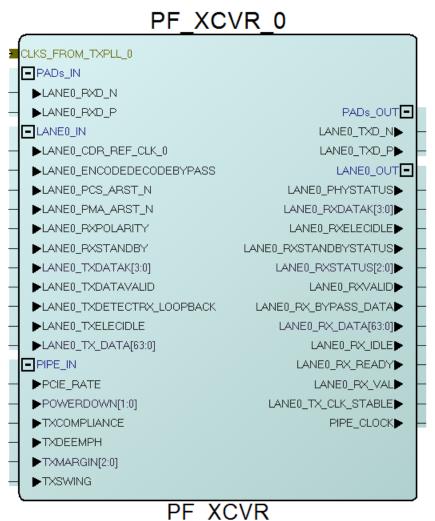

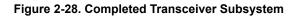

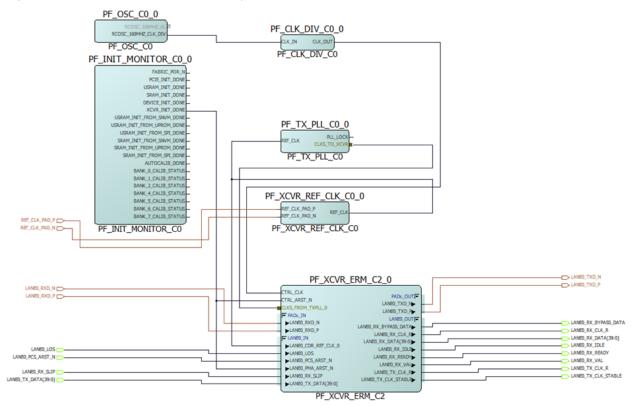

The ERM ports are exposed by the transceiver configurator dependent on the selected calibration when enabled (default) in the GUI, see Figure 1-7. If the XCVR module is generated without selecting the ERM option in the Libero SoC configurator, the module will still contain ERM in the component name, however, the ERM functionality is reduced. The following table lists the ports required or used in conjunction with the ERM module.

| Name                           | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|--------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CTRL_CLK                       | Input     | 40 MHz clock for the enhanced receiver management logic. The CTRL_CLK input clock can be sourced from the divided output of the PF_OSC (RCOSC_160MHZ_CLK_DIV).                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| CTRL_ARST_N                    | Input     | Input signal needed to reset ERM. User must drive this input from the XCVR_INIT_DONE signal of the PF_INIT_MONITOR component.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| LANE#_LOS                      | Input     | LANEx_LOS input which may be asserted from an external source such as optical SFP during no-signal condition as a means of preventing entry to lock-to-data. This input must be used to control application scenarios where the incoming data stream has enough activity to trigger the LANE#_RX_IDLE but lacks enough transitions to lock the RXPLL. LOS=0 (de-assertion) should happen when valid serial data is applied at the RxP/N inputs of the receiver. LOS=1 assertion must happen prior to the ERM's entry to lock-to-data, otherwise the assertion does nothing. |  |

| LANE#_CALIB_REQ                | Input     | Active-high input signal used to request an On-Demand calibration. LANE#_CALIB_REQ is edge triggered not level. User must clear and re-assert the CALIB_REQ for trigger on-demand calibration request.                                                                                                                                                                                                                                                                                                                                                                      |  |

| LANE#_CALIBRATING              | Output    | Output signal that will go HIGH to indicate that the DFE/CDR is calibrating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| LANE#_RX_VAL                   | Output    | Indicates CDR fine lock and ERM managed operations complete. See 1.3 Transceiver PCS Interface Modes for more information.         1 – indicates Fine Lock is asserted, and recovered data is valid.         0 – indicates Fine Lock is de-asserted and recovered data is invalid.                                                                                                                                                                                                                                                                                          |  |

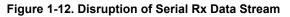

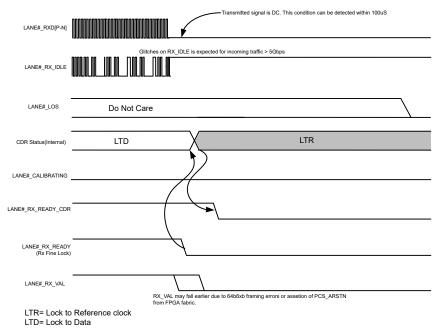

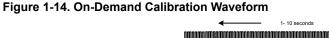

| LANE#_RX_IDLE                  | Output    | Indicates activity on the receiver inputs (RXD[P:N]). For ≤ 5 Gbps, active-low (RX_IDLE=0 indicates activity).<br>For >5G bit rates, this signal may not be accurate indicator of data activity. It may toggle or be HIGH although valid signal is applied at the receiver. This signal is exposed for debugging purposes only, for example, detection of signal when RxPLL is in lock2ref mode. See Figure 1-11, Figure 1-12, Figure 1-13, and Figure 1-14.                                                                                                                |  |

| LANE#_RX_READY                 | Output    | Indicates CDR fine lock completion. See 1.3 Transceiver PCS Interface Modes for more information.<br>1 – Fine lock is asserted (that is, RxPLL is locked to incoming data within<br>± 4000 ppm of the LANE#_TX_CLK_{G,R} frequency).<br>0 – Fine lock is de-asserted (that is. recovered clock is outside the ± 4000 ppm of the REFCLK frequency).                                                                                                                                                                                                                          |  |

| LANE#_RXD[P:N]                 | Input     | Differential pair of serial data inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| LANE#_DATA_EYE_<br>CALIBRATION | Input     | Active-high input signal (Asynchronous signal) to request Data Eye clock centering recalibration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

Table 1-3. ERM Ports

| continued                            |           |                                                                                                                                                       |  |

|--------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                                 | Direction | Description                                                                                                                                           |  |

| LANE#_DFE_COEFF_CALIBRAT             | Input     | Active -high input signal (Asynchronous signal) to request Incremental DFE Coefficient recalibration.                                                 |  |

| LANE#_DATA_EYE_<br>CALIBRATION_DONE  | Output    | Data Eye clock centering recalibration request handshake signal. This signal goes high when the Data Eye clock centering calibration is done.         |  |

| LANE#_DFE_COEFF_CALIBRAT<br>ION_DONE | Output    | Incremental DFE coefficient recalibration request handshake signal. This signal goes high when the Incremental DFE coefficient recalibration is done. |  |

#### Figure 1-7. Enhanced Receiver Management in XCVR Configurator

| General          |                         |                                |                          |

|------------------|-------------------------|--------------------------------|--------------------------|

| Iransceiver mode | Tx and Rx (Full Duplex) | ✓ Enhanced receiver management |                          |

| Number of lanes  | 1                       | Receiver calibration           | Dn-Demand and First Lock |

The operation ERM relies on the transceiver configurator settings to determine the selected calibration requirements, as shown in the following figure. The transceiver lane calibration options are selected with the transceiver configurator. See 1.1.1.9 Receiver Calibration for more information.

#### Figure 1-8. Calibration Options for Enhanced Receiver Management Operations

| Ξ | General          |                         |                                              |                          |

|---|------------------|-------------------------|----------------------------------------------|--------------------------|

|   | Transceiver mode | Tx and Rx (Full Duplex) | <ul> <li>Enhanced receiver manage</li> </ul> | ement                    |

|   | Number of lanes  | 1                       |                                              | None (CDR)               |

|   |                  |                         | Incrementally recalibrate                    | None (CDR)               |

|   |                  |                         | Incrementally recalibrate I                  | On-Demand                |

|   |                  |                         |                                              | On-Demand and First Lock |

| Ξ | PMA Settings     |                         |                                              | None (DFE)               |

The following receiver calibration options are provided for the ERM operation:

- None (CDR): Select if the XCVR is configured as CDR and no CTLE auto-calibration is performed. Static

settings are configured by Libero based on data rate and backplane model. This receiver calibration mode uses

Lock2Reference of the Rx PLL.

- **On-Demand and First Lock**: Select to perform calibration on first lock (after PoR) and on-demand. This option is available for both CDR and DFE configuration of the XCVR. You can trigger calibration on-demand using CALIB\_REQ port. The CALIBRATING signal is asserted upon CALIB\_REQ assertion and de-asserted when the calibration is completed.

- **On-Demand**: Select to perform calibration on-demand. This option is available for both CDR and DFE configuration of the XCVR. You can trigger calibration on-demand using CALIB\_REQ port. The CALIBRATING signal is asserted upon CALIB\_REQ assertion and de-asserted when the calibration is completed.

- None (Static DFE): DC Offset Calibration of the CDR is performed, however, the DFE Coefficients are set through PDC commands used from the register rather than from automatic DFE calibration operation. See 2.4.2 Physical Constraints. Static\_DFE does not use the DFE calibration routine and requires the user to carefully select DFE coefficient values. These values can be gathered by the SmartDebug tool or by simulation.

There are two potential ways to incrementally improve the performance of the DFE path when an initial calibration is completed.

- **Incrementally Recalibrate Data Eye**: This recalibration should improve the data eye for most gradients that typically occur from temperature or voltage changes within the system.

- **Incrementally Recalibrate DFE Coefficient**: This recalibration performs the DFE calibration in incremental method. The initially calculated DFE coefficient values are used as the starting values for this algorithm. This results in the reduction of the Calibration time by reducing the number of DFE coefficients that requires recalibration.

**Note:** Full calibration is always done for DFE. You must select one of the two options—On-Demand and First Lock or On-Demand—if the transceiver is configured in DFE mode.

Enable LANE#\_RX\_READY\_CDR and LANE#\_RX\_VAL\_CDR ports are optionally exposed by selecting the associated checkbox for the ERM solution. The XCVR component provides optional RX\_READY\_CDR and RX\_VAL\_CDR ports for the datapath and variation of the LANE#\_RX\_READY and LANE#\_RX\_VAL ports that are always exposed with the ERM. These additional ports are provided to monitor the CDR lock signal. These ports can be used for rate change from >5G to <5G and 10GBASE-KR auto-negotiation support.

XCVR designs implementing protocols with auto-negotiation logic typically negotiates link rates over DRI. In these use cases, the ERM will interfere with the auto-negotiation and can cause incorrect behavior.

| Clocks and Resets                  |           |   |                                          |                         |   |

|------------------------------------|-----------|---|------------------------------------------|-------------------------|---|

| Interface Clocks                   | nce dock  |   |                                          |                         |   |

| <u>T</u> X clock                   | Regional  | • | <u>R</u> X dock                          | Regional                | • |

| Interface Resets                   | TX and RX | Ŧ | PCS Reset                                | RX Only                 | • |

| Optional Ports<br>Enable TX_BYPAS: |           |   | ✓ Enable RX_READY_C ✓ Enable JA_CLK port | DR and RX_VAL_CDR ports |   |

#### Figure 1-9. Exposing RX\_READY\_CDR and RX\_VAL\_CDR Pins

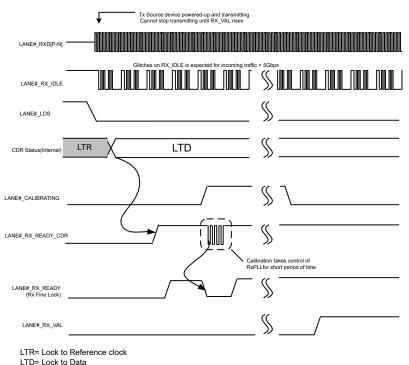

The ERM manages the device behavior at first power-up or release from device reset (DEVRSTn). The ERM managed calibration begins after the device complete its initial startup configuration and the assertion of XCVR\_INIT\_DONE de-asserts the CTRL\_ARST\_N. This requires a valid serial data stream to be applied to the RXD input pins at the time of de-assertion of the CTRL\_ARST\_N signal. At that time, the ERM performs the desired user selected calibration operation as shown in the following figure. The LANE#\_RX\_IDLE activity shows the detection of incoming data moving the ERM to place the CDR into LOCK2DATA operation while it completes calibration and fine lock operation. The operation is indicated by the LANE#\_CALIBRATING and RX\_READY status signals. The LANE#\_RX\_VAL with output high upon completion of the calibration and locking routine.

The following table lists the ports exposed based on DFE options.

#### Table 1-4. DFE Options

| Options                                    | Input Port                  | Output Port                      |

|--------------------------------------------|-----------------------------|----------------------------------|

| Incrementally recalibrate data eye         | LANE#_DATA_EYE_CALIBRATION  | LANE#_DATA_EYE_CALIBRATION_DONE  |

| Incrementally recalibrate DFE coefficients | LANE#_DFE_COEFF_CALIBRATION | LANE#_DFE_COEFF_CALIBRATION_DONE |

#### Figure 1-10. DFE Options

| ٩                                   |                               |                         |          |                                                                                                                 |                                         |   | 4          |                |

|-------------------------------------|-------------------------------|-------------------------|----------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------|---|------------|----------------|

| PF_XCVR_default_configuration       | General                       |                         |          |                                                                                                                 |                                         |   |            |                |

| IOGBASE-R                           | Contraction and the           | E I I I I I I I I       |          | Enhanced receiver management                                                                                    |                                         |   |            |                |

| OGBASE-KR                           | Transceiver mode              | Tx and Rx (Full Duplex) | <u> </u> | <ul> <li>Enhanced receiver management</li> </ul>                                                                |                                         |   |            |                |

| GMII                                | Number of lanes               | 1                       |          | Receiver calibration                                                                                            | None (CDR)                              | * |            |                |

| SGMII                               |                               | 1.00                    |          | Incrementally recalibrate data                                                                                  | eve                                     |   |            |                |

| PRI Rate 1<br>PRI Rate 2            |                               |                         |          | Incrementally recalibrate DFE                                                                                   |                                         |   |            |                |

| PRI Rate 3                          |                               |                         |          | I Incrementally recalibrate DFE                                                                                 | coefficients                            |   |            |                |

| PRI Rate 3<br>PRI Rate 4            |                               |                         |          |                                                                                                                 |                                         |   |            |                |

| PRI Rate 4 PRI Rate 5               | PMA Settings                  |                         |          |                                                                                                                 |                                         |   |            |                |

| PRI Rate 6                          |                               | 68                      |          |                                                                                                                 | 100000000000000000000000000000000000000 |   |            |                |

| PRI Rate 7                          | TX data rate                  | 5000                    | Mbps     | RX data rate                                                                                                    | 5000 Mbps                               |   |            |                |

| PRI Rate 8                          | TX clock division factor      | 1                       |          | and and the second s | Lock to data                            |   | / / /      | PF XCVR 0      |

| DI 3G                               | TX Clock division factor      | 11                      | <u> </u> | RX CDR lock mode                                                                                                | Lock to data                            |   | -CTRL GX   |                |

| DI HD                               | TX PLL base data rate         | 5000.000                | Mbos     | RX CDR reference dock source                                                                                    | Dedicated 💌                             |   | -CTRL ARST | N HILLING      |

| DI SD                               |                               |                         |          |                                                                                                                 |                                         |   | BORS, FROM |                |

| nterlaken 6.25G                     | TX PLL bit dock frequency     | 2500.000                | MHz      | RX CDR reference dock frequency                                                                                 | 125.0 MHz                               |   | F PADA, IN |                |

| nterlaken 10G                       |                               |                         |          | RX JA dock frequency                                                                                            | 125 MHz                                 |   |            |                |

| AUI                                 |                               |                         |          |                                                                                                                 |                                         |   | PF_X       | CVR::PF_XCVR_0 |

|                                     | PCS Settings                  |                         |          |                                                                                                                 |                                         |   |            |                |

| man I among and I                   | E PCS Settings                |                         |          |                                                                                                                 |                                         |   |            |                |

| Apply New preset                    | TX PCS-Fabric interface width | 60                      | ▼ bits   | RX PCS-Fabric interface width                                                                                   | 40 💌 bits                               |   |            |                |

|                                     | TA PEST BUILTINE THE THE      | 140                     | 00       | KA PCS-Pabric Interface widen                                                                                   | 140 015                                 |   |            |                |

|                                     | TX FPGA interface frequency   | 125                     | MHz      | RX FPGA interface frequency                                                                                     | 125 MHz                                 |   |            |                |

|                                     |                               | 14.0                    |          | not if an internet in equality                                                                                  |                                         |   |            |                |

|                                     | PMA Mode                      |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     | Enable CDR Bit-sl             | o port                  |          |                                                                                                                 |                                         |   |            |                |

|                                     | It Endure Cort Dit si         | p por c                 |          |                                                                                                                 |                                         |   |            |                |

|                                     | 8b 10b Encoding/Decoding      |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     |                               |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     | 64b6xb Gear Box               |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     | 6 64h66h                      |                         |          | C 646576                                                                                                        |                                         |   | • Symbol   |                |

|                                     | . 040000                      |                         |          | 0.0070                                                                                                          |                                         |   | Symbol     |                |

|                                     |                               |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     |                               |                         |          |                                                                                                                 |                                         |   |            |                |

| Messages 🔞 Errors 🗼 Warnings 🕕 Info |                               |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     |                               |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     |                               |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     |                               |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     |                               |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     |                               |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     |                               |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     |                               |                         |          |                                                                                                                 |                                         |   |            |                |

|                                     |                               |                         |          |                                                                                                                 |                                         |   |            |                |

The following waveforms show the behavior of the XCVR with ERM optionally included in the Libero generated component. XCVR configurations without ERM operates with reduced functionality and the LANE#\_RX\_READY behavior is identical to the LANE#\_RX\_READY\_CDR waveform since the ERM no longer manages the lane.

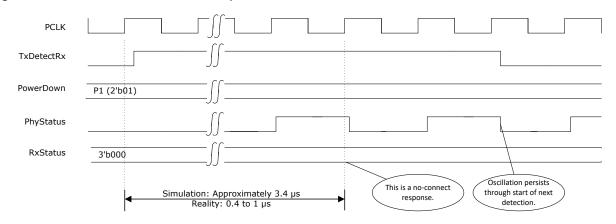

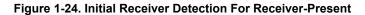

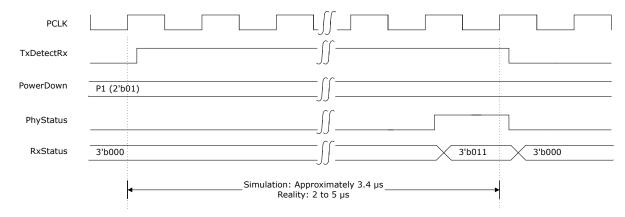

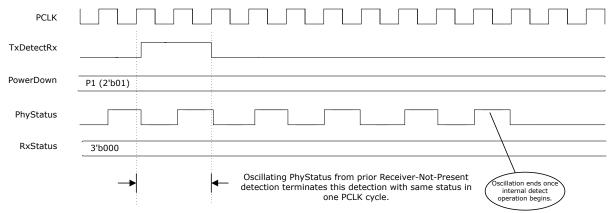

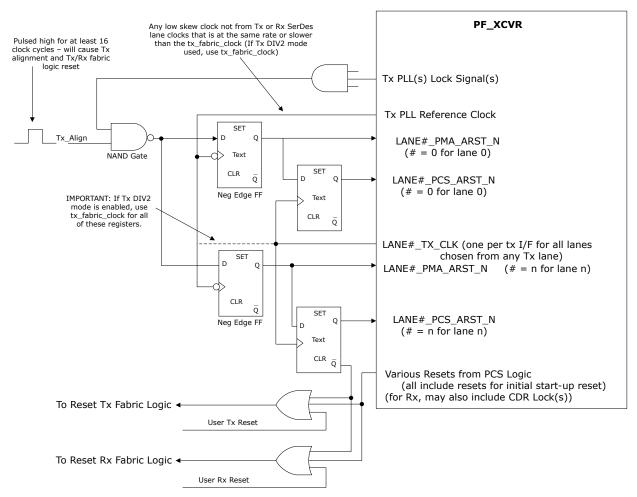

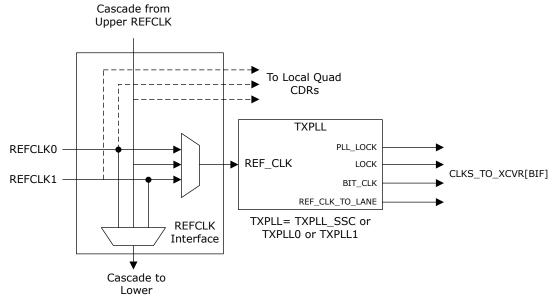

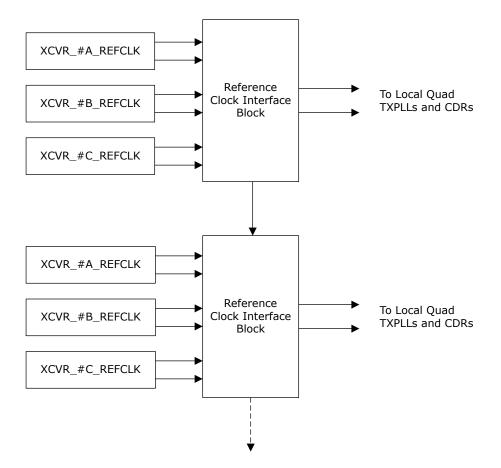

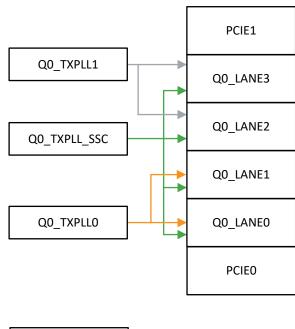

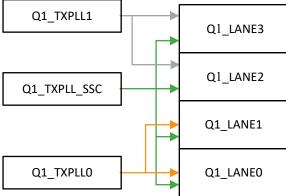

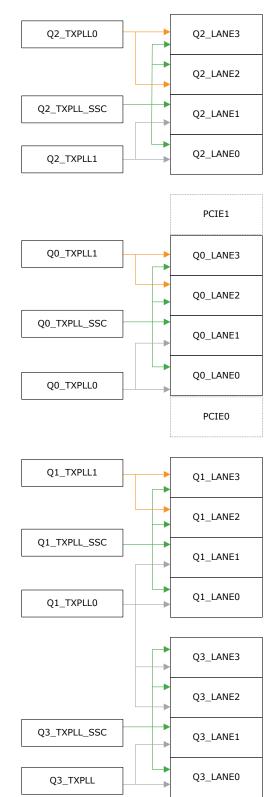

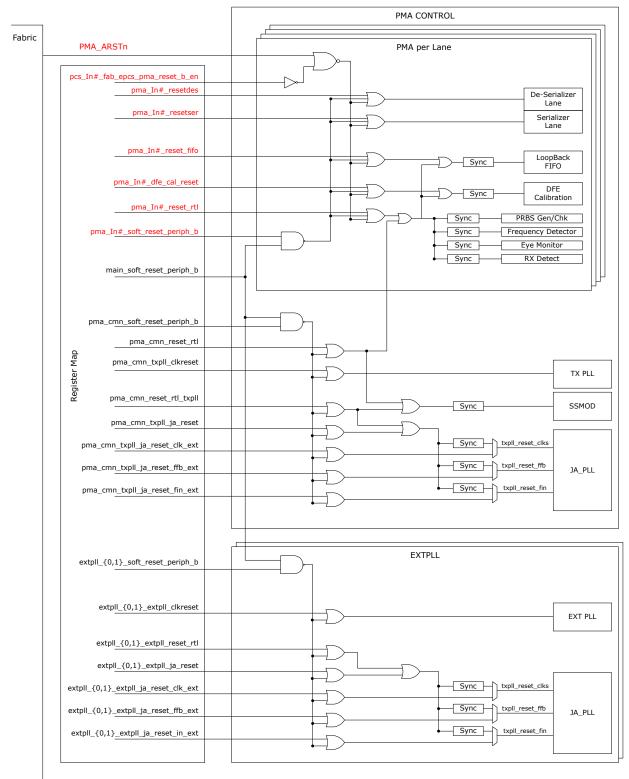

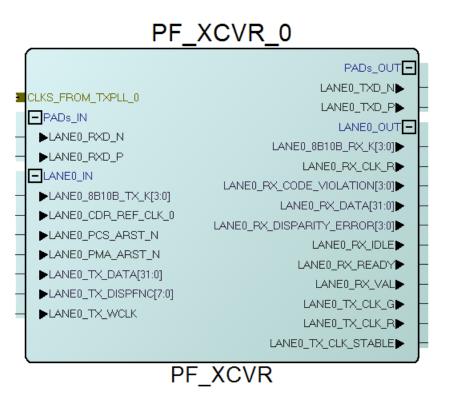

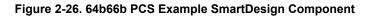

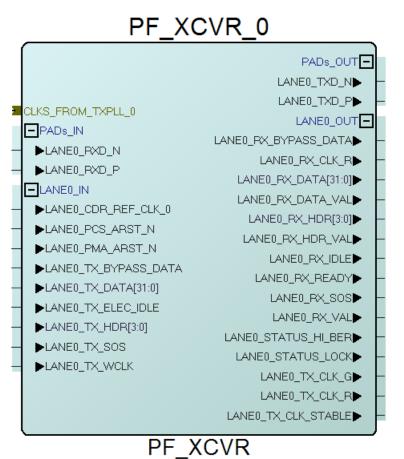

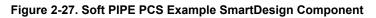

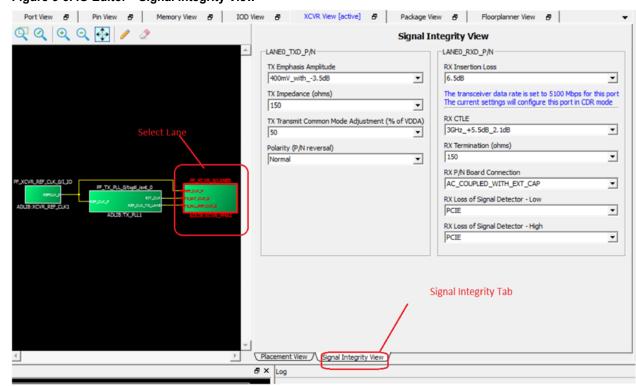

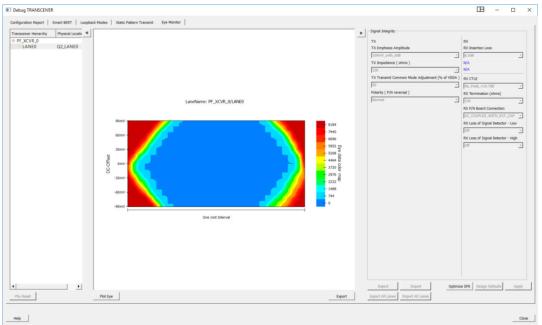

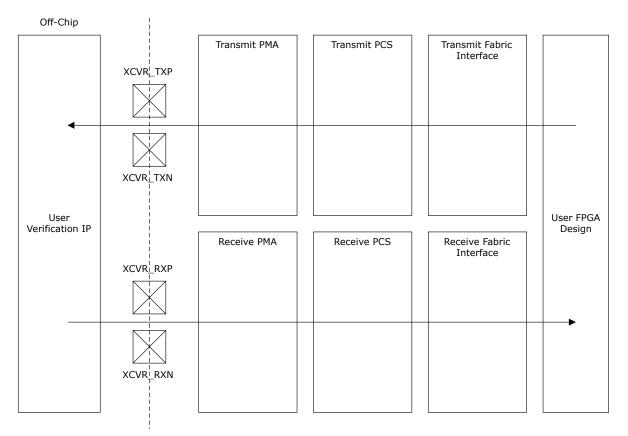

Figure 1-11. First Lock Calibration Waveform