# PolarFire® FPGA and PolarFire SoC FPGA PCI Express

## Introduction

Microchip's PolarFire FPGAs are the fifth-generation family of non-volatile FPGA devices, built on state-of-the-art 28 nm non-volatile process technology. PolarFire FPGAs deliver the lowest power at mid-range densities. PolarFire FPGAs lower the cost of mid-range FPGAs by integrating the industry's lowest power FPGA fabric, lowest power 12.7 Gbps transceiver lane, built-in low power dual PCI Express Gen2 (EP/RP), and, on select data security (S) devices, an integrated low-power crypto co-processor.

Microchip's PolarFire SoC FPGAs are the fifth-generation family of non-volatile SoC FPGA devices, built on state-of-the-art 28 nm non-volatile process technology. The PolarFire SoC family offers industry's first RISC-V based SoC FPGAs capable of running Linux. It combines a powerful 64-bit 5x core RISC-V Microprocessor Subsystem (MSS), based on SiFive's U54-MC family, with the PolarFire FPGA fabric in a single device.

PCI Express (PCIe) is a scalable, high-bandwidth serial interconnect technology that maintains compatibility with existing PCI systems. Microchip's PolarFire SoC FPGAs and PolarFire FPGAs contain fully integrated PCIe endpoint and root port subsystems with optimized embedded controller blocks that use the physical layer interface of the transceiver for the PCI Express (PIPE) interconnection within the transceiver block.

Each device includes two embedded PCIe subsystem (PCIESS) blocks that can be configured using the PF\_PCIE configurator in the Libero® SoC software.

The following table summarizes the PCIESS components available in PolarFire and PolarFire SoC families.

**Table 1. PCIESS Components**

| Fabric Component                                          | PolarFire FPGA (MPF) | PolarFire SoC FPGA (MPFS) |

|-----------------------------------------------------------|----------------------|---------------------------|

| Physical layer of XCVR                                    | ✓                    | ✓                         |

| PCIe IP (Data link layer (DL) and Transaction layer (TL)) | ✓                    | ✓                         |

| Bridge Layer                                              | ✓                    | ✓                         |

| AXI4 Layer                                                | ✓                    | ✓                         |

| MSS Component                                             |                      |                           |

| PCIe MSS                                                  | _                    | ✓                         |

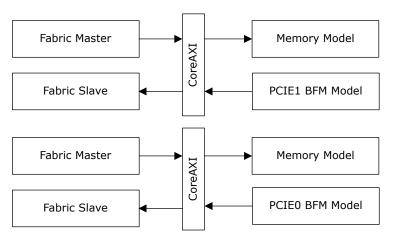

The PCIESS supports AMBA AXI4 master/slave user interface functionality between the AXI4 and PCIe systems.

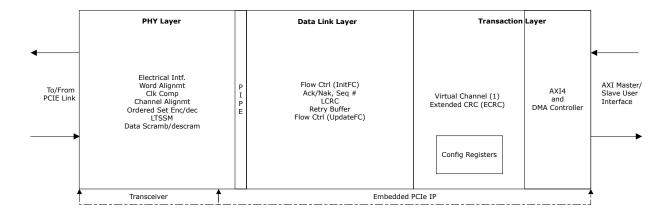

Figure 1. PCle Functional Layers of PCIESS

The PCIESS is compliant with the following standards:

- PCI Express Base Specification with GEN1/2, Revision 3.0

- PCI Express Card Electromechanical (CEM) 2.0

- PCI Industrial Computer Manufacturers Group (PICMG) 3.4

- PCI Power Management Specification, v1.2

- AMBA AXI Protocol Specification, Version 2.0 ARM, March 2010

## **Features**

The PCIESS is a hard block and supports the following features:

- PCIE 3.0 compliant with 2.5 and 5.0 Gbps line speeds

- x1, x2, and x4 lane-support<sup>1</sup>

- Endpoint support for up to six 32-bit or three 64-bit base address register (BAR)

- Root port support for up to two 32-bit or one 64-bit BAR

- Two fully-independent Direct Memory Access (DMA) engines with Scatter-Gather DMA (SGDMA) support

- One virtual channel (VC)

- Single-function capability

- Maximum payload size (MPS) of up to 256 bytes

- Advanced error reporting (AER) support

- Integrated clock domain crossing (CDC) to support user-selected frequency

- Lane reversal/polarity inversion

- Legacy PCI power management

- Endpoint hot-plug capability (not supported for root port)

- Native active-state power management L0 and L1 support

- Power management event (PME) message

- Latency tolerance reporting (LTR)

- 64-bit AXI master and slave interface to the FPGA fabric

- End-to-end data integrity

**User Guide** DS50003188B-page 2 © 2022 Microchip Technology Inc.

Each device supports two PCIESS blocks, which shares four lanes within a transceiver block. This permits two x1 PCIESS or two x2 PCIESS that can run simultaneously, or one PCIESS that can run as x4 and the other PCIESS is left unused.

## References

- For information about transmitter, receiver, and transceiver block generation, see PolarFire FPGA and PolarFire SoC FPGA Transceiver User Guide.

- For information about DRI, see PolarFire and PolarFire SoC DRI User Guide.

- For information about PolarFire SoC PCIe Root Port Linux reference design, see github.com/polarfire-soc/iciclekitreference- design.

- For information about PolarFire FPGA reference design, see DG0756: PolarFire FPGA PCIe Endpoint, DDR3, and DDR4 Memory Controller Data Plane Demo Guide.

- For information about MSS, see PolarFire SoC FPGA MSS Technical Reference Manual.

- For information about design initialization, see PolarFire FPGA and PolarFire SoC FPGA Device Power-Up and Resets User Guide.

- For information about board design recommendations, see respective UG0726: PolarFire FPGA Board Design User Guide or PolarFire SoC FPGA Board Design Guidelines User Guide.

- For information about configuration registers, see respective PolarFire Device Register Map or PolarFire SoC Register Map.

# **Table of Contents**

| Intr | oductio | on                               | 1  |

|------|---------|----------------------------------|----|

|      | 1.      | Features                         | 2  |

|      | 2.      | References                       | 3  |

| 1.   | Func    | tional Descriptions              | 5  |

|      | 1.1.    | Physical Layer Interface         | 5  |

|      | 1.2.    | Data-link and Transaction Layers | 7  |

|      | 1.3.    | Bridge Layer                     | 11 |

|      | 1.4.    | AXI4 Layer                       |    |

|      | 1.5.    | PCIESS Configuration Interface   |    |

|      | 1.6.    | PCIESS Port List                 | 23 |

| 2.   | PCle    | MSS                              | 30 |

| 3.   | Imple   | ementation                       | 31 |

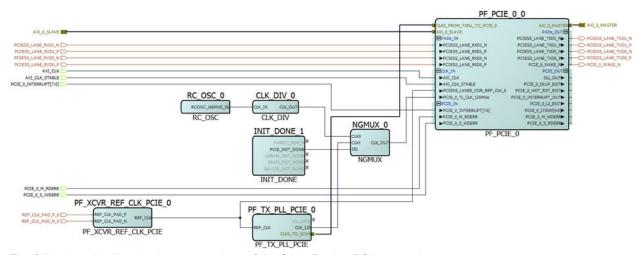

|      | 3.1.    | Libero Configurators             | 32 |

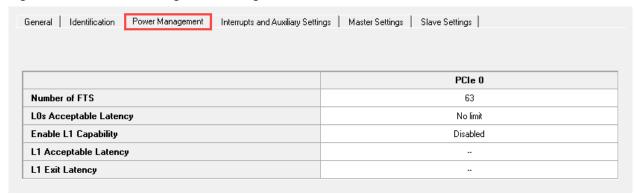

|      | 3.2.    | PCIe Configurator                | 32 |

|      | 3.3.    | Design Constraints               | 40 |

|      | 3.4.    | PCIe Simulation                  |    |

|      | 3.5.    | PCIe Subsystem Performance       |    |

|      | 3.6.    | Initialization                   | 44 |

| 4.   | Confi   | guration Registers               | 45 |

| 5.   | PCle    | Configuration Space              | 46 |

| 6.   | Board   | d Design Recommendations         | 49 |

|      | 6.1.    | AC-Coupling                      | 49 |

|      | 6.2.    | Lane Reversal                    | 49 |

|      | 6.3.    | Polarity Inversion               | 49 |

|      | 6.4.    | PCIe Power-Up                    | 49 |

| 7.   | Revis   | sion History                     | 51 |

| Mic  | rochip  | FPGA Support                     | 54 |

| The  | Micro   | ochip Website                    | 54 |

| Pro  | duct C  | Change Notification Service      | 54 |

| Cus  | stomer  | Support                          | 54 |

| Mic  | rochip  | Devices Code Protection Feature  | 54 |

|      | •       | ice                              |    |

|      |         | ks                               |    |

|      |         | anagement System                 |    |

|      | -       | e Sales and Service              |    |

| VVO  | iuwiu   | e dales allu del vice            |    |

#### 1. **Functional Descriptions**

The PCle subsystem uses several built-in features such as transceivers, embedded PCle controller, and programmable FPGA resources. The functional details of the PCIe subsystem are described in this chapter.

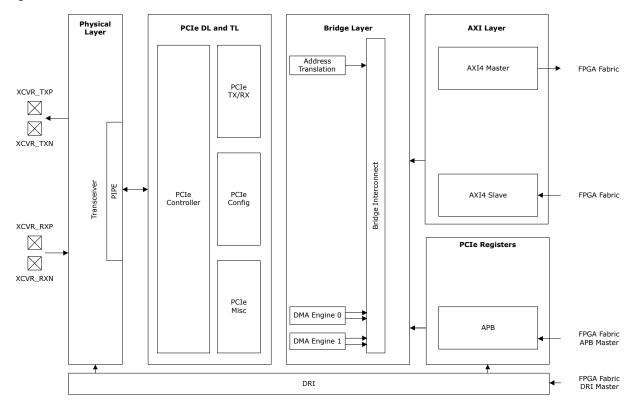

As shown in the following figure, the PCIESS is composed of four sub-modules:

- Physical layer

- PCIe DL and TL

- Bridge layer

- **AXI** layer

- Configuration interface (DRI and APB)

Figure 1-1. Embedded PCIESS Architecture

#### 1.1 **Physical Layer Interface**

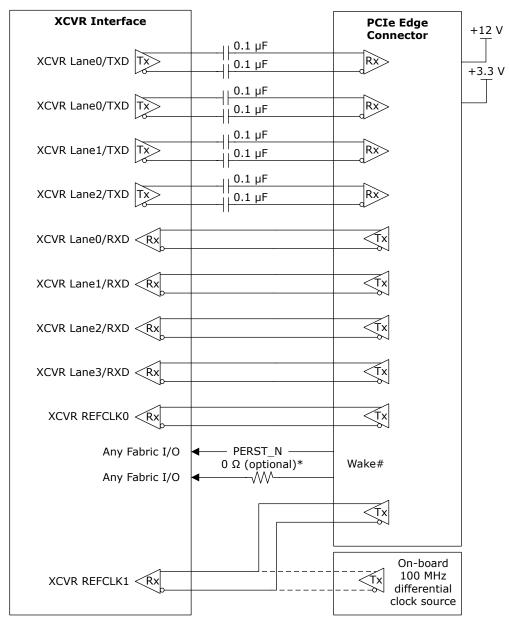

A PCIe lane consists of a pair of differential transmit signals and a pair of differential receive signals. The lanes are organized, as listed in the following table.

Table 1-1. Lane Configuration

| X1                              | X2                                               | Х3                                      |

|---------------------------------|--------------------------------------------------|-----------------------------------------|

| PCle0 (Lane0) and PCle1 (Lane2) | PCIe0 (Lane0, Lane1) and<br>PCIe1 (Lane2, Lane3) | PCle1 (Lane 0, Lane1, Lane2, and Lane3) |

**User Guide** DS50003188B-page 5 © 2022 Microchip Technology Inc.

## 1.1.1 Physical Layer Functions

The physical layer is an electrical physical media attachment (PMA) required to connect to a PCIe system, and supports the following features:

- PCI Express 2.0 electrical compliance

- 2.5 and 5.0 Gbps common-mode logic (CML) electrical interface

- Signal integrity programmability including differential output voltage, transmitter de-emphasis, and receiver-side continuous-time linear equalization (CTLE)

- ±300 ppm clock-tolerance compensation

- Serializer and de-serializer

- 8b/10b symbol encoding/decoding

- · Symbol alignment

- · Framing and application of symbols to lanes

- · Lane to lane Tx deskew

#### 1.1.2 Receiver

The transceiver input includes all the features required to build a PCIe interface, such as input level sensitivity, signal detection, and termination. When PCIESS is used within a device, the Libero SoC software configures the receiver with all the necessary input features. For more information, see PolarFire FPGA and PolarFire SoC FPGA Transceiver User Guide.

## 1.1.3 Transmitter

The transceiver output includes features such as output swing, termination, and de-emphasis. When PCIESS is used within a device, the Libero SoC software configures the transmitter with all the necessary output features. For more information, see PolarFire FPGA and PolarFire SoC FPGA Transceiver User Guide.

**Note:** In PCIe subsystem, the receiver detection circuitry within the transmitter is bypassed and the link training and status state machine (LTSSM) state moves to "polling.compliance" state (when 50  $\Omega$  is terminated to the Transmitter) when REFCLK is available and TX PLL is locked. The link training remains unaffected when an active receiver is connected. This causes the optional key-sight protocol test card (PTC) test (LOOPBACK\_THROUGH\_CONFIG) to fail. To pass the test, set the PMA\_RXPLL\_FLOCK\_SEL bit to 0 when LTSSM is in "polling.compliance" state and set to 1 in other states.

## 1.1.4 Reference Clock

For PCIe applications, a differential 100 or 125 MHz reference clock with a ±300 ppm tolerance is used by the transceiver transmit PLL and CDR PLL to generate the required 125 MHz output clock (depending on the lane speed settings), which is passed to the embedded PCIESS. The settings for the transmit PLL and the CDR PLL are automatically determined by the Libero SoC software.

The transceiver reference clock inputs accept LVDS/CML/HCSL input clock signals according to PCIe specifications. Proper termination is included as required by the specification. For more information, see PolarFire FPGA and PolarFire SoC FPGA Transceiver User Guide.

According to PCIe specifications, upstream and downstream PCIe devices must transmit data at a rate within 600 ppm for each other at all times. This specification allows a reference clock with a ±300 ppm tolerance. To ensure that the minimum clock period is not violated, the PCIESS uses a spread-spectrum technique that does not permit modulation above the nominal frequency.

The data rate can be modulated from 0% to 0.5% of the nominal data rate frequency at a modulation rate ranging from 30 to 33 KHz. Along with the ±300 ppm tolerance limit, both ports require the same bit-rate clock when the data is modulated using spread-spectrum clocking (SSC).

Both the family devices support the following clocking topologies defined by the PCIe specifications: common Refclk and separate Refclk.

- The Common Refclk is the most widely supported clocking method in open systems where the root port or root complex provides a clock to the endpoint. An advantage of this clocking architecture is that it supports SSC, which reduces electromagnetic interference (EMI).

- The Separate Refclk uses two independent clock sources: one each for the root and the endpoint. The clock sources must maintain ± 300 ppm frequency accuracy and cannot use SSC.

## 1.1.5 Low-Power States

The PCIESS supports PCIe low-power operation states known as L0s and L1 states. These states are available in both, root port, and endpoint configurations.

**L0s** (Autonomous electrical idle): This state reduces power during short intervals of idle. Devices must transition to L0s independently on each direction of the link.

**L1** (Directed electrical idle): This state reduces power when the downstream port directs the upstream ports. This state saves power in two ways:

- · Shutting down the transceiver circuitry and associated PLL.

- · Significantly decreasing the number of internal core transitions.

**Note:** PCIe Link Training and Status State Machine (LTSSM) hardware blocks of PolarFire transceiver do not support the L2/P2 power management link state. The L2/P2 power management link state does not achieve further operational power-savings for the PolarFire device.

To achieve further operational power savings, on top of the already power-optimized PolarFire device architecture, the FPGA designer must employ power management techniques directly to the FPGA fabric design.

- Software-driven L2/P2 entry commands issued by the PolarFire PCIESS Root Port to the downstream endpoints are not supported to the down-stream end-points. As a Root Port, this causes the link to be completely disrupted and only recoverable by re-initializing the link with side-band PERSTn (fundamental reset) or a power cycle.

- PolarFire PCIESS endpoint must not be commanded by the host to enter L2/P2 link state. As an endpoint, the link might be disruptive and only recoverable by re-initializing the link with side-band PERSTn (fundamental reset) or a power cycle.

## 1.2 Data-link and Transaction Layers

The PCIe DL and TL includes:

- · PCIe controller

- Lane reversal

- Link training and status state machine (LTSSM)

- Electrical idle generation

- Receiver detection

- TS1/TS2 generation/detection

- PCle transmit/receive interface between the PCle bridge and PCle controller

- PCle configuration interface providing the bridge access to the PCle configuration space

- PCle miscellaneous interface to allow the bridge access to manage low-power and interrupts

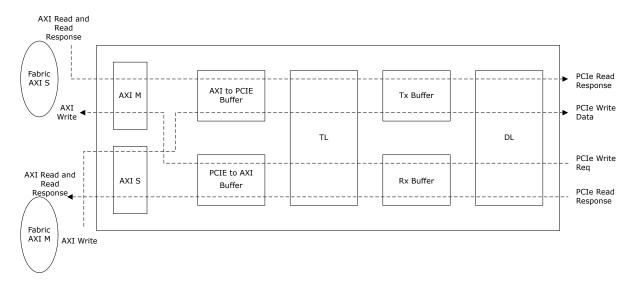

The PCIESS includes the data path from the transceiver to the user-defined application layer of the FPGA fabric. The AXI4 bridges the application layer to the transaction layer. The transaction layer communicates with the data-link layer through FIFOs. The data-link layer communicates with the physical layer through FIFOs. The data is then passed to the transaction layer blocks that manage read and write requests from the software. Finally, the data is passed to the application layer hosted in the FPGA fabric (Figure 1-7).

**Data Link Layer** – The data link layer (DL) is responsible for link management including transaction layer packet (TLP) acknowledgment (a retry mechanism in case of a non-acknowledged packet), flow control across the link (transmission and reception), power management, CRC generation and checking, error reporting, and logging. The DL verifies the packets sequence number and checks for errors. The DL ensures packet integrity, and adds a sequence number and Link Cyclic Redundancy Check (LCRC) to the packet.

The replay buffer located in the data link layer stores a copy of a transmitted TLP until the transmitted packet is acknowledged by the receive side of the link. Each stored TLP includes the header, an optional data payload (the maximum size of which is determined by the maximum payload size parameter), an optional end-to-end cyclic redundancy check (ECRC), the sequence number, and the link cyclic redundancy check (LCRC) field for transaction and data integrity. The replay buffer stores the read data payload from the AXI4 master and write data payload from the AXI4 slave.

**Transaction Layer** – The transaction layer is responsible for the transfer of transaction layer packets (TLP). The transaction layer disassembles the transaction and transfers data to the application layer in a form that it can recognize. The transaction layer generates a TLP from information sent by the application layer. This TLP includes a header and can also include a data payload. The application communicates to the PCIe link using AXI4 master and slave interface through bridge layer.

## 1.2.1 Flow Control

PCIe is a flow control-based protocol. Receivers advertise the supported number of receive buffers, and transmitters are not allowed to send TLPs without ensuring that sufficient receive buffer space is available. This control is provided by the 8 KB dedicated buffers included in the PCIESS receive and transmit channels.

**Maximum Payload Size** – The size of the TLP depends on the capabilities of both link partners. After the link is trained, the root complex sets the maximum payload size register (MAX\_PAYLOAD\_SIZE) value in the device control register. The maximum allowable payload size is 256 bytes.

## 1.2.2 Credit Queue

PCIe credit queues are categorized into posted, non-posted, and completion queues. When the host sends writes to the PCIESS, this data consumes posted and non-posted credits. When the host needs to send a completion to a read, it consumes completion credits. As is the case for most PCIe endpoints, the completion credit count is infinite in the PCIESS.

A completion timeout is a condition where the host blocks completion due to the lack of non-posted credits. When the PCIESS does a read, if completion data is not returned, the PCIESS issues a completion timeout and the transaction is voided, triggering the AXI slave to terminate the read to avoid a deadlock.

All credit settings are automatically set according to the buffer sizes fixed in the PCIESS. As per PCIe standards, when the PCIe controller issues a read request, it ensures that the controller can sync with the associated read data (completion TLP).

#### 1.2.3 Receive Buffer

The transaction layer contains an 8-KB receive buffer to accept incoming TLPs from the link and send them to the application layer for processing. The receive buffer stores TLPs based on the transaction type (posted, non-posted, or completion). A transaction always has a header but does not always have data. The receive buffer accounts for this distinction, maintaining separate resources for the headers and data for each type of transaction. For completion transactions, data (CPLD) TLPs are stored in the received buffer in the 64-bit addressing format, with each outstanding AXI4 slave read request consuming 16 credits (totaling 128 bytes), and the headers and data consuming one credit each (totaling 16 bytes).

## 1.2.4 Replay Buffer

In the transmit direction, the AXI4 bridge layer first checks the credits available on the far end before sending the TLP. There must be enough credits available for the entire TLP to be sent. The AXI4 bridge layer must then check that the PCIESS is ready to send the TLP. If there is enough credit, it can proceed with sending data. If the credit is insufficient, the TLP must wait until enough credit is available.

© 2022 Microchip Technology Inc. User Guide DS50003188B-page 8

The replay buffer is used to fetch TLPs that are:

- Issued by the AXI before their transmission on the PCIe link.

- Transmitted on the PCIe link, as long as they are not acknowledged by the opposite PCIe device, in case a replay is required.

The replay buffer is 8 KB, allowing the transmit buffer to support up to 16 outstanding transmit replay data packets with a maximum payload of 256 bytes each. A maximum of 32 TLPs can be supported by the replay buffer.

PCIe Protocol Compliance Test with LeCroy Exerciser:

Device testing for PCIe compliance with a LeCroy exerciser reports a failure for a PTC test related to Replay Buffer. However, the PTC test conducted on the Key-sight exerciser passed successfully. PolarFire FPGA met full compliance at the PCISIG Compliance Workshop #101 and entered into the integrators list. PTC Test 52-20 (LinkRetrainOnRetryFail) fails in the LeCroy testing suite. The root-cause is that the PCIe controller executes some of the second-round replays; prior to, rather than after, link re-training. It does not impact any application functionality as no transaction layer packet (TLP) is lost due to the built-in replay mechanism required by the PCle base specification. Replays occur both before and after link re-training as long as TLP is not acknowledged.

#### 1.2.5 **Extended CRC**

The PCIESS optionally performs automatic ECRC to ensure data integrity by default is disabled. The PCIE PEX SPC2 bridge configuration register controls the ECRC settings. For information about Configuration registers, see respective PolarFire Device Register Map or PolarFire SoC Register Map.

ECRC is enabled when PCIE Specific Capabilities Settings Register PCIE PEX SPC Bit[31] is set to 1 to indicate Advanced Error Reporting (AER) is enabled. ECRC error generation and checking can further be individually disabled or enabled by PCIE PEX SPC2 Bit[1] and Bit[2] register.

#### 1.2.6 **ECC**

PCIe subsystem has—AXI to PCIE, PCIE to AXI, Rx, Tx—memory buffers as shown in the following figure. These buffers support ECC capability with single bit error correction and dual bit error detection (SECDED). ECC can be disabled or enabled by configuring the ECC CONTROL register. This register also supports error injection feature.

Figure 1-2. PCle Subsystem Memory Buffers

The ECC error detection flags are captured in SEC\_ERROR\_INT and DED\_ERROR\_INT registers. These are RW registers and can be cleared by the user writing 1s.

SEC ERROR EVENT CNT and DED ERROR EVENT CNT are counter registers that record the number of SEC and DED errors encountered by AXI to PCIe, PCIe to AXI, Rx, and Tx buffers. The system register up-counts on the internal event it monitors, saturating at the largest unsigned value the counter can hold. The count value can be

**User Guide** DS50003188B-page 9 © 2022 Microchip Technology Inc.

cleared by writing all-ones pattern through the DRI. Writing through DRI takes momentary precedence over functional up-count. Writing zeros to the count register has no effect.

In addition to these, the dual bit error detection flags are exposed to fabric as listed in the following table.

Table 1-2. Error Ports

| Signal         | Direction | Description                                                                                                                                                                                                                                                               |

|----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCIE_#_M_WDERR | _         | Asserted to '1' when PCIe to AXI buffer reports dual error. The TLP is forwarded to AXI interface. Error during AXI master IF write transactions.                                                                                                                         |

| PCIE_#_S_RDERR | _         | Asserted to '1' when PCIe to AXI buffer reports dual error. The TLP is forwarded to AXI interface. Error during AXI slave IF read transactions.                                                                                                                           |

| PCIE_#_M_RDERR | _         | Reports data error if the uncorrectable error is detected in the fabric memory used by application. If this signal is asserted, the PCIe controller sets the TLP header bit EP (error forwarding field) to '1'.  Report error during AXI master IF read transactions.     |

| PCIE_#_S_WDERR | _         | Reports data error if the uncorrectable error is detected in the fabric memory used by the application. If this signal is asserted, the PCIe controller sets the TLP header bit EP (error forwarding field) to '1'.  Report error during AXI slave IF write transactions. |

Table 1-3. Summary of Dual Error in Buffers

| Dual Error in<br>Buffer | Effect at PCle IF                                                                                                                                                                                                                                             | Effect at Fabric IF                                                                                                 |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Rx buffer               | TLP is forwarded to AXI IF.                                                                                                                                                                                                                                   | Application requires to poll SEC_ERROR_EVENT_CNT or DED_ERROR_EVENT_CNT status register to find out the error.      |

| Tx buffer               | TLP is transmitted. Tx buffer memory error is ignored and cannot be recovered by PCle protocol                                                                                                                                                                | Application requires to poll SEC_ERROR_EVENT_CNT or DED_ERROR_EVENT_CNT status register to find out the error.      |

| PCIE to AXI buffer      | TLP forwarded to AXI IF.                                                                                                                                                                                                                                      | The PCIE_#_M_WDERR and PCIE_#_S_RDERR signals to fabric IF are asserted.                                            |

| AXI to PCIE buffer      | If ECRC is enabled, PCIe interface marks this TLP as erroneous and an ECRC error is generated by PCIe controller.  If ECRC is disabled, TLP is discarded.  If this AXI to PCIE buffer error is during a read transaction, it results in a completion timeout. | If this error is during a write transaction, PCIESS_AXI_#_S_BRESP [1:0] == 2'b10 is returned in AXI Write Response. |

**Note:** Rx/Tx buffer reports either SEC or DED error, when TLP is forwarded to AXI interface. The ERROR\_INT and ERROR\_EVENT\_CNT registers indicate the SEC or DED errors.

To enable ECC after PCIe enumeration, follow:

- 1. Enable ECC using ECC\_CONTROL register.

- 2. Perform greater than 16 KB writes on PCle to AXI and AXI to PCle.

- Clear the SEC\_ERROR\_EVENT\_CNT, DED\_ERROR\_EVENT\_CNT, SEC\_ERROR\_INT, and DED\_ERROR\_INT registers.

- ECC errors can be injected using the ECC CONTROL register.

#### 1.3 **Bridge Layer**

The bridge layer includes:

- Two independent DMA engines.

- An address translator to convert between the AXI and PCIe interfaces.

- A bridge interconnect module to interconnect and arbitrate between input and output flows.

#### 1.3.1 **DMA Transfers**

Each PCIe controller supports the following built-in DMA features, enabling low-power and efficient data transfer to the FPGA fabric:

- · Eight outstanding read and write requests

- Completion re-ordering support

- Flexible SGDMA modes, including dynamic DMA control per descriptor

- DMA engine that reports to the descriptor for easy software management

- Fetches up to three descriptors to optimize throughput

The PCIESS has two fully-independent DMA engines (DMA0 and DMA1), which helps to deliver higher performance on both, write and read functions. Each DMA engine can be configured to function as direct DMA or SGDMA. The DMA engines can be configured using PCIESS registers. For more information about DMA registers, see respective PolarFire Device Register Map or PolarFire SoC Register Map.

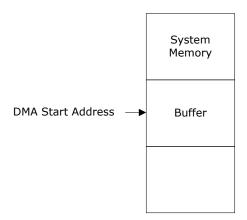

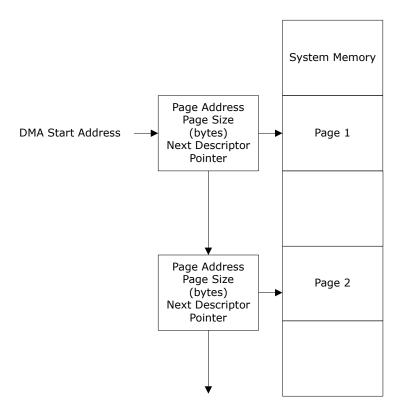

In direct DMA transfer mode, the DMA start address is a pointer to a contiguous data buffer mapped in the PCI bus address space. Data is read from and written to the buffer sequentially.

For DMA0, source is fixed to PCIe IF and destination is configurable. DMA0 is used to transfer data from:

- PCIe link (Host PC memory) to EP AXI (LSRAM/DDR in EP design).

- PCIe link (Host PC memory) to PCIe link (Host PC memory).

For DMA1, source is fixed to AXI IF and destination is fixed to PCIe IF. DMA1 is used to transfer data from EP AXI (LSRAM/DDR in EP design) to PCIe link (Host PC memory).

Figure 1-3. Direct DMA Transfer

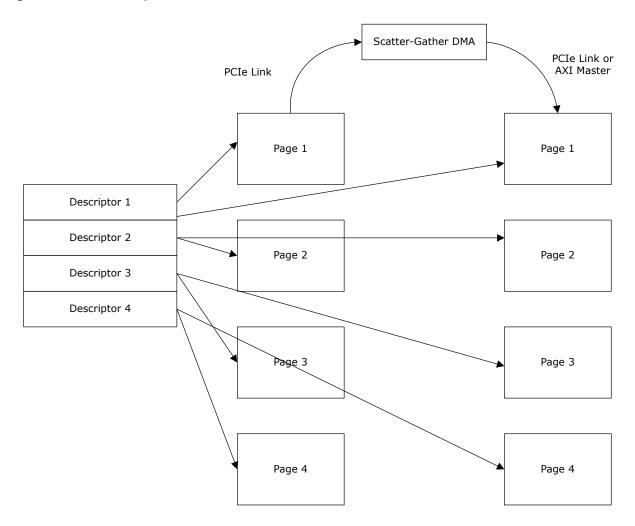

In SG transfer mode, the DMA source and/or destination start address is a pointer to a chained list of page descriptors. Each descriptor contains the address and size of a data block (page), and a pointer to the next descriptor block to enable circular buffers.

DS50003188B-page 11 **User Guide** © 2022 Microchip Technology Inc.

Figure 1-4. SGDMA Transfer

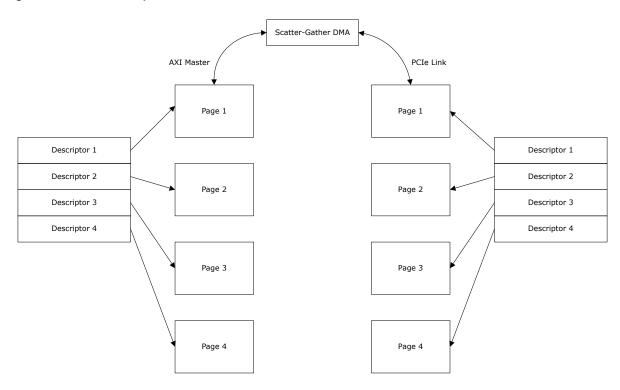

The implementation of SGDMA transfer is different in DMA0 and DMA1.

## **SGDMA Transfer in DMA0**

Source and Destination addresses are set according to the Descriptor. DMA source is always PCle link and destination can be configured as PCle link or AXI Master.

Figure 1-5. DMA0 Descriptor

**Note:** For DMA0, addresses and length must be multiples of 4 bytes. Source and destination start addresses must be 32 byte aligned. For example, if the start address is 0xXX14 and the destination address can be 0xXX14, 0xXX34, 0xXX54 and so on.

## **SGDMA Transfer in DMA1**

Source and destination addresses are set by two independent Scatter-Gather descriptors all DMA destination is always PCIe and source is AXI IF.

Figure 1-6. DMA1 Descriptor

**Note:** For DMA1, addresses and length must be multiple of 32 bytes. Source and destination start addresses must be 32 byte aligned.

## 1.3.2 Scatter-Gather DMA Descriptors

The following table lists the Scatter-Gather DMA Descriptors.

**Table 1-4. Scatter-Gather DMA Descriptors**

| Name        | Byte Offset | R/W | Description                                                                                                                                                                                                                                                                                                                         |

|-------------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DESC_STATUS | 0x00 - 0x03 | RW  | Enables dynamic monitoring of the SGDMA transfer (when 0 <sup>th</sup> bit of DESC_CONTROL register is set) Bits [3:0]: Provides the status number of the DMA engine. This number is incremented, enabling the application to determine the last processed descriptor, which is key in streaming flow between asynchronous devices. |

|             |             |     | Bits [7:4]:                                                                                                                                                                                                                                                                                                                         |

|             |             |     | Bit 4: Indicates SG-DMA descriptor has been processed.                                                                                                                                                                                                                                                                              |

|             |             |     | Bit 5: Indicates an error occurred during the processing of the current SGDMA descriptor.                                                                                                                                                                                                                                           |

|             |             |     | Bit 6: Indicates an End of Packet (EOP) condition has been reported by the source of the SGDMA transfer.                                                                                                                                                                                                                            |

|             |             |     | Bit 7: Reserved                                                                                                                                                                                                                                                                                                                     |

|             |             |     | Bits [31:8]: Indicates the Processed Page Size, which is the actual written or read page size.                                                                                                                                                                                                                                      |

| continued             |             |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------|-------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                  | Byte Offset | R/W                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DESC_CONTROL          | 0x04 - 0x07 | RO                                        | DESC_CONTROL enables dynamic control of the SGDMA transfer. Bit [0]: Defines whether the DMA engine provides a status report by writing to DESC_STATUS when the current SGDMA descriptor has been processed. Bits [3:1]: Reserved Bits [7:4]: Defines when an interrupt must be issued. Bit 4: Indicates an IRQ is issued when this SGDMA descriptor has been processed. Bit 5: Indicates an IRQ is issued if an error occurs. Bit 6: Indicates an IRQ is issued if the source of the transfer reports an EOP condition. Bit 7: Reserved Bits [31:8]: Provides the page size in bytes, from 1 to 16 M bytes. |

| DESC_NEXT_ADDR[63:32] | 0x0C - 0x0F | RO                                        | Indicates next descriptor address. This field must be aligned on a 32-byte boundary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DESC_NEXT_ADDR[31:5]  | 0x08 - 0x0B | RO                                        | Indicates next descriptor address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DESC_NEXT_RDY[4]      |             | Indicates if the next SGDMA Desc<br>able. | Indicates if the next SGDMA Descriptor is ready and fetchable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DESC_SE_COND[3:0]     |             |                                           | Defines the Start and End conditions for SGDMA descriptor processing. Bit 0: Indicates end the DMA transfer after this SGDMA descriptor has been processed (equivalent to an End Of Chain). Bit 1: Indicates to abort this SGDMA descriptor processing if an error occurs.                                                                                                                                                                                                                                                                                                                                   |

|                       |             |                                           | Bit 2: Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       |             |                                           | Bit 3: Indicates to start this SGDMA descriptor processing when the source of the transfer reports a SOP reception.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DESC_SRC_ADDR[31:0]   | 0x10 - 0x13 | RO                                        | Indicates the source address of the descriptors. It must be 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DESC_SRC_ADDR[63:32]  | 0x14 - 0x17 | RO                                        | byte aligned.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DESC_DEST_ADDR[31:0]  | 0x18 - 0x1B | RO                                        | Indicates the destination address of the descriptors. It must                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DESC_DEST_ADDR[63:32] | 0x1C - 0x1F | RO                                        | be<br>32 byte aligned.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## 1.3.3 PCIe/AXI4 Address Translation

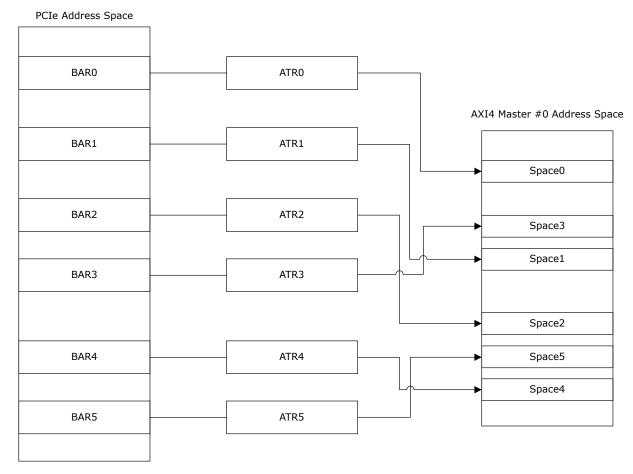

There are six address table registers (ATRs) that perform address translation from the PCIe address space (BAR) to the AXI master, and six ATRs for the slave, which addresses translation from the AXI4 slave to the PCIe address space.

For the address translation, PCIESS uses the following:

- · Master Windows

- Slave Windows

© 2022 Microchip Technology Inc. User Guide DS50003188B-page 15

## 1.3.3.1 Master Windows

Master windows translate the addresses from PCIE domain to AXI 4 domain.

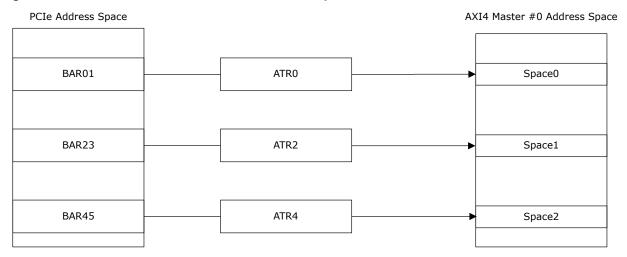

When the PCIESS is in endpoint mode, there is direct mapping between the BAR and the address tables, as shown in the following figures.

Each 32-bit BAR has an address translation table (ATR). The PCIe implementation supports up to six 32-bit base address registers (BARs). Each BAR is 32 bits, but two BARs can be combined to make a 64-bit BAR. For example, BAR0 (address offset 010h) and BAR1 (address offset 014h) can be combined to form a 64-bit BAR01.

For a 64-bit BAR mapping, address tables are used as follows:

- · BAR01 targets ATR0, and ATR1 remains unused

- · BAR23 targets ATR2, and ATR3 remains unused

- BAR45 targets ATR4, and ATR5 remains unused

Figure 1-7. PCIe to AXI4 Master Address Translation Endpoint Mode for 32-Bit BAR

Figure 1-8. PCle to AXI4 Master Address Translation Endpoint Mode for 64-Bit BAR

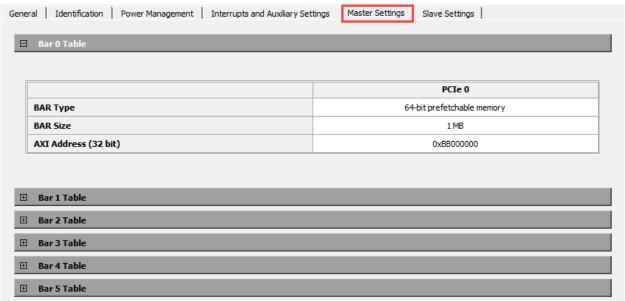

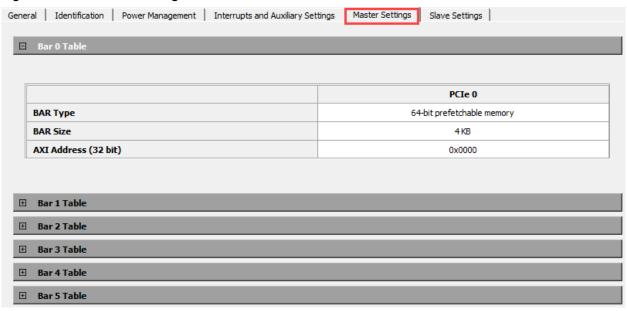

The PCIESS Configurator in Libero SoC software provides a GUI to configure the BAR settings for an endpoint application.

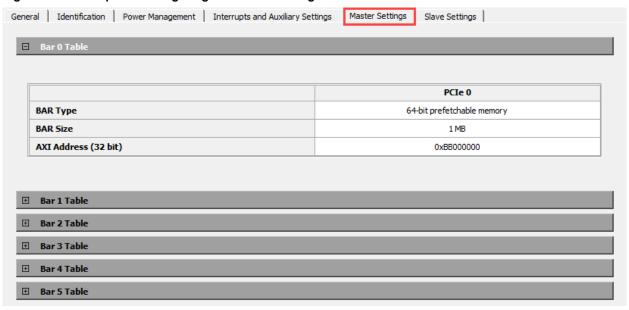

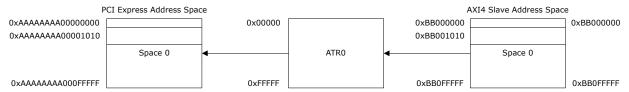

The following figure shows an example of configuring Master settings to map the BAR0 transactions to PCIe AXI master IF transactions for AXI address 0xBB000000.

Figure 1-9. Example of Configuring Master EP Settings

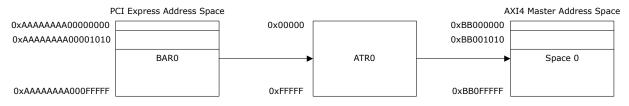

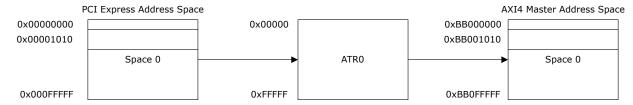

If BAR0 receives write/read request with offset 1010, then ATR0 translates this address to 0xBB001010.

Figure 1-10. PCIe to AXI4 Master Address Translation Endpoint Mode Example

Note: In this example, BAR0 address of host is shown as 0xAAAAAAAAAA00000000.

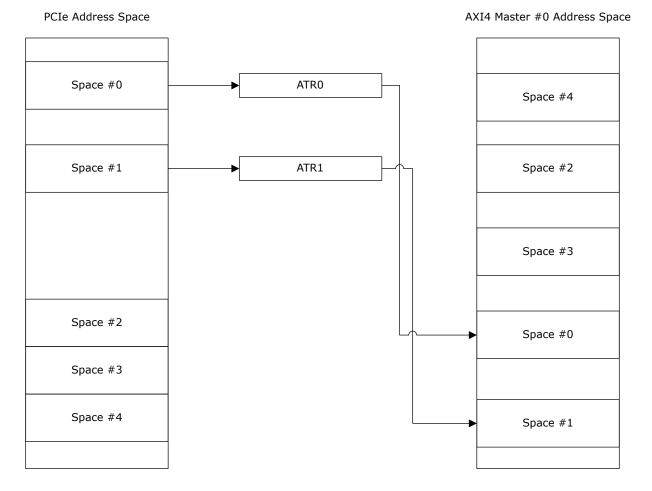

When the PCIESS is in root port mode (Figure 1-11), up to six translation tables (currently, Libero SoC supports two translation tables) can be implemented. When transferring PCI Express receive requests to the AXI master, the bridge performs a windows match using the PCIe 64-bit address. If a match is found, the bridge forwards the request to the desired AXI4 master interface and adds the corresponding AXI base address.

When the PCI Express BAR0/1 are configured as a 64-bit prefetchable memory space of 16 Kbytes, PCIe read and write requests targeting BAR0 or BAR1 are routed to the bridge configuration space. This memory space operates in the following two ways:

- When I/O or prefetchable memory windows are implemented, PCIe read and write requests targeting I/O or prefetchable memory windows are routed to the PCIe window address translation module.

- When I/O or prefetchable memory windows are not implemented, PCIe read and write requests that do not target BAR0 or BAR1 are routed to the PCIe window address translation module.

Figure 1-11. PCle to AXI4 Master Address Translation Root Port Mode

The following figure shows an example of configuring Master settings to map the PCIe RP address space to PCIe AXI master IF address space for AXI address 0xBB000000.

Figure 1-12. Example of Configuring Master RP Settings

When PCIe receives write/read request at address 0x00001010, this address is mapped to ATR0, which removes the upper 44 bits (depending on table size) and adds the translation address 0xBB000000 to offset 0x1010.

Figure 1-13. PCIe to AXI4 Master Address Translation Root Port Mode Example

## 1.3.3.2 Slave Windows

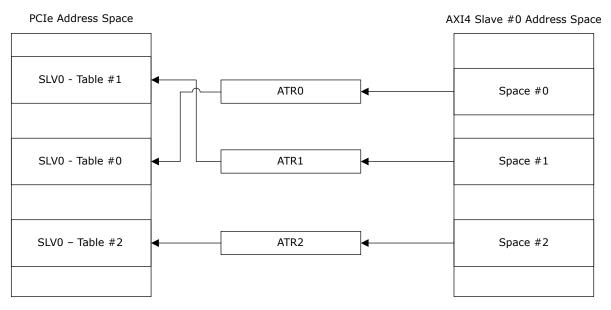

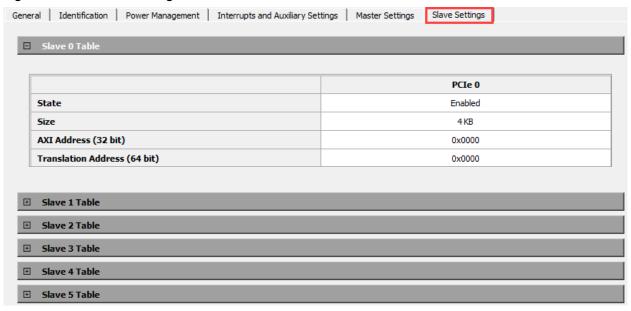

The address translation method used to transfer AXI slave receive requests to the PCIe interface is similar to the method used in the endpoint mode. Up to six translation tables can be implemented for AXI4 slave interface.

Figure 1-14. AXI4 Slave to PCle Address Translation

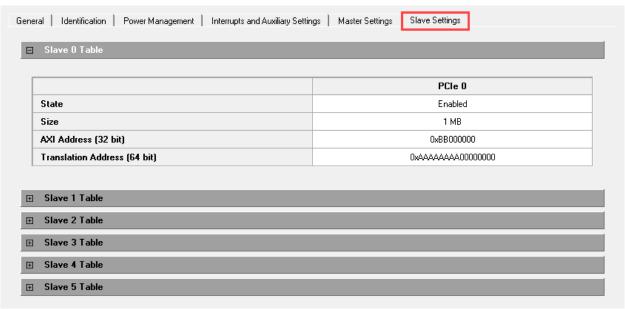

The following figure shows an example of configuring Slave settings to map AXI IF slave requests to PCIE requests for AXI address 0xBB000000 and PCIe address 0xAAAAAAA00000000.

Figure 1-15. Example of Slave EP Settings

When PCIe receives write/read request at address 0xBB001010, this address is mapped to Table0, which removes the upper 12 bits (depending on table size) and adds the translation address 0xAAAAAAAA0000000 to offset 0x1010.

Figure 1-16. AXI4 Slave to PCIe Address Translation Example

## 1.4 AXI4 Layer

The AXI4 layer of the PCIESS provides a transaction-level translation of AXI4 commands to PCIe packets and PCIe requests to AXI4 commands. The user application in the FPGA fabric must implement an AXI4 master interface to transfer data to the PCIe link and an AXI4 slave interface to receive data from the PCIe link.

## 1.4.1 AXI MasterIF

A typical PCIe application interface uses an AXI master interface to respond to data read requests and an AXI slave interface to initiate requests. The AXI master performs the following functions:

- · Conveys PCIe read and write transactions to the fabric in the form of AXI4 reads and writes.

- Accesses the DMA controller through the bridge and issues reads and writes that allow data pulled from the fabric to be sent over PCIe and data pulled from the PCIe to be written out to the fabric.

#### 1.4.1.1 AXI Master Write Transactions

Write transactions are handled in big-endian order as required by the PCI Express Base Specification. The master path does not reorder transactions, but arbitrates between transactions at the AXI4 master interface. If a transaction is currently waiting for a response phase, the transaction is allowed to complete before the read transaction is forwarded to the AXI4 master interface. PCIe transactions sizes may vary up to the configurable maximum payload size (256 bytes):

- AXI4 transactions are limited to 256 bytes, and the received TLP is divided into several AXI4 transactions.

- AXI4 master receives a write transaction, processing it in 256-byte segments.

- TLP is de-constructed from the PCle system and sent to the AXI4 interface in little-endian format.

## 1.4.1.2 AXI Master Read Transactions

Read transactions are handled similar to write transactions, except that before transferring the transaction to the AXI4 master read channel, the PCIESS checks the transmit buffer for available space. If the transmit replay buffer does not have sufficient place to store the PCIe completions, the PCIESS does not transfer the read transaction. Hence, the number of outstanding AXI4 master read transactions is limited by the size of the transmit buffer.

The AXI4 master read channel can receive transactions in any order, and data can be completely interleaved. However, the PCIESS generates completions in the order they are initiated on the link.

## 1.4.2 AXI SlavelF

The AXI4 slave interface forwards AXI read and write requests from the FPGA fabric to the PCIe link. The fabric application initiates PCIe transactions (memory write TLP and memory read TLP transactions) using the slave interface. The data on a read request comes back to the same interface. The slave path does not reorder transactions, but arbitrates between transactions if they occur simultaneously with master read completions. The order of priority for arbitrations is as follows:

- 1. Master read completions

- 2. Slave write requests

- 3. Slave read requests

## 1.4.2.1 AXI Slave Write Transactions

Slave write transactions support incrementing address bursts, fixed bursts, wrapping bursts, and narrow type transfers. Data interleaving, however, is not supported. Data packets of a maximum of 2 K bytes can be created. Wait states are used if the buffer is full, or has less than 128 bytes of available space. Write responses are generated as soon as the last phase is over with support for up to four outstanding write transactions.

© 2022 Microchip Technology Inc. User Guide DS50003188B-page 21

## 1.4.2.2 AXI Slave Read Transactions

PCIESS generates a PCIe tag, arbitrates between write requests and completions, and then checks for available credits. An error response is generated if a timeout occurs or if a "completion with error" status is received.

## 1.4.3 AXI4 Limitations

Unsupported AXI4 features in the PCIESS are:

- 8, 16, and 32 bits data bus widths.

- · User-defined signals.

- · Low-power interface.

- · Exclusive accesses are not supported.

## 1.4.4 Conversion Between PCle and AXI Transactions

The PCIESS converts AXI read and write transaction as described in the following sections:

## 1.4.4.1 Conversion from PCIe Write to AXI Write Transactions

A single PCIe write transaction is converted into multiple AXI write transactions at the fabric interface whenever the AXI write address space crosses the negotiated maximum payload size boundary. For example, the negotiated maximum payload size is 256 Bytes, then the address boundaries are 0x000, 0x100, 0x200, 0x300, ..., 0xE00, 0xF00. In this case, a PCIe write transaction writes a TLP with payload of 24 Double-Words, that is, 24 × 4 = 96 Bytes. The write transaction targets the contiguous AXI write addresses starting from 0x0005AAF0. With a payload size of 96 Bytes, the ending write address is 0x0005AAF0 + 0x50 = 0x0005AB50, which crosses the 256 Byte boundary. The bridge breaks it into two AXI write transactions—AXI write transaction starting at 0x0005AAF0 with 16 Bytes and AXI write transaction starting at 0x0005AB00 with the remaining 80 Bytes.

## 1.4.4.2 Conversion from PCIe Read to AXI Read Transactions

A single PCIe read transaction is converted into multiple AXI read transactions when the bridge complies with the following two constraints:

When the PCIe read transaction targets AXI address space that crosses the negotiated maximum payload boundary, the fabric logic may still return with one single AXI burst transaction. In this case, the PCIe bridge breaks it into multiple separate PCIe read completions with AXI read data broken at the negotiated maximum payload boundary in AXI address space.

Read requests, which cross the address boundaries at integer multiples of RCB bytes may be completed using more than one completion, but the data must not be fragmented except along the following:

- The first completion starts with the address specified in the request, and ends at one of the following:

- The address specified in the request plus the length specified by the request, that is, the entire request.

- An address boundary between the start and end of the request at an integer multiple of RCB bytes.

- · The final completion ends with the address specified in the request plus the length specified by the request.

- All completions between, but no including, the first and final completions will be an integer multiple of RCB bytes in length.

**Note:** For a root complex, RCB can be configured to 64 Bytes or 128 Bytes using PCIE\_PEX\_SPC[15] register bit. For an Endpoint, RCB is always 128 bytes.

The following are the examples of AXI split transactions:

- Assume the negotiated maximum payload size is 256 Bytes. Memory read request with address of 0x10000 and length of 192 bytes can be completed by a root complex with a RCB value of 64 Bytes with one of the following combination of completions (bytes):

- 192

- 128, 64

- 64, 128

- 64, 64, 64

- Assume the negotiated maximum payload size is 256 Bytes. Memory read request with address of 0x10200h and length of 256 bytes can be completed by an Endpoint in one of the following combination of completions (bytes):

- 256

- 96, 160

- 96, 128, 32

- 224, 32

## 1.5 PCIESS Configuration Interface

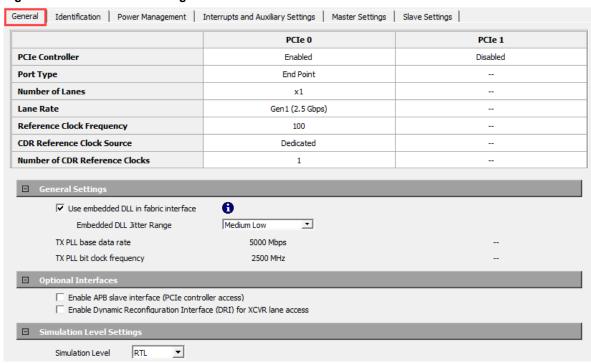

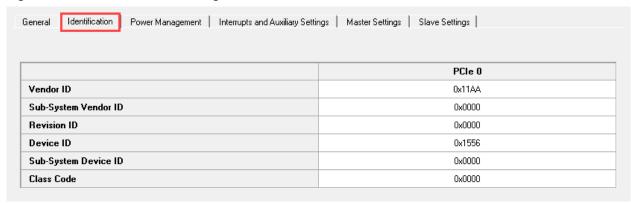

**Programmable FPGA Resources**: The registers required for the initial configuration of the PCIESS are loaded based on the options selected in the Libero PCIESS Configurator wizard. On device power-up, these values are automatically loaded into the configuration registers from the on-chip non-volatile memory during the design initialization process. The design initialization uses the dedicated resources to bring up the PCIESS features at power-up or device reset. This does not require any programmable FPGA user resources. The PCIESS then reads and writes the configuration space registers as the link comes up and the endpoint device is enumerated into the host system.

PCIESS can be dynamically configured through the following interfaces:

- DRI is used to configure transceiver lane registers.

- APB is used to configure PCle control registers.

## 1.6 PCIESS Port List

The PCIESS block is generated using the Libero PCIe Configurator. The generation of the PCIESS block includes ports based on the PCIe Configurator settings. The following table lists the port descriptions. The PCIESS also has several status signals, interrupt signals, and power management signals available to the FPGA fabric.

Table 1-5. PCIESS Port List<sup>1, 2</sup>

| Port Name                   | Direction | Description                                                                                                                              |

|-----------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| AXI_CLK                     | Input     | Global AXI clock. Shared for both PCIESS interfaces.                                                                                     |

| AXI_CLK_STABLE              | Input     | Clock lock signal. Indicates that the AXI_CLK source from the fabric is locked and ready for use.                                        |

| Master                      |           |                                                                                                                                          |

| PCIESS_AXI_#_M_ARADDR[31:0] | Output    | Read address. The address of the first transfer in a read burst transaction.                                                             |

| PCIESS_AXI_#_M_ARBURST[1:0] | Output    | Read burst type. The burst type and the size details determine how the address for each transfer within the burst is calculated.         |

| PCIESS_AXI_#_M_ARID[3:0]    | Output    | Read address ID. Identification tag for the read address group of signals.                                                               |

| PCIESS_AXI_#_M_ARLEN[7:0]   | Output    | Burst length. Indicates the exact number of transfers in a burst.                                                                        |

| PCIESS_AXI_#_M_ARREADY      | Input     | Read address ready. Indicates that the slave is ready to accept an address and associated control signals.                               |

| PCIESS_AXI_#_M_ARSIZE[1:0]  | Output    | Burst size. Indicates the size of each transfer in the burst.                                                                            |

| PCIESS_AXI_#_M_ARVALID      | Output    | Read address valid. Indicates that the channel is signaling valid read address and control information.                                  |

| PCIESS_AXI_#_M_AWADDR[31:0] | Output    | Write address. The address of the first transfer in a write burst transaction.                                                           |

| PCIESS_AXI_#_M_AWBURST[1:0] | Output    | Write burst type. The burst type and the size of information determine how the address for each transfer within the burst is calculated. |

| continued                   |           |                                                                                                                                                                                                                                                                                          |  |

|-----------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Port Name                   | Direction | Description                                                                                                                                                                                                                                                                              |  |

| PCIESS_AXI_#_M_AWID[3:0]    | Output    | Write address ID. Identification tag for the write address group of signals.                                                                                                                                                                                                             |  |

| PCIESS_AXI_#_M_AWLEN[7:0]   | Output    | Burst length. Indicates the exact number of transfers in a burst, which determines the number of data transfers associated with the address.                                                                                                                                             |  |

| PCIESS_AXI_#_M_AWREADY      | Input     | Write address ready. Indicates that the slave is ready to accept an address and associated control signals.                                                                                                                                                                              |  |

| PCIESS_AXI_#_M_AWSIZE       | Output    | Burst size. Indicates the size of each transfer in the burst.                                                                                                                                                                                                                            |  |

| PCIESS_AXI_#_M_AWVALID      | Output    | Write address valid. Indicates that the channel is signaling valid write address and control information.                                                                                                                                                                                |  |

| PCIESS_AXI_#_M_BID[3:0]     | Input     | Response ID tag. Identification tag for the write response.                                                                                                                                                                                                                              |  |

| PCIESS_AXI_#_M_BREADY       | Output    | Response ready. Indicates that the master is ready to accept a write response.                                                                                                                                                                                                           |  |

| PCIESS_AXI_#_M_BRESP[1:0]   | Input     | Write response. Indicates the status of the write transaction. when it is asserted to 2'b10 (SLVERR/DECERR), unsupported request to PCIe is reported.                                                                                                                                    |  |

| PCIESS_AXI_#_M_BVALID       | Input     | Write response valid. Indicates that the channel is signaling a valid write response.                                                                                                                                                                                                    |  |

| PCIESS_AXI_#_M_RDATA[63:0]  | Input     | Read data.                                                                                                                                                                                                                                                                               |  |

| PCIESS_AXI_#_M_RID[3:0]     | Input     | Read ID tag. Identification tag for the read data group of signals generated by the slave.                                                                                                                                                                                               |  |

| PCIESS_AXI_#_M_RLAST        | Input     | Read last. Indicates the last transfer in a read burst.                                                                                                                                                                                                                                  |  |

| PCIESS_AXI_#_M_RREADY       | Output    | Read ready. Indicates that the master can accept the read data and associated control signals, along with response information.                                                                                                                                                          |  |

| PCIESS_AXI_#_M_RRESP[1:0]   | Input     | <ul> <li>Read response. Indicates the status of the read transfer.</li> <li>When it is asserted to 2'b10(SLVERR), completion with unsupported request status is returned.</li> <li>When it is asserted to 2'b11(DECERR), completion with Completion Abort status is returned.</li> </ul> |  |

| PCIESS_AXI_#_M_RVALID       | Input     | Read valid. Indicates that the channel is signaling the required read data.                                                                                                                                                                                                              |  |

| PCIESS_AXI_#_M_WDATA[63:0]  | Output    | Write data.                                                                                                                                                                                                                                                                              |  |

| PCIESS_AXI_#_M_WLAST        | Output    | Write last. Indicates the last transfer in a write burst.                                                                                                                                                                                                                                |  |

| PCIESS_AXI_#_M_WREADY       | Input     | Write ready. Indicates that the slave can accept the write data.                                                                                                                                                                                                                         |  |

| PCIESS_AXI_#_M_WSTRB[7:0]   | Output    | Write strobes. Indicates the byte lanes that hold valid data. There is one write strobe bit for every eight bits of the write data bus.                                                                                                                                                  |  |

| PCIESS_AXI_#_M_WVALID       | Output    | Write valid. Indicates that valid write data and strobes are available.                                                                                                                                                                                                                  |  |

| Slave                       |           |                                                                                                                                                                                                                                                                                          |  |

| PCIESS_AXI_#_S_ARADDR[31:0] | Input     | Read address. The address of the first transfer in a read burst transaction.                                                                                                                                                                                                             |  |

| continued                   |           |                                                                                                                                                                                                                                                                                                                                                                             |  |

|-----------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Port Name                   | Direction | Description                                                                                                                                                                                                                                                                                                                                                                 |  |

| PCIESS_AXI_#_S_ARBURST[1:0] | Input     | Burst type. The burst type and the size of information determine how the address for each transfer within the burst is calculated.                                                                                                                                                                                                                                          |  |

| PCIESS_AXI_#_S_ARID[3:0]    | Input     | Read address ID. Identification tag for the read address group of signals.                                                                                                                                                                                                                                                                                                  |  |

| PCIESS_AXI_#_S_ARLEN[7:0]   | Input     | Burst length. Indicates the exact number of transfers in a burst.                                                                                                                                                                                                                                                                                                           |  |

| PCIESS_AXI_#_S_ARREADY      | Output    | Write address ready. Indicates that the slave is ready to accept an address and the associated control signals.                                                                                                                                                                                                                                                             |  |

| PCIESS_AXI_#_S_ARSIZE[1:0]  | Input     | Burst size. Indicates the size of each transfer in the burst.                                                                                                                                                                                                                                                                                                               |  |

| PCIESS_AXI_#_S_ARVALID      | Input     | Read address valid. Indicates that the channel is signaling valid read address and control information.                                                                                                                                                                                                                                                                     |  |

| PCIESS_AXI_#_S_AWADDR[31:0] | Input     | Write address. Address of the first transfer in a write burst transaction.                                                                                                                                                                                                                                                                                                  |  |

| PCIESS_AXI_#_S_AWBURST[1:0] | Input     | Burst type. The burst type and the size information determine how the address for each transfer within the burst is calculated.                                                                                                                                                                                                                                             |  |

| PCIESS_AXI_#_S_AWID[3:0]    | Input     | Write address ID. Identification tag for the write address group of signals.                                                                                                                                                                                                                                                                                                |  |

| PCIESS_AXI_#_S_AWLEN[7:0]   | Input     | Burst length. Indicates the exact number of transfers in a burst, which determines the number of data transfers associated with the address.                                                                                                                                                                                                                                |  |

| PCIESS_AXI_#_S_AWREADY      | Output    | Write address ready. Indicates that the slave is ready to accept an address and associated control signals.                                                                                                                                                                                                                                                                 |  |

| PCIESS_AXI_#_S_AWSIZE[1:0]  | Input     | Burst size. Indicates the size of each transfer in the burst.                                                                                                                                                                                                                                                                                                               |  |

| PCIESS_AXI_#_S_AWVALID      | Input     | Write address valid. Indicates that the channel is signaling valid write address and control information.                                                                                                                                                                                                                                                                   |  |

| PCIESS_AXI_#_S_BID[3:0]     | Output    | Response ID tag. Identification tag for the write response.                                                                                                                                                                                                                                                                                                                 |  |

| PCIESS_AXI_#_S_BREADY       | Input     | Response ready. Indicates that the master can accept a write response.                                                                                                                                                                                                                                                                                                      |  |

| PCIESS_AXI_#_S_BRESP[1:0]   | Output    | Write response. Indicates the status of the write transaction. It is asserted to 2'b10(SLVERR), when:                                                                                                                                                                                                                                                                       |  |

|                             |           | <ul> <li>an AXI Write Completion Timeout (128 ms in hardware and 128 µs in simulation) cannot be transferred to the PCle link due to an AXI write transaction, because the link is down or in low-power mode.</li> <li>ECRC error occurs in TLP/Poisoned TLP It is asserted to 2'b11(DECERR) when no address translation table is matched (Unsupported Address).</li> </ul> |  |

| PCIESS_AXI_#_S_BVALID       | Output    | Write response valid. Indicates that the channel is signaling a valid write response.                                                                                                                                                                                                                                                                                       |  |

| PCIESS_AXI_#_S_RDATA[63:0]  | Output    | Read data.                                                                                                                                                                                                                                                                                                                                                                  |  |

| PCIESS_AXI_#_S_RID[3:0]     | Output    | Read ID tag. Identification tag for the read data group of signals generated by the slave.                                                                                                                                                                                                                                                                                  |  |

| PCIESS_AXI_#_S_RLAST        | Output    | Read last. Indicates the last transfer in a read burst.                                                                                                                                                                                                                                                                                                                     |  |

| continued                  |           |                                                                                                                                                                                                                                           |  |

|----------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|