# UG0771 User Guide Microsemi FPGA Functional Safety

Power Matters."

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

© 2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

# Contents

| 1 | Revisi<br>1.1 |                                                                                          | tory                                                                                                                                                                                                         |                                 |

|---|---------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 2 | Introd        | uction                                                                                   |                                                                                                                                                                                                              | 2                               |

| 3 | Overv         | iew of                                                                                   | Functional Safety and IEC 61508                                                                                                                                                                              | 4                               |

| 4 |               | del Dev<br>Step 1–<br>4.1.1<br>4.1.2                                                     | Libero SOC v11.5 SP2 in<br>velopment 5<br>-FPGA Requirement Specification<br>Microsemi References<br>Verifying Step Was Completed Correctly                                                                  | 7<br>7                          |

|   | 4.2           | 4.1.3<br>4.1.4<br>Step 2–<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                            | Tools         Specific Techniques and Measures         -FPGA Architecture         Microsemi References         Verifying Step Was Completed Correctly         Tools         Specific Techniques and Measures | 7<br>7<br>8<br>8<br>8           |

|   | 4.3           | Step 3–<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                              | -Test Plan<br>Microsemi References<br>Verifying Step Was Completed Correctly<br>Tools<br>Specific Techniques and Measures                                                                                    | 8<br>8<br>8<br>9                |

|   | 4.4           | Step 4–<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6<br>4.4.7<br>4.4.8<br>4.4.9 |                                                                                                                                                                                                              | 9<br>9<br>1<br>1<br>2<br>3<br>3 |

|   | 4.5           |                                                                                          | -Synthesis                                                                                                                                                                                                   | 4<br>5<br>5<br>5                |

|   | 4.6           | 4.6.1<br>4.6.2<br>4.6.3<br>4.6.4                                                         | -Place and Route       1         Microsemi References       1         Verifying Step Was Completed Correctly       1         Tools       1         Specific Techniques and Measures       1                  | 5<br>5<br>6<br>6                |

|   | 4.7           | Step 8–<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.4                                              | -Static Timing Analysis       1         Microsemi References       1         Verifying Step Was Completed Correctly       1         Tools       1         Specific Techniques and Measures       1           | 6<br>6<br>6                     |

|   | 4.8           |                                                                                          | –Gate-level Simulation (Timed)                                                                                                                                                                               | 7                               |

|   |                                                   | 4.8.2<br>4.8.3<br>4.8.4                                          | Verifying Step Was Completed Correctly<br>Tools<br>Specific Techniques and Measures                                   | 17                                     |

|---|---------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|   | 4.9                                               | Step 10-<br>4.9.1<br>4.9.2<br>4.9.3                              | Bitstream Generation                                                                                                  | 18<br>18<br>18                         |

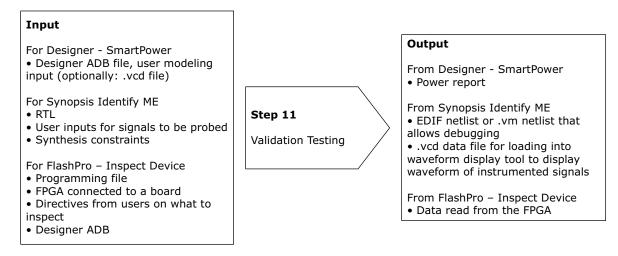

|   | 4.10                                              | Step 11-<br>4.10.1<br>4.10.2<br>4.10.3<br>4.10.4                 | Validation Testing Microsemi References Verifying Step Was Completed Correctly Tools Specific Techniques and Measures | 19<br>19<br>20                         |

| 5 | Specif                                            | ic Rest                                                          | rictions of Use                                                                                                       | 21                                     |

| 6 | Techn                                             | iques a<br>6.0.1                                                 | and Measures (IEC 61508-2, Table F2)                                                                                  |                                        |

| 7 | Availa                                            | ble IP (                                                         | Cores                                                                                                                 | 26                                     |

| 8 | Failure<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6 | Microser<br>Convers<br>FIT Form<br>Failure F<br>8.4.1<br>Adjustm | Single Event Upset (SEU) Data                                                                                         | 27<br>27<br>27<br>27<br>27<br>27<br>28 |

| 9 | Apper                                             | ndix: Sa                                                         | Ifety Compliance Checklists                                                                                           | 29                                     |

# **Figures**

| Figure 1  | V-Model Development Using Libero SoC                           | 5  |

|-----------|----------------------------------------------------------------|----|

| Figure 2  | V-Model Development Step 1—FPGA Requirement Specification      |    |

| Figure 3  | V-Model Development Step 2—FPGA Architecture                   |    |

| Figure 4  | V-Model Development Step 3—Test Planning                       |    |

| Figure 5  | V-Model Development Step 4a—Logical Module Design: Design      | 9  |

| Figure 6  | V-Model Development Step 4b—Logical Module Design: Test Plan   | 10 |

| Figure 7  | V-Model Development Step 4c—Logical Module Design: Coding      | 11 |

| Figure 8  | V-Model Development Step 4d—Logical Module Design: Test        | 12 |

| Figure 9  | V-Model Development Step 5c—Logical Module Integration: Coding | 13 |

| Figure 10 | V-Model Development Step 5d—Logical Module Integration: Test   | 14 |

| Figure 11 | V-Model Development Step 6—Synthesis                           | 14 |

| Figure 12 | V-Model Development Step 7—Place and Route                     | 15 |

| Figure 13 | V-Model Development Step 8—Static Timing Analysis              | 16 |

| Figure 14 | V-Model Development Step 9—Gate-Level Simulation (Timed)       | 17 |

| Figure 15 | V-Model Development Step 10—Bitstream Generation               | 18 |

| Figure 16 | V-Model Development Step 11—Validation Testing                 | 19 |

# **Tables**

| Table 1 | Libero SOC v11.5 SP2 Tools                                                                   |

|---------|----------------------------------------------------------------------------------------------|

| Table 2 | Techniques and Measures to Prevent Introduction of Faults during FPGA Design and Development |

|         | (IEC 61508–2, Table F2) 22                                                                   |

| Table 3 | IEC 61508-Qualified Microsemi IP Cores                                                       |

| Table 4 | Document Checklist for Using Libero SoC v11.5 SP2 in V-Model Development                     |

| Table 5 | Libero SoC v11.5 SP2 V-Model Activities Checklist                                            |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

# 1.1 Revision 1.0

Revision 1.0 is the first publication of this document.

# 2 Introduction

Microsemi is committed to providing customers with FPGAs that can be successfully used in critical safety designs. New technology brings new ways for a system containing electronics or programmable electronics to fail. Failures can cause harm to people and property. Even though it is impossible to guarantee a technological system will never fail, it is possible to reduce the risk of failure and to design systems so that if they do fail, they fail safely. To that end, functional safety standards were created, and continue to evolve.

International Electrotechnical Commission (IEC) 61508 Functional Safety of Electrical /Electronic/Programmable Electronic (E/E/PE) Safety-related Systems is a standard created for industrial applications and is intended to be the basis for functional safety in all industries. Microsemi is working with TUV-Rheinland in Cologne, Germany to ensure that the Microsemi SoC FPGA development environment is compliant with IEC 61508.

This document explains how to use Libero<sup>®</sup> SoC v11.5 SP2 to develop Microsemi's third-generation FPGAs (IGLOO<sup>®</sup> nano, IGLOO PLUS, ProASIC<sup>®</sup>3/e, ProASIC3L, and SmartFusion<sup>®</sup> FPGAs) in compliance with IEC 61508:2010 up to safety integrity level (SIL) 3. Specifically, Libero SoC v11.5 SP2 is qualified for use with the following devices:

- IGLOO AGL030V2

- IGLOO\_AGL030V5

- IGLOO\_AGL060V5

- IGLOO AGL125V5

- IGLOO AGL250V2

- IGLOO\_AGL250V5

- IGLOO\_AGL1000V5

- IGLOO\_AGLN010V2

- IGLOO\_AGLN010V5

- IGLOO\_AGLN020V2

- IGLOO\_AGLN020V5

- IGLOO\_AGLN060V2

- IGLOO\_AGLN060V5

- IGLOO\_AGLN125V2

- IGLOO\_AGLP006V5

- IGLOO\_AGLP125V5

- ProASIC3\_A3P030

- ProASIC3\_A3P060

- ProASIC3\_A3P1000

- ProASIC3\_A3P125

- ProASIC3\_A3P250

- ProASIC3\_A3P400

- ProASIC3 A3P600

- ProASIC3 A3P600L

- ProASIC3 A3PE1500

- ProASIC3 A3PE3000

- ProASIC3 A3PE600

- ProASIC3 A3PN010

- ProASIC3 A3PN015

- ProASIC3 A3PN020

- ProASIC3 A3PN030Z

- ProASIC3 A3PN060

- ProASIC3 A3PN060Z

- ProASIC3 A3PN125

- ProASIC3\_A3PN125Z

- ProASIC3\_A3PN250

- ProASIC3\_A3PN250Z

- SmartFusion\_A2F200M3E

- SmartFusion\_A2F500M3G

For a list of soft IP cores that qualified to IEC 61508 SIL3, see Available IP Cores, page 26.

# **3** Overview of Functional Safety and IEC 61508

IEC 61508 Functional Safety of E/E/PE Safety-related Systems is widely accepted by the industry as the standard to develop and implement safe electronic designs. IEC 61508 provides a generic approach for all safety life cycle activities involved in systems containing E/E/PE elements.

IEC 61508 is an umbrella standard intended to be customized for specific industries. For example, ISO 26262 is the customized IEC 61508-based standard for the automotive industry, and IEC 61513 for the nuclear Industry. If IEC 61508 is not customized for an industry, IEC 61508 itself may be used.

IEC 61508 provides a framework to address the functional safety of systems that contain electrical, electronic, or programmable electronic components. The process described to be compliant with the standard consists of the best practices agreed upon by IEC. The standard consists of the following sections:

- 1. General Requirements

- 2. Requirements for E/E/PE Systems

- 3. Software Requirements

- 4. Definitions and Abbreviations

- 5. Examples of Methods for the Determination of Safety Integrity Levels

- 6. Guidelines for the Application of IEC 61508-2 and IEC 61508-3

- 7. Overview of Techniques and Measures

Sections 1 through 3 contain the requirements for compliance with IEC 61508. All systems must meet the applicable requirements in sections 1 and 2. In addition, software must meet applicable requirements from section 3.

Understanding there is no such thing as zero risk when it comes to safety, IEC 61508 takes a risk reduction approach. Safety integrity level as defined in IEC 61508-4 is the probability of an E/E/PE safety-related system satisfactorily performing the specified safety functions under all the stated conditions within a stated period of time. SILs 1 through 4 are assigned to the safety functions in a system. The methods to determine the SIL can be found in IEC 61508-5. As the SIL increases, the IEC 61508 requirements become more stringent.

It is not acceptable to consider safety at the component level only. In most situations, safety is achieved by a number of systems, which rely on many technologies (for example, mechanical, hydraulic, pneumatic, electrical, and programmable electronic technologies). Any safety strategy must, therefore, consider not only all the elements within an individual system (for example, sensors, controlling devices, and actuators) but also all the subsystems that make up the overall safety-related system. Although IEC 61508 only addresses E/E/PE systems, it can be used as a framework for other safety-related systems. To be compliant with IEC 61508, the safety of the entire system must be addressed, starting at the beginning of the project. Developers need to consider the following:

- What is the required SIL?

- How is the safety function defined?

- What is the safe state?

- What are the temporal requirements?

When possible, safety risks are eliminated or reduced in system concept, architecture, or design. Part of compliance involves using best practice processes during development, implementation, and operations. Best practices also need to be used for technical techniques and measures used in FPGA development. The techniques and measures to be used depend on the SIL and are listed in IEC 61508.

IEC 61508 requires the use of a V-model for development. For information about Libero SoC components used in V-Model development, see How to Use Libero SOC v11.5 SP2 in V-Model Development, page 5.

# 4 How to Use Libero SOC v11.5 SP2 in V-Model Development

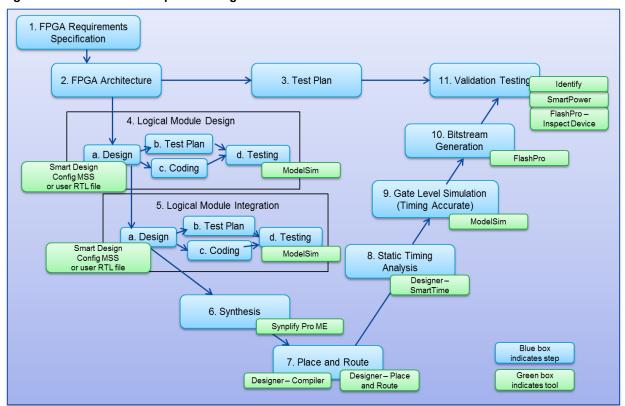

Most often, FPGAs are components in a much more complicated system. That puts the FPGA's development near the bottom of the V in the development of the system of interest. Because the development of an FPGA is slightly different from the development of an ASIC, the Microsemi V-model looks slightly different, but it follows the principles and methodology that are shown in Figure 3: ASIC development life cycle (the V-Model) in IEC61508-2. The following figure illustrates how to use Libero SOC v11.5 SP2 in V-Model development.

Figure 1 • V-Model Development Using Libero SoC

The following table lists the tools in the Libero SOC tool flow that are used in V-Model development.

| Tool                     | Description                                                                                 | Cat. |

|--------------------------|---------------------------------------------------------------------------------------------|------|

| SmartDesign              | Contains the graphics required for design creation.                                         | Т3   |

| Config MSS               | Configures in-built microcontroller subsystem components.                                   | Т3   |

| Synopsys Synplify Pro ME | Performs high-level optimization before synthesizing the RTL code into specific FPGA logic. | Т3   |

| Tool                           | Description                                                                                                                                                                                                                                                                                                                                           | Cat. |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Designer – Compile             | Contains a variety of functions that perform legality checks and<br>basic netlist optimization. Checks for netlist errors (bad<br>connections and fan-out problems), removes unused logic<br>(gobbling), and combines functions to reduce logic count and<br>improve performance. Verifies that the device has sufficient<br>resources to fit design. | Т3   |

| Designer – Place and Route     | Provides the cockpit and engine used to place and route the design.                                                                                                                                                                                                                                                                                   | Т3   |

| Designer – SmartTime           | Provides gate-level static timing analysis.                                                                                                                                                                                                                                                                                                           | T2   |

| Mentor Graphics ModelSim ME    | Provides gate-level verification, allowing verification of HDL code line by line.                                                                                                                                                                                                                                                                     | T2   |

| Designer – Bitstream Generator | Provides the cockpit and engine to export the programing file to program the part, and to export the pin report and IBIS file to design the board.                                                                                                                                                                                                    | Т3   |

| FlashPro                       | Programs the FPGA.                                                                                                                                                                                                                                                                                                                                    | Т3   |

| Designer – SmartPower          | Provides the cockpit and engine to analyze power consumption of the design.                                                                                                                                                                                                                                                                           | T2   |

| Synopsys Identify ME           | Helps find and correct functional design bugs by probing internal signals of the design directly from the programmed FPGA at the system speed.                                                                                                                                                                                                        | T2   |

| FlashPro - Inspect Device      | Allows users to read analog blocks, eNVM, and µFROM.                                                                                                                                                                                                                                                                                                  | T2   |

#### Table 1 • Libero SOC v11.5 SP2 Tools

The following sections describe each step in V-model development using Libero SoC in more detail.

**Note:** IEC 61508 also specifies techniques and measures to be used in each step. These are listed in Techniques and Measures (IEC 61508-2, Table F2), page 22, and in IEC 61508–2, table F2.

# 4.1 Step 1—FPGA Requirement Specification

As mentioned in earlier sections, FPGAs are usually part of a bigger system. Requirements for the system, including safety requirements, are defined during early development and then flowed down to the various subsystems. The results of the system requirement flow-down are an input to FPGA development. The first step in the V-model for FPGA development is to create an FPGA specification or requirements document. The specification is written in enough detail for the design to achieve the required safety function.

For the specification to be IEC 61508-compliant, the FPGA specification must be:

- complete and correct in terms of the safety requirements assigned to the FPGA

- free from contradictions

- understandable and unambiguous, and

- capable of being verified and validated.

In addition, the hardware and software constraints must be listed.

#### *Figure 2* • V-Model Development Step 1—FPGA Requirement Specification

#### Input

• System requirements specification, parent specification, or flow-down of requirements from upper-level specifications

• Overall safety concept, safety specification, or flow-down of safety requirements from upper-tiered safety requirements

Detailed FPGA requirements specification

# 4.1.1 Microsemi References

None

# 4.1.2 Verifying Step Was Completed Correctly

- Cross-check detailed FPGA requirements specification against input documents. Using unique identification numbers for the items facilitates the check.

- Peer review the detailed FPGA requirements specification.

### 4.1.3 Tools

- Standard word-processing software (such as Microsoft Word)

- · Requirements authoring and management tools

### 4.1.4 Specific Techniques and Measures

None

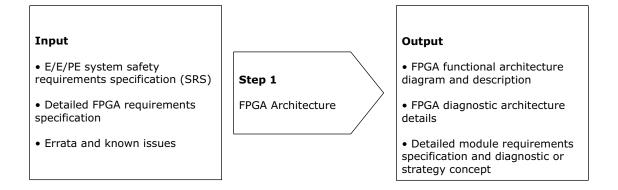

# 4.2 Step 2—FPGA Architecture

In the FPGA Architecture step, the FPGA design is divided into blocks. The requirements in the FPGA specification are partitioned and assigned to the blocks. The interconnections between the blocks and between the blocks and external interfaces are defined. The blocks are assigned such that each block can independently be developed and tested. Typically, a block diagram is created to show the blocks and their interconnections.

As part of creating the FPGA architecture, a specific FPGA may be selected, and IP cores, third-party IP, and standard interfaces may be defined. All necessary safety requirements including design entry, use of specific tools, and sub-modular and modular diagnostic techniques are considered. Any architectural features necessary to check the correct operation of safety design are included. Any known issues with the FPGA devices and tools are considered. The errata for Libero SOC v11.5 SP2 can be found in *Libero SoC v11.5 SP2 Release Notes*.

#### Figure 3 • V-Model Development Step 2—FPGA Architecture

## 4.2.1 Microsemi References

Errata for Libero SOC v11.5 SP2 in Libero SoC v11.5 SP2 Release Notes

### 4.2.2 Verifying Step Was Completed Correctly

- Cross-check input documents items against output document items.

- Peer review or inspect the architecture.

### 4.2.3 Tools

- Standard drawing software (such as Microsoft Visio)

- Standard word-processing software (such as Microsoft Word)

### 4.2.4 Specific Techniques and Measures

None

# 4.3 Step 3—Test Plan

In the Test Plan step, a test description or test specification is created for the fully-integrated FPGA. Each point in the FPGA specification or functional requirements document is addressed. Tests are specified to verify correct functionality and possible fault conditions.

### Figure 4 • V-Model Development Step 3—Test Planning

#### Input

Detailed module requirements specification and diagnostic or strategy concept

| Step 3    |

|-----------|

| Test Plan |

#### Output

FPGA test description

## 4.3.1 Microsemi References

None

## 4.3.2 Verifying Step Was Completed Correctly

- Cross-check testable items in the design document against the numbered tests in the test description

- Peer review the test strategy and coverage

# 4.3.3 Tools

Standard word-processing software (such as Microsoft Word)

### 4.3.4 Specific Techniques and Measures

None

# 4.4 Step 4—Logical Module Design

Logical module design consists of designing individual logical modules, specifying the tests necessary to verify functionality, coding the modules, and then testing them.

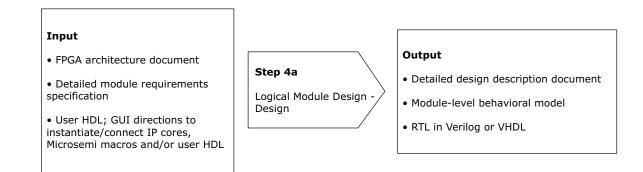

### 4.4.1 Step 4a—Logical Module Design: Design

The modules or blocks in the FPGA are designed during the Design phase of the Logical Module Design step. Factors considered during this step are RAM usage and arrangement, clocking resources (PLLs) routing and arrangement, block I/O connectivity, and bus types. A design document is created, which details a method to achieve the block's requirements. The design document may be at the level of specifying state machine functions, mathematical functions, and detailed block I/O definitions. It must be of sufficient detail to allow a competent engineer to fully implement the block in the FPGA, including diagnostics.

At this stage, it is recommended that the behavior of the block be modeled. A model can be used to verify FPGA architecture and provide a method for checking the final block implementation. The model may be implemented in a high-level modeling language.

For some designs, it may be desirable to include Microsemi's IP cores. These IP cores are called Microsemi DirectCores and can be found in the IP catalog in Libero SOC v11.5 SP2. Microsemi IP cores qualified for use up to IEC 61508 SIL 3 are listed in Available IP Cores, page 26.

#### Figure 5 • V-Model Development Step 4a—Logical Module Design: Design

### 4.4.1.1 Microsemi References

Information about SmartDesign, Config MSS, and catalog core generation from *Libero SoC v11.5 User Guide*

### 4.4.1.2 Verifying Step Was Completed Correctly

- Cross-check the input specification against the output design document.

- Peer review documents.

- Config MSS:

- Use RTL simulation of the generated design to verify intended functionality.

- Review reports, warnings, and errors to determine if output is as expected.

- · Check output file dates with respect to the inputs.

- Use gate-level simulation of the generated design to verify intended functionality.

- Review timing constraints in SmartTime.

- Use a lint tool.

- SmartDesign:

- Use RTL simulation of the generated design to verify intended functionality.

- Use gate-level simulation of the generated design to verify intended functionality.

- Review reports, warnings, and errors to determine if output is as expected.

- Review output logs.

- Check output file dates with respect to the inputs.

- Use of a lint tool.

### 4.4.1.3 Tools

- Standard word-processing software (such as Microsoft Word)

- SmartDesign

- Config MSS

### 4.4.1.4 Specific Techniques and Measures

None

## 4.4.2 Step 4b—Logical Module Design: Test Plan

In the Module Design – Test Plan step, a test description or test specification is created. The test document describes the tests to be used to verify that the block design meets all its requirements.

Each specification item or functional requirement is addressed. Tests are specified to verify correct functionality and possible fault conditions. Tests are also specified to verify the capability of the diagnostic features within the block.

#### Figure 6 • V-Model Development Step 4b—Logical Module Design: Test Plan

#### Input

• E/E/PE system requirements specification (for overall safety items)

• FPGA requirements specification (for FPGA-level requirements)

• Logical module design functional description

#### Step 4b

Logical Module Design – Test Plan

#### Output

Logical module design test description

### 4.4.2.1 Microsemi References

Information about creating a SmartDesign test bench and creating an HDL test bench in *Libero SoC* v11.5 User Guide, pages 80–81

### 4.4.2.2 Verifying Step Was Completed Correctly

- Cross-check testable items in the design document against numbered tests in the test description

- Peer review the test strategy and coverage

### 4.4.2.3 Tools

- Standard word-processing software (Microsoft Word)

- Libero SoC Create SmartDesign Testbench

- Libero SoC Create HDL Testbench

### 4.4.2.4 Specific Techniques and Measures

None

# 4.4.3 Step 4c—Logical Module Design: Coding

In the Logical Module Design – Coding step, the detailed block functional description of the block is translated into a synthesizable design description, which typically takes the form of a (V)HDL description of the circuit functions. A standard text editor may be used for design entry. Libero SoC v11.5 SP2 offers options to use SmartDesign, Config MSS, and the Configure catalog to instantiate, configure, and connect cores and peripherals. Structured diagrammatic methods and a design description in (V)HDL are highly recommended in IEC 61508 for all SILs. Schematic entry and Boolean equations are not recommended for SIL 3.

#### Figure 7 • V-Model Development Step 4c—Logical Module Design: Coding

### 4.4.3.1 Microsemi References

None

### 4.4.3.2 Verifying Step Was Completed Correctly

- Use a lint tool (if applicable).

- Conduct a code inspection or walkthrough.

- Config MSS:

- Use RTL simulation of the generated design to verify intended functionality.

- Review reports, warnings, and errors to determine if output is as expected.

- · Cross-check output file dates against the inputs.

- · Use gate-level simulation of the generated design to verify intended functionality.

- Review timing constraints in SmartTime.

- Use a lint tool.

- SmartDesign:

- · Use RTL simulation of the generated design to verify intended functionality.

- Use gate-level simulation of the generated design to verify intended functionality.

- Review reports, warnings, and errors to determine if output is as expected.

- Review output logs.

- Cross-check output file dates against the inputs.

- Use a lint tool.

### 4.4.3.3 Tools

- Standard text editor

- Configure MSS

- SmartDesign

#### 4.4.3.4 Specific Techniques and Measures

- Structured Description: IEC 61508-2 Table F.2.1

- Design Description in (V)HDL: IEC 61508-2 Table F.2.2

- Schematic Entry: IEC 61508-2 Table F.2.3

- Restricted Use of Asynchronous Constructs: IEC 61508-2 Table F.2.9

- Code Inspection or Walkthrough: IEC 61508-2 Table F.2.15

### 4.4.4 Step 4d—Logical Module Design: Test

In the Logical Module Design - Test step, the tests specified in the test description document are executed and the results analyzed. Of the many techniques available for testing blocks, those appropriate for testing the design are selected. First, a test bench or executable code is created for each

item in the block's test description document. Test benches are typically created in (V)HDL or Verilog using a standard text editor. The use of scripts is recommended because scripts not only save time but also allow tests to be run with a high degree of reliability and repeatability. Next, the tests are run and the results collected and analyzed. Information about the pass/fail status of each test must be easily accessible by the engineering team and the management. The source code is modified to correct the faults in the software and is retested.

#### Figure 8 • V-Model Development Step 4d—Logical Module Design: Test

Input

Step 4d

Logical Module Design Test • Test pass or fail status

Output

• Test pass or fail diagnostics (to aid debug)

### 4.4.4.1 Microsemi References

Logical module design test

• Design source files

description document

None

### 4.4.4.2 Verifying Step Was Completed Correctly

- Use tools.

- Peer review test results.

- Manually check for valid simulator output.

- Check for the presence of report file and its time and date stamp.

- Check for time and date stamps of simulation library files.

- Mentor Graphics ModelSim ME:

- Review logs for correctness.

- Compare results across RTL and multiple gate-level simulations.

- Verify that the behavior on the FPGA is as expected.

- Check output file and simulation library dates against the inputs.

- Manually check for valid simulator output.

- Confirm that the correct top is used.

- Peer review simulation scripts, test benches, and test results.

### 4.4.4.3 Tools

Mentor Graphics ModelSim ME

### 4.4.4.4 Specific Techniques and Measures

- Application of Proven-in-Use (V)HDL Simulators: IEC 61508-2 Table F.2.7

- Functional Test on Module Level (for example, (V)HDL Test benches): IEC 61508-2 Table F.2.8

- Coverage of the Verification Scenarios (Test benches): IEC 61508-2 Table F.2.12

- Documentation of Simulation Results: IEC 61508-2 Table F.2.14

- Application of Proven-in-Use Libraries/CPLD Technologies: IEC 61508-2 Table F.2.24

## 4.4.5 Step 5—Logical Module Integration

The steps for logical module integration are the same as logical module design. The blocks developed during logical module design are combined so that the whole FPGA's design is defined.

## 4.4.6 Step 5a—Logical Module Integration: Design

The design effort for logical module integration is very similar to the design effort for logical module design except in module integration, the design of the whole FPGA is considered instead of individual blocks. The FPGA architecture document may be used to describe the interaction among the blocks. For more information, see Step 4a—Logical Module Design: Design, page 9.

## 4.4.7 Step 5b—Logical Module Integration: Test Plan

The steps for creating a test plan for logical module integration are the same as those for creating the test plan for logical module design except the testing is done at a higher level in the architecture, usually full-chip testing. For more information, see Step 4b—Logical Module Design: Test Plan, page 10.

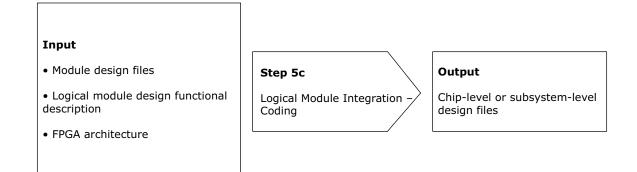

### 4.4.8 Step 5c—Logical Module Integration: Coding

During logical module integration coding, individual blocks developed during the *Logical Module Design* step are combined to create the complete FPGA design.

Libero SmartDesign and Config MSS tools can be used for modular integration. These tools generate code for IP and can simplify code generation and connection of modules. SmartDesign and Config MSS generate an HDL file from a schematic representation. This HDL source can be included in the design in the same way as manually-coded HDL.

#### Figure 9 • V-Model Development Step 5c—Logical Module Integration: Coding

### 4.4.8.1 Microsemi References

None

### 4.4.8.2 Verifying Step Was Completed Correctly

- Analyze the report file output for automated steps.

- Check for VHDL source files time and date stamp.

- Config MSS:

- Use RTL simulation of the generated design to verify intended functionality.

- Review reports, warnings, and errors to determine if output is as expected.

- Check output file dates against the inputs.

- Use gate-level simulation of the generated design to verify intended functionality.

- Review timing constraints in SmartTime.

- Use a lint tool.

- SmartDesign:

- Use RTL simulation of the generated design to verify intended functionality.

- Use gate-level simulation of the generated design to verify intended functionality.

- · Review reports, warnings, errors to determine if output is as expected.

- Review output logs.

- Check output file dates against the inputs.

- Use a lint tool.

### 4.4.8.3 Tools

- SmartDesign

- Config MSS

- Libero text editor

#### 4.4.8.4 Specific Techniques and Measures

- Modularization: IEC 61508-2 Table F.2.11

- Application of Validated Soft Cores: IEC 61508-2 Table F.2.16a

Step 5d

Validation of Soft IP Cores: IEC 61508-2 Table F.2.16b

#### 4.4.9 Step 5d—Logical Module Integration: Test

The Logical Module Integration - Test step is similar to the Module Design - Test step except instead of individual blocks, the combined blocks as a whole are tested. For more information, see Step 4d-Logical Module Design: Test, page 11.

#### Figure 10 • V-Model Development Step 5d—Logical Module Integration: Test

#### Input

Design source files

• Logical module design test description document

Logical Module Integration Test

Output

Test pass or fail status

• Test pass or fail diagnostics (to aid debug)

#### 4.4.9.1 **Microsemi References**

None

#### 4.4.9.2 Verifying Step Was Completed Correctly

- Peer review or inspect test results.

- Manually check for valid simulator output.

- Check for the presence of the report file and its time and date stamp. •

- Check of time and date stamp of simulation library files. •

- Mentor Graphics ModelSim ME:

- Review logs for correctness.

- Compare results across RTL and multiple gate-level simulations.

- Verify that the FPGA behavior is as expected.

- Check output file and simulation library dates against the inputs.

- Manually check for valid simulator output. ٠

- Confirm that the correct top is used.

- Peer review simulation scripts, test benches, and test results.

#### 4.4.9.3 Tools

Mentor Graphics ModelSim ME

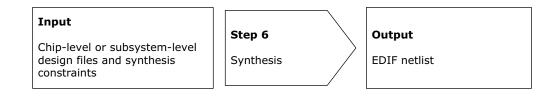

#### 4.5 Step 6—Synthesis

Synopsys Synplify Pro ME, the synthesis tool in the Libero SOC tool suite, performs high-level optimizations before synthesizing the RTL code into specific FPGA logic.

#### Figure 11 • V-Model Development Step 6—Synthesis

# 4.5.1 Microsemi References

Synopsys FPGA Synthesis Synplify Pro ME I-2014.03M-SP1 User Guide for Libero SoC v11.5

## 4.5.2 Verifying Step Was Completed Correctly

- Review generated report files for warnings.

- Check internal project database time and date stamp.

- Check input file list.

- Check output file dates against the inputs.

- Use RTL simulation of the generated design to verify intended functionality.

- Review reports, warnings, and errors to determine if output is as expected.

- Review timing constraints.

- Make sure the Go button does nothing when pushed.

### 4.5.3 Tools

Synopsys Synplify Pro ME

### 4.5.4 Specific Techniques and Measures

- Internal Consistency Checks: IEC 61508-2 Table F.2.17

- Documentation of Synthesis Constraints, Results, and Tools: IEC 61508-2 Table F.2.22

- Application of Proven-in-Use Synthesis: IEC 61508-2 Table F.2.23

- Application of Proven-in-Use Libraries/CPLD Technologies: IEC 61508-2 Table F.2.24

- Script-Based Procedure: IEC 61508-2 Table F.2.25

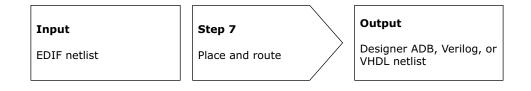

# 4.6 Step 7—Place and Route

In the Place and Route step, the Designer – Compile subroutine translates the logic functions into a format that can be implemented within the target FPGA. The Designer – Compile subroutine contains a variety of functions that perform legality checking and basic netlist optimization. It checks for netlist errors (bad connections and fanout problems), removes unused logic (gobbling), and combines functions to reduce logic count and improve performance. It also verifies that the FPGA has sufficient resources to meet the design requirements. A netlist is created, which includes the placement and routing of each logic cell. When the default *timing-driven* setting is used, place and route runs automatically.

### Figure 12 • V-Model Development Step 7—Place and Route

# 4.6.1 Microsemi References

Information about place and route in Libero SoC v11.5 User Guide, pages 108 - 112

## 4.6.2 Verifying Step Was Completed Correctly

- Analyze tool-generated report files (check for warnings, critical warnings, and so on).

- Check internal project database time and date stamp.

- Check for valid gate-level simulation results.

- Designer Compile subroutine:

- Use gate-level simulation of the generated design to verify intended functionality.

- Make sure the Go button does nothing when pushed.

- Check output file dates against the inputs.

- Review reports, warnings, and errors to determine if output is as expected.

- Check input file list.

- Manually review constraints.

- Designer Place and Route subroutine:

- Use gate-level simulation of the generated design to verify intended functionality.

- Review reports, warnings, and errors to determine if output is as expected.

- Check output file dates against the inputs.

- Make sure the Go button does nothing when pushed.

- Use SmartTime post layout to verify design timing.

- Review timing constraints in SmartTime.

### 4.6.3 Tools

- Designer Compiler subroutine

- Designer Place and Route subroutine

### 4.6.4 Specific Techniques and Measures

- Justification of Proven-in-Use for Applied Hard Cores: IEC 61508-2 Table F.2.26a

- Application of Validated Hard Cores: IEC 61508-2 Table F.2.26b

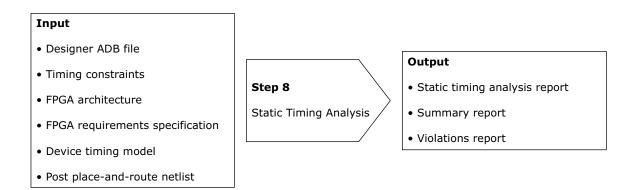

# 4.7 Step 8—Static Timing Analysis

During static timing analysis, static timing is analyzed at the gate level.

### Figure 13 • V-Model Development Step 8—Static Timing Analysis

# 4.7.1 Microsemi References

SmartTime for Libero SoC v11.5 User's Guide

## 4.7.2 Verifying Step Was Completed Correctly

- Review tool output files for timing failures:

- Check that the tool reads the correct constraints (.sdc) file.

- Check the clocks summary report.

- Check for the presence of the report file and its time and date stamp.

- Check unconstrained paths in report files.

- Review timing constraints in SmartTime.

- Verify golden simulations against actual behavior on the device.

- Test the device in a production context.

- Review reports, warnings, and errors to determine if output is as expected.

- Check output file dates against the inputs.

- Ensure that the flow is driven to the correct part/speed grade.

- Use SmartTime post layout to verify design timing.

- Confirm that the top specified is the top needed.

## 4.7.3 Tools

Designer – SmartTime subroutine

## 4.7.4 Specific Techniques and Measures

- Documentation of Synthesis Constraints, Results, and Tools: IEC 61508-2 Table F.2.22

- Static Analysis of the Propagation Delay (STA): IEC 61508-2 Table F.2.27b

- Additional Slack (> 20%) For Process Technologies in Use for Less Than 3 Years: *IEC 61508-2 Table F.2.31*

# 4.8 Step 9—Gate-level Simulation (Timed)

A simulation of the design is created using the netlist from place-and-route. The simulation can first be run without timing data. However, all relevant timing data is later added to the logic simulator to detect any timing violations. It is typical to reuse the simulation test benches created during logical module design testing (see Step 4d—Logical Module Design: Test, page 11).

#### Figure 14 • V-Model Development Step 9—Gate-Level Simulation (Timed)

Input

• Back-annotated netlist and SDF

• Back-annotated netlist and SDF with timing information

• User testbench

Step 9

Gate-Level Simulation

### Output

• Pass/fail value change dump file (.vcd)

• Test pass or fail diagnostics to aid debug

# 4.8.1 Microsemi References

Libero SoC v11.5 User Guide, page 112

### 4.8.2 Verifying Step Was Completed Correctly

- Manually check waveforms.

- Check for time and date stamps in the report file.

- Manually check report file pass or fail status.

- If the simulator gives a false pass to a test, compare simulation results across RTL and multiple gate-level netlists.

- Review logs for correctness.

- Compare results across RTL and multiple gate-level simulations.

- Verify behavior on the FPGA is as expected.

- Check output file and simulation library dates against the inputs.

- Manually check for valid simulator output.

- Confirm that the correct top is used.

- Peer review simulation scripts, test benches, and test results.

### 4.8.3 Tools

Mentor Graphics ModelSim ME

## 4.8.4 Specific Techniques and Measures

- Application of Proven-in-Use Libraries/CPLD Technologies: IEC 61508-2 Table F.2.24

- Simulation of the Gate Netlist to Check Timing Constraints: IEC 61508-2 Table F.2.27a

- Additional Slack (> 20%) for Process Technologies in Use for Less than 3 Years: IEC 61508-2 Table F.2.31

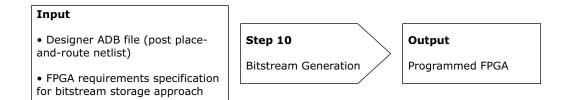

# 4.9 Step 10—Bitstream Generation

The programing files are generated during bitstream generation. The final netlist is used to create the code, which programs the logic cells in the FPGAs. The programing data file (.pdb) is created by the Bitstream Generator subroutine in Designer and sent to the Microsemi FlashPro programmer, which programs the FPGA.

#### *Figure 15* • V-Model Development Step 10—Bitstream Generation

## 4.9.1 Microsemi References

FlashPro for Software v11.5 User's Guide

### 4.9.2 Verifying Step Was Completed Correctly

- Review tool-generated report files.

- Check programming files time and date stamp.

- Microsemi Designer Bitstream Generator subroutine:

- Review reports, warnings, and errors for expected behavior.

- Verify golden simulations against actual behavior on the device.

- Check output file dates against inputs.

- Make sure the Go button does nothing when pushed.

- Confirm the correct top is used.

- Check the contents of memories in SmartDebug.

- FlashPro:

- Review reports, warnings, and errors for expected behavior.

- Perform functional testing on silicon.

- Run standalone verify on the programmed device.

- Verify golden simulations against actual behavior on the device; ensure the root module is set correctly.

- Make sure the Go button does nothing when pushed.

- Run device\_info in FlashPro for the device being programmed.Tools

- Designer Bitstream Generator subroutine

- Microsemi FlashPro programmer

### 4.9.3 Specific Techniques and Measures

None

# 4.10 Step 11—Validation Testing

During the Validation Testing step, it is determined whether the FPGA meets the requirements in the FPGA specification. The FPGA is tested according to the test plan (see Step 3—Test Plan, page 8). If the validation is not successful, the Libero SOC tool suite provides tools to help in the debug process. The SmartPower subroutine in Microsemi Designer analyses the power consumption of the design. Synopsys Identify ME helps find and correct functional design bugs by probing internal signals of the design directly from the programmed FPGA at system speed. The Inspect Device subroutine in Microsemi FlashPro allows users to read analog blocks, eNVM, and  $\mu$ FROM.

#### *Figure 16* • V-Model Development Step 11—Validation Testing

## 4.10.1 Microsemi References

- SmartPower for Libero SoC Software v11.5 User's Guide

- Synopsys Identify RTL J-2014.09M-1 Debugger User Guide for Libero SoC v11.5

- FlashPro for Software v11.5 User's Guide

## 4.10.2 Verifying Step Was Completed Correctly

- Review tool-generated report files.

- To determine if power requirements are correctly calculated, measure power usage on the programmed part in production context.

- To determine the design is correctly modified to trace an internal signal, verify the device behavior is as expected.

- To determine the RTL is in the programming bitstream, prior to production, build the design in a clean environment without Synopsys Identify ME insertion, and check that the checksums generated match the production bitstream.

- To determine that the RTL is in the programming bitstream and the correct signal trace is returned, verify the device behavior is as expected.

- Run standalone verify in FlashPro on the programmed device to determine that the bitstream programmed is the bitstream expected.

- SmartPower:

- Review power report, warnings, and errors for expected behavior.

- Test device power usage in a production context.

- Check output file dates against the inputs.

- Confirm that the correct top is used.

- · Review input parameters (frequency, probabilities, toggle rates, and operating conditions).

- Synopsys Identify ME:

- Check the simulation results against the signals on the board.

- Review reports, warnings, and errors for expected behavior.

- Check design netlist for instantiation of debugger IP.

- Check for valid inputs for all points of analysis.

- FlashPro Inspect Device:

- Check results against user simulation to ensure the design does not write to an unexpected eNVM address.

- Check the board or device power supply.

- Check the cable connection to the JTAG header on board.

- Check continuity of the JTAG cable.

- Check the device status.

- Check for expected results from the device.

- Check configuration contents from file against those displayed in UI.

- Check the simulation results against the signals on the board.

- Check that the correct top is set within Libero.

- Check the eNVM Flash Memory Builder configuration.

- Check the UFROM configuration in Designer, and data assigned.

- Read the device info, and make sure it is correct.

- Read the device status using the View device status option, and check the design versions.

- Review reports, warnings, and errors for expected behavior.

### 4.10.3 Tools

- Designer SmartPower

- Synopsys Identify ME

- Microsemi FlashPro

## 4.10.4 Specific Techniques and Measures

Final Verification and Validation during Mass Production, Per-Unit-Check: IEC 61508-2 Table F.2.41

# 5 Specific Restrictions of Use

Restrictions of use to the Libero SOC tool flow are detailed in *Libero SoC v11.5 SP2 Release Notes*. The Libero SoC v11.5 SP2 certification applies to specific Microsemi devices only. For a list of these devices, see Introduction, page 2.

IP cores referenced in Available IP Cores, page 26 have no restrictions of use.

# 6 Techniques and Measures (IEC 61508-2, Table F2)

To be compliant with IEC 61508 and to prevent the introduction of faults during the development of an FPGA, it is necessary to use techniques and measures specified in IEC 61508-2, paragraph 7.4.6.7 and table F2. Table 2, page 22 lists the techniques and measures for each SIL (except SIL 4, which is outside the scope of this document). Techniques and measures automatically realized by using the Libero SOC tool flow are checked. The designations HR\*, HR, R, -, and NR indicate the importance of the technique or measure. The designations low, medium, and high indicate the effectiveness of the technique or measure.

- HR\*: The technique or measure is highly recommended for this SIL. No design should exclude this technique or measure.

- **HR:** The technique or measure is highly recommended for this SIL. If this technique or measure is not used, then the rationale behind not using it should be detailed.

- R: The technique or measure is recommended for this SIL. If this technique or measure is not used or none of the possible alternatives are used, then the rationale behind not using it should be detailed.

- -: The technique or measure has no recommendations for or against being used.

- NR: The technique or measure is positively not recommended for this SIL. If this technique or measure is used, then the rationale behind using it should be detailed.

### 6.0.1 Effectiveness

- Low: If used, the technique or measure should be used to the extent necessary to give at least low

effectiveness against systematic failures.

- Medium: If used, the technique or measure should be used to the extent necessary to give at least medium effectiveness against systematic failures.

- High: The technique or measure should be used to the extent necessary to give high effectiveness

against systematic failures.

#### Table 2 • Techniques and Measures to Prevent Introduction of Faults during FPGA Design and Development (IEC 61508–2, Table F2)

|    |           |                                                                                 | See IEC |       |       |       |

|----|-----------|---------------------------------------------------------------------------------|---------|-------|-------|-------|

| /  | Ref       | Technique/Measure                                                               | 61508-7 | SIL 1 | SIL 2 | SIL 3 |

| es | ign Entry | y Phase                                                                         |         |       |       |       |

|    | 1         | Structured description                                                          | E3      | HR    | HR    | HR*   |

|    |           |                                                                                 |         | high  | high  | high  |

|    | 2         | Design description in (V)HDL                                                    | E1      | HR    | HR    | HR*   |

|    |           |                                                                                 |         | high  | high  | high  |

|    | 3         | Schematic entry                                                                 | E2      | -     | -     | NR    |

|    |           |                                                                                 |         | high  | high  |       |

|    | 4         | Design description using Boolean equations                                      |         | R     | R     | NR    |

|    |           |                                                                                 |         | high  | high  |       |

|    | 5a        | For circuit descriptions that use Boolean                                       |         | HR    | HR    | HR*   |

|    |           | equations, manual inspection in designs with<br>limited low complexity          |         | high  | high  | high  |

|    | 5b        | For circuit descriptions that use Boolean                                       |         | HR    | HR    | HR*   |

|    |           | equations, simulation of state transitions in<br>designs with higher complexity |         | high  | high  | high  |

# Table 2 • Techniques and Measures to Prevent Introduction of Faults during FPGA Design and Development (IEC 61508–2, Table F2) (continued)

| ✓  | Ref       | Technique/Measure                                     | See IEC<br>61508-7 | SIL 1  | SIL 2  | SIL 3 |

|----|-----------|-------------------------------------------------------|--------------------|--------|--------|-------|

| ✓  | 6         | Application of proven-in-use design                   | E4                 | HR     | HR     | HR*   |

|    |           | environment                                           |                    | high   | high   | high  |

| √  | 7         | Application of proven-in-use design                   | E4                 | HR     | HR     | HR*   |

|    |           | environment (V)HDL simulators                         |                    | high   | high   | high  |

|    | 8         | Functional test at module level (using, for           | E6                 | HR     | HR     | HR*   |

|    |           | example, (V)HDL test benches)                         |                    | high   | high   | high  |

|    | 9         | Restricted use of asynchronous constructs             | E9                 | HR     | HR     | HR*   |

|    |           |                                                       |                    | high   | high   | high  |

|    | 10        | Design for testability (depending on the test         | E11                | R      | R      | R     |

|    |           | coverage in percentage)                               |                    | > 95%  | > 98%  | > 99% |

|    | 11        | Modularization                                        | E12                | R      | R      | HR    |

|    |           |                                                       |                    | medium | medium | high  |

|    | 12        | Coverage of the verification scenarios (test benches) | E13                | R      | R      | HR    |

|    |           |                                                       |                    | medium | medium | high  |

|    | 13        | Observation of coding guidelines                      | E14                | HR     | HR     | HR*   |

|    |           |                                                       |                    | high   | high   | high  |

|    | 14        | Documentation of simulation results                   | E17                | HR     | HR     | HR    |

|    |           |                                                       |                    | low    | medium | high  |

|    | 15a       | Code inspection                                       | E18                | R      | R      | HR    |

|    |           |                                                       |                    | medium | high   | high  |

|    | 15b       | Walkthrough                                           | E19                | R      | R      | HR    |

|    |           |                                                       |                    | medium | high   | high  |

|    | 16a       | Application of validated soft cores                   | E20                | R      | R      | HR    |

|    |           |                                                       |                    | medium | high   | high  |

|    | 16b       | Validation of soft cores                              | E21                | R      | R      | HR    |

|    |           |                                                       |                    | medium | high   | high  |

| yn | thesis Pl | nase                                                  |                    |        |        |       |

| ✓  | 17        | Internal consistency checklists (see for              |                    | HR     | HR     | HR*   |

|    |           | example IEC 61508-7, E4)                              |                    | high   | high   | high  |

|    | 18a       | Simulation of the gate netlist to check timing        | E22                | R      | R      | R     |

|    |           | constraints                                           |                    | medium | medium | high  |

|    | 18b       | Static analysis of the propagation delay (STA)        | E23                | R      | R      | R     |

|    |           |                                                       |                    | medium | medium | high  |

|    | 19a       | Verification of the gate netlist against a            | E24                | R      | R      | HR    |

|    |           | reference model by simulation                         |                    | medium | medium | high  |

# Table 2 • Techniques and Measures to Prevent Introduction of Faults during FPGA Design and Development (IEC 61508–2, Table F2) (continued)

| ~                     | Ref        | Technique/Measure                                                                                                                                                                                                                           | See IEC<br>61508-7 | SIL 1                           | SIL 2                           | SIL 3                            |

|-----------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------|---------------------------------|----------------------------------|

|                       | 19b        | Comparison of the gate netlist with the                                                                                                                                                                                                     | E25                | R                               | R                               | HR                               |

|                       |            | reference model (formal equivalence check)                                                                                                                                                                                                  |                    | medium                          | medium                          | high                             |

|                       | 20         | For PLD/CPLD in complex designs; check of                                                                                                                                                                                                   |                    | R                               | R                               | HR                               |

|                       |            | the design by simulation                                                                                                                                                                                                                    |                    | medium                          | medium                          | high                             |

|                       | 21         | Check of IC vendor requirements and                                                                                                                                                                                                         | E26                | HR                              | HR                              | HR*                              |

|                       |            | constraints                                                                                                                                                                                                                                 |                    | high                            | high                            | high                             |

|                       | 22         | Documentation of synthesis constraints,                                                                                                                                                                                                     | E27                | HR                              | HR                              | HR*                              |

|                       |            | results, and tools                                                                                                                                                                                                                          |                    | high                            | high                            | high                             |

| √                     | 23         | Application of proven-in-use synthesis tools                                                                                                                                                                                                | E28                | HR                              | HR                              | HR*                              |

|                       |            |                                                                                                                                                                                                                                             |                    | high                            | high                            | high                             |

| √                     | 24         | Application of proven-in-use libraries/CPDL                                                                                                                                                                                                 | E29                | HR                              | HR                              | HR*                              |

|                       |            |                                                                                                                                                                                                                                             |                    | high                            | high                            | high                             |

| √                     | 25         | Script-based procedures                                                                                                                                                                                                                     | E30                | R                               | R                               | HR                               |

|                       |            |                                                                                                                                                                                                                                             |                    | high                            | high                            | high                             |

| la                    | cement, F  | Routing, Layout Generation Phase                                                                                                                                                                                                            |                    |                                 |                                 |                                  |

|                       | 26a        | Justification of proven-in-use for applied hard                                                                                                                                                                                             | E34                | HR                              | HR                              | HR*                              |

|                       |            | cores                                                                                                                                                                                                                                       |                    | high                            | high                            | high                             |

|                       | 26b        | Application of validated hard cores                                                                                                                                                                                                         | E35                | HR                              | HR                              | HR*                              |

|                       |            |                                                                                                                                                                                                                                             |                    | high                            | high                            | high                             |

|                       | 26c        | On-line testing of hard cores                                                                                                                                                                                                               | E36                | HR                              | HR                              | HR*                              |

|                       |            |                                                                                                                                                                                                                                             |                    | high                            | high                            | high                             |

|                       | 27a        | Simulation of the gate netlist to check timing                                                                                                                                                                                              | E22                | HR                              | HR                              | HR*                              |

|                       |            | constraints                                                                                                                                                                                                                                 |                    | high                            | high                            | high                             |

|                       | 27b        | Static analysis of the propagation delay (STA)                                                                                                                                                                                              | E23                | HR                              | HR                              | HR*                              |

|                       |            |                                                                                                                                                                                                                                             |                    | high                            | high                            | high                             |

|                       |            |                                                                                                                                                                                                                                             | E24                | HR                              | HR                              | HR*                              |

|                       | 28a        | Verification of the gate netlist against a                                                                                                                                                                                                  |                    |                                 |                                 |                                  |

|                       | 28a        | Verification of the gate netlist against a reference model by simulation                                                                                                                                                                    |                    | high                            | high                            | high                             |

|                       | 28a<br>28b | reference model by simulation<br>Comparison to the gate netlist with the                                                                                                                                                                    | E25                | high<br>HR                      | high<br>HR                      | high<br>HR*                      |

|                       |            | reference model by simulation                                                                                                                                                                                                               |                    | -                               | -                               | -                                |

| ✓                     |            | reference model by simulation<br>Comparison to the gate netlist with the                                                                                                                                                                    |                    | HR                              | HR                              | HR*                              |

| ✓                     | 28b        | reference model by simulation<br>Comparison to the gate netlist with the<br>reference model (formal equivalence check)                                                                                                                      | E25                | HR<br>high                      | HR<br>high                      | HR*<br>high                      |

| ✓<br>✓                | 28b        | reference model by simulation<br>Comparison to the gate netlist with the<br>reference model (formal equivalence check)<br>Design rule check (DRC)<br>Application of proven-in-use design                                                    | E25                | HR<br>high<br>HR                | HR<br>high<br>HR                | HR*<br>high<br>HR                |

| <ul> <li>✓</li> </ul> | 28b<br>29  | reference model by simulation<br>Comparison to the gate netlist with the<br>reference model (formal equivalence check)<br>Design rule check (DRC)                                                                                           | E25<br>E37         | HR<br>high<br>HR<br>high        | HR<br>high<br>HR<br>high        | HR*<br>high<br>HR<br>high        |