# Plastic Package Information for RTG4<sup>™</sup> Sub-QML FPGAs

## Introduction

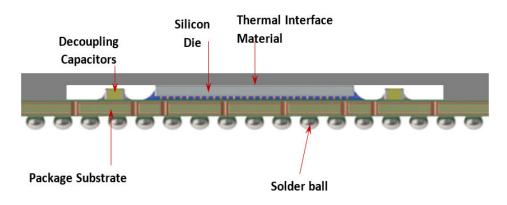

Microchip's RTG4<sup>™</sup> Sub-QML FPGA has been qualified to JEDEC standards in a flip-chip (FC/FCG) 1657 ball grid array plastic package, with 1.0 mm ball pitch. It is pin compatible with our QML Class V-qualified RTG4 FPGAs in ceramic packages CG/LG1657. This document summaries RTG4 plastic package information and recommended Printed Circuit Board (PCB) design rules.

Figure 1. RTG4<sup>™</sup> Sub-QML FPGA in Plastic FC/FCG 1657 Package

# **Table of Contents**

| Intr | oduction                                           | 1 |

|------|----------------------------------------------------|---|

| 1.   | Thermal Characteristics                            | 3 |

| 2.   | Package Specifications                             | 4 |

|      | 2.1. Package Information and Materials             | 4 |

|      | 2.2. Package Mechanical Drawing                    | 5 |

|      | 2.3. Packaging Pin Assignment                      | 5 |

|      | 2.4. Pin Descriptions                              | 5 |

|      | 2.5. Daisy Chain Packages                          | 5 |

|      | 2.6. Package Marking Specifications                | 6 |

|      | 2.7. Packing and Shipping                          | 6 |

|      | 2.8. Recommended PCB Design Rules for BGA Packages | 6 |

| 3.   | Moisture Sensitive Level                           | 8 |

| 4.   | Soldering Reflow Guidelines                        | 9 |

| 5.   | Revision History1                                  | 2 |

| Mic  | rochip Information                                 | 3 |

|      | The Microchip Website                              | 3 |

|      | Product Change Notification Service                | 3 |

|      | Customer Support1                                  | 3 |

|      | Microchip Devices Code Protection Feature          | 3 |

|      | Legal Notice1                                      | 3 |

|      | Trademarks14                                       | 4 |

|      | Quality Management System1                         | 5 |

|      | Worldwide Sales and Service1                       | 6 |

## **1.** Thermal Characteristics

The temperature variable in the Microchip SoC Products Group Libero<sup>®</sup> SoC software refers to the junction temperature, not the ambient, case, or board temperatures. This is an important distinction because dynamic and static power consumption will cause the chip's junction temperature to be higher than the ambient, case, or board temperatures.

The following equations show the relationship between thermal resistance, temperature gradient, and power.

$\Theta_{JB} = (T_J - T_B)/P$

$\Theta_{\rm IC} = (T_{\rm I} - T_{\rm c})/P$

where:

$\Theta_{IB}$  = Junction-to-board thermal resistance

$\Theta_{IC}$  = Junction-to-case thermal resistance

$T_{I}$  = Junction temperature

T<sub>A</sub> = Ambient temperature

$T_B$  = Board temperature (measured 1.0 mm away from the package edge)

$T_{C}$  = Case temperature

P = Total power dissipated by the device

The following table lists the details of package thermal resistance.

#### Table 1-1. Package Thermal Resistance

| RTG4 <sup>™</sup> Product     | Θ <sub>JA</sub> | Θ <sub>JB</sub> | Θ <sub>JC</sub> | Units |

|-------------------------------|-----------------|-----------------|-----------------|-------|

| FCG/FC1657 <sup>1, 2, 3</sup> | 7.52            | 1.31            | 0.075           | °C/W  |

Notes: Theta-JC and Theta-JB values are simulated with conduction heat transfer only.

- 1. Theta-JA values are simulated for still air.

- 2. Theta-JB for FCG/FC1657 refers to the thermal resistance between the junction to the board as defined in the JESD51 standards.

- 3. Theta-JC refers to the thermal resistance between the junction and the top surface (package lid).

## 2. Package Specifications

The following sections describe the package information and specifications of the RTG4 Sub-QML FPGA.

## 2.1 Package Information and Materials

The following figure shows package information of the RTG4 sub-QML FPGA.

Figure 2-1. Package Information

The following table lists the package information and materials of the RTG4 FC/FCG 1657 package.

| Package Information and Materials  | FC1657                                      | FCG1657                            |

|------------------------------------|---------------------------------------------|------------------------------------|

| Package type                       | Flip-chip Ball Grid Array (BGA)             |                                    |

| Package size <sup>1</sup>          | 42.5 mm x 42.5 mm                           |                                    |

| Package pitch                      | 1 mm                                        |                                    |

| Packaged device weight             | 16.05 gm                                    |                                    |

| Decoupling capacitors <sup>2</sup> | Presidio precious metal electrode (PME) 050 | 08                                 |

| Solder ball composition            | Eutectic SnPb (Sn: 63%/Pb: 37%)             | SAC305 (Sn: 96.5%/Ag: 3%/Cu: 0.5%) |

| Solder bump composition            | Pb-free (Sn: 98.2%/Ag: 1.8%)                |                                    |

| Substrate                          | Organic substrate with ultra-low alpha      |                                    |

| Lid <sup>3</sup>                   | AlSiC                                       |                                    |

### Table 2-1. FC1657/FCG1657 Package Information

### Notes:

- 1. FC1657 and FCG1657 packages have the same footprint and IO pin assignment as the CG/CB/ LG1657 package.

- 2. The same internal decoupling capacitors are used in RTG4's CG/CB/LG1657 and CQ352 packages.

- 3. The lids in the FC1657 and FCG1657 packages are not grounded.

### 2.2 Package Mechanical Drawing

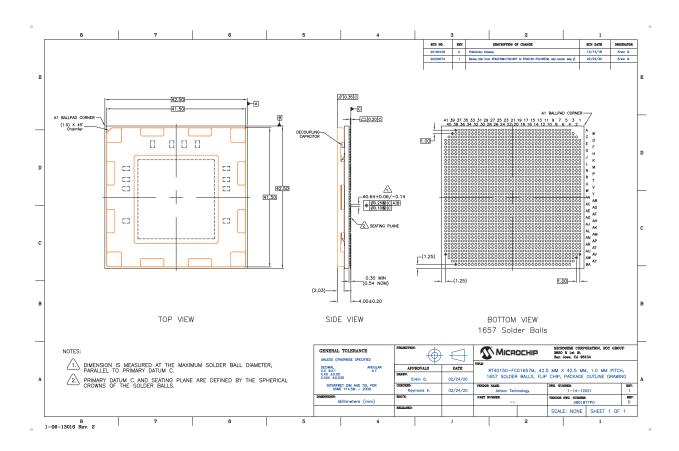

The following figure shows the package outline drawing of FC/FCG 1657.

### Figure 2-2. Package Outline Drawing

### 2.3 Packaging Pin Assignment

For details, see the FC1657 and FCG1657 Package Pin Assignment Table.

### 2.4 Pin Descriptions

For details, see the DS0130: RTG4 FPGA Pin Descriptions Datasheet.

### 2.5 Daisy Chain Packages

For details, see the FCG1657 Daisy Chain Package User Guide.

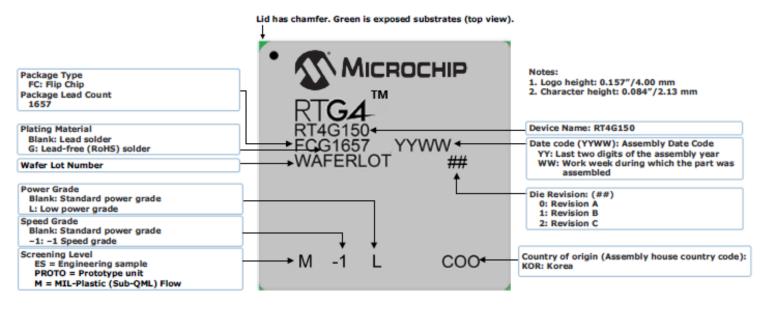

### 2.6 Package Marking Specifications

Microchip marks the part number on the top of every RTG4 device along with other device specifications, as shown in the following figure.

#### Figure 2-3. RTG4 Plastic Device Marking Specifications

### 2.7 Packing and Shipping

The RTG4 Sub-QML FPGA in plastic packaging is packed in trays to provide protection from mechanical damage. The maximum number of devices per tray is 12.

### 2.8 Recommended PCB Design Rules for BGA Packages

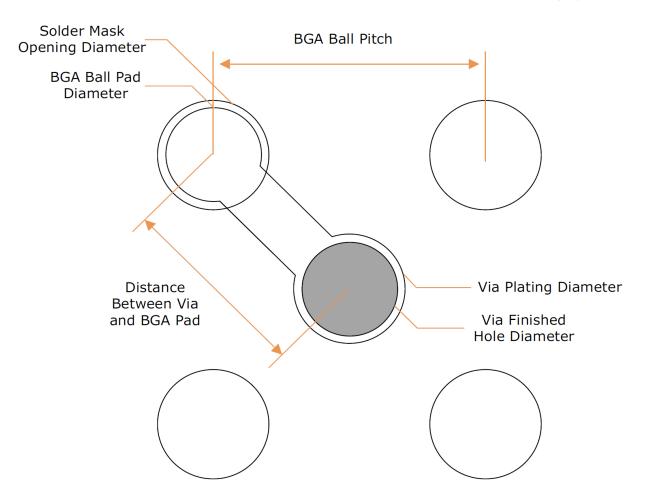

The land pad information on the package side is required prior to the start of the board layout, so that the board pads can be designed to match the component-side land geometry. The typical values of these land pads are shown in the following figure and listed in Table 2-2. For BGA packages, Non-Solder Mask Defined (NSMD) pads on the board are suggested to allow a clearance between the land metal (diameter) and the solder mask opening (diameter), as shown in the following figure. The space between the NSMD pad and the solder mask, the actual signal trace widths, and through dimensions depend on the capability of the PCB vendor. The cost of the PCB is higher when the line width and spaces are smaller.

| Table 2-2. Recommende | ed PCB Designs Rules |

|-----------------------|----------------------|

|-----------------------|----------------------|

| Design Rule for Packages               | FC1657/FCG1657 (in mm) |

|----------------------------------------|------------------------|

| BGA ball pad diameter                  | 0.51                   |

| Solder mask opening diameter           | 0.54                   |

| BGA ball pitch                         | 1.0                    |

| Line width between via and solder land | 0.15                   |

| Distance between via and solder Land   | 0.7                    |

| Via finished hole diameter             | 0.33                   |

| Via plating diameter                   | 0.48                   |

## 3. Moisture Sensitive Level

RTG4 Sub-QML FPGAs in FC/FCG1657 packages have Moisture Sensitive Level (MSL) 4.

## 4. Soldering Reflow Guidelines

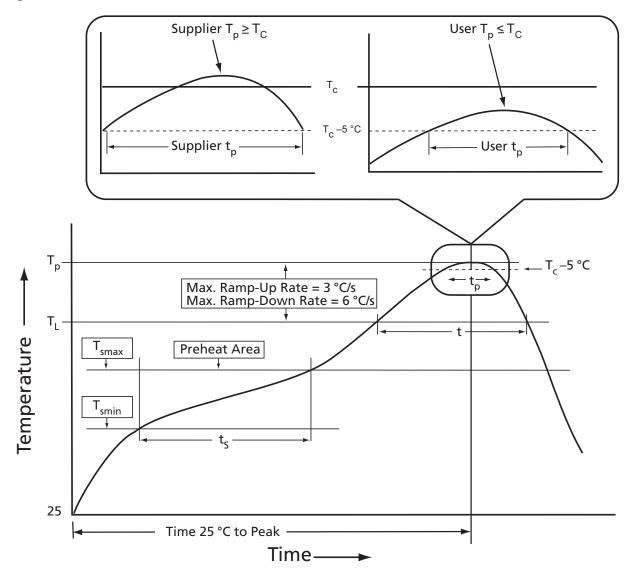

This section describes the standard reflow profile for standard and lead-free packages.

**Note:** The reflow is for reference only. Users must optimize their own board level parameters to get proper reflow outcome. Per package qualification maximum number of reflow that can be done on Microchip FPGA packages is 3.

| Package Thickness | Volume mm <sup>3</sup> < 350 | Volume mm <sup>3</sup> ≥ 350 |

|-------------------|------------------------------|------------------------------|

| <2.5 mm           | 235 + 0/–5 °C                | 225 + 0/–5 °C                |

| 2.5 mm            | 225 + 0/–5 °C                | 225 + 0/–5 °C                |

**Table 4-2.** Pb-Free Process—Classification Temperature (T<sub>C</sub>)

| Package Thickness (in mm) | Volume mm <sup>3</sup> <sub>-</sub> < 350 | Volume mm <sup>3</sup> 350–2000 | Volume mm <sup>3</sup> <sub>2</sub> > 2000 |

|---------------------------|-------------------------------------------|---------------------------------|--------------------------------------------|

| <1.6                      | 260 + 0 °C <sup>1</sup>                   | 260 + 0 °C <sup>1</sup>         | 260 + 0 °C <sup>1</sup>                    |

| 1.6–2.5                   | 260 + 0 °C <sup>1</sup>                   | 250 + 0 °C <sup>1</sup>         | 245 + 0 °C <sup>1</sup>                    |

| ≥2.5                      | 250 + 0 °C <sup>1</sup>                   | 245 + 0 °C <sup>1</sup>         | 245 + 0 °C <sup>1</sup>                    |

### Notes:

- 1. Tolerance: The device manufacturer/supplier must assure process compatibility up to and including the stated classification temperature at the rated MSL level (that is, peak reflow temperature + 0 °C. For example, 260 °C + 0 °C).

- 2. At the discretion of the device manufacturer, but not the board assembler/user, the maximum peak package body temperature ( $T_p$ ) can exceed the values specified in Table 4-2 and Table 4-3. The use of a higher  $T_p$  does not change the  $T_c$ .

- 3. Package volume excludes external terminals (balls, bumps, lands, and leads) and/or non-integral heat sinks.

- 4. The maximum component temperature reached during reflow depends on package thickness and volume. The use of convection reflow processes reduces the thermal gradients between packages. However, thermal gradients due to differences in thermal mass of SMD packages might still exist.

- 5. Moisture sensitivity levels of components used in a Pb-free assembly process must be evaluated using the Pb-free classification temperatures and profiles defined in Table 4-2 and Table 4-3, if Pb-free.

- 6. SMD packages classified to a given moisture sensitivity level by using Procedures or Criteria defined within any previous version of J-STD-020, JESD22-A112 (rescinded), IPC-SM-786 (rescinded) need not be reclassified to the current revision, unless a change in classification level or a higher peak classification temperature is required.

#### Table 4-3. Classification Reflow Profile

| Profile Feature                                                                                                                                                                     | SnPb Eutectic Assembly                       | Pb-Free Assembly                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| <b>Preheat and Soak</b><br>Temperature minimum (T <sub>smin</sub> )<br>Temperature maximum (T <sub>smax</sub> )<br>Time (T <sub>smin</sub> to T <sub>smax</sub> ) (t <sub>s</sub> ) | 100 °C<br>150 °C<br>60s–120s                 | 150 °C<br>200 °C<br>60s–120s                 |

| Average ramp-up rate ( $T_{smax}$ to $T_p$ )                                                                                                                                        | 3 °C/second maximum                          | 3 °C/second maximum                          |

| Liquidous temperature (T_L) Time at liquidous $(t_L)$                                                                                                                               | 183 °C<br>60s-150s                           | 217 °C<br>60s–150s                           |

| Peak package body temperature $(T_p)^1$                                                                                                                                             | See classification temperature in Table 4-1. | See classification temperature in Table 4-2. |

| Time $(t_p)^2$ within 5 °C of the specified classification temperature $(T_C)$                                                                                                      | 202s                                         | 302s                                         |

| Average ramp-down rate ( $T_p$ to $T_{smax}$ )                                                                                                                                      | 6 °C/s maximum                               | 6 °C/s maximum                               |

| Time 25 °C to peak temperature                                                                                                                                                      | 6 minutes maximum                            | 8 minutes maximum                            |

#### Notes:

- 1. Tolerance for peak profile temperature (T<sub>p</sub>) is defined as a supplier minimum and a user maximum.

- 2. Tolerance for time at peak profile temperature (t<sub>p</sub>) is defined as a supplier minimum and a user maximum.

- 3. All temperatures refer to the center of the package, measured on the package body surface that is facing up during the assembly reflow (for example, live-bug). If parts are reflowed in other than the normal live-bug assembly reflow orientation (that is, dead-bug), then the  $T_p$  must be within  $\pm 2$  °C of the live-bug  $T_p$  and still meet the  $T_0$  requirements. Otherwise, the profile is adjusted to achieve the latter. To accurately measure actual peak package body temperatures, see the JEP140 for recommended thermocouple use.

- 4. Reflow profiles in this document are for classification/preconditioning and are not meant to specify board assembly profiles. Actual board assembly profiles must be developed based on specific process needs and board designs, and must not exceed the parameters that are listed in Table 4-3.

For example, if  $T_0$  is 260 °C and time  $t_p$  is 30 seconds, then:

- For a supplier: The peak temperature must be at least 260 °C. The time above 255 °C must be at least 30 seconds.

- Fora user: The peak temperature must not exceed 260 °C. The time above 255 °C must not exceed 30 seconds.

- 5. All components in the test load must meet the classification profile requirements.

- 6. SMD packages classified to a given moisture sensitivity level by using Procedures or Criteria defined within any previous version of J-STD-020, JESD22-A112 (rescinded), IPC-SM-786 (rescinded) need not be reclassified to the current revision, unless a change in classification level or a higher peak classification temperature is desired.

The following figure shows the reflow profile.

### Figure 4-1. Reflow Profile

## 5. Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

| Revision | Date    | Description                                                                                                                                                                                              |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В        | 12/2023 | <ul> <li>The following is a summary of changes in revision B of this document:</li> <li>Added a note stating that the lids in the FC1657 and FCG1657 packages are not grounded, in Table 2-1.</li> </ul> |

| А        | 12/2021 | Initial Revision.                                                                                                                                                                                        |

# **Microchip Information**

## The Microchip Website

Microchip provides online support via our website at www.microchip.com/. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- **General Technical Support** Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

## **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

### **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.

### Legal Notice

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure

that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at www.microchip.com/en-us/support/design-help/ client-support-services.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge, IGaT, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, MarginLink, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2023, Microchip Technology Incorporated and its subsidiaries. All Rights Reserved.

ISBN: 978-1-6683-3687-8

### **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# Worldwide Sales and Service

| MERICAS                  | ASIA/PACIFIC          | ASIA/PACIFIC            | EUROPE                |

|--------------------------|-----------------------|-------------------------|-----------------------|

| orporate Office          | Australia - Sydney    | India - Bangalore       | Austria - Wels        |

| 355 West Chandler Blvd.  | Tel: 61-2-9868-6733   | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39  |

| andler, AZ 85224-6199    | China - Beijing       | India - New Delhi       | Fax: 43-7242-2244-393 |

| l: 480-792-7200          | Tel: 86-10-8569-7000  | Tel: 91-11-4160-8631    | Denmark - Copenhagen  |

| ax: 480-792-7277         | China - Chengdu       | India - Pune            | Tel: 45-4485-5910     |

| chnical Support:         | Tel: 86-28-8665-5511  | Tel: 91-20-4121-0141    | Fax: 45-4485-2829     |

| ww.microchip.com/support | China - Chongqing     | Japan - Osaka           | Finland - Espoo       |

| eb Address:              | Tel: 86-23-8980-9588  | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820   |

| ww.microchip.com         | China - Dongguan      | Japan - Tokyo           | France - Paris        |

| lanta                    | Tel: 86-769-8702-9880 | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20 |

| uluth, GA                | China - Guangzhou     | Korea - Daegu           | Fax: 33-1-69-30-90-79 |

| l: 678-957-9614          | Tel: 86-20-8755-8029  | Tel: 82-53-744-4301     | Germany - Garching    |

| nx: 678-957-1455         | China - Hangzhou      | Korea - Seoul           | Tel: 49-8931-9700     |

| ustin, TX                | Tel: 86-571-8792-8115 | Tel: 82-2-554-7200      | Germany - Haan        |

| l: 512-257-3370          | China - Hong Kong SAR | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400  |

| oston                    | Tel: 852-2943-5100    | Tel: 60-3-7651-7906     | Germany - Heilbronn   |

| estborough, MA           | China - Nanjing       | Malaysia - Penang       | Tel: 49-7131-72400    |

| el: 774-760-0087         | Tel: 86-25-8473-2460  | Tel: 60-4-227-8870      | Germany - Karlsruhe   |

| ax: 774-760-0088         | China - Qingdao       | Philippines - Manila    | Tel: 49-721-625370    |

| hicago                   | Tel: 86-532-8502-7355 | Tel: 63-2-634-9065      | Germany - Munich      |

| asca, IL                 | China - Shanghai      | Singapore               | Tel: 49-89-627-144-0  |

| l: 630-285-0071          | Tel: 86-21-3326-8000  | Tel: 65-6334-8870       | Fax: 49-89-627-144-44 |

| ax: 630-285-0075         | China - Shenyang      | Taiwan - Hsin Chu       | Germany - Rosenheim   |

| allas                    | Tel: 86-24-2334-2829  | Tel: 886-3-577-8366     | Tel: 49-8031-354-560  |

| ddison, TX               | China - Shenzhen      | Taiwan - Kaohsiung      | Israel - Ra'anana     |

| el: 972-818-7423         | Tel: 86-755-8864-2200 | Tel: 886-7-213-7830     | Tel: 972-9-744-7705   |

| ax: 972-818-2924         | China - Suzhou        | Taiwan - Taipei         | Italy - Milan         |

| etroit                   | Tel: 86-186-6233-1526 | Tel: 886-2-2508-8600    | Tel: 39-0331-742611   |

| ovi, MI                  | China - Wuhan         | Thailand - Bangkok      | Fax: 39-0331-466781   |

| l: 248-848-4000          | Tel: 86-27-5980-5300  | Tel: 66-2-694-1351      | Italy - Padova        |

| ouston, TX               | China - Xian          | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286   |

| l: 281-894-5983          | Tel: 86-29-8833-7252  | Tel: 84-28-5448-2100    | Netherlands - Drunen  |

| dianapolis               | China - Xiamen        |                         | Tel: 31-416-690399    |

| oblesville, IN           | Tel: 86-592-2388138   |                         | Fax: 31-416-690340    |

| l: 317-773-8323          | China - Zhuhai        |                         | Norway - Trondheim    |

| ax: 317-773-5453         | Tel: 86-756-3210040   |                         | Tel: 47-72884388      |

| el: 317-536-2380         |                       |                         | Poland - Warsaw       |

| os Angeles               |                       |                         | Tel: 48-22-3325737    |

| ission Viejo, CA         |                       |                         | Romania - Bucharest   |

| l: 949-462-9523          |                       |                         | Tel: 40-21-407-87-50  |

| ax: 949-462-9608         |                       |                         | Spain - Madrid        |

| el: 951-273-7800         |                       |                         | Tel: 34-91-708-08-90  |

| aleigh, NC               |                       |                         | Fax: 34-91-708-08-91  |

| l: 919-844-7510          |                       |                         | Sweden - Gothenberg   |

| ew York, NY              |                       |                         | Tel: 46-31-704-60-40  |

| el: 631-435-6000         |                       |                         | Sweden - Stockholm    |

| in Jose, CA              |                       |                         | Tel: 46-8-5090-4654   |

| el: 408-735-9110         |                       |                         | UK - Wokingham        |

| el: 408-436-4270         |                       |                         | Tel: 44-118-921-5800  |

| anada - Toronto          |                       |                         | Fax: 44-118-921-5820  |

|                          |                       |                         |                       |