# PolarFire<sup>®</sup> SoC FPGA Packaging and Pin Descriptions

### Introduction

This guide provides pin and packaging information (such as bank assignments and mechanical information) for PolarFire SoC FPGAs.

PolarFire SoC FPGAs feature a flexible I/O structure that supports a range of mixed voltages (1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V) through bank selection. The HSIO and GPIO are configured as differential I/Os or two single-ended I/Os. For more information about HSIO, GPIO, and supported I/O standards, see UG0916: PolarFire SoC FPGA IO User Guide.

# **Table of Contents**

| Intro                                                                 | oductio                                                                                                            | n                                                                                                                                                                                                                                             | 1                                                                                    |  |  |  |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|

| 1.                                                                    | Packa<br>1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.                                                                      | aging Overview<br>Bank Locations<br>Packaging Pin Assignment<br>Pin Descriptions<br>Package Pinouts<br>Mechanical Drawings                                                                                                                    | 3<br>10<br>. 10<br>. 16                                                              |  |  |  |

| 2.                                                                    | Packa                                                                                                              | age Material Information                                                                                                                                                                                                                      | . 26                                                                                 |  |  |  |

| 3.                                                                    | Therm                                                                                                              | nal Specifications                                                                                                                                                                                                                            | .27                                                                                  |  |  |  |

| 4.                                                                    | Packa                                                                                                              | age Marking                                                                                                                                                                                                                                   | . 28                                                                                 |  |  |  |

| 5.                                                                    | Packi                                                                                                              | ng and Shipping                                                                                                                                                                                                                               | . 29                                                                                 |  |  |  |

| 6.                                                                    | Therm<br>6.1.                                                                                                      | nal Management<br>System Level Heat Sink Solutions                                                                                                                                                                                            |                                                                                      |  |  |  |

| 7.                                                                    | Therm<br>7.1.                                                                                                      | nal Interface Material<br>Heat Sink Attachments                                                                                                                                                                                               |                                                                                      |  |  |  |

| 8.                                                                    | Heat Sink Removal Procedure                                                                                        |                                                                                                                                                                                                                                               |                                                                                      |  |  |  |

| 0.                                                                    |                                                                                                                    |                                                                                                                                                                                                                                               |                                                                                      |  |  |  |

| 9.                                                                    |                                                                                                                    | nmended PCB Design Rules for BGA Packages                                                                                                                                                                                                     | . 33                                                                                 |  |  |  |

| 9.                                                                    | Recor                                                                                                              |                                                                                                                                                                                                                                               |                                                                                      |  |  |  |

| 9.<br>10.                                                             | Recor<br>Moistu<br>Revisi<br>11.1.<br>11.2.<br>11.3.                                                               | nmended PCB Design Rules for BGA Packages                                                                                                                                                                                                     | . 34<br>. 35<br>. 35<br>. 35<br>35                                                   |  |  |  |

| 9.<br>10.<br>11.                                                      | Recor<br>Moistu<br>Revisi<br>11.1.<br>11.2.<br>11.3.<br>11.4.                                                      | nmended PCB Design Rules for BGA Packages<br>ure Sensitive Level (MSL)<br>ion History<br>Revision B<br>Revision A.<br>Revision 2.0.                                                                                                           | . 34<br>. 35<br>. 35<br>. 35<br>35<br>35                                             |  |  |  |

| 9.<br>10.<br>11.<br>The                                               | Recor<br>Moistu<br>Revisi<br>11.1.<br>11.2.<br>11.3.<br>11.4.                                                      | nmended PCB Design Rules for BGA Packages<br>ure Sensitive Level (MSL)<br>ion History<br>Revision B<br>Revision A.<br>Revision 2.0.<br>Revision 1.0                                                                                           | . 34<br>. 35<br>. 35<br>. 35<br>35<br>35<br>35                                       |  |  |  |

| <ol> <li>9.</li> <li>10.</li> <li>11.</li> <li>The<br/>Pro</li> </ol> | Recor<br>Moistu<br>Revisi<br>11.1.<br>11.2.<br>11.3.<br>11.4.<br>Microo<br>duct Cl                                 | nmended PCB Design Rules for BGA Packages<br>ure Sensitive Level (MSL)<br>ion History<br>Revision B<br>Revision A<br>Revision A<br>Revision 2.0.<br>Revision 1.0.                                                                             | . 34<br>. 35<br>. 35<br>. 35<br>. 35<br>. 35<br>. 35<br>. 36                         |  |  |  |

| 9.<br>10.<br>11.<br>The<br>Pro<br>Cus                                 | Recor<br>Moistu<br>Revisi<br>11.1.<br>11.2.<br>11.3.<br>11.4.<br>Microo<br>duct Cl<br>stomer                       | nmended PCB Design Rules for BGA Packages<br>ure Sensitive Level (MSL)<br>ion History<br>Revision B<br>Revision A<br>Revision A<br>Revision 2.0.<br>Revision 1.0.<br>chip Website<br>hange Notification Service                               | . 34<br>. 35<br>. 35<br>. 35<br>. 35<br>. 35<br>. 35<br>. 36<br>. 36                 |  |  |  |

| 9.<br>10.<br>11.<br>The<br>Pro<br>Cus<br>Mic                          | Recor<br>Moistu<br>Revisi<br>11.1.<br>11.2.<br>11.3.<br>11.4.<br>Microo<br>duct Cl<br>stomer<br>rochip             | nmended PCB Design Rules for BGA Packages<br>ure Sensitive Level (MSL)<br>ion History<br>Revision B<br>Revision A<br>Revision 2.0.<br>Revision 1.0.<br>chip Website.<br>hange Notification Service                                            | . 34<br>. 35<br>. 35<br>. 35<br>. 35<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36         |  |  |  |

| 9.<br>10.<br>11.<br>The<br>Pro<br>Cus<br>Mic<br>Leg                   | Recor<br>Moistu<br>Revisi<br>11.1.<br>11.2.<br>11.3.<br>11.4.<br>Microo<br>duct Cl<br>stomer<br>rochip             | nmended PCB Design Rules for BGA Packages<br>ure Sensitive Level (MSL)<br>ion History<br>Revision B<br>Revision A<br>Revision 2.0<br>Revision 1.0<br>chip Website<br>hange Notification Service<br>Support<br>Devices Code Protection Feature | . 34<br>. 35<br>. 35<br>. 35<br>. 35<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 37 |  |  |  |

| 9.<br>10.<br>11.<br>The<br>Pro<br>Cus<br>Mic<br>Leg<br>Trad           | Recor<br>Moistu<br>Revisi<br>11.1.<br>11.2.<br>11.3.<br>11.4.<br>Microo<br>duct Cl<br>stomer<br>rochip<br>al Notio | nmended PCB Design Rules for BGA Packages<br>ure Sensitive Level (MSL)<br>Revision B<br>Revision A<br>Revision 2.0<br>Revision 1.0<br>chip Website<br>hange Notification Service<br>Support<br>Devices Code Protection Feature<br>ce          | . 34<br>. 35<br>. 35<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 36<br>. 37<br>. 37 |  |  |  |

## 1. Packaging Overview

PolarFire SoC FPGAs are available in multiple packages. Each package (device variant) has various I/O banks with the flexibility of using different I/O standards. HSIO and GPIO banks have a maximum supply voltage of 1.8 V and 3.3 V respectively.

The following table lists the PolarFire SoC FPGA variants, with user I/O and XCVR lanes, in Pb-free packages.

| -           |                    |                    |                    |                    |                    |                    |                    |

|-------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| Bank Number | FCG1152            | FCG1152            | FCVG784            | FCSG536            | FCVG484            | FCVG484            | FCVG484            |

|             | MPFS460T           | MPFS250T           | MPFS250T           | MPFS250T           | MPFS250T           | MPFS160T           | MPFS095TS          |

| Bank 0      | HSIO               |

| Bank 1      | GPIO               |

| Bank 2      | MSSIO              |

| Bank 3      | JTAG/<br>FIXED I/O |

| Bank 4      | MSSIO              |

| Bank 5      | MSS-SGMII          |

| Bank 6      | MSS-DDR            |

| Bank 7      | GPIO               | GPIO               | GPIO               | GPIO               | _                  | —                  | —                  |

| Bank 8      | HSIO               | HSIO               | HSIO               | —                  | _                  | —                  | _                  |

| Bank 9      | GPIO               | GPIO               | GPIO               | —                  | _                  | —                  | —                  |

| XCVR 0      | Yes                |

| XCVR 1      | Yes                | Yes                | Yes                | —                  | —                  | —                  | _                  |

| XCVR 2      | Yes                | Yes                | _                  | _                  | _                  | _                  | _                  |

| XCVR 3      | Yes                | Yes                | —                  | —                  | —                  | —                  | _                  |

| XCVR 4      | Yes                |                    | _                  | _                  | _                  | _                  | _                  |

#### Table 1-1. Organization of I/O Banks

### 1.1 Bank Locations

PolarFire SoC FPGA I/O are grouped based on I/O voltage standards and I/O capabilities. Each I/O bank has dedicated I/O supplies and ground voltages. Due to these dedicated supplies, only I/O with compatible standards are assigned to the same I/O voltage bank.

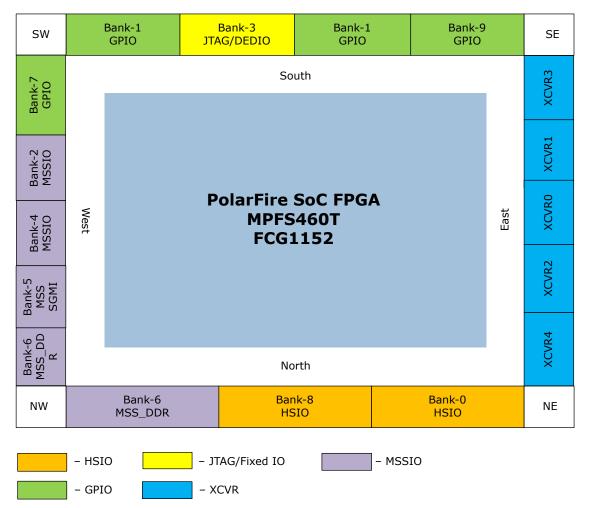

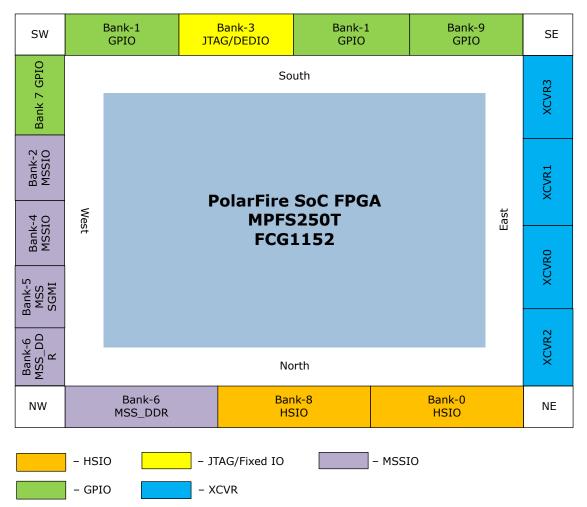

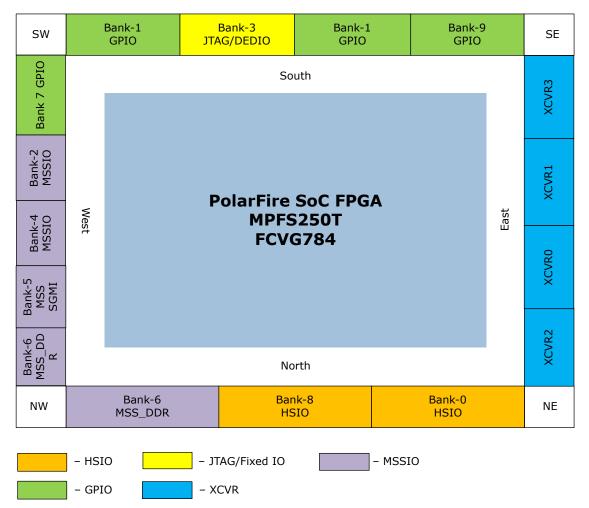

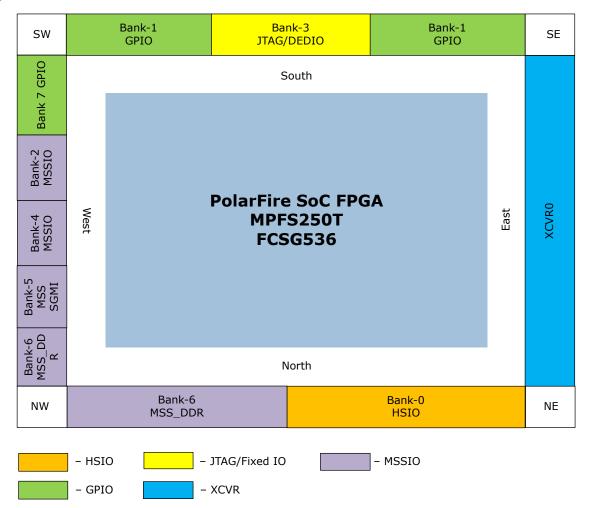

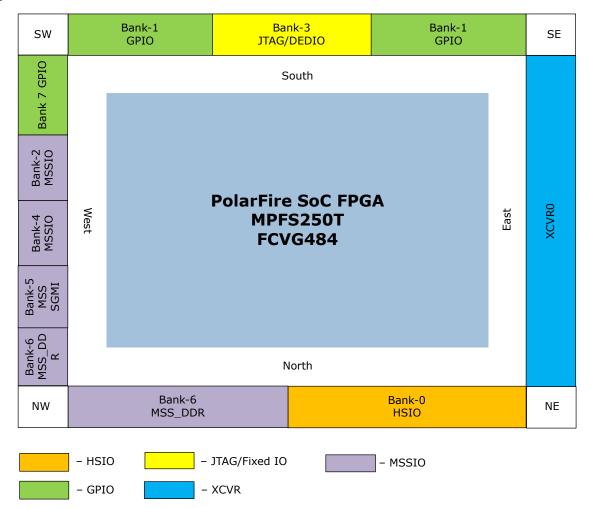

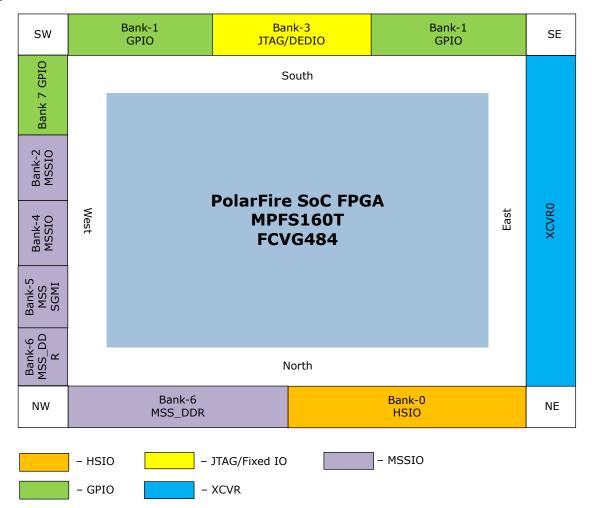

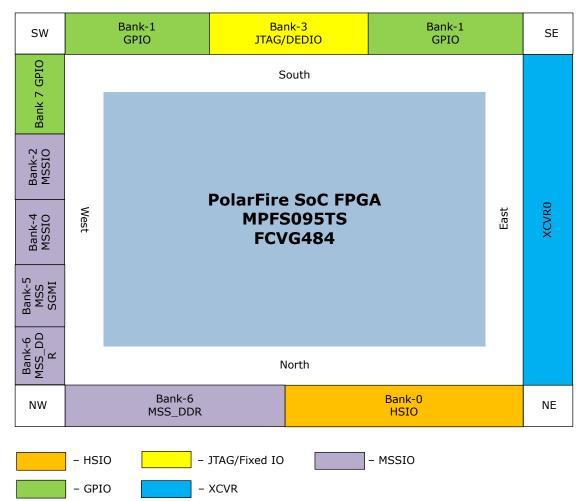

The following illustrations show the bank locations for the MPFS460T, MPFS250T, MPFS160T, and MPFS095T devices with available package combinations.

Figure 1-1. PolarFire SoC FPGA MPFS460T-FCG1152 I/O Bank Locations

Figure 1-2. PolarFire SoC FPGA MPFS250T-FCG1152 I/O Bank Locations

Figure 1-3. PolarFire SoC FPGA MPFS250T-FCVG784 I/O Bank Locations

Figure 1-4. PolarFire SoC FPGA MPFS250T-FCSG536 I/O Bank Locations

Figure 1-5. PolarFire SoC FPGA MPFS250T-FCVG484 I/O Bank Locations

Figure 1-6. PolarFire SoC FPGA MPFS160T-FCVG484 I/O Bank Locations

Figure 1-7. PolarFire SoC FPGA MPFS095TS-FCVG484 I/O Bank Locations

### 1.2 Packaging Pin Assignment

PolarFire SoC Packaging Pin Assignment Table (PPAT) contains information about recommended DDR pinouts, PCIe capability for XCVR-0, DDR lane information for I/O CDR, and generic IOD interface pin placement.

### 1.3 Pin Descriptions

PolarFire SoC devices have user I/O (GPIO/HSIO) pins, dedicated I/O bank pins, memory interface, XCVR interface, clocking pins, and supply pins.

### 1.3.1 User I/O

PolarFire SoC FPGA I/Os are paired up to meet the differential I/O standards and grouped into lanes of 12 buffers with a lane controller for memory interfaces. For more information about the memory controller, see UG0906: PolarFire SoC FPGA DDR Memory Controller User Guide.

There are two types of I/O buffers—HSIO and GPIO. HSIO is optimized for 1.2 Gbps (DDR4) operation with operating supplies between 1.1 V and 1.8 V. GPIO buffers support a wider range of I/O interfaces with speeds of up to 1066 Mbps when using single-ended standards and 1.25 Gbps when using differential standards, and operating

supplies ranging from 1.2 V to 3.3 V. GPIO supports multiple standards, including 3.3 V with an integrated Clock Data Recovery (CDR) to high-speed serial interfaces such as 1GbE.

Each PolarFire SoC FPGA user I/O uses a IOxyBz naming convention, where:

- IO = The type of I/O.

- x = The I/O pair number in Bank z.

- y = P (positive) or N (negative). In Single-Ended mode, the I/O pair operates as two separate I/O—P and N. Differential mode is implemented with a fixed I/O pair and cannot be split with an adjacent I/O.

- B = Bank (see note in 1.3.1.1 Supported I/O Features.

- z = Bank number. GPIOxyBz and HSIOxyBz are bi-directional user I/O pins that are capable of differential signaling.

#### 1.3.1.1 Supported I/O Features

The following table lists the I/O features supported on HSIO and GPIO.

#### Table 1-2. Supported I/O Features

| I/O Feature                                               | HSIO             | GPIO | Additional Information   |

|-----------------------------------------------------------|------------------|------|--------------------------|

| Programmable on/off clamp                                 | —                | Yes  | —                        |

| Hot-plug                                                  | —                | Yes  | —                        |

| Cold sparing                                              | Yes <sup>1</sup> | Yes  | —                        |

| True differential output driver                           | —                | Yes  | —                        |

| Programmable on/off 100 $\Omega$ differential termination | —                | Yes  | —                        |

| PVT-compensated output drive                              | Yes              | Yes  | —                        |

| Programmable slew control                                 | —                | Yes  | —                        |

| PVT compensated slew control                              | Yes              | —    | —                        |

| Programmable input hysteresis                             | Yes              | Yes  | —                        |

| Mobile Industry Processor Interface (MIPI) (input)        | —                | Yes  | High-speed and low-power |

| MIPI (output)                                             | _                | Yes  | High-speed               |

**Note:** 1. HSIO is pseudo-cold spare that is, it requires the spare device to have its HSIO VDDI banks powered-up to prevent I/O leakage through the ESD diodes.

#### 1.3.2 MSS I/Os

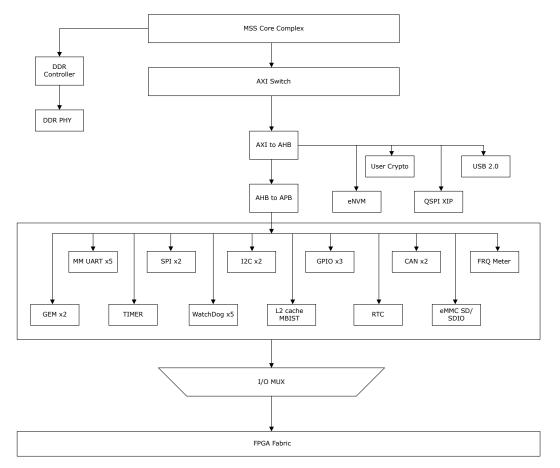

The PolarFire SoC family offers the industry's first RISC-V based SoC FPGAs. The PolarFire SoC family combines a powerful 64-bit 5x core RISC-V Microprocessor Sub-System (MSS) with the FPGA fabric in a single device. Packed with this powerful combination, PolarFire SoC devices offer the scalable features of FPGAs and high-performance of ASICs. Only the FPGA fabric resources vary but the MSS remains the same across PolarFire SoC device variants, making these devices ideal for many applications.

#### Figure 1-8. MSS I/O Block Diagram

There are 38 MSS I/Os that can be configured using the Libero<sup>®</sup> SoC software to interface with various peripherals. See PolarFire SoC Packaging Pin Assignment Table for the pinout information of the MSS pins. The pinout provides multiple options on where the MSS peripherals can be connected. The following interfaces are configured using the software.

- CAN Controller (x2)

- I2C (x2)

- MMUART (x5)

- SPI (x2)

- Quad SPI with XIP

- Gigabit Ethernet MAC (GEM x2)

- eMMC SD/SDIO

- Universal Serial Bus OTG Controller (USB)

- DDR Controller

- GPIO

#### 1.3.3 Supply Pins

The following table lists multiple power supply pins required for proper device operation. For more information about unused conditions and power sequence, see UG0901: PolarFire SoC FPGA Board Design Guidelines User Guide.

| Name                    | Description                                          | Operating Voltage             |

|-------------------------|------------------------------------------------------|-------------------------------|

| XCVR_VREF               | Voltage reference for transceiver                    | 0.9 V/1.25 V                  |

| VDD_XCVR_CLK            | Power for transceiver reference clock input buffers  | 2.5 V/3.3 V                   |

| VDDA25                  | Transceiver PLL power                                | 2.5 V                         |

| VDDA                    | Power for transceiver Tx and Rx lanes 0, 1, 2, and 3 | 1.0 V/1.05 V                  |

| VSS                     | Core digital ground                                  | NA                            |

| VDD                     | Device core digital supply                           | 1.0 V/1.05 V                  |

| VDDIx (JTAG Bank)       | Supply for I/O circuits in a bank                    | 1.8 V/2.5 V/3.3 V             |

| VDDIx (GPIO Banks)      | Supply for I/O circuits in a bank                    | 1.2 V/1.5 V/1.8 V/2.5 V/3.3 V |

| VDDIx (MSSIO Banks)     | Supply for MSS I/O circuits in a bank                | 1.2 V/1.5 V/1.8 V/2.5 V/3.3 V |

| VDDIx (MSS SGMII Banks) | Supply for MSS SGMII circuits in a bank              | 2.5 V/3.3 V                   |

| VDDIx (MSS DDR Bank)    | Supply for MSS DDR circuits in a bank                | 1.2 V/1.5 V/1.8 V             |

| VDDIx (HSIO Banks)      | Supply for HSIO I/O circuits in a bank               | 1.2 V/1.5 V/1.8 V             |

#### Table 1-3. Supply Pins

#### 1.3.3.1 Packaging Decoupling Capacitors

PolarFire SoC 0.8 mm and 1.0 mm pitch packages contain decoupling capacitors to support high-speed I/O operation.

Small, low-profile CSP packages (0.5 mm ball pitch, 16 mm × 16 mm, and smaller) do not have package decoupling capacitors.

The following table lists the packaging decoupling capacitors contained in non-CSP packages.

Table 1-4. Decoupling Capacitor per Die-Package

| Supply<br>Name | Bank No./IO Type                | Capacitor<br>Rating | FC1152, 35 x<br>35 mm,<br>1.0 mm |              | FC784, 23 x 23 mm,<br>0.8 mm |              |              | FCV484, 19 x 19 mm, 0.8<br>mm |                  |                  | ı, 0.8           |

|----------------|---------------------------------|---------------------|----------------------------------|--------------|------------------------------|--------------|--------------|-------------------------------|------------------|------------------|------------------|

|                |                                 |                     | MPFS<br>450T                     | MPFS<br>250T | MPFS<br>250T                 | MPFS<br>150T | MPFS<br>095T | MPF<br>250T                   | MPF<br>S150<br>T | MPF<br>S095<br>T | MPF<br>S025<br>T |

| VDDA           | SERDES Power                    | 4.7 nF              | 1                                | 1            | 1                            | 1            | 1            | 1                             | 1                | 1                | 1                |

| VDDA           | SERDES Power                    | 2.2 nF              | 1                                | 1            | 1                            | 1            | 1            | —                             | _                | —                | —                |

| VDDA           | SERDES Power                    | 1.5 nF              | 1                                | 1            | 1                            | 1            | 1            | _                             | _                | _                | _                |

| VDDA           | SERDES Power                    | 1.0 nF              | 1                                | 1            | 1                            | 1            | 1            | 1                             | 1                | 1                | 1                |

| VDDI0          | Bank 0/HSIO Bank<br>Power       | 1.0 µF              | 1                                | 1            | 1                            | 1            | 1            | _                             |                  |                  |                  |

| VDDI8          | Bank 8/HSIO Bank<br>Power       | 1.0 µF              | 1                                | 1            | 1                            | 1            | 1            | _                             |                  |                  |                  |

| VDDI6          | Bank 6/HSIO - DDR<br>Bank Power | 1.0 µF              | 1                                | 1            | 1                            | 1            | 1            | _                             |                  |                  |                  |

| VDD18          | HSIO/MSS_DDR<br>Input Power     | 1.0 µF              | 1                                | 1            | 1                            | 1            | 1            | _                             |                  | _                | —                |

| VDDI1          | Bank 1/GPIO Bank<br>Power       | 1.0 µF              | 1                                | 1            | 1                            | 1            | 1            |                               |                  |                  |                  |

| con            | tinued                                        |                     |                                  |              |                              |              |              |                               |                  |                  |                  |

|----------------|-----------------------------------------------|---------------------|----------------------------------|--------------|------------------------------|--------------|--------------|-------------------------------|------------------|------------------|------------------|

| Supply<br>Name | Bank No./IO Type                              | Capacitor<br>Rating | FC1152, 35 x<br>35 mm,<br>1.0 mm |              | FC784, 23 x 23 mm,<br>0.8 mm |              |              | FCV484, 19 x 19 mm, 0.8<br>mm |                  |                  | ı, 0.8           |

|                |                                               |                     | MPFS<br>450T                     | MPFS<br>250T | MPFS<br>250T                 | MPFS<br>150T | MPFS<br>095T | MPF<br>250T                   | MPF<br>S150<br>T | MPF<br>S095<br>T | MPF<br>S025<br>T |

| VDDI9          | Bank 9/GPIO Bank<br>Power                     | 1.0 µF              | 1                                | 1            | 1                            | 1            | 1            | —                             | _                | —                |                  |

| VDDI7          | Bank 7/GPIO Bank<br>Power                     | 1.0 µF              | 1                                | 1            | 1                            | 1            | 1            | _                             |                  |                  |                  |

| VDDI2          | Bank 2/MSSIO Bank<br>Power                    | —                   |                                  |              | —                            | —            | —            | _                             |                  | —                | —                |

| VDDI4          | Bank 4/MSSIO Bank<br>Power                    | —                   |                                  |              |                              |              |              | _                             |                  |                  |                  |

| VDDI5          | Bank-5/MSS SGMII<br>Bank Power,<br>Pre-Driver |                     |                                  |              | _                            | —            |              |                               |                  |                  | —                |

| VDD25          | PGM, PLL Power                                | 1.0 µF              | 1                                | 1            | 1                            | 1            | 1            | _                             | _                | _                | _                |

| VDD            | Core Power                                    | 2.2 µF              | 1                                | 1            | 1                            | 1            | 1            | —                             | —                | —                | —                |

| Total Num      | ber of Capacitors                             |                     | 13                               | 13           | 13                           | 13           | 13           | 2                             | 2                | 2                | 2                |

Note: FCSG536 and FCSG325 do not have package capacitors.

#### 1.3.4 Memory Interface

Valid locations for DDR memory interfaces are shown in PolarFire SoC Packaging Pin Assignment Table. By using Libero SoC, all individual DDR interface pins are identified from the DDR macro. For more information about the memory interface, see UG0906: PolarFire SoC FPGA DDR Memory Controller User Guide.

#### 1.3.5 DDR Interface

The DDR subsystems are hardened ASIC blocks for interfacing the LPDDR3, LPDDR4, DDR3, and DDR4 memories. It supports 16-bit, 32-bit, and 64-bit data bus width modes with ECC support. The DDRIO uses fixed impedance calibration for different drive strengths. These values are programmed using Libero SoC software for the selected I/O standard. The values are fed to the pull-up or pull-down reference network to match the impedance with an external resistor. For more information about DDR signals, see UG0906: PolarFire SoC FPGA DDR Memory Controller User Guide.

#### 1.3.6 Clocking Pins

CCC blocks, located at each corner of the PolarFire SoC FPGAs, contain two PLLs and two DLLs that provide flexible on-chip and off-chip clock management and synthesis capabilities. CCCs are labeled according to their locations in the core. For example, the CCC located in the northeast corner is labeled as CCC\_NE. For more information about clocking pins, see UG0913: PolarFire SoC FPGA Clocking Resources User Guide.

Preferred clock inputs (CLKIN) are located on three sides of the device, with eight preferred clock inputs on the west side, twelve on the north side, and either 12 or 16 inputs on the south side, depending on the package. For more information about clocking pin names, descriptions, and operating voltages, see Table 1-3

#### 1.3.7 Dedicated I/O Bank Pins

JTAG, SPI, and DEVRST\_N signals share the same Bank 3 supply and are not directly available to the fabric. SPI IOs are, however, dynamically switched over to be used by the fabric whenever the PolarFire SoC controller is not using them. Dedicated I/O bank supplies must be powered up higher than their operational threshold and enabled before the PolarFire SoC controller negates the main power-on reset to the fabric. Table 1-5, Table 1-6, and Table 1-7

list the JTAG, SPI, and DEVRST\_N pin names and descriptions. Libero configures unused user I/O as input buffer disabled, and output buffer tri-stated with weak pull-up.

For more information about unused conditions and power sequence, see UG0901: PolarFire SoC FPGA Board Design Guidelines User Guide.

The JTAG bank voltages can be set to operate at 1.8 V, 2.5 V, or 3.3 V. The following table lists the JTAG pins.

#### Table 1-5. JTAG Pins

| Pin Names | Direction | Weak Pull-Up/Unused<br>Condition | Description                                                                                          |

|-----------|-----------|----------------------------------|------------------------------------------------------------------------------------------------------|

| TMS       | Input     | Yes/DNC                          | JTAG test mode select                                                                                |

| TRSTB     | Input     | Yes <sup>1</sup>                 | JTAG test reset. Must be held low during device operation                                            |

| TDI       | Input     | Yes/DNC                          | JTAG test data in<br>In ATPG or Test mode, when using a 4-bit TDI bus, this I/O is<br>used as TDI[0] |

| ТСК       | Input     | No <sup>2</sup>                  | JTAG test clock                                                                                      |

| TDO       | Output    | No/DNC                           | JTAG test data out                                                                                   |

**Note:** 1. If TRSTB is unused and in the Avionics mode, either an external 1 kW pull-down resistor should be connected to it, to override the weak internal pull-up or it should be driven low from the external source.

Note: 2. In unused condition, must be connected to VSS through 10 kW resistor.

#### Table 1-6. Device Reset Pins

| Name     | Direction | Weak Pull-up | Description                 |

|----------|-----------|--------------|-----------------------------|

| DEVRST_N | Input     | 22 kΩ        | Device reset (asserted low) |

#### Table 1-7. SPI Interface Pins

| Name        | Direction             | Description                                                                                                                                                                                                                                                                  |

|-------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK         | Bi-directional        | SPI clock                                                                                                                                                                                                                                                                    |

| SS          | <b>Bi-directional</b> | SPI slave select                                                                                                                                                                                                                                                             |

| SDI         | Input                 | SDI input for the shared SPI interface                                                                                                                                                                                                                                       |

| SDO         | Output                | SDO output for the shared SPI interface                                                                                                                                                                                                                                      |

| SPI_EN      | Input                 | Pulled up or down through a resistor or driven dynamically from an external source to enable or tri-state the SPI I/O                                                                                                                                                        |

| IO_CFG_INTF | Input                 | <ul><li>Pulled up or down through a resistor or driven dynamically from an external source to indicate whether the shared SPI interface is a master or a slave. Dedicated to the system controller.</li><li>0: SPI slave interface</li><li>1: SPI master interface</li></ul> |

#### Table 1-8. Special Pins

| Name | Direction | Description                                                                                                                                                                                   |

|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC   | —         | No connect pin. This pin indicates that it is not connected within the circuitry. NC pins can be driven by any voltage or can be left floating with no effect on the operation of the device. |

| continue      | continued |                                                                                                                                         |  |  |  |  |  |  |

|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Name          | Direction | Description                                                                                                                             |  |  |  |  |  |  |

| DNC           | —         | Do not connect pin. DNC pins must not be connected to any signal on the PCB, and they must be left unconnected.                         |  |  |  |  |  |  |

| LPRB_A        | Output    | Specifies an internal signal for probing (oscilloscope-like feature). The two live probe                                                |  |  |  |  |  |  |

| LPRB_B        | Output    | I/O cells function as either of the following:<br>– Live probe<br>– User I/O (HSIO)                                                     |  |  |  |  |  |  |

| FF_EXIT_N     | Input     | Reserved                                                                                                                                |  |  |  |  |  |  |

| Shield Signal | Output    | Shield signal is required for each DDR data byte signal. It must be driven with maximum drive strength to improve the signal integrity. |  |  |  |  |  |  |

#### 1.3.8 XCVR Interface

The transceiver I/O available in the PolarFire SoC devices are dedicated for high-speed serial communication protocols. Libero defined DNC pins are pulled up internally when not used in the Libero design.

For more information about unused conditions and power sequence, see UG0901: PolarFire SoC FPGA Board Design Guidelines User Guide.

The following table lists the XCVR Interface pins and descriptions.

#### Table 1-9. XCVR Interface Pins

| Name             | Direction | Description                                                                          |  |  |

|------------------|-----------|--------------------------------------------------------------------------------------|--|--|

| XCVR_xy_REFCLK_P | Input     | Differential serial reference clock.                                                 |  |  |

| XCVR_xy_REFCLK_N |           | xy - location<br>x - transceiver number (0, 1, 2, 3)<br>y - lane number (0, 1, 2, 3) |  |  |

| XCVR_x_TXy_P     | Output    | Differential serial transmit pins.                                                   |  |  |

| XCVR_x_TXy_N     |           | x - transceiver number (0, 1, 2, 3)<br>y - lane number (0, 1, 2, 3)                  |  |  |

| XCVR_x_RXy_P     | Input     | Differential serial receive pins.                                                    |  |  |

| XCVR_x_RXy_N     |           | x - transceiver number (0, 1, 2, 3)<br>y - lane number (0, 1, 2, 3)                  |  |  |

### 1.4 Package Pinouts

For more information about the pinout, see PolarFire SoC Packaging Pin Assignment Table.

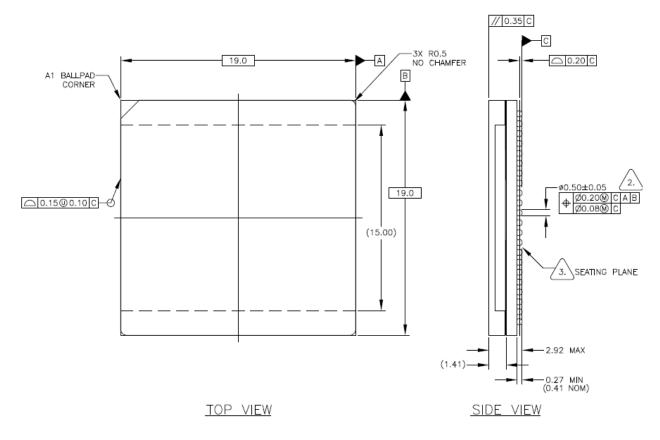

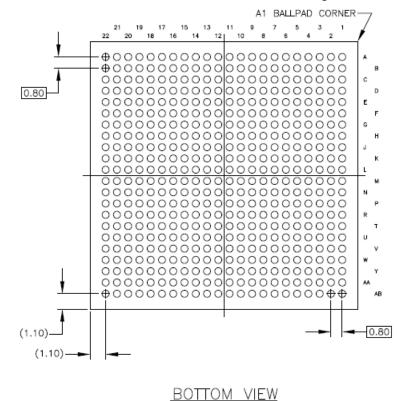

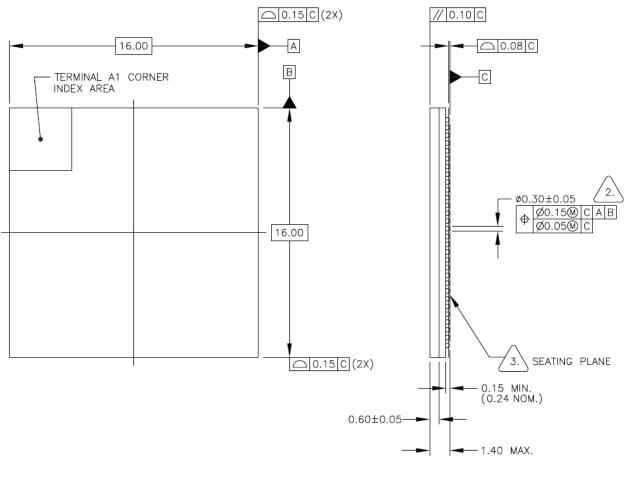

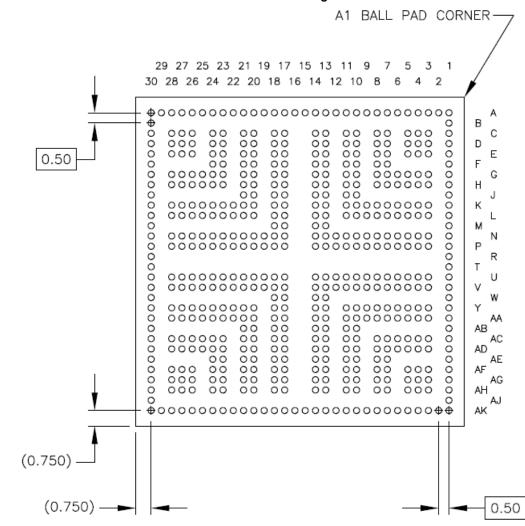

### 1.5 Mechanical Drawings

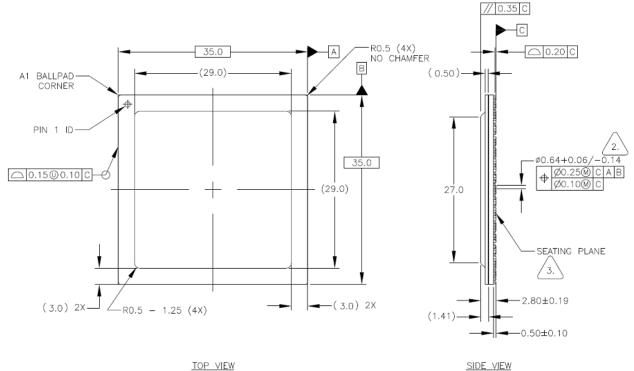

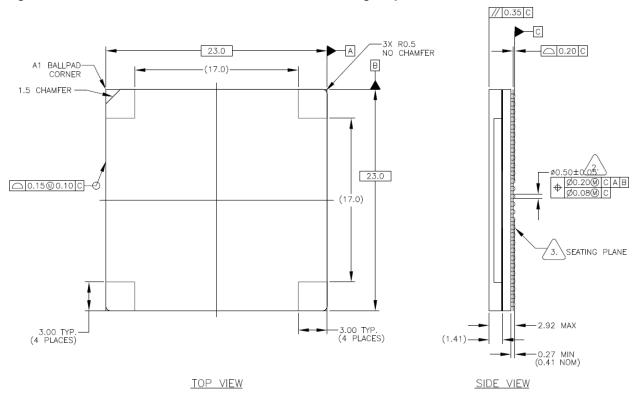

The following illustrations show the top, bottom, and side views, and dimensions for the PolarFire SoC FPGAs.

Figure 1-9. MPFS460T/MPFS250T-FCG1152 Package Top-View and Side-View

TOP VIEW

© 2021 Microchip Technology Inc.

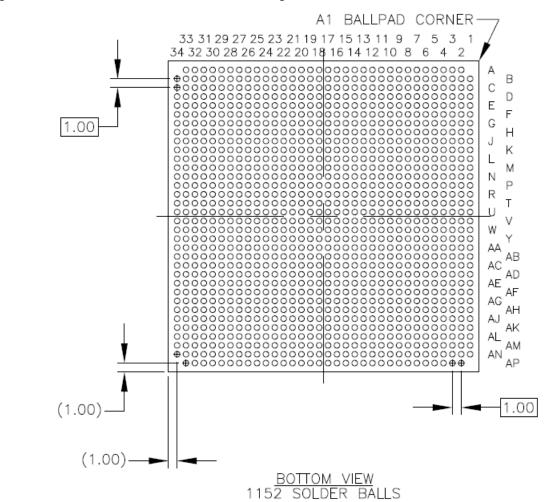

Figure 1-10. MPFS460T/MPFS250T-FCG1152 Package Bottom-View

Figure 1-11. MPFS250T-MPFS160T-MPFS095T-FCVG784 Package Top-View and Side-View

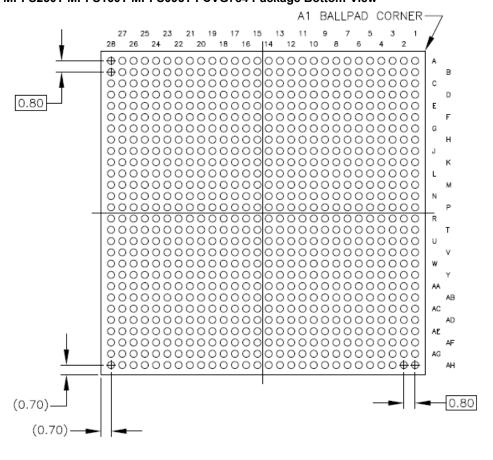

#### Figure 1-12. MPFS250T-MPFS160T-MPFS095T-FCVG784 Package Bottom-View

BOTTOM VIEW 784 SOLDER BALLS

Figure 1-13. MPFS250T/MPFS160T/MPFS095T/MPFS025T - FCVG484 Package Top-View and Side-View

#### Figure 1-14. MPFS250T/MPFS160T/MPFS095T/MPFS025T - FCVG484 Package Bottom-View

484 SOLDER BALLS

Figure 1-15. MPFS250T/MPFS160T/MPFS095T-FCSG536 Package Top-View and Side-View

TOP VIEW

SIDE VIEW

#### Figure 1-16. MPFS250T/MPFS160T/MPFS095T-FCSG536 Package Bottom-View

### BOTTOM VIEW 536 SOLDER BALLS

The following table lists the PolarFire SoC FPGAs Package description and specification.

#### Table 1-10. PolarFire SoC FPGAs Package Information

| Package          | Description        | Package Specifications |            |           |              |

|------------------|--------------------|------------------------|------------|-----------|--------------|

|                  |                    | Package type           | Pitch (mm) | Size (mm) | Maximum I/Os |

| MPFS460T-FCG1152 | Flip-chip with lid | BGA                    | —          | 35 × 35   | —            |

| MPFS250T-FCG1152 | Flip-chip with lid | BGA                    | 1          | 35 × 35   | 512          |

| MPFS250T-FCVG784 | Flip-chip with lid | BGA                    | 0.8        | 23 x 23   | —            |

| MPFS160T-FCVG784 | Flip-chip with lid | BGA                    | 0.8        | 23 x 23   | —            |

| MPFS095T-FCVG784 | Flip-chip with lid | BGA                    | 0.8        | 23 x 23   | —            |

| continued        |                    |                        |            |           |              |

|------------------|--------------------|------------------------|------------|-----------|--------------|

| Package          | Description        | Package Specifications |            |           |              |

|                  |                    | Package type           | Pitch (mm) | Size (mm) | Maximum I/Os |

| MPFS250T-FCVG484 | Flip-chip with lid | BGA                    | 0.8        | 19 × 19   | 284          |

| MPFS160T-FCVG484 | Flip-chip with lid | BGA                    | 0.8        | 19 × 19   | —            |

| MPFS095T-FCVG484 | Flip-chip with lid | BGA                    | 0.8        | 19 x 19   | 280          |

| MPFS250T-FCSG536 | —                  | BGA                    | 0.5        | 16 x 16   | 304          |

| MPFS160T-FCSG536 | —                  | BGA                    | —          | 16 x 16   | —            |

| MPFS095T-FCSG536 | _                  | BGA                    |            | 16 x 16   | _            |

## 2. Package Material Information

The following table lists the PolarFire SoC ball grid array RoHS packages.

Table 2-1. PolarFire SoC Ball Grid Array RoHS Packages

| Package Balls                | FCG1152      | FCVG784      | FCVG484      | FCSG536       |

|------------------------------|--------------|--------------|--------------|---------------|

| Package Pitch                | 1 mm         | 1 mm         | 0.8 mm       | 1 mm          |

| Substrate Material           | Epoxy Glass  | Epoxy Glass  | Epoxy Glass  | Epoxy Glass   |

| Solder Ball Composition RoHS | SAC305       | SAC305       | SAC305       | SAC305        |

| Solder Bump Material         | Sn98.2/Ag1.8 | Sn98.2/Ag1.8 | Sn98.2/Ag1.8 | Copper + SnAg |

**Note:** For all flip-chip BGA packages—Only FCG1152 and FCSG536 are not vented. FCVG784 and FCVG484 are vented.

## Thermal Specifications To be updated. 3.

## Package Marking To be updated. 4.

## 5. Packing and Shipping

The PolarFire SoC series devices are packed in trays, which are used to pack most of the Microchip surface-mount devices. Trays provide excellent protection from mechanical damage. In addition, they are manufactured using the anti-static material to provide limited protection against ESD damage.

### Table 5-1. Standard Device Counts per Tray and Carton

| Package | Maximum Number of<br>Devices per Tray | Maximum Number of Trays<br>per Stack | Maximum Number of Units per<br>Inner Carton |

|---------|---------------------------------------|--------------------------------------|---------------------------------------------|

| FCG1152 | TBD                                   | TBD                                  | TBD                                         |

| FCVG784 | TBD                                   | TBD                                  | TBD                                         |

| FCVG484 | TBD                                   | TBD                                  | TBD                                         |

| FCSG536 | TBD                                   | TBD                                  | TBD                                         |

### 6. Thermal Management

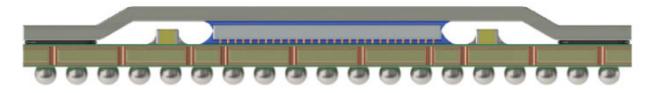

Microchip PolarFire SoC FPGAs are offered in lidded flip-chip BGA (FCBGA) format. Lidded FCBGA features a controlled bond-line thermal interface material (TIM) thickness that reduces the thermal resistance (Theta-JC) between the junction and the externally applied thermal solution. The lid or heat spreader also spreads the heat away from the die to the package perimeter and to the printed circuit board.

Optimized package electrical performance with multiple power and ground planes to take care of signal return paths, and dense core via under the die to improve power delivery adds benefit in dissipating heat through the bottom of the package and to the board.

PolarFire SoC FPGAs in FCVG484 are also available in bare-die FCBGA. Bare-die flip-chip BGA produces the lowest possible thermal resistance (Theta-JC) between the junction and any externally applied thermal solution.

#### Figure 6-1. Heat Spreader with Thermal Interface Material

### 6.1 System Level Heat Sink Solutions

The use of external heat sinks, component placement in the PCB, and air flow in the system depends on the physical and mechanical limitations of the system. A system level thermal design engineer must understand these limitations and device capabilities to effectively manage the complete thermal strategy.

## 7. Thermal Interface Material

When using external heat sinks, a suitable thermal interface material must be considered to effectively transfer the heat from the component to the heat sink, and eventually to the environment.

For bare-die flip-chip BGAs, the surface of the silicon contacts the heat sink. For lidded flip-chip BGAs, the lid contacts the heat sink. The surface size of the bare-die flip-chip BGAs and lidded flip-chip BGAs are different. Microchip recommends a different type of thermal material for long-term use with each type of flip-chip BGA's package.

For lidded flip-chip BGAs, the lid contacts the external heat sink while bare-die flip-chip BGAs, the surface of the silicon contacts the external heat sink. The surface areas of lidded flip-chip BGAs and bare-die flip-chip BGAs are different. The system level thermal design engineer must choose the appropriate TIM to be used.

Thermal interface material is required because the surfaces of the PolarFire SoC package and the heat sinks base are not smooth. The surface roughness reduces the effective contact area between the package and the heat sinks base. The insulating air gaps created by voids between contacting surfaces are too large. The thermal interface materials fill these gaps and allow an effective conductive transfer of heat from the package to the external heat sink.

The selection of the appropriate thermal interface material is critical to ensure the lowest thermal contact resistance. One must consider the thermal conductivity of the TIM:

- The flatness of the surface contact areas

- The applied pressure on the thermal interface material

- The total thermal contact area.

In addition to thermal performance, TIMs are selected based on the ease of use in assembly and long-term reliability.

### 7.1 Heat Sink Attachments

There are six main methods for heat sink attachment. The following table lists their advantages and disadvantages.

- Thermal tape

- · Thermally conductive adhesive

- Wire form Z-clips

- Plastic clip-ons

- · Threaded stand-offs (PEMs) and compression springs

- Push-pins and compression springs

- Thermal compound (also called as thermal gel, thermal grease, thermal paste, heat-sink paste, or heat-sink compound)

## 8. Heat Sink Removal Procedure

The heat spreader on the package provides mechanical protection for the die and serves as the primary heat dissipation path. It is attached with an epoxy adhesive to provide the necessary adhesion strength to hold the package together. For an application in which an external heat sink subjects the lid adhesion joint to continuous tension or shear, extra support might be required.

If the removal of an attached external heat sink subjects the joint to tension, torque, or shear, care should be exercised to ensure that the lid itself does not come off. In such cases, it is recommended to use a small metal blade or metal wire to break the lid to heat sink joint from the corners and carefully pry the heat sink off. The initial cut should reach far enough so the blade has leverage to exert upward pressure against the heat sink. Contact the heat sink and heat sink adhesive manufacturer for more specific recommendations on heat sink removal.

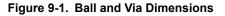

## 9. Recommended PCB Design Rules for BGA Packages

Microchip provides the diameter of a land pad on the package side. This information is required before starting the board layout so the board pads can be designed to match the component-side land geometry. The typical values of these land pads are shown in the following figure and summarized in Table 9-1. For Microchip BGA packages, Non-Solder Mask Defined (NSMD) pads on the board are suggested to allow a clearance between the land metal (diameter) and the solder mask opening (diameter) as shown in the following figure.

The space between the NSMD pad and the solder mask, the actual signal trace widths, and via dimensions depend on the capability of the PCB vendor. The cost of the PCB is higher when the line width and spaces are smaller.

Table 9-1. Recommended PCB Design Rules

| Design Rule for Packages               | 0.8 mm Pitch | 1.0 mm Pitch | 0.5 mm Pitch |

|----------------------------------------|--------------|--------------|--------------|

|                                        | FCVG         | FCG          | FCSG         |

| Ball Pad diameter                      | 0.5 mm       | 0.6 mm       | 0.35 mm      |

| Ball Pad opening                       | 0.4 mm       | 0.5 mm       | 0.275 mm     |

| Solder Ball pitch                      | 0.8 mm       | 1.00 mm      | 0.50 mm      |

| Line width between via and solder land | —            | —            | —            |

| Distance between via and solder land   | —            | —            | —            |

| Via finished hole diameter             | —            | —            | —            |

| Via plating diameter                   | _            | —            | —            |

**Note:** For more information about package fanout, see *PolarFire SoC FPGA Package Fanout Application Note* (yet to be published).

## 10. Moisture Sensitive Level (MSL)

The following table lists MSL of Microchip PolarFire SoC packages'. For more information about solder re-flow guidelines for Sn/Pb and Pb-free, see https://www.microsemi.com/company/quality/soldering-profiles.

### Table 10-1. Moisture Sensitive Levels

| Package | MSL |

|---------|-----|

| FCG1152 | 4   |

| FCVG784 | 4   |

| FCVG484 | 4   |

| FCSG536 | 3   |

### 11. Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most— current publication.

### 11.1 Revision B

The following is a summary of the changes made in revision B of this document.

- Updated Table 1-1

- Updated 1.3.1.1 Supported I/O Features

- Updated Table 1-4

- Updated Table 1-5

- Updated 1.5 Mechanical Drawings

- Updated Table 1-10

- Updated Table 2-1

- Updated Table 9-1

- Updated Table 10-1

### 11.2 Revision A

The following is a summary of the changes made in revision A of this document.

- Updated Table 1-1

- Updated Table 1-2

- Updated Table 1-3

- Updated Table 1-6

### 11.3 Revision 2.0

The following is a summary of the changes made in revision 2.0 of this document.

- Updated 1.3.2 MSS I/Os. Added refer to PolarFire SoC Packaging Pin Assignment Table for the pin out information for the MSS pins.

- Deleted Unused Condition columns from all the details. Added refer to UG0901: PolarFire SoC FPGA Board Design Guidelines User Guide.

- Added LPDDR4 memory in 1.3.5 DDR Interface.

- Updated 1.3.7 Dedicated I/O Bank Pins. Added UG0901: PolarFire SoC FPGA Board Design Guidelines User Guide.

- Updated 1.3.8 XCVR Interface. Added UG0901: PolarFire SoC FPGA Board Design Guidelines User Guide.

### 11.4 Revision 1.0

The first publication of this document.

## The Microchip Website

Microchip provides online support via our website at www.microchip.com/. This website is used to make files and information easily available to customers. Some of the content available includes:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- **General Technical Support** Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- **Business of Microchip** Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## Product Change Notification Service

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

# **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- · Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

## **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- · Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code

protection does not mean that we are guaranteeing the product is "unbreakable." Code protection is constantly

evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act.

If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue

for relief under that Act.

## Legal Notice

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUENTIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

<sup>©</sup> 2021, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-8305-2

# **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

| MERICAS                  | ASIA/PACIFIC                              | ASIA/PACIFIC                              | EUROPE                                    |

|--------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|

|                          |                                           |                                           |                                           |

| Corporate Office         | Australia - Sydney<br>Tel: 61-2-9868-6733 | India - Bangalore<br>Tel: 91-80-3090-4444 | Austria - Wels<br>Tel: 43-7242-2244-39    |

|                          |                                           | India - New Delhi                         |                                           |

| Chandler, AZ 85224-6199  | China - Beijing                           |                                           | Fax: 43-7242-2244-393                     |

| el: 480-792-7200         | Tel: 86-10-8569-7000                      | Tel: 91-11-4160-8631                      | Denmark - Copenhager                      |

| ax: 480-792-7277         | China - Chengdu                           | India - Pune                              | Tel: 45-4485-5910                         |

| echnical Support:        | Tel: 86-28-8665-5511                      | Tel: 91-20-4121-0141                      | Fax: 45-4485-2829                         |

| ww.microchip.com/support | China - Chongqing                         | Japan - Osaka<br>Tel: 81-6-6152-7160      | Finland - Espoo                           |

| Veb Address:             | Tel: 86-23-8980-9588                      |                                           | Tel: 358-9-4520-820                       |

| /ww.microchip.com        | China - Dongguan                          | Japan - Tokyo                             | France - Paris                            |

| tlanta                   | Tel: 86-769-8702-9880                     | Tel: 81-3-6880- 3770                      | Tel: 33-1-69-53-63-20                     |

| uluth, GA                | China - Guangzhou                         | Korea - Daegu                             | Fax: 33-1-69-30-90-79                     |

| el: 678-957-9614         | Tel: 86-20-8755-8029                      | Tel: 82-53-744-4301                       | Germany - Garching                        |

| ax: 678-957-1455         | China - Hangzhou                          | Korea - Seoul                             | Tel: 49-8931-9700                         |

| ustin, TX                | Tel: 86-571-8792-8115                     | Tel: 82-2-554-7200                        | Germany - Haan                            |

| el: 512-257-3370         | China - Hong Kong SAR                     | Malaysia - Kuala Lumpur                   | Tel: 49-2129-3766400                      |

| oston                    | Tel: 852-2943-5100                        | Tel: 60-3-7651-7906                       | Germany - Heilbronn<br>Tel: 49-7131-72400 |

| /estborough, MA          | China - Nanjing                           | Malaysia - Penang                         |                                           |

| el: 774-760-0087         | Tel: 86-25-8473-2460                      | Tel: 60-4-227-8870                        | Germany - Karlsruhe                       |

| ax: 774-760-0088         | China - Qingdao                           | Philippines - Manila                      | Tel: 49-721-625370                        |

| chicago                  | Tel: 86-532-8502-7355                     | Tel: 63-2-634-9065                        | Germany - Munich                          |

| asca, IL                 | China - Shanghai                          | Singapore                                 | Tel: 49-89-627-144-0                      |

| el: 630-285-0071         | Tel: 86-21-3326-8000                      | Tel: 65-6334-8870                         | Fax: 49-89-627-144-44                     |

| ax: 630-285-0075         | China - Shenyang                          | Taiwan - Hsin Chu                         | Germany - Rosenheim                       |

| allas                    | Tel: 86-24-2334-2829                      | Tel: 886-3-577-8366                       | Tel: 49-8031-354-560                      |

| ddison, TX               | China - Shenzhen                          | Taiwan - Kaohsiung                        | Israel - Ra'anana                         |

| el: 972-818-7423         | Tel: 86-755-8864-2200                     | Tel: 886-7-213-7830                       | Tel: 972-9-744-7705                       |

| ax: 972-818-2924         | China - Suzhou                            | Taiwan - Taipei                           | Italy - Milan                             |

| etroit                   | Tel: 86-186-6233-1526                     | Tel: 886-2-2508-8600                      | Tel: 39-0331-742611                       |

| ovi, MI                  | China - Wuhan                             | Thailand - Bangkok                        | Fax: 39-0331-466781                       |

| el: 248-848-4000         | Tel: 86-27-5980-5300                      | Tel: 66-2-694-1351                        | Italy - Padova                            |

| ouston, TX               | China - Xian                              | Vietnam - Ho Chi Minh                     | Tel: 39-049-7625286                       |

| el: 281-894-5983         | Tel: 86-29-8833-7252                      | Tel: 84-28-5448-2100                      | Netherlands - Drunen                      |

| Idianapolis              | China - Xiamen                            |                                           | Tel: 31-416-690399                        |

| oblesville, IN           | Tel: 86-592-2388138                       |                                           | Fax: 31-416-690340                        |

| el: 317-773-8323         | China - Zhuhai                            |                                           | Norway - Trondheim                        |

| ax: 317-773-5453         | Tel: 86-756-3210040                       |                                           | Tel: 47-72884388                          |

| el: 317-536-2380         |                                           |                                           | Poland - Warsaw                           |

| os Angeles               |                                           |                                           | Tel: 48-22-3325737                        |

| ission Viejo, CA         |                                           |                                           | Romania - Bucharest                       |

| el: 949-462-9523         |                                           |                                           | Tel: 40-21-407-87-50                      |

| ax: 949-462-9608         |                                           |                                           | Spain - Madrid                            |

| el: 951-273-7800         |                                           |                                           | Tel: 34-91-708-08-90                      |

| aleigh, NC               |                                           |                                           | Fax: 34-91-708-08-91                      |

| el: 919-844-7510         |                                           |                                           | Sweden - Gothenberg                       |

| ew York, NY              |                                           |                                           | Tel: 46-31-704-60-40                      |

| el: 631-435-6000         |                                           |                                           | Sweden - Stockholm                        |

| an Jose, CA              |                                           |                                           | Tel: 46-8-5090-4654                       |

| el: 408-735-9110         |                                           |                                           | UK - Wokingham                            |

| el: 408-436-4270         |                                           |                                           | Tel: 44-118-921-5800                      |

| anada - Toronto          |                                           |                                           | Fax: 44-118-921-5820                      |

| el: 905-695-1980         |                                           |                                           |                                           |

| ax: 905-695-2078         |                                           |                                           |                                           |