# **Fusion Security**

## **Table Of Contents**

| Introduction to Security in Fusion       1         Fusion Security Features       2         AES Encryption of Programming Files       2         FlashLock       4 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security In Action                                                                                                                                                |

| Application 2: Nontrusted Environment – Unsecured Location                                                                                                        |

| Fusion FlashROM Security Use Models                                                                                                                               |

| Generation of Programming Files with AES Encryption – Application 3       15         Generated Programming File Header Definition       16                        |

| Conclusion         17           Glossary         17                                                                                                               |

| References    17      Related Documents    17                                                                                                                     |

| List of Changes                                                                                                                                                   |

## Introduction to Security in Fusion

The need for security on field programmable gate array (FPGA) programmable logic devices has never been greater than today. If the contents of the FPGA can be read by an external source, the intellectual property (IP) of the system is vulnerable to unauthorized copying. Microsemi Fusion<sup>®</sup> devices contain state-of-the-art circuitry to make the Flash-based devices secure during and after programming. The new Fusion Flash FPGAs consist of an FPGA array core, FlashROM and Flash Memory Blocks (FBs). The FlashROM and the FPGA core fabric can be securely programmed independently of each other, allowing the FlashROM to be updated without changing the FPGA core fabric. The FlashROM, the FBs, and the FPGA core fabric can be securely programmed independently of each other, allowing the FPGA core fabric can be securely programmed independently of each other, allowing the FPGA core fabric can be securely programmed independently of each other, allowing the FPGA core fabric can be securely programmed independently of each other, allowing the FPGA core fabric can be securely programmed independently of each other, allowing the FPGA core fabric can be securely programmed independently of each other, allowing the FPGA core fabric can be securely programmed independently of each other, allowing the FPGA core fabric.

Microsemi has incorporated the advanced encryption standard (AES) decryption core into the new Fusion devices and has also included the Microsemi flash-based lock technology (FlashLock<sup>®</sup>). Together, they provide leading-edge security in a programmable logic device. Configuration data loaded into Fusion can be decrypted prior to being written to the FPGA core using the AES 128-bit block cipher standard. The AES encryption key is stored in on-chip, nonvolatile Flash memory.

Fusion devices have been designed with the most comprehensive programming logic design security in the industry. In the architecture of Fusion devices, security has been designed into the very fabric. The Flash cells are located beneath seven metal layers, and the use of many device design and layout techniques makes invasive attacks difficult. Since device layers cannot be removed without disturbing the charge on the programmed (or erased) Flash gates, devices cannot be easily deconstructed to decode the design. Fusion is unique in being re-programmable and having inherent resistance to both invasive attacks on valuable IP. Secure remote in-system programming (ISP) is now

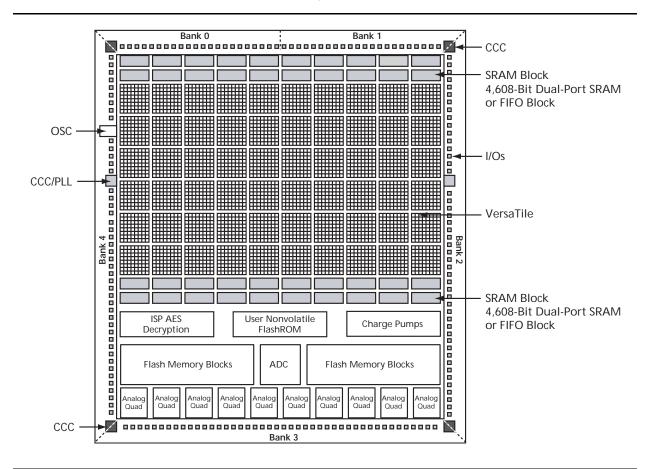

possible with AES encryption capability for the programming file during electronic transfer. Figure 1 shows a view of the AES decryption core inside Fusion devices, which is used to decrypt the encrypted programming file when programming.

This application note outlines the security features offered in Fusion devices, some applications and uses, as well as the different software settings for each application.

Figure 1 • Block Representation of the AES Decryption Core in an AFS600 FPGA Fusion

# **Fusion Security Features**

Consider Fusion devices as containing three entities: FlashROM, FBs, and the FPGA core fabric. These parts can be programmed or updated independently with a STAPL programming file. The programming files can be AES-encrypted or plain text. This allows maximum flexibility in providing security to the entire device. See the *AC236: Fusion FlashROM* application note for the FlashROM structure.

Unlike SRAM-based FPGA devices, which require a separate boot PROM to store programming data, Fusion devices are non-volatile, and the secured configuration data is stored in on-chip Flash cells that are part of the FPGA fabric. Once programmed, this data is an inherent part of the FPGA array and does not need to be loaded at system power-up. SRAM-based FPGAs load the configuration bitstream upon power-up; therefore, the configuration is exposed and can be read easily.

The built-in FPGA core, FB, and FlashROM support programming files encrypted with the 128-bit AES (FIPS-192) block ciphers. The AES key is stored in dedicated, on-chip Flash memory and can be programmed before the device is shipped to other parties (allowing secure remote field updates).

## AES Encryption of Programming Files

Fusion devices employ AES as part of the security mechanism that prevents invasive and noninvasive attacks. The mechanism entails encrypting the programming file with AES encryption then passing the programming file through the AES decryption core, which is embedded in the device. The file is decrypted there, and the device is successfully programmed.

The AES key is protected by a FlashLock security Pass Key that is also implemented in Fusion devices. This FlashLock Pass Key technology is exclusive to the Microsemi Flash-based device families. FlashLock Pass Key technology can also be implemented without the AES encryption option, providing a choice of different security levels.

In essence, security features can be categorized into the following three options:

- AES encryption with FlashLock Pass Key protection

- FlashLock protection only (no AES encryption)

- No protection

Each of the above options will be explained in more detail in the following sections with application examples and software implementation options.

#### Advanced Encryption Standard

AES is a cryptographic algorithm that complies with Federal Information Processing Standard (FIPS) Publication 192, used by U.S. government organizations to protect sensitive, unclassified information.

Microsemi has implemented the 128-bit AES (Riindael) algorithm in Fusion devices. With this key size. there are approximately 3.4 ×10<sup>38</sup> possible 128-bit keys. The DES standard has a 56-bit key size, which provides approximately 7.2 × 10<sup>16</sup> possible keys. In their AES fact sheet, the National Institute of Standards and Technology (NIST) uses the following hypothetical example to illustrate the theoretical security provided by AES. If one were to assume that a computing system existed that could recover a DES key in a second, it would take that same machine approximately 149 trillion years to crack a 128-bit AES key. NIST continues to make their point by stating the universe is believed to be less than 20 billion vears old.1

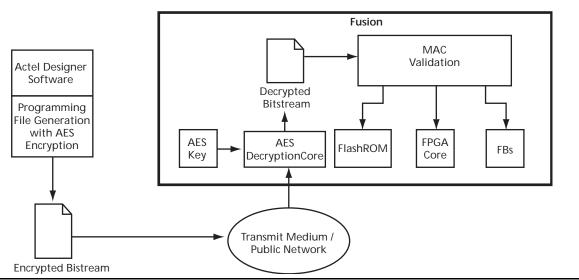

The AES key is securely stored on-chip in dedicated Fusion Flash memory and cannot be read out. In the first step, the AES key is generated and programmed into the device (for example, at a secure or trusted programming site). The Microsemi Designer software tool provides AES key generation capability. After the key has been programmed into the device, the device will only correctly decrypt programming files that have been encrypted with the same key. If the individual programming file content is incorrect, a Message Authentication Control (MAC) mechanism inside the device will fail in authenticating the programming file. In other words, when an encrypted programming file is being loaded into a device that has a different programmed AES key, the MAC will prevent this incorrect data from being loaded, preventing possible device damage. See Figure 2 on page 4 for a graphical representation of this process.

It is important to note that the user decides what level of protection will be implemented for the device. When AES protection is desired, the FlashLock Pass Key must be set. The AES key is a content protection mechanism, whereas the FlashLock Pass Key is a device protection mechanism. When the AES key is programmed into the device, the device still needs the Pass Key to protect the FPGA and FlashROM contents and the security settings, including the AES key. Using the FlashLock Pass Key prevents modification of the design contents by means of simply programming the device with a different AES key.

1. National Institute of Standards and Technology, "ADVANCED ENCRYPTION STANDARD (AES) Questions, and Answers," 28 January 2002, <a href="http://csrc.nist.gov/groups/STM/cavp/documents/aes/aesval.html">http://csrc.nist.gov/groups/STM/cavp/documents/aes/aesval.html</a> (10 January 2005).

#### **AES Decryption in Fusion Devices**

Fusion has a built-in 128-bit AES decryption core, which decrypts the encrypted programming file and performs a MAC check that authenticates the file prior to programming. This will ensure the following:

- · Correct decryption of the encrypted programming file

- Prevention of erroneous or corrupted data being programmed during the programming file transfer

- Correct bitstream passed to the device for decryption

Figure 2 shows the use of AES in the Fusion.

Figure 2 • Example Application Scenario Using AES in Fusion Devices Fusion

#### FlashLock

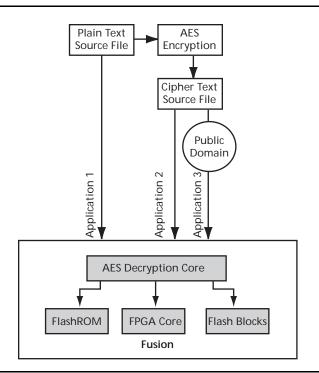

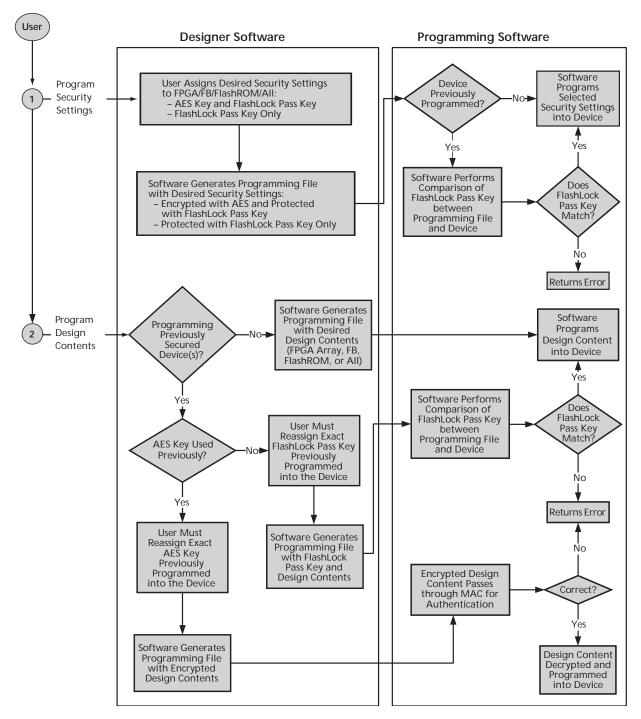

The 128-bit Flash-based FlashLock feature in Fusion works via a key mechanism. The user locks or unlocks the device with a user-defined FlashLock Pass Key. When the device is locked, there is no access to the FPGA without the correct FlashLock Pass Key. By default, functions such as device write, verify, and erase are disabled. Figure 3 on page 5 shows the application scenarios and the corresponding security settings selected during the programming file generation step.

# **Security In Action**

Figure 3 shows some applications of the security advantages of Fusion devices.

Figure 3 • Security Options in Fusion

### **Application 1: Trusted Environment**

As shown in Figure 4 on page 6, this application allows the programming of devices at design locations where research and development take place. Therefore, encryption is not necessary and is optional to the user. This is often a secure way to protect the design, since the design program files are not sent elsewhere. In situations where production programming is not available at the design location, programming centers (such as Microsemi in-house programming) provide a way of programming designs at an alternative, secure, and trusted location. In this scenario, the user will generate a STAPL programming file from the Designer software in plain text format containing information on the entire design or the portion of the design to be programmed. The user can choose to employ the FlashLock Pass Key feature with the design. Once the design is programmed to unprogrammed devices, the design will be protected by this FlashLock Pass Key.

### Application 2: Nontrusted Environment – Unsecured Location

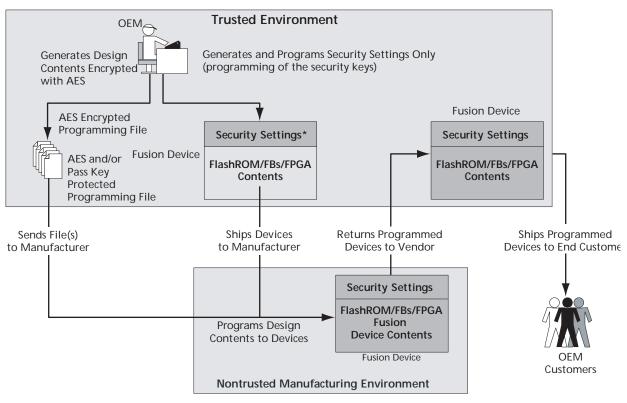

Often, programming of the devices is not performed in the same location as actual design implementation to reduce manufacturing cost. Overseas programming centers and contract manufacturers are examples of this scenario.

To achieve security in this case with Fusion, the AES key and the FlashLock Pass Key can be initially programmed in-house (trusted environment). This is done by generating a programming file with only the security settings and no design contents. The design FPGA core, and/or FlashROM, and/or FB contents are generated in a separate programming file. This programming file must be set with the same AES key that was used to program to the device previously so the device will correctly decrypt this encrypted programming file. As a result, the encrypted design content programming file can be safely sent off-site to nontrusted programming locations for design programming. Figure 4 shows a more detailed flow for this application.

Note: \*Programmed portion indicated with gray.

Figure 4 • Implementing Device Programming in a Nontrusted Environment Fusion

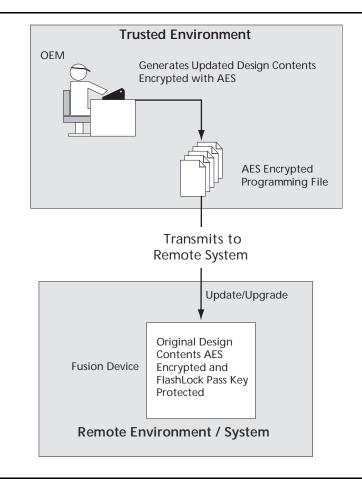

## Application 3: Nontrusted Environment – Field Updates/Upgrades

Programming or reprogramming of devices may occur at remote locations. Reconfiguration of devices in consumer products/equipment through public networks is one example. Typically, the remote system is already programmed with particular design contents. When design update (FPGA array contents update) and/or data upgrade (FlashROM and/or FB contents upgrade) is necessary, an updated programming file with AES encryption can be generated, sent across public networks, and transmitted to the remote system. Reprogramming can then be done using this AES-encrypted programming file, providing easy and secure field upgrades. Fusion devices support this secure ISP using AES. The detailed flow for this application is shown in Figure 5.

To prepare devices for this scenario, the user can initially generate a programming file with the available security setting options. This programming file is programmed into the devices before shipment. Microsemi recommends that the programming file use encryption with an AES key, especially when ISP is done via public domain.

Figure 5 • Remote Update in Nontrusted Environment – Field Updates/Upgrades Fusion

# Fusion FlashROM Security Use Models

Each of the subsequent sections describes in detail the available selections in Microsemi Designer software as an aid to understanding security applications and generating appropriate programming files for those applications. Before proceeding, it is helpful to review Figure 3 on page 5, which gives a general overview of the programming file generation flow within the Designer software as well as what occurs during the device programming stage. Specific settings are discussed in the following sections.

In Figure 3 on page 5, the flow consists of two sub-flows. Sub-flow 1 describes programming security settings to the device only, while sub-flow 2 describes programming the design contents only.

In Application 1, described on page 5, the user does not need to generate separate files but can generate one programming file containing both security settings and design contents. Then programming of the security settings and design contents is done in one step. Both sub-flow 1 and sub-flow 2 are used.

In Application 2, described on page 6, the trusted site should follow sub-flows 1 and 2 separately to generate two separate programming files. The programming file from sub-flow 1 will be used at the trusted site to program the device(s) first. The programming file from sub-flow 2 will be sent off-site for production programming.

In Application 3, described on page 7, typically only sub-flow 2 will be used because only updates to the design content portion are needed and no security settings need to be changed.

In the event that update of the security settings is necessary, see the "Reprogramming Devices" on page 14 for details.

Note: If programming the Security Header only, just perform Step 1. If programming design content only, just perform Step 2.

Figure 6 • Fusion Security Programming Flows Fusion

Generation of the Programming File in a Trusted Environment – Application 1

# Generation of the Programming File in a Trusted Environment – Application 1

As discussed in the "Application 1: Trusted Environment" on page 5, in a trusted environment the user can choose to program the device with plain text bitstream content. It is possible to use plain text for programming even when the FlashLock Pass Key option has been selected. In this application, it is not necessary to employ AES encryption protection. For AES encryption settings, see "Generation of Security Header Programming File Only – Application 2" on page 12.

The generated programming file includes the security setting (if selected) and the plain text programming file content for either the FPGA Array, FlashROM, or both the FPGA Array, FlashROM, and/or FB. These options are indicated in Table 1.

| Security Protection   | FlashROM Only | FPGA Core Only | FB Core Only | All |

|-----------------------|---------------|----------------|--------------|-----|

| No AES / No FlashLock | $\checkmark$  | $\checkmark$   | $\checkmark$ | √   |

| FlashLock             | $\checkmark$  | $\checkmark$   | $\checkmark$ | ✓   |

| AES and FlashLock     | _             | _              | _            | _   |

For this scenario, generate the programming file as follows:

1. Select the **Silicon features to be programmed** (Security Settings, FPGA Array, FlashROM, Flash Memory Block), as shown in Figure 7. Click **Next**.

If **Security Settings** is selected (that is, the FlashLock security Pass Key feature), the following step will be displayed to prompt you to select the security level setting. If no security setting is selected, you will be directed to Step 3.

| Silicon feat | ure(s) to be programmed:     |                      |         |                                                     |     |  |

|--------------|------------------------------|----------------------|---------|-----------------------------------------------------|-----|--|

| 🔽 Sr         | ecurity settings             |                      |         |                                                     |     |  |

| 🔽 FF         | PGA Array                    |                      |         |                                                     |     |  |

| 🔽 FI         | ashROM                       |                      |         |                                                     |     |  |

| F            | lashROM configuration file:  |                      |         |                                                     |     |  |

| ſ            | D:\Actelprj\PwrM\smartgen    | \FROM\FROM           | 1.ufc   | Brov                                                | vse |  |

| 🔽 Er         | mbedded Flash Memory         |                      |         |                                                     |     |  |

| Γ            | Instance Name                | Instance<br>Location | Program | Embedded Flash Memory<br>Configuration File         |     |  |

|              | nvm_system_inst/NVM_IN<br>ST | 1                    | 4       | C:\Actelprj\PwrM\smartgen\nvm_sysn<br>\nvm_sysm.efc |     |  |

| ŀ            |                              |                      |         |                                                     |     |  |

Figure 7 • All Silicon Features Checked Fusion

2. Choose the appropriate security level setting and enter a FlashLock Pass Key. The default is the **Medium** security level as shown in Figure 8. Click **Next**.

|            | High                | Protect with Pass Key                                                                            | e e e e e e e e e e e e e e e e e e e | <u>^</u> |  |

|------------|---------------------|--------------------------------------------------------------------------------------------------|---------------------------------------|----------|--|

| ·          | Medium              | <ul> <li>Lock the FPGA Array for both wri</li> <li>Use the Pass Key to write or verif</li> </ul> | у.                                    |          |  |

|            | None                | - Lock the FlashROM for both read<br>interface.<br>- Use the Pass Key to read or write           |                                       | ~        |  |

|            |                     |                                                                                                  | Default Level                         |          |  |

|            | ax length is 32 HEX |                                                                                                  |                                       |          |  |

| JEDB2777   | 91708FC178391CE     | 2850960448                                                                                       | Generate random key                   |          |  |

|            | v lanath is 32 HEV  | chars)                                                                                           |                                       |          |  |

| ES Keu (ma |                     | onaroj.                                                                                          |                                       |          |  |

| ES Key (ma |                     |                                                                                                  | Generate random key                   |          |  |

|            | v length is 32 HEV  | chars):                                                                                          |                                       |          |  |

#### Figure 8 • Medium Security Level Selected Fusion

3. Choose the desired settings for the FlashROM configurations to be programmed as shown in Figure 9. Click **Finish** to generate the STAPL programming file for the design.

|                                                                                                                | FlashRC | )M re   | gion | s:       |    |    |    |     |   |                 |       |                                          |   |      |       |     | _ | Region_7_0       |                 |

|----------------------------------------------------------------------------------------------------------------|---------|---------|------|----------|----|----|----|-----|---|-----------------|-------|------------------------------------------|---|------|-------|-----|---|------------------|-----------------|

| Program                                                                                                        | words   | 15      | 14   | 13       | 12 | 11 | 10 | 9   | 8 | 7               | 6     | 5                                        | 4 | 3    | 2     | 1   | 0 | Properties:      |                 |

| page                                                                                                           | pages   |         |      |          |    | _  |    | -   | _ |                 |       |                                          |   |      |       |     |   | Name             | Region_7_0      |

| ☑                                                                                                              | 7       |         |      |          |    |    |    |     |   |                 |       |                                          |   |      |       |     |   | Start page       | 7               |

| Г                                                                                                              | 6       | 1       |      |          |    |    |    | - 1 |   | 1               |       |                                          |   |      |       | - 1 |   | Start word       | 0               |

|                                                                                                                |         | -       | _    | -        | _  | _  | -  | _   | _ | -               | _     | -                                        | _ | _    | -     |     | _ | Length           | 16              |

|                                                                                                                | 5       |         |      |          |    |    |    |     |   |                 |       |                                          |   |      |       |     |   | Content<br>State | Static<br>Fixed |

| Г                                                                                                              | 4       | a comme |      | cimmits. |    | ·  |    |     |   |                 |       | Committee of                             |   |      |       |     |   | Type             | HEX             |

|                                                                                                                | 4       | -       | _    | -        | _  | _  | _  | _   | _ | -               | _     | -                                        | _ | _    | _     | _   | _ | Value            | 012345678       |

| Г                                                                                                              | 3       |         |      |          |    |    |    |     |   |                 |       |                                          |   |      |       |     |   | Value            |                 |

| Г                                                                                                              | 2       |         |      |          |    |    |    |     | _ | All property of |       | C. C |   | 1    |       |     | _ |                  |                 |

|                                                                                                                | -       | -       |      | -        |    | _  | -  | _   | _ | -               |       | -                                        | _ | -    | -     |     | _ |                  |                 |

|                                                                                                                | 1       |         |      |          |    |    |    |     |   |                 |       |                                          |   |      |       |     |   |                  |                 |

| Г                                                                                                              | 0       | 1       |      | -        |    |    |    |     | - | (All losses)    |       |                                          |   |      |       |     | _ |                  |                 |

| Read and a second s |         | -       |      | -        |    | _  |    |     | _ | -               |       |                                          | - |      | -     | _   | _ |                  |                 |

|                                                                                                                |         |         |      |          |    |    |    |     |   |                 |       |                                          |   |      |       |     |   |                  |                 |

|                                                                                                                |         |         |      |          |    |    |    |     |   |                 | : Bac |                                          | 1 | - KI | ext > |     |   | Finish           | Cancel          |

#### Figure 9 • FlashROM Configuration Settings Fusion

Generation of Security Header Programming File Only – Application 2

# Generation of Security Header Programming File Only – Application 2

As mentioned in the "Application 2: Nontrusted Environment – Unsecured Location" on page 6, the designer may employ FlashLock Pass Key protection or FlashLock Pass Key with AES encryption on the device before sending it to a nontrusted or unsecured location for device programming. To achieve this, the user needs to generate a programming file containing only the security settings desired (Security Header programming file).

Note: If AES encryption is configured, FlashLock Pass Key protection must also be configured.

Table 2 lists the available security options.

| Security Option       | FlashROM Only | FPGA Core Only | FB Core Only | All |

|-----------------------|---------------|----------------|--------------|-----|

| No AES / No FlashLock | _             | -              | _            | -   |

| FlashLock             | $\checkmark$  | $\checkmark$   | $\checkmark$ | ✓   |

| AES and FlashLock     | $\checkmark$  | $\checkmark$   | $\checkmark$ | ✓   |

Table 2 • FlashLock Security Options Fusion

For this scenario, generate the programming file as follows:

1. Select the Security settings option, as shown in Figure 10. Click Next.

| Olivera territ | r_Management.stp                           |                      |         | Brows                                               | se  |

|----------------|--------------------------------------------|----------------------|---------|-----------------------------------------------------|-----|

|                | re(s) to be programmed:<br>curity settings |                      |         |                                                     |     |

|                | GA Arrav                                   |                      |         |                                                     |     |

|                | shROM                                      |                      |         |                                                     |     |

|                | shPOM configuration file:                  |                      |         |                                                     |     |

| 11.04          | \Actelpri\PwrM\smartgen                    | FROMVERON            | Lufe    | Brows                                               | se. |

| ⊢ Em           | bedded Flash Memory                        |                      |         |                                                     |     |

|                | Instance Name                              | Instance<br>Location | Program | Embedded Flash Memory<br>Configuration File         |     |

| n<br>S         | vm_system_inst/N∀M_IN<br>T                 | 1                    |         | C:\Actelprj\PwrM\smartgen\nvm_sysm<br>\nvm_sysm.efc |     |

| Program        | ming previously secured d                  | evice(s)             |         |                                                     |     |

| all a constant | uture (max length is 8 HEX                 |                      |         |                                                     |     |

|                |                                            |                      |         |                                                     |     |

|                |                                            |                      |         |                                                     |     |

|                |                                            |                      |         |                                                     |     |

Figure 10 • Security Settings Fusion

- 2. Choose the desired security level setting and enter the key(s) as shown in Figure 11.

- The High security level employs FlashLock Pass Key with AES Key protection.

- The Medium security level employs FlashLock Pass Key protection only

|                         | High                | Protect with 128-bit Advanced Encry                     | ption Standard (AES) key 🛛 📐 |  |

|-------------------------|---------------------|---------------------------------------------------------|------------------------------|--|

|                         |                     | and Pass Key<br>- Use AES key to write or verify the FI | PGA Arrau                    |  |

| -   -                   | Medium              | Use AES key to write or verify the F                    |                              |  |

| _ ] _                   | None                | interface.                                              |                              |  |

|                         |                     |                                                         | Default Level                |  |

| <sup>p</sup> ass Key (r | max length is 32 HE | X chars):                                               |                              |  |

| 686AD5                  | 58674B6D539EF2B     | A86F85320608                                            | Generate random key          |  |

|                         |                     |                                                         |                              |  |

|                         | nax length is 32 HE | K chars):                                               |                              |  |

| NES Key (n              |                     | 330E00351396B                                           | Generate random key          |  |

| 3                       | DB0256C7E005EB      |                                                         |                              |  |

| 3                       | DB0256C7E005EB      |                                                         |                              |  |

Figure 11 • High Security Level to Implement Both FlashLock Pass Key and AES Key Protection Fusion

Table 3 lists header file security options.

3. When done, click Finish to generate the Security Header programming file

| Security Option       | FlashROM Only | FPGA Core Only | FB Core Only | All          |

|-----------------------|---------------|----------------|--------------|--------------|

| No AES / No FlashLock | $\checkmark$  | $\checkmark$   | $\checkmark$ | $\checkmark$ |

| FlashLock             | $\checkmark$  | $\checkmark$   | $\checkmark$ | ✓            |

| AES and FlashLock     | $\checkmark$  | $\checkmark$   | $\checkmark$ | $\checkmark$ |

# **Reprogramming Devices**

Previously programmed Fusion devices can be reprogrammed using the steps in the "Generation of the Programming File in a Trusted Environment – Application 1" on page 10 and "Generation of Security Header Programming File Only – Application 2" on page 12. In the case where a FlashLock Pass Key has been programmed previously, the user must generate the new programming file with a FlashLock Pass Key that matches the one previously programmed into the device. The software will check the FlashLock Pass Key in the programming file against the FlashLock Pass Key in the device. The keys must match before the device can be unlocked to perform further programming with the new programming file.

Figure 7 on page 10 shows the option **Programming previously secured device(s)**, which the user should check before proceeding. Upon going to the next step, the user will be notified that the same FlashLock Pass Key needs to be entered, as shown in Figure 12

| Medium                                                                                                 | Protect with Pass Key<br>- Lock the FPGA Array for both writing ar<br>- Use the Pass Key to write or verify.<br>- Lock the FlashROM for both reading ar<br>interface.<br>- Use the Pass Key to read or write. |                     |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Pass Key (max length is 32 HEX<br>686AD58674B6D539EF2BA<br>Ine Pass Key must m<br>previously programme | ( chars):<br>.86F85320608<br>.atch the one<br>ed in this device.                                                                                                                                              | Generate random key |

| ES Key (max length is 32 HEX                                                                           |                                                                                                                                                                                                               | Generate random key |

#### Figure 12 • FlashLock Pass Key

It is important to note that when the security settings need to be updated, the user also needs to select the **Security settings** check box in Figure 7 on page 10 to modify the security settings. The user must consider the following:

- If only a new AES key is necessary, the user must re-enter the same Pass Key previously

programmed into the device in Designer and then generate a programming file with same Pass

Key and a different AES key. This ensures the programming file can be used to access and

program the device.

- If a new Pass Key is necessary, the user can generate a new programming file with a new Pass Key (with the same or a new AES key if desired). However, for programming, the user must first load the original programming file with the Pass Key that was previously used to unlock the device. Then the new programming file can be used to program the new security settings.

# Generation of Programming Files with AES Encryption – Application 3

This section discusses how to generate design content programming files needed specifically at unsecured or remote locations to program device(s) with a security header (FlashLock Pass Key and AES Key) already programmed ("Application 2: Nontrusted Environment – Unsecured Location" on page 6 and "Application 3: Nontrusted Environment – Field Updates/Upgrades" on page 7). In this case, the encrypted programming file must correspond to the AES key already programmed into the device. If AES encryption was previously selected to encrypt the FlashROM, the FB, and the FPGA array, then AES encryption must be set when generating the programming file for them. AES encryption can be applied to the FlashROM only, the FB only, the FPGA array only, or all. The user must ensure both the FlashLock Pass Key and the AES key match those already programmed to the device(s), and all security settings must match what was previously programmed. Otherwise, the encryption and/or device unlocking will not be recognized when attempting to program the device with the programming file.

The generated programming file will be AES-encrypted.

In this scenario, generate the programming file as follows:

1. Select the **Security settings** and the portion of the device to be programmed. Select **Programming previously secured device(s)** as shown in Figure 13. Click **Next**.

| Silicon | feature(s) to be programmed:                                     |                      |         |                                               |        | 1 |

|---------|------------------------------------------------------------------|----------------------|---------|-----------------------------------------------|--------|---|

| Г       | Security settings                                                |                      |         |                                               |        |   |

| V       | FPGA Array                                                       |                      |         |                                               |        |   |

| 1       | FlashROM                                                         |                      |         |                                               |        |   |

|         | FlashROM configuration file:                                     |                      |         |                                               |        |   |

|         | C:\Actelprj\PwrM\smartgen'                                       | FROMIFROM            | 1.ufc   |                                               | Browse | 1 |

| V       | Embedded Flash Memory                                            |                      |         |                                               |        |   |

|         | Instance Name                                                    | Instance<br>Location | Program | Embedded Flash Memory<br>Configuration File   |        | - |

|         | nvm_system_inst/NVM_IN<br>ST                                     | 1                    | Г       | C:\Actelprj\PwrM\smartgen\nv<br>\nvm_sysm.efc | m_sysm |   |

|         | gramming previously secured de<br>signature (max length is 8 HEX | 0000000000           |         |                                               |        |   |

Note: The settings in this figure are used to show the generation of an AES-encrypted programming file for both the FPGA array and FlashROM contents. One or both locations may be selected for encryption.

Figure 13 • FlashLock Pass Key and AES Key Protected Programming Files Settings Fusion

Generated Programming File Header Definition

Choose the **High** security level to employ both FlashLock Pass Key and AES Key protection as shown in Figure 14. Enter both keys and click **Next**.

| Medium                                  | Protect with 128-bit Advanced Encry<br>and Pass Key<br>• Use AES key to write or verify the F<br>• Use AES key to write or verify the F<br>interface. | PGA Array.          |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|

| _   _ None<br>ass Key (max length is 32 | I<br>IEX chars):                                                                                                                                      | Default Level       |  |

| ES Key (max length is 32 l              | IEX chars):                                                                                                                                           | Generate random key |  |

|                                         | 337ECEED661C21                                                                                                                                        | Generate random key |  |

Figure 14 • Security Level Set High for FlashLock Pass Key and AES Key Protection Fusion

Programming with this file is intended for an unsecured environment. The AES key encrypts the programming file with the same AES key already used in the device and utilizes it to program the device.

## **Generated Programming File Header Definition**

In each STAPL programming file generated, there will be information about how the AES key and the FlashLock Pass Key are configured. Table 4 lists the header definitions in STAPL programming files for different security levels.

Table 4 • STAPL File Header Definitions for Various Security Levels

| Security Level                                 | STAPL File Header Definition      |

|------------------------------------------------|-----------------------------------|

| No security (no FlashLock Pass Key or AES key) | NOTE "SECURITY" "Disable";        |

| FlashLock Pass Key with no AES key             | NOTE "SECURITY" "KEYED ";         |

| FlashLock Pass Key with AES key                | NOTE "SECURITY" "KEYED ENCRYPT "; |

## Conclusion

The new and enhanced security features offered in Microsemi Fusion devices provide

state-of-the-art security to designs programmed into these Flash-based devices. Microsemi Fusion devices employ the encryption standard used by NIST and the U.S. government – AES using the 128-bit Rijndael algorithm.

The combination of an on-chip AES decryption engine and Microsemi FlashLock technology provides the highest level of security against invasive attacks and design theft, implementing the most robust and secure ISP solution. These security features protect IP within the FPGA and protect the system from cloning, wholesale "black box" copying of a design, invasive attacks, and explicit IP or data theft.

# Glossary

| Term                             | Explanation                                                                                                                                                                                                                                                           |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security Header Programming File | Programming file used to program the AES key and/or FlashLock<br>Pass Key into the FlashROM and/or FPGA array core of the device.<br>Programming file used to program the AES key and/or FlashLock<br>Pass Key into the FlashROM, FB, and/or FPGA core of the device. |

| AES (Encryption) Key             | 128-bit key defined by the user when the AES encryption option is set in the Microsemi designer software when generating the programming file.                                                                                                                        |

| FlashLock Pass Key               | 128-bit key defined by the user when the FlashLock option is set in the Microsemi designer software when generating the programming file.                                                                                                                             |

|                                  | The user must enter the FlashLock Pass Key to the programming software before programming (and actual decryption if the AES option is configured) is done.                                                                                                            |

| FlashLock                        | Security features that protect the device content from attacks. This is achieved by the following:                                                                                                                                                                    |

|                                  | <ul> <li>Flash technology that does not require an external bitstream to<br/>program the device</li> </ul>                                                                                                                                                            |

|                                  | <ul> <li>FlashLock Pass Key that secures device content and prevents<br/>access to the device as necessary</li> </ul>                                                                                                                                                 |

|                                  | AES key that allows secure device reprogrammability                                                                                                                                                                                                                   |

## References

National Institute of Standards and Technology. "ADVANCED ENCRYPTION STANDARD (AES) Questions and Answers." 28 January 2002.

<http://csrc.nist.gov/groups/STM/cavp/documents/aes/aesval.html> (10 January 2005).

# **Related Documents**

AC236:Fusion FlashROM

# **List of Changes**

The following table shows important changes made in this document for each revision.

| Revision                   | Changes                | Pages |

|----------------------------|------------------------|-------|

| Revision 1<br>(March 2016) | Non-technical updates. | NA    |

| Revision 0<br>(April 2006) | Initial release.       | NA    |

\*The part number is located on the last page of the document.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

#### E-mail: sales.support@microsemi.com

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; Enterprise Storage and Communication solutions, security technologies and scalable anti-tamper products; Ethernet Solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.