# Synopsys FPGA Synthesis Synplify Pro for Microsemi Edition

Attribute Reference

May 2015

### **Copyright Notice and Proprietary Information**

Copyright © 2015 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

### **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only.

Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

| "This document is duplicated with | h the permission of Synops | sys, Inc., for the |

|-----------------------------------|----------------------------|--------------------|

| exclusive use of                  |                            | and its            |

| employees. This is copy number _  | ·                          |                    |

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

### **Disclaimer**

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

## Registered Trademarks (®)

Synopsys, AEON, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, CHIPit, CoMET, CODE V, Design Compiler, DesignWare, EMBED-IT!, Formality, Galaxy Custom Designer, Global Synthesis, HAPS, HapsTrak, HDL Analyst, HSIM, HSPICE, Identify, Leda, LightTools, MAST, METeor, ModelTools, NanoSim, NOVeA, OpenVera, ORA, PathMill, Physical Compiler, PrimeTime, SCOPE, Simply Better Results, SiVL, SNUG, SolvNet, Sonic Focus, STAR Memory System, Syndicated, Synplicity, the Synplicity logo, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, UMRBus, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

## Trademarks (™)

AFGen, Apollo, ARC, ASAP, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Cosmos, CosmosLE, CosmosScope, CRITIC, CustomExplorer, CustomSim, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, DesignerHDL, DesignPower, DFTMAX, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, HANEX, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping System, HSIMplus, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Intelli, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Macro-PLUS, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, ORAengineering, Physical Analyst, Planet, Planet-PL, Polaris, Power Compiler, Raphael, RippledMixer, Saturn, Scirocco, Scirocco-i, SiWare, Star-RCXT, Star-SimXT, StarRC, System Compiler, System Designer, Taurus, Total-Recall, TSUPREM-4, VCSi, VHDL Compiler, VMC, and Worksheet Buffer are trademarks of Synopsys, Inc.

## Service Marks (sm)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license.

ARM and AMBA are registered trademarks of ARM Limited.

Saber is a registered trademark of SabreMark Limited Partnership and is used under license.

All other product or company names may be trademarks of their respective owners.

Printed in the U.S.A May 2015

# Contents

| Chapter 1: Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| How Attributes and Directives are Specified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Summary of Attributes and Directives11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Summary of Global Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 2: Attributes and Directives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Attributes and Directives Summary       13         alsloc       15         alspin       18         alspreserve       21         black_box_pad_pin       24         black_box_tri_pins       29         full_case       32         loop_limit       36         parallel_case       38         pragma translate_off/pragma translate_on       40         syn_allow_retiming       43         syn_black_box       47         syn_encoding       54         syn_encoding       54         syn_global_buffers       69         syn_hier       76         syn_insert_buffer       94         syn_insert_pad       100         syn_syn_keep       108         syn_loc       114         syn_lopoplimit       117         syn_maxfan       119         syn multstyle       125 |

| syn_netlist_hierarchy130          |

|-----------------------------------|

| syn_noarrayports                  |

| $syn\_noclockbuf \dots \dots 140$ |

| syn_noprune                       |

| syn_pad_type                      |

| syn_preserve161                   |

| syn_probe                         |

| syn_radhardlevel174               |

| syn_ramstyle177                   |

| syn_reference_clock183            |

| syn_replicate                     |

| syn_resources                     |

| syn_safe_case193                  |

| syn_sharing195                    |

| syn_shift_resetphase              |

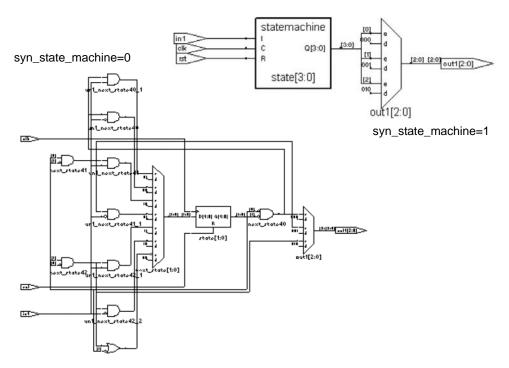

| syn_state_machine204              |

| syn_tco< <i>n</i> >               |

| syn_tpd< <i>n</i> >               |

| syn_tristate                      |

| syn_tsu< <i>n</i> >               |

| translate off/translate on        |

#### CHAPTER 1

## Introduction

This document is part of a set that includes reference and procedural information for the Synopsys® Synplify Pro® FPGA synthesis tool.

This document describes the attributes and directives available in the synthesis tools. The attributes and directives let you direct the way a design is analyzed, optimized, and mapped during synthesis.

This chapter includes the following introductory information:

- How Attributes and Directives are Specified, on page 8

- Summary of Attributes and Directives, on page 11

- Summary of Global Attributes, on page 11

## How Attributes and Directives are Specified

By definition, *attributes* control mapping optimizations and *directives* control compiler optimizations. Because of this difference, directives must be entered directly in the HDL source code. Attributes can be entered either in the source code, in the SCOPE Attributes tab, or manually in a constraint file. For detailed procedures on different ways to specify attributes and directives, see Specifying Attributes and Directives, on page 89 in the *User Guide*.

Verilog files are case sensitive, so attributes and directives must be entered exactly as presented in the syntax descriptions. For more information about specifying attributes and directives using C-style and Verilog 2001 syntax, see Verilog Attribute and Directive Syntax, on page 377.

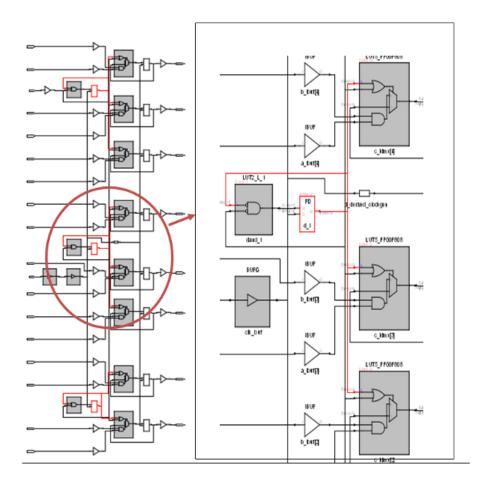

#### The SCOPE Attributes Tab

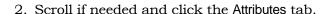

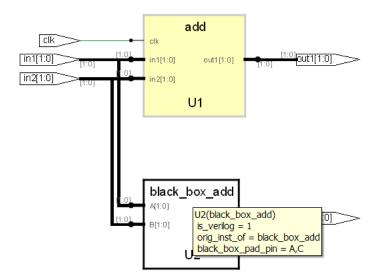

This section describes how to enter attributes using the SCOPE Attributes tab. To use the SCOPE spreadsheet, use this procedure:

1. Start with a compiled design, then open the SCOPE window.

3. Click in the Attribute cell and use the pull-down menus to enter the appropriate attributes and their values.

The Attributes panel includes the following columns.

| Column                                                                                                                                                                                                                                                                                                                                                                                                                       | Description                                                                                                                                                                                                                                                                                       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Enabled                                                                                                                                                                                                                                                                                                                                                                                                                      | (Required) Turn this on to enable the constraint.                                                                                                                                                                                                                                                 |  |

| Object Type                                                                                                                                                                                                                                                                                                                                                                                                                  | Specifies the type of object to which the attribute is assigned. Choose from the pull-down list, to filter the available choices in the Object field.                                                                                                                                             |  |

| Object                                                                                                                                                                                                                                                                                                                                                                                                                       | (Required) Specifies the object to which the attribute is attached. This field is synchronized with the Attribute field, so selecting an object here filters the available choices in the Attribute field. You can also drag and drop an object from the RTL or Technology view into this column. |  |

| Attribute  (Required) Specifies the attribute name. You can choose from a pull-down list that includes all available attribute for the specified technology. This field is synchronized the Object field. If you select an object first, the attribute is filtered. If you select an attribute first, the synthesis filters the available choices in the Object field. You must select an attribute before entering a value. |                                                                                                                                                                                                                                                                                                   |  |

| Value (Required) Specifies the attribute value. You must spec<br>the attribute first. Clicking in the column displays the<br>default value; a drop-down arrow lists available values<br>where appropriate.                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                   |  |

| Val Type                                                                                                                                                                                                                                                                                                                                                                                                                     | Specifies the kind of value for the attribute. For example, string or boolean.                                                                                                                                                                                                                    |  |

| Description                                                                                                                                                                                                                                                                                                                                                                                                                  | Contains a one-line description of the attribute.                                                                                                                                                                                                                                                 |  |

| Comment                                                                                                                                                                                                                                                                                                                                                                                                                      | Contains any comments you want to add about the attributes.                                                                                                                                                                                                                                       |  |

For more details on how to use the Attributes panel of the SCOPE spreadsheet, see Specifying Attributes Using the SCOPE Editor, on page 92 in the *User Guide*.

When you use the SCOPE spreadsheet to create and modify a constraint file, the proper define\_attribute or define\_global\_attribute statement is automatically generated for the constraint file. The following shows the syntax for these statements as they appear in the constraint file.

define\_attribute {object} attributeName {value}

define\_global\_attribute attributeName {value}

| object        | The design object, such as module, signal, input, instance, port, or wire name. The object naming syntax varies, depending on whether your source code is in Verilog or VHDL format. See syn_black_box, on page 47 for details about the syntax conventions. If you have mixed input files, use the object naming syntax appropriate for the format in which the object is defined. Global attributes, since they apply to an entire design, do not use an <i>object</i> argument. |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| attributeName | The name of the synthesis attribute. This must be an attribute, not a directive, as directives are not supported in constraint files.                                                                                                                                                                                                                                                                                                                                              |

| value         | String, integer, or boolean value.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

See Summary of Global Attributes, on page 11 for more details on specifying global attributes in the synthesis environment.

## Summary of Attributes and Directives

The Attributes and Directives Summary, on page 13 summarize the synthesis attributes and directives. For detailed descriptions of individual attributes and directives, see the individual attributes and directives, which are listed in alphabetical order.

## Summary of Global Attributes

Design attributes in the synthesis environment can be defined either globally, (values are applied to all objects of the specified type in the design), or locally, values are applied only to the specified design object (module, view, port, instance, clock, and so on). When an attribute is set both globally and locally on a design object, the local specification overrides the global specification for the object.

In general, the syntax for specifying a global attribute in a constraint file is:

#### define\_global\_attribute attribute\_name {value}

The table below contains a list of attributes that can be specified globally in the synthesis environment.

For complete descriptions of any of the attributes listed below, see Attributes and Directives Summary, on page 13.

| Global Attribute      | Can Also Be<br>Set On Design<br>Objects |  |

|-----------------------|-----------------------------------------|--|

| syn_allow_retiming    | X                                       |  |

| syn_hier              | X                                       |  |

| syn_multstyle         | х                                       |  |

| syn_netlist_hierarchy |                                         |  |

| syn_noarrayports      |                                         |  |

|                       |                                         |  |

| Global Attribute | Can Also Be<br>Set On Design<br>Objects |  |

|------------------|-----------------------------------------|--|

| syn_noclockbuf   | X                                       |  |

| syn_ramstyle     | X                                       |  |

| syn_replicate    | X                                       |  |

#### CHAPTER 2

## Attributes and Directives

All attributes and directives supported for synthesis are listed in alphabetical order. Each command includes syntax, option and argument descriptions, and examples. You can apply attributes and directives globally or locally on a design object.

# Attributes and Directives Summary

The following attributes and directives are listed in alphabetical order:

| alsloc                                   | alspin             |

|------------------------------------------|--------------------|

| alspreserve                              | black_box_pad_pin  |

| black_box_tri_pins                       | full_case          |

| loop_limit                               | parallel_case      |

| pragma translate_off/pragma translate_on | syn_allow_retiming |

| syn_black_box                            | syn_encoding       |

| syn_enum_encoding                        | syn_global_buffers |

| syn_hier                                 | syn_insert_buffer  |

| syn_insert_pad                           | syn_isclock        |

| syn_keep                                 | syn_loc            |

| syn_looplimit                                 | syn_maxfan                                        |

|-----------------------------------------------|---------------------------------------------------|

| syn_multstyle                                 | syn_netlist_hierarchy                             |

| syn_noarrayports                              | syn_noclockbuf                                    |

| syn_noprune                                   | syn_pad_type                                      |

| syn_preserve                                  | syn_probe                                         |

| syn_radhardlevel                              | syn_ramstyle                                      |

| syn_reference_clock                           | syn_replicate                                     |

| syn_resources                                 | syn_safe_case                                     |

| syn_sharing                                   | syn_shift_resetphase                              |

| syn_state_machine                             | syn_tco <n></n>                                   |

| syn_tpd <n></n>                               | syn_tristate                                      |

| syn_tsu <n></n>                               | translate_off/translate_on                        |

| syn_sharing syn_state_machine syn_tpd <n></n> | syn_shift_resetphase syn_tco <n> syn_tristate</n> |

#### alsloc

#### Attribute

Preserves relative placements of macros and IP blocks in the Microsemi Designer place-and-route tool.

| Vendor    | Technology |

|-----------|------------|

| Microsemi | All        |

#### **Description**

Preserves relative placements of macros and IP blocks in the Microsemi Designer place-and-route tool. The alsloc attribute has no effect on synthesis, but is passed directly to Microsemi Designer.

The alsloc constrain is passed directly to the post synthesis EDN netlist as the following:

```

(property alsloc (string "R15C6"))

(property alsloc (string "R35C6"))

```

### alsloc Syntax Specification

| Name   | Global | Object               |

|--------|--------|----------------------|

| alsloc | No     | Macro or<br>IP block |

#### alsloc Value

| Value    | Default | Description                    |

|----------|---------|--------------------------------|

| location | None    | Location of macro or IP block. |

This table summarizes the syntax in different files:

| FDC     | <pre>define_attribute {object} alsloc {location}</pre> | SCOPE Example   |

|---------|--------------------------------------------------------|-----------------|

| Verilog | <pre>object I* synthesis alsloc = "location" *I;</pre> | Verilog Example |

| VHDL    | attribute alsloc of object : label is "location";      | VHDL Example    |

#### **SCOPE Example**

Following is an example of setting alsloc on a macro (u1).

```

define attribute {u1} alsloc {R15C6}

```

### **Verilog Example**

```

module test(in1, in2, in3, clk, q);

input in1, in2, in3, clk;

output q;

wire out1 /* synthesis syn keep = 1 */, out2;

and2a u1 (.A (in1), .B (in2), .Y (out1))

/* synthesis alsloc="R15C6" */;

assign out2 = out1 & in3;

df1 u2 (.D (out2), .CLK (clk), .Q (q))

/* synthesis alsloc="R35C6" */;

endmodule

module and2a(A, B, Y); // synthesis syn black box

input A, B;

output Y;

endmodule

module df1(D, CLK, Q); // synthesis syn black box

input D, CLK;

output Q;

endmodule

```

### **VHDL Example**

```

library IEEE;

use IEEE.std_logic_1164.all;

entity test is

port (in1, in2, in3, clk : in std_logic;

q : out std_logic);

end test;

architecture rtl of test is

signal out1, out2 : std_logic;

component AND2A

port (A, B : in std_logic;

Y : out std_logic);

end component;

```

```

component df1

port (D, CLK : in std_logic;

Q : out std_logic);

end component;

attribute syn_keep : boolean;

attribute syn_keep of out1 : signal is true;

attribute alsloc: string;

attribute alsloc of U1: label is "R15C6";

attribute alsloc of U2: label is "R35C6";

attribute syn_black_box : boolean;

attribute syn_black_box of AND2A, df1 : component is true;

begin

U1: AND2A port map (A => in1, B => in2, Y => out1);

out2 <= in3 and out1;

U2: df1 port map (D => out2, CLK => clk, Q => q);

end rt1;

```

### alspin

Attribute

Assigns the scalar or bus ports of the design to Microsemi I/O pin numbers.

| Vendor    | Technology |

|-----------|------------|

| Microsemi | A11        |

#### **Description**

The alspin attribute assigns the scalar or bus ports of the design to Microsemi I/O pin numbers (pad locations). Refer to the Microsemi databook for valid pin numbers. If you use alspin for bus ports or for slices of bus ports, you must also use the syn\_noarrayports attribute. See *Specifying Locations for Microsemi Bus Ports*, on page 499 of the *User Guide* for information on assigning pin numbers to buses and slices.

The alspin pin location is passed as a property string to the output EDN netlist as the following:

(instance (rename dataoutZ0 "dataout") (viewRef netlist (cellRef df1 (libraryRef &54SXA))) (property alspin (string "48"))

### alspin Syntax Specification

| Name   | Global | Object |

|--------|--------|--------|

| alspin | No     |        |

### alspin Value

| Value      | Default | Description           |

|------------|---------|-----------------------|

| pin_number | None    | The Microsemi I/O pin |

This table summarizes the syntax in different files:

| FDC     | <pre>define_attribute {port_name} alspin {pin_number}</pre>         | Constraint File<br>Example |

|---------|---------------------------------------------------------------------|----------------------------|

| Verilog | object <b>/</b> * synthesis alspin = "pin_number" * <b>/</b> ;      | Verilog Example            |

| VHDL    | <pre>attribute alspin of object : objectType is "pin_number";</pre> | VHDL Example               |

#### **Constraint File Example**

In the attribute syntax, *port\_name* is the name of the port and *pin\_number* is the Microsemi I/O pin.

```

define_attribute {DATAOUT} alspin {48}

```

#### **Verilog Example**

Where *object* is the port and *pin\_number* is the Microsemi I/O pin. For example:

```

module comparator (datain, clk, dataout);

output reg dataout /* synthesis alspin="48" */;

input [7:0] datain;

input clk;

always@(posedge clk)

begin

dataout <=datain;

end

endmodule</pre>

```

#### **VHDL Example**

See VHDL Attribute and Directive Syntax, on page 574 for different ways to specify VHDL attributes and directives.

Where *object* is the port, *objectType* is signal, and *pin\_number* is the Microsemi I/O pin. For example:

```

library ieee;

use ieee.std_logic_1164.all;

entity comparator is

port (datain : in std logic vector(7 downto 0);

clk : in std logic;

dataout : out std_logic_vector(7 downto 0));

attribute alspin : string;

attribute alspin of dataout : signal is "48";

end;

architecture rtl of comparator is

begin

process(clk)

begin

if clk'event and clk = '1' then

dataout <=datain;</pre>

end if;

end process;

end rtl;

```

### alspreserve

#### **Attribute**

Specifies a net that you do not want removed by the Microsemi Designer place-and-route tool.

| Vendor    | Technology |

|-----------|------------|

| Microsemi | A11        |

### **Description**

The alspreserve attribute pecifies a net that you do not want removed (optimized away) by the Microsemi Designer place-and-route tool. The alspreserve attribute has no effect on synthesis, but is passed directly to the Microsemi Designer place-and-route software. However, to prevent the net from being removed during the synthesis process, you must also use the syn\_keep directive.

The alspreserve attribute is passed to the ouput EDN netlist file as the following:

```

(net (rename and_outZ0Z3 "and_out3") (joined

(portRef b (instanceRef outZ0Z1))

(portRef y (instanceRef and_out3_1))

)

(property alspreserve (integer 1)))

```

### alspreserve Syntax Specification

| Name        | Global | Object |

|-------------|--------|--------|

| alspreserve | No     | Net    |

### alspreserve Value

| Value  | Default | Description                 |

|--------|---------|-----------------------------|

| object | None    | Name of the net to preserve |

This table summarizes the syntax in different files:

| FDC     | <pre>define_attribute {n: net_name} alspreserve {1}</pre> | Constraint File<br>Example |

|---------|-----------------------------------------------------------|----------------------------|

| Verilog | object /* synthesis alspreserve = 1 */;                   | Verilog Example            |

| VHDL    | attribute alspreserve of <i>object</i> : signal is true;  | VHDL Example               |

#### **Constraint File Example**

```

define_attribute {n:and_out3} alspreserve {1};

define attribute {n:or out1} alspreserve {1};

```

#### **Verilog Example**

```

module complex (in1, out1);

input [6:1] in1;

output out1;

wire out1;

wire or_out1 /* synthesis syn_keep=1 alspreserve=1 */;

wire and_out1;

wire and_out2;

wire and_out3 /* synthesis syn_keep=1 alspreserve=1 */;

assign and_out1 = in1[1] & in1[2];

assign and_out2 = in1[3] & in1[4];

assign and_out3 = in1[5] & in1[6];

assign or_out1 = and_out1 | and_out2;

assign out1 = or_out1 & and_out3;

endmodule

```

### **VHDL Example**

See VHDL Attribute and Directive Syntax, on page 574 for different ways to specify VHDL attributes and directives.

```

library ieee;

use ieee.std_logic_1164.all;

library symplify;

use symplify.attributes.all;

```

```

entity complex is

port (input : in std logic vector (6 downto 1);

output : out std logic);

end complex;

architecture RTL of complex is

signal and out1 : std logic;

signal and out2 : std logic;

signal and out3 : std logic;

signal or out1 : std logic;

attribute syn keep of and out3 : signal is true;

attribute syn keep of or out1 : signal is true;

attribute alspreserve of and out3 : signal is true;

attribute alspreserve of or out1 : signal is true;

begin

and out1 <= input(1) and input(2);

and out2 <= input(3) and input(4);

and out3 <= input(5) and input(6);

or out1 <= and out1 or and out2;

output <= or out1 and and_out3;</pre>

end;

```

### black\_box\_pad\_pin

Directive

Specifies that the pins on a black box are I/O pads visible to the outside environment.

#### black\_box\_pad\_pin Values

| Value    | Description                                         |

|----------|-----------------------------------------------------|

| portName | Specifies ports on the black box that are I/O pads. |

#### **Description**

Used with the syn\_black\_box directive and specifies that pins on black boxes are I/O pads visible to the outside environment. To specify more than one port as an I/O pad, list the ports inside double-quotes ("), separated by commas, and without enclosed spaces.

To instantiate an I/O from your programmable logic vendor, you usually do not need to define a black box or this directive. The synthesis tool provides predefined black boxes for vendor I/Os. For more information, refer to your vendor section under FPGA and CPLD Support.

The black\_box\_pad\_pin directive is one of several directives that you can use with the syn\_black\_box directive to define timing for a black box. See syn\_black\_box, on page 47 for a list of the associated directives.

#### black\_box\_pad\_pin Values Syntax

The following support applies for the black\_box\_pad\_pin attribute.

| Global S | Support                | Object                                                       |                 |

|----------|------------------------|--------------------------------------------------------------|-----------------|

| No       |                        | Verilog module or VHDL architecture declared for a black box |                 |

| This tal | ole sumr               | marizes the syntax in different files:                       |                 |

| Verilog  | object/*               | synthesis black_box_pad_pin = portList */;                   | Verilog Example |

| VHDL     | attribute<br>portList, | black_box_pad_pin of object: objectType is                   | VHDL Example    |

#### Where

- *object* is a module or architecture declaration of a black box.

- *portList* is a spaceless, comma-separated list of the names of the ports on black boxes that are I/O pads.

- *objectType* is a string in VHDL code.

#### **Verilog Example**

This example shows how to specify this attribute in the following Verilog code segment:

```

module BBDLHS(D,E,GIN,GOUT,PAD,Q)

/* synthesis syn black box black box pad pin="GIN[2:0],Q" */;

```

### **VHDL Example**

This example shows how to specify this attribute in the following VHDL code:

```

library AI;

use ieee.std logic 1164.all;

Entity top is

generic (width : integer := 4);

port (in1,in2 : in std logic vector(width downto 0);

clk : in std logic;

q : out std logic vector (width downto 0)

);

end top;

architecture top1 arch of top is

component test is

generic (width1 : integer := 2);

port (in1,in2 : in std logic vector(width1 downto 0);

clk : in std logic;

q : out std logic vector (width1 downto 0)

);

end component;

attribute syn black box : boolean;

attribute black box pad pin : string;

attribute syn black box of test : component is true;

attribute black box pad pin of test : component is

```

```

"in1(4:0), in2[4:0], q(4:0)";

begin

test123 : test generic map (width) port map (in1,in2,clk,q);

end top1_arch;

```

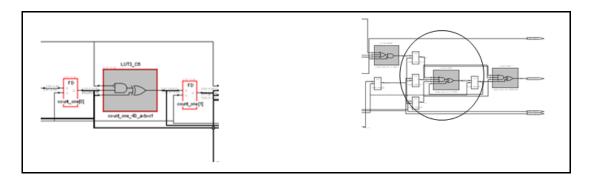

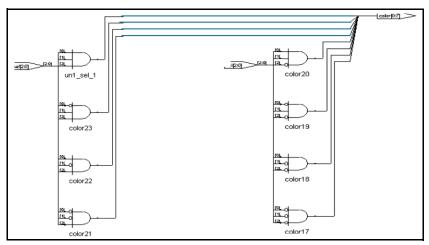

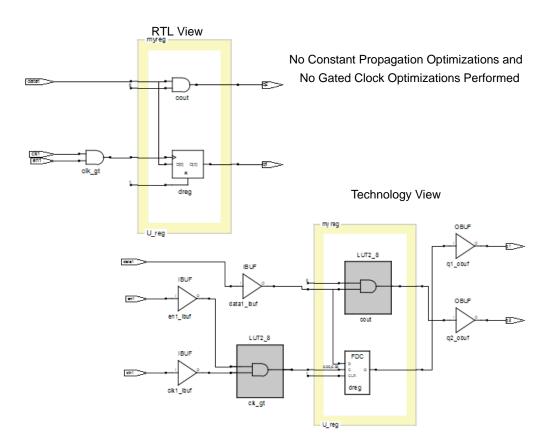

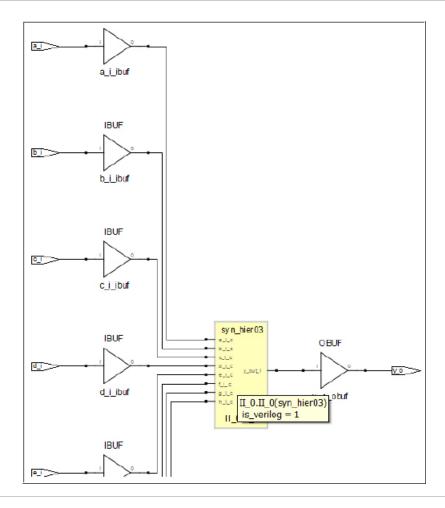

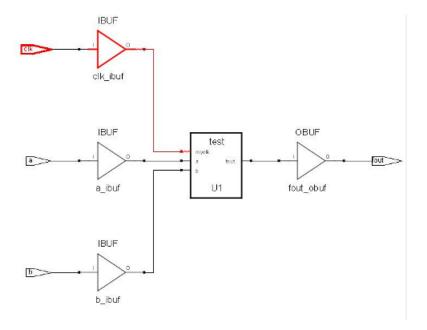

#### Effect of Using black\_box\_pad\_pin

The following example shows the effect of applying the attribute.

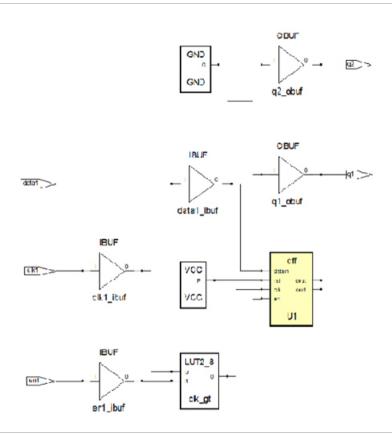

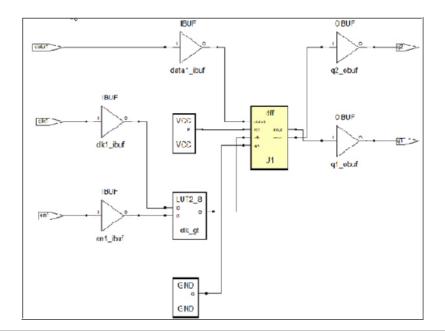

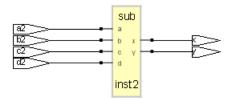

#### Before using black\_box\_pad\_pin

### After using black\_box\_pad\_pin

### black\_box\_tri\_pins

#### Directive

Specifies that an output port on a black box component is a tristate.

#### black\_box\_tri\_pins Values

| Value    | Description                                                   |

|----------|---------------------------------------------------------------|

| portName | Specifies an output port on the black box that is a tristate. |

### **Description**

Used with the syn\_black\_box directive and specifies that an output port on a black box component is a tristate. This directive eliminates multiple driver errors when the output of a black box has more than one driver. To specify more than one tristate port, list the ports inside double-quotes ("), separated by commas (,), and without enclosed spaces.

The black\_box\_tri\_pins directive is one of several directives that you can use with the syn\_black\_box directive to define timing for a black box. See syn\_black\_box, on page 47 for a list of the associated directives.

### black\_box\_tri\_pins Values Syntax

The following support applies for the black\_box\_tri\_pins attribute.

| Global S | upport                 | Object                                                       |                 |  |

|----------|------------------------|--------------------------------------------------------------|-----------------|--|

| No       |                        | Verilog module or VHDL architecture declared for a black box |                 |  |

| This tab | le sumr                | narizes the syntax in different files:                       |                 |  |

| Verilog  | object/*               | synthesis black_box_tri_pins = portList */;                  | Verilog Example |  |

| VHDL     | attribute<br>portList; | olack_box_tri_pins of object. objectType is                  | VHDL Example    |  |

#### Where

• *object* is a module or architecture declaration of a black box.

- portList is a spaceless, comma-separated list of the tristate output port names.

- *objectType* is a string in VHDL code.

#### **Verilog Example**

Here is an example with a single port name:

```

module BBDLHS(D,E,GIN,GOUT,PAD,Q)

/* synthesis syn black box black box tri pins="PAD" */;

```

Here is an example with a list of multiple pins:

```

module bb1(D,E,tri1,tri2,tri3,Q)

/* synthesis syn black box black box tri pins="tri1,tri2,tri3" */;

```

For a bus, you specify the port name followed by all the bits on the bus:

```

module bb1(D,bus1,E,GIN,GOUT,Q)

/* synthesis syn black box black box tri pins="bus1[7:0]" */;

```

### **VHDL Example**

```

library ieee;

use ieee.std logic 1164.all;

package my components is

component BBDLHS

port (D: in std logic;

E: in std logic;

GIN : in std logic;

GOUT : in std logic;

PAD : inout std logic;

Q: out std logic);

end component;

attribute syn black box : boolean;

attribute syn black box of BBDLHS : component is true;

attribute black box tri pins : string;

attribute black box tri pins of BBDLHS: component is "PAD";

end package my components;

```

Multiple pins on the same component can be specified as a list:

```

attribute black_box_tri_pins of bb1 : component is

"tri,tri2,tri3";

```

To apply this directive to a port that is a bus, specify all the bits on the bus:

```

attribute black_box_tri_pins of bb1 : component is "bus1[7:0]";

```

### full case

#### Directive

For Verilog designs only. Indicates that all possible values have been given, and that no additional hardware is needed to preserve signal values.

#### full\_case Values

| Value          | Description                                                                                         |  |

|----------------|-----------------------------------------------------------------------------------------------------|--|

| 1<br>(Default) | All possible values have been given and no additional hardware is needed to preserve signal values. |  |

#### **Description**

For Verilog designs only. When used with a case, casex, or casez statement, this directive indicates that all possible values have been given, and that no additional hardware is needed to preserve signal values.

#### full\_case Values Syntax

This table summarizes the syntax in the following file type:

| Verilog <i>object</i> /* synthesis full_case */; | Verilog Examples |

|--------------------------------------------------|------------------|

|--------------------------------------------------|------------------|

#### **Verilog Examples**

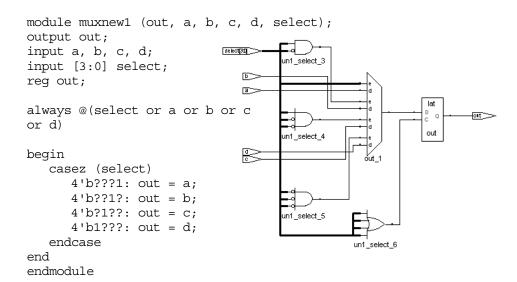

The following casez statement creates a 4-input multiplexer with a pre-decoded select bus (a decoded select bus has exactly one bit enabled at a time):

This code does not specify what to do if the select bus has all zeros. If the select bus is being driven from outside the current module, the current module has no information about the legal values of select, and the synthesis tool must preserve the value of the output out when all bits of select are zero. Preserving the value of out requires the tool to add extraneous level-sensitive latches if out is not assigned elsewhere through every path of the always block. A warning message like the following is issued:

"Latch generated from always block for signal out, probably missing assignment in branch of if or case."

If you add the full\_case directive, it instructs the synthesis tool not to preserve the value of out when all bits of select are zero.

```

module muxnew3 (out, a, b, c, d, select);

output out;

input a, b, c, d;

input [3:0] select;

reg out;

always @(select or a or b or c or d)

```

```

begin

casez (select) /* synthesis full_case */

4'b???1: out = a;

4'b??1?: out = b;

4'b?1??: out = c;

4'b1???: out = d;

endcase

end

endmodule

```

If the select bus is decoded in the same module as the case statement, the synthesis tool automatically determines that all possible values are specified, so the full\_case directive is unnecessary.

#### Assigned Default and full\_case

As an alternative to full\_case, you can assign a default in the case statement. The default is assigned a value of 'bx (a 'bx in an assignment is treated as a "don't care"). The software assigns the default at each pass through the casez statement in which the select bus does not match one of the explicitly given values; this ensures that the value of out is not preserved and no extraneous level-sensitive latches are generated.

The following code shows a default assignment in Verilog:

```

module muxnew2 (out, a, b, c, d, select);

output out;

input a, b, c, d;

input [3:0] select;

req out;

always @(select or a or b or c or d)

begin

casez (select)

4'b???1: out = a;

4'b??1?: out = b;

4'b?1??: out = c;

4'b1???: out = d;

default: out = 'bx;

endcase

end

endmodule

```

Both techniques help keep the code concise because you do not need to declare all the conditions of the statement. The following table compares them:

| Default Assignment                                                                               | full_case                                                                                                    |  |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| Stays within Verilog to get the desired hardware                                                 | Must use a synthesis directive to get the desired hardware                                                   |  |

| Helps simulation debugging because you can easily find that the invalid select is assigned a 'bx | Can cause mismatches between pre- and post-synthesis simulation because the simulator does not use full_case |  |

## loop\_limit

Directive

Verilog

Specifies a loop iteration limit for for loops in the design when the loop index is a variable, not a constant.

### loop\_limit Values

| Value    | Description                                          |  |

|----------|------------------------------------------------------|--|

| 1 - 1999 | Overrides the default loop limit of 2000 in the RTL. |  |

#### **Description**

For Verilog designs only. Specifies a loop iteration limit for for loops in the design when the loop index is a variable, not a constant. The compiler uses the default iteration limit of 1999 when the exit or terminating condition does not compute a constant value, or to avoid infinite loops. The default limit ensures the effective use of runtime and memory resources.

If your design requires a variable loop index or if the number of loops is greater than the default limit, use the loop\_limit directive to specify a new limit for the compiler. If you do not, you get a compiler error. You must hard code the limit at the beginning of the loop statement. The limit cannot be an expression. The higher the value you set, the longer the runtime. To override the default limit of 2000 in the RTL, use the Loop Limit option on the Verilog tab of the Implementation Options panel. See Verilog Panel, on page 207 in the Command Reference.

**Note:** VHDL applications use the syn\_looplimit directive (see syn\_looplimit, on page 117).

#### Ioop\_limit Values Syntax

The following support applies for the loop\_limit directive.

#### Global Support Object

Yes

Specifies the beginning of the loop statement.

This table summarizes the syntax in the following file:

Verilog /\* synthesis loop\_limit integer \*/ loopStatement

Verilog Example

# **Verilog Example**

The following is an example where the loop limit is set to 2000:

```

module test(din,dout,clk);

input[1999 : 0] din;

input clk;

output[1999 : 0] dout;

reg[1999 : 0] dout;

integer i;

always @(posedge clk)

begin

/* synthesis loop_limit 2000 */

for(i=0;i<=1999;i=i+1)

begin

dout[i] <= din[i];

end

end

end

endmodule</pre>

```

## Effect of Using loop\_limit

### Before using loop\_limit

If the code has more than 2000 loops and the attribute is not set, the tool will produce an error.

```

@E:CS162 : loop_limit.v(10) | Loop iteration limit 2000 exceeded - add '// synthesis loop_limit 4000' before the loop construct

```

### After using loop\_limit

Code with more than 2000 loops will not produce the loop\_limit error.

# parallel\_case

Directive

For Verilog designs only. Forces a parallel-multiplexed structure rather than a priority-encoded structure.

### **Description**

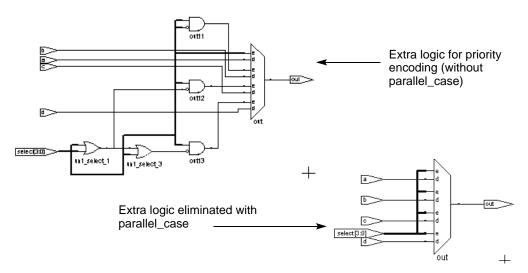

case statements are defined to work in priority order, executing (only) the first statement with a tag that matches the select value. The parallel\_case directive forces a parallel-multiplexed structure rather than a priority-encoded structure.

If the select bus is driven from outside the current module, the current module has no information about the legal values of select, and the software must create a chain of disabling logic so that a match on a statement tag disables all following statements.

However, if you know the legal values of select, you can eliminate extra priority-encoding logic with the parallel\_case directive. In the following example, the only legal values of select are 4'b1000, 4'b0100, 4'b0010, and 4'b0001, and only one of the tags can be matched at a time. Specify the parallel\_case directive so that tag-matching logic can be parallel and independent, instead of chained.

# parallel\_case Syntax

The following support applies for the parallel\_case directive.

### Global Support Object

| No | A case, casex, or casez statement declaration |

|----|-----------------------------------------------|

This table summarizes the syntax in the following file type:

| Verilog Example |

|-----------------|

|                 |

### **Verilog Example**

You specify the directive as a comment immediately following the select value of the case statement.

```

module muxnew4 (out, a, b, c, d, select);

output out;

input a, b, c, d;

input [3:0] select;

reg out;

always @(select or a or b or c or d)

begin

casez (select) /* synthesis parallel case */

4'b???1: out = a;

4'b??1?: out = b;

4'b?1??: out = c;

4'b1???: out = d;

default: out = 'bx;

endcase

end

endmodule

```

If the select bus is decoded within the same module as the case statement, the parallelism of the tag matching is determined automatically, and the parallel\_case directive is unnecessary.

# Effect of Using parallel\_case

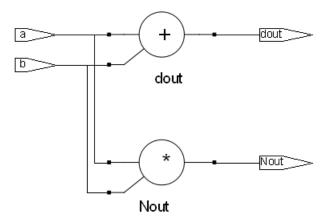

# pragma translate\_off/pragma translate\_on

#### Directive

Allows you to synthesize designs originally written for use with other synthesis tools without needing to modify source code. All source code that is between these two directives is ignored during synthesis.

# **Description**

Another use of these directives is to prevent the synthesis of stimulus source code that only has meaning for logic simulation. You can use pragma translate\_off/translate\_on to skip over simulation-specific lines of code that are not synthesizable.

When you use pragma translate\_off in a module, synthesis of all source code that follows is halted until pragma translate\_on is encountered. Every pragma translate\_off must have a corresponding pragma translate\_on. These directives cannot be nested, therefore, the pragma translate\_off directive can only be followed by a pragma translate\_on directive.

**Note:** See also, translate\_off/translate\_on, on page 227. These directives are implemented the same in the source code.

This table summarizes the syntax in the following file type:

| Verilog | /* pragma translate_off */ /* pragma translate_on */ /*synthesis translate_off */ /*synthesis translate_on */                     | Verilog Example |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| VHDL    | <ul><li>pragma translate_off</li><li>pragma translate_on</li><li>synthesis translate_off</li><li>synthesis translate_on</li></ul> | VHDL Example    |  |

### **Verilog Example**

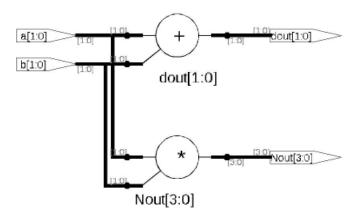

```

module test(input a, b, output dout, Nout);

assign dout = a + b;

//Anything between pragma translate_off/translate_on is ignored by

the synthesis tool hence only

//the adder circuit above is implemented, not the multiplier

circuit below:

/* synthesis translate_off */ assign Nout = a * b;

/* synthesis translate_on */

endmodule

```

# **VHDL Example**

```

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic unsigned.all;

entity test is

port (

a : in std logic vector(1 downto 0);

b: in std logic vector(1 downto 0);

dout : out std logic vector(1 downto 0);

Nout: out std logic vector(3 downto 0)

);

end;

architecture rtl of test is

begin

dout <= a + b;

--Anything between pragma translate off/translate on is ignored by

the synthesis tool hence only

--the adder circuit above is implemented not the multiplier circuit

below:

--pragma translate off

Nout <= a * b;

--pragma translate on

end:

```

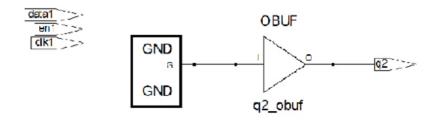

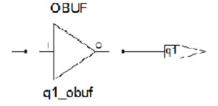

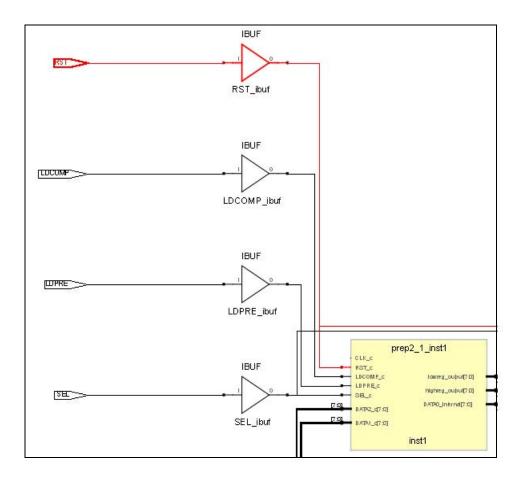

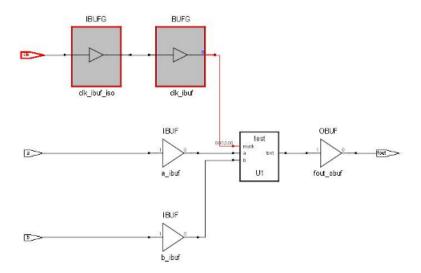

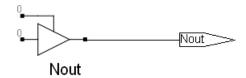

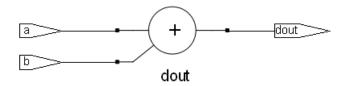

# Effect of Using pragma translate\_off/pragma translate\_on

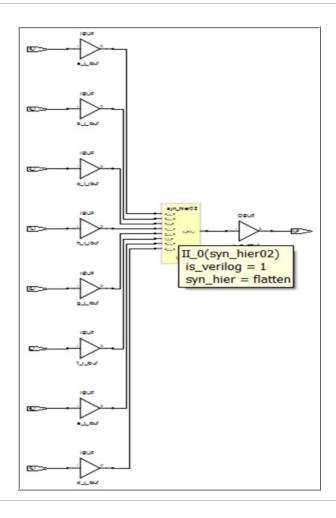

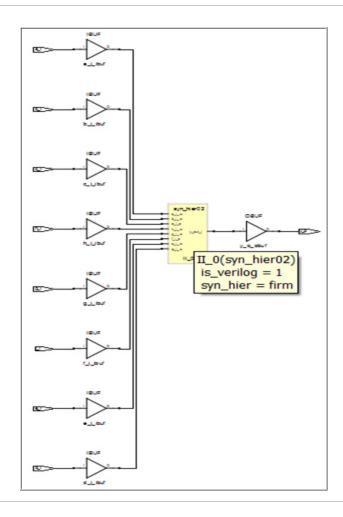

Before applying the attribute:

After applying the attribute:

# syn\_allow\_retiming

#### Attribute

Determines if registers can be moved across combinational logic to improve performance.

| Vendor    | Technology                                        | Synthesis Tool |

|-----------|---------------------------------------------------|----------------|

| Microsemi | Fusion<br>IGLOO, IGLOOe, IGLOO+<br>ProASIC3/3E/3L | Synplify Pro   |

## syn\_allow\_retiming values

| 1   true  | Allows registers to be moved during retiming. |

|-----------|-----------------------------------------------|

| 0   false | Does not allow retimed registers to be moved. |

# **Description**

The syn\_allow\_retiming attribute determines if registers can be moved across combinational logic to improve performance.

The attribute can be applied either globally or to specific registers. Typically, you enable the global Retiming option in the UI (or the set\_option -retiming 1 switch in Tcl) and use the syn\_allow\_retiming attribute to disable retiming for specific objects that you do not want moved.

### syn\_allow\_retiming Syntax

| Global | Object   |

|--------|----------|

| Yes    | Register |

You can specify the attribute in the following files:

| FDC     | define_attribute {register} syn_allow_retiming {1 0} define_global_attribute syn_allow_retiming {1 0} | FDC<br>Example     |

|---------|-------------------------------------------------------------------------------------------------------|--------------------|

| Verilog | object /* synthesis syn_allow_retiming = 0   1 */;                                                    | Verilog<br>Example |

| VHDL    | attribute syn_allow_retiming of object: objectType is true   false;                                   | VHDL<br>Example    |

### **FDC Example**

```

define_attribute {register} syn_allow_retiming {1|0}

define_global_attribute syn_allow_retiming {1|0}

```

| Enable | Object Type | Object            | Attribute          | Value | Value Type | Description              |

|--------|-------------|-------------------|--------------------|-------|------------|--------------------------|

| •      | <any></any> | <global></global> | syn_allow_retiming | 1     | boolean    | Controls retiming of reg |

### **Verilog Example**

```

object /* synthesis syn_allow_retiming = 0 | 1 */;

```

Here is an example of applying it to a register:

#### **VHDL Example**

attribute syn\_allow\_retiming of object: objectType is true | false;

The data type is Boolean. Here is an example of applying it to a register:

```

LIBRARY IEEE;

IEEE.STD LOGIC 1164.ALL;

USE

IEEE.std logic unsigned.ALL;

USE

ENTITY ones cnt IS

PORT (vin : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

vout : OUT STD LOGIC VECTOR (3 DOWNTO 0);

clk : IN STD LOGIC);

END ones cnt;

ARCHITECTURE lan OF ones cnt IS

signal vout req : STD LOGIC VECTOR (3 DOWNTO 0);

attribute syn allow retiming : boolean;

attribute syn allow retiming of vout reg : signal is true;

BEGIN

gen vout: PROCESS(clk, vin)

VARIABLE count : STD LOGIC VECTOR (vout 'RANGE);

BEGIN

if rising edge(clk) then

count := (OTHERS => '0');

FOR I IN vin'RANGE LOOP

count := count + vin(i);

END LOOP;

vout req <= count;</pre>

end if;

vout <= vout reg;</pre>

END PROCESS gen vout;

END lan;

```

See VHDL Attribute and Directive Syntax, on page 574 for different ways to specify VHDL attributes and directives.

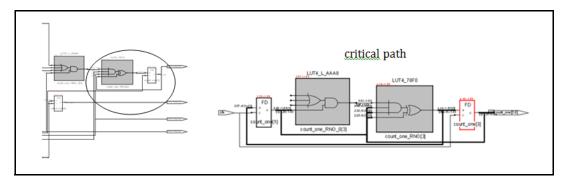

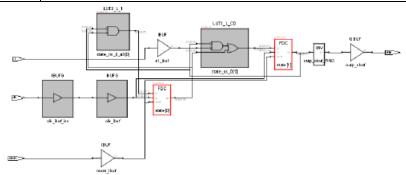

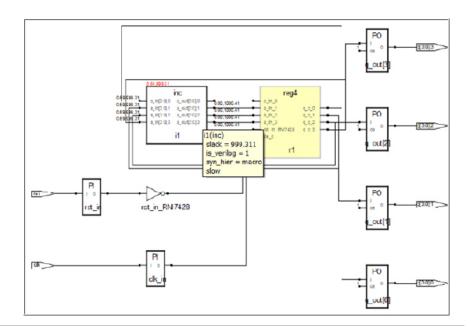

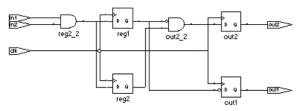

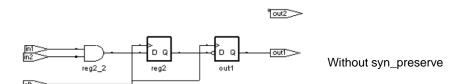

### Effect of using syn\_allow\_retiming

Before applying syn\_allow\_retiming.

| Verilog | output reg [3:0]count_one /* synthesis syn_allow_retiming=0*/; |

|---------|----------------------------------------------------------------|

| VHDL    | attribute syn_allow_retiming of vout_reg : signal is false;    |

The critical path and the worst slack for this scenario are given below along with the original count\_one [3] register (before being retimed) as found in the design.

After applying syn\_allow\_retiming.

Verilog output reg [3:0]count\_one /\* synthesis syn\_allow\_retiming=1\*/; attribute syn\_allow\_retiming of vout\_reg : signal is true;

The critical path and the worst slack for this scenario are shown along with the four '\*\_ret' retimed registers.

VHDL

# syn\_black\_box

Directive

Defines a module or component as a black box.

# syn\_black\_box Value

| Value      | Default | Description                       |

|------------|---------|-----------------------------------|

| moduleName | N/A     | Defines an object as a black box. |

### **Description**

Specifies that a module or component is a black box for synthesis. A black box module has only its interface defined for synthesis; its contents are not accessible and cannot be optimized during synthesis. A module can be a black box whether or not it is empty.

Typically, you set syn\_black\_box on objects like the ones listed below. You do not need to define a black box for such an object if the synthesis tool includes a predefined black box for it.

- Vendor primitives and macros (including I/Os).

- User-designed macros whose functionality is defined in a schematic editor, IP, or another input source where the place-and-route tool merges design netlists from different sources.

In certain cases, the tool does not honor a syn\_black\_box directive:

- In mixed language designs where a black box is defined in one language at the top level but where there is an existing description for it in another language, the tool can replace the declared black box with the description from the other language.

- If your project includes black box descriptions in srs, ngc, or edf formats, the tool uses these black box descriptions even if you have specified syn\_black\_box at the top level.

To override this and ensure that the attribute is honored, use these methods:

• Set a syn\_black\_box directive on the module or entity in the HDL file that contains the description, not at the top level. The contents will be black-boxed.

• If you want to define a black box when you have an srs, ngc, or edf description for it, remove the description from the project.

Once you define a black box with syn\_black\_box, you use other source code directives to define timing for the black box. You must add the directives to the source code because the timing models are specific to individual instances. There are no corresponding Tcl directives you can add to a constraint file.

#### Black-box Source Code Directives

Use the following directives with syn\_black\_box to characterize black-box timing:

| syn_isclock     | Specifies a clock port on a black box.                                    |

|-----------------|---------------------------------------------------------------------------|

| syn_tpd <n></n> | Sets timing propagation for combinational delay through the black box.    |

| syn_tsu <n></n> | Defines timing setup delay required for input pins relative to the clock. |

| syn_tco <n></n> | Defines the timing clock to output delay through the black box.           |

#### Black Box Pin Definitions

You define the pins on a black box with these directives in the source code:

| black_box_pad_pin  | Indicates that a black box is an I/O pad for the rest of the design. |

|--------------------|----------------------------------------------------------------------|

| black_box_tri_pins | Indicates tristates on black boxes.                                  |

For more information on black boxes, see Instantiating Black Boxes in Verilog, on page 368, and Instantiating Black Boxes in VHDL, on page 572.

### syn\_black\_box Syntax Specification

| Verilog | <pre>object /* synthesis syn_black_box */;</pre>        | Verilog<br>Example |

|---------|---------------------------------------------------------|--------------------|

| VHDL    | attribute syn_black_box of object : objectType is true; | VHDL<br>Example    |

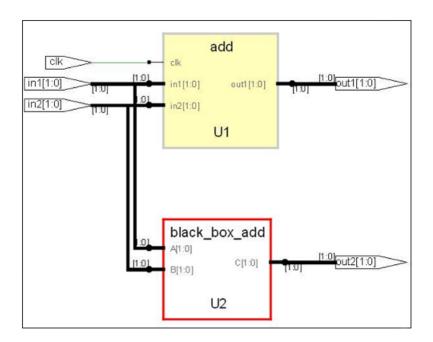

## **Verilog Example**

```

module top(clk, in1, in2, out1, out2);

input clk;

input [1:0] in1;

input [1:0] in2;

output [1:0]out1;

output [1:0]out2;

U1 (clk, in1, in2, out1);

black box_add U2 (in1, in2, out2);

endmodule

module add (clk, in1, in2, out1);

input clk;

input [1:0]in1;

input [1:0] in2;

output [1:0]out1;

reg [1:0] out1;

always@(posedge clk)

begin

out1 <= in1 + in2;

end

endmodule

module black box add(A, B, C)/* synthesis syn black box */;

input [1:0]A;

input [1:0]B;

output [1:0]C;

assign C = A + B;

endmodule

```

## **VHDL Example**

```

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic unsigned.all;

entity add is

port(

in1 : in std logic vector(1 downto 0);

in2 : in std logic vector(1 downto 0);

clk : in std logic;

out1 : out std logic vector(1 downto 0));

end;

architecture rtl of add is

begin

process(clk)

begin

if (clk'event and clk='1') then

out1 <= (in1 + in2);

end if;

end process;

end;

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic unsigned.all;

entity black box add is

port (

A : in std logic vector(1 downto 0);

B : in std logic_vector(1 downto 0);

C : out std_logic_vector(1 downto 0));

end:

architecture rtl of black box add is

attribute syn black box : boolean;

attribute syn black box of rtl: architecture is true;

begin

C \ll A + B;

end:

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic unsigned.all;

```

```

entity top is

port (

in1 : in std logic vector(1 downto 0);

in2 : in std logic vector(1 downto 0);

clk : in std logic;

out1 : out std logic vector(1 downto 0);

out2 : out std logic vector(1 downto 0));

end;

architecture rtl of top is

component add is

port (

in1 : in std logic vector(1 downto 0);

in2 : in std logic vector(1 downto 0);

clk : in std logic;

out1 : out std logic vector(1 downto 0));

end component;

component black box add

port (

A : in std logic vector(1 downto 0);

B : in std logic vector(1 downto 0);

C : out std logic vector(1 downto 0));

end component;

begin

U1: add port map(in1, in2, clk, out1);

U2: black box add port map(in1, in2, out2);

end:

```

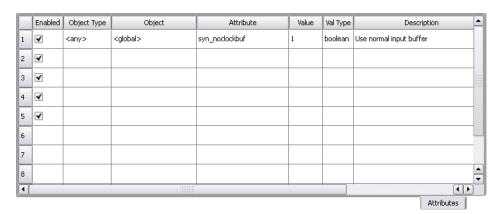

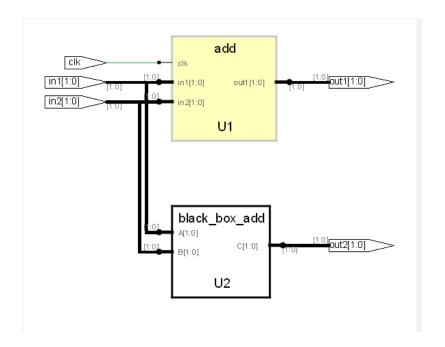

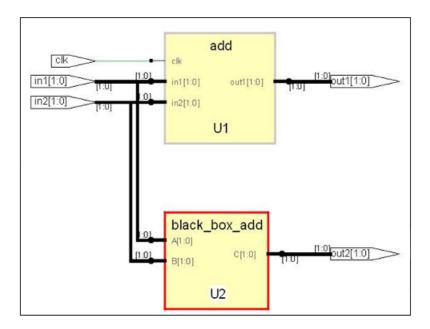

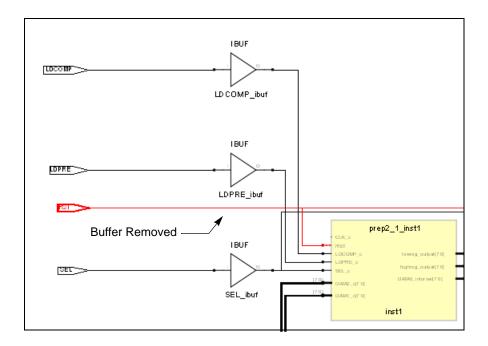

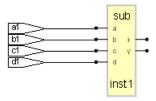

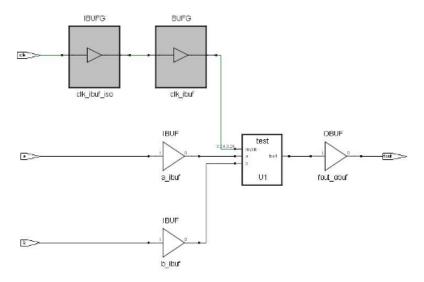

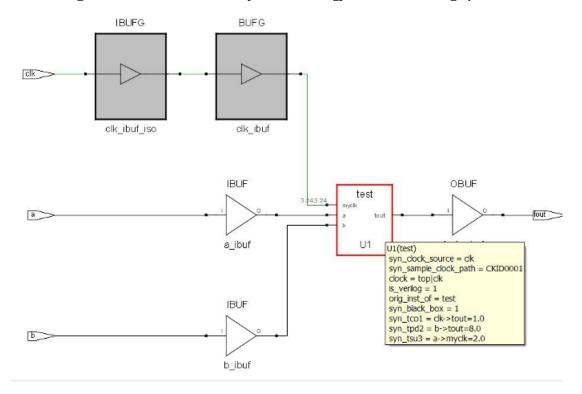

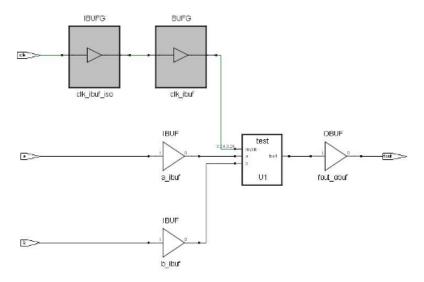

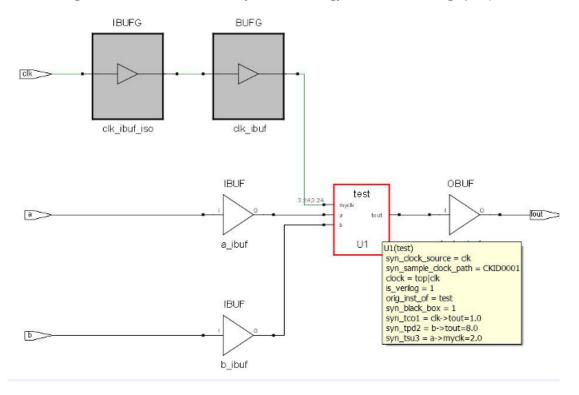

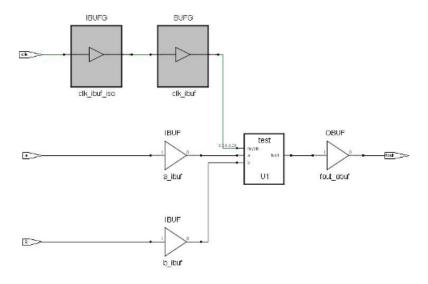

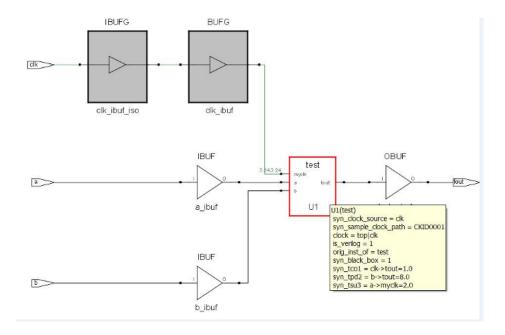

# Effect of Using syn\_black\_box

When the syn\_black\_box attribute is not set on the black\_box\_add module, its content are accessible, as shown in the example below:

```

module black box add(input [1:0]A, [1:0]B, output [1:0]C);

```

After applying syn\_black\_box, the contents of the black box are no longer visible:

module black\_box\_add(input [1:0]A, [1:0]B, output [1:0]C)/\*

synthesis syn black box \*/;

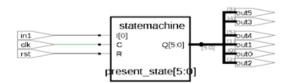

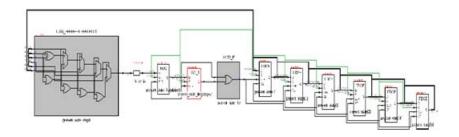

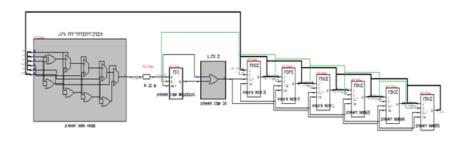

# syn\_encoding

#### Attribute

Overrides the default FSM Compiler encoding for a state machine and applies the specified encoding.

| Vendor    | Devices                        |

|-----------|--------------------------------|

| Microsemi | ProASIC3, Fusion, SmartFusion2 |

### syn\_encoding Values

The default is that the tool automatically picks an encoding style that results in the best performance. To ensure that a particular encoding style is used, explicitly specify that style, using the values below:

| Value  | Description                                                                                                                                                                                                                                                      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| onehot | Only two bits of the state register change (one goes to 0, one goes to 1) and only one of the state registers is hot (driven by 1) at a time. For example:                                                                                                       |

|        | 0001, 0010, 0100, 1000                                                                                                                                                                                                                                           |

|        | Because onehot is not a simple encoding (more than one bit can be set), the value must be decoded to determine the state. This encoding style can be slower than a gray style if you have a large output decoder following a state machine.                      |

| gray   | More than one of the state registers can be hot. The synthesis tool <i>attempts</i> to have only one bit of the state registers change at a time, but it can allow more than one bit to change, depending upon certain conditions for optimization. For example: |

|        | 000, 001, 011, 010, 110                                                                                                                                                                                                                                          |

|        | Because gray is not a simple encoding (more than one bit can be set), the value must be decoded to determine the state. This encoding style can be faster than a onehot style if you have a large output decoder following a state machine.                      |

#### Value Description

#### sequential

More than one bit of the state register can be hot. The synthesis tool makes no attempt at limiting the number of bits that can change at a time. For example:

000, 001, 010, 011, 100

This is one of the smallest encoding styles, so it is often used when area is a concern. Because more than one bit can be set (1), the value must be decoded to determine the state. This encoding style can be faster than a onehot style if you have a large output decoder following a state machine.

#### safe

This implements the state machine in the default encoding and adds reset logic to force the state machine to a known state if it reaches an invalid state. This value can be used in combination with any of the other encoding styles described above. You specify safe before the encoding style. The safe value is only valid for a state register, in conjunction with an encoding style specification.

- For example, if the default encoding is onehot and the state machine reaches a state where all the bits are 0, which is an invalid state, the safe value ensures that the state machine is reset to a valid state.

- If recovery from an invalid state is a concern, it may be appropriate to use this encoding style, in conjunction with onehot, sequential or gray, in order to force the state machine to reset. When you specify safe, the state machine can be reset from an unknown state to its reset state.

- If an FSM with asynchronous reset is specified with the value safe and you do not want the additional recovery logic (flip-flop on the inactive clock edge) inserted for this FSM, then use the syn\_shift\_resetphase attribute to remove it. See <a href="mailto:syn\_shift\_resetphase">syn\_shift\_resetphase</a>, on page 200 for details.

#### original

This respects the encoding you set, but the software still does state machine and reachability analysis.

You can specify multiple values. This snippet uses safe,gray. The encoding style for register OUT is set to gray, but if the state machine reaches an invalid state the synthesis tool will reset the values to a valid state.

```

module prep3 (CLK, RST, IN, OUT);

input CLK, RST;

input [7:0] IN;

output [7:0] OUT;

reg [7:0] OUT;

reg [7:0] current_state /* synthesis syn_encoding="safe,gray" */;

// Other code

```

## **Description**

This attribute takes effect only when FSM Compiler is enabled. It overrides the default FSM Compiler encoding for a state machine. For the specified encoding to take effect, the design must contain state machines that have been inferred by the FSM Compiler. Setting this attribute when syn state machine is set to 0 will not have any effect.

The default encoding style automatically assigns encoding based on the number of states in the state machine. Use the syn\_encoding attribute when you want to override these defaults. You can also use syn\_encoding when you want to disable the FSM Compiler globally but there are a select number of state registers in your design that you want extracted. In this case, use this attribute with the syn\_state\_machine directive on for just those specific registers.

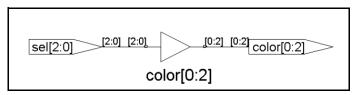

The encoding specified by this attribute applies to the final mapped netlist. For other kinds of enumerated encoding, use syn\_enum\_encoding. See syn\_enum\_encoding, on page 63 and syn\_encoding Compared to syn\_enum\_encoding, on page 65 for more information.

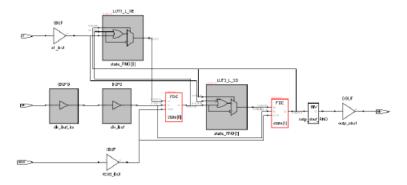

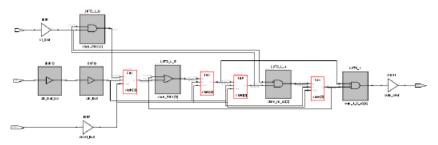

### **Encoding Style Implementation**

The encoding style is implemented during the mapping phase. A message appears when the synthesis tool extracts a state machine, for example:

```

@N: CL201 : "c:\design\..."|Trying to extract state machine for register current state

```

The log file reports the encoding styles used for the state machines in your design. This information is also available in the FSM Viewer.

See also the following:

- For information on enabling state machine optimization for individual modules, see syn\_state\_machine, on page 204.

- For VHDL designs, see syn\_encoding Compared to syn\_enum\_encoding, on page 65 for comparative usage information.

## **Syntax Specification**

#### Global Object

| No | Instance, register |  |

|----|--------------------|--|

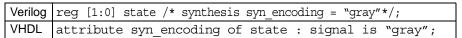

This table shows how to specify the attribute in different files:

| FDC     | define_attribute {object} syn_encoding {value}           | SCOPE Example   |

|---------|----------------------------------------------------------|-----------------|

| Verilog | Object /* synthesis syn_encoding = "value" */;           | Verilog Example |

| VHDL    | attribute syn_encoding of object: objectType is "value"; | VHDL Example    |

If you specify the syn\_encoding attribute in Verilog or VHDL, all instances of that FSM use the same syn\_encoding value. To have unique syn\_encoding values for each FSM instance, use different entities or modules, or specify the syn encoding attribute in a constraint file.

### **SCOPE Example**

|   |   | Enabled | Object Type | Object       | Attribute    | Value | Val Type | Description                                             |

|---|---|---------|-------------|--------------|--------------|-------|----------|---------------------------------------------------------|

| ĺ | 1 | •       | fsm         | i:state[3:0] | syn_encoding | gray  |          | FSM encoding (onehot, sequential, gray, original, safe) |

The *object* must be an instance prefixed with **i**:, as in **i**:*instance*. The instance must be a sequential instance with a view name of statemachine.

Although you cannot set this attribute globally, you can define a SCOPE collection and then apply the attribute to the collection. For example:

```

define_scope_collection sm {find -hier -inst * -filter

@inst_of==statemachine}

define attribute {$sm} {syn encoding} {safe}

```

### **Verilog Example**

The object can be a register definition signals that hold the state values of state machines.

```

module fsm (clk, reset, x1, outp);

input

clk, reset, x1;

output

outp;

reg

outp;

reg [1:0] state /* synthesis syn encoding = "onehot" */;

parameter s1 = 2'b00; parameter s2 = 2'b01;

parameter s3 = 2'b10; parameter s4 = 2'b11;

always @(posedge clk or posedge reset)

begin

if (reset)

state <= s1;

else begin

case (state)

s1: if (x1 == 1'b1)

state <= s2;

else

state <= s3; s2: state <= s4;

s3: state <= s4;

s4: state <= s1;

endcase

end

end

always @(state) begin

case (state)

s1: outp = 1'b1;

s2: outp = 1'b1;

s3: outp = 1'b0;

s4: outp = 1'b0;

endcase

end

endmodule

```

# **VHDL Example**

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity fsm is

port (x1 : in std_logic;

reset : in std_logic;

clk : in std_logic;

outp : out std_logic);

end fsm;

```

```

architecture rtl of fsm is

signal state : std logic vector(1 downto 0);

constant s1 : std logic vector := "00";

constant s2 : std logic vector := "01";

constant s3 : std logic vector := "10";

constant s4 : std logic vector := "11";

attribute syn encoding : string;

attribute syn encoding of state : signal is "onehot";

begin

process (clk, reset)

begin

if (clk'event and clk = '1') then

if (reset = '1') then

state <= s1;

else

case state is

when s1 =>

if x1 = '1' then

state <= s2;

else

state <= s3;

end if;

when s2 =>

state <= s4;

when s3 =>

state <= s4;

when s4 =>

state <= s1;

end case;

end if;

end if;

end process;

process (state)

begin

case state is

when s1 =>

outp <= '1';

when s2 =>

outp <= '1';

when s3 =>

outp <= '0';

```

```

when s4 =>

outp <= '0';