# Using SHA-256 System Services in SmartFusion2 and IGLOO2 Devices - Libero SoC v11.4

#### **Table of Contents**

| Purpose                                                         |

|-----------------------------------------------------------------|

| Introduction                                                    |

| Reference                                                       |

| Design Requirements and Details                                 |

| Overview of SHA-256 Function in SmartFusion2 and IGLOO2 SHA-256 |

| Cryptographic Services Block in SmartFusion2 and IGLOO2         |

| Cryptographic Services Block in SmartFusion2 Device             |

| Cryptographic Services Block in IGLOO2 Device                   |

| Using SHA-256 System Services in SmartFusion2 and IGLOO2 Device |

| Design Description                                              |

| Design Example 1: Using SHA-256 Services in SmartFusion2 Device |

| Hardware Implementation                                         |

| Software Implementation                                         |

| Running the Design                                              |

| Design Example 2: Using SHA-256 Services in IGLOO2 Device       |

| Hardware Implementation                                         |

| Running the Design                                              |

| Conclusion                                                      |

| Appendix A - Design and Programming Files                       |

| List of Changes                                                 |

## **Purpose**

This application note provides the design example for using the secure hash algorithm (SHA)-256 accelerator block in the SmartFusion®2 system-on-chip (SoC) field programmable gate array (FPGA) devices and IGLOO®2 devices.

### Introduction

SHA is a cryptographic hash function that can process a message to produce a condensed representation called a message digest. The SHA-256 algorithm is part of the standard SHA algorithm, defined in the National Institute of Standards and Technology (NIST) as a U.S. Federal Information Processing Standard (FIPS) 180-3. The built-in SHA-256 accelerator block can be accessed and performed the SHA-256 operation in the selected devices of the SmartFusion2 SoC FPGA and IGLOO2 FPGA families. These devices are marked as S (Data and Design Security) in the device part number. The SHA-256 accelerator block, also known as SHA-256 engine, resides inside the System Controller of the SmartFusion2 SoC FPGA and IGLOO2 FPGA devices. The SHA-256 accelerator block is accessible through the SHA-256 system services. The system services are system controller actions initiated by asynchronous events from the ARM® Cortex®-M3 processor in the SmartFusion2 device or a Fabric Master in the SmartFusion2/IGLOO2 devices. In SmartFusion2 and IGLOO2 devices, the SHA-256 engine can take message inputs of any size up to 2<sup>32</sup> bits in length and digest them down to a 256-bit result, as per the SHA-256 standard. The SHA-256 Cryptographic Services can be used for data security applications and disabled using factory or user security settings. This application note describes how to use the SHA-256 accelerator block using SHA-256 system service in the SmartFusion2 and IGLOO2 devices.

## Reference

The following references are used in this document.

- SmartFusion2 Microcontroller Subsystem User Guide

- SmartFusion2 Security and Reliability User Guide

- SmartFusion2 SoC Security FPGAs

- IGLOO2 FPGA High Performance Memory Subsystem User Guide

- IGLOO2 Security and Reliability User Guide

- IGLOO2 Security FPGAs

## **Design Requirements and Details**

Table 1 lists the SmartFusion2 design requirements and details.

Table 1 • SmartFusion2 Design Requirements and Details

| Design Requirements and Details                    | Description                         |

|----------------------------------------------------|-------------------------------------|

| Hardware Requirements                              |                                     |

| SmartFusion2 Evaluation Kit (M2S090S-EVAL-KIT)     | Rev D                               |

| 12 V adapter (provided along with the kit)         |                                     |

| FlashPro4 programmer (provided along with the kit) |                                     |

| • M2S090TS-FGG484                                  |                                     |

| Host PC or Laptop                                  | Any 64-bit Windows Operating System |

| Software Requirements                              |                                     |

| Libero® System-on-Chip (SoC)                       | v11.4                               |

| SoftConsole                                        | v3.4 SP1                            |

| ModelSim <sup>®</sup>                              | -                                   |

Table 2 lists the IGLOO2 design requirements and details.

#### Table 2 • IGLOO2 Design Requirements and Details

| Design Requirements and Details                                                                                                                                                                         | Description                         |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|--|--|--|

| Hardware Requirements                                                                                                                                                                                   |                                     |  |  |  |  |  |  |

| <ul> <li>IGLOO2 Evaluation Kit (M2GL090S-EVAL-KIT)</li> <li>12 V adapter (provided along with the kit)</li> <li>FlashPro4 programmer (provided along with the kit)</li> <li>M2GL090TS-FGG484</li> </ul> | Rev D                               |  |  |  |  |  |  |

| Host PC or Laptop                                                                                                                                                                                       | Any 64-bit Windows Operating System |  |  |  |  |  |  |

| Software Requirements                                                                                                                                                                                   |                                     |  |  |  |  |  |  |

| Libero SoC                                                                                                                                                                                              | v11.4                               |  |  |  |  |  |  |

## Overview of SHA-256 Function in SmartFusion2 and IGLOO2 SHA-256

In the SmartFusion2 and IGLOO2 devices, the SHA-256 accelerator block is part of the Cryptographic Services block that resides in the System Controller. The SHA-256 accelerator block implements the SHA-256 function.

SHA is a cryptographic hash function designed by the U.S. National Security Agency (NSA) and published in 2001 by the NIST - FIPS. This Standard specifies several secure hash algorithms, including SHA-256. SHA-256 is a one-way hash function that can process a message to produce a message digest. In this application note, the term message digest and hashed output are used interchangeably. The input data is message and hash value is message digest.

The SHA-256 algorithm determines the integrity of the message – any change to the message, with a very high probability, results in a different message digest. This property is widely used in security applications and protocol, generation and verification of digital signatures and message authentication codes, and so on. Following are the basic properties of the SHA-256 algorithm:

Message size: < 2<sup>64</sup> bits

Block size: 512 bitsWord size: 32 bits

· Message digest size: 256 bits

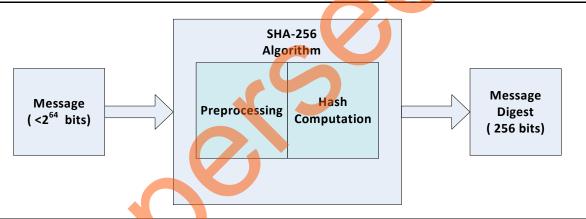

.Figure 1 shows the basic SHA-256 operation.

Figure 1 • SHA-256 Operation

The SHA-256 algorithm includes the following two stages:

- Preprocessing

- Hash computation

Preprocessing involves padding a message, parsing the padded message into 512-bit blocks, and setting initialization values to be used in the hash computation. The hash computation generates a message scheduled from the padded message and uses that schedule, along with functions, constants, and word operations to iteratively generate a series of hash values. The final hash value generated by the hash computation is used to determine the message digest. For more information about preprocessing and hash computation, refer to FIPS PUB 180-3 publication.

Note: The hash algorithms is secured. For a given algorithm, it is computationally infeasible to:

- · find a message that corresponds to a given message digest or

- find two different messages that produce the same message digest

Any change to a message, with a very high probability, results in a different message digest.

In the SmartFusion2 and IGLOO2 devices, the SHA-256 accelerator block can take message inputs of any size up to  $2^{32}$  bits in length and process to a 256-bit result, as per the standard. If the message ends with a partial byte, the significant bits are assumed to be at the least significant bit (LSB) end of the byte. The unused most significant bits (MSBs) of the final byte are ignored. The input and output data format of the SHA-256 system service is little-endian type.

In SmartFusion2 and IGLOO2, the SHA accelerator block does not have built-in algorithm-level distributed power architecture (DPA) countermeasures. So, the built-in design security applications are only used in protocols that effectively prevent DPA attacks from succeeding. When hashing is used with a secret value such as a key, the SmartFusion2 and IGLOO2 device built-in design security protocols strictly limit the number of uses of the secret to prevent its leaking through side-channels. Hashing is used with public data, where no secrets are processed, a low DPA resistance may not be a concern. However, when hashing is used in user data security applications involving secret data (such as an HMAC key), the user is responsible for using protocols that ensure that the same secret data is not used repeatedly, or it may become vulnerable to extraction using DPA techniques.

## Cryptographic Services Block in SmartFusion2 and GLOO2

In the SmartFusion2 and IGLOO2 devices, the SHA-256 accelerator block is part of the Cryptographic Services block that resides inside the System Controller. This following sub-sections describe the Cryptographic Services block along with the System Controller.

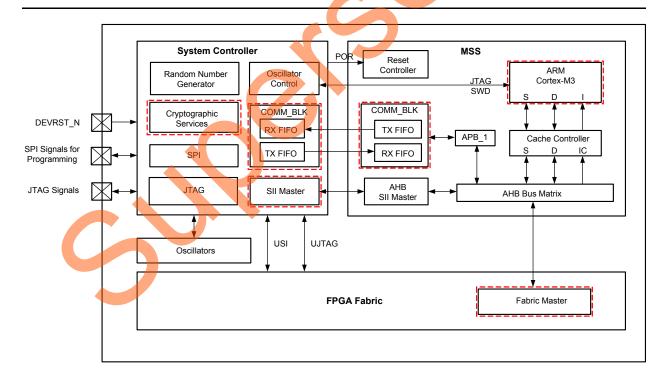

#### Cryptographic Services Block in SmartFusion2 Device

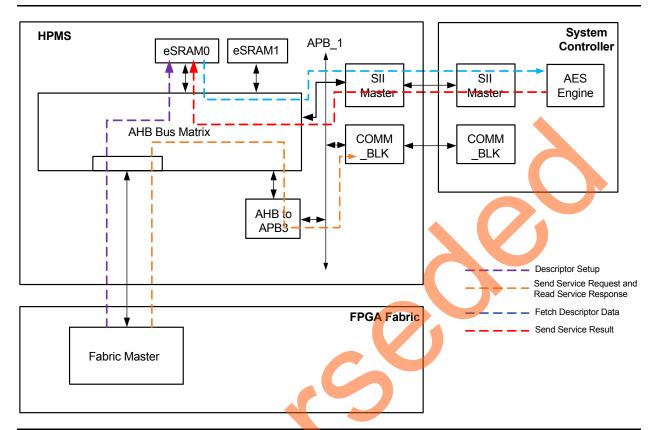

The Cryptographic Services block can be accessed through the communication block, COMM\_BLK. There are two communication block (COMM\_BLK) instances — one is in the microcontroller subsystem (MSS) and the other one is in the System Controller, which communicate with each other. The COMM\_BLK consists of an advanced peripheral bus (APB) interface, eight-byte transmit FIFO, and eight-byte receive FIFO. For more information, refer to the COMM\_BLK chapter in *SmartFusion2 Microcontroller Subsystem User Guide*, and *IGLOO2 FPGA High Performance Memory Subsystem User Guide*. The COMM\_BLK provides a bi-directional message passing facility between the MSS and the System Controller. Figure 2 shows the SmartFusion2 blocks used for SHA-256 system service.

Figure 2 • System Controller Block in SmartFusion2 Device

The SHA-256 system services are initiated using the COMM\_BLK block in the MSS. The SHA-256 system services can be read or write by any master on the advanced microcontroller bus architecture (AMBA®) high-performance bus (AHB) matrix; either by the Cortex-M3 processor or a design in the FPGA Fabric (also known as a Fabric Master). The System Controller receives the command through the COMM\_BLK block in the System Controller. The System Controller uses the system IP interface (SII) master to transfer data to and from the MSS memory space for system services. When the SHA-256 service is requested, the data structure is written to the COMM\_BLK block that contains the address in the memory of the input and resultant data, length of the data, and status. For more information about the data structure, refer to Table 3 on page 6. The message digest (SHA-256 hashed output) from SHA-256 operation returned by the System Controller is written to a memory address specified in this data structure. On completion of the requested service, the System Controller returns a status message through the COMM\_BLK block.

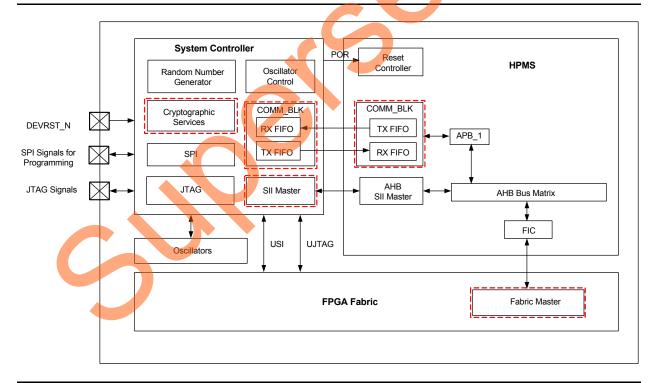

#### Cryptographic Services Block in IGLOO2 Device

The architecture and uses of the SHA-256 accelerator block in IGLOO2 is similar to the SmartFusion2 device. The exceptions are:

- The COMM\_BLK in the System Controller communicates with the COMM\_BLK in the high performance memory subsystem (HPMS).

- A Fabric Master can initiate the SHA-256 system services.

Microsemi<sup>®</sup> provides the CoreSysServices DirectCore IP that acts as Fabric Master to use the SHA-256 system services. The CoreSysServices DirectCore IP communicates with the COMM\_BLK block through one of the fabric interface controllers (FICs) to send the SHA-256 system service request, retrieve the message digest, and send it back to the user interface. Figure 3 shows the IGLOO2 blocks used in SHA-256 system service.

Figure 3 • System Controller Block in IGLOO2 Device

For more information about the System Controller, refer to SmartFusion2 System Controller User Guide and IGLOO2 FPGA System Controller User Guide. For more information about the COMM\_BLK block, refer to the Communication Block chapter in the SmartFusion2 Microcontroller Subsystem User Guide, and IGLOO2 FPGA High Performance Memory Subsystem User Guide.

## Using SHA-256 System Services in SmartFusion2 and IGLOO2 Device

This section describes the steps for accessing the SHA-256 system service in SmartFusion2 or IGLOO2 and its use model. Table 3 and Table 4 list the data, and response data structures associated with this system service.

Following are the main steps to use the SHA-256 system service in the SmartFusion2 or IGLOO2 device:

1. Set up the SHA256DATA descriptor data in the user memory space as listed in Table 3, containing the following 12 bytes:

Table 3 • SHA256DATA Structure

| Offset | Length (bytes) | Field         | Description                                                                 |

|--------|----------------|---------------|-----------------------------------------------------------------------------|

| 0      | 4              | LENGTH        | Length of data pointed to by DATAINPTR field in bits (up to $2^{32}$ bits). |

| 4      | 4              | HASHRESULTPTR | Pointer to 32-byte buffer to receive 256-bit hash result.                   |

| 8      | 4              | DATAINPTR     | Pointer to data to be hashed.                                               |

- 2. Set up the input data at DATAINPTR location.

- For embedded design in SmartFusion2, enable COMM\_BLK\_INTR (INTISR[19]) in Cortex-M3

Processor Interrupts. For fabric design in SmartFusion2 or IGLOO2, enable the COMBLK\_INTR

interrupt from the COMM\_BLK block to fabric by enabling COMBLK\_INTR\_ENBL bit (2th bit) in

INTERRUPT\_ENABLE0 register at address 0x40006000.

- 4. Set up the COMM\_BLK register in byte mode and send the SHA-256 command. The command value of the SHA-256 Cryptographic Service is 0x0A (decimal 10).

- 5. Wait for RCVOKAY bit to be set in the COMM\_BLK STATUS register.

- The System Controller receives the command through the COMM\_BLK block in the System Controller. The system controller reads the data from the address pointer and generates the message digest. On completion, the service system controller returns a status message through the COMM\_BLK. Once the status message is received, RCVOKAY bit is set.

- 6. Read the Word Data register in the COMM\_BLK and check the command, status code, and SHA256DATAPTR descriptor pointer as listed in Table 4.

Table 4 • SHA-256 Service Response

| Offset | Length (bytes) |    | Field    |     | Description                                   |

|--------|----------------|----|----------|-----|-----------------------------------------------|

| 0      | 1              |    | CMD = 10 |     | Command                                       |

| 1      | 1              |    | STATUS   |     | Command status:                               |

|        |                |    |          |     | 0: Success                                    |

|        |                |    |          |     | 127: HRESP error occurred during MSS transfer |

|        |                |    |          |     | 253: Not licensed                             |

|        |                |    |          |     | 254: Service disabled by factory security     |

|        |                |    |          |     | 255: Service disabled by user security        |

| 2      | 4              | SH | A256DATA | PTR | Pointer to SHA256DATA structure               |

7. If STATUS is successful, read the message digest data from user memory space (the return data buffer address is specified in DATAINPTR).

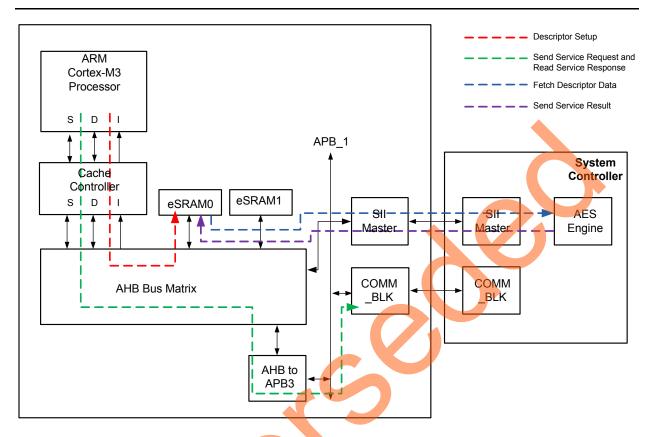

Figure 4 shows the system service data flow diagram in the SmartFusion2 device from the Cortex-M3 processor using eSRAM0 for input data and message digest output.

Figure 4 • SHA-256 Service Flow Diagram in SmartFusion2 Device

Figure 5 shows the system service data flow diagram in the IGLOO2 device using eSRAM0 for input data and message digest output.

Figure 5 • SHA-256 Service Flow Diagram in IGLOO2 Device

Microsemi provides a system service driver and CoreSysServices soft IP to run the SHA-256 operation in SmartFusion2 and IGLOO2. So, the user does not need to write software code from scratch or create a complex master in fabric to run the SHA-256 system services.

In SmartfFusion2, the SHA-256 system can be accessed:

- using mss sys services driver in the firmware core configurator

- using CoreSysServices as Fabric Master

In the IGLOO2 device, CoreSysServices soft IP can be used as fabric master to run SHA-256 system service. CoreSysServices provides a simple user interface on one side and an AHB-Lite master interface to connect to the FIC to use system services through the COMM\_BLK block. The IGLOO2 approach can be used in the SmartFusion2 device too. For more information about the CoreSysServices soft IP, refer to the CoreSysServices Handbook.

## **Design Description**

This application note includes the following design examples to use the SHA-256 system service:

- SHA\_256\_Services\_SF2: This design demonstrates the running SHA-256 system service in the SmartFusion2 device using the system driver firmware code supplied by Microsemi.

- SHA\_256\_Services\_IGL2 design example: This design demonstrates the running SHA-256 system service in the IGLOO2 device using the CoreSysServices IP core supplied by Microsemi.

The SmartFusion2 device design is implemented on the *SmartFusion2 Evaluation Kit Board* using an M2S090TS-FG484 device and the IGLOO2 device design is implemented on the *IGLOO2 Evaluation Kit Board* using an M2GL090TS-FGG484 device.

## Design Example 1: Using SHA-256 Services in SmartFusion2 Device

The design consists of an RC oscillator, a Fabric CCC (FCCC), and the MSS. The Fabric PLL(FPLL) is used to provide the base clock for the MSS. The system services are run using C routine in the MSS, as described in the "Software Implementation" section. In addition, a universal asynchronous receiver/transmitter (MMUART1) in the MSS is used to display the operation of the SHA-256 system service.

#### **Hardware Implementation**

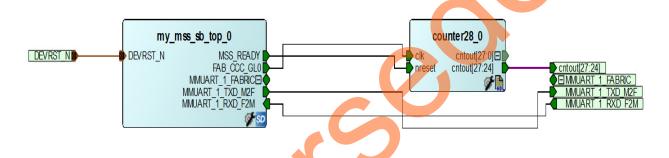

Figure 6 on page 9 shows a block diagram of the first design example. The RC oscillator generates a 50 MHz input clock and the FPLL generates a 100 MHz clock from the RC oscillator. This 100 MHz clock is used as the base clock for the MSS. The MMUART\_1 signals are routed through the FPGA fabric to communicate with the serial terminal program. The counter block is used to show that the device is up and running.

Figure 6 • SmartFusion2 SHA-256 System Service Design

#### Software Implementation

The software design performs the following operations:

- Initializes the System Service Driver

- Initializes MMUART 1

- Performs SHA-256 Cryptographic Services

#### sha 256 checksum()

The sha\_256\_checksum() function provides access to the SmartFusion2 SHA-256 encryption Cryptographic Service. It allows the user to provide 64 bytes (512-bits) of input data/text, This input is used for hashing to generate 256-bit message digest.

### **Running the Design**

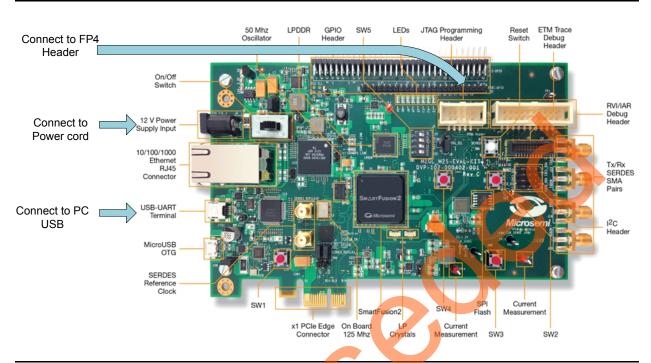

The following steps describe how to run the design on the SmartFusion2 Evaluation Kit board using the M2S090TS-FG484 device:

- Connect the power supply to the M2S\_EVAL\_Kit board and power on the board using SW7.

- 2. Plug the FlashPro4 ribbon cable into the JTAG Programming Header on the SmartFusion2 Evaluation Kit board.

- 3. Program the SmartFusion2 Evaluation Kit board with the provided STAPL file (refer to "Appendix A Design and Programming Files " on page 16) using FlashPro4.

4. Connect one end of the USB Mini-B cable to the J18 connector provided in the SmartFusion2 Evaluation Kit board. Connect the other end of the USB cable to the Host PC.

Figure 7 • SmartFusion2 Evaluation Kit Board

- 5. Invoke the SoftConsole Integrated Design Environment (IDE), open the included SoftConsole project and launch the debugger.

- 6. Start a HyperTerminal session with 57600 baud rate, 8 data bits, 1 stop bit, no parity, and no flow control. If the computer does not have the HyperTerminal program, use any free serial terminal emulation program such as PuTTY or Tera Term. For configuring HyperTerminal, TeraTerm, or PuTTY, refer to Configuring Serial Terminal Emulation Programs Tutorial.

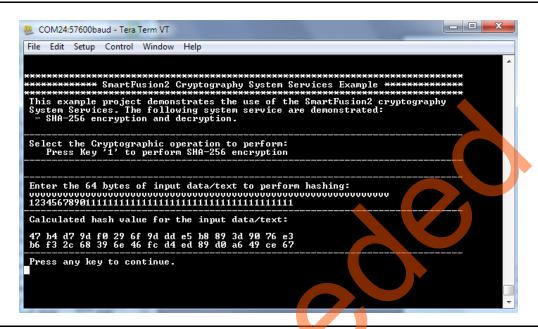

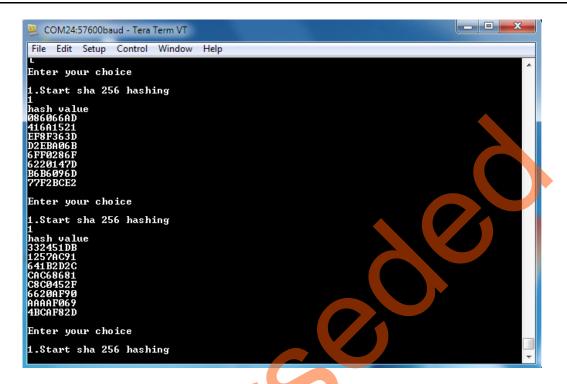

7. Run the debugger in the SoftConsole tool. The **HyperTerminal** window shows various options to run the SHA-256 operation. Follow the instruction on the screen to run the example. Figure 8 shows the **HyperTerminal** window showing SHA-256 operation.

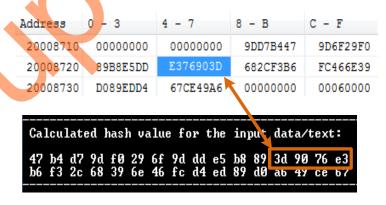

Figure 8 • SHA-256 System Service Design using HyperTerminal

Note: The ASCII-Hex notation is used as input by the program so that the data is easily readable. The ASCII characters are selected by the value from the ordered sixteen character set 0-9 and a-f. The input data goes from the first byte to the last byte of the multi-byte message entered and displayed from left to right as shown by the terminal emulator. Each input ASCII byte represents two Hex bytes. For example, if 1 is entered as ASCII input, it is converted into Hex input 31 for SHA-256 input. So, the 64-byte ASCII input is used as 512-bit Hex input. However, the message digest output is displayed in Hex format in endian order (from left to right and then top to bottom), as shown in Figure 9.

Figure 9 • Message Digest Output Mapping between SoftConsole Memory Viewer and HyperTerminal

## Design Example 2: Using SHA-256 Services in IGLOO2 Device

The design consists of the following:

- IGLOO2 HPMS

- An on-chip 50 MHz RC oscillator

- A FCCC

- A CoreSysServices IP block

- · A CoreRESET IP block

- A CoreABC IP block

- A CoreUARTapb IP block

- · A Fabric state machine to control the CoreSysServices block

- An APB data block to reformat the message digest output, so that it can be displayed by a terminal emulator.

#### **Hardware Implementation**

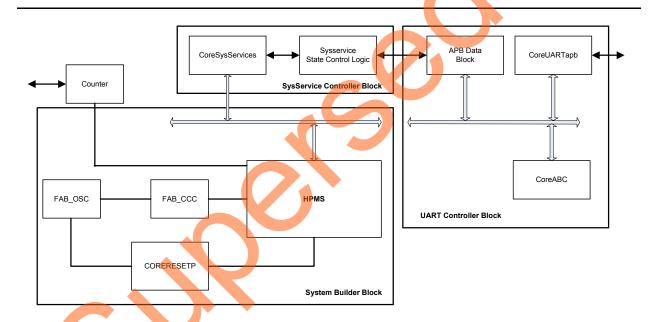

Figure 10 shows the block diagram of the IGLOO2 design. The main blocks are system builder block, Sysservice controller block, and UART controller block.

Figure 10 • IGLOO2 SHA-256 System Service Design

#### System Builder Block

This block includes a 50 MHz RC oscillator that is used as the main clock. It is used with a CCC to provide a 100 MHz reference clock to the HPMS. This 100 MHz clock is also used as main clock for the Fabric blocks. CoreResetP generates reset signals for all the blocks.

#### Sysservice Controller Block

This is the main block that uses CoreSysServices IP to run the SHA-256 system services. CoreSysServices IP sends the SHA-256 command to the System Controller through the COMM\_BLK block in the HPMS. The Fabric Sysservice state control logic connects to the user interface of CoreSysServices IP. This state control logic initiates the SHA-256 system service and captures the digest data from CoreSysService. The fabric Sysservice state block sends the input data/message that is basically a big-endian binary counter and the four MSBs are connected 4-bit DIP switch input in the board. The counter increments after every SHA-256 operation. The incremented value is used as input for the next operation.

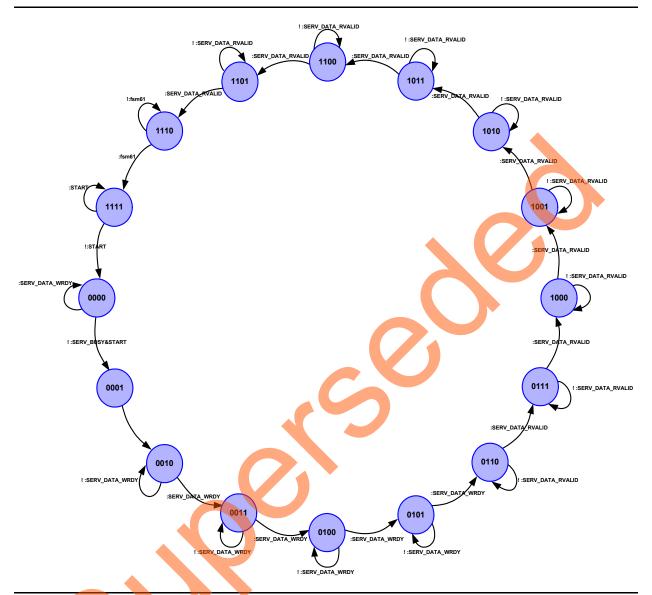

Figure 11 shows the state machine for the Sysservice block.

Figure 11 • Sysservice State block - State Diagram

#### **UART Controller Block**

The UART controller block takes the user input and initiates the SHA-256 operation. It is also used to display the Hashed output to HyperTerminal. The UART controller block has the following three main components:

- · APB data block

- CoreABC block

- CoreUARTapb block

The APB data block captures the message digest data and converts the binary data to ASCII Hex data to display in human readable format on the HyperTerminal. The CoreABC program controls initiating fabric state machine and displaying the data through the CoreUARTapb interface. In addition, there is a counter block used to show that the device is up and running.

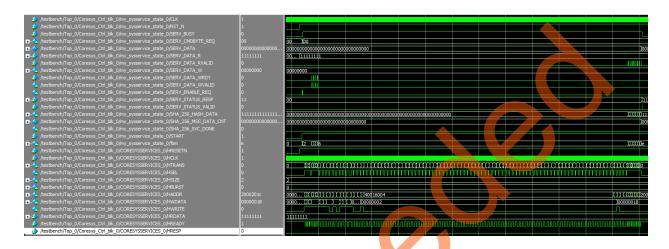

#### Simulating IGLOO2 SHA-256 System Service Design

The design file includes the testbench files and ModelSim do-file to run simulation in the Libero SoC software. The simulation uses the system service memory model in the SmartFusion2 simulation library to exercise the data transfer between the HPMS and the Fabric. The ModelSim do file, named run\_sha.do, forces START signal in the CoreSysCtrl block to initiate the state machine for SHA-256 operation. Figure 12 shows the simulation waveform displaying CoreSysServices IP user interface and AHB-lite interface.

Figure 12 • Sysservice State Block Simulation Waveform

#### **Running the Design**

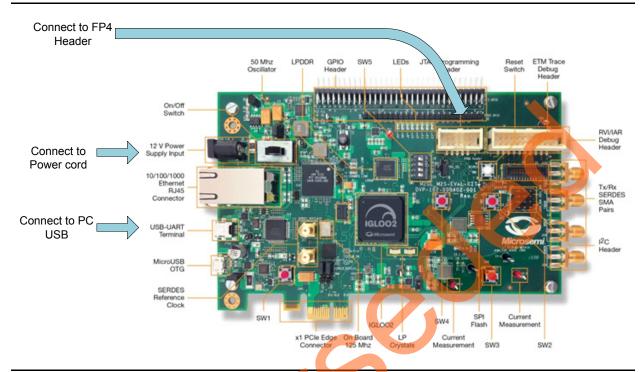

This section describes how to run the design in the IGLOO2 Evaluation Kit board using the M2GL090TS-FG484 device:

- Connect the power supply to the IGLOO2 Evaluation Kit board and power on the board using SW7.

- 2. Plug the FlashPro4 ribbon cable into connector J5 (JTAG Programming Header) on the IGLOO2 Evaluation Kit board (refer to Figure 13 on page 15).

- 3. Connect the mini USB cable between the FlashPro4 and the USB port of the Host PC.

4. Connect one end of the USB mini-B cable to the J18 connector provided on the IGLOO2 Evaluation Kit board. Connect the other end of the USB cable to the Host PC. Ensure that the USB to UART bridge drivers are automatically detected (can be verified in the Device Manager).

Figure 13 • IGLOO2 Evaluation Kit Board

- 5. If USB to UART bridge drivers are not installed, download and install the drivers from www.microsemi.com/soc/documents/CDM 2.08.24 WHQL Certified.zip.

- 6. Start a HyperTerminal session with 57600 baud rate, 8 data bits, 1 stop bit, no parity, and no flow control. If the computer does not have the HyperTerminal program, any free serial terminal emulation program such as PuTTY or Tera Term can be used. Refer to Configuring Serial Terminal Emulation Programs Tutorial for configuring HyperTerminal, Tera Term, or PuTTY.

- 7. Program the IGLOO2 Evaluation Kit board with the provided STAPL file (refer to "Appendix A Design and Programming Files" on page 16) using FlashPro4.

After programming, the HyperTerminal displays a message to run the SHA-256 system services as shown in Figure 14.

Figure 14 • SHA-256 System Service Design in IGLO02 using HyperTerminal

### Conclusion

The SmartFusion2 and IGLOO2 family of FPGAs are the most secure programmable logic devices. In selected SmartFusion2 and IGLOO2 devices, the SHA-256 accelerator block can perform SHA-256 operation as defined in NIST FIPS180-3. The SHA-256 system services, along with the other Cryptographic Services offered, allows to use the SmartFusion2 and IGLOO2 devices in various secure applications.

## **Appendix A - Design and Programming Files**

The SmartFusion2 and IGLOO2 SHA-256 design files can be downloaded from the Microsemi Corporation website: <a href="http://soc.microsemi.com/download/rsc/?f=sf2\_igl2\_sha\_256\_liberov11p4\_df">http://soc.microsemi.com/download/rsc/?f=sf2\_igl2\_sha\_256\_liberov11p4\_df</a>

The SmartFusion2 design file consists of both Libero VHDL and Verilog project, SoftConsole software project, and programming files (\*.stp) for the SmartFusion2 Evaluation Kit. The IGLOO2 design file consists of Libero VHDL and Verilog project and programming files (\*.stp) for the IGLOO2 Evaluation Kit. Refer to the Readme.txt file included in the design file folder for the directory structure and description.

## **List of Changes**

The following table lists critical changes that were made in each revision of the document.

| Revision*                      | Changes          | Page |

|--------------------------------|------------------|------|

| Revision 1<br>(September 2014) | Initial release. | NA   |

Note: \*The revision number is located in the part number after the hyphen. The part number is displayed at the bottom of the last page of the document. The digits following the slash indicate the month and year of publication.

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Sales: +1 (949) 380-6136

Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

and system solutions for communications, defense and security, aerospace, and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs, and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.