# Identify® Reference

June 2013

http://solvnet.synopsys.com

## **Copyright Notice and Proprietary Information**

© 2013 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the term© 2013 Synopsys, Inc.© 2013 Synopsys, Inc.s of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

## **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only.

Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

| "This document is duplicated with th | e permission of Synops | sys, Inc., for the |

|--------------------------------------|------------------------|--------------------|

| exclusive use of                     |                        | and its            |

| employees. This is copy number       | ,,                     |                    |

## **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

### **Disclaimer**

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

## Registered Trademarks (®)

Synopsys, AEON, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, CHIPit, CoMET, CODE V, Design Compiler, DesignWare, EMBED-IT!, Formality, Galaxy Custom Designer, Global Synthesis, HAPS, HapsTrak, HDL Analyst, HSIM, HSPICE, Identify, Leda, LightTools, MAST, METeor, ModelTools, NanoSim, NOVeA, OpenVera, ORA, PathMill, Physical Compiler, PrimeTime, SCOPE, Simply Better Results, SiVL, SNUG, SolvNet, Sonic Focus, STAR Memory System, Syndicated, Synplicity, the Synplicity logo, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, UMRBus, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

## Trademarks (™)

AFGen, Apollo, ARC, ASAP, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Cosmos, CosmosLE, CosmosScope, CRITIC, CustomExplorer, CustomSim, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, DesignerHDL, DesignPower, DFTMAX, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, HANEX, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping System, HSIMplus, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Intelli, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Macro-PLUS, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, ORAengineering, Physical Analyst, Planet, Planet-PL, Polaris, Power Compiler, Raphael, RippledMixer, Saturn, Scirocco, Scirocco-i, SiWare, Star-RCXT, Star-SimXT, StarRC, System Compiler, System Designer, Taurus, Total-Recall, TSUPREM-4, VCSi, VHDL Compiler, VMC, and Worksheet Buffer are trademarks of Synopsys, Inc.

## Service Marks (sm)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license.

ARM and AMBA are registered trademarks of ARM Limited.

Saber is a registered trademark of SabreMark Limited Partnership and is used under license.

All other product or company names may be trademarks of their respective owners.

Printed in the U.S.A June 2013

# Contents

| Chapter 1: Command Reference Introduction                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manual Conventions8Text Conventions8Syntax Conventions8Symbol Conventions9                                                                                                                                                                                                                                                                                                                             |

| Tool Conventions10File System Conventions10Design Hierarchy Conventions11                                                                                                                                                                                                                                                                                                                              |

| Chapter 2: Startup Modes           Synthesis Tool Pointers         16           HAPS Board Bring-up Utility         16           Configuring the Synthesis Tool         16           License Types         18           Synthesis Tool Command-Line Options         19           Custom Initialization Script         20           Script Locations         20           Scripting Priority         20 |

| Sample Initialization File                                                                                                                                                                                                                                                                                                                                                                             |

| Chapter 3: Command Concepts                                                                                                                                                                                                                                                                                                                                                                            |

| General Commands                                                                                                                                                                                                                                                                                                                                                                                       |

| File System Commands                                                                                                                                                                                                                                                                                                                                                                                   |

| Design Hierarchy Commands                                                                                                                                                                                                                                                                                                                                                                              |

| Design Instrumentation Commands                                                                                                                                                                                                                                                                                                                                                                        |

| Design Debugging Commands                                                                                                                                                                                                                                                                                                                                                                              |

# **Chapter 4: Alphabetical Command Reference**

| activation            |    |

|-----------------------|----|

| breakpoints           |    |

| cd                    |    |

| chain                 |    |

| clear                 |    |

| com                   | 35 |

| compile               | 38 |

| device                | 39 |

| encryption            | 43 |

| exit                  | 14 |

| help                  | 14 |

| haps                  | 45 |

| hierarchy             | 48 |

| idcode                | 53 |

| iice5                 | 55 |

| instrumentation       | 35 |

| jtag server           | 37 |

| licenseinfo6          |    |

| logicanalyzer6        |    |

| log                   |    |

| project               | 71 |

| pwd                   |    |

| remote trigger        |    |

| run                   | 74 |

| searchpath            |    |

| setsys                | 77 |

| show                  |    |

| signals               |    |

| source                |    |

| statemachine          |    |

| stop                  | 38 |

| transcript            |    |

| watch                 |    |

| waveform              |    |

| write instrumentation |    |

| write samples         |    |

| write vcd             |    |

| write vhdlmodel       |    |

|                       |    |

#### CHAPTER 1

# Command Reference Introduction

The Identify® tool set consists of the Identify instrumentor and the Identify debugger. These two tools allow you to debug your HDL design:

- · In the target system

- At the target speed

- At the VHDL/Verilog RTL Source level

The Identify tool set increases your debugging capabilities of high-end FPGA designs, FPGA-based prototypes, and system-on-a-chip designs. For the first time you will be able to debug live hardware with the internal design visibility you need while using intuitive debugging techniques.

To efficiently use the system and its underlying tools, this manual provides you with a comprehensive listing of all the commands the Identify tool set accepts. You can access this command information by concept listing or alphabetically.

In addition to easy look-up access to the commands, this manual also contains conventions that help display the command information easily and quickly. These manual conventions organize each command so that the information can be attained easily.

The remainder of this chapter describes:

- Manual Conventions

- Tool Conventions

## **Manual Conventions**

There are several conventions this manual uses in order to organize command information effectively. These conventions are:

| This convention   | Organizes this information                                                                                                                                                                                 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Text convention   | Text containing paths, directories, command names, and menu selections. All system specific command and path information has its own text convention to make is decipherable throughout the manual.        |

| Syntax convention | Symbols used to separate command examples and other important system text. Syntax conventions include any type of brackets and parentheses that separate commands and functions from the rest of the text. |

### **Text Conventions**

There are several text conventions this manual uses to organize command, path and directory information. These conventions or text styles are:

| This convention  | Organizes this information                 |

|------------------|--------------------------------------------|

| Bold             | command titles                             |

| Monospacing type | command, path name, and directory examples |

| Sans-serif type  | commands, literals, and keywords           |

| Italics          | variable arguments                         |

|                  |                                            |

## **Syntax Conventions**

There are several conventions this manual uses to convey command syntax. These conventions are:

| This convention | Organizes this information                                                                                             |

|-----------------|------------------------------------------------------------------------------------------------------------------------|

| bold            | Commands and literal arguments entered as shown.                                                                       |

| italics         | User-defined arguments or example command information.                                                                 |

| []              | Optional information or arguments for command use. Do not use these brackets with the command within the command line. |

|                 | Items that can be repeated any number of times.                                                                        |

| 1               | Choices you can make between two items or commands.<br>The items are located on either side of this of this symbol.    |

| #               | Comments concerning the code or information within the command line.                                                   |

| {}              | Escape characters for search strings; also entered in bold font as a literal in some commands                          |

## **Symbol Conventions**

This manual contains symbol conventions detailing the tools that use these commands. These symbols are located adjacent to the command name in any of the command listing chapters. These symbols are:

| This convention | Organizes this information                                                                                                                                                                                   |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •               | Any command that is used in the Identify instrumentor only. This symbol is located underneath any Identify instrumentor command in the command listing chapters.                                             |

| <b>D</b>        | Any command that is used in the Identify debugger only. This symbol is located underneath any Identify debugger command in the command listing chapters.                                                     |

| ••              | Any command that is used in both the Identify instrumentor and Identify debugger tools. This symbol is located underneath the commands that have applications in both tools in the command listing chapters. |

## **Tool Conventions**

There are tool concepts you must familiarize yourself with when using the Identify tool set. These concepts help you to decipher structural and HDL-related information.

## **File System Conventions**

The term file system refers to any command that uses file, directory, or path name information in its argument. A file system command must contain specific conventions.

### Path Separator "/"

All file system commands that contain a directory name use only forward slashes, regardless of the underlying operating system:

/usr/data.dat c:/Synopsys/data.dat

### Wildcards

A wildcard is a command element you can use to search for specific file information. You can use these wildcards in combination with the file system commands. Conventions for wildcards are as follows:

| Syntax | Description                        |

|--------|------------------------------------|

| *      | Matches any sequence of characters |

| 5      | Matches any single character       |

Square brackets are used in pattern matching as follows:

| Syntax | Description                                 |  |

|--------|---------------------------------------------|--|

| [abcd] | Matches any character in the specified set. |  |

| [a-d]  | Matches any character in a specified range. |  |

To use square brackets in wildcard specifications, you must delimit the entire name with curly braces {}. For example

$$\{ [a-d] 1 \}$$

matches any character in the specified range (a-d) preceding the character 1.

## **Design Hierarchy Conventions**

Design hierarchy refers to the structure of your design. Design hierarchy conventions define a way to refer to objects within the design hierarchy.

The Identify tool set supports VHDL and Verilog. These languages vary in their hierarchy conventions. The VHDL and Verilog languages contain design units and hierarchies of these design units. In VHDL, these design units are entity/architecture pairs, in Verilog they are modules. VHDL and Verilog design units are organized hierarchically. Each of the following HDL design units creates a new level in the hierarchy:

#### **VHDL**

- The top-level entity

- Architectures

- Component instantiation statements

- Process statements

- · Control flow statements: if-then-else, and case

- Subprogram statements

- Block statements

## **Verilog**

- The top-level module

- Module instantiation statements

- Always statements

- Control flow statements: if-then-else, and case

- · Functions and tasks

### **Design Hierarchy References**

A reference to an element in the design hierarchy consists of a path made up of references to design units (similar to a file reference described earlier). Regardless of the underlying HDL (VHDL or Verilog) the path separator character is always "/":

```

/inst/reset n

```

Absolute path names begin with a path separator character. The top-level design unit is represented by the initial "/". Thus, a port on the top-level design unit would be represented:

```

/port name

```

The architecture of the top-level VHDL design unit is represented:

/arch

Relative path names do not start with the path separator, and are relative to the current location in the design hierarchy. Initially, the current location is the top-level design unit, but commands exist that allow you to change the location.

**Note:** Design unit and hierarchy information can be case sensitive depending on the HDL language. VHDL names are not case sensitive. In contrast, all Verilog names are case sensitive.

#### Wildcards

A wildcard is a command element you can use to search for specific design hierarchy information. You can use these wildcards in combination with the design hierarchy commands. Conventions for wildcards are as follows:

| Syntax | Description                        |

|--------|------------------------------------|

| *      | Matches any sequence of characters |

| 5      | Matches any single character       |

Square brackets are used in hierarchy pattern matching as follows:

| Syntax | Description                                 |

|--------|---------------------------------------------|

| [abcd] | Matches any character in the specified set. |

| [a-d]  | Matches any character in a specified range. |

To use square brackets in pattern matching, you must delimit the entire name with curly braces {}. For example

matches any character in the specified range (a-d) preceding the character 1.

#### CHAPTER 2

# Startup Modes

The Identify instrumentor and the Identify debugger can be started in any of three execution modes as outlined below:

• identify instrumentor

Opens the Identify instrumentor in the graphical interface

• identify instrumentor -f fileName.tcl

Runs a Tcl startup file and then opens the Identify instrumentor in the graphical user interface.

• identify instrumentor shell [-version]

Opens the Identify instrumentor in the shell and/or script mode. If the optional -version argument is included, reports the software version without opening the Identify instrumentor.

identify debugger

Opens the Identify debugger in the graphical interface.

• identify debugger -f fileName.tcl

Runs a Tcl startup file and then opens the Identify debugger in the graphical user interface.

• identify\_debugger\_shell [-version]

Opens the Identify debugger in the shell and/or script mode. If the optional -version argument is included, reports the software version without opening the Identify debugger.

**Note:** Depending on the command shell, you may be required to provide the full path name to the program executable as well as the full path name to the files specified in any of the filename arguments.

## **Synthesis Tool Pointers**

When the Identify instrumentor or the Identify debugger is started from the command line, two additional arguments can be passed to the tool to identify the location and type of the synthesis tool associated with the project.

**Note:** The path to the synthesis tool and the tool type can also be defined after the Identify instrumentor or Identify debugger has been started as described in Command Line Configuration, on page 18.

The syntax of the two command-line arguments is:

-synplify install synthesisToolPath

-synplify\_tool synplify | synplify\_pro | synplify\_premier | synplify\_premier\_dp

The arguments are entered on the same command line in any order.

## **HAPS Board Bring-up Utility**

The Identify debugger can be launched in the board bring-up mode using the -board\_bringup option to the identify\_debugger GUI command:

identify\_debugger -board\_bringup

## **Configuring the Synthesis Tool**

When the Identify instrumentor or Identify debugger in launched from the synthesis tool GUI, the path to the synthesis tool and its tool type are defined.

When the Identify instrumentor or Identify debugger is started independently and then opens a synthesis project file, the path to the synthesis tool executable and the tool type must be defined either when starting the Identify instrumentor or Identify debugger (see Synthesis Tool Pointers above) or after the tool is started as defined in the following subsections.

**Note**: The Identify instrumentor uses the synthesis tool compiler to compile the design.

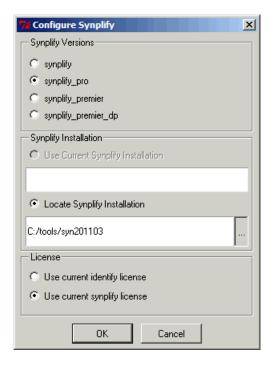

### **GUI Configuration**

To set the path to the synthesis tool from the Identify GUI:

1. Select Options->Configure Symplify from the menu to display the Configure Symplify dialog box.

- 2. In the dialog box:

- Select the corresponding synthesis tool radio button in the Synplify Versions section.

- Select the Locate Synplify Installation radio button and enter the path to the synthesis tool installation in the Synplify Installation section.

- Select the appropriate license radio button in the License section.

- 3. Click the OK button to accept the values and close the dialog box.

### **Command Line Configuration**

The path to the synthesis tool can also be set from the command line with a set synplify configuration command. The syntax for the command is:

set\_synplify\_configuration -type synToolVersion {-locate installPath |-current} -license identify|synplify [-help]

In the syntax, synToolVersion is synplify, synplify pro, synplify premier, or synplify premier dp and installPath is the path to the synthesis tool installation directory.

## **License Types**

All of the startup execution mode commands accept an optional -licensetype argument to specify a license type other than the default. The license type can be either a vendor-specific license or a full license.

**Note:** The -licensetype argument is required when initially starting the Identify instrumentor or Identify debugger in the shell mode.

The following values are accepted by the -licensetype argument:

| identinstrumentor        | requests a full Identify instrumentor license           |

|--------------------------|---------------------------------------------------------|

| identinstrumentor_actel  | requests a Microsemi-only Identify instrumentor license |

| identinstrumentor_altera | requests an Altera-only Identify instrumentor license   |

| identinstrumentor_xilinx | requests a Xilinx-only Identify instrumentor license    |

| identdebugger        | requests a full Identify debugger license            |

|----------------------|------------------------------------------------------|

| identdebugger_actel  | requests an Microsemi-only Identify debugger license |

| identdebugger_altera | requests an Altera-only Identify debugger license    |

| identdebugger_xilinx | requests a Xilinx-only Identify debugger license     |

The following examples illustrate using the -licensetype argument. The first example opens the Identify instrumentor in the graphical interface with an Altera-only license, and the second example opens the Identify debugger in the shell mode with a full license.

```

identify_instrumentor -licensetype identinstrumentor_altera

identify debugger shell -licensetype identdebugger

```

To verify the license currently being used by the Identify instrumentor or Identify debugger, enter the command licenseinfo in the console window or at the shell prompt.

**Note:** Changing the license type with the -licensetype argument is valid only for the current session and does not change the default license type defined in the Select available license dialog box.

## **Synthesis Tool Command-Line Options**

When starting the synthesis tool from the command line, an additional argument can be included to specify the location of the Identify installation directory. For example, the command

pathToSynplifyInstall/synplify\_pro -identify\_dir pathToIdentifyInstall

starts Synplify Pro in the GUI and sets the default installation path in the synthesis tool for launching the Identify tool set. The installation path specified appears in the Configure Identify Launch dialog box (Options->Configure Identify Launch) in the synthesis tool GUI.

The -identify\_dir argument overrides any SYN\_IDENTIFY\_EXE environment variable default setting.

# **Custom Initialization Script**

The Identify tool set can be customized using a TCL-style initialization script. This script is sourced on tool startup and allows you to define custom procedures and variables, or to program start-up behavior.

## **Script Locations**

The Identify software first looks for initialization scripts, titled synrc.tcl, in the /etc directory of the Identify installation path and then in the user's home directory. On a Linux-based platform, this is the standard home directory. On Windows, the value of the environment value USERPROFILE is used. On a standard Windows installation, this path is generally represented as:

c:/Documents and Settings/userName/synrc.tcl

## **Scripting Priority**

The script is first sourced from the installation directory and then from the home directory. Since the format is Tcl, a second user-specific script overrides Tcl procedures and variables previously defined.

### Sample Initialization File

A sample synrc file is distributed with the software. The file resides in the /etc directory of the installation path. The file is named synrc.template.tcl and must be renamed to synrc.tcl to enable its functionality. This file contains some sample functions and can be used as an example of how to provide a custom waveform viewer for use in the Identify debugger. If you are interested in interfacing and using your own waveform viewer with the Identify debugger, refer to the application note "Interfacing Your Waveform Viewer" available on the Synopsys SolvNet web site.

#### CHAPTER 3

# **Command Concepts**

All commands that the Identify tool set uses are divided into several specific categories. These categories, or concepts, separate the commands in terms of how these commands impact the system and also in terms of the tools within the system that utilize them. These concepts are defined in their respective sections below.

Each section in this chapter also contains a table that lists the commands alphabetically. The tables separate the commands into three different columns of information. These columns are:

Tool Usage – describes in symbol form the tools that can utilize the specific commands. The symbols are:

Command available only in Identify instrumentor

Command available only in Identify debugger

Command available in both Identify instrumentor and Identify debugger

- Use this command ... lists the command name or command example.

- To do this ... defines the uses of the command and lists command conventions and standards.

### This chapter contains:

- General Commands, on page 23

- File System Commands, on page 24

- Design Hierarchy Commands, on page 24

- Design Instrumentation Commands, on page 25

- Design Debugging Commands, on page 26

# **General Commands**

A general command is any command that allows you to control and access aspects of both the Identify instrumentor and Identify debugger. These commands access aspects of these tools, such as accessing the online command help and exiting the program.

|            | Use this command | To do this                                                                 |

|------------|------------------|----------------------------------------------------------------------------|

| 10         | clear            | Remove all the console output in the graphical user interface.             |

| <b>1 0</b> | exit             | Exit the program and close its window.                                     |

| 10         | help             | Display the online help system and a help topic about a command, if given. |

| <b>1 0</b> | instrumentation  | Manipulate incremental instrumentations.                                   |

| <b>1 0</b> | licenseinfo      | Display product version and license status.                                |

| <b>1 0</b> | log              | Record commands and their output into a log file.                          |

| <b>1 0</b> | project          | Create, open, and save projects.                                           |

| ••         | searchpath       | Set a search path to find HDL design files.                                |

| <b>1 0</b> | setsys           | Manipulate internal customization variables.                               |

| ••         | source           | Run a TCL script.                                                          |

| ••         | transcript       | Record commands into a transcript file.                                    |

|            |                  |                                                                            |

# File System Commands

File system commands allow you to navigate through the file system on your computer.

|            | Use this command | To do this                            |

|------------|------------------|---------------------------------------|

| <b>1 0</b> | cd               | Change the working directory.         |

| 10         | pwd              | Display the present working directory |

# **Design Hierarchy Commands**

Design hierarchy handling commands allow you to navigate through the design hierarchy of your HDL design.

|            | Use this command | To do this                                                                                                                                       |

|------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| ••         | hierarchy        | Navigate through the design hierarchy of your HDL design. A find option allows you to search for specific HDL design units within an HDL design. |

| <b>1 0</b> | show             | Display the HDL source code in the source window.                                                                                                |

# **Design Instrumentation Commands**

Design entry and instrumentation commands allow you to manipulate and instrument your HDL design and to insert the IICE.

|            | Use this command      | To do this                                                                                                                                                                                    |

|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | breakpoints           | Instrument breakpoints as HDL source level trigger conditions of the IICE.                                                                                                                    |

| •          | compile               | Import and compile HDL design files.                                                                                                                                                          |

| <b>1 0</b> | device                | Describe device-specific parameters used to implement your design.                                                                                                                            |

| <b>1 0</b> | encryption            | Set the current password to use before encrypting or decrypting a file.                                                                                                                       |

| <b>1 0</b> | iice                  | Duplicate IICE Configuration dialog box functions including defining sample clock, setting counter width for complex triggering, defining trigger conditions and states, and sampling method. |

| •          | signals               | Instrument signals for sampling and/or triggering in the IICE.                                                                                                                                |

| •          | write instrumentation | Write the instrumented HDL design files to a specified directory.                                                                                                                             |

# **Design Debugging Commands**

Design debugging commands allow you to debug your HDL design, interacting with the IICE and analyzing sample data at the RTL HDL source level.

|    | Use this command | To do this                                                                                                                                                                                                            |

|----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •  | activation       | Save or reload a set of trigger settings                                                                                                                                                                              |

| •  | chain            | Set up the JTAG chain of devices to be debugged.                                                                                                                                                                      |

| •  | com              | Set up the communication to the on-chip hardware, including cable and port settings.                                                                                                                                  |

| 10 | device           | Query the type of target device(s) used to implement your design.                                                                                                                                                     |

| 10 | encryption       | Set the current password to use before encrypting or decrypting a file.                                                                                                                                               |

| •  | haps             | Queries the hardware to generate the requisite Tcl file for Certify board generation.                                                                                                                                 |

| •  | idcode           | Set up and maintain a table of device ID codes.                                                                                                                                                                       |

| •• | iice             | Query the IICE Configuration dialog box settings selected during the instrumentation phase including sample clock, counter width for complex triggering, trigger conditions and states, and selected sampling method. |

| •  | logicanalyzer    | Configures the logic analyzer for real-time debugging.                                                                                                                                                                |

| •  | remote_trigger   | Sets/resets events on a specified debugger instantiation, on all debuggers in a multiple debugger configuration, or on specific IICE units in a multi-IICE configuration.                                             |

|   | Use this command | To do this                                                                                                                                     |

|---|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| • | run              | Arm the IICE with currently activated trigger conditions and wait for a trigger. When the trigger occurs, acquire and display the sample data. |

| • | statemachine     | Define the behavior of the state machine triggering hardware.                                                                                  |

| • | stop             | Activate or deactivate a HDL source level breakpoint.                                                                                          |

| • | watch            | Activate or deactivate a HDL source level watchpoint.                                                                                          |

| • | waveform         | Implement a waveform viewer                                                                                                                    |

| • | write samples    | Write the sample data in text format.                                                                                                          |

| • | write vcd        | Write the sample data to a Verilog Change<br>Dump (vcd) format.                                                                                |

| • | write vhdlmodel  | Write the sample data in a VHDL model format.                                                                                                  |

#### **CHAPTER 4**

# Alphabetical Command Reference

All commands are listed alphabetically in this chapter. Each command contains syntax, argument return values, default values, and examples.

# activation 💠

Allows you to save or reload a set of trigger settings (enabled watchpoints and breakpoints). Including the -sample option causes the sample data to be loaded or saved with the trigger settings. If the optional *activationName* argument is included, the named activation is loaded or saved; if *activationName* is omitted, last\_run.adb is used as the default activation name. The activation clear and activation list commands clear the current trigger settings and list all of the saved activations for the current instrumentation, respectively.

### **Syntax**

activation load|save [-sample] [activationName] activation clear|list

### **Command Example**

activation load -sample instr trial1

# breakpoints 1

Instructs the Identify instrumentor to add or delete special debug logic to or from the specified IICE. This debug logic implements breakpoint-style RTL source-level trigger conditions.

### **Syntax**

**breakpoints add|delete [-iice** *iiceID*|**all**] *breakpointName* [*breakpointName* ...] **breakpoints map** *breakpointName MictorPinName*

### **Arguments and Options**

For the add and delete options, one or more breakpoints can be added or deleted at the same time.

add breakpointName [breakpointName ...]

delete breakpointName [breakpointName ...]

The map option is used exclusively with the real-time debugging feature to assign a breakpoint to a Mictor connector pin. In the above syntax, *MictorPin-Name* is the concatenation of the Mictor board HapsTrak connector location, the Mictor connector name, and the Mictor pin name separated with periods. For example, 3.M1.D3e is the D3e pin of Mictor connector M1 on the Mictor board installed in HapsTrak connector 3.

Breakpoint names consists of two components:

- The full hierarchical path of the HDL design unit that denotes the underlying control statement of the breakpoint.

- The HDL source code location given by the filename and the line number of the breakpoint.

These two components together ensure that each breakpoint has a unique name for identification purposes.

### -iice iiceID|all

Used when more than one IICE is defined to specify the IICE (*iiceID*) where the breakpoint is to be added or deleted. If the argument all is specified, the corresponding breakpoint is added to or deleted from each IICE.

### **Command Example**

```

breakpoints add /beh/arb_inst/beh/process_83/case_88/arb.vhd:90

breakpoints delete -iice trap2

/beh/blk_xfer_inst/beh/process_85/case_97/xfer.vhd:107

breakpoints map /beh/process_50/case_88/if_90/alu.v:72 3.M1.D5e

```

### See Also

• stop, on page 88

# cd 🕩 🕩

Changes the present working directory in the file system to a different designated directory.

### **Syntax**

cd directory

### **Arguments and Options**

directory

Specifies the designated directory name. You must use forward slashes to describe relative and absolute path names irrespective of the operating system. On a Windows-based platform, the directory may include a drive letter followed by a colon.

## **Command Example**

cd c:/temp

cd ../homedirs/adam

### See Also

• pwd, on page 72

# chain 🕩

Sets up and manipulates the JTAG chain of devices. Because more than one device can be connected in a JTAG chain, the commands allows you to setup the JTAG chain representation in the Identify debugger to select the particular device to be debugged.

### **Syntax**

chain add deviceName instructionRegisterWidth

chain clear

chain info [-raw|-active]

chain replace position chipID instructionRegisterLength

chain select chipID

### **Arguments and Options**

add deviceName instructionRegisterWidth

Creates and labels a device and assigns that device with an instruction register width. Every device attached to the JTAG must be identified by a unique name. This device name can include any alpha-numeric characters. Spaces and other characters cannot be used.

The instruction register is an N-bit register that holds the OPCODE for the JTAG controller. Every device has a specific instruction register width, which can be found in the device's Data Book.

#### clear

Deletes the current chain description.

#### info

Displays the chain description.

#### info -raw

Returns a machine readable JTAG chain description. The chain is represented by a Tcl list of chain elements where each element is a two-item Tcl list specifying the device name and instruction register width. Example:

```

{{device_a 8} {device_b 10}}

```

#### info -active

Returns the name of the device that is currently selected for debugging.

#### chain replace position chipID instructionRegisterLength

Changes the name or register length of a device that has been previously defined using the chain add command. In the command syntax, *position* is the value shown by the chain info command for the device to be replaced.

#### select deviceName

Selects a device for system debugging. Only devices added and labeled using chain add can be selected.

### **Command Example**

```

chain add fpga 5

chain select fpga

chain info -active

chain replace 1 new fpga 8

```

#### See Also

- device, on page 39

- com, on page 35

# clear 💠 💠

Removes all the console output in the graphical user interface. This command is only supported in the graphical modes.

### **Syntax**

clear

### **Arguments and Options**

none

Sets up and manipulates communication settings between the Identify debugger and the Intelligent In-Circuit Emulator (IICE).

### **Syntax**

com cabletype [type]

com cableoptions option [value]

com check

com port [lpt1|lpt2|lpt3|lpt4]

### **Arguments and Options**

cabletype [type]

Describes the type of cable connecting the system to the hardware being analyzed. The supported cable types are byteblaster, xilinxparallel, xilinxusb, xilinxauto, Microsemi\_BuiltinJTAG, JTAGTech3710, Altera\_BuiltinJTAG, and demo. A umrbus selection in also available to indicate that the UMRBus is to be used as the communication interface between the hardware and the host machine running the Identify debugger.

#### cableoptions option [value]

- Specifies or reports cable-specific option settings:

- **byteblaster\_port** [*integer*] specifies the parallel port number; default is 1 (lpt1).

- **flashPro\_trst** [*string*] specifies the setting of the TRST (tristate) pin. Accepted values (*string*) are off, toggle, low, and hi; the default is off.

- **flashProLite\_trst** [*string*] specifies the setting of the TRST (tristate) pin. Accepted values (*string*) are off, toggle, low, and hi; the default is off.

- **flashPro3\_trst** [*string*] specifies the setting of the TRST (tristate) pin. Accepted values (*string*) are off, toggle, low, and hi; the default is off.

- **JTAGTech\_port** [integer] specifies the interface card address (0 to 255). The default address is 0.

- **JTAGTech\_tapnum** [*integer*] specifies the active tap port on the JTAG Technologies tap pod. Values (*integer*) range from 1 to 4; the default is 1.

- **JTAGTech\_type** [**PCI**|**USB**] specifies the type of computer interface connection (parallel or USB); the default is PCI (parallel).

- **xilinxparallel\_port** [*integer*] specifies the parallel port number from 1 to 4; the default is 1 (lpt1).

- **xilinxparallel\_speed** [*integer*] specifies the parallel port communications speed; acceptable values are 5000000 (5MHz), 2500000 (2.5 MHz, and 200000 (200kHz); the default is 5000000.

- **xilinxusb\_speed** [*integer*] specifies the USB port communications speed; acceptable values are 24000000 (24MHz), 12000000 (12 MHz), 6000000 (6 MHz), 3000000 (3 MHz), 1500000 (1.5MHz), or 750000 (750 kHz); the default is 12000000.

#### check

Performs a connectivity check on the JTAG cable connection.

### port [lpt1|lpt2|lpt3|lpt4]

Specifies the host computer parallel port to which the JTAG cable is connected. The supported ports are lpt1, lpt2, lpt3, and lpt4.

# **Command Example**

```

com cabletype byteblaster

com cableoptions byteblaster_port 2

com port lpt1

```

# See Also

• chain, on page 33

# compile •

Prints a list of the design files and the respective order in which they are read.

# **Syntax**

compile list

# **Arguments and Options**

list [-vhdl|-verilog]

Prints a list of the design files and the respective order in which they are read. If the -vhdl or -verilog option is included, limits the list to only the specified file type.

# **Command Example**

compile list -vhdl

## See Also

• searchpath, on page 76

# device 🕩 🕩

Defines device-specific parameters used to implement the instrumented HDL design.

# **Syntax**

device estimate [-iice all|iiceName] [-resources | -noresources | -raw]

device jtagport [builtin|soft|umrbus]

device prepare\_incremental [0|1]

device skewfree

device technologydefinitions [0|1]

device xilinxinsertbufg

device xilinxjtagaddr1

device xilinxjtagaddr2

device xilinxusesrl16

device capimbaseaddr

# **Arguments and Options**

#### estimate or estimate -iice all

Reports total number of instrumented signals and estimated resource utilization for the current implementation.

#### estimate -iice iiceName

Reports total number of instrumented signals and estimated resource utilization for the named IICE (*iiceName*) for the current implementation.

#### estimate -resources or estimate -resources -iice all

Reports only the estimated resource utilization for current implementation.

#### estimate -resources -iice iiceName

Reports only estimated resource utilization for the named IICE (*iiceName*) for the current implementation.

#### estimate -noresources or estimate -noresources -iice all

Reports only the number of instrumented signals for current implementation.

#### estimate -resources -iice iiceName

Reports only the number of instrumented signals for the named IICE (*iiceName*) for the current implementation.

#### estimate -raw

Displays the instrumented signal information and estimated resource utilization for the current implementation in a machine-readable format.

#### jtagport [builtin|soft|umrbus]

Determines if the built-in JTAG port of the target device is used for the IICE connection or if the Synopsys test port is used. Selection can only be set in the Identify instrumentor. With no argument specified, the current setting is displayed. The following selections are available:

#### builtin

Specifies that the JTAG port built into the target device is the port used. No extra user pin is required. This is the default value when the device family specified is other than generic.

#### soft

Specifies that the IICE communicates through a JTAG TAP controller that is automatically inserted by the Identify instrumentor. The Synopsys JTAG port requires four additional user pins.

#### umrbus

Specifies that the UMRBus is to be used as the communication interface between the hardware and the host machine running the Identify debugger (the JTAG port is not used).

#### prepare incremental

Sets up the Identify instrumentor to support incremental changes to the instrumented signals.

## skewfree [0|1]

Causes the IICE to be built using skew-resistant hardware when no global clock resources are available for the JTAG clock. When this option is enabled (1), master-slave flip-flops are used on the JTAG chain to prevent clock skew from affecting the logic. This setting also causes the Identify instrumentor to NOT explicitly define the JTAG clock as requiring global clock resources. The skewfree option is disabled (0) by default.

## technologydefinitions [0|1]

Disables/enables the generation of black boxes for undefined module definitions. This option is available only in Identify instrumentor and is enabled by default.

## xilinxinsertbufg [0|1]

Due to the timing requirements of the JTAG clock in Xilinx designs, the Identify instrumentor automatically adds a BUFG component to this clock signal to ensure that the signal is implemented using the chip's global clock resources.

If you prefer to have the synthesis tool detect and add the BUFG component, disable (0) this option to change this behavior. Use caution with this option; if the JTAG clock is either not in a global clock buffer or is implemented using skew-free hardware, the debug logic will not function properly. The skewfree option overrides the behavior of this setting, as no BUFG is inserted for skew-free hardware. The xilinxinsertbufg option is enabled (1) by default.

## xilinxjtagaddr1 [user1|user2|user3|user4]

Selects the first user instruction register for Virtex-4, Virtex-5, and Virtex-6 boundary scan cells for the built-in JTAG controller. The default is user3. This option is available only in the Identify instrumentor.

## xilinxjtagaddr2 [user1|user2|user3|user4]

Selects the second user instruction register for Virtex-4/Virtex-5 boundary scan cells for the built-in JTAG controller. The default is user4. This option is available only in the Identify instrumentor.

## xilinxusesrl16 [0|1]

Determines if the IICE uses shift registers for the debug logic in Xilinx Virtex-II designs when enabled (1). If shift registers are used, the area cost of the debug logic can potentially be reduced. The xilinxusesrl16 option is enabled (1) by default.

**Note**: Valid values must be set for the above options before you instrument your design.

#### capimbaseaddr baseAddress

Specifies the address of a CAPIM inserted for UMRBus communication. In a multi-FPGA debug environment, a CAPIM is inserted into each FPGA where signals are instrumented. The base address value is decremented with each CAPIM added. The default base address is 57.

## **Command Example**

```

device estimate -iice IICE -noresources

device jtagport builtin

device skewfree 1

```

## See Also

- chain, on page 33

- com, on page 35

# encryption ��

Sets the current password to use before encrypting or decrypting a file. In the Identify instrumentor, this command sets the password to be used when writing out an encrypted file with the write instrumentation command. In the Identify debugger, this command is used to set the password to enable encrypted files to be displayed.

**Note:** Setting the password with this command displays the password on the screen and in any log files that you create. If this is a concern, use only the graphical interface when instrumenting and debugging designs that use the encryption feature.

# **Syntax**

encryption set\_passwd password

## **Arguments and Options**

set\_passwd password

The set\_passwd argument requires a single string (password) entry. The new password is stored for decrypting/encrypting until it is changed or until the Identify instrumentor or Identify debugger is shut down.

**Note:** Passwords are the user's responsibility; Synopsys cannot recreate a lost or forgotten password.

# **Command Example**

encryption set passwd xyzzy

## See Also

- write instrumentation, on page 96

- project, on page 71

Exits the program and closes the window.

# **Syntax**

exit

## **Arguments and Options**

None

# **Command Example**

exit

# help 💠

Displays the online help system and a help topic about a command.

# **Syntax**

help [commandName]

# **Arguments and Options**

commandName

Displays help text about the specified command. If the *commandName* argument is omitted, help descriptions for all commands are printed to the screen.

# haps 🌵

Queries the hardware to generate the requisite Tcl file for Certify board generation and to performs the verification tests.

# **Syntax**

haps

board

prog binFile devID

setvcc voltage

setclk clockName frequency

restart

list [testName]

run [testName|AII]

confscr scriptFileName

vbgen tclFile

help [testName]

## **Arguments and Options**

#### board

Displays the board status to the screen. Status includes clock and voltage settings, reset configuration, daughter card connections, firmware version, and board serial number.

#### prog binFile devID

Programs the FPGA identified by *devID* with the specified bin file. The *devID* value begins with 1 which corresponds to the first FPGA on the board.

#### setvcc voltage

Sets the I/O voltage for the board regions. The acceptable values for *voltage* are 1v5, 1v8, 2v5, and 3v3 (HAPS-70 system voltage regions are limited to a maximum of 1.8 volts).

#### setclk clockName frequency

Sets the frequency for the global input clock identified by *clockName* to the specified frequency. The *frequency* value is in kHz unless specified otherwise. For example, the command haps setclk GCLK1 150MHz specifies a clock frequency of 150 MHz for GCLK1.

#### restart

Restarts the board.

#### list

Lists the available local board tests.

#### run [testName|All]

Runs a particular test or runs all local board tests. In the above syntax, *testName* is one of:

umr\_check fpgalD frequency - verifies the basic functionality of the UMRBus. In the syntax:

fpgalD – indicates which FPGA device is to be tested. The default is 1, which is the first FPGA device on the board.

*frequency* – sets the frequency for GCLK1 which is used in the test of the design. The default frequency is 140MHz.

**con\_speed** *frequency* **fast**|**sweep** – verifies the connectivity between HapsTrak connectors as well as the speed at which HSTDM can run. In the syntax:

*frequency* – sets the frequency at which HSTDM is to be verified.

**fast**|**sweep** – sets the run mode. The default is **fast** mode. When mode is set to **sweep**, the test sweeps every channel of the connection which can require up to four hours to complete.

**self\_test** – replaces the traditional self test with an STB2 test card.

**clock\_check** – reports the clock frequency of each GCLK output to allow of all of the GCLK frequencies to be verified.

When the All argument is used, runs all local tests with the individual test parameter defaults. For more complete test details, see the individual test descriptions under the haps command in the *Certify Command Reference* and see *HAPS Board Bring-up Utility* in Chapter 11, *Connecting to the Target System*, in the Identify User Guide.

## confscr scriptFileName

Runs confprosh tel scripts. For example, the confscr option can be used to source a HAPS clock and voltage-region configuration script; the user could then run clock checks to verify the on-board clock configuration.

## vbgen tclFile

Queries the HAPS system and generates a corresponding Tcl file for Certify board file generation.

## help [testName]

Shows help information. If *testName* is included, shows help for the specified test.

# **Command Example**

haps run umr\_check 2 180 haps setclk GCLK1 150MHz haps setvcc 1v8

# hierarchy •••

Navigates through the design hierarchy and shows design and hierarchy elements in the HDL design. These design elements include the following types, depending on the HDL language used to describe the design:

- Entity VHDL design unit type.

- Module Verilog design unit type.

- Instance VHDL or Verilog design unit type.

# **Syntax**

hierarchy add [options] element [element ...]

hierarchy cd hierarchyPath

hierarchy delete [options] element [element ...]

hierarchy find [options] [hierarchyPath]

hierarchy Is [-long] [-recursive] [-all] [hierarchyPath]

hierarchy pwd

hierarchy toplevel

# **Arguments and Options**

add [options] element [element ...]

Connects all signals or breakpoints in the specified hierarchical element to the IICE. The add argument applies only to the Identify instrumentor.

The following add argument options are available:

## -iice iiceID|all

Used when more than one IICE is defined to specify which IICE (*iiceID*) to connect. If the argument all is specified, the signals or breakpoints are connected to each IICE.

#### -sample

Connects all signals in the specified hierarchical element to the IICE sample buffer.

#### -trigger

Connects all signals in the specified hierarchical element to the IICE trigger logic.

#### -breakpoint

Connects all breakpoints in the specified hierarchical element to the IICE.

#### -recursive

Allow hierarchies to be traversed when a wildcard is included in the *element* argument.

**Note:** The -sample, -trigger, -breakpoint, and -recursive options can be combined in a single add argument.

#### cd hierarchyPath

Changes the current design hierarchy to the one specified by *hierarchyPath*. Either a relative or an absolute hierarchical path name can be used.

cd /

Changes the current design hierarchy to the top level of the hierarchy.

cd ..

Changes the current design hierarchy to next higher level.

#### delete [options] element [element ...]

Disconnects all signals or breakpoints in the specified hierarchical element from the IICE. The delete argument applies only to the Identify instrumentor.

The following delete argument options are available:

#### -iice iiceID|all

Used when more than one IICE is defined to specify which IICE (*iiceID*) to disconnect. If the argument **all** is specified, the signals or breakpoints are disconnected from each IICE.

#### -signal

Disconnects all sample and trigger signals in the specified hierarchical element from the IICE.

#### -breakpoint

Disconnects all breakpoints in the specified hierarchical element from the IICE.

**Note:** The -signal and -breakpoint options can be combined in a single delete argument.

## find [options] [hierarchyPath]

Searches for specific HDL design units and lists those elements. Use this command to locate specified design units in the compiled HDL design file. The search is started from the specified hierarchical path. If you do not provide *hierarchyPath*, the search starts from the current working hierarchy.

The following find options are available:

#### -iice iiceID|all

Used when more than one IICE is defined to specify the IICE (*iiceID*) to be searched. If the argument all is specified, each IICE is searched.

#### -name elementName

The HDL element name to be located.

#### -noequiv

Limits the search to named path only and does not search equivalent paths.

## -type instance|breakpoint|signal|\*

The type of HDL element for the target search. If \* is entered, search includes all elements.

#### -ls

Prints verbose information for each HDL element found.

## -stat status | \*

Serves as a filter to search for an HDL element with a specific instrumentation status. If \* is entered, any instrumentation status is included in the search. The *status* argument takes the following options:

- disabled limits search to disabled watchpoints, breakpoints, and other disabled HDL design units (available only in Identify debugger).

- enabled limits search to enabled watchpoints, breakpoints, and other enabled HDL design units (available only in Identify debugger).

- instrumented limits search to the sampling clock, and watchpoints and breakpoints that have been marked as instrumented (available only in Identify instrumentor).

- not-instrumented limits search to watchpoints and breakpoints that have not been instrumented (available only in Identify instrumentor).

- sample\_only limits search to sample-only watchpoints (available only in Identify instrumentor).

- trigger\_only limits search to trigger-only watchpoints (available only in Identify instrumentor).

## -maxdepth integer

Limits search to a maximum depth within the hierarchy tree.

#### -all

Lists "hidden" HDL design units, such as signals/breakpoints within dead code or, in the Identify debugger, breakpoints that were not instrumented. By, default, HDL elements with enabled status are searched.

## Is [-long] [-recursive] [-all] [hierarchyPath]

Displays all information about the HDL design units within the current design hierarchy. You can display this design unit information in a long listing using the -long option or you can display this information recursively using the -recursive option. The -all option shows all HDL elements including hidden elements.

#### pwd

Lists the current HDL design hierarchy.

## toplevel

Shows top-level hierarchy name.

# **Command Example**

```

hierarchy cd ..

hierarchy cd /top/ul/arui

hierarchy ls -recursive

hierarchy find -type breakpoint -stat instrumented

```

## See Also

• show, on page 78

# idcode 💠

Sets up and maintains a table of device ID codes. The ID code information is used for auto-detection of the devices on the JTAG chain during debugging. If the chain can be successfully detected, you do not need to manually specify the chain using the chain command.

# **Syntax**

idcode add [-quiet] idcode deviceName instructionRegisterWidth

idcode clear

idcode info [-raw]

## **Arguments and Options**

add [-quiet] idcode deviceName instructionRegisterWidth

Creates an entry in the device table for a given device.

The *idcode* argument should be a binary representation of a 32-bit number in the form of a string. The string can contain 'x' entries for bits that are irrelevant.

The *deviceName* argument can be any descriptive string. The string must be quoted if it includes spaces.

The *instructionRegisterWidth* argument takes an integer value. Every device has a specific instruction register width, which can be found in the device's Data Book.

The -quiet option adds the device, but does not display a user notification.

#### clear

Deletes the entire ID code table.

## info [-raw]

Returns a description of the device table. The table is represented by a Tcl list of device elements where each element is a three item Tcl list specifying the ID code, device name, and instruction register width. Example:

```

{1100110011001100110011001100 device_a 8} {00001100110011001100110011111 device b 10}

```

The optional -raw option generates the description in a machine-readable format.

# **Command Example**

```

idcode add 0010000000111000100010001000 device_type 8

idcode add -quiet 0010000000111000100010001 "device type" 8

idcode clear

```

## See Also

- device, on page 39

- chain, on page 33

Duplicates the functionality of the IICE Configuration dialog box.

# **Syntax**

iice clock|controller|current|delete|info|list|new|rename | sampler|assignmentsreport [option]

# **Arguments and Options**

## iice clock [options] [signalName]

Defines the signal to be used for the IICE sample clock. The *signalName* is the full hierarchical path name to the signal. You can select any signal within the HDL design as the sample clock. However, this signal cannot be sampled itself while used as the sample clock. This option can only be used during instrumentation. If *signalName* is not specified, the option returns the name of the IICE clock.

#### -edge positive negative

Specifies the active edge of the clock (positive or negative) when an IICE sample clock is specified. The -edge option is only available in the Identify instrumentor; the default edge is rising (positive).

## -iice iiceID|all

Used when more than one IICE is defined to specify/report the controller parameters for the specified IICE (*iiceID*). If the argument all is specified, the controller parameters apply to each IICE.

## iice controller [options] [none|counter|statemachine]

Specifies IICE controller configuration; simple triggering (none), complex triggering (counter), or state machine. The following options are supported:

#### -iice iiceID|all

Used when more than one IICE is defined to specify/report the controller parameters for the specified IICE (*iiceID*). If the argument all is specified, the controller parameters apply to each IICE.

## -countermode [events|cycles|watchdog|pulsewidth]

Selects the complex counter mode. The value *n* referenced below is the value set by the countervalue option (applies only to Identify debugger).

#### events

Stops sampling after the trigger condition occurs for the n+1'th time. This is the default value for -countermode.

## cycles

Stops sampling n cycles after the trigger condition occurs.

#### watchdog

Stops sampling if the trigger condition does not occur for n consecutive cycles.

#### pulsewidth

Stops sampling when the trigger condition has met n consecutive cycles. The number n is controlled by the current setting of countervalue.

If no argument is given, the current mode is returned.

#### -counterval unsignedInteger

Sets a value for the complex counter (applies only to Identify debugger). *unsignedInteger*

Load the given value into the complex counter. This value must fit into the complex counter width as defined in the Identify instrumentor. The default value for the complex counter is 0 which disables the counter.

If no value is given, the current setting is returned.

## -counterwidth integer

Instruments a versatile counter of variable size for complex triggering (applies only to Identify instrumentor). If no argument is given, the command shows the current counter width. An integer parameter in the range between 1 and 32 specifies a new counterwidth. 0 suppresses the creation of any counter. All other values are invalid. The default value for the counterwidth is 16 (the IICE contains a 16-bit complex counter).

#### -triggerconditions integer

Used when instrumenting a design for state-machine triggering (applies only to Identify instrumentor). This command specifies the number of trigger conditions available for state-machine triggering. The range is from 1 to 16. The default value is 4. If no argument is given, the command shows the current pattern-tree setting.

This option is a critical setting with respect to instrumentation cost. Choosing a trigger setup with the minimum amount of trigger conditions is recommended to reduce resource usage in the instrumentation. Choosing a trigger-condition value greater than 1 requires that multiple trigger states be created. Use the triggerstates option to specify the desired number of states.

#### -triggerstates [integer]

Used when instrumenting a design to use state-machine triggering (applies only to Identify instrumentor). This option specifies the maximum number of states instrumented in the state machine. The range is 2 to 16; powers of 2 are preferable as other integers limit functionality and do not provide any cost savings. The default is 4. If no argument is given, the option shows the current triggerstates setting.

## -exporttrigger 0|1

Determines if the master trigger signal of the IICE hardware is exported to the top-level of the instrumented design (applies only to Identify instrumentor). Enables (1) or disables the creation of a trigger port. Export trigger port creation is disabled by default.

## -importtrigger integer

Determines if the master trigger signal of the active IICE hardware includes any triggers received from external sources (applies only to Identify instrumentor). Specifying a value between 1 and 8 creates a corresponding number of input ports.

**Note:** When using an external trigger, the pin assignment for the corresponding input port must be defined in the synthesis or place and route tool.

## -crosstrigger 0|1 [-iice iiceID]

Enables (1) or disables an IICE to include trigger signals from other IICE units when determining its trigger condition (applies only to Identify instrumentor). If the -iice argument is omitted, the command applies to the current IICE.

#### -crosstriggermode disabled|any|all|after -crosstriggeriice iice|D|all

Determines the trigger conditions in the Identify debugger when the IICE controller is set to simple or complex-counter triggering. The following options are supported:

#### disabled

Destination IICE triggers normally (triggers from source IICE units are ignored).

#### any

Destination IICE triggers when any source IICE triggers or on its own internal trigger.

#### all

Trigger occurs when all events, irrespective of order, occur at all IICE units including local IICE unit.

## after -crosstriggeriice iiceID|all

Trigger occurs after source IICE triggers coincident with next destination IICE trigger. The -crosstriggeriice argument specifies a specific source IICE unit (*iiceID*) or all source IICE units (all).

## iice current [iiceID]

Used when more than one IICE is defined to select the active IICE (*iiceID*). If the *iiceID* argument is omitted, reports the ID of the currently active IICE. Note that *iiceID* is case sensitive.

#### iice delete iiceID

Deletes the specified IICE (*iiceID*). The iice delete command is only available in the Identify instrumentor.

## iice info [iiceID]

Reports the status of the specified IICE (*iiceID*). If the *iiceID* argument is omitted, reports the status of the currently active IICE.

#### iice list

Lists the IDs (names) of each defined IICE.

## iice new [iiceID] [-type rtd|regular]

Creates a new IICE with the name *iiceID*. If the *iiceID* argument is omitted, the new IICE is named IICE\_n where n is the next sequential integer. The -type option indicates if the IICE is to be configured for real-time debugging (rtd) or normal debugging (regular). For more information on the real-time debugging feature, see the *User Guide*.

The lice new command is only available in the Identify instrumentor.

#### iice rename iiceID

Renames the currently active IICE to the name specified (*iiceID*). The iice rename command is only available in the Identify instrumentor.

## iice sampler [options]

The following lice sampler options are supported in the Identify instrumentor:

- -iice {iice/D|all} internal memory|hapssram

- -compression 0|1

- -sram option [value]

- -rtd {mictorlocs {location [location ...]}|board boardType}

- -depth depth Value

- -qualified\_sampling 0|1

- -always\_armed 0|1

The following lice sampler options are supported in the Identify debugger:

- -triggertime early|middle|late

- -samplemode normal|qualified\_fill|qualified\_intr|always\_armed

- -runselftest 0|1

- -datacompression 0|1

- -enablemask 0|1 [-msb integer -lsb integer] signalName

- -group interger

## Identify Instrumentor iice sampler Options

#### -iice iiceID|all

Used when more than one regular IICE is defined to specify/report the IICE sampler parameters for the specified IICE (*iiceID*). If the argument all is specified, the IICE sampler parameters apply to each qualified IICE.

## internal\_memory|hapssram

The internal\_memory/hapssrm argument specifies the type of RAM used to capture the sample data; internal\_memory uses local RAM (the default) and hapssram uses the memory on a HAPS SRAM daughter board (available only with HAPS board configurations; unavailable with real-time debug IICE).

## -compression 0|1

The -compression option determines if data compression is to be applied when the sample data is unchanged between cycles (the data is automatically decompressed when viewed). A value of 1 enables data compression. An internal default is set to force an update after 64 cycles of unchanging data. The -compression option applies only to regular IICE units and is not supported by real-time debug IICE.

## -sram option [value]

The -sram option applies only when the *bufferType* is set to hapssram. The -sram options are described below. If *value* is not specified, the current setting is reported. The -sram option applies only to regular IICE units and is not supported by real-time debug IICE.

## sramlocations [location]

The connector location where the daughter card or cards are physically connected. *Location* is one or more integers between 1 and 6 that represent the HapsTrak connectors of the FPGA under debug. Eligible locations are board dependent.

## numberboardstack [integer]

The number of daughter cards stacked at the specified SRAM locations. *Integer* can be 1 or 2 and applies to all connector locations (the stack depth must be the same at all locations).

## type [value]

The SRAM daughter card type. Currently, only the SRAM 1x1HTII daughter card is supported (type = 6).

#### clockfreq [value]