# Synopsys FPGA Synthesis Synplify Pro for Microsemi Edition

**User Guide**

May 2013

# **Copyright Notice and Proprietary Information**

Copyright © 2013 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

# **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only.

Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

| "This document is duplicated with | h the permission of Sy | nopsys, Inc., for the |

|-----------------------------------|------------------------|-----------------------|

| exclusive use of                  |                        | and its               |

| employees. This is copy number    |                        |                       |

## **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

### **Disclaimer**

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

# Registered Trademarks (®)

Synopsys, AEON, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, CHIPit, CoMET, CODE V, Design Compiler, DesignWare, EMBED-IT!, Formality, Galaxy Custom Designer, Global Synthesis, HAPS, HapsTrak, HDL Analyst, HSIM, HSPICE, Identify, Leda, LightTools, MAST, METeor, ModelTools, NanoSim, NOVeA, OpenVera, ORA, PathMill, Physical Compiler, PrimeTime, SCOPE, Simply Better Results, SiVL, SNUG, SolvNet, Sonic Focus, STAR Memory System, Syndicated, Synplicity, the Synplicity logo, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, UMRBus, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

# Trademarks (™)

AFGen, Apollo, ARC, ASAP, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Cosmos, CosmosLE, CosmosScope, CRITIC, CustomExplorer, CustomSim, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, DesignerHDL, DesignPower, DFTMAX, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, HANEX, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping System, HSIMplus, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Intelli, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Macro-PLUS, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, ORAengineering, Physical Analyst, Planet, Planet-PL, Polaris, Power Compiler, Raphael, RippledMixer, Saturn, Scirocco, Scirocco-i, SiWare, Star-RCXT, Star-SimXT, StarRC, System Compiler, System Designer, Taurus, Total-Recall, TSUPREM-4, VCSi, VHDL Compiler, VMC, and Worksheet Buffer are trademarks of Synopsys, Inc.

# Service Marks (sm)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license.

ARM and AMBA are registered trademarks of ARM Limited.

Saber is a registered trademark of SabreMark Limited Partnership and is used under license.

All other product or company names may be trademarks of their respective owners.

Printed in the U.S.A

May 2013

# Contents

| Chapter 1: Introduction                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synopsys FPGA and Prototyping Products16FPGA Implementation Tools16Synopsys FPGA Tool Features18                                                                                                                                              |

| Scope of the Document21The Document Set21Audience21                                                                                                                                                                                           |

| Getting Started22Starting the Software22Getting Help22                                                                                                                                                                                        |

| User Interface Overview                                                                                                                                                                                                                       |

| Chapter 2: FPGA Synthesis Design Flows                                                                                                                                                                                                        |

| Logic Synthesis Design Flow                                                                                                                                                                                                                   |

| Chapter 3: Preparing the Input                                                                                                                                                                                                                |

| Setting Up HDL Source Files30Creating HDL Source Files30Using the Context Help Editor32Checking HDL Source Files33Editing HDL Source Files with the Built-in Text Editor34Setting Editing Window Preferences38Using an External Text Editor40 |

| Using Mixed Language Source Files                                                                                                                                                                                                             |

| Working with Constraint Files                                                                                                                                                                                                                 |

| Generating Constraint Files for Forward Annotation                                                                                                                                                                                                                                                       | 50                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Chapter 4: Specifying Constraints                                                                                                                                                                                                                                                                        |                              |

| Using the SCOPE Editor                                                                                                                                                                                                                                                                                   |                              |

| Specifying SCOPE Constraints  Entering and Editing Scope Constraints  Setting Clock and Path Constraints  Defining Input and Output Constraints  Specifying Standard I/O Pad Types  Using the TCL View of SCOPE GUI  Guidelines for Entering and Editing Constraints                                     | 57<br>59<br>60<br>62         |

| Specifying Timing Exceptions                                                                                                                                                                                                                                                                             | 68<br>72                     |

| Finding Objects with Tcl find and expand Specifying Search Patterns for Tcl find Refining Tcl Find Results with -filter Using the Tcl Find Command to Define Collections Using the Tcl expand Command to Define Collections Checking Tcl find and expand Results Using Tcl find and expand in Batch Mode | 74<br>74<br>76<br>78         |

| Combining Tcl find with Other Operations                                                                                                                                                                                                                                                                 | 81                           |

| Using Collections  Comparison of Methods for Defining Collections  Creating and Using Scope Collections  Creating Collections using Tcl Commands  Viewing and Manipulating Collections with Tcl Commands                                                                                                 | 82<br>83<br>85               |

| Converting SDC to FDC                                                                                                                                                                                                                                                                                    | 92                           |

| Using the SCOPE Editor (Legacy)  Entering and Editing SCOPE Constraints (Legacy)  Specifying SCOPE Timing Constraints (Legacy)  Entering Default Constraints  Setting Clock and Path Constraints  Defining Clocks  Defining Input and Output Constraints (Legacy)  Defining False Paths (Legacy)         | 95<br>97<br>97<br>97<br>.100 |

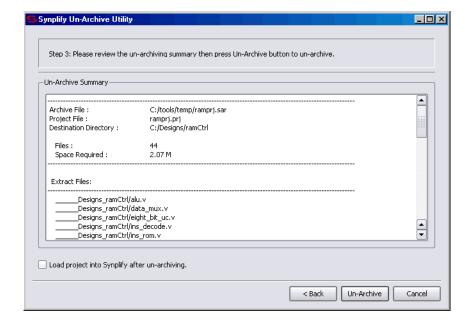

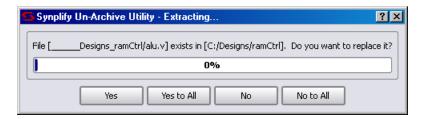

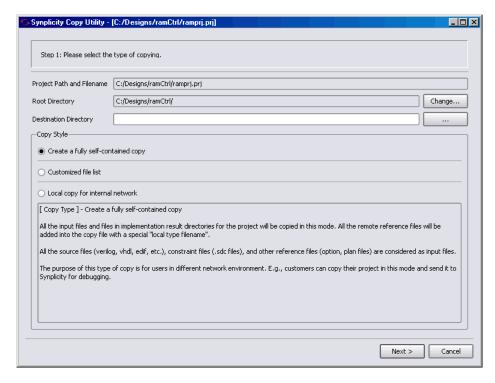

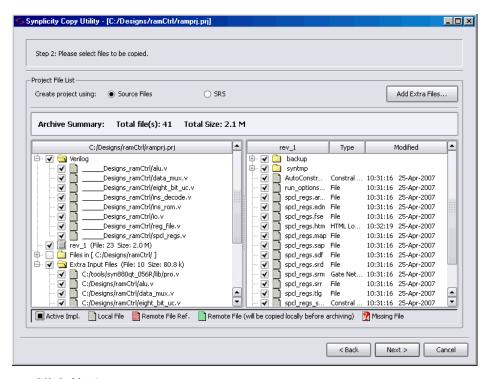

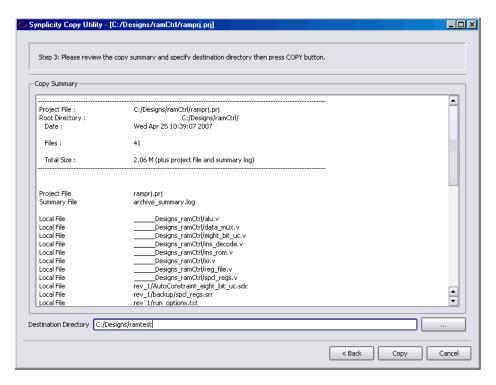

### Chapter 5: Setting up a Logic Synthesis Project Setting Up Project Files ......112 Creating a Project File ......112 Opening an Existing Project File ......115 Setting Project View Display Preferences ......117 Updating Verilog Include Paths in Older Project Files ......119 Creating Custom Folders ......120 Manipulating Custom Project Folders ......123 Specifying Attributes and Directives in VHDL ......143 Specifying Attributes Using the SCOPE Editor ......146 Identifying the Files to Search ......151 Filtering the Files to Search ......151 Archiving Files and Projects .......153 Un-Archive a Project .......157

**Chapter 6: Inferring High-Level Objects**

| Instantiating Black Boxes and I/Os in VHDL                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Defining State Machines for Synthesis175Defining State Machines in Verilog175Defining State Machines in VHDL176Specifying FSMs with Attributes and Directives177 |

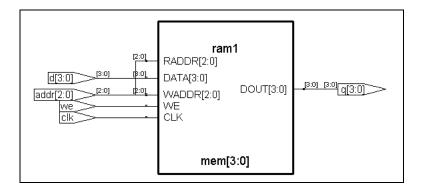

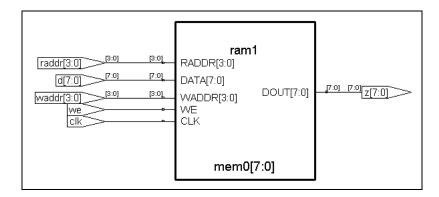

| Inferring RAMs180Inference Versus Instantiation180Basic Guidelines for Coding RAMs181Specifying RAM Implementation Styles185                                     |

| Initializing RAMs                                                                                                                                                |

| Chapter 7: Specifying Design-Level Optimizations                                                                                                                 |

| Tips for Optimization192General Optimization Tips192Optimizing for Area193Optimizing for Timing194                                                               |

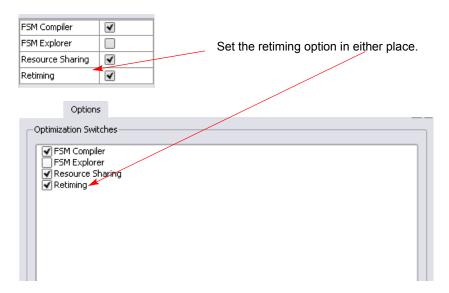

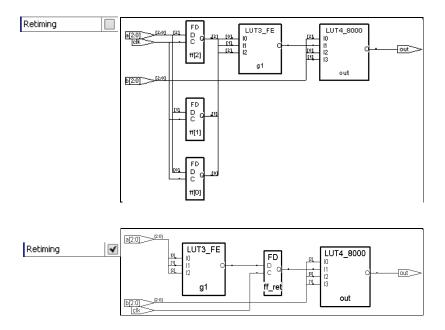

| Retiming196Controlling Retiming196Retiming Example198Retiming Report199How Retiming Works200                                                                     |

| Preserving Objects from Optimization203Using syn_keep for Preservation or Replication204Controlling Hierarchy Flattening207Preserving Hierarchy207               |

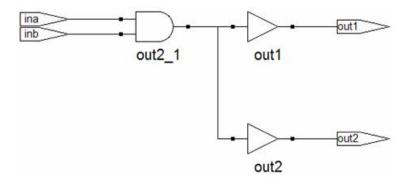

| Optimizing Fanout       .209         Setting Fanout Limits       .209         Controlling Buffering and Replication       .211                                   |

| Sharing Resources                                                                                                                                                |

| Inserting I/Os                                                                                                                                                   |

| Optimizing State Machines                                                                                                                                        |

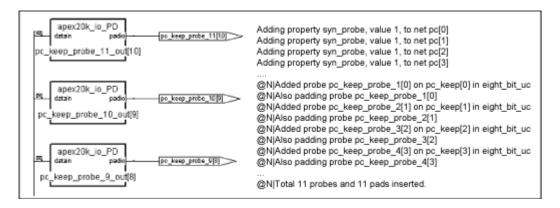

| Inserting Probes                                                                                                                                                                                                                      | 227 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 8: Synthesizing and Analyzing Results                                                                                                                                                                                         |     |

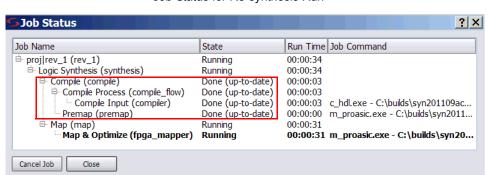

| Synthesizing Your Design                                                                                                                                                                                                              | 232 |

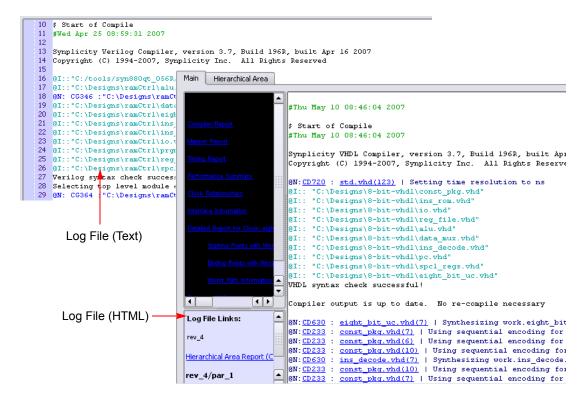

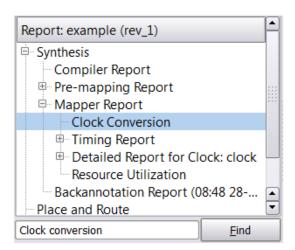

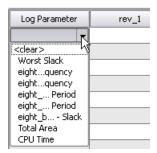

| Checking Log Results  Viewing the Log File  Analyzing Results Using the Log File Reports  Using the Watch Window                                                                                                                      | 237 |

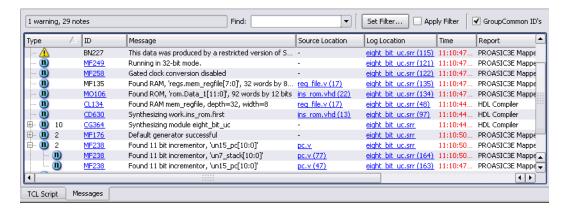

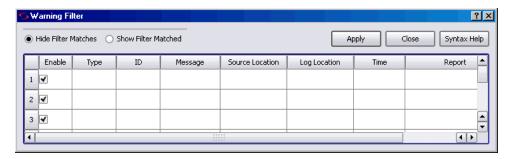

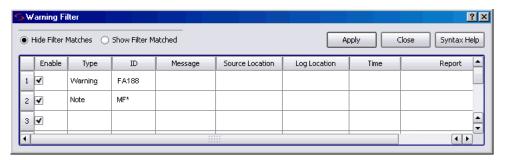

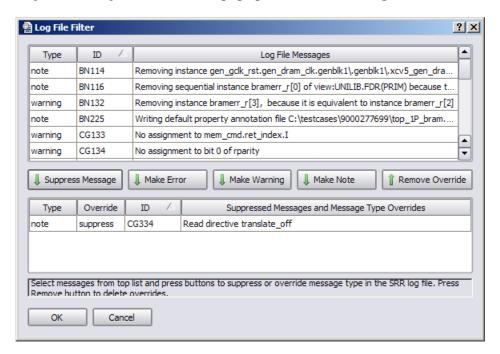

| Handling Messages Checking Results in the Message Viewer Filtering Messages in the Message Viewer Filtering Messages from the Command Line Automating Message Filtering with a Tcl Script Log File Message Controls Handling Warnings |     |

| Chapter 9: Analyzing with HDL Analyst and FSM Viewer                                                                                                                                                                                  | •   |

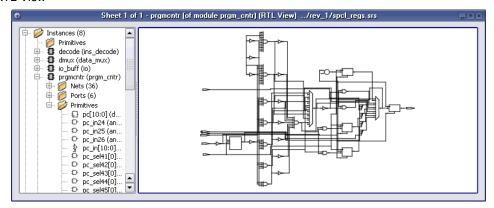

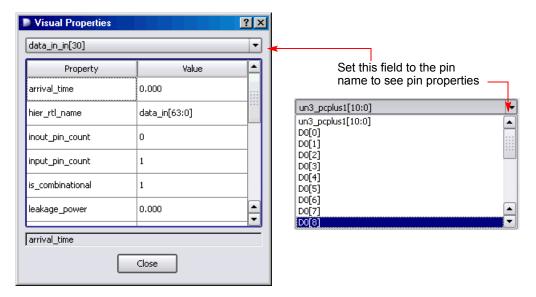

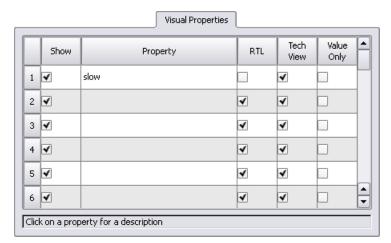

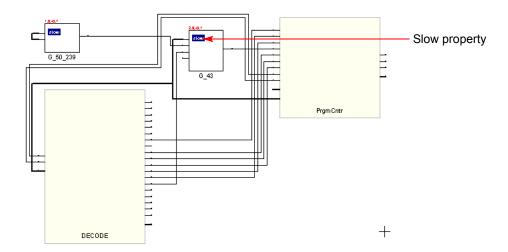

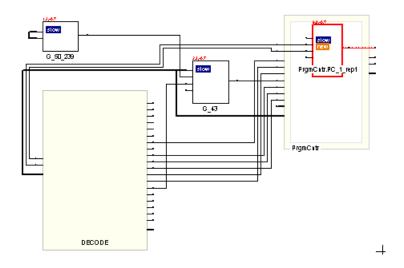

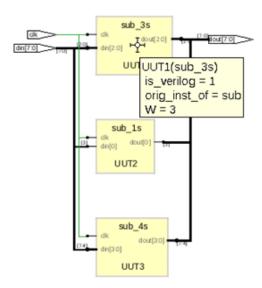

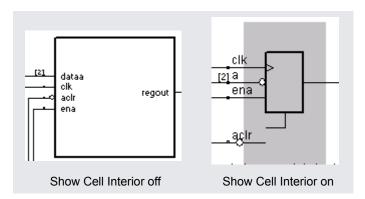

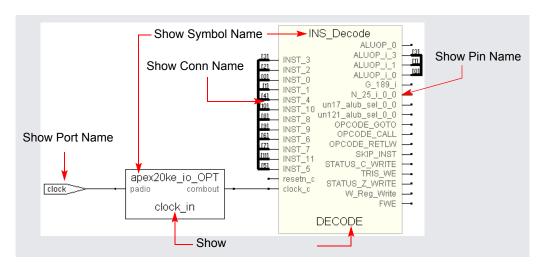

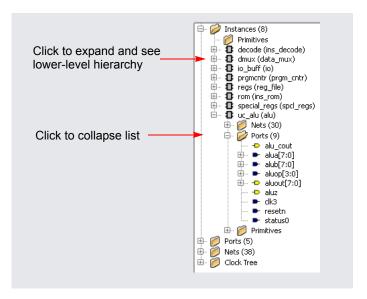

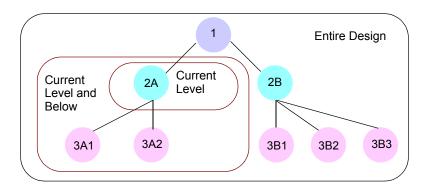

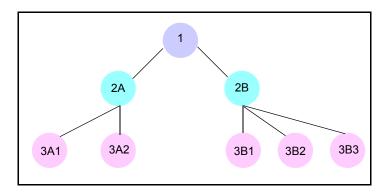

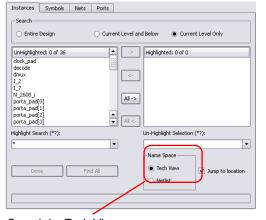

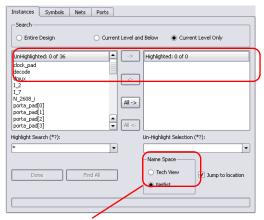

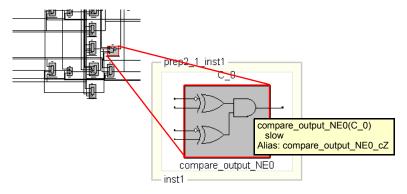

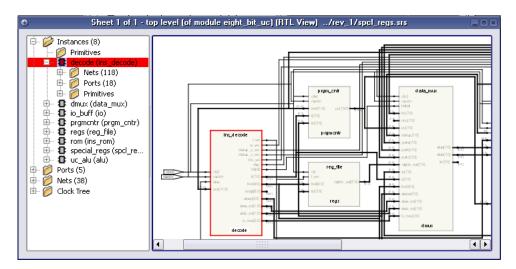

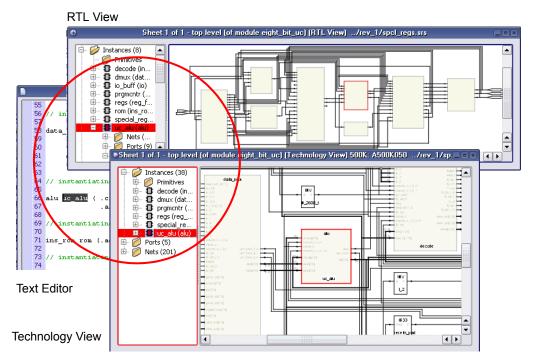

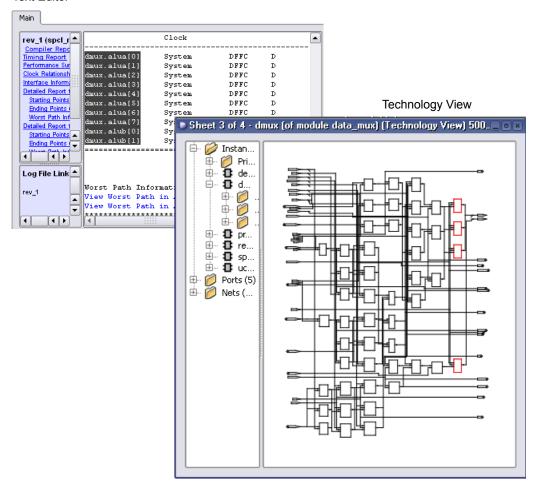

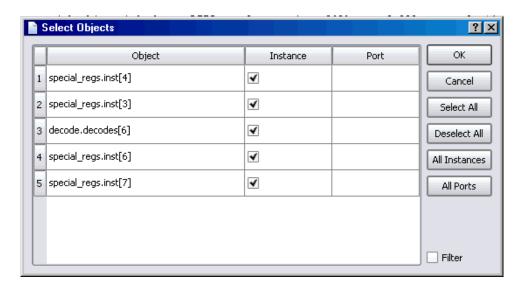

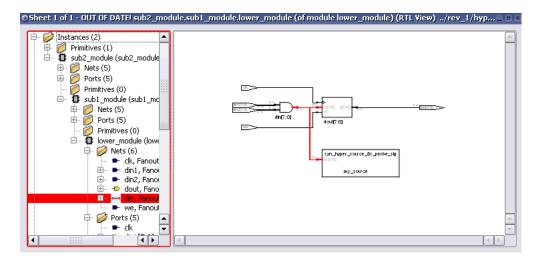

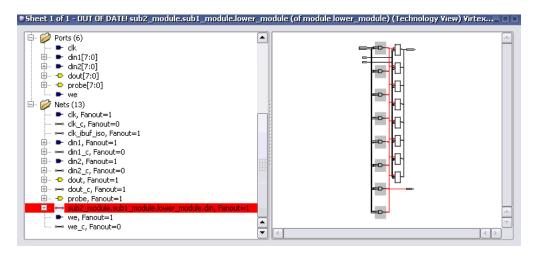

| Working in the Schematic Views  Differentiating Between the Views  Opening the Views  Viewing Object Properties  Selecting Objects in the RTL/Technology Views                                                                        |     |

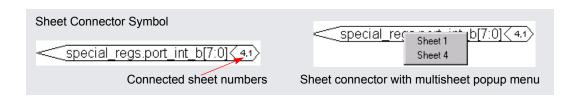

| Working with Multisheet Schematics  Moving Between Views in a Schematic Window  Setting Schematic View Preferences  Managing Windows                                                                                                  | 267 |

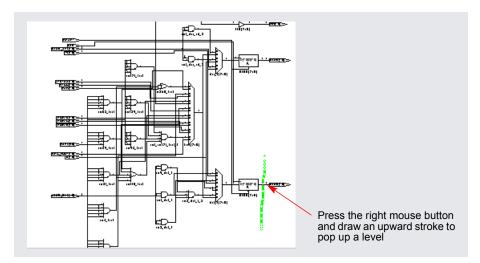

| Moving Between Views in a Schematic Window                                                                                                                                                                                            |     |

| Crossprobing Crossprobing within an RTL/Technology View Crossprobing from the RTL/Technology View Crossprobing from the Text Editor Window Crossprobing from the Tcl Script Window Crossprobing from the FSM Viewer                        | . 291<br>. 292<br>. 294<br>. 297       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

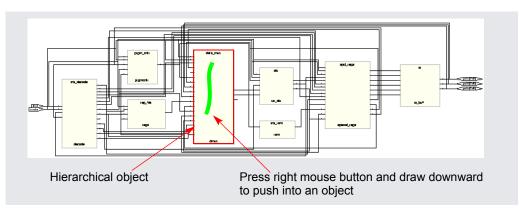

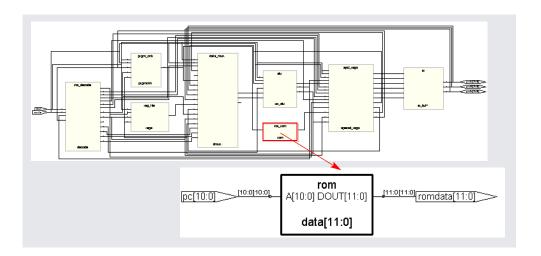

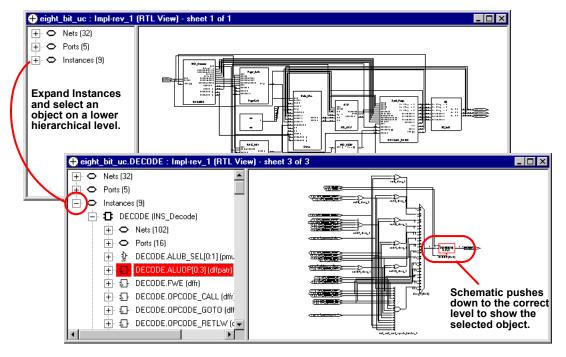

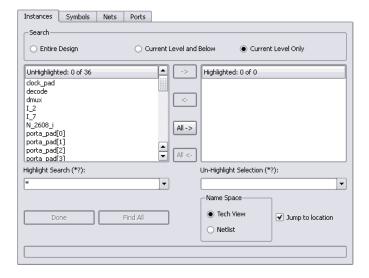

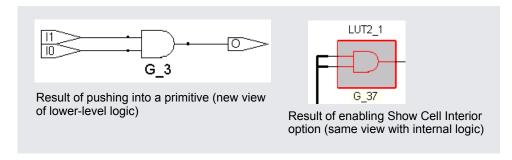

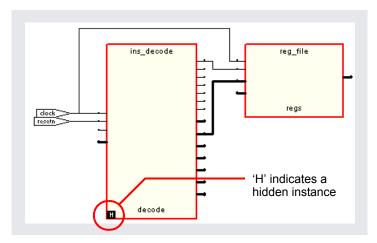

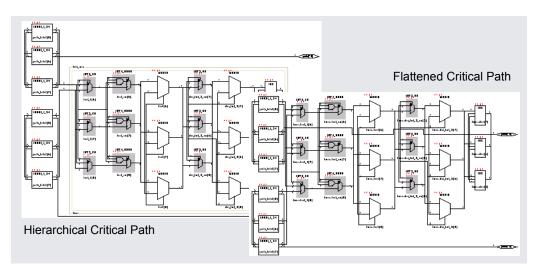

| Analyzing With the HDL Analyst Tool Viewing Design Hierarchy and Context Filtering Schematics Expanding Pin and Net Logic Expanding and Viewing Connections Flattening Schematic Hierarchy Minimizing Memory Usage While Analyzing Designs | 300<br>303<br>305<br>309<br>311<br>315 |

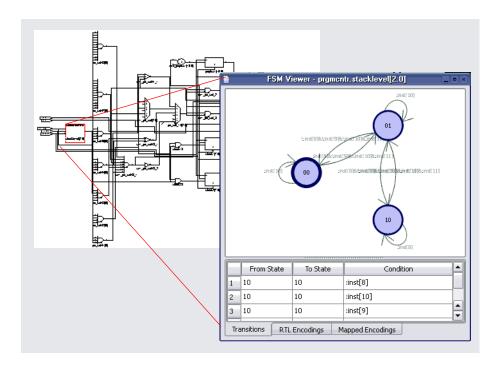

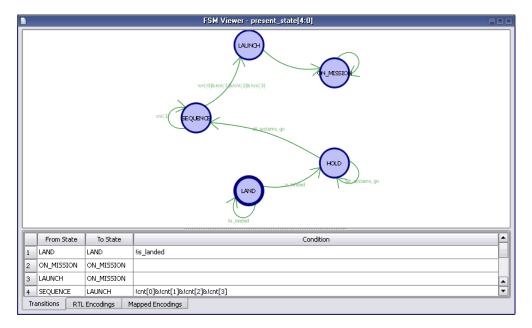

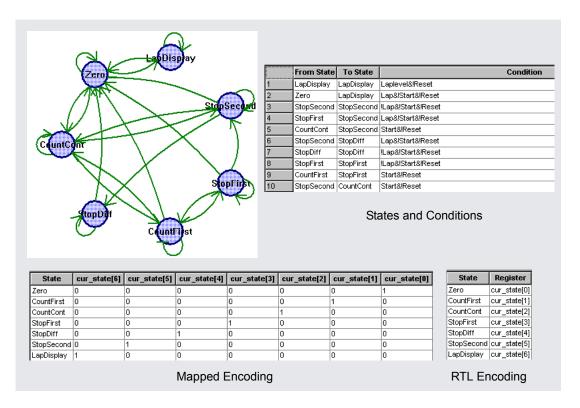

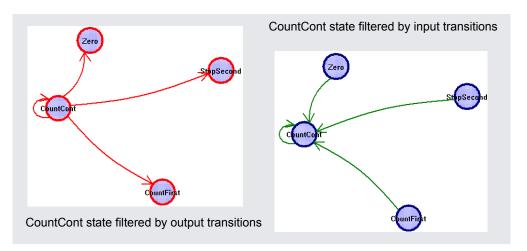

| Using the FSM Viewer                                                                                                                                                                                                                       | . 315                                  |

| Chapter 10: Analyzing Timing                                                                                                                                                                                                               |                                        |

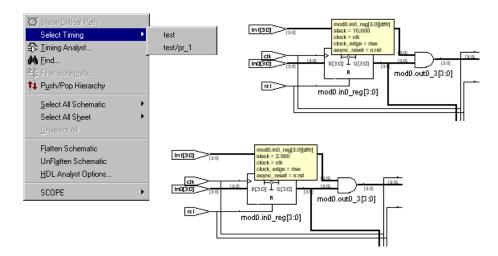

| Analyzing Timing in Schematic Views Viewing Timing Information Annotating Timing Information in the Schematic Views Analyzing Clock Trees in the RTL View Viewing Critical Paths Handling Negative Slack                                   | 322<br>323<br>325<br>325               |

| Generating Custom Timing Reports with STA                                                                                                                                                                                                  | 329                                    |

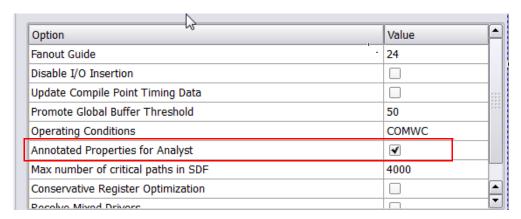

| Using Analysis Design Constraints                                                                                                                                                                                                          | 333<br>334                             |

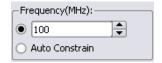

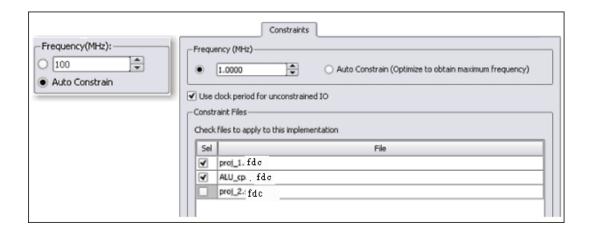

| Using Auto Constraints                                                                                                                                                                                                                     |                                        |

| Chapter 11: Optimizing for Microsemi Designs                                                                                                                                                                                               |                                        |

| Optimizing Microsemi Designs Using Predefined Microsemi Black Boxes Using Smartgen Macros Working with Radhard Designs Specifying syn_radhardlevel in the Source Code                                                                      | 346<br>347<br>347                      |

| Chapter 12: Working with Synthesis Output                                                                                                                                                                                                  |                                        |

| Passing Information to the P&R Tools                                                                                                                                                                                                       | 352                                    |

| Specifying Pin Locations       35         Specifying Locations for Microsemi Bus Ports       35         Specifying Macro and Register Placement       35                                                                                       | 3                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Generating Vendor-Specific Output35Targeting Output to Your Vendor35Customizing Netlist Formats35                                                                                                                                              | 4                   |

| Chapter 13: Running Post-Synthesis Operations                                                                                                                                                                                                  |                     |

| Running P&R Automatically after Synthesis                                                                                                                                                                                                      | 8                   |

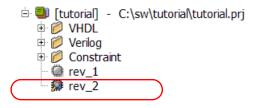

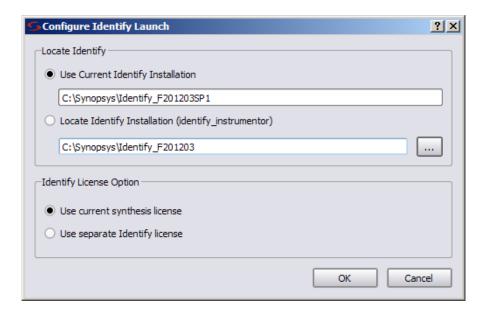

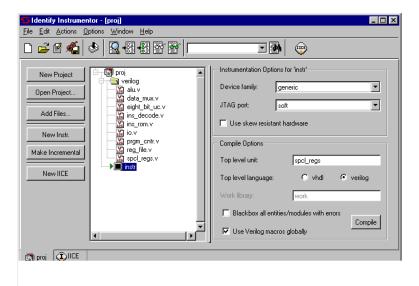

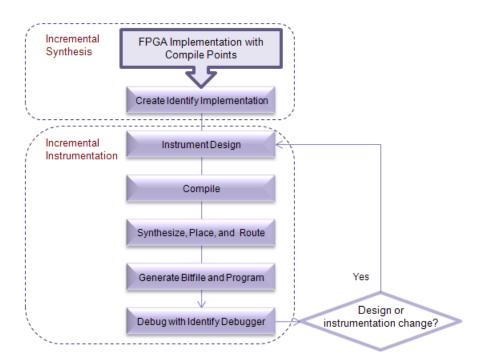

| Working with the Identify Tools                                                                                                                                                                                                                | 59<br>51<br>52      |

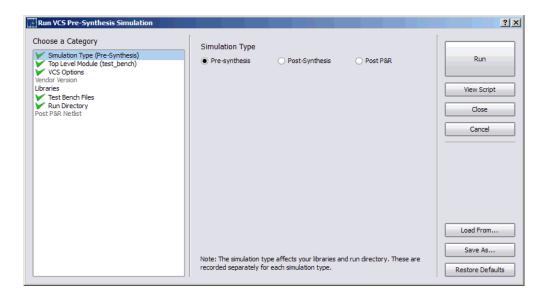

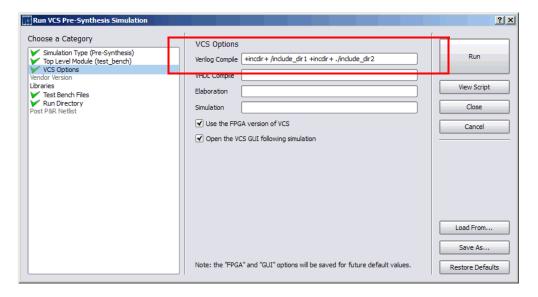

| Simulating with the VCS Tool                                                                                                                                                                                                                   | 6                   |

| Chapter 14: Working with IP Input                                                                                                                                                                                                              |                     |

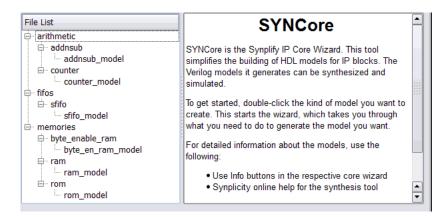

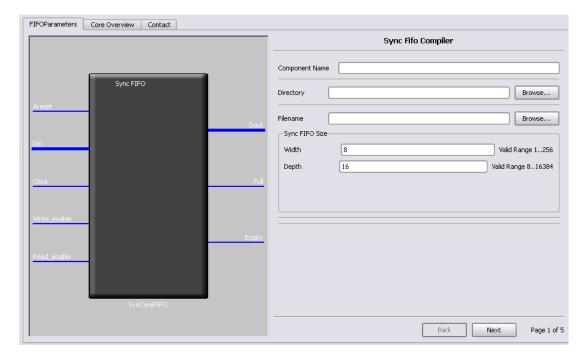

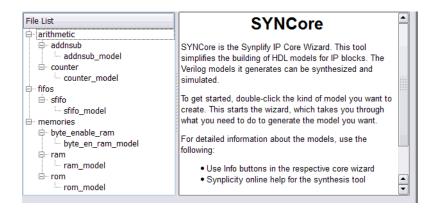

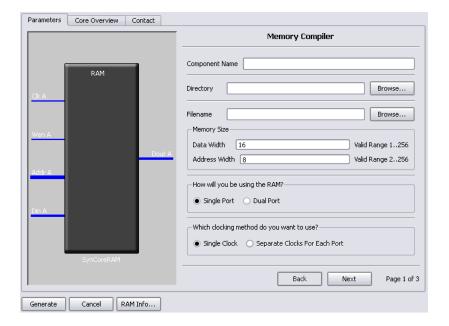

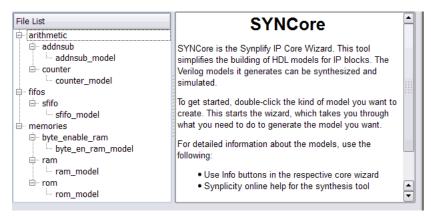

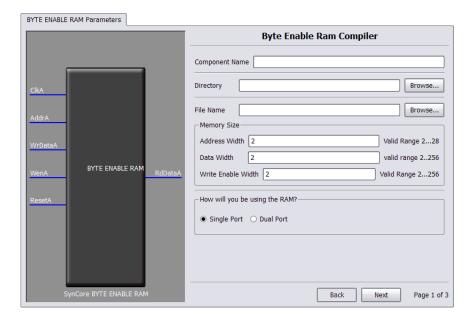

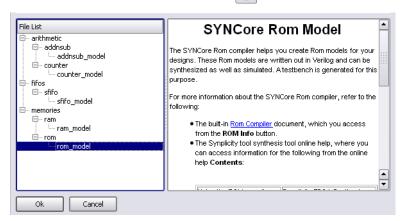

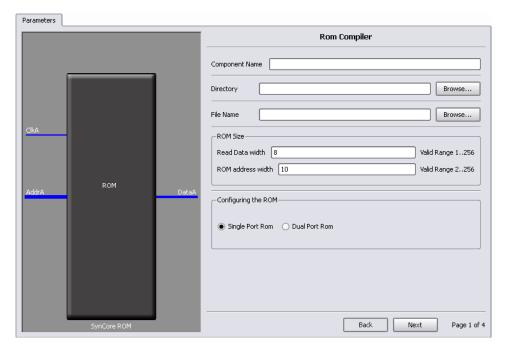

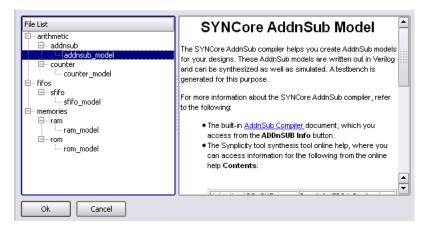

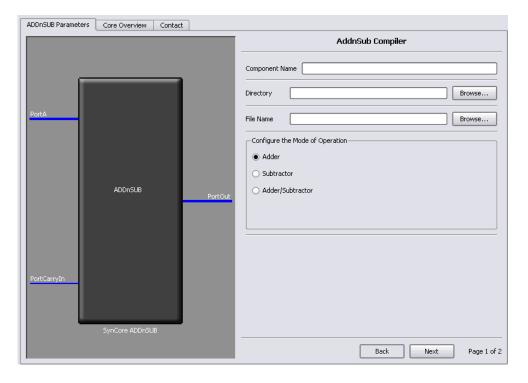

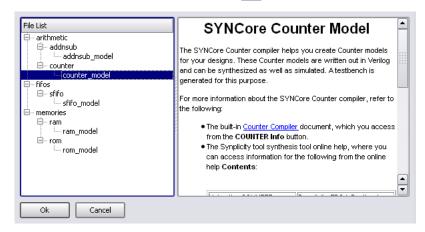

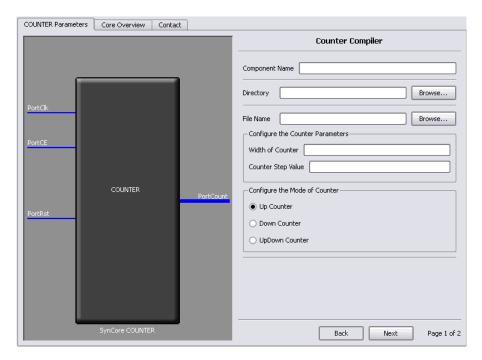

| Generating IP with SYNCore37Specifying FIFOs with SYNCore37Specifying RAMs with SYNCore37Specifying Byte-Enable RAMs with SYNCore38Specifying ROMs with SYNCore39Specifying Adder/Subtractors with SYNCore39Specifying Counters with SYNCore40 | '2<br>'8<br>6<br>92 |

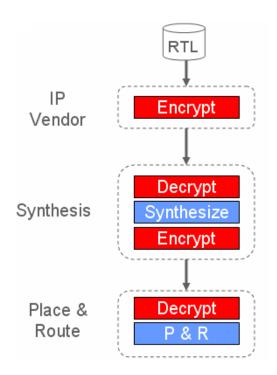

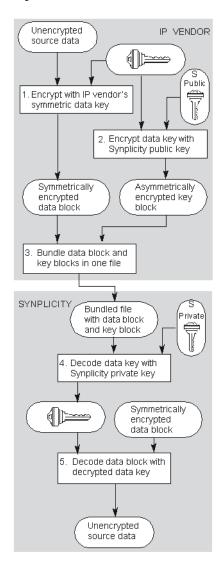

| The Synopsys FPGA IP Encryption Flow                                                                                                                                                                                                           | 0                   |

| Working with Encrypted IP                                                                                                                                                                                                                      | 6<br>8<br>9         |

| Using Hyper Source                                                                                                                                                                                                                             | 26<br>26            |

## **Chapter 15: Working with Compile Points**

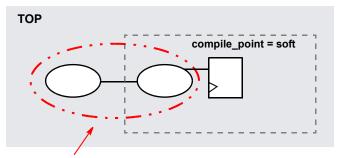

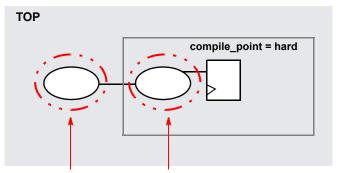

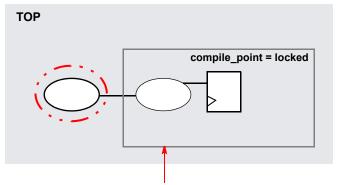

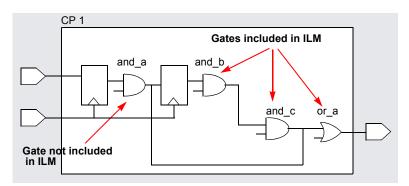

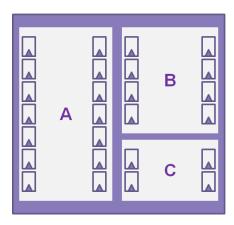

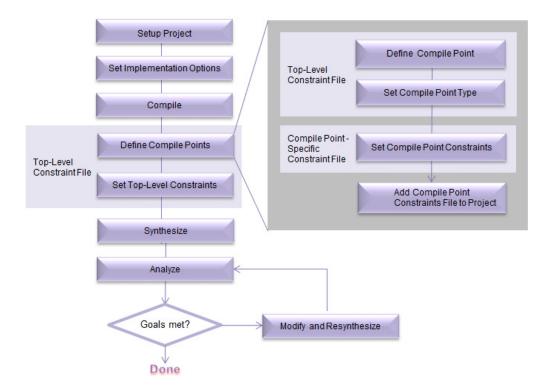

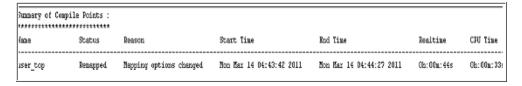

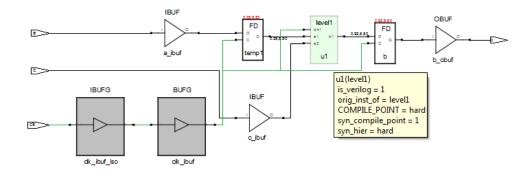

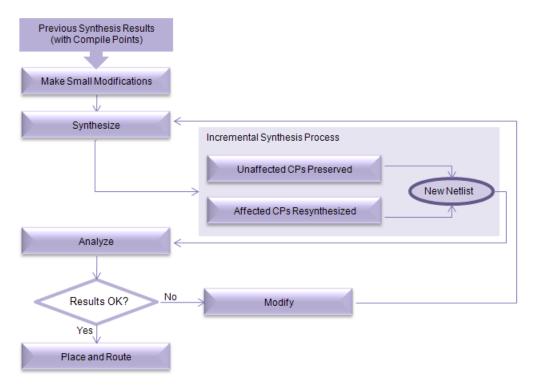

| Compile Point Basics Advantages of Compile Point Design Manual Compile Points Nested Compile Points Compile Point Types                                                                                                                     | 432                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Compile Point Synthesis Basics Compile Point Constraint Files Interface Logic Models Interface Timing for Compile Points Compile Point Synthesis Incremental Compile Point Synthesis Forward-annotation of Compile Point Timing Constraints | 441<br>444<br>447<br>450        |

| Synthesizing Compile Points The Manual Compile Point Flow Creating a Top-Level Constraints File for Compile Points Defining Manual Compile Points Setting Constraints at the Compile Point Level Analyzing Compile Point Results            | 452<br>454<br>455<br>458        |

| Using Compile Points with Other Features                                                                                                                                                                                                    |                                 |

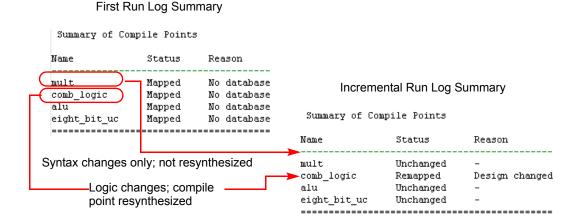

| Resynthesizing Incrementally                                                                                                                                                                                                                |                                 |

| Chapter 16: Optimizing Processes for Productivity                                                                                                                                                                                           |                                 |

| Using Batch Mode                                                                                                                                                                                                                            | 468                             |

| Working with Tcl Scripts and Commands Using Tcl Commands and Scripts Generating a Job Script Setting Number of Parallel Jobs Creating a Tcl Synthesis Script Using Tcl Variables to Try Different Clock Frequencies                         | 474<br>474<br>475<br>476<br>478 |

| Using Tcl Variables to Try Several Target Technologies Running Bottom-up Synthesis with a Script                                                                                                                                            | 480                             |

| Automating Flows with synhooks.tcl                                                                                                                                                                                                          | 481                             |

## **Chapter 17: Using Multiprocessing**

| Multiprocessing With C | Compile Points | 486 |

|------------------------|----------------|-----|

| Setting Maximum I      | Parallel Jobs  | 486 |

| License Utilization    |                | 487 |

#### CHAPTER 1

# Introduction

This introduction to the Synplify Pro® software describes the following:

- Synopsys FPGA and Prototyping Products, on page 16

- Scope of the Document, on page 21

- Getting Started, on page 22

- User Interface Overview, on page 24

# Synopsys FPGA and Prototyping Products

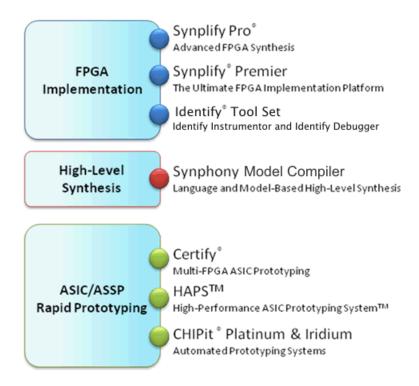

The following figure displays the Synopsys FPGA and Prototyping family of products.

### **FPGA Implementation Tools**

The Synplify Pro and Synplify Premier products are RTL synthesis tools especially designed for FPGAs (field programmable gate arrays) and CPLDs (complex programmable logic devices).

#### **Synplify Pro Product**

The Synplify Pro FPGA synthesis software is the de facto industry standard for producing high-performance, cost-effective FPGA designs. Its unique Behavior Extracting Synthesis Technology® (B.E.S.T.<sup>TM</sup>) algorithms, perform high-level optimizations before synthesizing the RTL code into specific FPGA logic. This approach allows for superior optimizations across the FPGA, fast runtimes, and the ability to handle very large designs. The Synplify Pro software supports the latest VHDL and Verilog language constructs including SystemVerilog and VHDL 2008. The tool is technology independent allowing quick and easy retargeting between FPGA devices and vendors from a single design project.

#### **Synplify Premier Product**

The Synplify Premier solution is a superset of the Synplify Pro product functionality and is the ultimate FPGA implementation and debug environment. It provides a comprehensive suite of tools and technologies for advanced FPGA designers, as well as ASIC prototypers targeting single FPGA-based prototypes. The Synplify Premier software is a technology independent solution that addresses the most challenging aspects of FPGA design including timing closure, logic verification, IP usage, ASIC compatibility, DSP implementation, debug, and tight integration with FPGA vendor back-end tools.

The Synplify Premier product offers FPGA designers and ASIC prototypers, targeting single FPGA-based prototypes, with the most efficient method of design implementation and debug. The Synplify Premier software provides in-system verification of FPGAs, dramatically accelerates the debug process, and provides a rapid and incremental method for finding elusive design problems.

Features exclusively supported in the Synplify Premier tool are the following:

- Fast and Enhanced Synthesis Modes

- Physical Synthesis

- Design Planning (Optional)

- DesignWare Support

- Integrated RTL Debug (Identify Tool Set)

- Power Switching Activity (SAIF Generation)

## **Synopsys FPGA Tool Features**

This table distinguishes between the Synplify Pro, Synplify, Synplify Premier, and Synplify Premier with Design Planner products.

|                                                            | Synplify | Synplify<br>Pro | Synplify<br>Premier | Synplify<br>Premier DP |

|------------------------------------------------------------|----------|-----------------|---------------------|------------------------|

| Performance                                                |          |                 |                     |                        |

| Behavior Extracting Synthesis<br>Technology® (BEST™)       | х        | X               | Х                   | Х                      |

| Vendor-Generated Core/IP<br>Support (certain technologies) |          | X               | X                   | Х                      |

| FSM Compiler                                               | X        | X               | X                   | X                      |

| FSM Explorer                                               |          | X               | X                   | X                      |

| Gated Clock Conversion                                     |          | X               | X                   | X                      |

| Register Pipelining                                        |          | X               | X                   | X                      |

| Register Retiming                                          |          | X               | X                   | X                      |

| Code Analysis                                              |          |                 |                     |                        |

| SCOPE® Spreadsheet                                         | X        | X               | X                   | X                      |

| HDL Analyst®                                               | Option   | X               | X                   | X                      |

| Timing Analyzer – Point-to-point                           |          | X               | X                   | X                      |

| FSM Viewer                                                 |          | X               | X                   | X                      |

| Crossprobing                                               |          | X               | X                   | X                      |

| Probe Point Creation                                       |          | X               | X                   | X                      |

| Physical Design                                            |          |                 |                     |                        |

| Design Plan File                                           |          |                 |                     | X                      |

| Logic Assignment to Regions                                |          |                 |                     | X                      |

| Area Estimation and Region<br>Capacity                     |          |                 |                     | x                      |

| Pin Assignment                                             |          |                 |                     | X                      |

|                                           | Synplify | Synplify<br>Pro | Synplify<br>Premier                      | Synplify<br>Premier DP                   |

|-------------------------------------------|----------|-----------------|------------------------------------------|------------------------------------------|

| Physical Synthesis<br>Optimizations       |          |                 |                                          | х                                        |

| Graph-based Physical Synthesis            |          |                 | X                                        | X                                        |

| Physical Analyst                          |          |                 | X                                        | X                                        |

| Prototyping                               |          |                 | X                                        | X                                        |

| Synopsys DesignWare<br>Foundation Library |          |                 | X                                        | X                                        |

| Runtime Advantages                        |          |                 |                                          |                                          |

| Enhanced Optimization                     |          |                 | X                                        | X                                        |

| Fast Synthesis                            |          |                 | X                                        | X                                        |

| Team Design                               |          |                 |                                          |                                          |

| Mixed Language Design                     |          | Х               | X                                        | X                                        |

| Compile Points                            |          | X               | X                                        | X                                        |

| True Batch Mode (Floating licenses only)  |          | Х               | X                                        | X                                        |

| GUI Batch Mode (Floating<br>licenses)     | ×        | ×               | ×                                        | X                                        |

| Batch Mode Post-synthesis P&R<br>Run      | -        | ×               | ×                                        | ×                                        |

| Back-annotation of P&R Data               | -        | -               | -                                        | ×                                        |

| Formal Verification Flow                  |          | X               | x<br>(Physical<br>synthesis<br>disabled) | x<br>(Physical<br>synthesis<br>disabled) |

| Identify Integration                      | Limited  | X               | X                                        | X                                        |

| Back-annotation of P&R Data               |          |                 |                                          | X                                        |

| Design Environment                        |          |                 |                                          |                                          |

| Technical Resource Center                 | X        | X               | X                                        | X                                        |

| Text Editor View                          | X        | X               | X                                        | X                                        |

|                                     | Synplify | Synplify<br>Pro | Synplify<br>Premier | Synplify<br>Premier DP |

|-------------------------------------|----------|-----------------|---------------------|------------------------|

| Watch Window                        |          | X               | X                   | X                      |

| Message Window                      |          | X               | X                   | X                      |

| Tcl Window                          |          | X               | X                   | X                      |

| Workspaces                          |          | X               | X                   | X                      |

| Multiple Implementations            |          | X               | X                   | X                      |

| Vendor Technology/Family<br>Support | Х        | Х               | Limited             | Limited                |

# Scope of the Document

The following explain the scope of this document and the intended audience.

#### The Document Set

This user guide is part of a document set that includes a reference manual and a tutorial. It is intended for use with the other documents in the set. It concentrates on describing how to use the Synopsys FPGA software to accomplish typical tasks. This implies the following:

- The user guide only explains the options needed to do the typical tasks described in the manual. It does not describe every available command and option. For complete descriptions of all the command options and syntax, refer to the User Interface Overview chapter in the Synopsys FPGA Synthesis Reference Manual.

- The user guide contains task-based information. For a breakdown of how information is organized, see Getting Help, on page 22.

#### **Audience**

The Synplify Pro software tool is targeted towards the FPGA system developer. It is assumed that you are knowledgeable about the following:

- Design synthesis

- RTL

- FPGAs

- Verilog/VHDL

# **Getting Started**

This section shows you how to get started with the Synopsys FPGA synthesis software. It describes the following topics, but does not supersede the information in the installation instructions about licensing and installation:

- Starting the Software, on page 22

- Getting Help, on page 22

### Starting the Software

- 1. If you have not already done so, install the Synopsys FPGA synthesis software according to the installation instructions.

- 2. Start the software.

- If you are working on a Windows platform, select

Programs->Synopsys->product version from the Start button.

- If you are working on a UNIX platform, type the appropriate command at the command line:

```

symplify pro

```

• The command starts the synthesis tool, and opens the Project window. If you have run the software before, the window displays the previous project. For more information about the interface, see the User Interface Overview chapter of the *Reference Manual*.

### **Getting Help**

Before you call Synopsys Support, look through the documented information. You can access the information online from the Help menu, or refer to the PDF version. The following table shows you how the information is organized.

| For help with             | Refer to the                                                                  |

|---------------------------|-------------------------------------------------------------------------------|

| Using software features   | Synopsys FPGA Synthesis User Guide                                            |

| How to                    | Synopsys FPGA Synthesis User Guide, application notes on the support web site |

| Flow information          | Synopsys FPGA Synthesis User Guide, application notes on the support web site |

| Error messages            | Online help (select Help->Error Messages)                                     |

| Licensing                 | Synopsys SolvNet Website                                                      |

| Attributes and directives | Synopsys FPGA Synthesis Reference Manual                                      |

| Synthesis features        | Synopsys FPGA Synthesis Reference Manual                                      |

| Language and syntax       | Synopsys FPGA Synthesis Reference Manual                                      |

| Tcl syntax                | Online help (select Help->Tcl Help)                                           |

| Tcl synthesis commands    | Synopsys FPGA Synthesis Reference Manual                                      |

| Product updates           | Synopsys FPGA Synthesis Reference Manual (Web menu commands)                  |

|                           |                                                                               |

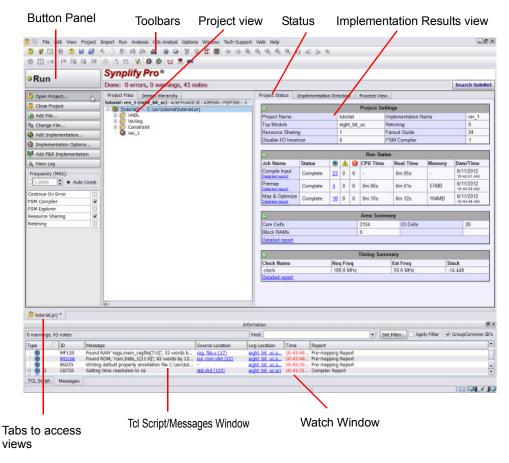

## **User Interface Overview**

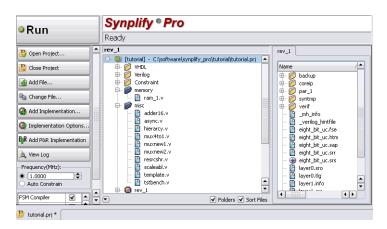

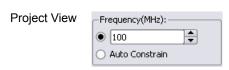

The user interface (UI) consists of a main window, called the Project view, and specialized windows or views for different tasks. For details about each of the features, see Chapter 2, *User Interface Overview* of the *Synopsys FPGA Synthesis Reference Manual*.

#### Synplify Pro Interface

#### **CHAPTER 2**

# FPGA Synthesis Design Flows

This chapter describes the Logic Synthesis Design Flow, on page 26.

# Logic Synthesis Design Flow

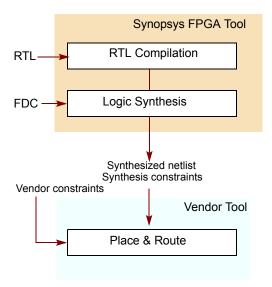

The Synopsys FPGA tools synthesize logic by first compiling the RTL source, and then doing logical mapping and optimizations. After logic synthesis, you get a vendor-specific netlist and constraint file that you use as inputs to the place-and-route (P&R) tool.

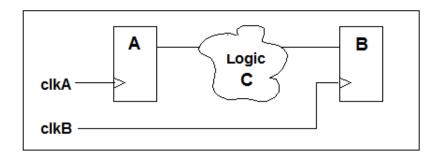

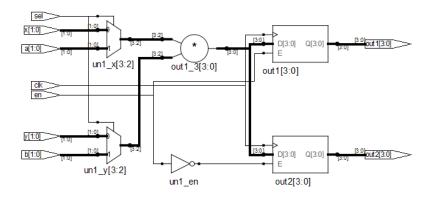

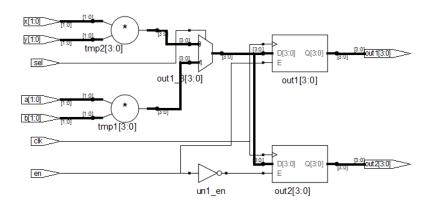

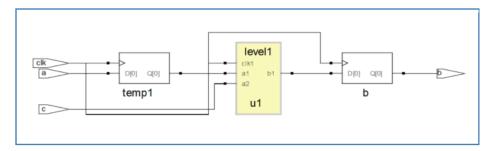

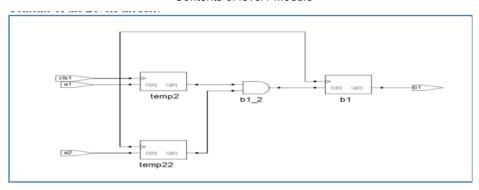

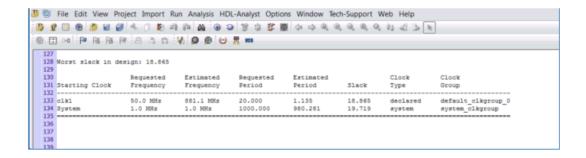

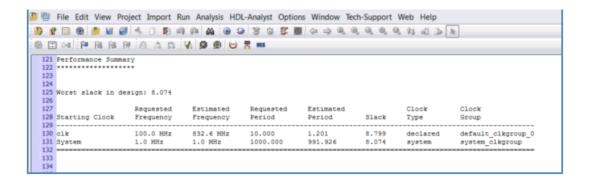

The following figure shows the phases and the tools used for logic synthesis and some of the major inputs and outputs. You can use the Synplify Pro synthesis software for this flow. The interactive timing analysis is optional. Although the flow shows the vendor constraint files as direct inputs to the P&R tool, you should add these files to the synthesis project for timing black boxes.

#### **Logic Synthesis Procedure**

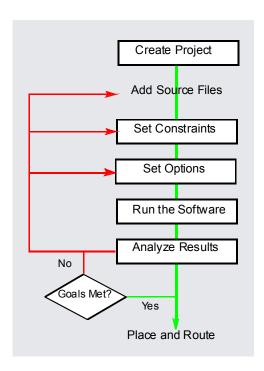

For a design flow with step-by-step instructions based on specific design data, download the tutorial from the website. The following steps summarize the process, which is also illustrated in the figure that follows.

- 1. Create a project.

- 2. Add the source files to the project.

- 3. Set attributes and constraints for the design.

- 4. Set options for the implementation in the Implementation Options dialog box.

- 5. Click Run to run logic synthesis.

- 6. Analyze the results, using the log file, the HDL Analyst schematic views, the Message window and the Watch Window.

After you have completed the design, you can use the output files to run place-and-route with the vendor tool and implement the FPGA.

The following figure lists the main steps in the flow:

#### **CHAPTER 3**

# Preparing the Input

When you synthesize a design, you need to set up two kinds of files: HDL files that describe your design, and project files to manage the design. This chapter describes the procedures to set up these files and the project. It covers the following:

- Setting Up HDL Source Files, on page 30

- Using Mixed Language Source Files, on page 41

- Working with Constraint Files, on page 46

# Setting Up HDL Source Files

This section describes how to set up your source files; project file setup is described in Setting Up Project Files, on page 112. Source files can be in Verilog or VHDL. For information about structuring the files for synthesis, refer to the *Reference Manual*. This section discusses the following topics:

- Creating HDL Source Files, on page 30

- Using the Context Help Editor, on page 32

- Checking HDL Source Files, on page 33

- Editing HDL Source Files with the Built-in Text Editor, on page 34

- Using an External Text Editor, on page 40

- Setting Editing Window Preferences, on page 38

### **Creating HDL Source Files**

This section describes how to use the built-in text editor to create source files, but does not go into details of what the files contain. For details of what you can and cannot include, as well as vendor-specific information, see the *Reference Manual*. If you already have source files, you can use the text editor to check the syntax or edit the file (see Checking HDL Source Files, on page 33 and Editing HDL Source Files with the Built-in Text Editor, on page 34).

You can use Verilog or VHDL for your source files. The files have v (Verilog) or vhd (VHDL) file extensions, respectively. You can use Verilog and VHDL files in the same design. For information about using a mixture of Verilog and VHDL input files, see Using Mixed Language Source Files, on page 41.

- 1. To create a new source file either click the HDL file icon ( or do the following:

- Select File->New or press Ctrl-n.

- In the New dialog box, select the kind of source file you want to create, Verilog or VHDL. Note that you can use the Context Help Editor for Verilog designs that contain SystemVerilog constructs in the source file. For more information, see Using the Context Help Editor, on page 32.

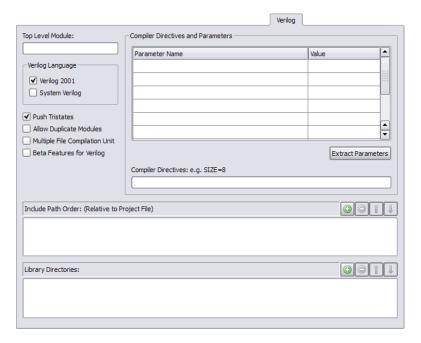

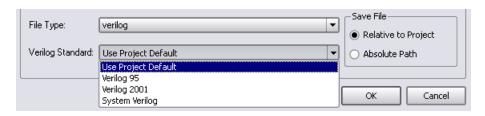

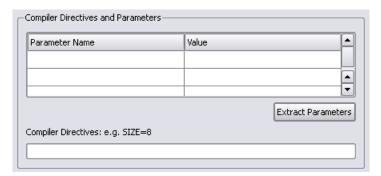

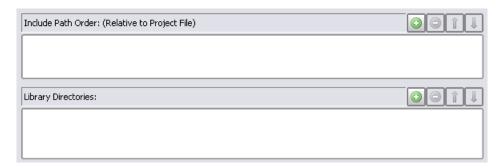

If you are using Verilog 2001 format or SystemVerilog, make sure to enable the Verilog 2001 or System Verilog option before you run synthesis (Project->Implementation Options->Verilog tab). The default Verilog file format for new projects is SystemVerilog.

- Type a name and location for the file and Click OK. A blank editing window opens with line numbers on the left.

- 2. Type the source information in the window, or cut and paste it. See Editing HDL Source Files with the Built-in Text Editor, on page 34 for more information on working in the Editing window.

For the best synthesis results, check the Reference Manual and ensure that you are using the available constructs and vendor-specific attributes and directives effectively.

3. Save the file by selecting File->Save or the Save icon ( ).

Once you have created a source file, you can check that you have the right syntax, as described in Checking HDL Source Files, on page 33.

### **Using the Context Help Editor**

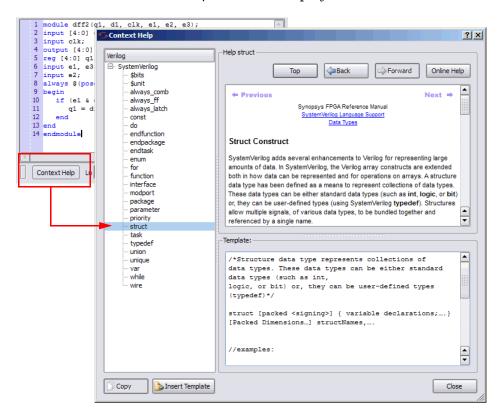

When you create or open a Verilog design file, use the Context Help button displayed at the bottom of the window to help you code with SystemVerilog constructs in the source file. This feature is currently supported for some of the SystemVerilog constructs.

To use the Context Help Editor:

1. Click on the Context Help button to display this text editor.

- 2. When you select a construct in the left-side of the window, the online help description for the construct is displayed. If the selected construct has this feature enabled, the online help topic is displayed on the top of the window and a generic code template for that construct is displayed at the bottom.

- 3. The Insert Template button is also enabled. When you click the Insert Template button, the code shown in the template window is inserted into your SystemVerilog file at the location of the cursor. This allows you to easily insert code and modify it for the design that you are going to synthesize.

- 4. If you want to copy only parts of the template, select the code you want to insert and click Copy. You can then paste it into your file.

### **Checking HDL Source Files**

The software automatically checks your HDL source files when it compiles them, but if you want to check your source code before synthesis, use the following procedure. There are two kinds of checks you do in the synthesis software: syntax and synthesis.

- 1. Select the source files you want to check.

- To check all the source files in a project, deselect all files in the project list, and make sure that none of the files are open in an active window. If you have an active source file, the software only checks the active file.

- To check a single file, open the file with File->Open or double-click the file in the Project window. If you have more than one file open and want to check only one of them, put your cursor in the appropriate file window to make sure that it is the active window.

- 2. To check the syntax, select Run->Syntax Check or press Shift+F7.

The software detects syntax errors such as incorrect keywords and punctuation and reports any errors in a separate log file (syntax.log). If no errors are detected, a successful syntax check is reported at the bottom of this file.

- 3. To run a synthesis check, select Run->Synthesis Check or press Shift+F8.

- The software detects hardware-related errors such as incorrectly coded flip-flops and reports any errors in a separate log file (syntax.log). If there are no errors, a successful syntax check is reported at the bottom of this file.

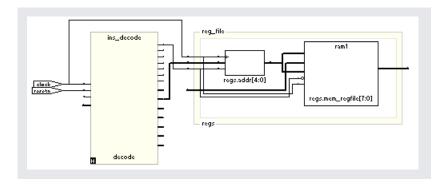

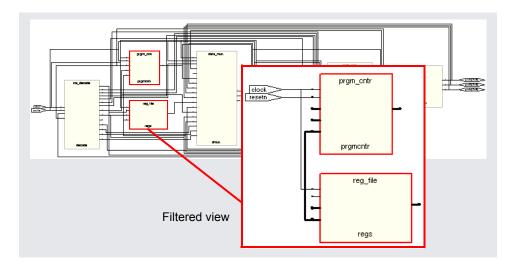

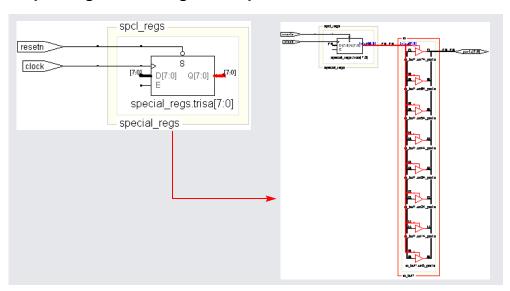

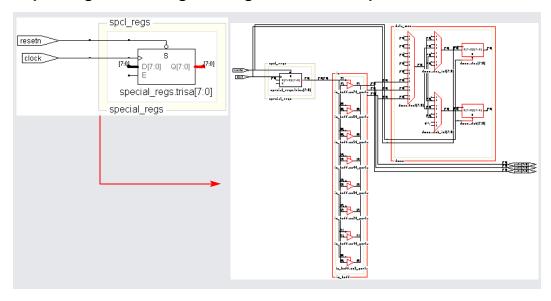

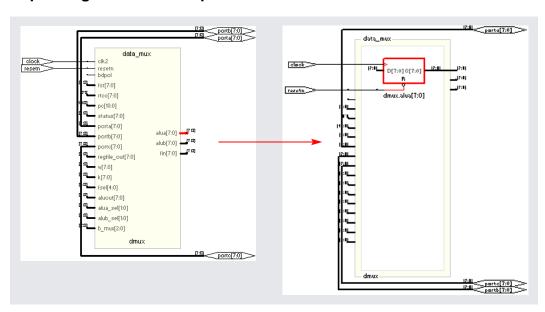

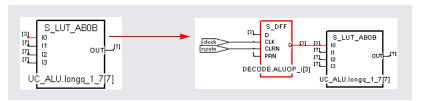

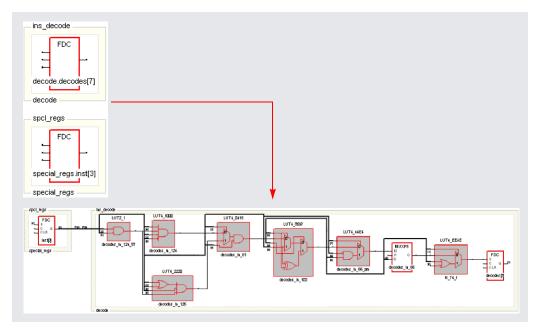

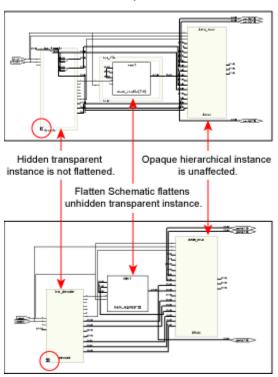

- 4. Review the errors by opening the syntax.log file when prompted and use Find to locate the error message (search for @E). Double-click on the 5-character error code or click on the message text and push F1 to display online error message help.

- 5. Locate the portion of code responsible for the error by double-clicking on the message text in the syntax.log file. The Text Editor window opens the appropriate source file and highlights the code that caused the error.

- 6. Repeat steps 4 and 5 until all syntax and synthesis errors are corrected.

Messages can be categorized as errors, warnings, or notes. Review all messages and resolve any errors. Warnings are less serious than errors, but you must read through and understand them even if you do not resolve all of them. Notes are informative and do not need to be resolved.

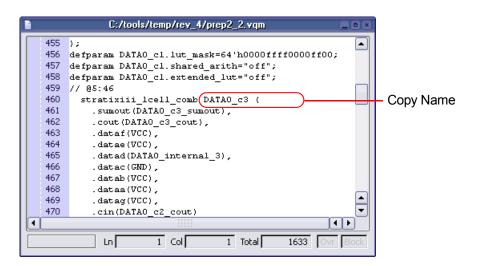

### **Editing HDL Source Files with the Built-in Text Editor**

The built-in text editor makes it easy to create your HDL source code, view it, or edit it when you need to fix errors. If you want to use an external text editor, see Using an External Text Editor, on page 40.

- 1. Do one of the following to open a source file for viewing or editing:

- To automatically open the first file in the list with errors, press F5.

- To open a specific file, double-click the file in the Project window or use File->Open (Ctrl-o) and specify the source file.

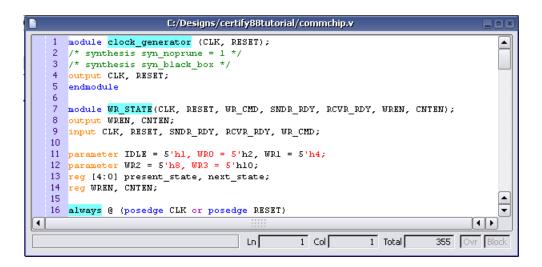

The Text Editor window opens and displays the source file. Lines are numbered. Keywords are in blue, and comments in green. String values are in red. If you want to change these colors, see Setting Editing Window Preferences, on page 38.

2. To edit a file, type directly in the window.

This table summarizes common editing operations you might use. You can also use the keyboard shortcuts instead of the commands.

| То                                               | Do                                                                                                                        |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Cut, copy, and paste;<br>undo, or redo an action | Select the command from the popup (hold down the right mouse button) or Edit menu.                                        |

| Go to a specific line                            | Press Ctrl-g or select Edit->Go To, type the line number, and click OK.                                                   |

| Find text                                        | Press Ctrl-f or select Edit -> Find. Type the text you want to find, and click OK.                                        |

| Replace text                                     | Press Ctrl-h or select Edit->Replace. Type the text you want to find, and the text you want to replace it with. Click OK. |

| Complete a keyword                               | Type enough characters to uniquely identify the keyword, and press Esc.                                                   |

| Indent text to the right                         | Select the block, and press Tab.                                                                                          |

| Indent text to the left                          | Select the block, and press Shift-Tab.                                                                                    |

| Change to upper case                             | Select the text, and then select Edit->Advanced ->Uppercase or press Ctrl-Shift-u.                                        |

|                                                  |                                                                                                                           |

| То                   | Do                                                                                                                                                                                         |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Change to lower case | Select the text, and then select Edit->Advanced ->Lowercase or press Ctrl-u.                                                                                                               |

| Add block comments   | Put the cursor at the beginning of the comment text, and select Edit->Advanced->Comment Code or press Alt-c.                                                                               |

| Edit columns         | Press Alt, and use the left mouse button to select<br>the column. On some platforms, you have to use<br>the key to which the Alt functionality is mapped,<br>like the Meta or diamond key. |

- 3. To cut and paste a section of a PDF document, select the T-shaped Text Select icon, highlight the text you need and copy and paste it into your file. The Text Select icon lets you select parts of the document.

- 4. To create and work with bookmarks in your file, see the following table.

Bookmarks are a convenient way to navigate long files or to jump to points in the code that you refer to often. You can use the icons in the Edit toolbar for these operations. If you cannot see the Edit toolbar on the far right of your window, resize some of the other toolbars.

| Do                                                                                                   |

|------------------------------------------------------------------------------------------------------|

| Click anywhere in the line you want to bookmark.                                                     |

| Select Edit->Toggle Bookmarks, press Ctrl-F2, or select the first icon in the Edit toolbar.          |

| The line number is highlighted to indicate that there is a bookmark at the beginning of that line.   |

| Click anywhere in the line with the bookmark.                                                        |

| Select Edit->Toggle Bookmarks, press Ctrl-F2, or select the first icon in the Edit toolbar.          |

| The line number is no longer highlighted after the bookmark is deleted.                              |

| Select Edit->Delete all Bookmarks, press Ctrl-Shift-F2, or select the last icon in the Edit toolbar. |

| The line numbers are no longer highlighted after the bookmarks are deleted.                          |

|                                                                                                      |

| То                                    | Do                                                                                                                                                                             |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Navigate a file<br>using<br>bookmarks | Use the Next Bookmark (F2) and Previous Bookmark (Shift-F2) commands from the Edit menu or the corresponding icons from the Edit toolbar to navigate to the bookmark you want. |

- 5. To fix errors or review warnings in the source code, do the following:

- Open the HDL file with the error or warning by double-clicking the file in the project list.

- Press F5 to go to the first error, warning, or note in the file. At the bottom of the Editing window, you see the message text.

- To go to the next error, warning, or note, select Run->Next Error/Warning or press F5. If there are no more messages in the file, you see the message "No More Errors/Warnings/Notes" at the bottom of the Editing window. Select Run->Next Error/Warning or press F5 to go to the the error, warning, or note in the next file.

- To navigate back to a previous error, warning, or note, select Run->Previous Error/Warning or press Shift-F5.

- 6. To bring up error message help for a full description of the error, warning, or note:

- Open the text-format log file (click View Log) and either double click on the 5-character error code or click on the message text and press F1.

- Open the HTML log file and click on the 5-character error code.

- In the Tcl window, click the Messages tab and click on the 5-character error code in the ID column.

- 7. To crossprobe from the source code window to other views, open the view and select the piece of code. See Crossprobing from the Text Editor Window, on page 294 for details.

- 8. When you have fixed all the errors, select File->Save or click the Save icon to save the file.

### **Setting Editing Window Preferences**

You can customize the fonts and colors used in a Text Editing window.

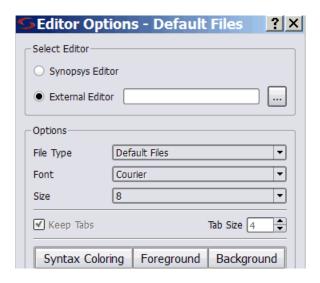

- 1. Select Options->Editor Options and either Synopsys Editor or External Editor. For more information about the external editor, see Using an External Text Editor, on page 40.

- 2. Then depending on the type of file you open, you can to set the background, syntax coloring, and font preferences to use with the text editor.

**Note:** Thereafter, text editing preferences you set for this file will apply to all files of this file type.

The Text Editing window can be used to set preferences for project files, source files (Verilog/VHDL), log files, Tcl files, constraint files, or other default files from the Editor Options dialog box.

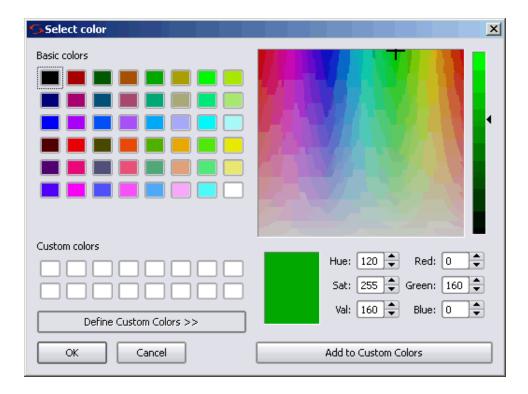

3. You can set syntax colors for some common syntax options, such as keywords, strings, and comments. For example in the log file, warnings and errors can be color-coded for easy recognition.

Click in the Foreground or Background field for the corresponding object in the Syntax Coloring field to display the color palette.

You can select basic colors or define custom colors and add them to your custom color palette. To select your desired color click OK.

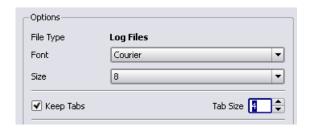

- 4. To set font and font size for the text editor, use the pull-down menus.

- 5. Check Keep Tabs to enable tab settings, then set the tab spacing using the up or down arrow for Tab Size.

6. Click OK on the Editor Options form.

### **Using an External Text Editor**

You can use an external text editor like vi or emacs instead of the built-in text editor. Do the following to enable an external text editor. For information about using the built-in text editor, see Editing HDL Source Files with the Built-in Text Editor, on page 34.

- 1. Select Options->Editor Options and turn on the External Editor option.

- 2. Select the external editor, using the method appropriate to your operating system.

- If you are working on a Windows platform, click the ...(Browse) button and select the external text editor executable.

- From a UNIX or Linux platform for a text editor that creates its own window, click the ... Browse button and select the external text editor executable.

- From a UNIX platform for a text editor that does not create its own window, do not use the ... Browse button. Instead type xterm -e editor. The following figure shows VI specified as the external editor.

From a Linux platform, for a text editor that does not create its own window, do not use the ... Browse button. Instead, type gnome-terminal -x editor. To use emacs for example, type gnome-terminal -x emacs.

The software has been tested with the emacs and vi text editors.

3. Click OK.

# Using Mixed Language Source Files

With the Synplify Pro software, you can use a mixture of VHDL and Verilog input files in your project. For examples of the VHDL and Verilog files, see the *Reference Manual*.

- 1. Remember that Verilog does not support unconstrained VHDL ports and set up the mixed language design files accordingly.

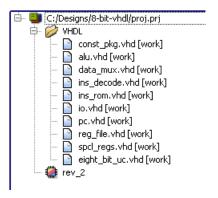

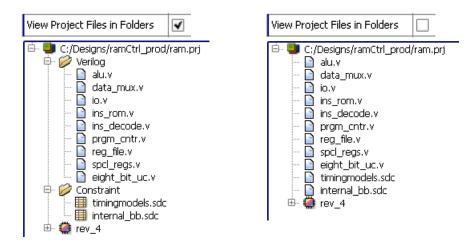

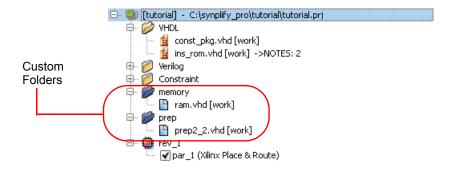

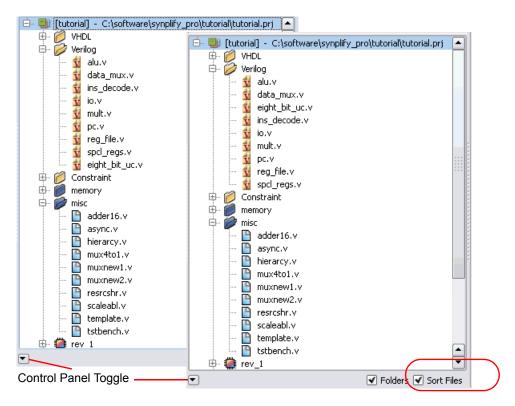

- 2. If you want to organize the Verilog and VHDL files in different folders, select Options->Project View Options and toggle on the View Project Files in Folders option.

When you add the files to the project, the Verilog and VHDL files are in separate folders in the Project view.

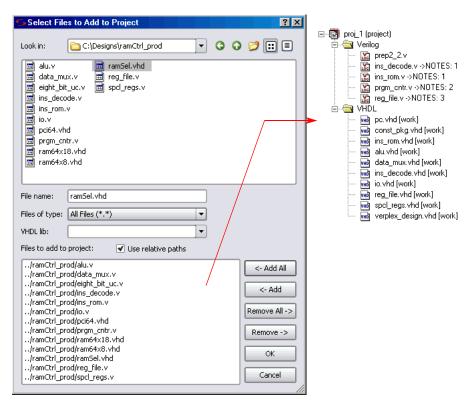

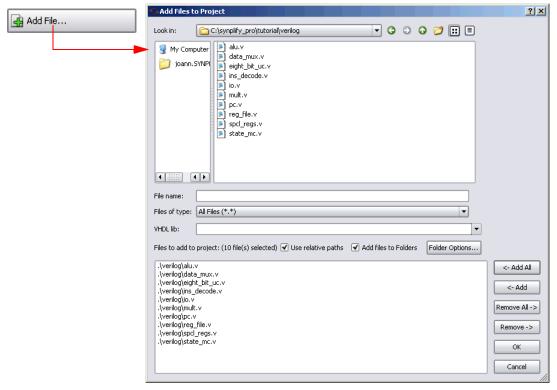

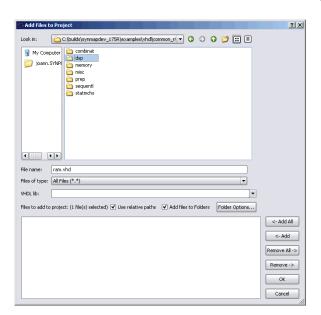

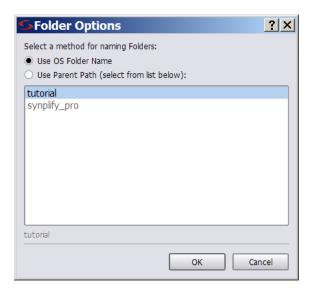

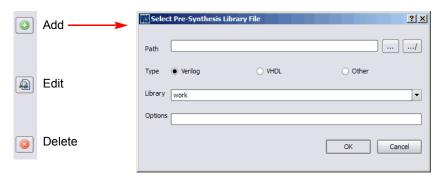

- 3. When you open a project or create a new one, add the Verilog and VHDL files as follows:

- Select the Project->Add Source File command or click the Add File button.

- On the form, set Files of Type to HDL Files (\*.vhd, \*.vhdl, \*.v).

- Select the Verilog and VHDL files you want and add them to your project. Click OK. For details about adding files to a project, see Making Changes to a Project, on page 116.

The files you added are displayed in the Project view. This figure shows the files arranged in separate folders.

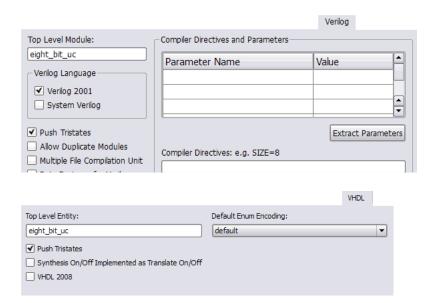

- 4. When you set device options (Implementation Options button), specify the top-level module. For more information about setting device options, see Setting Logic Synthesis Implementation Options, on page 129.

- If the top-level module is Verilog, click the Verilog tab and type the name of the top-level module.

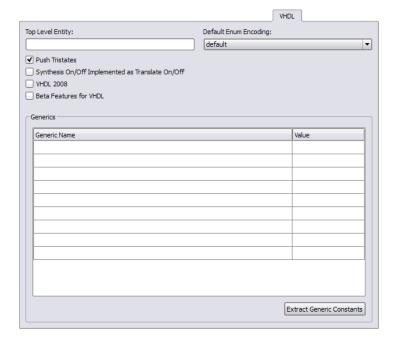

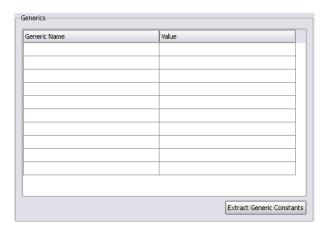

- If the top-level module is VHDL, click the VHDL tab and type the name

of the top-level entity. If the top-level module is not located in the

default work library, you must specify the library where the compiler

can find the module. For information on how to do this, see VHDL

Panel, on page 159.

You must explicitly specify the top-level module, because it is the starting point from which the mapper generates a merged netlist.

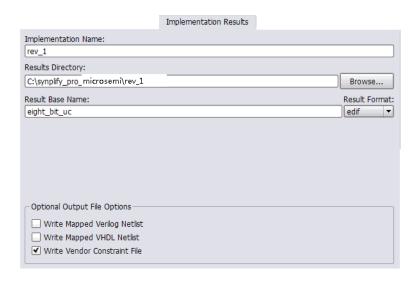

- 5. Select the Implementation Results tab on the same form and select one output HDL format for the output files generated by the software. For more information about setting device options, see Setting Logic Synthesis Implementation Options, on page 129.

- For a Verilog output netlist, select Write Verilog Netlist.

- For a VHDL output netlist, select Write VHDL Netlist.

- Set any other device options and click OK.

You can now synthesize your design. The software reads in the mixed formats of the source files and generates a single srs file that is used for synthesis.

6. If you run into problems, see Troubleshooting Mixed Language Designs, on page 44 for additional information and tips.

### **Troubleshooting Mixed Language Designs**

This section provides tips on handling specific situations that might come up with mixed language designs.

#### VHDL File Order

For VHDL-only designs or mixed designs where the top level is not specified, the FPGA synthesis tools automatically re-arrange the VHDL files so that the VHDL packages are compiled in the correct order.

However, if you have a mixed-language design where you have specified the top level, you must specify the VHDL file order for the tool. You only need to do this once, by selecting the Run->Arrange VHDL files command. If you do not do this, you get an error message.

### VHDL Global Signals

Currently, you cannot have VHDL global signals in mixed language designs, because the tool only implements these signals in VHDL-only designs.

### Passing VHDL Boolean Generics to Verilog Parameters

The tool infers a black box for a VHDL component with Boolean generics, if that component is instantiated in a Verilog design. This is because Verilog does not recognize Boolean data types, so the Boolean value must be represented correctly. If the value of the VHDL Boolean generic is TRUE and the Verilog literal is represented by a 1, the Verilog compiler interprets this as a black box.

To avoid inferring a black box, the Verilog literal for the VHDL Boolean generic set to TRUE must be 1'b1, not 1. Similarly, if the VHDL Boolean generic is FALSE, the corresponding Verilog literal must be 1'b0, not 0. The following example shows how to represent Boolean generics so that they correctly pass the VHDL-Verilog boundary, without inferring a black box.

#### **VHDL Entity Declaration**

#### Verilog Instantiation

```

Entity abc is

Generic

( .Number_Bits (16),

.Divide_Bit (1'b0)

Number_Bits

: integer := 0;

Divide_Bit

: boolean := False;

);

```

### Passing VHDL Generics Without Inferring a Black Box

In the case where a Verilog component parameter, (for example [0:0] RSR = 1'b0) does not match the size of the corresponding VHDL component generic (RSR: integer:= 0), the tool infers a black box.

You can work around this by removing the bus width notation of [0:0] in the Verilog files. Note that you must use a VHDL generic of type integer because the other types do not allow for the proper binding of the Verilog component.

# Working with Constraint Files

Constraint files are text files that are automatically generated by the SCOPE interface (see Specifying SCOPE Constraints, on page 57), or which you create manually with a text editor. They contain Tcl commands or attributes that constrain the synthesis run. Alternatively, you can set constraints in the source code, but this is not the preferred method.

This section contains information about

- When to Use Constraint Files over Source Code, on page 46

- i:statemod.statereg[\*], on page 49

- Tcl Syntax Guidelines for Constraint Files, on page 48

- Generating Constraint Files for Forward Annotation, on page 50

#### When to Use Constraint Files over Source Code

You can add constraints in constraint files (generated by SCOPE interface or entered in a text editor) or in the source code. In general, it is better to use constraint files, because you do not have to recompile for the constraints to take effect. It also makes your source code more portable. See Using the SCOPE Editor, on page 52 for more information.

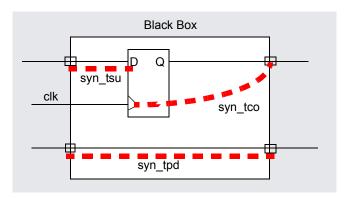

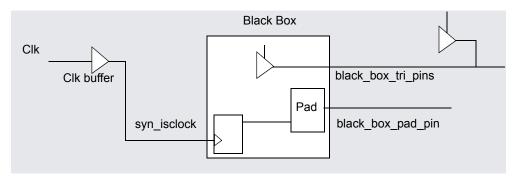

However, if you have black box timing constraints like syn\_tco, syn\_tpd, and syn\_tsu, you must enter them as directives in the source code. Unlike attributes, directives can only be added to the source code, not to constraint files. See Specifying Attributes and Directives, on page 142 for more information on adding directives to source code.

### **Using a Text Editor for Constraint Files (Legacy)**

You can use the Legacy SCOPE editor for the SDC constraint files created before release version G-2012.09. However, it is recommended that you translate your SDC files to FDC files to enable the latest version of the SCOPE editor and to utilize the enhanced timing constraint handling in the tool.

If you choose to use the legacy SCOPE editor, this section shows you how to manually create a Tcl constraint file. The software automatically creates this file if you use the legacy SCOPE editor to enter the constraints. The Tcl constraint file only contains general timing constraints. Black box constraints must be entered in the source code. For additional information, see When to Use Constraint Files over Source Code, on page 46.

- 1. Open a file for editing.

- Make sure you have closed the SCOPE window, or you could overwrite previous constraints.

- To create a new file, select File->New, and select the Constraint File (SCOPE) option. Type a name for the file and click OK.

- To edit an existing file, select File->Open, set the Files of Type filter to Constraint Files (sdc) and open the file you want.

- 2. Follow the syntax guidelines in Tcl Syntax Guidelines for Constraint Files, on page 48.

- 3. Enter the timing constraints you need. For the syntax, see the *Reference Manual*. If you have black box timing constraints, you must enter them in the source code.

- 4. You can also add vendor-specific attributes in the constraint file using define\_attribute. See Specifying Attributes in the Constraints File, on page 149 for more information.

- 5. Save the file.

- 6. Add the file to the project as described in Making Changes to a Project, on page 116, and run synthesis.

### **Tcl Syntax Guidelines for Constraint Files**

This section covers general guidelines for using Tcl for constraint files:

- Tcl is case-sensitive.

- For naming objects:

- The object name must match the name in the HDL code.

- Enclose instance and port names within curly braces {}.

- Do not use spaces in names.

- Use the dot (.) to separate hierarchical names.

- In Verilog modules, use the following syntax for instance, port, and net names:

#### v:cell[prefix:]objectName

Where *cell* is the name of the design entity, *prefix* is a prefix to identify objects with the same name, *objectName* is an instance path with the dot (.) separator. The prefix can be any of the following:

| Prefix (Lower-case) | Object                   |  |

|---------------------|--------------------------|--|

| i:                  | Instance names           |  |

| p:                  | Port names (entire port) |  |

| b:                  | Bit slice of a port      |  |

| n:                  | Net names                |  |

In VHDL modules, use the following syntax for instance, port, and net names in VHDL modules:

#### v:cell[.view] [prefix:]objectName

Where v: identifies it as a view object, lib is the name of the library, *cell* is the name of the design entity, *view* is a name for the architecture, *prefix* is a prefix to identify objects with the same name, and *objectName* is an instance path with the dot (.) separator. *View* is only needed if there is more than one architecture for the design. See the table above for the prefixes of objects.

• Name matching wildcards are \* (asterisk matches any number of characters) and ? (question mark matches a single character). These characters do not match dots used as hierarchy separators. For example, the following string identifies all bits of the statereg instance in the statemed module:

i:statemod.statereg[\*]

### **Checking Constraint Files**

You can check syntax and other pertinent information on your constraint files using the Constraint Check command. To generate a constraint report, do the following:

- 1. Create a constraint file and add it to your project.

- 2. Select Run->Constraint Check.

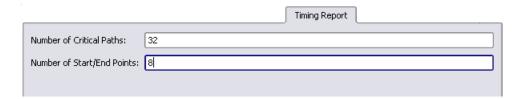

This command generates a report that checks the syntax and applicability of the timing constraints in the FPGA synthesis constraint files for your project. The report is written to the *projectName\_cck.rpt* file and lists the following information:

- Constraints that are not applied

- Constraints that are valid and applicable to the design

- Wildcard expansion on the constraints

- Constraints on objects that do not exist

For details on this report, see Constraint Checking Report, on page 440 of the *Reference Manual*.

### **Generating Constraint Files for Forward Annotation**

The tool automatically generates vendor-specific constraint files that you can use for forward-annotation. The synthesis constraints are mapped to the appropriate vendor constraints. You can control this process with some attributes as described in the following procedure.

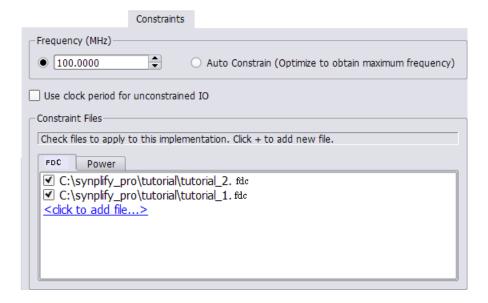

1. Set attributes to control forward annotation.

To forward-annotate timing constraints, set the clock period, max delay, input delay, output delay, multiple-cycle paths, and false paths in the SCOPE interface.

For details about these attributes, see the Reference Manual.

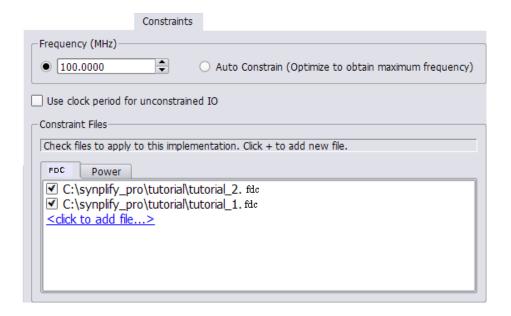

- 2. Select Project->Implementation Options, and check Write Vendor Constraints in the Implementation Results tab.

- 3. Click OK and run synthesis.

The software converts the synthesis set\_input\_delay, set\_output\_delay, set\_clock (including the set\_clock constraints generated by auto constraining), set\_multicycle\_path, set\_false\_path, set\_max\_delay, and global-frequency constraints into corresponding commands in the filename sdc.sdc file for Microsemi.

See the Reference Manual for details about forward annotation.

#### CHAPTER 4

# **Specifying Constraints**

This chapter describes how to specify constraints for your design. It covers the following:

- Using the SCOPE Editor, on page 52

- Specifying SCOPE Constraints, on page 57

- Specifying Timing Exceptions, on page 68

- Finding Objects with Tcl find and expand, on page 74

- Using Collections, on page 82

- Converting SDC to FDC, on page 92

- Using the SCOPE Editor (Legacy), on page 93

The following chapters discuss related information:

- Chapter 5, Constraints, for an overview of constraints

- Chapter 6, SCOPE Constraints Editor, for a description of the SCOPE editor

# Using the SCOPE Editor

The SCOPE (Synthesis Constraints OPtimization Environment®) presents a spreadsheet-like editor with a number of panels for entering and managing timing constraints and synthesis attributes. The SCOPE GUI is good for editing most constraints, but there are some constraints (like black box constraints) which can only be entered as directives in the source files. The SCOPE GUI also includes an advanced text editor that can help you edit constraints easily.

These constraints are saved to the FPGA Design Constraint (FDC) file. The FDC file contains *Synopsys SDC Standard* timing constraints (for example, create\_clock, set\_input\_delay, and set\_false\_path), along with the non-timing constraints (design constraints) (for example, define\_attribute, define\_scope\_collection, and define\_io\_standard). When working with these constraints, use the following processes:

- For existing designs, run the sdc2fdc script to translate legacy SDC constraints and create a constraint file that contains Synopsys SDC standard timing constraints and design constraints. For details about this script, see Converting SDC to FDC, on page 92.

- For new designs, use the SCOPE editor. See Creating Constraints in the SCOPE Editor, on page 52 for more information.

### Creating Constraints in the SCOPE Editor

The following procedure shows you how to use the SCOPE editor to create constraints for the FDC constraint file.

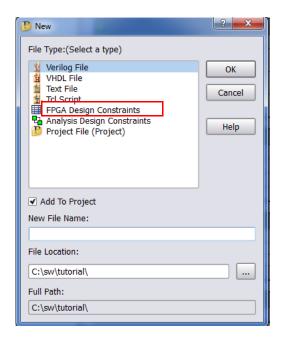

- 1. To create a new constraint file, follow these steps:

- Compile the design (F7).

- Open the SCOPE window by:

Clicking the SCOPE icon in the toolbar ( ).

This brings up the New Constraint File dialog box.

OR

Pressing Ctrl-n or selecting File -> New. This brings up the New dialog box.

- 2. To open an existing file, do one of the following:

- Double-click the file from the Project view.

- Press Ctrl-o or select File->Open. In the dialog box, set the kind of file you want to open to Constraint Files (SCOPE) (fdc), and double-click to select the file from the list.

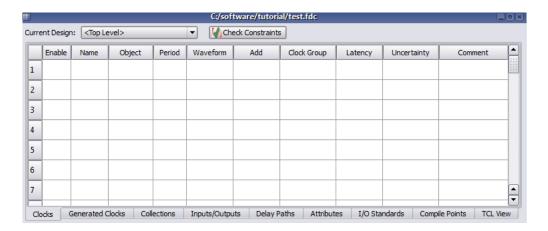

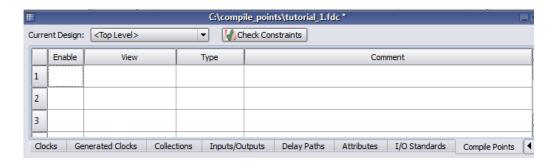

An empty SCOPE spreadsheet window opens. The tabs along the bottom of the SCOPE window list the different kinds of constraints you can add. For each kind of constraint, the columns contain specific data.

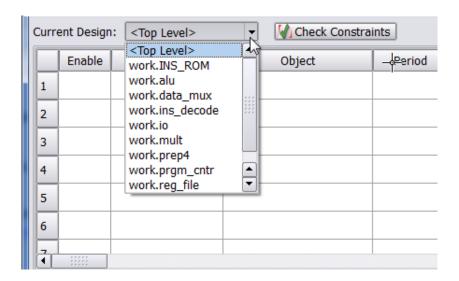

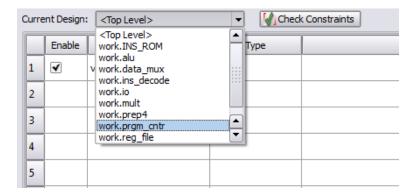

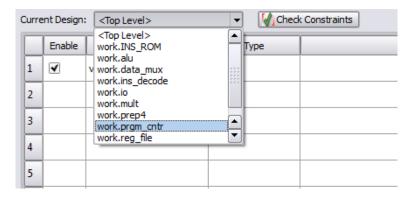

3. Select if you want to apply the constraint to the top-level or for modules from the Current Design option drop-down menu located at the top of the SCOPE editor.

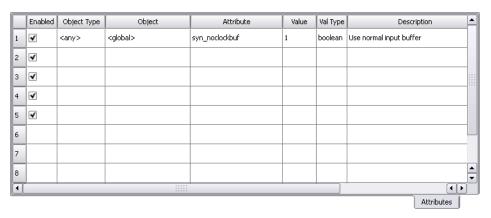

- 4. You can enter or edit the following types of constraints:

- Timing constraints—on the Clocks, Generated Clocks, Inputs/Outputs, Registers, or Delay Paths tab.

Design constraints—on the Collections, Attributes, I/O Standards, or Compile Points tab.

For details about these constraints, see Specifying SCOPE Constraints, on page 57.

For information about ways to enter constraints within the SCOPE editor, see Guidelines for Entering and Editing Constraints, on page 65.

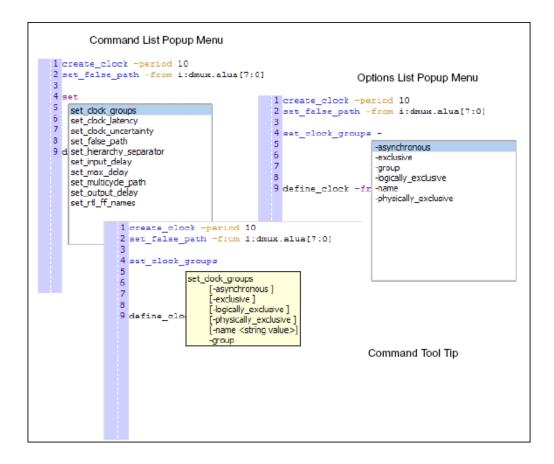

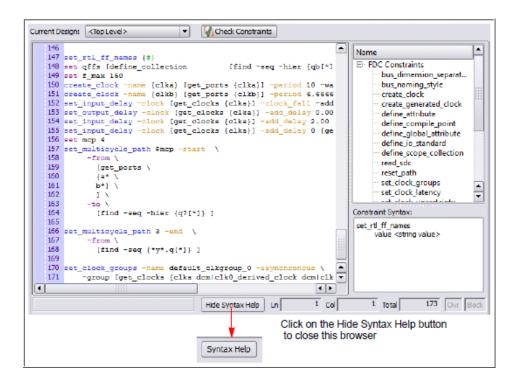

- 5. The free form constraint editor is located in the TCL View tab, which is the last tab in SCOPE. The text editor has a help window on the right-hand side. For more information about this text editor, see Using the TCL View of SCOPE GUI, on page 62.

- 6. Click on the Check Constraints button to run the constraint checker. The output provides information on how the constraints are interpreted by the tool.

All constraint information is saved in the same FPGA Design Constraint file (FDC) with clearly marked beginning and ending for each section. Do not manually modify these pre-defined SCOPE sections.

The following example shows the contents of an FDC file.

```

...........

# FDC constraints translated from Symplify Legacy Timing & Design Constraints

set_rtl_ff_names {#}

###==== BEGIN Header

# Synopsys, Inc. constraint file

# D:\bugs\timing 88\clk prior\scratch\top.fdc

# Written on Wed Jun 20 10:50:15 2012

# by Symplify Premier with Design Planner, G-2012.09 FDC Constraint Editor

# Custom constraint commands may be added outside of the SCOPE tab sections bounded with BEGIN/END.

# These sections are generated from SCOPE spreadsheet tabs.

###==== END Header

###==== BEGIN Clocks - (Populated from tab in SCOPE, do not edit)

create_clock -name {clka} {p:clka} -period 10 -waveform {0 5.0}

create clock -name {clkb} {p:clkb} -period 6.667 -waveform {0 3.3335}

set_clock_groups -derive -name default_clkgroup_0 -asynchronous -group [get_clocks {clka}]

set_clock_groups -derive -name default_clkgroup_1 -asynchronous -group [get_clocks {clkb}]

###==== END Clocks

###==== BEGIN "Generated Clocks" - (Populated from tab in SCOPE, do not edit)

###==== END "Generated Clocks"

###==== BEGIN Collections - (Populated from tab in SCOPE, do not edit)

define scope collection all inputs fdc {find -port * -filter @direction==input}

define_scope_collection all_outputs_fdc {find -port * -filter @direction==output} define_scope_collection all_clocks_fdc {find -hier -clock *}

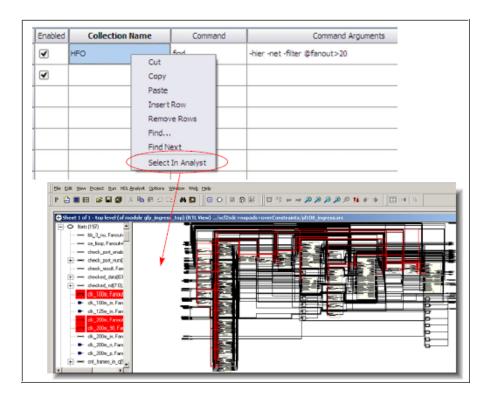

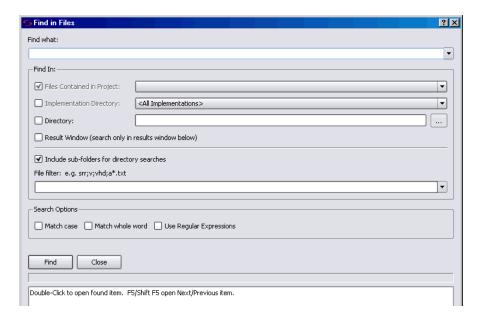

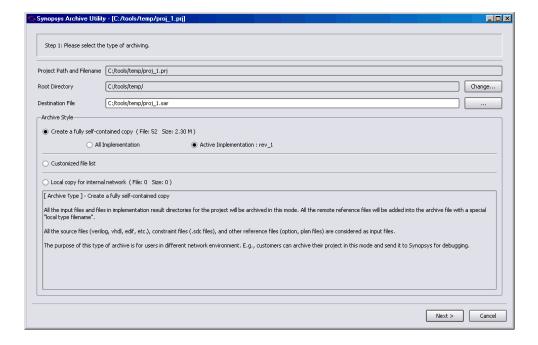

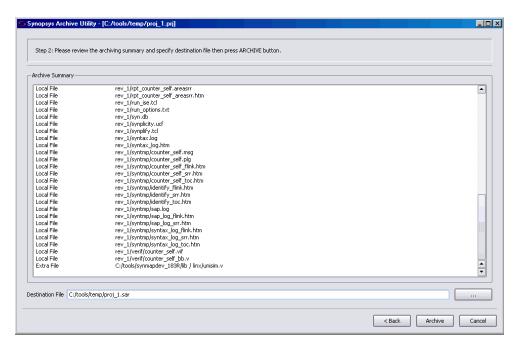

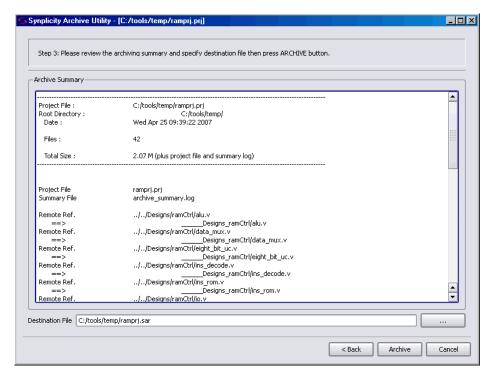

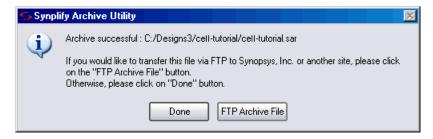

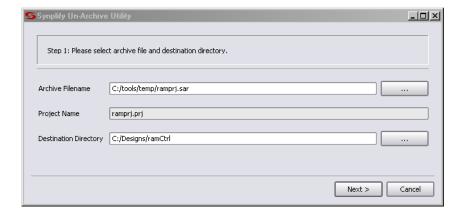

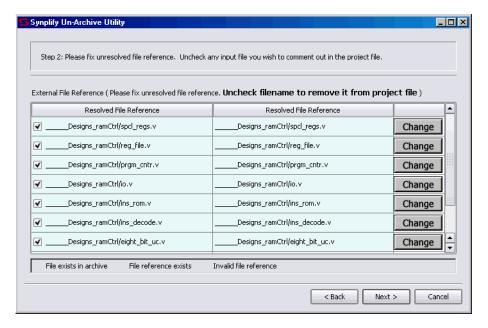

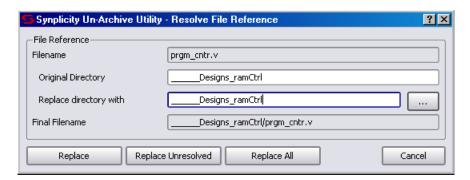

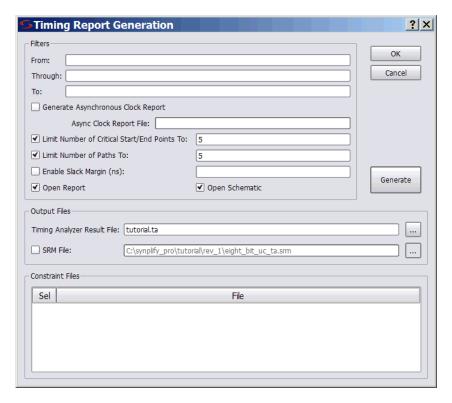

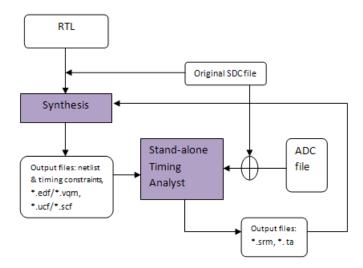

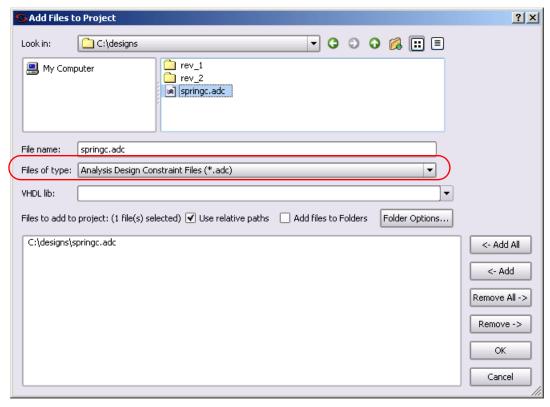

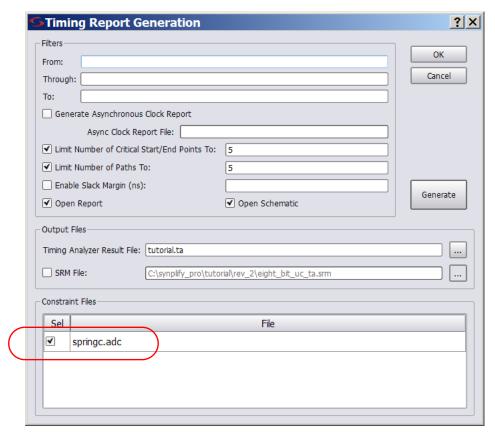

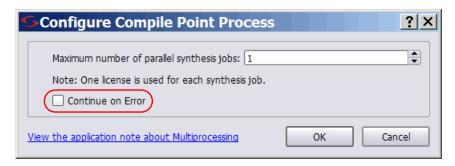

define_scope_collection all_registers_fdc {find -hier -seq *}