## UG0450

User Guide SmartFusion2 SoC and IGLOO2 FPGA System Controller

а 🔨 Міскоснір сотралу

Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

## Contents

| 1.2       Revision 5.0       1         1.3       Revision 4.0       1         1.4       Revision 3.0       1         1.5       Revision 2.0       1         1.6       Revision 1.0       1         1.7       Revision 0.0       2         2       System Controller 3       2         2.1       Introduction       3         2.2       Functional Description       4         2.2.1       Subsystems       5         2.2.2       Interfaces       5         2.2.3       System IP Interface (SII) Master       5         2.2.4       Communication Block (COMM_BLK)       5         2.2.5       Oscillator Control       6         2.2.6       Random Number Generator       6         2.2.7       Cryptographic Services       6         2.2.8       JTAG       8         2.2.10       Dedicated Programming SPI Peripheral       10         2.2.11       Device Reset       10         2.2.12       USI Interface       10         2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       11                                                                                                                                                                         | 1 |        |           | ory             |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|-----------|-----------------|-----|

| 1.3       Revision 4.0       1         1.4       Revision 3.0       1         1.5       Revision 1.0       1         1.6       Revision 1.0       1         1.7       Revision 0.0       2         2       System Controller 3       2         2.1       Introduction       3         2.2.1       Subsystems       5         2.2.2       Interfaces       5         2.2.3       System IP Interface (SII) Master       5         2.2.4       Communication Block (COMM BLK)       5         2.2.5       Oscillator Control       6         2.2.6       Communication Block (COMM BLK)       5         2.2.6       Random Number Generator       6         2.2.7       Cryptographic Services       6         2.2.8       JTAG       6         2.2.9       User JTAG       6         2.2.10       Dedicated Programming SPI Peripheral       10         2.2.11       Device Reset       10         2.2.12       User Infaces       11         2.2.13       System Controller Suspend Mode       11         2.2.14       System Controller Suspend Mode       11         3.1       <                                                                                                                                 |   | 1.1    |           |                 |     |

| 1.4       Revision 3.0       1         1.5       Revision 2.0       1         1.6       Revision 1.0       1         1.7       Revision 0.0       2         2       System Controller 3       2         2.1       Introduction       3         2.2.1       Subsystems       5         2.2.1       Subsystems       5         2.2.1       Subsystems       5         2.2.2       Interfaces       5         2.2.3       System IP Interface (SII) Master       5         2.2.4       Communication Block (COMM_BLK)       5         2.2.5       Oscillator Control       6         2.2.6       Random Number Generator       6         2.2.7       Cryptographic Services       6         2.2.9       User JTAG       6         2.2.10       Dedicated Programming SPI Peripheral       10         2.2.11       Device Requirements       11         2.2.12       User ITAG       6         2.2.2       User Itace       10         2.2.11       Device Requirements       11         2.2.12       User Requirements       11         2.2.13       Lick Requirements                                                                                                                                                |   |        |           |                 |     |

| 1.5       Revision 2.0       1         1.6       Revision 1.0       1         1.7       Revision 0.0       2         2       System Controller 3       2         2.1       Introduction       3         2.2       Functional Description       4         2.2.1       Subsystems       5         2.2.2       System Pl Interface (SII) Master       5         2.2.3       System Pl Interface (SII) Master       5         2.2.4       Communication Block (COMM_BLK)       5         2.2.5       Oscillator Control       6         2.2.6       Random Number Generator       6         2.2.7       Cryptographic Services       6         2.2.8       JTAG       6         2.2.9       User JTAG       8         2.2.10       Dedicated Programming SPI Peripheral       10         2.2.11       Device Reset       10         2.2.12       USI Interface       10         2.2.13       Clock Requirements       11         2.14       System Controller Suspend Mode       11         3.1       Introduction       14         3.2       Device and Design Information Services       18                                                                                                                          |   |        |           |                 |     |

| 1.6       Revision 1.0       1         1.7       Revision 0.0       2         2       System Controller 3       2         2.1       Introduction       3         2.2       Functional Description       4         2.2.1       Subsystems       5         2.2.2       Interfaces       5         2.2.3       System IP Interface (SII) Master       5         2.2.4       Communication Block (COMM_BLK)       5         2.2.5       Oscillator Control       6         2.2.6       Random Number Generator       6         2.2.7       Cryptographic Services       6         2.2.8       JTAG       6         2.2.9       User JTAG       8         2.10       Decicated Programming SPI Peripheral       10         2.2.11       Device Reset       10         2.2.12       Usl Interface       10         2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       14         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18 <td< td=""><td></td><td></td><td></td><td></td><td></td></td<>                                                                     |   |        |           |                 |     |

| 1.7       Revision 0.0       2         2       System Controller 3         2.1       Introduction       3         2.2       Functional Description       4         2.2.1       Subsystems       5         2.2.2       Interfaces       5         2.2.3       System IP Interface (SII) Master       5         2.2.4       Communication Block (COMM ELK)       5         2.2.5       Oscillator Control       6         2.2.6       Random Number Generator       6         2.2.7       Cryptographic Services       6         2.2.9       User JTAG       6         2.2.9       User JTAG       8         2.2.10       Dedicated Programming SPI Peripheral       10         2.2.11       Device Reset       10         2.2.12       USI Interface       10         2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       11         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Services       18         3.2.1       Services       19         3.2.2       US                                                                                                                            |   | -      |           |                 |     |

| 2         System Controller 3           2.1         Introduction         3           2.2         Functional Description         4           2.2.1         Subsystems         5           2.2.2         Interfaces         5           2.2.3         System IP Interface (SII) Master         5           2.2.4         Communication Block (COMM_BLK)         5           2.2.5         Oscillator Control         6           2.2.6         Random Number Generator         6           2.2.7         Cryptographic Services         6           2.2.9         User JTAG         6           2.2.10         Dedicated Programming SPI Peripheral         10           2.2.11         Device Reset         10           2.2.13         Clock Requirements         11           2.2.14         System Controller Suspend Mode         11           3.1         Introduction         14           3.2         Device and Design Information Services         18           3.2.1         Service         18           3.2.2         USERCODE Service         18           3.2.1         Services         21           3.2.1         Istreaction Services         22 <td></td> <td></td> <td></td> <td></td> <td></td> |   |        |           |                 |     |

| 2.1       Introduction       3         2.2       Functional Description       4         2.2.1       Subsystems       5         2.2.2       Interfaces       5         2.2.3       System IP Interface (SII) Master       5         2.2.4       Communication Block (COMM_BLK)       5         2.2.5       Oscillator Control       6         2.2.6       Random Number Generator       6         2.2.7       Cryptographic Services       6         2.2.8       JTAG       6         2.2.9       User JTAG       8         2.10       Dedicated Programming SPI Peripheral       10         2.2.11       Device Reset       10         2.2.12       USI Interface       10         2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       11         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       18         3.2.3       Device Certificate Service       19         3.4       User Design Version Service       2                                                                                                  |   | 1.7    | Revision  | 10.0            | . Z |

| 2.2       Functional Description       4         2.2.1       Subsystems       5         2.2.2       Interfaces       5         2.2.3       System IP Interface (SII) Master       5         2.2.4       Communication Block (COMM_BLK)       5         2.2.5       Oscillator Control       6         2.2.6       Random Number Generator       6         2.2.7       Cryptographic Services       6         2.2.8       JTAG       6         2.2.9       User JTAG       6         2.2.11       Device Reset       10         2.2.12       USI Interface       10         2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       11         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Setail Number Service       18         3.2.2       USERCODE Service       18         3.2.3       Device Certificate Service       19         3.3.4       Flash*Freeze Service       19         3.4       Styper Design Version Service       20         3.4       Cryptographic Services       21<                                                                                                  | 2 | Syster | n Cont    | roller 3        |     |

| 2.2.1       Subsystems       5         2.2.2       Interfaces       5         2.2.3       System IP Interface (SII) Master       5         2.2.4       Communication Block (COMM_BLK)       5         2.2.5       Oscillator Control       6         2.2.6       Random Number Generator       6         2.2.6       Random Number Generator       6         2.2.7       Cryptographic Services       6         2.2.8       JTAG       6         2.2.9       User JTAG       6         2.2.10       Dedicated Programming SPI Peripheral       10         2.2.11       Device Reset       10         2.2.12       USI Interface       10         2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       11         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       19         3.3.4       User Design Version Service       20         3.4       Acroptographic Services       21         3.4.1       AES Services                                                                                                     |   |        |           |                 |     |

| 2.2.2       Interfaces       5         2.2.3       System IP Interface (SII) Master       5         2.2.4       Communication Block (COMM_BLK)       5         2.2.5       Oscillator Control       6         2.2.6       Random Number Generator       6         2.2.7       Cryptographic Services       6         2.2.8       JTAG       6         2.2.9       User JTAG       6         2.2.10       Dedicated Programming SPI Peripheral       10         2.2.11       Device Reset       10         2.2.12       USI Interface       10         2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       11         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.1       Serial Number Service       19         3.2.2       USERCODE Service       20         3.3       Flash*Freeze Services       21         3.4.1       AES Services       21         3.5       DAVice Services       23         3.6       Starge Services       21                                                                                                         |   | 2.2    |           |                 |     |

| 2.2.3       System IP Interface (SII) Master       5         2.2.4       Communication Block (COMM_BLK)       5         2.2.5       Oscillator Control       6         2.2.6       Random Number Generator       6         2.2.7       Cryptographic Services       6         2.2.8       JTAG       6         2.2.9       User JTAG       6         2.2.10       Dedicated Programming SPI Peripheral       10         2.2.11       Device Reset       10         2.2.12       USI Interface       10         2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       11         2.2.14       System Services       14         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       19         3.2.3       Device Certificate Service       20         3.4       User Design Version Services       21         3.5       DPA-Resistant Key-Tree Services       23         3.5       DPA-Resistant Key-Tree Services       25         3.5.1 </td <td></td> <td></td> <td></td> <td>•</td> <td></td>                          |   |        |           | •               |     |

| 2.2.4       Communication Block (COMM_BLK)       5         2.2.5       Oscillator Control       6         2.2.6       Random Number Generator       6         2.2.7       Cryptographic Services       6         2.2.8       JTAG       6         2.2.9       User JTAG       6         2.2.9       User JTAG       8         2.2.10       Dedicated Programming SPI Peripheral       10         2.2.11       Device Reset       10         2.2.12       USI Interface       10         2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       11         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       19         3.2.4       User Design Version Service       19         3.3       Flash*Freeze Service       20         3.4       Cryptographic Services       21         3.4.2       SHA-256 Services       22         3.5       DPA-Resistant Key-Tree Services       23         3.5.1       Key-Tree Cryptographic Se                                                                                         |   |        |           |                 |     |

| 22.6       Random Number Generator       6         22.7       Cryptographic Services       6         22.8       JTAG       6         22.9       User JTAG       8         22.10       Dedicated Programming SPI Peripheral       10         22.11       Device Reset       10         22.12       USI Interface       10         22.13       Clock Requirements       11         22.14       System Controller Suspend Mode       11         3       System Services       14         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       18         3.2.3       Device Certificate Service       19         3.3       Flash*Freeze Service       20         3.4       Cryptographic Services       21         3.4.1       AES Services       21         3.5       DPA-Resistant Key-Tree Service       25         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6.1       ECC Point Mul                                                                                         |   |        |           | ,               |     |

| 2.2.7       Cryptographic Services       6         2.2.8       JTAG       6         2.2.9       User JTAG       8         2.2.10       Dedicated Programming SPI Peripheral       10         2.2.11       Device Reset       10         2.2.12       USI Interface       10         2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       11         3       System Services       14         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.1       Serial Number Service       18         3.2.1       Serial Number Service       19         3.2.1       Serial Perion Service       19         3.2.3       Device Certificate Service       19         3.3       Flash*Freeze Service       20         3.4       Cryptographic Services       21         3.5       DPA-Resistant Key-Tree Services       22         3.5.1       Key-Tree Services       25         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Res                                                                                         |   |        | -         |                 |     |

| 2.2.8       JTAG       6         2.2.9       User JTAG       8         2.2.10       Dedicated Programming SPI Peripheral       10         2.2.11       Device Reset       10         2.2.12       USI Interface       10         2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       11         3       System Services       14         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       18         3.2.3       Device Certificate Service       19         3.2.4       User Design Version Service       19         3.3       Flash*Freeze Service       20         3.4       Cryptographic Services       21         3.4.1       AES Services       23         3.5       DPA-Resistant Key-Tree Services       23         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6       Elliptic Curve Cryptographic Service       27         3.6.2<                                                                                |   |        |           |                 |     |

| 22.9       User JTAG       8         22.10       Dedicated Programming SPI Peripheral       10         22.11       Device Reset       10         22.12       USI Interface       10         22.13       Clock Requirements       11         22.14       System Controller Suspend Mode       11         3       System Services       14         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       18         3.2.3       Device Certificate Service       19         3.2.4       User Design Version Service       19         3.3       Flash*Freeze Services       21         3.4.1       AES Services       21         3.4.2       SHA-256 Services       23         3.5       DPA-Resistant Key-Tree Services       25         3.5.1       Key-Tree Cryptographic Service       27         3.6       Elliptic Curve Cryptography Services       27         3.6.1       ECC Point Multiplication Service       27         3.6.2                                                                                |   |        |           |                 |     |

| 22.10       Dedicated Programming SPI Peripheral       10         22.11       Device Reset       10         22.12       USI Interface       10         22.13       Clock Requirements       11         22.14       System Controller Suspend Mode       11         3       System Services       14         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       18         3.2.3       Device Certificate Service       19         3.3       Flash*Freeze Service       19         3.4       Cryptographic Services       20         3.4       Cryptographic Services       21         3.4.1       AES Services       21         3.4.2       SHA-256 Services       23         3.5       DPA-Resistant Key-Tree Services       25         3.5.1       Key-Tree Cryptographic Service       27         3.6       Elliptic Curve Cryptography Services       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       Challenge-Response Cryptographic Service       28                                                                      |   |        | -         |                 |     |

| 2.2.12       USI Interface       10         2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       11         3       System Services       14         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       18         3.2.3       Device crificate Service       19         3.3       Flash*Freeze Service       19         3.4       User Design Version Services       20         3.4       Cryptographic Services       21         3.4.1       AES Services       23         3.5       DPA-Resistant Key-Tree Services       23         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6       Elliptic Curve Cryptography Services       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Multiplication Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       3                                                      |   |        | -         |                 |     |

| 2.2.13       Clock Requirements       11         2.2.14       System Controller Suspend Mode       11         3       System Services       14         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       18         3.2.3       Device Certificate Service       19         3.2.4       User Design Version Service       19         3.3       Flash*Freeze Service       20         3.4       AES Services       21         3.4.1       AES Services       21         3.4.2       SHA-256 Services       23         3.5       DPA-Resistant Key-Tree Service       25         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Addition Service       28         3.6.3       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32                                                           |   |        |           | Device Reset    | 10  |

| 2.2.14       System Controller Suspend Mode       11         3       System Services       14         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       18         3.2.3       Device Certificate Service       19         3.2.4       User Design Version Service       19         3.3       Flash*Freeze Service       20         3.4       AES Pervices       21         3.4.1       AES Services       21         3.4.2       SHA-256 Services       23         3.5       DPA-Resistant Key-Tree Service       26         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6       Elliptic Curve Cryptography Services       27         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36                                                            |   |        |           |                 |     |

| 3 System Services       14         3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       18         3.2.3       Device Certificate Service       19         3.2.4       User Design Version Service       19         3.3       Flash*Freeze Service       20         3.4       Cryptographic Services       21         3.4.1       AES Services       21         3.4.2       SHA-256 Services       23         3.5       DPA-Resistant Key-Tree Services       23         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6.1       ECC Point Multiplication Service       27         3.6.2       ECC Point Addition Service       28         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.3       Key Generation and Enrollment Services       32         3.7.3       Key Genenstruction       36                                                              |   |        | -         |                 |     |

| 3.1       Introduction       14         3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       18         3.2.3       Device Certificate Service       19         3.2.4       User Design Version Service       19         3.3       Flash*Freeze Service       20         3.4       Cryptographic Services       21         3.4.1       AES Services       21         3.4.2       SHA-256 Services       23         3.5       DPA-Resistant Key-Tree Services       23         3.5       DPA-Resistant Key-Tree Services       26         3.5.1       Key-Tree Cryptographic Service       27         3.6.1       ECC Point Multiplication Service       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36         3.7.4       User-Enrolled SRAM-PUF Keys for Desi                                             | _ |        |           |                 |     |

| 3.2       Device and Design Information Services       18         3.2.1       Serial Number Service       18         3.2.2       USERCODE Service       18         3.2.3       Device Certificate Service       19         3.2.4       User Design Version Service       19         3.3       Flash*Freeze Service       20         3.4       User Design Version Service       20         3.4       Cryptographic Services       21         3.4.1       AES Services       21         3.4.2       SHA-256 Services       23         3.5       DPA-Resistant Key-Tree Services       25         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6       Elliptic Curve Cryptography Services       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36         3.7.4       User-Enr                                             | 3 | Syster |           |                 |     |

| 3.2.1Serial Number Service183.2.2USERCODE Service183.2.3Device Certificate Service193.2.4User Design Version Service193.3Flash*Freeze Service203.4Cryptographic Services213.4.1AES Services213.4.2SHA-256 Services233.5DPA-Resistant Key-Tree Services233.5DPA-Resistant Key-Tree Services263.5.1Key-Tree Cryptographic Service263.5.2Challenge-Response Cryptographic Service273.6Elliptic Curve Cryptography Services273.6.1ECC Point Multiplication Service283.6.2ECC Point Addition Service293.7SRAM-PUF Services303.7.1Create User Activation Code303.7.2Key Generation and Enrollment Services323.7.3Key Reconstruction363.7.4User-Enrolled SRAM-PUF Keys for Design Security37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |        |           |                 |     |

| 3.2.2       USERCODE Service       18         3.2.3       Device Certificate Service       19         3.2.4       User Design Version Service       19         3.3       Flash*Freeze Service       20         3.4       Cryptographic Services       21         3.4.1       AES Services       21         3.4.2       SHA-256 Services       23         3.5       DPA-Resistant Key-Tree Services       25         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6       Elliptic Curve Cryptography Services       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36         3.7.4       User-Enrolled SRAM-PUF Keys for Design Security       37                                                                                                                                                                         |   | 3.2    |           |                 |     |

| 3.2.3       Device Certificate Service       19         3.2.4       User Design Version Service       19         3.3       Flash*Freeze Service       20         3.4       Cryptographic Services       21         3.4.1       AES Services       21         3.4.2       SHA-256 Services       23         3.5       DPA-Resistant Key-Tree Services       23         3.5       DPA-Resistant Key-Tree Services       25         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6       Elliptic Curve Cryptography Services       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36         3.7.4       User-Enrolled SRAM-PUF Keys for Design Security       37                                                                                                                                                            |   |        | • • • • • |                 |     |

| 3.2.4User Design Version Service193.3Flash*Freeze Service203.4Cryptographic Services213.4.1AES Services213.4.2SHA-256 Services233.5DPA-Resistant Key-Tree Services253.5.1Key-Tree Cryptographic Service263.5.2Challenge-Response Cryptographic Service273.6Elliptic Curve Cryptography Services273.6.1ECC Point Multiplication Service283.6.2ECC Point Addition Service293.7SRAM-PUF Services303.7.1Create User Activation Code303.7.2Key Generation and Enrollment Services323.7.3Key Reconstruction363.7.4User-Enrolled SRAM-PUF Keys for Design Security37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |        |           |                 |     |

| 3.4       Cryptographic Services       21         3.4.1       AES Services       21         3.4.2       SHA-256 Services       23         3.5       DPA-Resistant Key-Tree Services       25         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6       Elliptic Curve Cryptography Services       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36         3.7.4       User-Enrolled SRAM-PUF Keys for Design Security       37                                                                                                                                                                                                                                                                                                                                                                                        |   |        |           |                 |     |

| 3.4.1       AES Services       21         3.4.2       SHA-256 Services       23         3.5       DPA-Resistant Key-Tree Services       25         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6       Elliptic Curve Cryptography Services       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36         3.7.4       User-Enrolled SRAM-PUF Keys for Design Security       37                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 3.3    | Flash*Fr  | reeze Service   | 20  |

| 3.4.2       SHA-256 Services       23         3.5       DPA-Resistant Key-Tree Services       25         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6       Elliptic Curve Cryptography Services       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36         3.7.4       User-Enrolled SRAM-PUF Keys for Design Security       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 3.4    | Cryptog   | raphic Services | 21  |

| 3.5       DPA-Resistant Key-Tree Services       25         3.5.1       Key-Tree Cryptographic Service       26         3.5.2       Challenge-Response Cryptographic Service       27         3.6       Elliptic Curve Cryptography Services       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36         3.7.4       User-Enrolled SRAM-PUF Keys for Design Security       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |        | •••••     |                 |     |

| 3.5.1Key-Tree Cryptographic Service263.5.2Challenge-Response Cryptographic Service273.6Elliptic Curve Cryptography Services273.6.1ECC Point Multiplication Service283.6.2ECC Point Addition Service293.7SRAM-PUF Services303.7.1Create User Activation Code303.7.2Key Generation and Enrollment Services323.7.3Key Reconstruction363.7.4User-Enrolled SRAM-PUF Keys for Design Security37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |        |           |                 |     |

| 3.5.2       Challenge-Response Cryptographic Service       27         3.6       Elliptic Curve Cryptography Services       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36         3.7.4       User-Enrolled SRAM-PUF Keys for Design Security       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 3.5    |           |                 |     |

| 3.6       Elliptic Curve Cryptography Services       27         3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36         3.7.4       User-Enrolled SRAM-PUF Keys for Design Security       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |        |           |                 |     |

| 3.6.1       ECC Point Multiplication Service       28         3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36         3.7.4       User-Enrolled SRAM-PUF Keys for Design Security       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 3.6    |           |                 |     |

| 3.6.2       ECC Point Addition Service       29         3.7       SRAM-PUF Services       30         3.7.1       Create User Activation Code       30         3.7.2       Key Generation and Enrollment Services       32         3.7.3       Key Reconstruction       36         3.7.4       User-Enrolled SRAM-PUF Keys for Design Security       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 0.0    |           |                 |     |

| 3.7.1Create User Activation Code303.7.2Key Generation and Enrollment Services323.7.3Key Reconstruction363.7.4User-Enrolled SRAM-PUF Keys for Design Security37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |        | 3.6.2     |                 |     |

| 3.7.2Key Generation and Enrollment Services323.7.3Key Reconstruction363.7.4User-Enrolled SRAM-PUF Keys for Design Security37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 3.7    |           |                 |     |

| 3.7.3       Key Reconstruction       36         3.7.4       User-Enrolled SRAM-PUF Keys for Design Security       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |        | -         |                 |     |

| 3.7.4 User-Enrolled SRAM-PUF Keys for Design Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |        |           |                 |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |        |           |                 |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |        | -         |                 |     |

|      |          | -                                                   |      |

|------|----------|-----------------------------------------------------|------|

| 3.8  | Non-De   | terministic Random Bit Generator (NRBG) Services    |      |

|      | 3.8.1    | Self Test Service                                   | . 41 |

|      | 3.8.2    | Instantiate Service                                 | . 41 |

|      | 3.8.3    | Generate Service                                    | . 42 |

|      | 3.8.4    | Uninstantiate Service                               | . 44 |

|      | 3.8.5    | Reset Service                                       | . 44 |

| 3.9  | Zeroizat | ion Service                                         | . 44 |

|      | 3.9.1    | FPGA Fabric Configuration NVM                       | . 45 |

|      | 3.9.2    | User Security Keys and Settings                     | . 45 |

|      | 3.9.3    | Factory Security Keys and Configuration Settings    | . 45 |

|      | 3.9.4    | System Controller Memory                            | . 45 |

|      | 3.9.5    | Digital Data Path                                   | . 45 |

|      | 3.9.6    | Fabric Registers                                    | . 45 |

|      | 3.9.7    | Fabric SRAM                                         | . 45 |

|      | 3.9.8    | HPMS SRAM                                           | . 45 |

|      | 3.9.9    | eNVM Memory Array and eNVM Registers                | . 45 |

| 3.10 | Program  | ming Service                                        | . 46 |

|      | 3.10.1   | IAP Service                                         | . 47 |

|      | 3.10.2   | ISP Service                                         | . 48 |

| 3.11 | NVM Da   | ata Integrity Check Service                         | . 49 |

| 3.12 | Unrecog  | nized Command Response                              | . 50 |

| 3.13 | Asvnchr  | onous Messages                                      | . 50 |

|      | 3.13.1   | -                                                   |      |

| 3.14 | How to   | Use System Services in SmartFusion2                 |      |

|      | 3.14.1   | Use Model 1: Fetching Device and Design Information |      |

| 3.15 | How to   | Use System Services in IGLOO2                       | . 55 |

|      | 3.15.1   | Configuring System Services                         |      |

|      | 3.15.2   | Fetching Device and Design information              |      |

|      | 3.15.3   | Related Applications                                |      |

|      |          |                                                     |      |

## **Figures**

| Figure 1  | SmartFusion2 - System Controller Interfacing with AHB Bus Matrix             | 3  |

|-----------|------------------------------------------------------------------------------|----|

| Figure 2  | IGLOO2 - System Controller Interfacing with AHB Bus Matrix                   |    |

| Figure 3  | SmartFusion2 - Interfacing of the System Controller with MSS and FPGA Fabric | 4  |

| Figure 4  | IGLOO2 - Interfacing of the System Controller with HPMS and FPGA Fabric      | 5  |

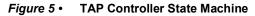

| Figure 5  | TAP Controller State Machine                                                 |    |

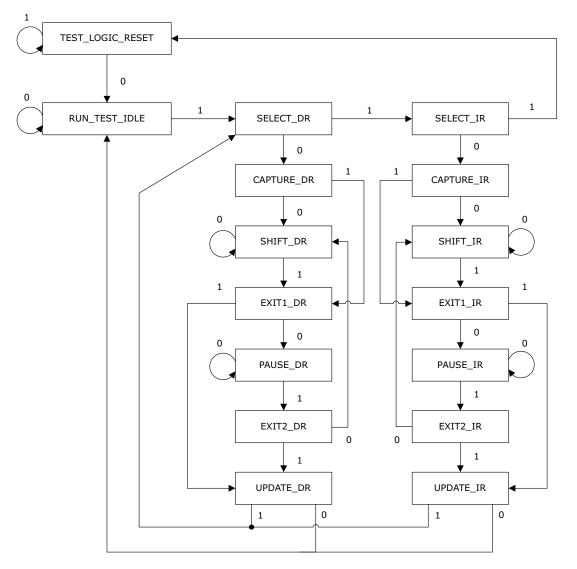

| Figure 6  | UJTAG Macro                                                                  |    |

| Figure 7  | UJTAG Usage Example in Test and Debug Applications                           | 10 |

| Figure 8  | FLASH_FREEZE Macro                                                           | 11 |

| Figure 9  | Enabling System Controller Suspended Mode in New Project Window              | 12 |

| Figure 10 | Enabling System Services Suspend mode in Project Settings Window             | 13 |

| Figure 11 | System Services Sample Projects                                              | 51 |

| Figure 12 | Functional Block Diagram for Accessing System Services                       |    |

| Figure 13 | System Builder Window                                                        |    |

| Figure 14 | System Builder - Device Features Tab                                         | 57 |

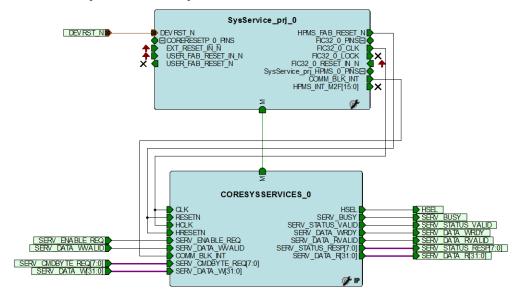

| Figure 15 | CoreSysServices IP to COMM_BLK Path                                          | 58 |

| Figure 16 | System Builder - Clock Tab                                                   | 58 |

| Figure 17 | System Builder - Memory Map Tab                                              | 59 |

| Figure 18 | SmartDesign Connections                                                      |    |

| Figure 19 | CORESYSSERVICES_0 Configuration                                              |    |

| Figure 20 | HPMS Subsystem and CoreSysServices IP Connections                            | 61 |

## **Tables**

| Table 1              | Boundary Scan Opcodes                               | 8  |

|----------------------|-----------------------------------------------------|----|

| Table 2              | UJTAG Port Description                              |    |

| Table 3              | SmartFusion2 and IGLOO2 System Services             |    |

| Table 4              | Device and Design Information Services Status       |    |

| Table 5              | Serial Number Service Request                       |    |

| Table 6              | Serial Number Service Response                      |    |

| Table 7              | USERCODE Service Request                            |    |

| Table 8              | USERCODE Service Response                           |    |

| Table 9              | Device Certificate Service Request                  |    |

| Table 10             | Device Certificate Service Response                 |    |

| Table 11             | Design Version Service Request                      |    |

| Table 12             | Design Version Service Response                     |    |

| Table 13             | Flash*Freeze Request                                |    |

| Table 14             | FFOPTIONS                                           |    |

| Table 15             | Flash*Freeze Service Response                       |    |

| Table 16             | Flash*Freeze Service Status                         |    |

| Table 17             | Cryptographic Services Status Codes                 |    |

| Table 18             | 128-bit AES Service Request                         |    |

| Table 19             | AES128DATA Descriptor                               |    |

| Table 20             | MODE Parameter                                      |    |

| Table 21             | OPMODE Parameter                                    |    |

| Table 22             | 128-bit AES Service Response                        |    |

| Table 22             | 256-bit AES Service Request                         |    |

| Table 23             | AES256DATA Descriptor                               |    |

| Table 25             | 256-bit AES Service Response                        |    |

| Table 25             | SHA-256 Service Request                             |    |

| Table 20<br>Table 27 | SHA256DATA Structure                                |    |

| Table 27             | SHA-256 Service Response                            |    |

| -                    |                                                     |    |

| Table 29             | HMAC Service Request                                |    |

| Table 30             | HMACDATA Structure                                  |    |

| Table 31             | HMAC Service Response                               |    |

| Table 32             | DPA-Resistant Key-Tree Services Status Codes        |    |

| Table 33             | Key-Tree Service Request                            |    |

| Table 34             | KEYTREEDATA Structure                               |    |

| Table 35             | KeyTree Service Response                            |    |

| Table 36             | Challenge-Response Service Request                  |    |

| Table 37             | CHRESP Structure                                    |    |

| Table 38             | Challenge-Response Service Response                 |    |

| Table 39             | Challenge-Response Service Response                 |    |

| Table 40             | Elliptic Curve Point Multiplication Service Request |    |

| Table 41             |                                                     |    |

| Table 42             |                                                     |    |

| Table 43             | Elliptic Curve Point Addition Service Request       |    |

| Table 44             | ECCPADD Structure                                   |    |

| Table 45             | Elliptic Curve Point Addition Service Response      |    |

| Table 46             | PUFUSERAC Service Request                           |    |

| Table 47             | PUFUSERAC Structure                                 |    |

| Table 48             | Elliptic Curve Point Addition Service Response      |    |

| Table 49             | PUFUSERAC Status                                    |    |

| Table 50             | PUFUSERKC Service Request                           |    |

| Table 51             | PUFUSERKC Service Request                           |    |

| Table 52             | PUFUSERACKCEXPORT Memory Layout                     |    |

| Table 53             | PUFUSERACKCIMPORT                                   |    |

| Table 54             | PUFUSERKC Service Response                          | 35 |

| Table 55  | PUFUSERKC Service Response                                      | 35 |

|-----------|-----------------------------------------------------------------|----|

| Table 56  | PUFUSERKEY Service Request                                      | 36 |

| Table 57  | PUFUSERKEY Structure                                            | 36 |

| Table 58  | PUFUSERKC Service Response                                      | 37 |

| Table 59  | USERPUFKEY Status                                               | 37 |

| Table 60  | PUFPUBLICKEY Service Request                                    | 37 |

| Table 61  | PUFPUBLICKEY Structure                                          | 38 |

| Table 62  | PUFPUBLICKEY Structure                                          | 38 |

| Table 63  | USERPUFKEY Status                                               | 38 |

| Table 64  | PUFPUBLICKEY Structure                                          | 38 |

| Table 65  | PUFPUBLICKEY Structure                                          | 39 |

| Table 66  | USERPUFKEY Status                                               | 39 |

| Table 67  | PUFSEED Status                                                  | 39 |

| Table 68  | NRBG Service Response Status Codes                              | 40 |

| Table 69  | DRBG Self Test Request                                          |    |

| Table 70  | DRBG Self Test Response                                         |    |

| Table 71  | DRBG Instantiate Request                                        | 41 |

| Table 72  | DRBGINSTANTIATE Structure                                       | 42 |

| Table 73  | DRBG Instantiate Service Response                               |    |

| Table 74  | DRBG Generate Request                                           |    |

| Table 75  | DRBGGENERATE Structure                                          |    |

| Table 76  | DRBG Reseed Request                                             |    |

| Table 77  | DRBGRESEED Structure                                            |    |

| Table 78  | DRBG Reseed Service Response                                    | 43 |

| Table 79  | DRBG Generate Service Response                                  |    |

| Table 80  | DRBG Uninstantiate Request                                      |    |

| Table 81  | Uninstantiate Response                                          |    |

| Table 82  | DRBG Reset Request                                              |    |

| Table 83  | DRBG Reset Response                                             |    |

| Table 84  | Zeroization Request                                             |    |

| Table 85  | Zeroization Configuration Options                               |    |

| Table 86  | Programming Service Status Codes                                |    |

| Table 87  | Autherrcode                                                     |    |

| Table 88  | Errorcode                                                       |    |

| Table 89  | IAP Programming Service Request                                 |    |

| Table 90  | OPTIONS                                                         |    |

| Table 91  | MODE                                                            |    |

| Table 92  | IAP Response                                                    |    |

| Table 93  | ISP Programming Service Request                                 |    |

| Table 94  | ISP Response                                                    |    |

| Table 95  | NVM Data Integrity Check Service Request                        | 49 |

| Table 96  | OPTIONS                                                         |    |

| Table 97  | NVM Data Integrity Check Response                               |    |

| Table 98  | DIGESTERR                                                       |    |

| Table 99  | Unrecognized Command Message                                    |    |

| Table 100 | POR Digest Error Message                                        |    |

| Table 101 | System Services APIs for Fetching Device and Design Information |    |

| Table 102 | User Interface Signals                                          |    |

| Table 103 | Command Codes for Device and Design Information Services        |    |

|           |                                                                 |    |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

## 1.1 Revision 6.0

The following is a summary of the changes in revision 6.0 of this document.

- Updated System Controller Suspend Mode, page 11.

- Updated Figure 5.

## 1.2 **Revision 5.0**

Updated Dedicated Programming SPI Peripheral, page 10 and System Controller Suspend Mode, page 11.

## 1.3 Revision 4.0

The following is a summary of the changes in revision 4.0 of this document.

- Added the Related Applications, page 63.

- Updated the Key-Tree Cryptographic Service, page 26.

- Updated the Challenge-Response Cryptographic Service, page 27.

- Added the Elliptic Curve Cryptography Services, page 27.

- Added the SRAM-PUF Services, page 30.

- Updated the Non-Deterministic Random Bit Generator (NRBG) Services, page 40.

- Added a note in Flash\*Freeze Service, page 20about deep-power-down action.

- Updated Table 99, page 50 for command change.

- Updated the references as per the standard.

## 1.4 Revision 3.0

The following is a summary of the changes in revision 3.0 of this document.

- Updated value for OPMODE 3 in Table 21, page 22.

- Updated Reseed Service, page 43.

- Updated System Controller Suspend Mode, page 11.

## 1.5 Revision 2.0

The following is a summary of the changes in revision 2.0 of this document.

- Updated Table 3, page 15.

- Updated DPA-Resistant Key-Tree Services, page 25.

- Updated Non-Deterministic Random Bit Generator (NRBG) Services, page 40.

- Updated the Instantiate Service, page 41.

- Updated the Generate Service, page 42

- Updated the Reseed Service, page 43.

- Added Table 87, page 46, Table 88, page 47.

- Updated Figure 2, page 4 and Figure 4, page 5.

- Updated SYSRESET, page 10.

- Updated System Controller Suspend Mode, page 11.

- Added Clock Requirements, page 11.

## 1.6 Revision 1.0

The following is a summary of the changes in revision 1.0 of this document.

- · Restructured the user guide.

- Updated Table 21, page 22, Table 56, page 36, Table 85, page 45.

- Added How to Use System Services in IGLOO2, page 54 section.

- Updated Figure 2, page 4.

- Added System Controller Suspend Mode, page 11.

## 1.7 Revision 0.0

Revision 0.0 was the first publication of this document.

# 2 System Controller

## 2.1 Introduction

This chapter discusses the subsystems and interfaces in the SmartFusion2 and IGLOO2 System Controller. The System Controller manages the programming of the device and handles system service requests. The System Controller serves as the base on which the following system services (described in the System Services, page 14) are made available with SmartFusion2 and IGLOO2 devices:

- Device and design information services

- Flash\*Freeze services

- Cryptographic services

- DPA-resistant key tree services

- Non-deterministic random bit generator services

- Zeroization service

- Programming services

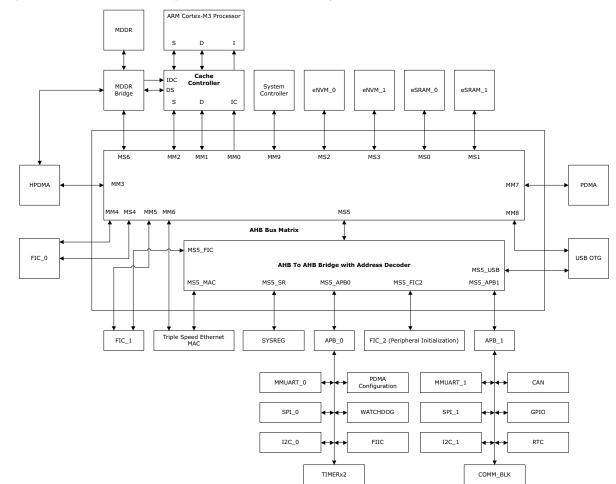

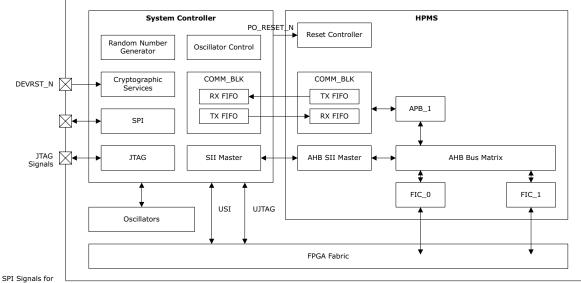

The following figure shows the connectivity of the SmartFusion2 System Controller to the AHB bus matrix.

#### Figure 1 • SmartFusion2 - System Controller Interfacing with AHB Bus Matrix

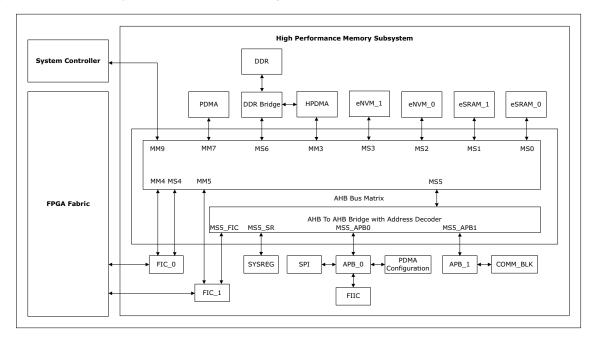

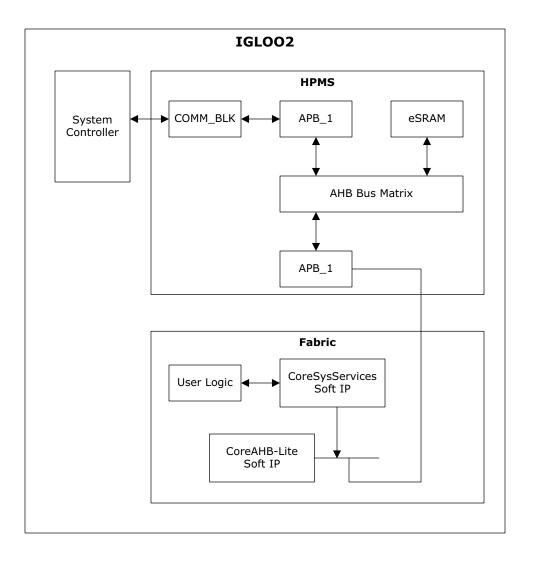

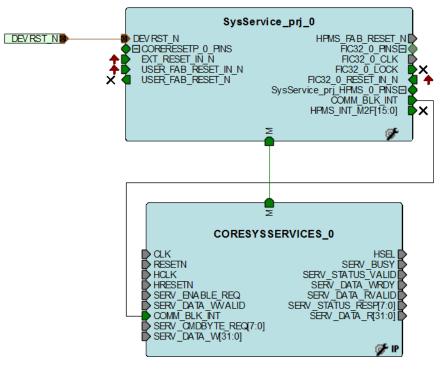

The following figure shows the connectivity of the IGLOO2 System Controller to the AHB bus matrix.

Figure 2 • IGLOO2 - System Controller Interfacing with AHB Bus Matrix

## 2.2 Functional Description

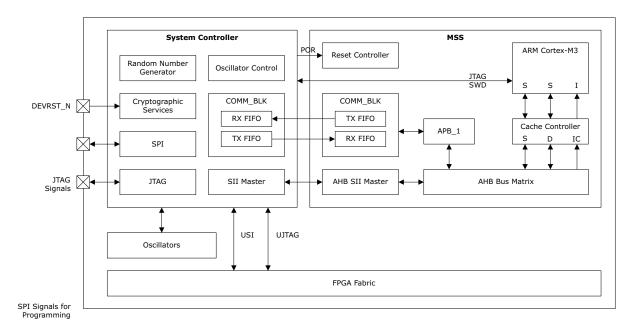

The following figure shows the interfacing of the SmartFusion2 System Controller with MSS and the FPGA fabric.

Figure 3 • SmartFusion2 - Interfacing of the System Controller with MSS and FPGA Fabric

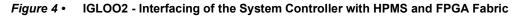

The following figure shows the interfacing of the IGLOO2 System Controller with HPMS and the FPGA fabric.

SPI Signals for Programming

The SmartFusion2 and IGLOO2 System Controllers consist of the following subsystems and interfaces, as shown in Figure 3, page 4 and Figure 4, page 5.

### 2.2.1 Subsystems

- System IP Interface (SII) Master

- Communication Block (COMM\_BLK)

- Oscillator Control

- Random Number Generator

- Cryptographic Services

- JTAG

- Dedicated Programming SPI Peripheral

#### 2.2.2 Interfaces

- DEVRST\_N

- SPI signals for programming

- JTAG signals

- User JTAG

- User services interface (USI)

The following sections provide short description of these sub-systems and interfaces.

## 2.2.3 System IP Interface (SII) Master

The system IP interface (SII) master connects the System Controller with all the internal elements. It is used to transfer data to and from the MSS or HPMS memory space by the System Controller for system services. It is also used for factory tests but not available for customer.

## 2.2.4 Communication Block (COMM\_BLK)

The communication block (COMM\_BLK) provides a bidirectional message passing facility between the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor/Fabric master and the System Controller. It is similar to a mailbox communication channel that allows message bytes to be passed from the Fabric master to the System Controller and vice versa. For more information, refer to the "Communication Block" chapter in the UG0448: IGLOO2 High Performance Memory Subsystem User Guide and UG0331: SmartFusion2 Microcontroller Subsystem User Guide. The COMM\_BLK is used to call system services. System

services can be implemented using API functions. For more information, refer to the System Services, page 14.

## 2.2.5 Oscillator Control

The oscillator control block manages the on-chip RC oscillators and crystal oscillators. It performs oscillator initialization and control during device start-up. The on-chip oscillators are automatically disabled if the users do not configure the blocks (System Controller, MSS/HPMS, and FPGA fabric logic) that are required for them. If the subsystem is not configured for use, the oscillator is turned off synchronously without generating runt clock pulses. The 50 MHz RC oscillator is the default clock source; it is enabled after power-on reset. For more information about how to set up RC oscillators and the main crystal oscillator as clock sources, refer to the "Oscillator Configuration" section in the *UG0449: SmartFusion2 and IGLOO2 Clocking Resources User Guide.*

## 2.2.6 Random Number Generator

The System Controller contains a random number generator block which is available for user cryptographic services. The Deterministic Random Bit Generator (DRBG) is implemented as defined in National Institute of Standards and Technology (NIST) Special Publication 800-90. It provides the following features:

- Designed to support AIS-31 random number generation requirement.

- Uses AES-256 CTR mode per NIST SP800-90 for the DRBG implementation.

- Built-in hardware tests for auto correlation and continuous random number generation testing (CRNGT).

For more information, refer "Non-Deterministic Random Bit Generator (NRBG)" section in the UG0443: SmartFusion2 and IGLOO2 FPGA Security Best Practices User Guide.

## 2.2.7 Cryptographic Services

The System Controller contains an AES encryption and decryption engine which can be dynamically configured for key lengths of 128 or 256 bits. A NIST-approved SHA-256 authentication algorithm is also provided. For more information, refer to the "Other Cryptographic Services" section in the UG0443: SmartFusion2 and IGLOO2 FPGA Security Best Practices User Guide.

## 2.2.8 JTAG

The System Controller implements the functionality of a JTAG slave, with IEEE 1532 support, which also implies IEEE 1149.1 compliance. JTAG communicates with the System Controller using a Command register that conveys the JTAG instruction to be executed and a 128-bit data I/O buffer that transfers any associated data. The JTAG interface is used for the following operations:

- In-system programming (ISP)

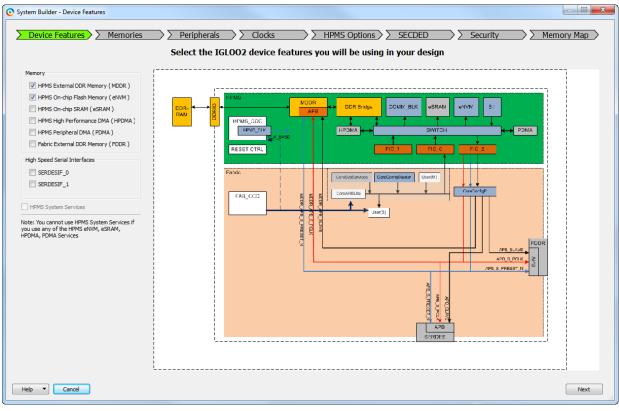

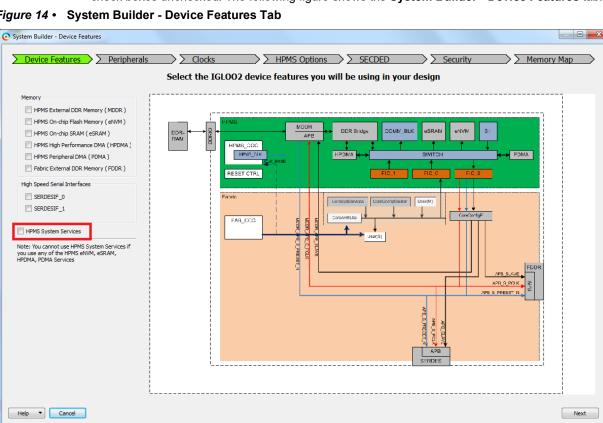

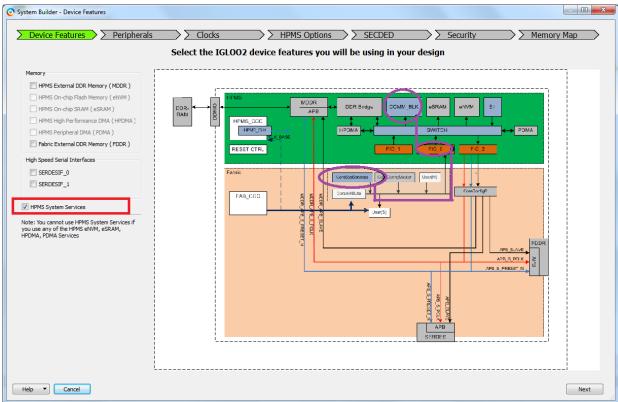

- For more information, refer UG0451: SmartFusion2 and IGLOO2 Programming User Guide.