# Power over Ethernet PD690xx Auto Mode Registers Map

**Rev 1.3**

#### Table of Contents

|                                                                              | 3                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GENERAL NOTE<br>EXAMPLE 1<br>EXAMPLE 2<br>GENERAL CONFIGURATION INSTRUCTIONS | 3<br>3                                                                                                                                                                                                                                                                                                                                 |

| I <sup>2</sup> C PROTOCOL STRUCTURE WITH HOST                                | 5                                                                                                                                                                                                                                                                                                                                      |

| SYSTEM INITIALIZATION REGISTERS                                              | 6                                                                                                                                                                                                                                                                                                                                      |

| PORTS INITIALIZATION / CONFIGURATION REGISTERS (PORT SETTING)                | 9                                                                                                                                                                                                                                                                                                                                      |

| SYSTEM STATUS / MONITORING                                                   | 9                                                                                                                                                                                                                                                                                                                                      |

| PORT STATUS MONITORING                                                       | 12                                                                                                                                                                                                                                                                                                                                     |

| PORT COMMANDS                                                                | 16                                                                                                                                                                                                                                                                                                                                     |

| INTERRUPT REGISTERS                                                          | 17                                                                                                                                                                                                                                                                                                                                     |

| PD690XX DETAILED REGISTERS LIST AND DESCRIPTION                              | 19                                                                                                                                                                                                                                                                                                                                     |

| OPENING A CONFIGURATION REGISTER FOR WRITE OPERATION                         | 37                                                                                                                                                                                                                                                                                                                                     |

|                                                                              | EXAMPLE 1<br>EXAMPLE 2<br>GENERAL CONFIGURATION INSTRUCTIONS<br>I <sup>2</sup> C PROTOCOL STRUCTURE WITH HOST<br>SYSTEM INITIALIZATION REGISTERS<br>PORTS INITIALIZATION / CONFIGURATION REGISTERS (PORT SETTING)<br>SYSTEM STATUS / MONITORING<br>PORT STATUS MONITORING<br>PORT COMMANDS<br>INTERRUPT REGISTERS LIST AND DESCRIPTION |

# 1. Introduction

This Register Mapping Matrix comprises internal registers description for the PD690xx (RTOEM) PoE device.

### 1.1. General Note

PD690xx communication protocol is based on dual byte format (16 bit data), as illustrated in Section 2 below.

Each Read or Write transaction is framed in a dual byte packet. Registers of 8 bits or less are used as Read and Write pairs (two registers in a single packet). When calling a single 16 bit register, or two 8 bit registers, user (Host) should use a single "even" address, as specified in this document. There is no need to perform dual read/write transactions.

Note that writing/reading from an "odd" address will not be executed.

### 1.2. Example 1

To read Port 1 I<sub>cut</sub> 8 bit register, user should access both Port 0 and Port 1 simultaneously through address "1000". Note that register in address "1001" **CANNOT** be accessed directly, but only through address "1000".

### 1.3. Example 2

To write into "System Power Budget 0" register, user should access "138C" address via 16 bit wide register. Register in address "138D" cannot be accessed directly.

If user attempts to read or write from "138D" address, data transfer will be corrupted and might damage IC configuration.

Addresses marked in brackets "(...)" cannot be accessed directly!

### 1.4. General Configuration Instructions

To protect PoE system from incorrect configuration sequencing, PD69012 has a dedicated software protection mechanism that ensures sensitive configuration registers are modified only when PoE ports are OFF.

This mechanism also ensures that PoE system is initialized properly after modifying those registers.

**Important**: Set PoE system configuration registers (such as AT/AF mode, Res/Legacy Detection mode, I<sub>CUT</sub> currents levels etc.) only when system is initializing and ports are OFF.

The recommended sequence is:

- 1. Disable all ports (via Disable pin or via Disable Port Register)

- 2. Change mode to **config** mode (see instructions below)

- 3. Perform all necessary changes (Registers Set)

- 4. Return to normal operational Auto mode

- 5. Enable PoE ports power

To enter CONFIG mode, do the following:

1. DisPortsCmd register (address 0x1332) → Write data = 0x03FF

or disable each port in Portx\_CR register (addresses 0x131A to 0x1330) bits [1:0] → Data = 00

- 2. Change mode:

- a. SW\_ConfigReg (address 0x139E) → Write data = 0xDC03

- b. I2C\_ExtSyncType (address 0x1318) → Write data = 0x0020 (Mode Event Sync)

- c. EXT\_EV\_IRQ (address 0x1144) → Write data = 0x0020 (Mode Event IRQ Sync)

d. To ensure this command was properly performed, user may read SW\_ConfigReg register (go to address 0x139E) → Expected Read Data = 0x0003

**Note:** At this point, RAM space (address 0x1000 to the end) is open for Write operations. In this mode user can make changes to relevant registers.

3. After completing Write operation, return to operational Auto mode:

- a. SW\_ConfigReg (address 0x139E) → Write data = 0xDC00

- b. I2C\_ExtSyncType (address 0x1318) → Write data = 0x0020

- c. EXT\_EV\_IRQ (address 0x1144) → Write data = 0x0020

To ensure that command was performed properly, user can read SW\_ConfigReg register:

- (address 0x139E) → Expected Data = 0x0000

- 4. Enable all PoE ports:

- DisPortsCmd register (address 0x1332) → Write data = 0x0000, or enable each port in the Portx\_CR register (addresses 0x131A to 0x1330) bits [1:0] → Write data = 01

# 2. I<sup>2</sup>C Protocol Structure with Host

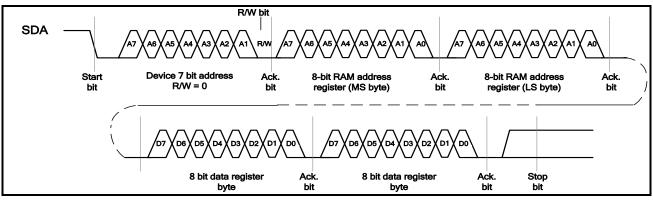

Figure 1 illustrates the sequence structure for Write cycles. Each packet ends with an Ack bit sent from the PoE system.

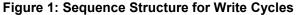

Sequence structure for Read cycles (see\_Figure 2): Second start bit indicates a read cycle is following. The PoE system issues all Acknowledge bits, except for those issued by the Host as part of the reply from the PoE Device. The Host provides a stop bit.

Figure 2: Sequence Structure for Read Cycles

# 3. System Initialization Registers

| Register Name                                  | Register Description                                                                                                                                                         | Address<br>(HEX)                             | Default Value                                                                       | Register<br>Width<br>(BITS) | Read/<br>Write |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------|----------------|

|                                                | Timer Value for Overload                                                                                                                                                     | Conditions                                   | 1                                                                                   |                             |                |

| Tovld_AF                                       | Formula:<br>• 1 LSB bit = 125µs                                                                                                                                              | 100E                                         | 208H (65 ms)                                                                        | 16                          | R/W            |

| Tovld_AT                                       | <ul> <li>Range: 0 to 522ms</li> <li><i>Example:</i><br/>For 10ms<br/>10 / .125 = 80 (decimal)</li> </ul>                                                                     | 1010                                         | 208H<br>(65 ms)                                                                     | 16                          | R/W            |

| Ма                                             | aximum V <sub>main</sub> Voltage Level Threshold (Be                                                                                                                         | fore Power                                   | ing Off All Ports                                                                   | )                           |                |

| VmainHighTh                                    | Formula:<br>• 1 bit = 61mV, Range: 0 to 1023 = 0<br>to 59.392V<br>Example:<br>For 50V max<br>50V / 61mV = 820 (decimal)                                                      | 12FE                                         | 10'h3bc                                                                             | 10                          | R/W            |

| Mi                                             | nimum V <sub>main</sub> Voltage Level Threshold (Be                                                                                                                          | fore Power                                   | ing Off All Ports                                                                   | )                           |                |

| VmainATLowTh                                   | Formula:<br>• 1 bit = 61mV, Range: 0 to 1023 = 0<br>to 59.392V                                                                                                               | 1300                                         | 10'h313                                                                             | 10                          | R/W            |

| VmainAFLowTh                                   | Example:<br>For 45V min<br>45V / 61mV = 738 (decimal)<br>(Hysteresis of V <sub>main</sub> Thresholds = 1V)                                                                   | 1302                                         | 10'h2b0                                                                             | 10                          | R/W            |

|                                                | Power Budget Guard Band Value for t                                                                                                                                          | he Master F                                  | PoE Device                                                                          |                             |                |

| N/A – Irrelevant                               | PD69012 has a Dynamic Guard Band<br>instead of a Static Guard Band<br>See <i>PD690xx Technical Note TN-144</i> for<br>Auto Mode Power Management's<br>mechanism description. | N/A                                          | N/A                                                                                 | N/A                         | N/A            |

| Total Pow                                      | er Budget – Sets the Maximum Power Le                                                                                                                                        | vel, Availab                                 | le for All Ports (                                                                  | System)                     |                |

| Master<br>Configuration for<br>SysPowerBudget0 | Master IC configuration for system<br>power budget<br>Supports up to eight power banks levels.<br>Power budgets 000 to 111 (according to                                     | 138C<br>138E<br>1390<br>1392<br>1394<br>1396 | 8700 (3456W)<br>10E0 (432W)<br>BB8 (300W)<br>898 (220W)<br>7D0 (200W)<br>5DC (150W) | 16                          | R/W            |

| 7                                              | power good I/Os)<br>1 Bit LSB = 0.1W                                                                                                                                         | 1398<br>1398<br>139A                         | 4B0 (120W)<br>3E8 (100W)                                                            |                             |                |

| Register Name                                  | Register Description                                                                                                                                                                                                                                                                                                                                                           | Address<br>(HEX) | Default Value | Register<br>Width<br>(BITS) | Read/<br>Write |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|-----------------------------|----------------|

|                                                | Power Management                                                                                                                                                                                                                                                                                                                                                               | Mode             |               | •                           |                |

| PM mode – sys<br>Flag                          | <ul> <li>Set power management calculation method for IC:</li> <li>"0": Static Mode; according to Class or Port Power Allocation Level (PPL) → PPL is set through Address Registers 1334 to 134A</li> <li>"1": Dynamic Mode; according to actual (real time) power consumption</li> </ul>                                                                                       | 1160<br>Bit [6]  | 0 = Static    | 1                           | R/W            |

|                                                | General User Regis                                                                                                                                                                                                                                                                                                                                                             | ters             | 1             | T                           | r              |

| General User<br>register                       | General User register for user's use                                                                                                                                                                                                                                                                                                                                           | 0318             | 16'h0000      | 16                          | R/W            |

| Legacy CAP<br>Detection                        | Legacy CAP Detection Enable register<br>BIT[2]<br>• "1" = Cap Detection disabled<br>• "0" = Cap Detection enabled                                                                                                                                                                                                                                                              | 1160<br>Bit[2]   | 1= Disabled   | 16                          | R/W            |

| Software<br>Configuration<br>register          | Software Configuration & Change Mode<br>Protection register<br>Bits [2:0] = SW Configuration Key<br>• 000: Stand alone master \ slave<br>• 001: Macro mode slave<br>• 010: Manual mode<br>• 011: Config. mode<br>Bits [7:3] = Spare = Not Used<br>Bits [15:8] = Special Change Mode<br>Key<br>Verification key for the mode change →<br>Only if 0xDC enable mode changes       | 139E             | 16'h0003      | 16                          | R/W            |

| I2C Communication<br>External Sync<br>register | This register defines the type of external<br>sync event expected by I2C<br>communication<br>• 0x01: Detection Sync<br>• 0x02: Startup Sync<br>• 0x04: Update PB Sync<br>• 0x08: Read Indications Sync<br>• 0x10: Macro Sync<br>• 0x20: Mode Sync<br>• 0x20: Mode Sync<br>• 0x40: Interrupt Out Sync<br>• 0x80: Read PM Indications Sync<br>0x100: Masters Sync (for Host use) | 1318             | 16'h0000      | 16                          | R/W            |

| Register Name                                     | Register Description                                                                                                                                                                                                                                                                                                                                                                  | Address<br>(HEX) | Default Value | Register<br>Width<br>(BITS) | Read/<br>Write |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|-----------------------------|----------------|

| External Event:<br>Interrupt register for<br>SYNC | This register defines the type of external<br>sync, Interrupt Request Signal event<br>expected by I2C communication<br>• 0x01: Detection Sync<br>• 0x02: Startup Sync<br>• 0x04: Update PB Sync<br>• 0x08: Read Indications Sync<br>• 0x10: Macro Sync<br>• 0x20: Mode Sync<br>• 0x40: Interrupt Out Sync<br>• 0x80: Read PM Indications Sync<br>• 0x100: Masters Sync (for host use) | 1144             | 16'h0000      | 16                          | R/W            |

# 4. Ports Initialization / Configuration Registers (Port Setting)

| Register Name                                                         | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Address<br>(HEX)                                                                             | Default<br>Value                                  | Register<br>Width | Read/<br>Write |  |  |  |  |  |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------|----------------|--|--|--|--|--|

|                                                                       | Set / Updates Icut Value – According to Class Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |                                                   |                   |                |  |  |  |  |  |

| ICUT mode – sys<br>Flag                                               | <ul> <li>Set I<sub>cut</sub> level according to CLASS</li> <li>"0": Set I<sub>cut</sub> according to CLASS</li> <li>"1": Set I<sub>cut</sub> to maximum value according to power allocation limits (for more information see address registers 1334 to 134A)</li> </ul>                                                                                                                                                                                                                                              | 1160<br>Bit[4]                                                                               | 1 = I <sub>cut</sub><br>MAX                       | 1                 | R/W            |  |  |  |  |  |

|                                                                       | Per Port Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | on                                                                                           |                                                   |                   |                |  |  |  |  |  |

| Per Port<br>Configuration:<br>(12 registers)<br>Port0_CR<br>Port11_CR | BITS [0;1] = Port Enable<br>"00": Port Disable<br>"01": Port Enable<br>"10": Force Power<br>"11": Reserved (future use)<br>BITS [2;3] = Port Pair Control<br>"00": Reserved (future use)<br>"01": ALT A<br>"10": ALT B (back off enable)<br>"11": Reserved (future use)<br>BITS [4;5] = AF/AT Port type<br>"00": AF<br>"00": AF<br>"01": AT<br>"10": Reserved (future use)<br>"11": Reserved (future use)<br>BITS [6;7] = Port Priority<br>"00": Critical = Highest priority<br>level<br>"11": Reserved (future Use) | 131A<br>131C<br>131E<br>1320<br>1322<br>1324<br>1326<br>1328<br>132A<br>132C<br>132E<br>1330 | DFLT=<br>01-EN<br>01-ALTA<br>01-AT<br>00-Critical | 16                | R/W            |  |  |  |  |  |

### 5. System Status / Monitoring

| Register Name                                  | Register Description                              | Address<br>(HEX) | Default<br>Value | Register<br>Width | Read/<br>Write |  |  |

|------------------------------------------------|---------------------------------------------------|------------------|------------------|-------------------|----------------|--|--|

| V <sub>main</sub> Voltage Measurement Register |                                                   |                  |                  |                   |                |  |  |

| V <sub>main</sub>                              | V <sub>main</sub> voltage measurement register    |                  |                  |                   |                |  |  |

|                                                | 1 LSB Bit =61 mV<br>Range = 0 to 1023 = 0 to 62 V | 105c             | 10'h0            | 10                | Read           |  |  |

| Hardware Configuration & Mode Register         |                                                   |                  |                  |                   |                |  |  |

| Register Name                    | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Address<br>(HEX) | Default<br>Value                    | Register<br>Width | Read/<br>Write |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------|-------------------|----------------|

| System INIT register             | Internal Register: Latched from<br>ASIC_INI and I2C_INI I/Os after<br>Power Up<br>Bits[0;3] = ASIC_INI Value<br>Bits[4;7] = I2C_INI Value<br>Bits[8;15] = Version Register Value                                                                                                                                                                                                                                                                                                                                                                                                   | 1164             | 16'h0                               | 16                | Read           |

|                                  | Averaged Junction Tempera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ture Level       |                                     |                   |                |

| Averaged Junction<br>Temperature | Averaged Junction Temperature,<br>as constantly calculated and<br>monitored by two temperature<br>sensors, located on PD69012 Die.<br>Typical accuracy is $\pm$ -5° C<br>Temperature formula =<br>Deg C = (reg_value: 684) /<br>(-1.514)) - 40<br>(1 LSB = ~0.66C)                                                                                                                                                                                                                                                                                                                 | 130A             | 10'h0                               | 10                | Read           |

|                                  | Device Version Control R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | egister          | T                                   |                   |                |

| CFGC_ICVER                       | IC HW & SW version; it is an<br>internal / read only register.<br>This register identifies chip type<br>and internal analog, digital code,<br>and ROM versions, based on the<br>following coding:<br>BITS [15-11]: Microsemi PoE<br>Family Indication (5 MSB bits):<br>• 5'b00010 = PD64004<br>• 5'b00110 = PD64012<br>• 5'b00111 = PD69012<br>(default)<br>• 5'b01000 = PD69004<br>BITS [10-8]: Analog version (3 bits)<br>= 1 dec<br>BITS [7-5]- Digital version (3 bits) =<br>1 dec<br>BITS [4-0]: SW ROM version (5<br>LSB bits) = 2 dec<br>System Total Power Monitoring (Rea | 031A             | 16'b001<br>11,001,<br>001,00<br>010 | 16                | Read           |

| Register Name                      | Register Description                                                                     | Address<br>(HEX)             | Default<br>Value | Register<br>Width | Read/<br>Write |

|------------------------------------|------------------------------------------------------------------------------------------|------------------------------|------------------|-------------------|----------------|

| SysTotalRealPowerC<br>ons          | Total power consumption of the whole system (Master + 7 Slaves)                          | 12E8                         | 16'h0            | 16                | Read           |

|                                    | 1 LSB = 0.1 Watt                                                                         |                              |                  |                   |                |

|                                    | Power consumption monitoring – as read from Master IC.                                   | 12EC<br>12EE                 |                  |                   |                |

| TotalPowerConsSlav<br>e0 to Slave7 | 16 bits register Per IC<br>From Slave 0, address 12EC<br>(Master), to Slave 7 – Add 12FA | 12F0<br>12F2<br>12F4<br>12F6 | 16'h0            | 16                | Read           |

|                                    | 1 LSB = 0.1W                                                                             | 12F8<br>12FA                 |                  |                   |                |

|                                    | Local Total Power Level (Read                                                            | from Slave                   | IC)              |                   |                |

|                                    | Power consumption monitoring, as read from Slave IC.                                     |                              |                  |                   |                |

| LocalTotalRealPower<br>Cons        | Real total power consumption<br>∑(PortXPowerCons)                                        | 12AA                         | 16'h000<br>0     | 16                | Read           |

|                                    | 1 LSB = 0.1W                                                                             |                              |                  |                   |                |

|                                    | Bit [0]: V <sub>main</sub> is above upper threshold                                      |                              |                  |                   |                |

|                                    | Bit[1]: Junction temperature is above threshold (150° C)                                 |                              |                  |                   |                |

| Additional IC Status               | Bit [2]: Disable ports I/O is active                                                     |                              |                  |                   |                |

| Indications                        | Bit [3]: V <sub>main</sub> is below AT low threshold                                     | 1314                         | 16'h00           | 16                | Read           |

|                                    | Bit [4]: V <sub>main</sub> is below AF low threshold                                     |                              |                  |                   |                |

|                                    | Bit [5]: The temperature is above<br>alarm threshold                                     |                              |                  |                   |                |

# 6. Port Status Monitoring

| Register Name                     | Register Description                                                                                                                                                                                                                                                                                     | Address<br>(HEX)                                                                             | Default<br>Value | Register<br>Width | Read/<br>Write |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------|-------------------|----------------|

|                                   | Port Classification Results                                                                                                                                                                                                                                                                              | Status                                                                                       |                  | -                 |                |

| Port0_class<br>Port1_class        | Port CLASS Status Monitoring:<br>[3:0]: First finger result<br>[7:4]: Second finger result<br>[15:8]: Final detected class<br>• 000: Class 0<br>• 001: Class 1<br>• 010: Class 1<br>• 010: Class 2<br>• 011: Class 3<br>• 100: Class 4<br>• 101: Reserved<br>• 110: Reserved<br>• 111: Class not defined | 11C2<br>11C4<br>11C6<br>11C8<br>11CA<br>11CC<br>11CE<br>11D0<br>11D2<br>11D4<br>11D6<br>11D8 | 7'h7             | 16                | Read           |

|                                   | Port Power Consumption                                                                                                                                                                                                                                                                                   | Value                                                                                        |                  |                   |                |

| Port0PowerCons<br>Port11PowerCons | Real Time (actual) port power<br>consumption.<br>Calculated based on I <sub>port</sub> * V <sub>port</sub><br>12 registers per IC: Port 0 to Port 11<br>LSB = 0.1W                                                                                                                                       | 12B4<br>12B6<br>12B8<br>12BA<br>12BC<br>12BE<br>12C0<br>12C2<br>12C4<br>12C6<br>12C8<br>12CA | 16'h0            | 16                | Read           |

|                                   | AC Disconnect Status Re                                                                                                                                                                                                                                                                                  | gister                                                                                       | T                |                   | -              |

| Port Disconnection<br>Status      | See port status registers<br>address 11AA – 11C0                                                                                                                                                                                                                                                         |                                                                                              |                  |                   | Read           |

|                                   | Port Power Status Due to DC I                                                                                                                                                                                                                                                                            | <b>Disconnect</b>                                                                            | T                |                   |                |

|                                   | See port status registers<br>Address 11AA – 11C0                                                                                                                                                                                                                                                         |                                                                                              |                  |                   |                |

|                                   | Port Overload Statu                                                                                                                                                                                                                                                                                      | S                                                                                            | T                | 1                 | ·              |

| Port Overload Status              | See port status registers<br>Address 11AA – 11C0                                                                                                                                                                                                                                                         |                                                                                              |                  |                   |                |

| F                                 | Port Off Due to Disable_Ports pin or V                                                                                                                                                                                                                                                                   | <mark>main Out o</mark>                                                                      | f Range          |                   |                |

| Port Off due to<br>Disable        | See port status registers<br>Address 11AA – 11C0                                                                                                                                                                                                                                                         |                                                                                              |                  |                   |                |

| Register Name                                               | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Address<br>(HEX)                                                                             | Default<br>Value | Register<br>Width | Read/<br>Write |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------|-------------------|----------------|

|                                                             | OVL During Startup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | )                                                                                            |                  |                   |                |

| Over Load during<br>Startup                                 | See port status registers<br>addresses 11AA – 11C0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |                  |                   |                |

|                                                             | Port Start up Stage is Con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | npleted                                                                                      |                  |                   |                |

| Start Up Completed                                          | See port status registers<br>addresses 11AA – 11C0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |                  |                   |                |

|                                                             | Port Over Power Consumptie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | on Status                                                                                    |                  |                   |                |

| Port Over Power                                             | See port status registers<br>addresses 11AA – 11C0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |                  |                   |                |

|                                                             | Read Port Status Regis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ster                                                                                         | -                |                   | -              |

| Port Status [0-7]<br>Port Status [8-10]<br>Port Status [11] | <ul> <li>Port status indication is based on real-time snapshot of port status.</li> <li>Status Indication Coding Bits are NOT latched and may be changed to reflect real-time (True) port status at Read Operation time slot.</li> <li>The indication is based on two fields:</li> <li><b>Bits [7-0]</b>: Coded into 21 different status indications as listed below:</li> <li>Decimal Value = 0 (zero): Port is on; Port was turned on due to a valid signature (res or cap)</li> <li>Decimal Value = 1: Port is On; Port was turned on due to Force Power command</li> <li>Decimal Value 2: Port is in Starting Up stage</li> <li>Decimal Value 3: Port is powered up due to Force Power command</li> <li>Decimal Value 4: Searching; Port is waiting for detection, or during detection phase</li> <li>Decimal Value 5: Invalid Signature; Invalid signature (detection) has been detected</li> <li>Decimal Value 6: Class Error; Error in classification has been detected</li> </ul> | 11AA<br>11AC<br>11AE<br>11B0<br>11B2<br>11B4<br>11B6<br>11B8<br>11BA<br>11BC<br>11BE<br>11C0 | 16'h00           | 16                | Read           |

# Auto Mode PD690xx Registers Map

| Register Name | Register Description                                                                            | Address<br>(HEX) | Default<br>Value | Register<br>Width | Read/<br>Write |

|---------------|-------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|----------------|

|               | Decimal Value 7: Test Mode; Port is<br>waiting to be turned on in Test Mode<br>Force Power      |                  |                  |                   |                |

|               | Decimal Value 8: Valid Signature; A<br>valid signature has been detected<br>(Detection Pass)    |                  |                  |                   |                |

|               | Decimal Value 9: Disabled; Port is disabled                                                     |                  |                  |                   |                |

|               | Decimal Value 10: Startup OVL;<br>Over-load during startup                                      |                  |                  |                   |                |

|               | Decimal Value 11: Startup UDL;<br>Under-load during startup                                     |                  |                  |                   |                |

|               | Decimal Value 12: Startup Short;<br>Short during startup                                        |                  |                  |                   |                |

|               | Decimal Value 13: DvDtFail; Failure in the Dv/Dt algorithm                                      |                  |                  |                   |                |

|               | Decimal Value 14: Test Error; Port<br>was turned on as Test Mode (Force<br>Power) and has error |                  |                  |                   |                |

|               | Decimal Value 15: OVL; Overload detected                                                        |                  |                  |                   |                |

|               | Decimal Value 16: UDL; Under-load detected                                                      |                  |                  |                   |                |

|               | Decimal Value 17: Short Circuit;<br>Short circuit detected                                      |                  |                  |                   |                |

|               | Decimal Value 18: PM; Port was<br>turned off due to Power<br>Management Mechanism               |                  |                  |                   |                |

|               | Decimal Value 19: System Disabled;<br>Chip level error                                          |                  |                  |                   |                |

|               | Decimal Value 20: Unknown;<br>General chip error                                                |                  |                  |                   |                |

|               | Bits [10-8]: Additional 3 bits coding for 8 additional status indications                       |                  |                  |                   |                |

|               | BITS [8-10] Coding:                                                                             |                  |                  |                   |                |

| Register Name | Register Description                                                                                                                                                                                                                                                                                                                         | Address<br>(HEX) | Default<br>Value | Register<br>Width | Read/<br>Write |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|----------------|

|               | <ul> <li>000: Disabled</li> <li>001: Searching</li> <li>010: Delivering Power</li> <li>011: Test Mode</li> <li>100: Test Error</li> <li>101: Implementation Specific*</li> <li>110: Reserved</li> <li>111: Reserved</li> <li>BIT[11]: <ul> <li>0: Port in AF Mode after Class</li> <li>1: Port in AT Mode after Class</li> </ul> </li> </ul> |                  |                  |                   |                |

# 7. Port Commands

| Register Name                                           | Register Description                                                                                                           | Address<br>(HEX)                                                                             | Default<br>Value | Register<br>Width | Read/<br>Write |  |  |  |  |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------|-------------------|----------------|--|--|--|--|

| Port Bypass Resistor (Res) Detection                    |                                                                                                                                |                                                                                              |                  |                   |                |  |  |  |  |

|                                                         | No Bypass or Disable Res<br>Detection function in Auto mode                                                                    |                                                                                              |                  |                   |                |  |  |  |  |

| Port Bypass Classification                              |                                                                                                                                |                                                                                              |                  |                   |                |  |  |  |  |

|                                                         | No Bypass or Disable<br>Classification function in Auto<br>mode                                                                |                                                                                              |                  |                   |                |  |  |  |  |

|                                                         | Port Enable Contro                                                                                                             | bl                                                                                           |                  |                   |                |  |  |  |  |

| Port Disable/Enable –<br>Fast Port Off in 1<br>register | One single register to disable ports<br>(bit per port)<br>0: Port Enable<br>1: Port Disable                                    | 1332                                                                                         | 16'h0            | 16                | R/W            |  |  |  |  |

|                                                         | Turns off Main Switching FET (Port OFF)                                                                                        |                                                                                              |                  |                   |                |  |  |  |  |

| Port0_CR<br>Port11_CR                                   | Per Port Control register:<br>Bits [0;1]<br>00: Port Disabled<br>01: Port Enabled<br>10: Force Power<br>11: Reserved           | 131A<br>131C<br>131E<br>1320<br>1322<br>1324<br>1326<br>1328<br>132A<br>132C<br>132E<br>1330 | 2'h01<br>Enable  | 2                 | R/W            |  |  |  |  |

|                                                         | Port Test Mode Force ON Com                                                                                                    | mand (even                                                                                   | t)               |                   |                |  |  |  |  |

| Port0_CR<br>Port11_CR                                   | Per Port Control register –<br>Bits [0 ;1]<br>• 00: Port Disabled<br>• 01: Port Enabled<br>• 10: Force Power<br>• 11: Reserved | 131A<br>131C<br>131E<br>1320<br>1322<br>1324<br>1326<br>1328<br>132A<br>132C<br>132E<br>1330 | 2'h01<br>Enable  | 2                 | R/W            |  |  |  |  |

# 8. Interrupt Registers

| Port Interrupt Out<br>register | Interrupt Register<br>This 12 bits register has a bit per<br>port indication corresponding to the<br>port that had an interrupt out event.<br>BIT [011] = Ports 0 to 11<br>This bit switches LSD I/O between<br>LED stream data functionality<br>output and interrupt (INT)<br>functionality output<br>(enabling the INTERRUPT OUT<br>I/O at the LSD pin)                                                                                                                                                                                                                     | 13A6          | 12'd000        | 12 | RO  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|----|-----|

| Port Interrupt Out<br>register | port indication corresponding to the<br>port that had an interrupt out event.<br>BIT [011] = Ports 0 to 11<br>This bit switches LSD I/O between<br>LED stream data functionality<br>output and interrupt (INT)<br>functionality output<br>(enabling the INTERRUPT OUT                                                                                                                                                                                                                                                                                                         |               | 12'd000        | 12 | RO  |

|                                | LED stream data functionality<br>output and interrupt (INT)<br>functionality output<br>(enabling the INTERRUPT OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |                |    |     |

| Interrupt I/O Enable           | BIT [5]<br>"1" = LED Stream Data (LSD) Out<br>"0" = INT Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1160<br>BIT 5 | 1 =<br>Disable | 16 | R/W |

|                                | Each bit in this INT MASK register<br>refers to a specific event MASKED<br>or ENABLED to be latched in INT<br>register.<br>"1" = Event enabled (not masked)<br>"0" = Masked<br>The events are:<br>[0] Port Power Up<br>[1] Port Power Down<br>[2] Detection Fail<br>[3] OVL or Short<br>[4] UDL or Disconnect<br>[5] OVL During Start<br>[6] Port Off due to PM<br>[7] Port Off at Start Up<br>[8] Over Temperature<br>[9] Temperature Alarm<br>[10] V <sub>main</sub> < AF limit<br>[11] V <sub>main</sub> < AT limit<br>[12] V <sub>main</sub> > Lim<br>[13] Reserved Event | 13A4          | 16'd000        | 16 | R/W |

|                                | Power Up – Interrupt E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | vent          |                |    |     |

| Register Name                             | Register Description                                                                                                                                                                                                                                                                                  | Address<br>(HEX) | Default<br>Value | Register<br>Width | Read/<br>Write |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|----------------|

| Port Power Up                             | Per Port Power Up event.<br>Logic "1" indicates that the specific<br>port was switched <b>on</b> (including force<br>power command)<br>• [0] Port #1<br>• [1] Port #2<br>• [2] Port #3<br>• [3] Port #4<br>Formula:<br>• "1" = Event was detected<br>• "0" = Event was not detected<br>or was cleared | 01AE             | 4'd0             | 4                 | RO             |

|                                           | Interrupt – Clear On Read C                                                                                                                                                                                                                                                                           | ommand           | •                |                   |                |

| Port Power Up - Clear<br>On Read register | Read Operation of this register clears<br>up specific bit in associated interrupt<br>register.<br>Logic "1": clears specific bit.<br>• [0] Port #1<br>• [1] Port #2<br>• [2] Port #3<br>• [3] Port #4<br>Formula:<br>"1" = Clears event operation<br>"0" = Does not clear operation                   | 01AF             | 4'd0             | 4                 | RO             |

# 9. PD690xx Detailed Registers List and Description

| REGISTER<br>NAME                                                     | REGISTER DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ADDRESS<br>(HEX)                                                                             | DEFAULT<br>VALUE<br>(HEX) | REGIST<br>ER<br>WIDTH<br>(BITS) | READ/<br>WRITE |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------|---------------------------------|----------------|

| Port [0 to 11]<br>Current Sense<br>register<br>(I <sub>sense</sub> ) | Per Port Current Consumption (I <sub>sense</sub> ) Level<br>Port 0 = Address 1044<br>Port 1 = Address 1046<br><br>Port 11 = Address 105 A<br>I <sub>sense</sub> level is the port real time current monitoring<br>(value) as measured on the external Sense<br>Resistor (Sense pin).<br>Register can range from<br>0 to 1.25A<br>Register Resolution = 305µA per LSB<br>I <sub>sense</sub> value is automatically averaged and updated<br>every ~1ms<br>Reset value = 0<br>Typical accuracy of this Current Monitoring<br>register is ±5% | 1044<br>1046<br>1048<br>104A<br>104C<br>104E<br>1050<br>1052<br>1044<br>1056<br>1058<br>105A | 0                         | [11:0]                          | RO             |

| V <sub>main</sub><br>Measurement<br>register                         | Main Power Supply: Voltage Measurement<br>register<br>V <sub>main</sub> voltage is measured on V <sub>main</sub> pin<br>Register can range from 0 to ~63V<br>Register Resolution = 61mV per LSB<br>V <sub>main</sub> value is automatically averaged and updated<br>every ~20 ms<br>Reset value = 0<br>Typical accuracy is ±3%                                                                                                                                                                                                            | 105C                                                                                         | 0                         | [9:0]                           | RO             |

| l <sup>2</sup> C External<br>Sync Control<br>register                | IC Interrupt Signal (pin) is driven by an internal<br>Interrupt register.<br>This register is <b>doubled buffered</b> . This prevents<br>skipping (missing) any internal event while busy<br>with the Interrupt Handling Routine.<br>For Host to update the Interrupt register,<br>Microsemi recommends using the following<br>routine:<br>1. Set <b>Register 1318</b> to the desired (expected)                                                                                                                                          | 1318                                                                                         | 0                         | [15:0]                          | R/W            |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                           | REGIST                |                |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|-----------------------|----------------|

| REGISTER<br>NAME                       | REGISTER DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ADDRESS<br>(HEX) | DEFAULT<br>VALUE<br>(HEX) | ER<br>WIDTH<br>(BITS) | READ/<br>WRITE |

|                                        | Sync Type (see below).<br>2. Perform <b>Write Command</b> to Register 1144<br>(which updates the actual Double Register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                           |                       |                |

|                                        | This register defines the type of external sync<br>Interrupt Request Signal event expected by I <sup>2</sup> C<br>communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                           |                       |                |