#### **APPLICATION NOTE**

### Introduction

This application note provides detailed information and circuitry design guidelines for implementing a 48-port Power over Ethernet (PoE) system based on Microsemi's ™ 12-channel PoE manager − PD69012. For communication with hosting system a UART or I<sup>2</sup>C interface is used.

This document allows designers to integrate PoE capabilities, as specified in IEEE802.3af and IEEE802.3at standards, into an Ethernet switch. Enhanced mode provides additional PoE capabilities using PD69000 PoE Controller.

PD69012 PoE manager implements real time functions as specified in IEEE 802.3af and IEEE802.3at standards, including detection, classification and port-status monitoring, as well as system level activities such as power management, and MIB (Management Information Base) support for system management. PoE manager is designed to detect and disable disconnected PDs (Powered Devices) using both DC and AC disconnection methods, as specified in standard.

This application note should be used in conjunction with Application Note 175, catalogue number 06-0055-080 for Layout Design Guidelines. For easier design and development, an Evaluation board (P/N PD-DB-7448E) can be ordered.

## Applicable Documents \_

- IEEE 802.3af-2003 standard, DTE Power via MDI

- IEEE802.3at-2009 standard, DTE Power via MDI

- PD69012 datasheet, catalogue number 06-0069-058

- PD69000 datasheet, catalogue number 06-0070-058

- Application Note 175, Layout Design Guidelines for PoE Systems, catalogue number 06-0055-080

- PD-IM-7400 Evaluation Board User Guide, catalogue number 06-0025-056

- Serial Communication Protocol User Guide, catalogue number 06-0032-056

- Technical Note 134, Emergency Power Management, catalogue number 06-0014-081

## Background \_\_\_\_\_

PD69012 has two operation modes:

- Auto mode (Automatic operation) provides a basic set of features for a stand-alone application (no need for a local PoE Controller).

- Enhanced mode provides an enhanced features-set using a local dedicated PoE Controller (PD69000).

This application note defines Enhanced mode of operation. In this mode, PoE managers communicate with PD69000 PoE Controller via an Enhanced Serial Peripheral Interface (ESPI) bus.

PoE Controller's features are listed below.

### **Enhanced Mode Features**

- IEEE 802.3af compliant

- IEEE802.3at compliant

- IETF Power Ethernet MIB (RFC 3621) compliant

- Can be cascaded for up to eight PoE managers, 96 ports

- Pre-standard PD detection

- Detection of Cisco devices

- UART and I<sup>2</sup>C communication

- Advanced power management; up to 96 ports

- User friendly PoE communication protocol

- Continuous voltage and current monitoring per port and per system

- Parameter setting per port and per system

- Disables ports

- Thermal monitoring & protection

- Built-in 3.3V regulator

- Internal power on reset

- Port matrix

- Interrupt out

- H/W system status pin

- Port's LEDs support

- Emergency Power Management

- Software download for program upgrading

- RoHS compliant

## Integration

The system described is destined for a 48-port switch. Same design can be applied to 1 to 8 PoE managers controlling 12 ports each (from 12 ports to 96 ports in multiplies of 12).

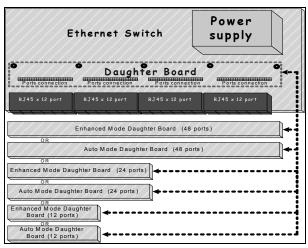

PoE system daughter board can be easily integrated on top of a switch and thereby provides capability to add any PoE application while using different daughter applications (Enhanced mode or Auto mode) (refer to Figure 1).

Figure 1: PoE Daughter Board Integration

## **Overall Description**

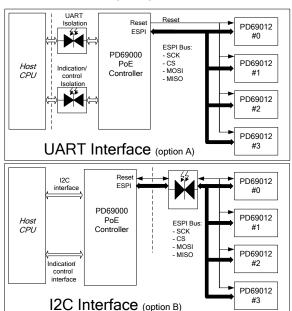

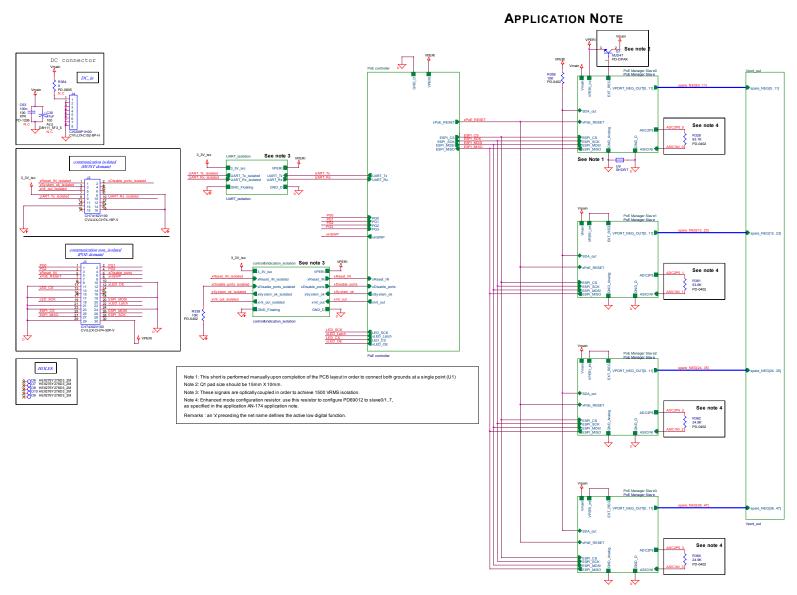

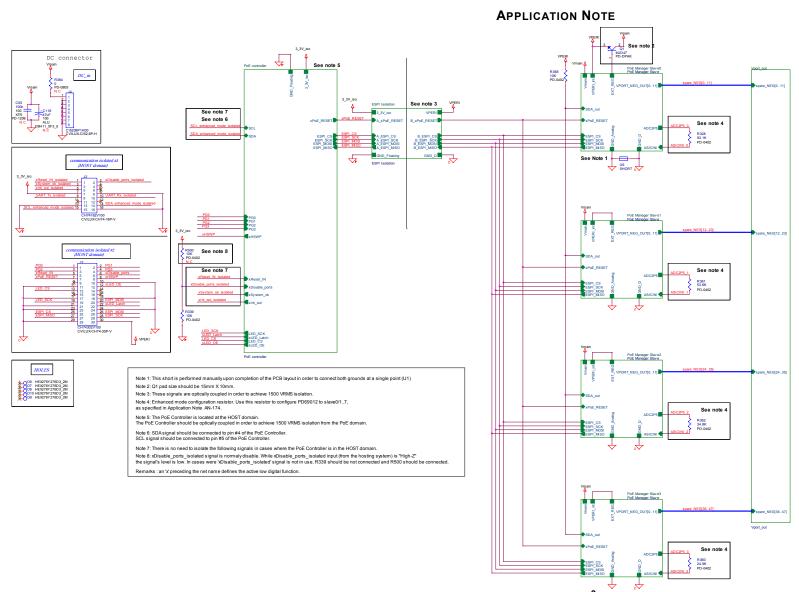

Circuit includes the following blocks (Figure 2):

- 1. PoE circuit for 48 ports based on four PD69012s

- 2. PoE Controller circuit, used for initializing, controlling, and monitoring each of the PD69012s via an internal ESPI bus. PoE Controller communicates with Host CPU via an isolated UART interface, or via a non-isolated I<sup>2</sup>C interface (refer to Figure 2, options A and B).

- 3. Isolation circuit for UART and isolation circuit for indication/control signals (refer to Figure 2, option A) or isolation circuit for ESPI bus and Reset signals (refer to Figure 2, option B).

**Note** In general, (unless otherwise mentioned) this Application Note deals with the UART interface; for I<sup>2</sup>C interface information, refer to I<sup>2</sup>C Interface section.

In cases where a 48 port enhanced PoE system having UART interface is designed, refer to Figure 6 to Figure 12.

In cases where a 48 port enhanced PoE system with I<sup>2</sup>C interface is designed, refer to Figure 7 to Figure 10, Figure 13 and Figure 14.

#### **APPLICATION NOTE**

Figure 2: 48-port Enhanced Mode Configuration

## **General Circuit Description**

The 48-port configuration for a PoE system shown in Figure 2 comprises four PoE managers circuits (PD69012) functioning as slaves to a PoE Controller (PD69000). The PoE Controller utilizes a ESPI bus to control PD69012s. PoE operations are automatically performed by PoE manager circuits, while PoE Controller performs power management and other tasks.

#### **Communication Interfaces**

Communication between Host CPU and local PoE Controller is performed via an isolated UART interface or an I<sup>2</sup>C interface. For more information, refer to the Serial Communication Protocol User Guide, catalogue number 06-0032-056.

#### **ESPI Bus**

ESPI bus is used for internal communication and includes the following lines:

- MOSI (Master Out/Slave In) provides communication from PoE Controller to PD69012s.

- MISO (Master In/Slave Out) provides communication from PD69012s to PoE Controller.

- **SCK** is a serial clock generated by the Controller.

- CS (Chip Select) is utilized by the PoE Controller to transmit data to all PD69012s simultaneously, while only the chosen PoE manager responds back.

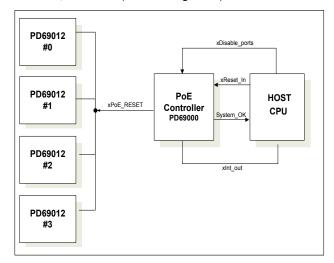

#### Control

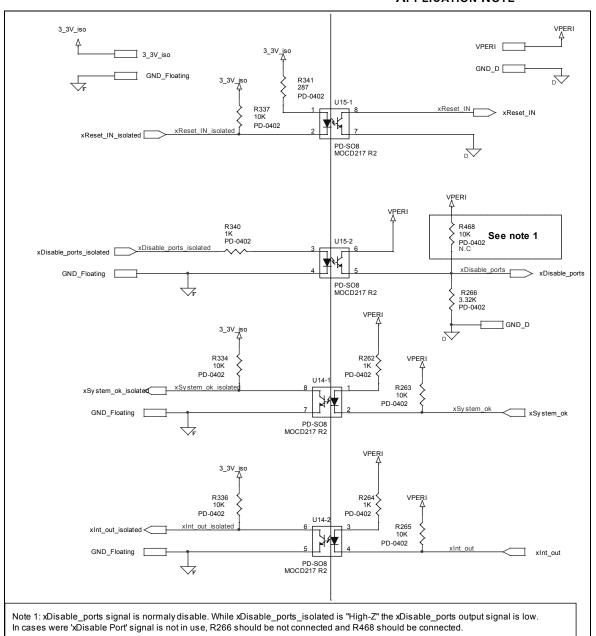

An **xReset\_IN\_isolated** control signal driven by Host CPU resets the PoE system.

An **xDisable\_ports\_isolated** control signal driven by Host CPU disables all PoE ports at once.

Refer to Figure 3.

#### Indications

A digital output signal, **xSystem\_ok\_isolated** derived from PoE Controller, indicates main input voltage is within range.

PoE Controller produces an **xInt\_out\_isolated** interrupt signal which indicates PoE events.

#### **Communication Flow**

Host CPU issues commands, utilizing a dedicated Serial Communication Protocol to PoE Controller via isolated I/O lines. This isolation is a basic requirement of IEEE PoE standards.

PoE Controller converts Serial Communication Protocol to the required register configuration, for storage in PD69012.

#### Main Supply

PoE system operates within a range of 44 to 57V (802.3at port's range is 50 to 57V). To comply with UL SELV regulations, maximum output voltage **should not** exceed 60V.

When utilizing DC Disconnect function, the PoE system can operate over up to 57V. However, AC Disconnect function requires a 5V level to be added to supply voltage (55 + 5 = 60V).

Therefore, maximum input voltage **should not** exceed 55V. Supplied voltage must be isolated from Switch supply and chassis by 1500V<sub>rms</sub>.

#### **Grounds**

Several grounds are utilized in the system:

- Chassis

- Digital

- GND\_Analog\_CPU (Controller's ground)

- Analog

Chassis ground is connected to switch's chassis ground. This ground plane should be  $1500V_{rms}$  isolated from PoE circuitry.

Digital, **GND\_Analog\_CPU** and analog grounds are electrically same ground. However, to reduce noise coupling, grounds are physically separated and connected only at a single point.

This is further detailed in the AN-175 Application Note, catalogue number 06-0055-080.

#### 3.3V Regulator

Each PD69012 has a 3.3V regulator (EXT\_REG & VPERI) providing up to 6mA. This current is utilized for powering components external to PoE domain; those components must also be isolated by 1500V<sub>rms</sub> from the switch circuitry.

#### **APPLICATION NOTE**

An external transistor can be connected to output port to increase current. Q1 can provide up to 30mA to PoE Controller and to opto-couplers in the interface circuitry (refer to Figure 6).

## **Detailed Circuit Description**

Following sections describe Overall Block Diagram (refer to Figure 6).

#### Communication Interfaces

There are two communication interfaces in this circuitry:

- Between Ethernet switch and PoE Controller; this interface is a 1500V<sub>rms</sub> isolation UART interface or an I<sup>2</sup>C interface. Note that each circuitry's side is fed by a separate power supply. Isolation circuit is detailed in Figure 12.

- Between PoE Controller and PoE managers; interface used here is a standard ESPI.

#### **Control and Indication Signals**

Control/Indication signals are of the single H/W lines type, running between Host CPU and PoE Controller. These signals are optically coupled to achieve 1500V<sub>rms</sub> isolation (refer to Figure 3).

Figure 3: Control and Indication Signals

#### **Control Signals**

There are two control lines driven by Host CPU to PoE Controller:

- xDisable\_ports: Disables all PoE ports. When PoE Controller detects low level voltage at pin #29 it sends a disable command via ESPI to PoE manager's ports.

- \* xReset\_In: Resets PoE Controller and all PoE managers. When the PoE Controller detects low level voltage at pin #1 it enters Reset mode and all its output pins switch to Tri-state mode. When xReset\_In line returns to 'high', PoE Controller initializes and sends (upon a flag state) 'low' level

logic to PoE managers via **xPoE\_RESET** line (pin # 32).

#### **Indication Signals**

Two signals are utilized to provide Host CPU with the following event indications.

- System\_OK: Indicates main voltage is within desired range.

- xint\_out: Interrupt signal coming from PoE Controller, indicating events such as Port On, Port Off, Port Fault, PoE Manager Fault, Voltage out of Range, etc.

For full list of interrupt events, refer to serial communication protocol, *User Guide 06-0032-056*.

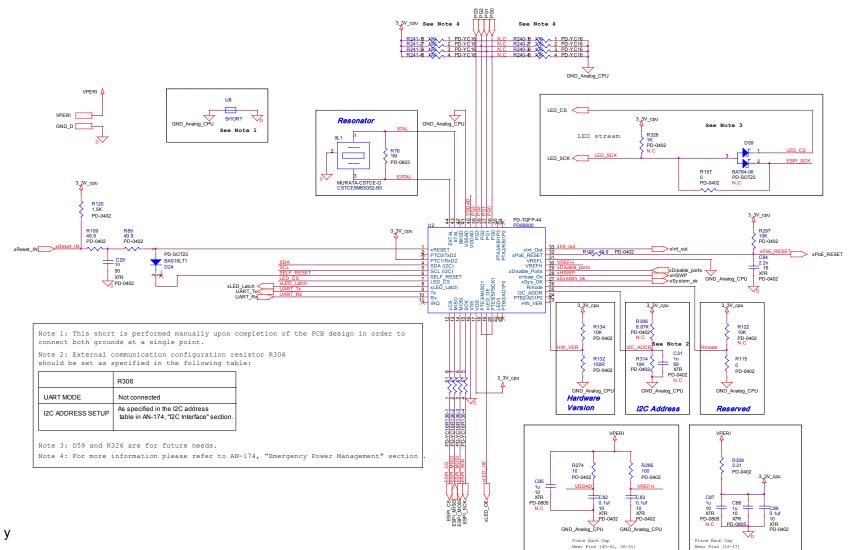

#### **PoE Controller Circuitry**

Refer to Figure 7.

PoE Controller features 1.2Mb/s ESPI for each of the PoE managers, and a communication interface with Host CPU via UART or I<sup>2</sup>C protocol.

UART or I<sup>2</sup>C communication between Host CPU and PoE Controller are managed by setting the address of pin #25 of PoE Controller (I<sup>2</sup>C\_ADDR). For UART and I<sup>2</sup>C communication address table, refer to I<sup>2</sup>C Interface, page 6.

PoE Controller runs at about 10MHz, facilitated by an external resonator XL1.

PoE Controller requires stable, filtered power for its operation. Therefore a number of components are included in the design:

- C86 and C89: Used for filtering and stabilization of V<sub>PERI</sub> voltage generated by PD69012 circuitry and Q1.

- C82 and C83: Used for filtering reference voltages (V<sub>DDAD</sub> and V<sub>REFH</sub>).

- VPERI: PoE Controller's 3.3V operating voltage is obtained from PoE manager Circuitry #0 via current driver Q1 (refer to Figure 6). This device can provide up to 30mA, based on the application requirements.

- SELF\_RESET: As required by the application, PoE Controller can self-reset itself. This reset can also be performed by an external source utilizing xReset\_In signal (usually by Host Controller).

- HW\_VER (Hardware Version): This input line provides a hardware configuration indication to PoE Controller. This line is factory controlled and may not be changed (voltage divider R134/R132).

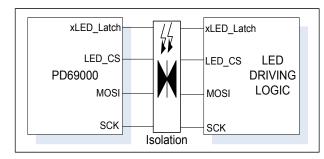

### **LED Support**

Refer to Figure 4.

LED support for port status indication is provided by **SPI bus** (SCK and MOSI), **LED\_CS** and **xLED\_Latch** signals. Bus behavior is synchronous serial communication (Clock, Data) in one direction (write only), 100kb/s, transmitting the status of up to 96 ports. Packet is transmitted with Start header and End header bytes. For more details, refer to *Technical Note-118 catalogue number 06-0008-081*.

#### **APPLICATION NOTE**

Figure 4: SPI Bus and LED Support

#### **Emergency Power Management**

PoE circuits can be powered by up to four separate power supplies (refer to Figure 5). It is recommended each power supply be capable of generating a logic signal that indicates its operate/fail status. Two logical output signals can be derived from PSU:

- Power good signal (default)

- PG = logical '1'; indicates operational power supply

- PG = logical '0'; indicates failed power supply

In this mode, R241 should not be connected, whereas R240 should be connected in a pull-down configuration.

- xPower good signal

- PG = logical '0'; indicates operational power supply

- PG = logical '1'; indicates failed power supply

In this mode only R241 is connected in a pull-up configuration.

The PoE circuit allocates power to the system in accordance with overall available power derived from logic signals that arrive from power supplies. With four power supplies that have up to four different output power levels; up to sixteen power banks can be derived from their combinations. Pins being used are as follows:

| Pin<br>Number | Signal | Remarks      |

|---------------|--------|--------------|

| #36           | PG0    | Power Good 0 |

| #37           | PG1    | Power Good 1 |

| #38           | PG2    | Power Good 2 |

| #39           | PG3    | Power Good 3 |

If PG pin is not used, pin can be connected to GND or  $V_{peri}$  (according to the appropriate PG logic) with no resistor. Figure 5 illustrates the connections between power supplies' logic signals and PoE Controller.

#### R2415 Logic PG0 PS1 PIG 50 W Vperi PG1 PS2 PIG R240 60 W PD69000 Vmain Vperi T R241≸ PG2 P.G PS3 70 W Vperi R241 PG3 PS4 100 W

Figure 5: Power Good

For isolation requirement destined for Emergency Power Management, refer to *Technical Note-134 catalogue number 06-0014-081*; "Isolation Requirements Section".

#### **xHSWP - PoE Hot Swap Functionality**

Hot swapping (hot plugging) functionality is the capability to remove and replace PoE system while units are operating. PoE system can be plugged and unplugged only while using dedicated hot swap hardware (not included in this application note). An <a href="xHSWP">xHSWP</a> signal is issued from PoE Controller to hot swapping hardware to control it.

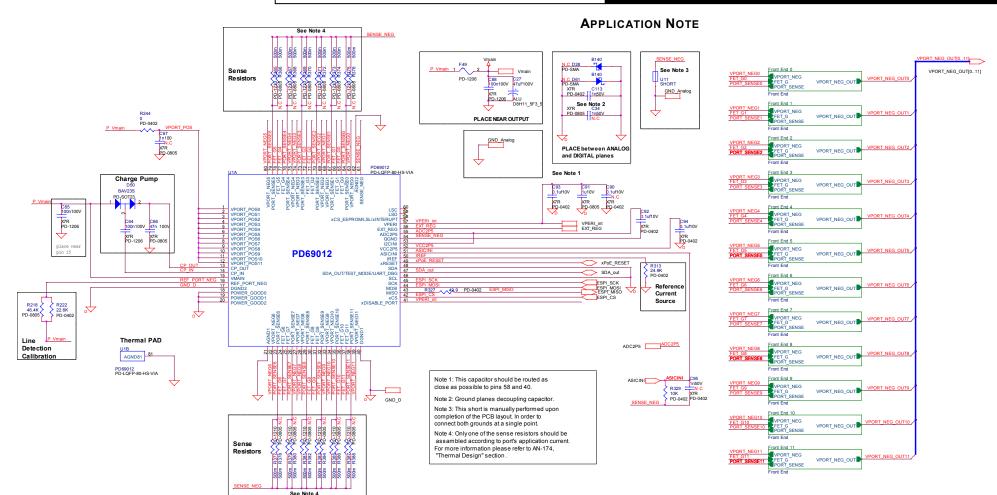

#### PoE Manager Circuitry

Refer to Figure 8.

PD69012 performs a variety of internal operations and PoE functions that require a minimum of external components. Each PD69012 handles up to 12 ports. Figure 8 shows PoE Manager #0 with its related components for a 12-port configuration.

**Note** For the solution described in this Application Note (48-port), multiply by four the circuitry shown in Figure 8.

#### **Enhanced Mode Configuration**

Set by R328/R329 divider tied to the ASICINI line (R328/Figure 6). Divider's voltage value is set at Enhanced Mode operation to configure PoE manager to Slaves 0-7, as specified in the following table:

#### **APPLICATION NOTE**

|          |                    |                    | Resistors<br>Value |                |  |

|----------|--------------------|--------------------|--------------------|----------------|--|

| ASIC_INI | Minimum<br>Voltage | Maximum<br>Voltage | R329<br>(low)      | R328<br>(high) |  |

| Slave0   | 0.19               | 0.29               | 10000              | 93100          |  |

| Slave1   | 0.35               | 0.44               | 10000              | 52300          |  |

| Slave2   | 0.51               | 0.6                | 10000              | 34800          |  |

| Slave3   | 0.67               | 0.75               | 10000              | 24900          |  |

| Slave4   | 0.83               | 0.9                | 10000              | 18700          |  |

| Slave5   | 0.99               | 1.06               | 10000              | 14300          |  |

| Slave6   | 1.15               | 1.21               | 10000              | 11300          |  |

| Slave7   | 1.3                | 1.36               | 10000              | 8870           |  |

#### **Line Detection Calibration**

When performing line detection procedure, PoE manager utilizes certain voltage levels over output port. To accurately set these levels, reference voltages are developed across a parallel combination of R218 and R222.

This combination simulates the equipment tied to the port.

#### **Reference Current Source**

Reference for internal voltages within PD69012 is set by a precision resistor (R313).

#### Charge Pump

An increase of 5V over power supply main input (44 to 55V, +5V) is required.

5V increase is implemented by a Charge-Pump circuitry that utilizes three elements:

- A self-sustaining clock mechanism, utilized to start and keep the process going. This is performed in PD69012 internally.

- Energy transfer element (C64 and C66).

- Switching diode to constrain energy flow in one direction (D50).

#### **Sense Resistors**

A  $500m\Omega$  (or  $487m\Omega$ ), (1%) sense resistor is connected to port output line. This resistor measures port's current.

Resistance of resistor with its traces should be close to  $500m\Omega$ . For more information, refer to *Layout Design Guidelines*, *catalogue number 06-0055-080*.

#### Low Pass Filter

Each of the output ports includes internal protection circuitry against external discharges that may damage PD69012. C67 and R244 create a path to the ground which limits damaging potentials (for circuitry of PoE Manager #0).

#### **Protection Fuse for Abnormal Operating Voltage**

When an IC experiences an input voltage above its absolute maximum rating, it is exposed to unexpected damage. Since PoE manager is connected to a high current source, best design practice is to use a protection fuse (F49) to avoid high current path during PSU over voltage faults.

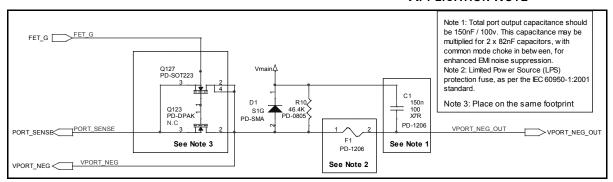

#### Front-end Circuitry

Refer to Figure 9.

This circuit is an analog front-end destined for a single port. For this application note, circuit is to be multiplied up to 48 times in accordance with the number of PoE ports in the system.

#### **Output Ports**

Refer to Port 0.

Output port circuitry is shown in Figure 9. Note that R10 (46.4k) is of the same value as R218, used as a line detection calibration resistor (Refer to Figure 9). Each port In turn is supplied with a constant current across this resistor.

Load resistance of PD attached to port is calculated in parallel with R10. Resulting voltage developed across both resistances is compared to calibration source (R218 || R222) voltage, which establishes terminal's validity. Other components are also used:

- D1 is a polarity reversal diode, used to prevent a reversed voltage from an external source.

- C1 forms a noise suppression component.

- F1 is utilized as a current limiting device, operating as specified in IEC 60950-1:2001. If the power supply is lower than 100W it is not required.

Note If output port circuitry is not fully populated, meaning 10 ports instead of 12, then unused ports are to be wired as follows: PORT\_SENSE and FET\_G should be tied to AGND, and VPORT\_NEG should be tied to V<sub>main</sub> nets. The following components can be removed for unused channels: Q127, C1, F1, D1, and R10.

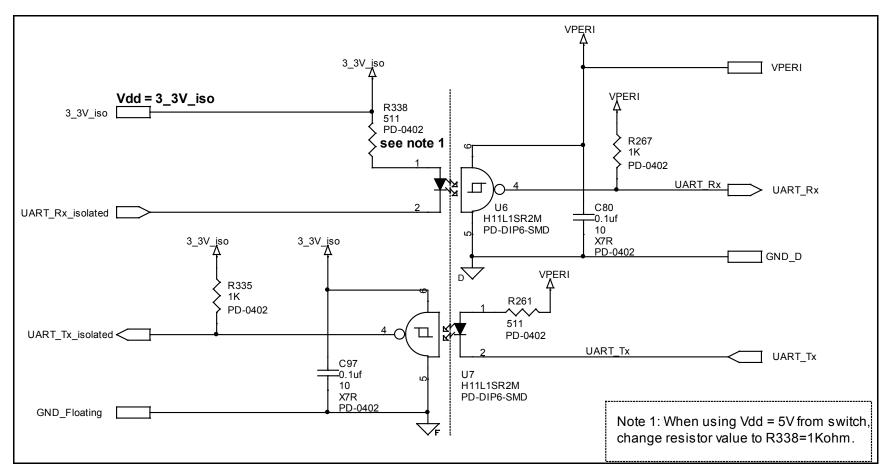

### **UART Interface Circuitry**

Refer to Figure 12.

Isolation circuitry comprises opto-couplers that are destined to provide 1500V<sub>rms</sub> isolation required by standard (IEEE 802.3af and IEEE802.3at).

Circuit supports:

- 3.3V (or 5V) TTL level signals

- 19,200 bps

- 8 bit

- No parity

- 1 stop bit

#### APPLICATION NOTE

No flow control

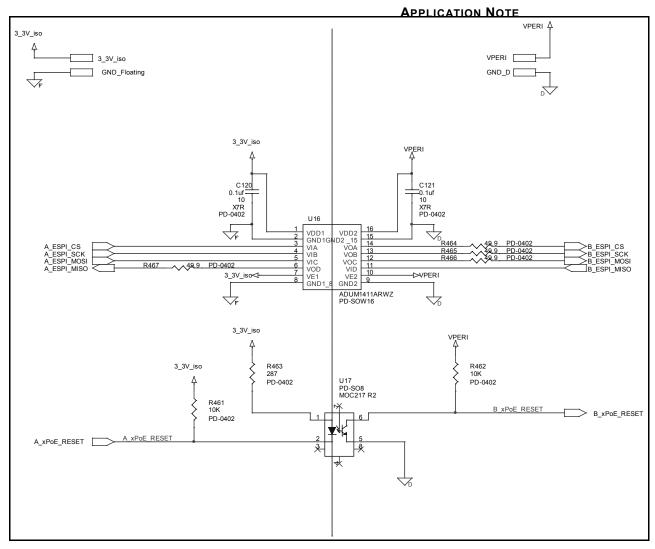

#### I<sup>2</sup>C Interface

Refer to Figure 13 and Figure 14.

PoE Controller can communicate with hosting system using UART or I<sup>2</sup>C communication.

For I<sup>2</sup>C interface, cost effective design is to place PoE Controller in Host domain and isolate ESPI bus and reset signals (refer to Figure 2; PoE Controller is 1500V<sub>rms</sub>, isolated from PoE manager domain).

- To design a 48 port Enhanced PoE system with UART interface, refer to Figure 6 through Figure 12.

- To design a 48 port Enhanced PoE system with an I<sup>2</sup>C interface, refer to Figure 7 through Figure 10, and Figure 13 through Figure 14.

- An SDA signal should be connected to pin #4 of the PoE Controller. An SCL signal should be connected to pin #5 of the PoE Controller.

I<sup>2</sup>C communication between Host CPU and PoE Controller is managed by setting PoE Controller's address. This is done by selecting a value for R306. This resistor sets analog level into pin #25 (I2C\_ADDR) as specified in the following table.

| l <sup>2</sup> C<br>Address | Address<br>(hex) | R306<br>(ohms) | l <sup>2</sup> C<br>Address | Address<br>(hex) | R306<br>(ohms) |

|-----------------------------|------------------|----------------|-----------------------------|------------------|----------------|

| #0                          | UART             | NA             | #8                          | 0x20             | 8870           |

| #1                          | 0x4              | 97600          | #9                          | 0x24             | 6810           |

| #2                          | 0x8              | 53600          | #10                         | 0x28             | 5230           |

| #3                          | 0xC              | 35700          | #11                         | 0x2C             | 3920           |

| #4                          | 0x10             | 25500          | #12                         | 0x30             | 2800           |

| #5                          | 0x14             | 19100          | #13                         | 0x34             | 1870           |

| #6                          | 0x18             | 14700          | #14                         | 0x38             | 1020           |

| #7                          | 0x1C             | 11300          | #15                         | 0x3C             | 324            |

#### **Ground Interface Connection (AGND)**

Power supplies ground connector J4 (refer to Figure 6) enables the current a path back to power supply.

Ground connection should be capable of carrying all strings current back to power supplies.

#### Thermal Design

Design for 802.3at PoE standard should take into account power dissipation of PoE manager, power dissipation of associated circuitry, and maximum ambient operating temperature of switch. Adequate ventilation and airflow should be part of design to avoid thermal over-stress on the following components:

#### **Ambient Temperature**

Application's thermal design should take into account temperature derived from Switch's power dissipation and from PoE daughter board, powered at maximum load.

#### PD69012 Maximum Operating Temperature

PoE design should ensure PD69012's maximum operating junction temperature (150° C) is **not** exceeded under worst case conditions. Worst case conditions typically involve operation under maximum ambient temperature, output ports fully loaded at 802.3at power, and all other unit functions fully operational. *PD69012 datasheet, catalogue number 06-0069-058* contains additional thermal characteristics details.

#### PD69000

Layout considerations should ensure that:

- PD69000 is placed away from potential high temperature spots.

- Maximum case temperature does not exceed 85°C under worst case conditions.

#### **Sense Resistors**

Refer to Figure 8.

Each port's front-end circuit has a single sense resistor. Resistor's value should be  $500m\Omega$  (or  $487m\Omega$ ). It dissipates about 0.26W at 720mA (802.3at maximum load) and 62 mW at 350 mA (802.3af maximum load). Resistors should be placed near PD69012 to achieve maximum current accuracy. Heat generated from these resistors contributes to a higher ambient temperature near PD69012. For 802.3af ports, use the following sense resistors types:

| QTY for<br>12 Ports | Description                     | PCB<br>Footprint | Manufa. | Manufa. Part<br>Number |

|---------------------|---------------------------------|------------------|---------|------------------------|

| 12                  | RES TCK FLM<br>0.500R 1% 125 mW |                  |         | LCR0805R500F           |

|                     | 0805 SMT                        | PD-0805          | Venkel  | SNT                    |

|                     | RES TCK FLM                     |                  |         |                        |

| 12                  | 0.487R 1% 125 mW                |                  |         | SR732ETTDR4            |

|                     | 0805 SMT                        | PD-0805          | Koa     | 87F                    |

For 802.3at ports use, the following sense resistors types:

| QTY for<br>12 Ports | Description   | PCB<br>Footprint | Manufa.  | Manufa. Part<br>Number |

|---------------------|---------------|------------------|----------|------------------------|

|                     | RES TCK FLM   |                  |          |                        |

|                     | 0.500R 1% 500 |                  |          | LCR1210R5              |

| 12                  | mW 1210 SMT   | PD-1210          | Venkel * | 00FSNT-MS              |

|                     | RES TCK FLM   |                  |          |                        |

|                     | 0.487R 1% 500 |                  |          | LCR1210R487            |

| 12                  | mW 1210 SMT   | PD-1210          | Venkel * | FSNT-MS                |

\*Dedicated part number for Microsemi PoE application; preferential pricing for Microsemi customers.

**Note** Sense resistor's temperature coefficient of resistance (ppm) must be less than or equal to  $\pm 200 \ [10^{-6}\ ]^{\circ} \ C]$

#### **Power MOSFETs**

Refer to Figure 8.

Each port circuit has a single external Power MOSFET. Design should ensure maximum operating junction

#### **APPLICATION NOTE**

temperature of MOSFET (150°C or 175°C as specified in MOSFET's datasheet) is **not** exceeded under worst case conditions.

For more details on how to examine and choose a MOSFET for a PoE application, refer to the 'How to choose MOSFET for 802.3at and 802.3af PoE applications' Technical Note, catalogue number 06-0022-081. Examples for approved MOSFETs are shown in the following tables:

Table 1: 802.3af - MOSFETs Examples

| # | PCB<br>Footprint | Manufacturer | Manufacturer's Part<br>Number |  |

|---|------------------|--------------|-------------------------------|--|

| 1 | SOT-223          | Fairchild    | IRLM110A                      |  |

| 2 | DPAK             | Fairchild    | FQD5N15                       |  |

| 3 | SOT-223          | Infineon     | BSP372                        |  |

Table 2: 802.3at - MOSFETs Examples

| # | PCB<br>Footprint | Manufacturer | Manufacturer's Part<br>Number |  |  |

|---|------------------|--------------|-------------------------------|--|--|

| 1 | DPAK             | Fairchild    | FQD19N10L                     |  |  |

| 2 | SOT-223          | Fairchild    | FDT3612_SB82273 *             |  |  |

| 3 | DPAK             | ST           | STD10NF10T4                   |  |  |

| 4 | DPAK             | IR           | IRFR3910                      |  |  |

| 5 | SOT-223          | Infineon     | BSP373                        |  |  |

\*Dedicated part number for Microsemi PoE application; preferential pricing for Microsemi customers.

Figure 6: Overall Block Diagram for 48-port Enhanced System (UART Interface)

Figure 7: PD69000 PoE Controller Circuitry

Figure 8: PD69012 Circuitry for PoE Manager #0

Figure 9: Front-End Circuitry

Figure 10: Vport Out (Port's Interface)

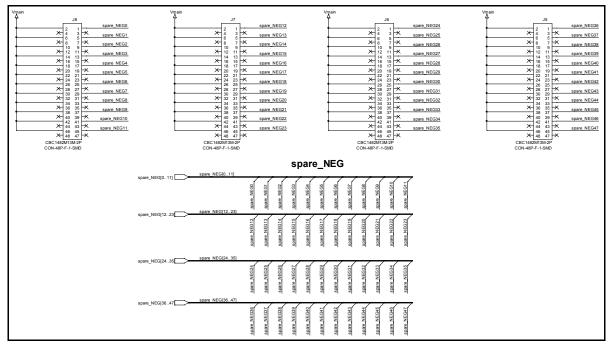

Figure 11: Control and Indication Isolation Circuitry

Figure 12: UART Isolation Circuitry

Figure 13: Overall Block Diagram for 48-port Enhanced System (I<sup>2</sup>C Interface)

Figure 14: ESPI Isolation Circuitry

#### **APPLICATION NOTE**

## **Bill of Materials for a PoE System**

**Table 3: Main Block Components**

| Block | Qty | Reference | Description                                           | PCB Foot<br>Print     | Manufacturer | Manufacturer's Part<br>Number      |

|-------|-----|-----------|-------------------------------------------------------|-----------------------|--------------|------------------------------------|

|       | 1   | J2        | Pin Header Dual Raw<br>Board mount 16 Pin p<br>2mm TH | CVILUX-<br>CH74-16P-V | CviLux       | CH74162V100                        |

|       | 1   | J3        | Pin Header Dual Raw<br>Board mount 30 Pin p<br>2mm TH | CVILUX-<br>CH74-30P-V | CviLux       | CH74302V100                        |

|       | 1   | J4        | Pin Header male<br>1 row 8 pins<br>Horizontal         | CVILUX-<br>CI52-8P-H  | CviLux       | CI5208P1H00                        |

|       | 1   | Q1        | TRN NPN 250V 1A<br>15W D-Pak SMT                      | PD-DPAK               | Fairchild    | MJD47                              |

| Main  | 1   | R328      | RES SMT 93.1KΩ<br>1% 1/16w 0402                       | PD-0402               | Rohm         | MCR01MZPF9312<br>Bottom of Form    |

|       | 1   | R358      | RES TCK FLM 10K<br>1% 62.5 mW 0402<br>SMT             | PD-0402               | Vishay       | CRCW0402-10K0 1% ET1<br>E3         |

|       | 1   | R360      | RES TCK FLM 24.9K<br>1% 62.5mW 0402<br>SMT            | PD-0402               | Yageo        | RC0402FR-0724K9                    |

|       | 1   | R361      | RES SMT 53.6 KΩ<br>1% 1/16 w 0402                     | PD-0402               | Yageo        | RC0402FR-0753K6L<br>Bottom of Form |

|       | 1   | R362      | Resistor, SMT 34.8K, 1%, 1/16W 0402                   | PD-0402               | Rohm         | MCR01MZPF3482                      |

|       | 1   | R339      | RES TCK FLM 10K<br>1% 62.5mW 0402<br>SMT              | PD-0402               | Vishay       | CRCW0402-10K0 1% ET1<br>E3         |

#### **Table 4: PoE Controller Components**

|            |     | 1                   |                                             | naronor comp     | 1                |                               |

|------------|-----|---------------------|---------------------------------------------|------------------|------------------|-------------------------------|

| Block      | Qty | Reference           | Description                                 | PCB<br>Footprint | Manufacturer     | Manufacturer's Part<br>Number |

|            | 1   | C29                 | CAP CER 1 nF 50V<br>X7R 10% 0402 SMT        | PD-0402          | Murata           | GRM36R71H102KA01L             |

|            | 3   | C82, C83,<br>C89    | CAP CER 0.1µF 10V<br>X7R 10% 0402 SMT       | PD-0402          | Murata           | GRM155R71C104KA88D            |

|            | 1   | C84                 | CAP CER 2.2nF 16V<br>X7R 10% 0402 SMT       | PD-0402          | Yageo            | CC0402KRX7R7BB222             |

|            | 1   | C86                 | CAP CRM 1µF 10V<br>10% X7R 0805 SMT         |                  |                  |                               |

|            | 1   | C80                 | DIO 75V 200mA<br>SOT23 SMT                  | PD-0805          | Phycomp          | 2222-240-15663                |

|            | 1   | D24                 | trr=4nSEC SWI                               | PD-SOT23         | ON Semiconductor | BAS16LT1                      |

|            | 1   | R76                 | RES 1M 62.5mW 1%<br>0603 SMT MTL FLM        | PD-0603          | Samsung          | RC1608F1004CS                 |

| PoE        | 3   | R89, R100,<br>R109  | RES TCK FLM 49.9R<br>1% 62.5mW 0402<br>SMT  | PD-0402          | Bourns           | CR0402-FX-49R9-ELF            |

| Controller | 2   | R115, R157          | RES 0R 62.5mW 5%<br>0402 SMT MTL FLM        | PD-0402          | Vishay           | CRCW0402-0R0 5% ET1 E3        |

|            | 1   | R120                | RES TCK FLM 1.5K<br>1% 62.5mW 0402<br>SMT   | PD-0402          | Vishay           | CRCW0402-1K50 1% ET1<br>E3    |

|            | 1   | R132                | RES TCK FLM 150R<br>1% 62.5mW 0402<br>SMT   | PD-0402          | Yageo            | RC0402FR-07150RL              |

|            | 3   | R134, R297,<br>R314 | RES TCK FLM 10K<br>1% 62.5mW 0402<br>SMT    | PD-0402          | Vishay           | CRCW0402-10K0 1% ET1<br>E3    |

|            | 1   | R136                | RES NET 4X51R<br>62.5mW 5% ISOL<br>1206 SMT | PD-YC16          | СТЅ              | 742X083510JP                  |

|            | 1   | R241                | RES 10K 62.5mW<br>5% 1/4_1206 NET<br>QUAD   | PD-YC16          | Vishay           | CRA06S08310K0JTA              |

#### **APPLICATION NOTE**

| Block             | Qty | Reference | Description                                | PCB<br>Footprint   | Manufacturer | Manufacturer's Part<br>Number |

|-------------------|-----|-----------|--------------------------------------------|--------------------|--------------|-------------------------------|

| PoE<br>Controller |     |           | RES TCK FLM 10R<br>1% 62.5mW 0402          |                    |              |                               |

|                   | 1   | R274      | SMT                                        | PD-0402            | Bourns       | CR0402-FX-0100-ELF            |

|                   |     |           | RES TCK FLM 100R<br>1% 62.5mW 0402         |                    |              |                               |

|                   | 1   | R295      | SMT                                        | PD-0402            | Bourns       | CR0402-FX-1000-ELF            |

|                   | 1   | R308      | RES TCK FLM 2.21R<br>1% 62.5mW 0402<br>SMT | PD-0402            | Vishav       | CRCW04022R21FKED              |

|                   | 1   | U2        | PoE Controller                             | PD-TQFP-44         | Microsemi    | PD69000                       |

|                   | 1   | XL1       | Resonator 9.83MHz<br>SMT                   | MURATA-<br>CSTCE-G | Murata       | CSTCE9M83G52-B0               |

#### **Table 5: PoE Manager Slave Components**

|         | Table 5: PoE Manager Slave Components |             |                                       |                     |                |                            |  |  |

|---------|---------------------------------------|-------------|---------------------------------------|---------------------|----------------|----------------------------|--|--|

| Block   | QTY*                                  | Reference   | Description                           | PCB Footprint       | Manufacturer   | Manufacturer's Part Number |  |  |

|         |                                       |             | CAP ALU 47µF 100V 20%                 |                     |                |                            |  |  |

|         |                                       |             | 8X11.5 105C P = 3.5mm                 | D8H11_5F            |                |                            |  |  |

|         | 11                                    | C27         | T/H                                   | 3_5                 | Rubycon        | 100PX47M T7 8X11.5         |  |  |

|         |                                       | C64, C65,   | CAP CRM 100nF 100V                    | DD 4000             | A \            | 400040404164704            |  |  |

|         | 2                                     | C88         | 10% X7R 1206 SMT<br>CAP CRM 47nF 100V | PD-1206             | AVX            | 12061C104KAT2A             |  |  |

|         | 1                                     | C66         | 10% X7R 0805 SMT                      | PD-0805             | Murata         | GRM40X7R473K100            |  |  |

|         | '                                     | C00         | CAP CRM 1µF 10V 10%                   | PD-0003             | iviui ala      | GRIVI40X/R4/3R100          |  |  |

|         | 1                                     | C91         | X7R 0805 SMT                          | PD-0805             | Phycomp        | 2222-240-15663             |  |  |

|         | <u>'</u>                              | C92, C93,   | CAP CER 0.1µF 10V X7R                 | 1 D-0003            | ТПусопір       | 2222-240-13003             |  |  |

|         | 3                                     | C94         | 10% 0402 SMT                          | PD-0402             | Murata         | GRM155R71C104KA88D         |  |  |

|         |                                       |             | CAP CER 1nF 50V X7R                   |                     |                |                            |  |  |

|         | 1                                     | C113        | 10% 0402 SMT                          | PD-0402             | Murata         | GRM36R71H102KA01L          |  |  |

|         |                                       |             | DIO DUAL 250V 225mA                   |                     |                |                            |  |  |

|         |                                       |             | SMT SOT23 trr = 50nS                  |                     |                |                            |  |  |

|         | 1                                     | D50         | SERIAL PH                             | PD-SOT23            | Philips        | BAV23S                     |  |  |

|         |                                       |             | RES TCK FLM 46.4K                     |                     |                |                            |  |  |

| PoE     | 1                                     | R218        | 125mW 1% 0805 SMT                     | PD-0805             | EPCOS          | B54102-A2463-F460          |  |  |

| Manager |                                       | D000        | RES TCK FLM 22.6K 1%                  | DD 0400             | \ fi = le =    | CRCW0402-22K6 1% ET1       |  |  |

| Slave   | 1                                     | R222        | 62.5mW 0402 SMT                       | PD-0402             | Vishay         | E3                         |  |  |

|         | 1                                     | R244        | RES 0R 62.5mW 5% 0402<br>SMT MTL FLM  | PD-0402             | Vishay         | CRCW0402-0R0 5% ET1 E3     |  |  |

|         | '                                     | R244        | RES TCK FLM 24.9K 1%                  | PD-0402             | VISITAY        | CRCW0402-0R0 5% E11 E3     |  |  |

|         | 1                                     | R313        | 62.5mW 0402 SMT                       | PD-0402             | Yageo          | RC0402FR-0724K9            |  |  |

|         |                                       | 11010       | RES TCK FLM 49.9R 1%                  | 1 2 0 102           | ragoo          | 1100102111 0121110         |  |  |

|         | 1                                     | R327        | 62.5mW 0402 SMT                       | PD-0402             | Bourns         | CR0402-FX-49R9-ELF         |  |  |

|         |                                       | -           | RES TCK FLM 10K 1%                    |                     |                | CRCW0402-10K0 1% ET1       |  |  |

|         | 1                                     | R329        | 62.5mW 0402 SMT                       | PD-0402             | Vishay         | E3                         |  |  |

|         |                                       | R365, R367, |                                       |                     | •              |                            |  |  |

|         |                                       | R369, R371, |                                       |                     |                |                            |  |  |

|         |                                       | R373, R375, |                                       |                     |                |                            |  |  |

|         |                                       | R377, R379, | o //o.w                               |                     |                |                            |  |  |

|         | 10                                    | R381, R383, | Res 500mΩ 1/2 W                       | DD 4040             | Mankal         | LODADAODEOOEONE MOSS       |  |  |

|         | 12                                    | R385, R387  | 200 ppm 1210<br>12-port High PoE PSE  | PD-1210<br>PD-LQFP- | Venkel         | LCR1210R500FSNT-MS**       |  |  |

|         | 1                                     | U1          | Manager                               | 80-HS-VIA           | MICROSEMI      | PD69012                    |  |  |

|         |                                       | 01          | FUSE 1.5A 63V V. FST                  | 00-110-VIA          | IVIIOINOGLIVII | 1 000012                   |  |  |

|         | 1                                     | F49         | BLO 1206 SMT                          | PD-1206             | Bussmann       | TR1/CC12PD-1.5A –R**       |  |  |

|         |                                       | . 10        |                                       | . 2 .200            |                | 30121 2 1.0/1 11           |  |  |

<sup>1. ☐</sup> These quantities should be multiplied by the number of **PD69012** (four managers in this paper)

Microsemi

<sup>\*\*</sup>Special part number for Microsemi PoE application; preferential pricing for Microsemi customers.

#### **APPLICATION NOTE**

#### **Table 6: Front End Components**

| Block     | Qty* | Reference | Description                                           | PCB Footprint | Manufacturer | Manufacturer's Part Number     |

|-----------|------|-----------|-------------------------------------------------------|---------------|--------------|--------------------------------|

|           | 1    | C1        | CAP CRM 150nF 100V<br>10%^^X7R 1206 SMT               | PD-1206       | Syfer        | 1206J1000154KXT                |

|           | 1    | D1        | DIO RECOV. REC 400V<br>1A SMA SILICON SMT             | PD-SMA        | Diodes Inc.  | S1G                            |

| Front End | 1    | F1        | FUSE 1.5A 63V V. FST<br>BLO 1206 SMT                  | PD-1206       | Bussmann     | TR1/CC12PD-1.5A –R**           |

|           | 1    | Q127      | Transistor Fet N-Channel<br>100V<br>RES TCK FLM 46.4K |               |              | Refer to Power MOSFETs, page 7 |

|           | 1    | R10       | 125mW 1% 0805 SMT                                     | PD-0805       | EPCOS        | B54102-A2463-F460              |

<sup>1. ☐</sup> These quantities should be multiplied by the number of output ports (48 ports in this paper)

#### **Table 7: Vport out Components**

| QTY       |   | PCB       |                          |           |              |                            |

|-----------|---|-----------|--------------------------|-----------|--------------|----------------------------|

| Block     | * | Reference | Description              | Footprint | Manufacturer | Manufacturer's Part Number |

|           |   |           | Pin Header Female 2 rows | CON-48P-  |              |                            |

| Vport_out | 1 | J5        | 48 Pins P1.27x1.27       | F-1-SMD   | CviLux       | CBC1482M13M-2P             |

<sup>1.</sup> These quantities should be multiplied by the number of PD69012 (four managers in this paper)

#### **Table 8: Control and Indication Isolation**

| Block                  | QTY | Reference                          | Description                             | PCB Footprint | Manufacturer | Manufacturer's Part Number |

|------------------------|-----|------------------------------------|-----------------------------------------|---------------|--------------|----------------------------|

|                        | 3   | R262, R264,<br>R340                | RES TCK FLM 1K 1%<br>62.5mW 0402 SMT    | PD-0402       | Bourns       | CR0402-FX-1001-E           |

| Control and Indication | 6   | R263, R265,<br>R334, R336,<br>R337 | RES TCK FLM 10K 1%<br>62.5mW 0402 SMT   | PD-0402       | Vishay       | CRCW0402-10K0 1% ET1<br>E3 |

| Isolation              | 1   | R266                               | RES TCK FLM 3.32K 1%<br>62.5mW 0402 SMT | PD-0402       | Bourns       | CR0402-FX-3321-ELF         |

|                        | 1   | R341                               | Resistor, 287Ω, 1%, 1/16W 0402          | PD-0402       | ASJ          | CR10-2870FK                |

#### Table 9: Bill of Material for UART Communication Circuit (Host side 3\_3V\_iso = 3.3V)

| Block         | QTY | Reference                             | Description                            | PCB Footprint   | Manufacturer       | Manufacturer's Part Number |

|---------------|-----|---------------------------------------|----------------------------------------|-----------------|--------------------|----------------------------|

|               |     | CAP CER 0.1µF 10V X7R<br>10% 0402 SMT | PD-0402                                | Murata          | GRM155R71C104KA88D |                            |

| UART          | 2   | R261, R338                            | RES TCK FLM 511R 1%<br>62.5mW 0402 SMT | PD-0402         | Bourns             | CR0402-FX-5110-E           |

| Isolation 2 F |     | R267, R335                            | RES TCK FLM 1K 1%<br>62.5mW 0402 SMT   | PD-0402         | Bourns             | CR0402-FX-1001-E           |

|               | 2   | U6, U7                                | IC optoisolator SMT 6 pin              | PD-DIP6-<br>SMD | Fairchild          | H11L1SR2M                  |

#### Table 10: Bill of Material for ESPI Communication Circuit (Host side 3\_3V\_iso = 3.3V)

| Block             | QTY                    | Reference   | Description                                             | PCB Footprint | Manufacturer       | Manufacturer's Part Number |

|-------------------|------------------------|-------------|---------------------------------------------------------|---------------|--------------------|----------------------------|

|                   |                        |             | RES TCK FLM 10K 1%                                      |               |                    | CRCW0402-10K0 1% ET1       |

|                   | 2                      | R461, R462  | 62.5mW 0402 SMT                                         | PD-0402       | Vishay             | E3                         |

| ESPI<br>Isolation | 1                      | R463        | Resistor, 287 Ohm, 1%, 1/16W 0402                       | PD-0402       | ASJ                | CR10-2870FK                |

|                   | 2                      | C120, C121  | CAP CER 0.1µF 10V X7R<br>10% 0402 SMT                   | PD-0402       | Murata             | GRM155R71C104KA88D         |

|                   | 1                      | U16         | IC Dig.Isol VDD1-<br>3ch/VDD2-1ch 1 Mbps<br>3.3/5V SO16 | PD-<br>SOW16  | Analog Devices     | ADUM1411ARWZ               |

|                   | <u> </u>               | 0.0         | IC OPTOISOLATOR                                         | 3311.13       | ,a.og 2 0 1.000    | ,                          |

|                   | 1                      | U17         | MOC217                                                  | PD-SO8        | Fairchild          | MOC217 R2                  |

|                   |                        | R464, R465, | RES TCK FLM 49.9R 1%                                    |               |                    |                            |

|                   | 3 R466 62.5mW 0402 SMT |             | PD-0402                                                 | Bourns        | CR0402-FX-49R9-ELF |                            |

<sup>\*\*</sup>Special part number for Microsemi PoE application; preferential pricing for Microsemi customers.

#### **APPLICATION NOTE**

The information contained in the document is PROPRIETARY AND CONFIDENTIAL information of Microsemi and cannot be copied, published, uploaded, posted, transmitted, distributed or disclosed or used without the express duly signed written consent of Microsemi. If the recipient of this document has entered into a disclosure agreement with Microsemi, then the terms of such Agreement will also apply. This document and the information contained herein may not be modified, by any person other than authorized personnel of Microsemi. No license under any patent, copyright, trade secret or other intellectual property right is granted to or conferred upon you by disclosure or delivery of the information, either expressly, by implication, inducement, estoppels or otherwise. Any license under such intellectual property rights must be express and approved by Microsemi in writing signed by an officer of Microsemi.

Microsemi reserves the right to change the configuration, functionality and performance of its products at anytime without any notice. This product has been subject to limited testing and should not be used in conjunction with life-support or other mission-critical equipment or applications. Microsemi assumes no liability whatsoever, and Microsemi disclaims any express or implied warranty, relating to sale and/or use of Microsemi products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. The product is subject to other terms and conditions which can be located on the web at <a href="http://www.microsemi.com/legal/tnc.asp">http://www.microsemi.com/legal/tnc.asp</a>

#### **Revision History**

| Revision Level / Date  | Para. Affected                                          | Description                                                                                                     |

|------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 0.1 / 31 May. 08       | -                                                       | Initial Release – Preliminary version                                                                           |

| 0.2 / 31 June. 08      |                                                         | General modifications as a result of developement                                                               |

| 0.3 / 29 September. 08 |                                                         | General modifications as a result of developement                                                               |

| 0.4 / 25 October. 08   | Whole document                                          | 1. I <sup>2</sup> C interface supporting has been added.                                                        |

|                        |                                                         | xDisable_ports signal isolation has been changed from "Normaly Enable" to "Normaly Disable".                    |

| 0.5 / 25 January. 09   | Whole document                                          | Application modified to support sense resistor value of 500mohm and 487mohm     Draft 3.0 modified to Draft 3.3 |

| 0.6 / 7 May. 09        | "Front End" and<br>"ESPI isolation"<br>Bill of Material | 1. C1 capacitor value changed from 47nF to 150nF. 2. R463 Resistor value changed from 1KΩ to 287Ω.              |

| 1.0 / 6 Oct. 09        | Figure 8<br>Page 6                                      | Adding a protection fuse Protection fuse for abnormal operating voltage                                         |

| 1.2 / 31 Jan. 11       | Whole document                                          | General editing/ Thermal design redone                                                                          |

# © 2011 Microsemi Corp. All rights reserved.

For support contact: sales\_AMSG@microsemi.com

Visit our web site at: www.microsemi.com Catalog Number: 06-0054-080

Copyright © 2011 Rev. 1.2. 2011-01-31